3933中文资料

比较容易发表的几个核心期刊

医学类:《山东医药》、《时珍国医国药》、《护士进修》、《中国实验方剂学杂志》《体育文化导刊》国家体育总局文史工作委员会主办(月刊)ISSN:1671-1572 CN:11-4612/G8邮发代号:82-465 中文核心期刊(2008)《体育学刊》华南理工大学;华南师范大学主办(月刊)ISSN:1006-7116 CN:44-1404/G8 邮发代号:46-232该刊被以下数据库收录:Pж(AJ) 文摘杂志(俄)(2009)中文核心期刊(2008)期刊荣誉:Caj-cd规范获奖期刊《北京体育大学学报》北京体育大学主办(月刊)ISSN:1007-3612 CN:11-3785/G8 邮发代号:80-325该刊被以下数据库收录:中国人文社会科学引文数据库(CHSSCD—2004)中文核心期刊(2008)期刊荣誉:Caj-cd规范获奖期刊《武汉体育学院学报》武汉体育学院主办(月刊)ISSN:1000-520X CN:42-1105/G8该刊被以下数据库收录:Pж(AJ) 文摘杂志(俄)(2009) 中国人文社会科学引文数据库(CHSSCD—2004)中文核心期刊(2008)期刊荣誉:Caj-cd规范获奖期刊《山东体育学院学报》山东体育学院主办(月刊)ISSN:1006-2076 CN:37-1013/G8 邮发代号:44991中文核心期刊(2008)期刊荣誉:Caj-cd规范获奖期刊《新闻爱好者》河南日报报业集团主办(半月刊)ISSN:1003-1286 CN:41-1025/G2 邮发代号:36-94中文核心期刊(2008)《成都体育学院学报》成都体育学院主办(月刊)ISSN:1001-9154 CN:51-1097/G8 邮发代号:62-100该刊被以下数据库收录:中国人文社会科学引文数据库(CHSSCD—2004)中文核心期刊(2008)期刊荣誉:Caj-cd规范获奖期刊《图书馆建设》黑龙江省图书馆;黑龙江省图书馆学会主办(月刊)ISSN:1004-325X CN:23-1331/G2 邮发代号:14-162该刊被以下数据库收录:中国人文社会科学引文数据库(CHSSCD—2004)中文核心期刊(2008)《体育科学》中国体育科学学会主办(月刊)ISSN:1000-677X CN:11-1295/G8邮发代号:2-436该刊被以下数据库收录:中国人文社会科学引文数据库(CHSSCD—2004)中文核心期刊(2008)期刊荣誉:中科双效期刊Caj-cd规范获奖期刊《商业时代》杂志是全国中文核心期刊,中国商业联合会主管,中国商业经济学会主办,被权威学术类机构认定为“全国社科类核心期刊”、“全国贸易经济类核心期刊”。

杂志介绍

杂志介绍《教育研究与实验》全国教育学类中文核心期刊、CSSCI)来源期刊(双月刊)系中华人民共和国教育部主管、华中师范大学主办。

国内刊号CN42-1041/G4;国际刊号ISSN1003-160X。

邮发代号:38-144《科技管理研究》杂志由广东省科学学与科技管理研究会主办,是全国优秀科技期刊、全国中文核心期刊、中国人文社会科学引文索引(CSSCI)来源期刊、中国学术期刊统计源期刊,国际标准刊号:ISSN 1000-7695 国内统一刊号:CN 44-1223/G3,邮发代号:46-120《社会科学家》杂志由桂林市委主管,桂林市社会科学界联合会主办,是全国中文核心期刊,中国人文社会科学核心期刊,全国旅游经济类核心期刊,中文社会科学引文索引(CSSCI)国际统一刊号ISSN1002—3240 国内统一刊号CN45—1008/C邮发代号:48-48《经济纵横》杂志由吉林省社会科学院主办,被评定为全国“综合性经济科学类”核心期刊、全国中文核心期刊、中文社会科学引文索引(CSSCI)来源期刊。

国际标准刊号:ISSN 1007-7685国内统一刊号:CN22-1054/F 邮发代号 12-97。

《统计与决策》杂志由湖北省统计局主管、湖北省统计局统计科学研究所主办,是全国中文核心期刊,全国首届优秀经济期刊,中文社会科学引文索引(CSSCI)来源期刊,国内统一刊号:CN 42-1009/C国际统一刊号:ISSN 1002-6487邮发代号:38-150《河北法学》是由中共河北省委政法委员会主管,河北政法职业学院、河北省法学会主办的法学研究专业刊物,月刊,全国中文核心期刊、中国人文社会科学核心期刊、中文社会科学引文索引(CSSCI)来源期刊,国内刊号CN 13-1023/D,国际刊号ISSN 1002-3933,邮发代号18-68。

《理论前沿》是由中共中央党校主办,全国中文核心期刊,中国人文社会科学引文索引(CSSCI)来源期刊、国际统一刊号:ISSN1007-1962 国内统一刊号 CN:11-3807/D 邮发代号:82-2《毛泽东思想研究》由四川省社会科学院主管,四川省社会科学院、四川省社会科学界联合会、中共四川省委党史研究室共同主办,系全国第一家也是目前唯一一家公开出版的研究和宣传毛泽东思想的大型学术理论刊物。

HS93-00221中文资料

Hi-Pot (Vrms) 1500 1500 1500 3000 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500

Specifications

BI P/N1 RoHS2

3

Transformer Single Single Dual Dual Dual Dual Dual Dual Dual Dual Dual Dual Quad Quad

Turns Ratio5 (±5%) Primary : Secondary 1CT:2CT 1:1 1:2 & 1:2 1CS:2.5CS & 1CS:2.5CS 1CS:2.5CS & 1CS:2.5CS 1:2.5 & 1:2.5 1:1 & 1:1 1CS:2CS & 1CS:2CS 1 split:1 split & 1 split:1 split 1CT:2 & 1CT:2 1:2 & 1:2 1CT:1CT & 1CT:1CT 1:1 1:1.26

Style 6-pin DIL 6-pin DIL 6-pin DIL 10-pin DIL 12-pin SMT 14-pin DIL 14-pin DIL 14-pin DIL 16-pin DIL 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 16-pin SMT 32-pin SMT 32-pin SMT 32-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pin SMT 40-pinSMT 40-pin SMT 40-pin SMT

LM293中文资料_数据手册_参数

1OUT 1 1IN− 2 1IN+ 3 GND 4

8 VCC 7 2OUT 6 2IN− 5 2IN+

LM193 . . . FK PACKAGE (TOP VIEW)

NC 1OUT NC VCC NC

NC 1IN−

NC 1IN+

NCBiblioteka 3 2 1 20 194

18

5

17

6

16

7

15

8

14

9 10 11 12 13

NC 2OUT NC 2IN− NC

NC GND

NC 2IN+

NC

NC − No internal connection

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

FK package

150

°C

260

°C

Lead temperature 1,6 mm (1/16 in) from case for 60 s

J package

300

°C

Storage temperature range, Tstg

–65 to 150

°C

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

M393T2863AZ3中文资料

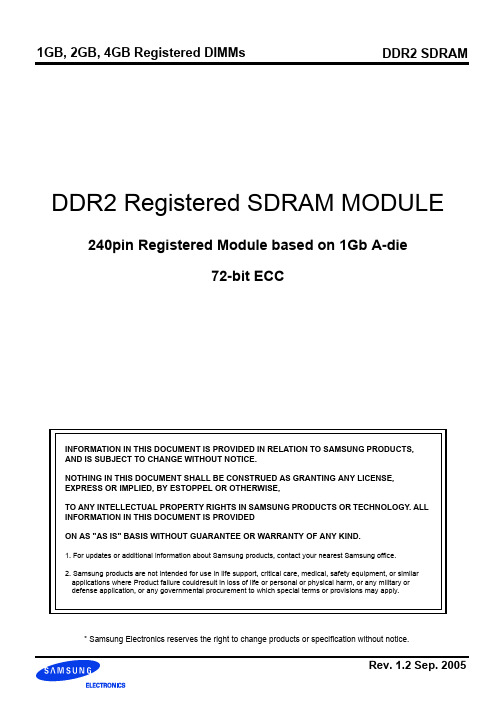

DDR2 Registered SDRAM MODULE 240pin Registered Module based on 1Gb A-die72-bit ECCINFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,AND IS SUBJECT TO CHANGE WITHOUT NOTICE.NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDEDON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.1. For updates or additional information about Samsung products, contact your nearest Samsung office.2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similarapplications where Product failure couldresult in loss of life or personal or physical harm, or any military ordefense application, or any governmental procurement to which special terms or provisions may apply.* Samsung Electronics reserves the right to change products or specification without notice.Table of Contents1.0 DDR2 Registered DIMM Ordering Information (4)2.0 Features (4)3.0 Address Configuration (4)4.0 Pin Configurations (Front side/Back side) (5)5.0 Pin Description (6)6.0 Input/Output Function Description (7)7.0 Functional Block Diagram (8)7.1 1GB, 128Mx72 Module (M393T2863AZ3/M393T2863AZA) (8)7.2 2GB, 256Mx72 Module (M393T5663AZ3/M393T5663AZA) (9)7.3 2GB, 256Mx72 Module (M393T5660AZ3/M393T5660AZA) (10)7.4 4GB, 512Mx72 Module (M393T5168AZ0/M393T5166AZA) (11)8.0 Absolute Maximum DC Ratings (12)9.0 AC & DC Operating Conditions (12)9.1 Operating Temperature Condition (13)9.2 Input DC Logic Level (13)9.3 Input AC Logic Level (13)9.4 AC Input Test Conditions (13)10.0 IDD Specification Parameters Definition (14)11.0 Operating Current Table(1-1) (15)11.1 M393T2863AZ3/M393T2863AZA : 1GB(128Mx8 *9) Module (15)11.2 M393T5663AZ3/M393T5663AZA : 2GB(128Mx8 *18) Module (15)11.3 M393T5660AZ3/M393T5660AZA : 2GB(256Mx4 *18) Module (16)11.4 M393T5168AZ0/M393T5166AZA : 4GB(st.512Mx4 *18) Module (16)12.0 Input/Output Capacitance (17)13.0 Electrical Characteristics & AC Timing for DDR2-667/533/400 (18)13.1 Refresh Parameters by Device Density (18)13.2 Speed Bins and CL, tRCD, tRP, tRC and tRAS for Corresponding Bin (18)13.3 Timing Parameters by Speed Grade (18)14.0 Physical Dimensions (20)14.1 128Mbx8 based 128Mx72 Module(1 Rank) (M393T2863AZ3/M393T2863AZA) (20)14.2 128Mbx8/256Mbx4 based 256Mx72 Module(2/1 Ranks)(M393T5663AZ3/M393T5663AZA/ M393T5660AZ3/M393T5660AZA) (21)14.3 st.512Mbx4 based 512Mx72 Module(2 Ranks) (M393T5168AZ0/M393T5166AZA) (22)15.0 240 Pin DDR2 Registered DIMM Clock Topology (23)Revision HistoryRevision Month Year History1.0July2005 - Initial Release1.1Aug.2005 - Revised IDD Current Values1.2Sep.2005 - Revised the Ordering InformationDDR2 Registered DIMM Ordering InformationPart Number Density Organization Component Composition Number of Rank Parity Register Height M393T2863AZ3-CD5/CC1GB128Mx72128Mx8(K4T1G084QA)*9EA1X30mm M393T2863AZA-CE6/D5/CC1GB128Mx72128Mx8(K4T1G084QA)*9EA1O30mm M393T5663AZ3-CD5/CC2GB256Mx72128Mx8(K4T1G084QA)*18EA2X30mm M393T5663AZA-CE6/D5/CC2GB256Mx72128Mx8(K4T1G084QA)*18EA2O30mm M393T5660AZ3-CD5/CC2GB256Mx72256Mx4(K4T1G044QA)*18EA1X30mm M393T5660AZA-CE6/D5/CC2GB256Mx72256Mx4(K4T1G044QA)*18EA1O30mm M393T5168AZ0-CD5/CC4GB512Mx72st.512Mx4(K4T2G064QA)*18EA2X30mm M393T5166AZA-CE6/D5/CC4GB512Mx72st.512Mx4(K4T2G264QA)*18EA2O30mm Note: “Z” of Part number(11th digit) stand for Lead-free products.Note: “3” of Part number(12th digit) stand for Dummy Pad PCB products.Note: "A" of Part number(12th digit) stand for Parity Register products.Features•Performance rangeE6(DDR2-667)D5(DDR2-533)CC(DDR2-400)UnitSpeed@CL3400400400MbpsSpeed@CL4533533400MbpsSpeed@CL5667533-MbpsCL-tRCD-tRP5-5-54-4-43-3-3CK•JEDEC standard 1.8V ± 0.1V Power Supply•V DDQ = 1.8V ± 0.1V•200 MHz f CK for 400Mb/sec/pin, 267MHz f CK for 533Mb/sec/pin, 333MHz f CK for 667Mb/sec/pin•8Banks•Posted CAS•Programmable CAS Latency: 3, 4, 5•Programmable Additive Latency: 0, 1 , 2 , 3 and 4•Write Latency(WL) = Read Latency(RL) -1•Burst Length: 4 , 8(Interleave/nibble sequential)•Programmable Sequential / Interleave Burst Mode•Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)•Off-Chip Driver(OCD) Impedance Adjustment•On Die Termination with selectable values(50/75/150 ohms or disable)•PASR(Partial Array Self Refresh)•Average Refresh Period 7.8us at lower than a T CASE 85°C, 3.9us at 85°C < T CASE < 95 °C- support High Temperature Self-Refresh rate enable feature•Serial presence detect with EEPROM•DDR2 SDRAM Package: 68ball FBGA - 256Mx4/128Mx8, 56ball BGA - st.512Mbx4•All of Lead-free products are compliant for RoHSNote: For detailed DDR2 SDRAM operation, please refer to Samsung’s Device operation & Timing diagram..Address ConfigurationOrganization Row Address Column Address Bank Address Auto Precharge 256Mx4(1Gb) based Module A0-A13A0-A9, A11BA0-BA2A10128Mx8(1Gb) based Module A0-A13A0-A9BA0-BA2A10NC = No Connect, RFU = Reserved for Future Use1. RESET (Pin 18) is connected to both OE of PLL and Reset of register.2. The Test pin (Pin 102) is reserved for bus analysis probes and is not connected on normal memory modules (DIMMs)3. NC/Err_Out ( Pin 55) and NC/Par_In (Pin 68) are for optional function to check address and command parity.4. CKE1,S1 Pin is used for double side Registered DIMM.Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back Pin Front Pin Back 1V REF 121V SS 31DQ19151V SS 61A4181V DDQ 91V SS 211DM5/DQS142V SS 122DQ432V SS 152DQ2862V DDQ 182A392DQS5212NC/DQS143DQ0123DQ533DQ24153DQ2963A2183A193DQS5213V SS 4DQ1124V SS 34DQ25154V SS 64V DD184V DD94V SS 214DQ465V SS 125DM0/DQS935V SS 155DM3/DQS12KEY95DQ42215DQ476DQS0126NC/DQS936DQS3156NC/DQS1265V SS 185CK096DQ43216V SS 7DQS0127V SS 37DQS3157V SS 66V SS 186CK097V SS 217DQ528V SS 128DQ638V SS 158DQ3067V DD 187V DD 98DQ48218DQ539DQ2129DQ739DQ26159DQ3168NC/Par_In 188A099DQ49219V SS 10DQ3130V SS 40DQ27160V SS 69V DD 189V DD 100V SS 220RFU 11V SS 131DQ1241V SS 161CB470A10/AP 190BA1101SA2221RFU 12DQ8132DQ1342CB0162CB571BA0191V DDQ 102NC(TEST)222V SS 13DQ9133V SS 43CB1163V SS 72V DDQ 192RAS 103V SS 223DM6/DQS1514V SS 134DM1/DQS1044V SS 164DM8/DQS1773WE 193S0104DQS6224NC/DQS1515DQS1135NC/DQS1045DQS8165NC/DQS1774CAS 194V DDQ 105DQS6225V SS 16DQS1136V SS 46DQS8166V SS 75V DDQ 195ODT0106V SS 226DQ5417V SS 137RFU 47V SS 167CB676S14196A13107DQ50227DQ5518RESET 138RFU 48CB2168CB777ODT1197V DD 108DQ51228V SS 19NC 139V SS 49CB3169V SS 78V DDQ 198V SS 109V SS 229DQ6020V SS 140DQ1450V SS 170V DDQ 79V SS 199DQ36110DQ56230DQ6121DQ10141DQ1551V DDQ 171CKE1480DQ32200DQ37111DQ57231V SS 22DQ11142V SS 52CKE0172V DD 81DQ33201V SS 112V SS 232DM7/DQS1623V SS 143DQ2053V DD 173NC 82V SS 202DM4/DQS13113DQS7233NC/DQS1624DQ16144DQ2154BA2174NC 83DQS4203NC/DQS13114DQS7234V SS 25DQ17145V SS 55NC/Err_Out 175V DDQ 84DQS4204V SS 115V SS 235DQ6226V SS 146DM2/DQS1156V DDQ 176A1285V SS 205DQ38116DQ58236DQ6327DQS2147NC/DQS1157A11177A986DQ34206DQ39117DQ59237V SS 28DQS2148V SS 58A7178V DD 87DQ35207V SS 118V SS 238VDDSPD 29V SS 149DQ2259V DD 179A888V SS 208DQ44119SDA 239SA030DQ18150DQ2360A5180A689DQ40209DQ45120SCL240SA190DQ41210V SS Pin Configurations (Front side/Back side)* The VDD and VDDQ pins are tied to the single power-plane on PCB.Pin Name DescriptionPin Name Description CK0Clock Inputs, positive line ODT0~ODT1On die termination CK0Clock inputs, negative line DQ0~DQ63Data Input/OutputCKE0, CKE1Clock Enables CB0~CB7Data check bits Input/Output RAS Row Address Strobe DQS0~DQS8Data strobesCAS Column Address Strobe DQS0~DQS8Data strobes, negative line WE Write Enable DM(0~8), DQS(9~17)Data Masks / Data strobes (Read)S0, S1Chip Selects DQS9~DQS17Data strobes (Read), negative line A0~A9, A11~A13Address InputsRFU Reserved for Future Use A10/AP Address Input/Autoprecharge NC No ConnectBA0~BA2DDR2 SDRAM Bank AddressTEST Memory bus test tool(Not Connect and Not Useable on DIMMs)SCL Serial Presence Detect (SPD) Clock Input V DD Core Power SDA SPD Data Input/Output V DDQ I/O Power SA0~SA2SPD addressV SS GroundPar_In Parity bit for the Address and Control bus V REF Input/Output Reference Err_Out Parity error found in the Address and Control bus V DDSPDSPD PowerRESETRegister and PLL control pinPin DescriptionSymbol Type DescriptionCK0Input Positive line of the differential pair of system clock inputs that drives input to the on-DIMM PLL.CK0Input Negative line of the differential pair of system clock inputs that drives the input to the on-DIMM PLL.CKE0~CKE1Input Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, or the Self Refresh mode.S0~S1Input Enables the associated SDRAM command decoder when low and disables decoder when high. When decoder is dis-abled, new commands are ignored but previous operations continue.These input signals also disable all outputs (except CKE and ODT) of the register(s) on the DIMM when both inputs are high.ODT0~ODT1Input I/O bus impedance control signals.RAS, CAS, WE Input When sampled at the positive rising edge of the clock, CAS, RAS, and WE define the operation to be executed by the SDRAM.V REF Supply Reference voltage for SSTL_18 inputsV DDQ Supply Isolated power supply for the DDR SDRAM output buffers to provide improved noise immunity BA0~BA2Input Selects which SDRAM bank of eight is activated.A0~A9,A10/APA11~A13Input During a Bank Activate command cycle, Address defines the row address.During a Read or Write command cycle, Address defines the column address. In addition to the column address, AP is used to invoke autoprecharge operation at the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA0, BA1, BA2 defines the bank to be precharged. If AP is low, autoprecharge is disabled. During a Precharge com-mand cycle, AP is used in conjunction with BA0, BA1, BA2 to control which bank(s) to precharge. If AP is high, all banks will be precharged regardless of the state of BA0 or BA1 or BA2. If AP is low, BA0 and BA1 and BA2 are used to define which bank to precharge.DQ0~63,CB0~CB7In/Out Data and Check Bit Input/Output pinsDM0~DM8Input Masks write data when high, issued concurrently with input data. Both DM and DQ have a write latency of one clock once the write command is registered into the SDRAM.V DD, V SS Supply Power and ground for the DDR SDRAM input buffers and core logicDQS0~DQS17In/Out Positive line of the differential data strobe for input and output data.DQS0~DQS17In/Out Negative line of the differential data strobe for input and output data.SA0~SA2Input These signals are tied at the system planar to either V SS or V DDSPD to configure the serial SPD EEPROM address range.SDA In/Out This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be connected from the SDA bus line to V DDSPD to act as a pullup.SCL Input This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected from the SCL bus time to V DDSPD to act as a pullup.V DDSPD Supply Serial EEPROM positive power supply (wired to a separate power pin at the connector which supports from 1.7 Volt to 3.6 Volt operation).RESET Input The RESET pin is connected to the RST pin on the register and to the OE pin on the PLL. When low, all register outputs will be driven low and the PLL clocks to the DRAMs and register(s) will be set to low level (The PLL will remain synchro-nized with the input clock )Par_In Input Parity bit for the Address and Control bus. ( “1 “ : Odd, “0 “ : Even) Err_Out Input Parity error found in the Address and Control busTEST In/Out Used by memory bus analysis tools (unused on memory DIMMs) Input/Output Function Description(populated as 1 rank of x8 DDR2 SDRAMs)1GB, 128Mx72 Module (M393T2863AZ3/M393T2863AZA)RS0DQS0DQS0DM0/DQS9NC/DQS9DM/ RDQS NU/RDQSCS DQS DQSDQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D0DQS1DQS1DM1/DQS10 NC/DQS10DM/ RDQS NU/RDQSCS DQS DQSDQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D1DQS2DQS2DM2/DQS11 NC/DQS11DM/ RDQS NU/RDQSCS DQS DQSDQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D2DQS3DQS3DM3/DQS12 NC/DQS12DM/ RDQS NU/RDQSCS DQS DQSDQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D3DQS8DQS8DM8/DQS17 NC/DQS17DM/ RDQS NU/RDQSCS DQS DQSCB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D8DQS4DQS4DM4/DQS13NC/DQS13DM/RDQSNU/RDQSCS DQS DQSDQ32DQ33DQ34DQ35DQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D4DQS5DQS5DM5/DQS14NC/DQS14DM/RDQSNU/RDQSCS DQS DQSDQ40DQ41DQ42DQ43DQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D5DQS6DQS6DM6/DQS15NC/DQS15DM/RDQSNU/RDQSCS DQS DQSDQ48DQ49DQ50DQ51DQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D6DQS7DQS7DM7/DQS16NC/DQS16DM/RDQSNU/RDQSCS DQS DQSDQ56DQ57DQ58DQ59DQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D7A0Serial PDA1A2SA0SA1SA2SCL SDAV SS D0 - D8V DD/V DDQ D0 - D8D0 - D8VREFV DDSPD Serial PDWPNotes :1. DQ-to-I/O wiring may be changed within a byte.2. DQ/DQS/DM/CKE/S relationships must be maintained as shown.3. Unless otherwise noted, resister values are 22 Ohms1:1REGISTERRSTS0*BA0-BA2A0-A13RASCASWECKE0ODT0RESETPCK7PCK7RSO-> CS : DDR2 SDRAMs D0-D8RBA0-RBA2 -> BA0-BA2 : DDR2 SDRAMs D0-D8RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D8RRAS -> RAS : DDR2 SDRAMs D0-D8RCAS -> CAS : DDR2 SDRAMs D0-D8RWE -> WE : DDR2 SDRAMs D0-D8RCKE0 -> CKE : DDR2 SDRAMs D0-D8RODT0 -> ODT0 : DDR2 SDRAMs D0-D8PLLOECK0CK0RESETPCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK7 -> CK : RegisterPCK7 -> CK : Register* S0 connects to DCS and VDD connects to CSR on the register.Functional Block DiagramSignals for Address and Command Parity Function (M393T2863AZA)V SSV SS PAR_IN C0C1PPOQERR Err_Out RegisterPAR_IN100K ohmsThe resistors on Par_In, A13, A14, A15, BA2 and the signal line of Err_Out refer to the section: "Register Options for Unused Address inputs"RS0DQS0DQS0DM0/DQS9NC/DQS9DM/RDQS NU/RDQSCS DQS DQSDQ0DQ1DQ2DQ3DQ4DQ5DQ6DQ7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D0DQS1DQS1DM1/DQS10NC/DQS10DM/RDQS NU/RDQSCS DQS DQSDQ8DQ9DQ10DQ11DQ12DQ13DQ14DQ15I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D1DQS2DQS2DM2/DQS11NC/DQS11DM/RDQS NU/RDQSCS DQS DQSDQ16DQ17DQ18DQ19DQ20DQ21DQ22DQ23I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D2DQS3DQS3DM3/DQS12NC/DQS12DM/RDQS NU/RDQSCS DQS DQSDQ24DQ25DQ26DQ27DQ28DQ29DQ30DQ31I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D3DQS8DQS8DM8/DQS17NC/DQS17DM/RDQS NU/RDQSCS DQS DQSCB0CB1CB2CB3CB4CB5CB6CB7I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D8DQS4DQS4DM4/DQS13NC/DQS13DM/RDQS NU/RDQSCS DQS DQSDQ32DQ33DQ34DQ35DQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D4DQS5DQS5DM5/DQS14NC/DQS14DM/RDQS NU/RDQSCS DQS DQSDQ40DQ41DQ42DQ43DQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D5DQS6DQS6DM6/DQS15NC/DQS15DM/RDQS NU/RDQSCS DQS DQSDQ48DQ49DQ50DQ51DQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D6DQS7DQS7DM7/DQS16NC/DQS16DM/RDQS NU/RDQSCS DQS DQSDQ56DQ57DQ58DQ59DQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D7DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D9DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D10DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D11DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D12DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D17DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D13DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D14DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D15DM/RDQS NU/RDQSCS DQS DQSI/O 0I/O 1I/O 2I/O 3I/O 4I/O 5I/O 6I/O 7D16RS1A0Serial PDA1A2SA0SA1SA2SCLSDAV SSD0 - D17V DD /V DDQ D0 - D17D0 - D17VREF V DDSPDSerial PD WP Notes :1. DQ-to-I/O wiring may be changed per nibble.2. Unless otherwise noted, resister values are 22 Ohms3. RS0 and RS1 alternate between the back and front sides of the DIMM1:2R E G I S T E RRSTS1*BA0-BA2A0-A13RAS CAS WE CKE0CKE1RESET**PCK7**PCK7**RS1-> CS : DDR2 SDRAMs D9-D17RBA0-RBA2 -> BA0-BA2: DDR2 SDRAMs D0-D17RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D17RRAS -> RAS : DDR2 SDRAMs D0-D17RCAS -> CAS : DDR2 SDRAMs D0-D17RWE -> WE : DDR2 SDRAMs D0-D17RCKE0 -> CKE : DDR2 SDRAMs D0-D8RCKE1 -> CKE : DDR2 SDRAMs D9-D17P L LOECK0CK0RESETPCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D17PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D17PCK7 -> CK : Register PCK7 -> CK : RegisterODT0ODT1RODT0 -> ODT0 : DDR2 SDRAMs D0-D8RODT1 -> ODT1 : DDR2 SDRAMs D9-D17S0*RSO-> CS : DDR2 SDRAMs D0-D8(populated as 2 rank of x8 DDR2 SDRAMs)2GB, 256Mx72 Module (M393T5663AZ3/M393T5663AZA)* S0 connects to DCS and S0 connects to CSR on a Register,S1 connects to DCS and S0 connects to CSR on another Register.** RESET, PCK7 and PCK7 connects to both Registers. Other signals connect to one of two Registers.Signals for Address and Command Parity Function (M393T5663AZA)V SS V DDPAR_IN C0C1PPO QERRRegister APAR_IN 100K ohmsThe resistors on Par_In, A13, A14, A15, BA2 and the signal line of Err_Out refer to the section: "Register Options for Unused Address inputs"V DD V DDC0C1PPO QERRErr_OutRegister BPAR_INVSSRS0DQS0DQS0DM CS DQS DQSDQ0 DQ1 DQ2 DQ3I/O 0I/O 1I/O 2I/O 3D0DM0/DQS9NC/DQS9DM CS DQS DQSDQ4DQ5DQ6DQ7I/O 0I/O 1I/O 2I/O 3D9DQS1DQS1DM CS DQS DQSDQ8 DQ9 DQ10 DQ11I/O 0I/O 1I/O 2I/O 3D1DM1/DQS10NC/DQS10DM CS DQS DQSDQ12DQ13DQ14DQ15I/O 0I/O 1I/O 2I/O 3D10DQS2DQS2DM CS DQS DQSDQ16 DQ17 DQ18 DQ19I/O 0I/O 1I/O 2I/O 3D2DM2/DQS11NC/DQS11DM CS DQS DQSDQ20DQ21DQ22DQ23I/O 0I/O 1I/O 2I/O 3D11DQS3DQS3DM CS DQS DQSDQ24 DQ25 DQ26 DQ27I/O 0I/O 1I/O 2I/O 3D3DM3/DQS12NC/DQS12DM CS DQS DQSDQ28DQ29DQ30DQ31I/O 0I/O 1I/O 2I/O 3D12DQS5DQS5DM CS DQS DQSDQ40 DQ41 DQ42 DQ43I/O 0I/O 1I/O 2I/O 3D5DM5/DQS14NC/DQS14DM CS DQS DQSDQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3D14DQS4DQS4DM CS DQS DQSDQ32 DQ33 DQ34 DQ35I/O 0I/O 1I/O 2I/O 3D4DM4/DQS13NC/DQS13DM CS DQS DQSDQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3D13DQS6DQS6DM CS DQS DQSDQ48 DQ49 DQ50 DQ51I/O 0I/O 1I/O 2I/O 3D6DM6/DQS15NC/DQS15DM CS DQS DQSDQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3D15DQS8DQS8DM CS DQS DQSCB0 CB1 CB2 CB3I/O 0I/O 1I/O 2I/O 3D8DM8/DQS17NC/DQS17DM CS DQS DQSCB4CB5CB6CB7I/O 0I/O 1I/O 2I/O 3D17DQS7DQS7DM CS DQS DQSDQ56 DQ57 DQ58 DQ59I/O 0I/O 1I/O 2I/O 3D7DM7DQS16NC/DQS16DM CS DQS DQSDQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3D16A0Serial PDA1A2SA0SA1SA2SCL SDAV SS D0 - D17V DD/V DDQ D0 - D17D0 - D17VREFV DDSPD Serial PDWPNotes :1. DQ-to-I/O wiring may be changed per nibble.2. Unless otherwise noted, resister values are 22 Ohms 1:2REGISTERRSTS0*BA0-BA2A0-A13RASCASWECKE0ODT0RESET**PCK7** PCK7**RSO-> CS : DDR2 SDRAMs D0-D17RBA0-RBA2 -> BA0-BA2 : DDR2 SDRAMs D0-D17RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D17RRAS -> RAS : DDR2 SDRAMs D0-D17RCAS -> CAS : DDR2 SDRAMs D0-D17RWE -> WE : DDR2 SDRAMs D0-D17RCKE0 -> CKE : DDR2 SDRAMs D0-D17RODT0 -> ODT0 : DDR2 SDRAMs D0-D17PLLOECK0CK0RESETPCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D8PCK7 -> CK : RegisterPCK7 -> CK : Register(populated as 1 rank of x4 DDR2 SDRAMs)2GB, 256Mx72 Module (M393T5660AZ3/M393T5660AZA)* S0 connects to DCS of Register1, CSR of Register2. CSR of reg-ister 1 and DCS of register 2 connects to VDD.** RESET, PCK7 and PCK7 connects to both Registers. Other sig-nals connect to one of two Registers.Signals for Address and Command Parity Function (M393T5660AZA)V SSV DDPAR_INC0C1PPOQERRRegister APAR_IN100K ohmsThe resistors on Par_In, A13, A14, A15, BA2 and thesignal line of Err_Out refer to the section: "RegisterOptions for Unused Address inputs"V DDV DDC0C1PPOQERR Err_OutRegister BPAR_IN(populated as 2 rank of x4 DDR2 SDRAMs)A0Serial PDA1A2SA0SA1SA2SCLSDAV SSD0 - D35V DD /V DDQ D0 - D35D0 - D35VREF V DDSPDSerial PD WP P L LOECK0CK0RESET PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D35PCK0-PCK6, PCK8, PCK9 -> CK : DDR2 SDRAMs D0-D35PCK7 -> CK : Register PCK7 -> CK : Register1:2R E G I S T E RRSTS1*BA0-BA2A0-A13RAS CAS WE CKE0CKE1RESET**PCK7**PCK7**RS1-> CS : DDR2 SDRAMs D18-D35RBA0-RBA2 -> BA0-BA2 : DDR2 SDRAMs D0-D35RA0-RA13 -> A0-A13 : DDR2 SDRAMs D0-D35RRAS -> RAS : DDR2 SDRAMs D0-D35RCAS -> CAS : DDR2 SDRAMs D0-D35RWE -> WE : DDR2 SDRAMs D0-D35RCKE0 -> CKE : DDR2 SDRAMs D0-D17RCKE1 -> CKE : DDR2 SDRAMs D18-D35ODT0ODT1RODT0 -> ODT0 : DDR2 SDRAMs D0-D17RODT1 -> ODT1 : DDR2 SDRAMs D18-D35S0*RSO-> CS : DDR2 SDRAMs D0-D174GB, 512Mx72 Module (M393T5168AZ0/M393T5166AZA)* S0 connects to DCS and S0 connects to CSR on a Register,S1 connects to DCS and S0 connects to CSR on another Register.** RESET, PCK7 and PCK7 connects to both Registers. Other signals connect to one of two Registers.VSS RS0DQS0DQS0DMCSDQS DQSDQ0DQ1DQ2DQ3I/O 0I/O 1I/O 2I/O 3D0DM0/DQS9NC/DQS9DMCSDQS DQSDQ4DQ5DQ6DQ7I/O 0I/O 1I/O 2I/O 3D9DQS1DQS1DM CS DQS DQS DQ8DQ9DQ10DQ11I/O 0I/O 1I/O 2I/O 3D1DM1/DQS10NC/DQS10DM CS DQS DQS DQ12DQ13DQ14DQ15I/O 0I/O 1I/O 2I/O 3D10DQS2DQS2DM CS DQS DQS DQ16DQ17DQ18DQ19I/O 0I/O 1I/O 2I/O 3D2DM2/DQS11NC/DQS11DM CS DQS DQS DQ20DQ21DQ22DQ23I/O 0I/O 1I/O 2I/O 3D11DQS3DQS3DM CS DQS DQS DQ24DQ25DQ26DQ27I/O 0I/O 1I/O 2I/O 3D3DM3/DQS12NC/DQS12DM CS DQS DQS DQ28DQ29DQ30DQ31I/O 0I/O 1I/O 2I/O 3D12DQS5DQS5DM CS DQS DQS DQ40DQ41DQ42DQ43I/O 0I/O 1I/O 2I/O 3D5DM5/DQS14NC/DQS14DM CS DQS DQS DQ44DQ45DQ46DQ47I/O 0I/O 1I/O 2I/O 3D14DQS4DQS4DM CS DQS DQS DQ32DQ33DQ34DQ35I/O 0I/O 1I/O 2I/O 3D4DM4/DQS13NC/DQS13DM CS DQS DQS DQ36DQ37DQ38DQ39I/O 0I/O 1I/O 2I/O 3D13DQS6DQS6DM CS DQS DQS DQ48DQ49DQ50DQ51I/O 0I/O 1I/O 2I/O 3D6DM6/DQS15NC/DQS15DM CS DQS DQS DQ52DQ53DQ54DQ55I/O 0I/O 1I/O 2I/O 3D15DQS8DQS8DM CS DQS DQS CB0CB1CB2CB3I/O 0I/O 1I/O 2I/O 3D8DM8/DQS17NC/DQS17DM CS DQS DQS CB4CB5CB6CB7I/O 0I/O 1I/O 2I/O 3D17DQS7DQS7DM CS DQS DQS DQ56DQ57DQ58DQ59I/O 0I/O 1I/O 2I/O 3D7DM7DQS16NC/DQS16DM CS DQS DQS DQ60DQ61DQ62DQ63I/O 0I/O 1I/O 2I/O 3D16DM/CSDQS DQSI/O 0I/O 1I/O 2I/O 3D18DM/CS DQS DQS I/O 0I/O 1I/O 2I/O 3D19DM/CS DQS DQS I/O 0I/O 1I/O 2I/O 3D20DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D21DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D23DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D22DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D24DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D26DM CS DQS DQS I/O 0I/O 1I/O 2I/O 3D25DMCSDQS DQSI/O 0I/O 1I/O 2I/O 3D27DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D28DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D29DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D30DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D32DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D31DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D33DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D35DM CS DQS DQSI/O 0I/O 1I/O 2I/O 3D34RS1Signals for Address and Command The resistors on Par_In, A13, A14, A15, BA2and the signal line of Err_Out refer to the sec-tion: "Register Options for Unused Address inputs"PAR_INErr_Out100K ohmsV SS V DDC0C1PPO QERRRegister A1PAR_INV DD V DDC0C1PPO QERRRegister B1PAR_INV SS V DDC0C1PPO QERRRegister A2PAR_INV DD V DDC0C1PPO QERRRegister B2PAR_INParity Function (M393T5166AZA)Register A1 and A2 share the a part of Add/Cmd input signal set.Register B1 and B2 share the rest part of Add/Cmd input signal set.Recommended DC Operating Conditions (SSTL - 1.8)Note : There is no specific device V DD supply voltage requirement for SSTL-1.8 compliance. However under all conditions V DDQ must be less than or equalto V DD .1. The value of V REF may be selected by the user to provide optimum noise margin in the system. Typically the value of V REF is expected to be about 0.5 x V DDQ of the transmitting device and V REF is expected to track variations in V DDQ .2. Peak to peak AC noise on V REF may not exceed +/-2% V REF (DC).3. V TT of transmitting device must track V REF of receiving device.4. AC parameters are measured with V DD , V DDQ and V DDL tied together.Symbol ParameterRatingUnits NotesMin.Typ. Max.V DD Supply Voltage 1.7 1.8 1.9V V DDL Supply Voltage for DLL 1.7 1.8 1.9V 4V DDQ Supply Voltage for Output 1.7 1.8 1.9V 4V REF Input Reference Voltage 0.49*V DDQ 0.50*V DDQ0.51*V DDQ mV 1,2V TTTermination VoltageV REF -0.04V REFV REF +0.04V3 Note :1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2standard.Symbol ParameterRating Units Notes V DD Voltage on V DD pin relative to V SS - 1.0 V ~ 2.3 V V 1V DDQ Voltage on V DDQ pin relative to V SS - 0.5 V ~ 2.3 V V 1V DDL Voltage on V DDL pin relative to V SS - 0.5 V ~ 2.3 V V 1V IN, V OUT Voltage on any pin relative to V SS - 0.5 V ~ 2.3 V V1T STGStorage Temperature-55 to +100°C 1, 2AC & DC Operating ConditionsAbsolute Maximum DC Ratings。

SN54393中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.POST OFFICE BOX 655303 • DALLAS, TEXAS 752652POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 752654POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 752657 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265POST OFFICE BOX 655303 • DALLAS, TEXAS 75265PACKAGING INFORMATIONOrderableDevice Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)7802601EA ACTIVE CDIP J 161TBD Call TI Level-NC-NC-NC 7802601FA ACTIVE CFP W 161TBD Call TI Level-NC-NC-NC 7802601FA ACTIVE CFP W 161TBD Call TI Level-NC-NC-NC JM38510/32701B2A ACTIVE LCCC FK 201TBD Call TI Level-NC-NC-NC JM38510/32701B2A ACTIVE LCCC FK 201TBD Call TI Level-NC-NC-NC JM38510/32701BEA ACTIVE CDIP J 161TBD Call TI Level-NC-NC-NC JM38510/32701BEA ACTIVE CDIP J 161TBD Call TI Level-NC-NC-NC JM38510/32702B2A ACTIVE LCCC FK 201TBD Call TI Level-NC-NC-NC JM38510/32702B2A ACTIVE LCCC FK 201TBD Call TI Level-NC-NC-NC JM38510/32702BCA ACTIVE CDIP J 141TBD Call TI Level-NC-NC-NC JM38510/32702BCA ACTIVE CDIP J 141TBD Call TI Level-NC-NC-NC JM38510/32702BDA ACTIVE CFP W 141TBD Call TI Level-NC-NC-NC JM38510/32702BDA ACTIVE CFP W 141TBD Call TI Level-NC-NC-NC JM38510/32702SCA ACTIVE CDIP J 141TBD Call TI Level-NC-NC-NC JM38510/32702SCA ACTIVE CDIP J 141TBD Call TI Level-NC-NC-NC JM38510/32702SDA ACTIVE CFP W 141TBD Call TI Level-NC-NC-NC JM38510/32702SDAACTIVE CFP W 141TBD Call TI Level-NC-NC-NC SN54393J OBSOLETE CDIP J 14TBD Call TI Call TI SN54393J OBSOLETE CDIP J 14TBD Call TI Call TISN54LS390J ACTIVE CDIP J 161TBD Call TI Level-NC-NC-NC SN54LS390J ACTIVE CDIP J 161TBD Call TI Level-NC-NC-NC SN54LS393J ACTIVE CDIP J 141TBD Call TI Level-NC-NC-NC SN54LS393J ACTIVE CDIP J 141TBD Call TI Level-NC-NC-NC SN74390N OBSOLETE PDIP N 16TBD Call TI Call TI SN74390N OBSOLETE PDIP N 16TBD Call TI Call TI SN74393N OBSOLETE PDIP N 14TBD Call TI Call TI SN74393N OBSOLETE PDIP N 14TBD Call TI Call TI SN74393N3OBSOLETE PDIP N 14TBD Call TI Call TI SN74393N3OBSOLETE PDIP N 14TBD Call TI Call TISN74LS390D ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390D ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390DE4ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390DE4ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390DR ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390DR ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390DRE4ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS390DRE4ACTIVESOICD162500Green (RoHS &CU NIPDAULevel-1-260C-UNLIMPACKAGE OPTION ADDENDUM17-Oct-2005Addendum-Page 1元器件交易网Orderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)SN74LS390N ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS390N ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74LS390N3OBSOLETE PDIP N16TBD Call TI Call TISN74LS390N3OBSOLETE PDIP N16TBD Call TI Call TISN74LS390NE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS390NE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS390NSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS390NSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS390NSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS390NSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS393J OBSOLETE CDIP J14TBD Call TI Call TISN74LS393J OBSOLETE CDIP J14TBD Call TI Call TISN74LS393N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS393N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74LS393N3OBSOLETE PDIP N14TBD Call TI Call TISN74LS393N3OBSOLETE PDIP N14TBD Call TI Call TISN74LS393NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS393NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS393NSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS393NSR ACTIVE SO NS142000Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)SN74LS393NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS393NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54393J OBSOLETE CDIP J14TBD Call TI Call TISNJ54393J OBSOLETE CDIP J14TBD Call TI Call TISNJ54393W OBSOLETE CFP W14TBD Call TI Call TISNJ54393W OBSOLETE CFP W14TBD Call TI Call TISNJ54LS390FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54LS390FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54LS390J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54LS390J ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54LS390W ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54LS390W ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SNJ54LS393FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54LS393FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54LS393J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54LS393J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54LS393W ACTIVE CFP W141TBD Call TI Level-NC-NC-NC SNJ54LS393W ACTIVE CFP W141TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

0190390023;中文规格书,Datasheet资料

This document was generated on 08/13/2012PLEASE CHECK FOR LATEST PART INFORMATIONPart Number:19039-0023Status:ActiveDescription:Avikrimp™ Snap Plug Receptacle for 14-16 AWG Wire, PVC, Fits Male Plug Diameter 3.96mm, Mylar Tape CarrierDocuments:Drawing (PDF)Product Specification PS-19902-015 (PDF)Product Specification PS-19902-011 (PDF)RoHS Certificate of Compliance (PDF)Agency CertificationCSA LR18689ULE152602GeneralProduct Family Quick Disconnects Series19039CommentsFits Male Plug Dia. 3.96mm Crimp Quality Equipment YesProduct Name Avikrimp™Type Snap Receptacle UPC800753049574PhysicalBarrel Type Closed Color - Resin Natural Flammability 94V-0GenderFemale Glow-Wire Compliant No InsulationPVC Lock to Mating Part None Material - MetalBrass Material - Plating MatingTin Material - Plating Termination Tin Material - Resin PVC Net Weight 1.378/g OrientationStraightPackaging Type Adhesive Tape on Reel Plating min - Mating4.064µm Plating min - Termination 4.064µm Tab Thickness N/A Tab WidthN/ATemperature Range - Operating -40°C to +105°CTermination Interface: Style Crimp or Compression Wire Insulation Diameter 3.81mm max.Wire Size AWG 14, 16Wire Size mm²1.00 -2.50ElectricalVoltage - Maximum600V Material InfoOld Part NumberBRB-8156TReference - Drawing NumbersProduct Specification PS-19902-011, PS-19902-015Sales DrawingSD-19039-001Seriesimage - Reference onlyEU RoHSChina RoHSELV and RoHS Compliant REACH SVHC Not ReviewedLow-Halogen Status Not ReviewedNeed more information on product environmental compliance?Email productcompliance@For a multiple part number RoHS Certificate of Compliance, click herePlease visit the Contact Us section for any non-product compliance questions.Search Parts in this Series 19039SeriesApplication Tooling | FAQTooling specifications and manuals are found by selecting the products below.Crimp Height Specifications are then contained in the Application Tooling Specification document.GlobalDescription Product #Mini-Mac™Applicator0638853700This document was generated on 08/13/2012PLEASE CHECK FOR LATEST PART INFORMATION分销商库存信息: MOLEX 0190390023。

AS3933_Datasheet

AS39333D Low Frequency Wake-Up ReceiverThe AS3933 is a 3-channel low power ASK receiver that is ableto generate a wake-up upon detection of a data signal whichuses a LF carrier frequency between 15-150 kHz. The integratedcorrelator can be used for detection of a programmable 16-bitor 32-bit Manchester wake-up pattern. The device can operateusing one, two, or three active channels.The AS3933 provides a digital RSSI value for each activechannel, it supports a programmable data rate and Manchesterdecoding with clock recovery. The AS3933 offers an internalClock Generator, which is either derived from a crystal oscillatoror the internal RC oscillator. The user can decide to use theexternal clock generator instead.The programmable features of AS3933 enable to optimize itssettings for achieving a longer distance while retaining areliable wake-up generation. The sensitivity level of AS3933 canbe adjusted in presence of a strong field or in noisyenvironments.Antenna tuning is greatly simplified, as the automatic tuningfeature ensures perfect matching to the desired carrierfrequency.The device is available in 16-pin TSSOP and 16-LD QFN (4x4mm)packages, and DoW (dice on wafer).Ordering Information and Content Guide appear at end ofdatasheet.Key Benefits & FeaturesThe benefits and features of AS3933, 3D Low FrequencyWake-Up Receiver are listed below:Figure 1:Added Value of Using AS3933•Enables low power active tags•3-channel ASK wake-up receiver•Selectable carrier frequency•Carrier frequency range 15 – 150 kHz•One, two, or three channel operation•1-D, 2-D, or 3-D wake-up pattern detection•Highly resistant to false wake-ups•32-bit programmable wake-up pattern•Improved immunity to false wake-ups•Supporting doubling of wake-up pattern•Allows frequency only detection•Wake-up without pattern detection selectable•Improved range with best-in-class sensitivity •Wake-up sensitivity 80μVRMS (typ.)General DescriptionAS3933 −G eneral D escriptionApplicationsThe AS3933, 3D Low Frequency Wake-Up Receiver is ideal for Active RFID tags, Real-time location systems, Operator identification, Access control, and Wireless sensors.Figure 2:AS3933 Typical Application Diagram with Crystal Oscillator•Adjustable range•Sensitivity level adjustable •Provides tracking of false wake-ups •False wake-up counter•Ensures wake-up in a noise environment •Periodical forced wake-up supported (1s – 2h)•Extended battery life •Current consumption in 3-channel listening mode 2.3 μA (typ.)•Flexible clock configuration •RTC based 32 kHz XTAL, RC-OSC, or external clock •Operates from a 3V battery •Operating supply range 2.4V – 3.6V (TA = 25°C)•Industrial temperature range•Operation temperature range -40°C to 85°CAS3933 − General DescriptionFigure 3:AS3933 Typical Application Diagram with RC OscillatorFigure 4:AS3933 Typical Application Diagram with Clock from External SourceAS3933 −P in A ssignmentsTSSOP-16 PackageFigure 5:TSSOP Pin Assignment (Top View)Pin DescriptionFigure 6:TSSOP-16 Pin DescriptionDescriptionCS 1 Digital inputChip selectSCL2SDI interface clockS D I 3 S D I data input S D O 4Digital output / tristate SDI data output (tristate when CS is low) V CC5Supply padPositive supply voltageGN D 6Negative supplyvoltagePin AssignmentsAS3933 − Pin AssignmentsQFN-16 PackageFigure 7:QFN Pin Assignment (Top View)LF3P 7 Analog I/OInput antenna channel three LF2P 8 Input antenna channel two LF1P 9Input antenna channel oneLFN10Common ground for antenna one, two and three XIN 11 Crystal oscillator input XOUT 12 Crystal oscillator outputV SS13 Supply pad SubstrateWAKE 14Digital output Wake-up output IRQD AT 15 D ata outputCL_D AT 16Manchester recovered clockAS3933 −P in A ssignmentsPin DescriptionFigure 8:QFN-16 Pin DescriptionLF3P 1 Analog I/OInput antenna channel three LF2P 2 Input antenna channel two LF1P 3Input antenna channel oneLFN4Common ground for antenna one, two and three XIN 5 Crystal oscillator input XOUT 6 Crystal oscillator outputV SS7 Supply pad SubstrateWAKE 8Digital output Wake-up output IRQD AT 9 D ata outputCL_D AT 10Manchester recovered clock CS 11 Digital inputChip select SCL12SDI interface clockS D I 13 S D I data input S D O 14Digital output /tristateSDI data output (tristate when CS is low) V CC15Supply padPositive supply voltageGND 16 Negative supply voltageAS3933 − Pin AssignmentsDice On WaferDoW Attributes:•Wafer Diameter: 8”•Process: 0.35μm•Wafer Thickness: 725μm ± 15μm•Scribe line: 80μm•Chip Size: 2.070 x 1.700 mm•Pad Size: 85 x 85 μmFigure 9:DoW Pad AssignmentAS3933 −P in A ssignments Figure 10:DoW Pad Description and PositionUpper Side 1GND381.51532.5 2GND634.51532.5 3VCC817.51532.5 4SDO1000.51532.5 5SDI1230.51532.5 6SCL1417.51532.5Right Side1CL_DAT1902.5257.52CS1902.51365.5Bottom Side 1XIN648.3594.5 2XOUT847.594.5 3VSS1203.587.5 4WAKE1387.587.5 5DAT1569.587.5Left Side 1LFN87.5303.5 2LF1P87.5669.5 3LF2P87.51103.5 4LF3P87.51356.5AS3933 − Absolute Maximum RatingsStresses beyond those listed in Absolute Maximum Ratings maycause permanent damage to the device. These are stress ratingsonly. Functional operation of the device at these or any otherconditions beyond those indicated in Operating Conditions isnot implied. Exposure to absolute maximum rating conditionsfor extended periods may affect device reliability.Figure 11:Absolute Maximum RatingsElectrical ParametersV DD DC supply voltage-0.55VV IN Input pin voltage-0.55VI SOURCE Input current(latch up immunity)-100100mA Norm: Jedec 78Electrostatic DischargeESD Electrostatic discharge ±2kV Norm: MIL 883 E method 3015 (HBM)Continuous Power DissipationP t Total power dissipation(all supplies and outputs)0.07mWTemperature Ranges and Storage Conditions T strg Storage temperature-65150°CT body Package bodytemperature 260°CNorm: IPC/JEDEC J-STD-020The reflow peak solderingtemperature (body temperature)is specified according IPC/JEDECJ-STD-020 “Moisture/ReflowSensitivity Classification forNon-hermetic Solid State SurfaceMount Devices”.RH NC Relative Humidity(non-condensing)585%MSL Moisture Sensitivity Level 3Represents a maximum floor life time of 168hAbsolute Maximum RatingsAS3933 −E lectrical C haracteristicsFigure 12:Operating ConditionsFigure 13:DC/AC Characteristics for Digital Inputs and OutputsV DD Positive supply voltage 2.433.6VV SS Negative supplyvoltage 0 0 V T AMBAmbient temperature-4085°CCMOS InputV IH High level input voltage0.6* V DD 0.7* V DD 0.8* V DD VV IL Low level input voltage 0.12* V DD0.2* V DD0.3* V DD V I LEAKInput leakage current100nACMOS OutputV OH High level output voltage With a load current of 1mAV DD - 0.4VV OL Low level output voltageWith a load current of 1mA V SS + 0.4 V C LCapacitive loadFor a clock frequency of 1 MHz 400pFTristate CMOS OutputV OH High level output voltage With a load current of 1mAV DD - 0.4VV OL Low level output voltage With a load current of 1mAV SS + 0.4 V I OZTristate leakage currentTo V DD and V SS100nAElectrical CharacteristicsAS3933 − Electrical CharacteristicsFigure 14:Electrical System SpecificationsInput CharacteristicsR IN AC Input Impedanceat125kHz In case no antennadamper is set (R1<4>=0)2MΩF1max Maximum InputFrequency Band1150 kHzF1min Minimum InputFrequency Band195 kHzF2max Maximum InputFrequency Band295 kHzF2min Minimum InputFrequency Band265 kHzF3max Maximum InputFrequency Band365 kHzF3min Minimum InputFrequency Band340 kHzF4max Maximum InputFrequency Band440 kHzF4min Minimum InputFrequency Band423 kHzF5max Maximum InputFrequency Band523 kHzF5min Minimum InputFrequency Band515 kHzCurrent ConsumptionI1CHRC Current Consumption instandard listening modewith one active channeland RC-oscillator asClock Generator3.1 μAI2CHRC Current Consumption instandard listening modewith two active channelsand RC-oscillator asClock Generator4.6 μAAS3933 −E lectrical C haracteristicsI3CHRC Current Consumption instandard listening modewith three activechannels andRC-oscillator as ClockGenerator6.1 μAI3CHSCRC Current Consumption inscanning mode withthree active channelsand RC-oscillator asClock Generator3.1 μAI3CHOORC Current Consumption inON/OFF mode with threeactive channels andRC-oscillator as ClockGenerator11% Duty Cycle 2.3μA50% Duty Cycle 3.8I3CHXT Current Consumption instandard listening modewith three activechannels and crystaloscillator as ClockGenerator6.5 8.9 μAIDATA Current Consumption inPreamble detection /Pattern correlation / Datareceiving mode(RC-oscillator)With 125 kHz carrierfrequency and 1 kbpsdata-rate. No load on theoutput pins.8.3 12 μAIBOOST Additional currentconsumption perchannel if gain boostenabled150 nAInput SensitivitySENS1 Input Sensitivity on allchannels in the Band1With 125 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection100 μVrmsSENS1B Input Sensitivity on allchannels in the Band1with 3dB gain boostWith 125 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection80 μVrmsSENS2 Input Sensitivity on allchannels in the Band2With 90 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection100 μVrmsAS3933 − Electrical CharacteristicsSENS2B Input Sensitivity on allchannels in the Band2with 3dB gain boostWith 90 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection80 μVrmsSENS3 Input Sensitivity on allchannels in the Band3With 60 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection100 μVrmsSENS3B Input Sensitivity on allchannels in the Band3with 3dB gain boostWith 60 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection80 μVrmsSENS4B Input Sensitivity on allchannels in the Band4with 3dB gain boostWith 30 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection80 μVrmsSENS5B Input Sensitivity on allchannels in the Band5with 3dB gain boostWith 18 kHz carrierfrequency, chip in defaultmode, 4 half bits burst + 4symbols preamble andsingle preamble detection80 μVrmsChannel Settling TimeTSAMP Amplifier settling time 250 μsCrystal OscillatorFXTAL FrequencyCrystal dependent2532.768 45kHz TXTAL Start-upTime 1 s IXTAL Currentconsumption 300nAExternal Clock SourceIEXTCL Currentconsumption 0.8 μA FEXTCL Frequency2545kHzAS3933 −E lectrical C haracteristics RC OscillatorFRCNCALFrequency If no calibration isperformed2532.768 45kHzFRCCAL32 If calibration with 32.768kHz reference signal isperformed31 32.768 34.5FRCCALMAX Maximum achievablefrequency after calibration23.75FRCCALMIN Minimum achievablefrequency after calibration45TRC Start-uptime From RC enable(R1<0> = 0)1 sTCALRC Calibrationtime 65 Periods of reference clockIRC Currentconsumption 650 nALC OscillatorFLCO MIN Minimum Frequency L=47mH (Premo:SDTR1103-0108+),C=2.3nF15 kHzFLCO MAX Maximum Frequency L=7.2mH (Premo:SDTR1103-0720+), C=1nF150 kHz RPAR MIN Minimum Eq. Parallel 10 kΩTuning CapsLF1PtuningCapacitance Maximum internalcapacitance (in step of1pF) on LF1P31 pFLF2Ptuning Maximum internalcapacitance (in step of1pF) on LF2P31 pFLF3Ptuning Maximum internalcapacitance (in step of1pF) on LF3P31 pFAS3933 − Typical Operating CharacteristicsFigure 15:Sensitivity vs Voltage and TemperatureFigure 16:Sensitivity vs RSSITypical Operating CharacteristicsAS3933 −T ypical O perating C haracteristics Figure 17:RC-Oscillator Frequency vs Voltage (Calibr.)Figure 18:RC-Oscillator Frequency vs Temperature (Calibr.)AS3933 − Detailed DescriptionThe AS3933 is a three-dimensional low power low-frequency Detailed Descriptionwake-up receiver. The AS3933 is capable of detecting thepresence of an inductive coupled carrier and can extract theenvelope of the ON-OFF-Keying (OOK) modulated carrier. Incase the carrier is Manchester coded, the clock can be recoveredfrom the received signal and the data can be correlated with aprogrammed pattern. If the detected pattern corresponds tothe stored one, a wake-up signal (IRQ) is risen up. The patterncorrelation can be disabled; in this case the wake-up detectionis based only on the frequency detection.The AS3933 is made up of three independent receivingchannels, one envelop detector, one data correlator, oneManchester decoder, 19 programmable registers with the mainlogic and a Clock Generator.The digital logic can be accessed by an SPI. The Clock Generatorcan be based on a crystal oscillator, or an internal RC-oscillatoror an external clock. In case the RC-oscillator is used to improveits accuracy, a calibration can be performed.The internal LC-oscillator can deliver the antenna’s oscillationfrequency for each channel and the internal tuning capacitorbank can provide fine tuning.The Internal RC-oscillator can be calibrated either over SPI orusing the internal algorithm based on the antenna resonancefrequency.Figure 19:Block Diagram of LF Wake-Up Receiver AS3933AS3933 −D etailed D escriptionAS3933 needs the following external components:•Power supply capacitor - CBAT - 100 nF.•32.768 kHz crystal with its two pulling capacitors - XTAL and CL - (it is possible to omit these components if theinternal RC oscillator is used instead of the crystaloscillator).•One, two, or three LC resonators according to the number of used channels.In case the internal RC-oscillator is used (no crystal oscillator is mounted), the pin XIN has to be connected to the supply, while pin XOUT should stay floating. Application diagrams with and without crystal are shown in Figure2, Figure3 and Figure4. Operating ModesThe diagram in Figure20 shows how the AS3933 operates. Figure 20:Operating Modes Flow ChartAS3933 − Detailed DescriptionListening ModeIn listening mode, the chip is active and looks continuously forthe presence of the carrier on the input of all active channels.In this mode, only the active channel amplifiers and the ClockGenerator are running. In case the carrier is detected, then theRSSI measurements get started on all three channels and theresult is stored in the memory.If the three dimensional detection is not required, then it ispossible to deactivate one or more channels. In case only twochannels are required, then the deactivated channel must bethe number two; while in case only one channel is needed, thenthe active channel must be the number one.Inside the listening mode, it is possible to distinguish thefollowing three low power sub modes:Standard Listening Mode. All channels are active at the sametime.Scanning Mode (Low Power Mode 1). In this sub-mode, a timeslot T=1ms is defined and in each time slot only one channelcan be active. As shown in Figure21 when a certain time slot isover, the current active channel is switched OFF and the nextchannel becomes active and so on. If, for example all threechannels are enabled, in the first time slot the only activechannel is the number one. When the first time slot is over, thechannel one is switched OFF and the channel three becomesactive. During the third time slot, the channel two is active whilethe other two are OFF. This channel rotation starts back fromthe channel one and goes on until the presence of the carrieris detected by any channel. The Scanning mode (channelrotation) is managed internally by the AS3933 and doesn’t needany activity from the host system (MCU). As soon as one channeldetects the frequency, all three channels become immediatelyactive at the same time. The AS3933 can perform asimultaneous multidirectional evaluation (on all threechannels) of the field and evaluate which channel has thestrongest RSSI. The channel with the highest RSSI will be putthrough to the demodulator. In this way it is possible to performmultidirectional monitoring of the field with a currentconsumption of a single channel, keeping the sensitivity asgood as if all channels are active at the same time.AS3933 −D etailed D escription Figure 21:Scanning ModeON/OFF Mode (Low Power Mode 2). In this low powersub-mode the chip sets the receiving channels in polling mode;all active channels are on at the same time only for a certaintime T (where T is 1 ms). The OFF-time can be defined with thebits R4<7:6>. If, for example, R4<7:6>=11 (see Figure25) theactive channels will be 1ms ON and 8ms OFF.Figure 22:ON/OFF ModeArtificial Wake-UpFor each of these sub modes it is possible to enable a further feature called Artificial Wake-up. The Artificial Wake-up is a counter based on the used Clock Generator. Three bits define a time window (see R8<2:0>). If no activity is seen within this time window, the chip will produce an interrupt on the WAKE pin that lasts 128 μs. With this interrupt the microcontroller (μC) can get feedback on the surrounding environment (e.g. read the false wake-up register R13<7:0>) and/or take actions in order to change the setup.Preamble Detection / Pattern CorrelationThe chip can go in to this mode after detecting a LF carrier only if the data correlation is enabled (R1<1>=1). The correlator searches first for preamble bits and then for data pattern. The paragraph Wake-Up Protocol: Pattern Detection Enabled describes how the protocol can be implemented. Should the pattern correlation be disabled (R1<1>=0), the AS3933 goes directly in Data receiving mode (see paragraph Data Receiving).If the received pattern matches, then the wake-up interrupt is displayed on the WAKE output (Wake goes high) and the chip goes in Data receiving mode. If the pattern fails, then the internal wake-up (on all active channels) is terminated and no interrupt is produced.Having per default DAT_MASK disabled (R0<6>=0), the DAT pin shows the entire demodulated incoming signal (carrierburst+preamble+pattern+data).If DAT_MASK is enabled (R0<6>=1), the data will be displayed only after the generation of the WAKEUP interrupt.Note(s): It is important to note that the Manchester decoder must be enabled (R1<3>=1) for this feature.Data ReceivingAfter a successful wake-up the chip enters the data receiving mode. In this mode the chip can be retained a normal OOK receiver. The data is provided on the DAT pin and in case the Manchester decoder is enabled (see R1<3>), the recovered clock is present on the CL_DAT. It is possible to set the chip back to listening mode either with a direct command CLEAR_WAKE (see Figure29) or by using the timeout feature. This feature automatically sets the chip back to listening mode after a certain time defined by the bits R7<7:5>.System and Block SpecificationRegister OverviewFigure 23:Register Overview76543210R0PATT32DAT_MASKON_OFF MUX_123 EN_A2 EN_A3 EN_A1R1ABS_HY AGC_TLIMAGC_U D ATT_ONEN_MANCHEN_PAT2 EN_WPAT EN_XTALR2S_ABS EN_EXT_CLKG_BOOST Reserved DISPLAY_CLK S_WU1R3HY_20m HY_POS FS_SLC FS_ENV R4T_OFF R_VAL GRR5PATT2BR6PATT1BR7T_OUT T_HBITR8BAND_SEL T_AUTOR9BLOCK_AGCReservedR10n.a RSSI1 R11n.a RSSI2 R12n.a RSSI3 R13F_WAKER14RC_CAL_OKRC_CAL_KORC_OSC_TAPSR15n.a.LC_OSC_OKLC_OSC_KOn.a.R16CLOCK_GEN_DISn.a.RC_OSC_MINRC_OSC_MAXn.a LC_OSC_MUXR17n.a.CAP__CH1 R18n.a.CAP__CH2 R19n.a.CAP__CH3Register Description and Default ValuesFigure 24:Default Values of RegistersR0<7>PAT32R/W0Pattern extended to 32 bits (PAT32=0 16 bits, PAT32=1 32bits)R0<6>DAT_MASKR/W0Masks data on DAT pin before wake-up (DAT_MASK = 0→ data not masked; DAT_MASK = 1 → data masked)R0<5> ON_OFF R/W 0 ON/OFF operation mode. (Duty-cycle defined in the register R4<7:6>R0<4> MUX_123 R/W 0 Scan mode enableR0<3> EN_A2 R/W 1 Channel2enableR0<2> EN_A3 R/W 1 Channel3enableR0<1> EN_A1 R/W 1 Channel1enableR0<0> Reserved 0 ReservedR1<7> ABS_HY R/W 0 EnableD ata slicer absolute referenceR1<6> AGC_TLIM R/W 0 AGC acting only on the first carrier burstR1<5> AGC_UD R/W 1 AGCoperating in both direction (up-down) R1<4> ATT_ON R/W 0 Antenna damper enableR1<3>EN_MANCHR/W0Manchester decoder enableR1<2> EN_PAT2 R/W 0 Double wake-up pattern correlationR1<1> EN_WPAT R/W 1 CorrelatorenableR1<0> EN_XTAL R/W 1 CrystaloscillatorenableR2<7> S_ABSH R/W 0D ataslicer absolute threshold reductionR2<6> EN_EXT_CLKR/W 0 Enables external clock generatorR2<5>G_BOOST R/W03dB Amplifier Gain Boost (G_BOOST=1) R2<5>Reserved0ReservedR2<3:2>DISPLAY_CLKR/W00Set to 11 in case the clock generator's frequency isshown on pin CL_DAT.R2<1:0> S_WU1 R/W 00 Tolerance setting for the stage wake-up (see Figure37)R3<7> HY_20m R/W 0 Data slicer hysteresisif HY_20m = 0 then comparator hysteresis = 40mV if HY_20m = 1 then comparator hysteresis = 20mVR3<6> HY_POS R/W 0 Data slicer hysteresis only on positive edges (HY_POS=0, hysteresis on both edges, HY_POS=1, hysteresis only on positive edges)R3<5:3> FS_SCL R/W 100D ata slicer time constant (see Figure45)R3<2:0> FS_ENV R/W 000 Envelop detector time constant (see Figure44)R4<7:6> T_OFF R/W 00 OFF time in ON/OFF operation modeT_OFF=00 1ms T_OFF=01 2ms T_OFF=10 4ms T_OFF=11 8msR4<5:4>D_RES R/W 01 Antennadampingresistor(see Figure40) R4<3:0> GR R/W 0000 Gainreduction(see Figure39)R5<7:0> TS2 R/W 01101001 2nd Byte of wake-up patternR6<7:0> TS1 R/W 10010110 1st Byte of wake-up patternR7<7:5> T_OUT R/W 000 Automatictime-out(see Figure49)R7<4:0> T_HBIT R/W 01011 Bit rate definition (see Figure48)R8<7:5>BAND_SEL R/W000Band selection (see Figure36)R8<2:0> T_AUTO R/W 000 Artificial wake-upT_AUTO=000 No artificial wake-upT_AUTO=001 1sec T_AUTO=010 5sec T_AUTO=011 20sec T_AUTO=100 2min T_AUTO=101 15min T_AUTO=110 1hour T_AUTO=111 2hourR9<7>BLOCK_AGCR/W0Disables AGCR9<6:0> 000000ReservedR10<4:0> RSSI1 R RSSIchannel1R11<4:0> RSSI2 R RSSIchannel2R12<4:0> RSSI3 R RSSIchannel3R13<7:0> F_WAK R Falsewake-upregisterR14<7> RC_CAL_OKR Successful RC calibrationR14<6> RC_CAL_KOR Unsuccessful RC calibrationR14<5:0> RC_OSC_TAPSR RC-Oscillator taps settingR15<4> LC_OSC_OKR LC-OscillatorworkingR15<3> LC_OSC_KOR LC-Oscillator not workingR16<7> CLOCK_GEN_DISR/W 0The Clock Generator output signal displayed on CL_DATpinR16<5> RC_OSC_MINR/W 0 Sets the RC-oscillator to minimum frequencyR16<4> RC_OSC_MAXR/W 0 Sets the RC-oscillator to maximum frequencyR16<2> LC_OSC_MUX3R/W 0 Displays the resonance frequency of LF3P on DAT pinR16<1> LC_OSC_MUX2R/W 0 Displays the resonance frequency of LF2P on DAT pinR16<0> LC_OSC_MUX1R/W 0 Displays the resonance frequency of LF1P on DAT pinR17<4:0> CAPS_CH1 R/W 00000 Capacitor banks on the channel1 R18<4:0> CAPS_CH1 R/W 00000 Capacitor banks on the channel2 R19<4:0>CAPS_CH1R/W00000Capacitor banks on the channel3Serial Peripheral Interface (SPI)This 4-wire interface is used by the Microcontroller (μC) to program the AS3933. The maximum clock operation frequency of the SPI is 6MHz.Figure 25:Serial Peripheral Interface (SPI) PinsNote(s): SDO is set to tristate if CS is low. In this way more than one device can communicate on the same SDO bus.SDI Command Structure. To program the SPI the CS signal has to go high. A SPI command is made up by a two bytes serial command and the data is sampled on the falling edge of SCLK. The Figure 26 shows how the command looks like, from the MSB (B15) to LSB (B0). The command stream has to be sent to the SPI from the MSB (B15) to the LSB (B0).Figure 26:SDI Command StructureThe first two bits (B15 and B14) define the operating mode.There are three modes available (write, read, direct command) plus one spare (not used), as shown in Figure 27.CS D igital Input CMOS Chip SelectSIN D igital Input CMOS Serial Data input for writing registers, data to transmit and/or writing addresses toselect readable register SOUT D igital Output CMOSSerial Data output for received data orread value of selected registers SCLKDigital InputCMOSClock for serial data read and writeB15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B3 B2 B1 B0Figure 27:SDI Command StructureIn case a write or read command happens the next 6 bits (B13to B8) define the register address which has to be written respectively read, as shown in Figure 28.Figure 28:SDI Command Structure0 0WRITE0 1 REA D 1 0 NOT ALLOWE D 1 1 D IRECT COMMAN D0 0 0 0 0 0 R0 0 0 0 0 0 1 R1 0 0 0 0 1 0 R2 0 0 0 0 1 1 R3 0 0 0 1 0 0 R4 0 0 0 1 0 1 R5 0 0 0 1 1 0 R6 0 0 0 1 1 1 R7 0 0 1 0 0 0 R8 0 0 1 0 0 1 R9 001010R10001011R11001100R120111R130 0 1 1 1 0 R14 0 0 1 1 1 1 R15 0 1 0 0 0 0 R16 0 1 0 0 0 1R170 1 0 0 1 0 R180 1 0 0 1 1 R19The last 8 bits are the data that has to be written respectivelyread. A CS toggle high-low-high terminates the commandmode.If a direct command is sent (B15-B14=11) the bits from B13 toB8 defines the direct command while the last 8 bits are omitted.Figure29 shows all possible direct commands:Figure 29:List of Direct Commandsclear_wake 0 0 0 0 0 0reset_RSSI 0 0 0 0 0 1trim_osc 0 0 0 0 1 0clear_false 0 0 0 0 1 1preset_default 0 0 0 1 0 0Calib_RCO_LC000101All direct commands are explained below:•clear_wake: clears the wake state of the chip. In case thechip has woken up (WAKE pin is high) the chip is set backto listening mode.•reset_RSSI: resets the RSSI measurement.•Calib_RCosc: starts the trimming procedure of the internalRC oscillator (see page 29).•clear_false: resets the false wake-up register(R13<7:0>=00).•preset_default: sets all register in the default mode, asshown in Figure24.•Calib_RCO_LC: calibration of the RC-oscillator with theexternal LC tank (see page 31).Writing of Data to Addressable Registers (WRITE Mode). TheSPI is sampled at the falling edge of SCLK (as shown in thefollowing diagrams).A CS toggling high-low-high indicates the end of the WRITEcommand after register has been written. The followingexample shows a write command.。

RF3933资料

Optimum Technology Matching® AppliedGaAs HBT InGaP HBTGaAs MESFET SiGe BiCMOS Si BiCMOS SiGe HBTGaAs pHEMT Si CMOS Si BJTGaN HEMTFunctional Block DiagramRF MICRO DEVICES®, RFMD®, Optimum Technology Matching®, Enabling Wireless Connectivity™, PowerStar®, POLARIS™ TOTAL RADIO™ and UltimateBlue™ are trademarks of RFMD, LLC. BLUETOOTH is a trade-mark owned by Bluetooth SIG, Inc., U.S.A. and licensed for use by RFMD. All other trade names, trademarks and registered trademarks are the property of their respective owners. ©2006, RF Micro Devices, Inc.Product DescriptionOrdering InformationRF IN VGQ Pin 1 (CUT)RF OUT VDQPin 2BASERF3933GaN WIDE-BAND POWER AMPLIFIERThe RF3933 is designed for commercial infrastructure, cellular and WiMAX infrastructure and general purpose broadband amplifier applica-tions. Using an advanced high power density Gallium Nitride (GaN) semi-conductor process, these high-performance amplifiers achieve high efficiency and flat gain over a broad frequency range in a single amplifier design. The RF3933 is an unmatched GaN transistor packaged in a flanged ceramic package which provides excellent thermal stability through the use of advanced heat sink and power dissipation technolo-gies. Ease of integration is accomplished through the incorporation of sim-ple, optimized matching networks external to the package that provide wideband gain and power performance in a single amplifier.FeaturesPeak Power=90W Gain=14dBAdvanced GaN HEMT Tech-nology48V OperationOptimized Evaluation Board Layout for 50Ω Operation ApplicationsCommercial Wireless Infra-structureCellular and WiMAX Infra-structureGeneral Purpose Broadband AmplifiersPublic Mobile RadiosIndustrial, Scientific and Med-icalRF3933GaN Wide-Band Power AmplifierProposed9RoHS Compliant and Pb-Free ProductPackage Style: Flanged CeramicRF3933ProposedPlease contactRFMD Technical Supportat (336) 678-5570for more information.。

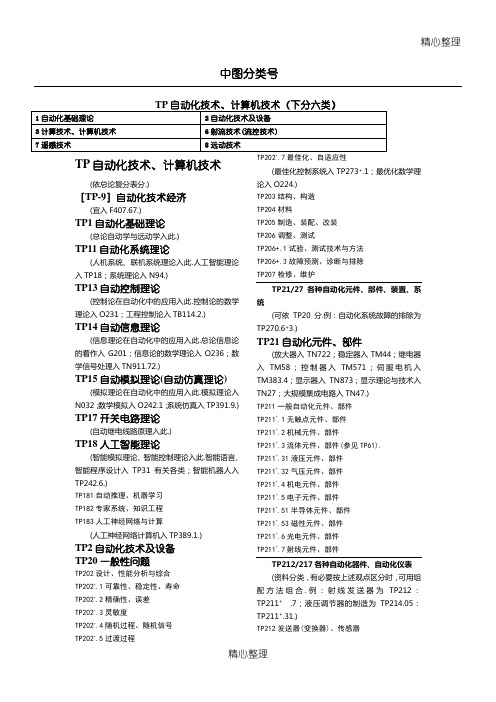

中图分类号-TP

精心整理中图分类号TP自动化技术、计算机技术(依总论复分表分.)[TP-9]自动化技术经济(宜入F407.67.)TP1自动化基础理论(总论自动学与远动学入此.)TP11自动化系统理论(人机系统、联机系统理论入此.人工智能理论入TP18;系统理论入N94.)TP13自动控制理论(理论入O231;工程控制论入(.总论信息论O236;数TP15自动模拟理论(自动仿真理论)(模拟理论在自动化中的应用入此.模拟理论入N032;数学模拟入O242.1;系统仿真入TP391.9.)TP17开关电路理论(自动继电线路原理入此.)TP18人工智能理论(智能模拟理论、智能控制理论入此.智能语言、智能程序设计入TP31有关各类;智能机器人入TP242.6.)TP202+.7最佳化、自适应性(最佳化控制系统入TP273+.1;最优化数学理论入O224.)TP203结构、构造TP204材料TP205制造、装配、改装TP206调整、测试TP206+.1试验、测试技术与方法TP206+.3故障预测、诊断与排除TP207检修、维护TP21/27各种自动化元件、部件、装置、系统(可依TP20分.例:自动化系统故障的排除为TP270.6+3.)TP21自动化元件、部件(放大器入TN722;稳定器入TM44;继电器入TM58;控制器入TM571;伺服电机入TM383.4;显示器入TN873;显示理论与技术入TN27;大规模集成电路入TN47.)TP211一般自动化元件、部件TP211+.1无触点元件、部件TP211+.2机械元件、部件TP211+.3流体元件、部件(参见TP61).TP211+.31液压元件、部件TP211+.32气压元件、部件TP211+.4机电元件、部件TP211+.5电子元件、部件TP211+.51半导体元件、部件TP211+.53磁性元件、部件TP211+.6光电元件、部件TP211+.7射线元件、部件TP212/217各种自动化器件、自动化仪表(资料分类,有必要按上述观点区分时,可用组配方法组合.例:射线发TP211+.7TP212(接收元件、测量元件及此.遥感传感器入TP732.)TP212.1物理传感器TP212.11温度传感器TP212.12机械量传感器TP212.13磁性传感器TP212.14光传感器TP212.2化学传感器TP212.3生物传感器、医学传感器TP212.6智能化传感器TP212.9传感器的应用(总论入此.专论入有关各类.)TP213分配器、配电器TP214调节器、调节阀TP214+.1线性调节器TP214+.2非线性调节器TP214+.3比例调节器(有差调节器)TP214+.4积分调节器(无差调节器)TP214+.5比例积分调节器TP214+.6比例微分调节器TP214+.7程序调节器TP217+.3有源校正元件TP23自动化装置与设备(总论入此;自动机入此.专论入有关各类;自动机理论入TP301.1.)TP24机器人技术(机器人工程学入此.机器人语言入TP31.)TP241机械手TP241.2工业机械手TP241.3专用机械手(办公用、服务行业用、家庭用机械手入此.)TP242机器人(电子机器人入此.)TP242.2工业机器人TP242.3专用机器人(见TP241.3注.)TP242.6智能机器人(人工智能理论入TP18;机器人语言与编程入TP31有关各类;智能电子玩具入TS958.2+8.)TP242.6+1机器人触觉TP242.6+2机器人视觉TP242.6+3机器人听觉TP242.6+4机器人嗅觉TP249应用(总论入此.)TP27自动化系统TP271一般自动化系统TP271+.1无触点系统TP271+.2机械系统TP271+.3流体系统TP271+.31液压系统(液压射流自动控制系统入此.)TP271+.32气压系统(气压射流自动控制系统入此.)TP271+.4机电系统TP271+.5电子系统TP271+.61连续线性系统(单环(回路)系统、TP271TP271TP271TP271TP271TP271+.73断续变参数系统TP271+.74随机变参数系统TP271+.8不连续(离散、断续)系统TP271+.81采样(脉冲)系统TP271+.82数字和程序系统TP271+.83继电器系统(双位、多位系统等入此.)TP271+.9反馈系统TP272/278各种自动化系统(资料分类,如有必要按上述观点区分时,可用组配方法组合.例:液压自动控制系统的调整为TP273.06:TP271+.31.)TP272自动调节、自动调节系统(多关联与多回路自动调节系统入此.)TP273自动控制、自动控制系统(计算机控制入此.控制机入TP391.8;教学机TP273+.4模糊控制、模糊控制系统TP273+.5计算机控制、计算机控制系统(智能控制、智能控制系统入此.)TP274数据处理、数据处理系统(自动检测及其系统入此.)TP274+.1自动记录和指示系统TP274+.2数据收集和处理系统(数据处理装置入此.)TP274+.3自动分类与质量检查系统TP274+.4集中检测与巡回检测系统TP274+.5采用各种新技术的自动检测系统TP274+.51放射线检测及其设备TP274+.52红外线检测及其设备TP274+.53超声波检测及其设备TP275自动随动、自动随动系统(自动随动装置入此.参见TM921.54.)TP276自动拖动、自动拖动系统(自动拖动装置入此.参见TM921.)TP277监视、报警、故障诊断系统TP278自动生产作业线(生产过程自动化、自动化车间、自动化工厂等入此.)TP29自动化技术在各方面的应用(总论入此.专论入有关各类.办公室自动化入C931.4.)TP3计算技术、计算机技术TP3-05计算机与其他学科的关系(计算机文化、计算机心理学等入此.)TP30一般性问题TP301理论、方法(计算机原理入此.开关理论入TP17.)TP301.1自动机理论(自动机入TP23.)TP301.2形式语言理论((TP302设计与性能分析TP302.1总体设计、系统设计TP302.2逻辑设计TP302.4制图TP302.7性能分析、功能分析(可靠性、灵敏度等分析入此.)TP302.8容错技术TP303总体结构、系统结构(总论计算机硬件及其外部设备的着作入此.专论各部件的着作入TP32/38有关各类.<3版类名:结构、构造>)TP303+.1元件TP303+.2插件、机架TP303+.3电源系统(供电形式、保护系统、UPS等入此.)TP304材料TP305制造、装配、改装(计算机的大密度装配技术入此.)TP309.1计算机设备安全TP309.2数据安全TP309.3数据备份与恢复TP309.5计算机病毒与防治TP309.7加密与解密TP31计算机软件TP311程序设计、软件工程TP311.1程序设计(程序正确性理论入此.<3版类名:理论方法>)TP311.11程序设计方法TP311.12数据结构TP311.13数据库理论与系统TP311.131数据库理论(各种数据库语言和数据库管理系统入以下有关各类.)TP311.132数据库系统:按类型分(总论数据库系统入此.各种具体数据库系统入TP311.138.专用数据库见TP392注.)TP311.132.1层次数据库TP311.132.2网状数据库TP311.132.3关系数据库TP311.132.4面向对象的数据库TP311.133.1分布式数据库TP311.133.2并行数据库TP311.134.1模糊数据库TP311.134.3多媒体数据库TP311.135.1文献型数据库TP311.135.3事实型数据库TP311.135.4超文本数据库TP311.138数据库系统:按系统名称分(依数据库系统名称的前两个英文字母区分,并按字母序列排.若系统名称的前两个字母相同,则再取第三个,以此类推.例:dBASE数据库为TP311.138DB.)TP311.5软件工程TP311.51程序设计自动化TP311.52软件开发TP311.53软件维护((PCTOOLS、杀病毒等软件入此.)TP312程序语言、算法语言(依语言名称的前两位英文字母区分,并按字母序列排,若程序语言名称的前两位字母相同时,则取第三位字母,以此类推,例:ALGOL语言为TP312AL,JAVA语言为TP312JA,TP312AL排在TP312JA之前.)TP313汇编程序(汇编语言入此.)TP314编译程序、解释程序TP315管理程序、管理系统TP316操作系统TP316.1/.5操作系统:按类型分(总论入此,具体某一操作系统入TP316.6/.8.)TP316.1分时操作系统TP316.2实时操作系统(WindowsNT入TP316.86.)TP316.8网络操作系统TP316.81Unix操作系统(兼论XENIX操作系统入此.)TP316.82XENIX操作系统TP316.83NOVELL操作系统TP316.84OS/2操作系统TP316.86WindowsNT操作系统TP316.89其他TP316.9中文操作系统(CCDOS、SPDOS、UCDOS等入此.兼论汉字信息处理入TP391.12.)TP317程序包(应用软件)(通用应用软件,如购买计算机时随机带来的软件包等入此.)TP317.1办公自动化系统(总论入此,如总论OFFICE系统的着作入此.专论入有关各类.如专论OFFICE系统中字处理WORD的着作入TP317.2;专论WORD使用入TP391.12.参见C931.4.)TP317.2文字处理软件(WPS、WORD、中文之星等软件的开发、研制入此.软件的使用入TP391.12.)TP317.3表处理软件(CCED、EXCEL等软件的开发、研制入此.软件的使用入TP391.13.)TP317.4图像处理软件(图形处理软件、动画制作软件入此.例:PowerPoint.软件的使用入TP319专用应用软件(总论入此.专论入有关各类TP319:>)(解算装置入此.)TP321TP321+.1求积仪、曲线仪TP321+.2积分器TP321+.21机械积分器TP321+.22液压积分器TP321+.23气压积分器TP321+.24电气、机电积分器TP321+.3手动计算机TP321+.5电动计算机TP322分析计算机(穿孔卡片计算机)电子式分析计算机入此.)TP322+.1穿孔机TP322+.2验孔机TP322+.3分类机TP322+.5制表机TP323电子计算器TP323+.1台式计算器TP323+.2袖珍计算器TP33/38各种电子计算机(可仿TP30分.例:电子数字计算机的电源系(开关电路、门电路、放大整形电路等入此.)TP332运算器和控制器(CPU)(参见TP342.)TP332.1逻辑部件TP332.1+1寄存器(移位寄存器等入此.)TP332.1+2计数器TP332.2运算器TP332.2+1加、减法器TP332.2+2乘、除法器TP332.3控制器、控制台(监视电路、微程序设计技术入此.参见TM571.)TP333存贮器(信息存贮技术入此.参见TP343.)TP333.1内存贮器(主存贮器)总论TP333.2外存贮器(辅助存贮器)总论TP333.3磁存贮器及其驱动器(磁存贮器的制造入TQ58.<3版类名:磁存贮器>)TP333.3+1磁芯存贮器TP333.3+11单孔磁芯存贮器TP333.3+12多孔磁芯存贮器(磁通变换器、双轴磁芯存贮器等入此.TP333.3+2磁薄膜存贮器)TP333.3+21平面磁薄膜存贮器TP333.3+3磁泡存贮器TP333.3+4磁鼓存贮器TP333.3+5磁盘存贮器(包括软盘、硬盘.)TP333.3+6磁带存贮器TP333.3+7电磁继电器存贮器TP333.4光存贮器及其驱动器(光盘服务器(光盘塔)、光盘刻录器入此.<3版类名:光存贮器>)TP333.4+1磁光存贮器TP333.4+2全息存贮器TP333.4+3激光存贮器TP333.5TP333.5+1TP333.5+2金属-氧化物-半导体>)(<3版类名:随机存贮器>)TP333.93交换器TP333.95延迟线存贮器TP333.95+1水银柱延迟线存贮器TP333.95+3石英晶体延迟线存贮器TP333.95+5磁滞伸缩延迟线存贮器TP333.96虚拟存贮器TP334外部设备(参见TP334.)TP334.1/.4各种外部设备(<以下TP334.1/.4为新的体系,原资料分类改入以下类目>)TP334.1终端设备(显示器入此.参见TN873.)TP334.2输入设备(鼠标入此.)TP334.2+1图形输入设备(光笔入此.)TP334.2+2图像输入设备(自动扫描仪入此.)TP334.2分(输入设备改为输出设备).)TP334.4输入输出控制器[TP334.5]外存储器(宜入TP333.2.)TP334.7接口装置、插件(网卡、声卡、电影卡、电视卡等入此.)TP334.8打印装置(网络打印机等入此.)TP334.8+1针式打印机(卡片打印机入此.)TP334.8+2热敏打印机TP334.8+3喷墨打印机TP334.8+4激光打印机TP334.8+8各种用途打印机(票据打印机入此.)TP334.9其他TP335信息转换及其设备(信息转换技术入此.编码器入TN762;译码器入TN764.)TP335+.1模拟-数字转换设备TP335+.2文字-代码转换设备TP335+.3图形-代码转换设备TP335+.4数字-模拟转换设备TP336总线、通道TP337仿真器TP338各种电子数字计算机(以下涉及多种分类标准的计算机,入最后编列的类.例:分布式小型计算机入TP338.8.)[TP338.1]微型计算机(宜入TP36.)TP338.2小型计算机TP338.3中型计算机TP338.4大型、巨型计算机TP338.6并行计算机TP338.7陈列式计算机TP338.8分布式计算机TP34电子模拟计算(连续作用电子计算机)TP342运算放大器和控制器(参见TP332.)TP342+.1运算放大器TP342+.2运算器TP342+.21加、减法器TP342+.22乘、除法器TP342+.23平方器、开方器TP342TP342TP343TP344TP346函数发生器TP347延时器TP348各种电子模拟计算机TP348+.1微分分析器与增量计算机(数字微分分析器入TP352+.1.)TP348+.2直流电子模拟计算机TP348+.3交流电子模拟计算机TP35混合电子计算机TP352数字-模拟计算机TP352+.1数字微分分析器TP353模拟-数字计算机TP36微型计算机(仿TP331/337分,必要时再仿TP30分.例:微型计算机存贮器性能分析入TP363.027.微机软件入TP31有关各类;微机的应用入TP39有关各类.)TP381激光计算机TP382射流计算机TP383超导计算机TP384分子计算机TP387第五代计算机(智能型计算机、超智能计算机、人工智能模拟、通用推理机、数据流计算机等入此.人工智能理论入TP18;智能机器人入TP242.6.)TP389.1人工神经网络计算机(人工神经网络入TP183.)TP39计算机的应用TP391信息处理(信息加工)(总论图像处理入TN911.73.)TP391.1文字信息处理[TP391.11]汉字信息编码(宜入H127.)TP391.12汉字处理系统(参见TP317.2.)TP391.13表格处理系统(参见TP317.3.)TP391.14文字录入技术(中英文打字、汉字输入法等入此.)TP391.2翻译机(机器翻译及其理论入H085.)TP391.3检索机(机器检索、机器检索速度等入此.利用计算机进行情报检索的着作入G354.4.)TP391.4模式识别与装置(自动读版装置入此.模式识别理论入O235.参见TN919.8.)TP391.41图像识别及其装置(计算机图形学入此;计算机绘图、三维动画制作、图形识别及其装置等入此.计算机辅助图入TP391.72.<3[TP391.42]声音识别TN912.34.)TP391.43TP391.44光模式识别及其装置(((机器教学入G433.)TP391.7机器辅助技术(计算机辅助教学入G434.)TP391.72机器辅助设计(CAD)、辅助制图(总论入此.<3版类名:机器辅助设计、自动设计(CAD)>)TP391.73机器辅助技术制造(CAM)(总论入此.)TP391.75机器辅助计算(CAC)(总论入此.)TP391.76机器辅助测试(CAT)(总论入此)TP391.77机器辅助分析(CAA)TP391.8控制机(计算机控制入TP273.)TP391.9计算机仿真(总论仿真技术、系统仿真、虚拟现实等入此.自动仿真理论入TP15.<3版类名:仿真机>)TP392各种专用数据库(虚拟网理论、网络仿真理论等入此.参见TM711.)TP393.02计算机网络结构与设计(网络分析、网络拓扑等入此.)TP393.03网络互连技术[TP393.04]通信规程、通信协议(宜入TN915.04.)[TP393.05]网络设备(宜入TN915.05.)TP393.06计算机网络测试、运行TP393.07计算机网络管理(网络管理软件入此.)TP393.08计算机网络安全(防火墙技术、网络安全软件入此.)TP393.09计算机网络应用程序(网络语言入TP312.)TP393.092网络浏览器(网址资源、WWW、Netscape、主页制作等入此.)TP393.093文件传送程序(FTP)TP393.094远程登录(Telnet)(公告牌(BBS)等入此.)TP393.098电子邮件(E-mail)TP393.1/.4各种计算机网(可仿TP393.0分.例:仿真局域网为TP393.101.)TP393.1局域网(LAN)、城域网(MAN)(Novell网入此.)TP393.11以太网(高速以太网、千兆位以太网入此.)TP393.12令牌网(TP393.13DQDB网()(TN915.63.)(总论ATM(异步传输模式)网入TN915.2.)[TP393.17]无线局域网(宜入TN925.93.)TP393.18校园网、企业网(Intranet)TP393.2广域网(WAN)(<3版类名:远程网络>){TP393.3}洲际网络(<停用:4版改入TP393.4>)TP393.4国际互联网(因特网Internet入此.国家信息基础设施[信息高速公路]入TN915.<3版类名:全球网络>)TP399在其他方面的应用(总论入此.在其他科学中的应用入有关各类.如愿集中于此,可采用组配编号法.例:商业售货计算机为TP399:F716.)TP6射流技术(流控技术)(气动技术入此.)TP605制造、装配TP606调整、测试TP606+.1静态测试TP606+.2动态测试TP607检修、维护TP61/67各种射流装置(可仿TP60分.例:射流元件性能分析为TP610.2.)TP61射流元件(参见TP211+.3)TP61+1有源射流元件TP61+2无源射流元件TP61+3数字射流元件(逻辑元件)TP61+3.1附壁式射流元件TP61+3.2紊流式射流元件(紊流放大器)(管状射流元件、板状射流元件等入此.)TP61+3.3动量交换式元件TP61+4比例射流元件(模拟元件)TP61+4.1对冲元件(模拟转换元件入此.)TP61+4.3涡流元件TP61+5液压式射流元件TP62射流附件TP62+1升压器TP62+2转换器TP62+3延时器TP62+4抽负器TP63检测发信装置TP64执行机构TP65动力源TP65+1气源净化系统TP65+2气源附件TP65+2.1过滤器TP65+2.2减压阀TP65+2.3定值器TP66射流控制线路TP67射流自动控制系统(总论入此.自动控制)入TP271+.3.)TP69射流技术的应用(TP7TP701TP702TP703TP704TP705制造、装配TP706调整、测试TP707检修、维护TP72/75各种遥感及装置(可仿TP70分.例:红外遥感传感器的装配入TP732.205.)TP72遥感方式TP721依传感器接受信号的来源分TP721.1被动式遥感TP721.2主动式遥感TP722依探测的波长范围分TP722.3紫外遥感TP722.4可见光遥感TP722.5红外遥感TP722.6微波遥感TP73探测仪器及系统TP731多光谱扫描仪TP732遥感传感器(参见TP212.)(总论入此.在其他科学中的应用入有关各类.如愿集中于此.可采用组配编号法.例:气象遥感为TP79:P407.)TP8远动技术TP80一般性问题TP801理论、研究(远动学入此.)TP802设计和性能分析TP802+.1可靠性、稳定性、寿命TP802+.2精确性、误差TP802+.3灵敏度TP802+.4远动信号、信号发射、接收及转换TP802+.5作用距离TP802+.6干扰(噪声)、抗干扰TP802+.7最佳化、自适应性TP802+.8信道划分TP803结构TP804材料TP805制造、装配TP806调整、测试TP806+.1试验、测试技术与方法TP806+.3故障预测、诊断与排除TP807检修、维护TP81/87各种远动装置及系统(可仿TP80分.例:远距离测量系统的检修为TP873.07.)[TP81]远动元件、部件(宜入TP21.) TP83远动化装置TP84远程信道TP84+1有线信道(电力线载波入此.)TP84+2无线电中继信道TP87远动化系统(总论远距离调节、控制和测量系统入此.)TP871远距离调节、远距离调节系统TP872远距离控制和信号、远距离控制和信号系统TP872+.1近作用的遥控系统TP872+.2断续遥控系统TP872+.21频率制TP872+.22时间制TP872+.3连续遥控系统TP872+.31频率制TP872TP872TP873TP873TP873TP873TP873TP873+.2多路遥测系统TP873+.21频率划分制TP873+.22时间划分制TP873+.23脉码划分制TP89远动技术在各方面的应用(总论入此.专论入有关各类.)。

清热化痰法治疗快速性心律失常的Meta分析