数电第二章习题

数电第2章作业答案

自我检测题解

题 2.1 答:TTL 与非门输入端采用多发射极管的主要作用是 速度快 。 题 2.2 答:TTL 与非门多余输入端的处理方法是 高电平或悬空或接电源或与其他输入 端并接 。 题 2.3 答:题 2.3 肖特基三极管是普通三极管集电结并联一个 肖特基二极管 (SBD) ,其正向压降较小容易导通。当三极管趋于深度饱和状态时,肖特基二极 管 分流 了三极管的一部分电流,使三极管工作在浅饱和状态。 题 2.4 答:TTL 与非门输出端采用推拉式输出的主要作用是 较强的负载能力 。 题 2.5 答:TTL 与非门的灌电流负载发生在输出低电平电平情况下,负载电流越大,则 输出电平越 高 。 题 2.6 答:门电路输入端个数称为门的 扇入 系数,门电路带同类门数量的多少称为门 扇出 系数。 题 2.7 答:TTL 三态门的三种可能的输出状态分别是 高电平 、 低电平 和 高阻态 。 题 2.8 答:在 TTL 三态门、OC 门、与非门和异或门电路中,能实现线与功能的门电路 有 OC 门,三态门 ,能实现总线连接方式的门电路有 三态门 。 题 2.9 答:CMOS 门电路与 TTL 门电路相比最大的优点是 低功耗 。 题 2.10 答:用工作速度来评价 TTL、ECL 和 CMOS 集成电路,速度快的集成电路依次 为 ECL;TTL;CMOS 。 题 2.11 答:用抗干扰能力来评价 TTL、ECL 和 CMOS 集成电路,抗干扰能力强的集成 电路依次为 CMOS;TTL;ECL 。 题 2.12 两输入异或电路的一输入端接地,另一输入端接信号,输出与输入的关系式 (A) F=A; (B) F=B; (C) F= A ; (D) F= B 。

数字电路-第2章习题解答PPT课件

解:设vBE=0V时,三极管T截止。T截止

时,IB=0。此时

VCC +10V

vI 00(10)

2

10

vI=2V

vI

R1 2kΩ

1R0CkΩvOT临界饱和时,vCE=0.7V。此时

6

2-8 在用或非门时,对多余输入端的处理方 法同与非门处理方法有什么区别?

A& B

A ≥1 B

F =A ·B 与非:接高电平; 或非:接低电平。

F =A +B

7

2-9 异或门能作为非门使用吗?为什么?

A =1 B

F F AB AB B 1, F A B 0, F A

所以一端接高电平即可构成非门电路。

端提升,为高电平;与非门输出

FA

FCAB

A B

当C=0时,三态门高 C

&

CMOS &F

阻,与非门输出F=1

EN

20kΩ

F C FCCABC

40

练习题2

•试判断如图所示电路能否按各图所要求的逻 辑关系正常工作?若不能正常工作,请做相 应的改动。若电路接法有错,改电路;若电 路正确但给定的逻辑关系不对,则写出正确 的逻辑表达式。能正常工作的在图中括号内 打“√”,否则打“×”。已知TTL门的 IOH/IOL=0.4mA/10mA,VOH/VOL=3.6V/0.3V, CMOS门的VDD=5V,VOH/VOL=5V/0V, IOH/IOL=0.51mA/0.51mA。

错误。 ⒉A=0,无论B、C取何值,AB=AC=0 ,故运算

错误。 ⒊1+B=1,A=B=1时,AB=1,故运算正确。

数字电路与逻辑设计 第02章 习题解答

IoH 0.5mA = ≈ 167 IiH 3 × 1uA IoH 0.5mA = ≈ 167 IiH 3 × 1uA

由 CMOS 的与非门电路可以得到,当与非门的 3 个输入端并接到高电平时,三个串接的 NMOS 管导通,而三个并接的 PMOS 管都截止,所以其输入高电平总电流为 3×IiH, n = 2)当非们输出为低电平时: 由 CMOS 的或非门电路可以得到,当或非门的 3 个输入端并接到低电平时,三个并接的 NMOS 管都截止,而三个串接的 PMOS 管导通,所以其输入低电平总电流为 3×IiL, n =

题图 2-7 答案:不能 2-8 由 CMOS 门组成的电路如题图 2-8 所示。已知 VDD =5V,VOH ≥3.5V,VOL ≤0.5V。门的驱动能力 IO=±4mA。问某人根据给定电路写出的输出表达式是否正确?

题图 2-8 (a) F1 = AB • CD 2-9 正确 (b) F2 =AB+CD 正确 (c) F3 =AB+CD 不正确

题图 2-5

∴ RL ≤

答案:①输出为高电平时:

′ − VOH (min) VCC nI OH + mI IH

(n = 2, m = 8)

=

5−3 = 3.2k 2*0.15 + 8*0.04

RL ≥

②当输出为低电平:

′ − VOL VCC (m ' = 6) I LM − m′I IL 5 − 0.3 = 0.47 K 16 − 6 ×1

RP (V − v BE 1 ) RP + R1 CC

0.1 (5 − 0.7) = 0.14V = 0.1 + 3

vI2= vI1 =0.14V

(5)vI1 经 10K 电阻接地 2-3

数字电子技术第二章(逻辑门电路)作业及答案

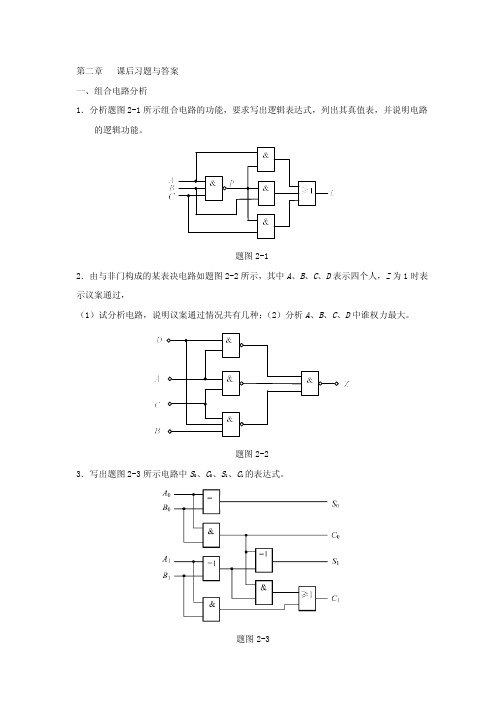

数字电子技术第二章(逻辑门电路)作业及答案第二章(逻辑门电路)作业及答案1.逻辑门电路如下图所示:(1)电路均为TTL电路,试写出各个输出信号的表达式。

(2)电路若改为CMOS电路,试写出各个输出信号的表达式。

答案:(1),,,(2),,,2、已知TTL反相器的电压参数为V IL(max)=0.8V,V OH(min)=3V,V TH=1.4V,V IH(min)=1.8V,V OL(max)=03V,V CC=5V,试计算其高电平噪声容限V NH和低电平噪声容限V NL。

答案:V NL= V IL(max) - V OL(max)=0.5V,V NH= V OH(min) - V IH(min) =1.2V。

3、试写出图2-1、图2-2所示逻辑电路的逻辑函数表达式。

解:(1)(2)4、试分析图2-3所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

5、试简要回答下列问题。

(1)有源(图腾柱)输出与集电极开路(OC)输出之间有什么区别?解:OC门输出端只能输出低电平和开路状态,其输出级需要上拉电阻才能输出高电平,且上拉电源可以与芯片电源不同,因此常用于不同电源电压芯片之间实现信号电平变换,OC门输出端可以并联实现线与;有源输出可以输出低电平与高电平,两个有源输出端连接在一起时,若是一个输出端输出高电平,另外一个输出端输出低电平时,可引起较大电流损坏输出级。

(2)TTL逻辑电路输入端悬空时,可视为输入高电平信号处理,而CMOS逻辑电路输入端则不允许悬空使用,试说明其原因。

解:因为CMOS电路的输入端具有非常高的输入阻抗,容易受到干扰,一旦受到干扰后,会使输出电平发生转换,产生功耗,因此输入端不能悬空,应该连接确定的逻辑电平。

6.请查阅74LS00芯片手册(常规温度范围的),回答如下问题:(1)电源电压范围;(2)输出高电平电压范围;(3)输出低电平电压范围;(4)输入高电平电压范围;(5)输入低电平电压范围;(6)该芯片的电源电流;(7)典型传播延迟时间;(8)扇出系数。

数电第二章习题教材

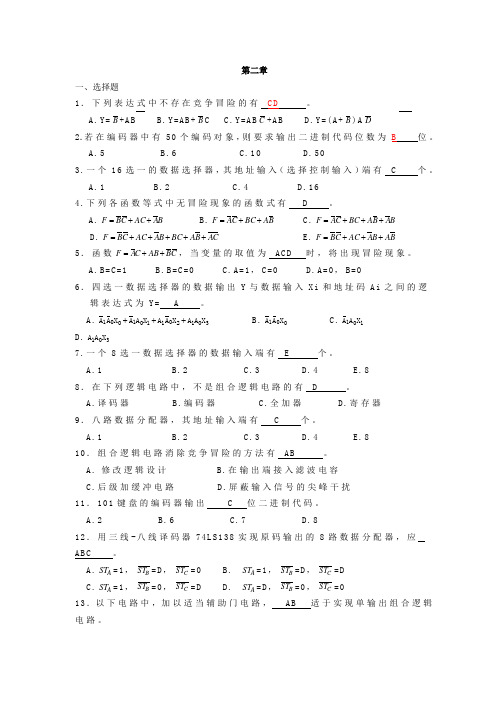

第二章一、选择题1.下列表达式中不存在竞争冒险的有 C D 。

A.Y =B +A BB.Y =A B +B CC.Y =A B C +A BD.Y =(A +B )A D2.若在编码器中有50个编码对象,则要求输出二进制代码位数为B 位。

A.5B.6C.10D.503.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。

A.1B.2C.4D.164.下列各函数等式中无冒险现象的函数式有 D 。

A.B A AC C B F ++=B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++=5.函数C B AB C A F ++=,当变量的取值为 A C D 时,将出现冒险现象。

A.B =C =1B.B =C =0C.A =1,C =0D.A =0,B =06.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 017.一个8选一数据选择器的数据输入端有 E 个。

A.1B.2C.3D.4E.88.在下列逻辑电路中,不是组合逻辑电路的有 D 。

A.译码器B.编码器C.全加器D.寄存器9.八路数据分配器,其地址输入端有 C 个。

A.1B.2C.3D.4E.810.组合逻辑电路消除竞争冒险的方法有 A B 。

A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰11.101键盘的编码器输出 C 位二进制代码。

A.2B.6C.7D.8 12.用三线-八线译码器74L S 138实现原码输出的8路数据分配器,应 A B C 。

A.A ST =1,B ST =D ,C ST =0B. A ST =1,B ST =D ,C ST =DC.A ST =1,B ST =0,C ST =DD. A ST =D ,B ST =0,C ST =013.以下电路中,加以适当辅助门电路, A B 适于实现单输出组合逻辑电路。

数字电路与系统设计:第2章习题答案

习题目录2.1 (2)2.2 (2)2.3 (2)2.4 (3)2.5 (3)2.6 (4)2.7 (4)2.8 (4)2.9 (4)2.10 (4)2.11 (5)2.12 (5)2.13 (7)2.14 (8)2.1 有A 、B 、C 三个输入信号,试列出下列问题的真值表,并写出最小项表达式∑m ( )。

(1)如果A 、B 、C 均为0或其中一个信号为1时。

输出F=1,其余情况下F=0。

(2)若A 、B 、C 出现奇数个0时输出为1,其余情况输出为0。

(3)若A 、B 、C 有两个或两个以上为1时,输出为1,其余情况下,输出为0。

F 1m 4)F 2m )3m 7)2.2 试用真值表证明下列等式:(1)A ⎺B+B ⎺C+A ⎺C=ABC+⎺A ⎺B ⎺C (2)⎺A ⎺B+⎺B ⎺C+⎺A ⎺C=AB BC AC 证明:(1)真值表相同,所以等式成立。

(真值表相同,所以等式成立。

2.3 对下列函数,说明对输入变量的哪些取值组合其输出为1? (1)F (A,B,C )=AB+BC+AC(2)F (A,B,C )=(A+B+C)(⎺A+⎺B+⎺C) (3)F (A,B,C )=(⎺AB+⎺BC+A ⎺C)AC解:本题可用真值表、化成最小项表达式、卡诺图等多种方法求解。

(1)F 输出1的取值组合为:011、101、110、111。

(2)F 输出1的取值组合为:001、010、011、100、101、110。

(3)F输出1的取值组合为:101。

2.4试直接写出下列各式的反演式和对偶式。

(1)F(A,B,C,D,E)=[(A⎺B+C)·D+E]·B(2) F(A,B,C,D,E)=AB+⎺C⎺D+BC+⎺D+⎺CE+B+E(3) F(A,B,C)=⎺A⎺B+C ⎺AB C解:(1) ⎺F=[(⎺A+B)·⎺C+⎺D]·⎺E+⎺BF'=[(A+⎺B)·C+D]·E+B(2) ⎺F=(⎺A+⎺B)(C+D)·(⎺B+⎺C)·D·(C+⎺E)·⎺B·⎺EF'=(A+B)(⎺C+⎺D)·(B+C)·⎺D·(⎺C+E)·B·E(3)⎺F=(A+B)·⎺C+ A+⎺B+CF'=(⎺A+⎺B)·C+⎺A+B+⎺C2.5用公式证明下列等式:(1)⎺A⎺C+⎺A⎺B+BC+⎺A⎺C⎺D=⎺A+BC(2)AB+⎺AC+(⎺B+⎺C) D=AB+⎺AC+D(3)⎺BC⎺D+B⎺CD+ACD+⎺AB⎺C⎺D+⎺A⎺BCD+B⎺C⎺D+BCD=⎺BC+B⎺C+BD(4)A⎺B⎺C+BC+BC⎺D+A⎺BD=⎺A + B +⎺C+⎺D证明:(1) ⎺A⎺C+⎺A⎺B+BC+⎺A⎺C⎺D ——⎺A⎺C⎺D被⎺A⎺C削去=⎺A(⎺B+⎺C)+BC=⎺A BC+BC ——削去互补因子=⎺A+BC(2) AB+⎺AC+(⎺B+⎺C) D=AB+⎺AC+BC D+BC ——增加冗余因子BC,为了削去BCD中的BC =AB+⎺AC+D(3)⎺BC⎺D+B⎺CD+ACD+⎺AB⎺C⎺D+⎺A⎺BCD+B⎺C⎺D+BCD=⎺BC⎺D+BD+ACD+⎺AB⎺C⎺D+⎺BCD+B⎺C⎺D ——B⎺CD与BCD合并成BD=⎺BC⎺D+BD+ACD+⎺AB⎺C⎺D+⎺BCD+B⎺C ——BD与B⎺C⎺D削去互补因子=⎺BC⎺D+BD+ACD+⎺BCD+B⎺C ——⎺AB⎺C⎺D被B⎺C削去=⎺BC+BD+ACD+B⎺C ——⎺BC⎺D与⎺BCD合并=⎺BC+BD+CD+ACD+B⎺C ——增加CD,可削去ACD=⎺BC+B⎺C+BD(4)A⎺B⎺C+BC+BC⎺D+A⎺BD=A⎺B⎺C (BC+BC⎺D)+⎺A+B+⎺D ——BC+BC⎺D削去互补因子=A⎺B⎺C (⎺B+⎺C+⎺D)+⎺A+B+⎺D=A⎺B⎺C +A⎺B⎺C⎺D+⎺A+B+⎺D=A⎺B⎺C+⎺A+B+⎺D=⎺A+ B +⎺C+⎺D2.6已知⎺ab+a⎺b=a⊕b,⎺a⎺b+ab=a b,证明:(1)a⊕b⊕c=a b c(2)a⊕b⊕c=⎺a ⎺b ⎺c证明:(1)a⊕b⊕c=(a⊕b)⊕c=a⊕b · c+(a⊕b)·⎺c=(a b)·c+ a b⎺c=a b c(2)(a⊕b)⊕c = (a⊕b) c=a b c=a b ⎺c=⎺a ⎺b ⎺c2.7试证明:(1)若⎺a⎺b+ a b=0则a x+b y=a⎺x + b⎺y证明:⎺a⎺b+ a b=0 即a b=0 ∴a =⎺bax + by =⎺bx + by = ⎺bx · by=(b+⎺x)(⎺b+⎺y)=b⎺y+⎺b⎺x+⎺x⎺y=a⎺x+b⎺y(2)若⎺a b+a⎺b=c,则⎺a c + a⎺c=b证明:a⊕b=c => a⊕b⊕c=c⊕c => a⊕b⊕c=0 => a⊕b⊕c⊕b=0⊕b => a⊕c=b2.8将下列函数展开成最小项之和:(1)F(ABC)=A+BC(2)F(ABCD)=(B+⎺C)D+(⎺A+B) C(3)F(ABC)=A+B+C+⎺A+B+C解:(1)F(ABC)=A+BC=A(B+⎺B)(C+⎺C)+(A+⎺A)BC=⎺ABC+A⎺B⎺C+A⎺BC+AB⎺C=∑m(3,4,5,6)(2) F(ABCD)=(B+⎺C)D+(⎺A+B) C=BD+⎺CD+⎺AC+BC=∑m(1,3,5,6,7,9,13,14,15)(3) F(ABC)=A+B+C+⎺A+B+C=∑m(0,2,6)2.9将题2.8中各题写成最大项表达式,并将结果与2.8题结果进行比较。

万里学院-数字电子技术基础-第二章习题及参考答案

题图 2-12 13.题图 2-13 是用 4 选 1 数据选择器设计的一个逻辑电路,试写出输出逻辑函数 Z 的最简 与或表达式。 表1 4 选 1 数据选择器功能表

A1

× 0 0 1 1

A0

× 0 1 0 1

E

W

0

1 0 0 0 0

D0 D1 D2 D3

题图 2-13 14.分析题图2-14中所示的逻辑电路,其中741LS51为8选1数据选择器,要求写出输出函数Z 的最简与-或表达式。

F1 ( A, B, C ) AC A BC A BC F2 ( A, B, C ) A BC AB C BC

题图2-22

题图2-23

16.试用如题图 2-23 所示的一片 8 选 1 数据选择器 74LS151 实现逻辑

Z ( A, B, C ) A B C A BC A BC 。

题图 2-6

7.组合逻辑电路及输入波形如题图 2-7 所示,要求:写出 L1、L2、L3 的逻辑表达式,分析 电路功能,并画出 L2 的波形。

题图 2-7 8.分析如题图 2-8 所示电路的逻辑功能,写出 Y1、Y2 的逻辑函数式,列出真值表,指出电 路完成什么逻辑功能。

题图 2-8 9.分析题图 2-9 电路的逻辑功能。要求: (1)写出各输出端的逻辑表达式并化简; (2)列出真值表; (3)总结电路的逻辑功能。

6.某学校有三个实验室,每个实验室各需 2kW 电力。这三个实验室由两台发电机组供电, 一台是 2kW,另一台是 4kW。三个实验室有时可能不同时工作,试设计一逻辑电路,使资源 合理分配。 7.设计一个能被 2 或 3 整除的逻辑电路,其中被除数 A、B、C、D 是 8421BCD 编码。规定能 整除时,输出 L 为高电平,否则,输出 L 为低电平。要求用最少的与非门实现。 (设 0 能被 任何数整除) 8.设计表决电路,要求 A、B、C 三人中只要有半数以上同意,决议就能通过。但同时 A 还 具有否决权,即只要 A 不同意,即使多数人意见也不能通过(要求用与非门实现) 。 9.有三个温度探测器,当探测的温度超过 60℃时,输出控制信号为 l;如果探测的温度 低于 60℃时,输出控制信号为 0,当有两个或两个以上的温度探测器输出 1 信号时,总 控制器输出 1 信号,自动控制调控设备,使温度降低到 60℃以下。试设计一组合逻辑电 路实现上述表决电路。 10.设计一个电话机信号控制电路。电路有 I0(火警) 、I1(盗警)和 I2(日常业务)三 种输入信号,通过排队电路分别从 L0、L1、L2 输出,在同一时间只能有一个信号通过。如 果同时有两个以上信号出现时,应首先接通火警信号,其次为盗警信号,最后是日常业 务信号。试按照上述轻重缓急设计该信号控制电路,要求用 2 输入端与非门来实现。 11.如题图 2-20 所示,为一工业用水容器示意图,图中虚线表示水位,A、B、C 电极被水 浸没时会有信号输出,试用与非门构成的电路来实现下述控制作用:水面在 A、B 间,为正 常状态,亮绿灯 G;水面在 B、C 间或在 A 以上为异常状态,点亮黄灯 Y;面在 C 以下为危险 状态,点亮红灯 R。要求写出设计过程。

数电新习题集(第二章解答)

2.1 列出下列各函数的真值表。

(1)B A AC C B A F +=),,(; (2)C B A C B A F ⊕⊕=),,(; 答案:2.2 试用真值表证明下列等式成立。

(1)))((C A B A BC A ++=+ 答案:A B C A BC +(A B)(A C)++0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1112.3 分别用摩根定律和反演规则对下列表达式求反。

(1)))((D C B D C B A F +++=; (2)D A D C ABC F ++=; (3))(D C B A CD B A F +++=。

答案:(1) FAB(C D)(B C D)=+++=A B CD BCD +++(2)F ABC CD AD =++ =(A B C)(C D)(A D)++++(3)F AB CD(A BC D)=+++ =AB CD A(BC D)+++2.4 用对偶规则求各式的对偶式。

(2)DE C B D A ++; (3)D C B A +++。

答案:(2) (A D)(B C(D E)+++(3) ABCD2.5 三人表决电路的输入信号A 、B 、C 表示甲、乙、丙三人对议案的态度。

当某人支持该议案时,相应的输入为1,否则为0。

仅当2人或2人以上支持时,该议案才能通过,这时输出F 为1,否则为0。

试导出该电路的真值表并写出其逻辑表达式。

答案:A B C F0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 11F ABC ABC ABC ABC =+++2.6 X =X 2X 1X 0和Y =Y 2Y 1Y 0分别是某数据处理电路的输入和输出,且均为二进制数。

若(1) 0≤X ≤2时,Y =2X ; (2) 3≤X ≤5时,Y =X -1; (3) X ≥6时,Y =X 。

数字电路课后习题答案第二章

2.8

(a)

(b)

2.9

(a)

(b)

2.10 (a)

(b)

(c)

2.11 decimal signed-magnitude two’s-magnitude one’s-complement 2.12 (a)

11010100 (b) 101110011 (c) 01011101 (d) 00100110 + 10101011 + 11010110 + 00100001 + 01011010 ------------------------------------------------------------------------------------------------------------------------01111111 10001111 01111101 10000000 yes no no yes

2.6

(a) (c) (e) (g) (i)

125 10 = 1111101 2 209 10 = 11010001 2 132 10 = 1000100 2 727 10 = 10402 5 1435 10 = 2633 8 1100010 110101 + 11001 ------------------------1001110 110000 110101 - 11001 -----------------------011100 1372 + 4631 ------------------6223 1372 + 4631 ------------------59A3 (b)

2.7

(a)

111111110 (d) 11000000 1011000 (c) 11011101 101110 1110010 + 1100011 + 100101 + 1101101 ------------------------------------------------------------------------------------101000000 1010011 11011111 0011010 000010 (c) 11000100 (d) 1110010 11011101 101110 - 1101101 - 1100011 - 100101 ------------------------------------------------------------------------------------0000101 01111010 001001 47135 + 5125 ------------------54262 4F1A5 + B8D5 ---------------------5AA7A + 18 00010010 00010010 00010010 (c) 175214 (d) 110321 + 152405 + 56573 ---------------------------------------------347621 167114 F35B + 27E6 -------------------11B41 + 115 01110011 01110011 01110011 (d) 1B90F + C44E --------------------27D5D +79 01001111 01001111 01001111 –49 10110001 11001111 11001110 –3 10000011 11111101 11111100 –100 11100100 10011100 10011011

数字电路与数字电子技术 课后答案第二章

1.有一分立元件门电路如图P2.1 ( a )所示,歌输入端控制信号如图p2.1 ( b )所示.。请对应图( b )画出输出电压 的波形。

( a )

图P2.1

解:

2.对应图P2.2所示的电路及输入信号波形画出 、 、 、 的波形。

图P2.2 ( a )

解:

F1, F2, F3, F4为图P2.2A

(b) TTL非门的输出端不能并联,应换为集电极开路门。

(c)输入端所接电阻 ,相当于”0”,使 =1,必须使 ,如取

(d)输入端所接电阻 相当于”1”,使 ,必须使 ,如取 ,相当于”0”,这时

7.电路如图P2.7 ( a ) ~ ( f )所示,已知输入信号A,B波形如图P2.7 ( g )所示,试画出各个电路输入电压波形。

(b)

可用于TTL门电路,原因同上.

13.试说明下列各种门电路中有哪些输出端可以并联使用:

(1)具有推拉式输出端的TTL门电路;

(2) TTL电路的OC门;

(3) TTL电路的三态门;

(4)普通的CMOS门;

(5)漏极开路的CMOS门;

(6) CMOS电路的三态门.

解:

(1)具有推拉式输出端的TTL门电路输出端不能并联,否则在一个门截止,一个门导通的情况下会形成低阻通路,损坏器件。

(b)

这种扩展输入端的方法不适用于TTL电路因为当扩展端C、D、E均为低电平时,三个二极管均截止,或非门的一个对应输入端通过100K 电阻接地,此时 ,将输入信号A,B封锁,电路工作不正常。

12.试分析图P2.12(a),(b)电路的逻辑功能,写出y的逻辑表达式,图中门电路均为CMOS门电路,本电路能否用于TTL门电路,并说明原因。

数电第二章习题

第二章一、选择题1.下列表达式中不存在竞争冒险的有 C D ; =B +A B =A B +B C =A B C +A B =A +B A D2.若在编码器中有50个编码对象,则要求输出二进制代码位数为B 位; .6 C3.一个16选一的数据选择器,其地址输入选择控制输入端有 C 个; .2 C4.下列各函数等式中无冒险现象的函数式有 D ;A.B A AC C B F ++=B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++= 5.函数C B AB C A F ++=,当变量的取值为 A C D 时,将出现冒险现象; =C =1 =C =0 C.A =1,C =0 =0,B =06.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A ;A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 017.一个8选一数据选择器的数据输入端有 E 个; .2 C8.在下列逻辑电路中,不是组合逻辑电路的有 D ;A.译码器B.编码器C.全加器D.寄存器 9.八路数据分配器,其地址输入端有 C 个; .2 C 10.组合逻辑电路消除竞争冒险的方法有 A B ;A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰11.101键盘的编码器输出 C 位二进制代码; .6 C12.用三线-八线译码器74L S 138实现原码输出的8路数据分配器,应 A B C ;A.A ST =1,B ST =D ,C ST =0B. A ST =1,B ST =D ,C ST =DC.A ST =1,B ST =0,C ST =DD. A ST =D ,B ST =0,C ST =013.以下电路中,加以适当辅助门电路, A B 适于实现单输出组合逻辑电路;A.二进制译码器B.数据选择器C.数值比较器D.七段显示译码器14.用四选一数据选择器实现函数Y =0101A A A A +,应使 A ; =D 2=0,D 1=D 3=1 =D 2=1,D 1=D 3=0 =D 1=0,D 2=D 3=1 =D 1=1,D 2=D 3=015.用三线-八线译码器74L S 138和辅助门电路实现逻辑函数Y =122A A A +,应 B ;A.用与非门,Y =765410Y Y Y Y Y YB.用与门,Y =32Y YC.用或门,Y =32Y Y +D.用或门,Y =765410Y Y Y Y Y Y +++++16.编码电路和译码电路中, B电路的输入是二进制代码A.编码B.译码C.编码和译码 17.组合逻辑电路输出状态的改变 AA.仅与该时刻输入信号的状态有关B.仅与时序电路的原状态有关C.与A 、B 皆有关位输入的二进制编码器,其输出端有 C 位 A. 256 B. 128 C. 4 D. 3 19.对于四位二进制译码器,其相应的输出端共有 B个B. 16个C. 8个D. 10个20.在下列逻辑电路中,不是组合逻辑电路的有 DA.译码器B.编码器C.全加器 D .寄存器22.对于输出低电平有效的2—4线译码器来说要实现,Y=A B AB ''+的功能,应外加 D A.或门 B.与门 C.或非门 D.与非门 23.两片8-3线优先编码器74148可扩展成 A 线优先编码器; A. 16-4 B. 10-5 C. 16-8 D. 10-8 24.两片3-8线译码器74138可扩展成 A 线译码器; A. 4-16 B. 5-10 C. 8-16线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出70~Y Y ''=C A.B.C.D.26.对于三位二进制译码器,其相应的输出端共有 C个B. 16个C. 8个D. 10个线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=110时,输出70~Y Y ''=B A.B.C.D.28.具有3条地址输入线的选择器含B 条数据输入线;29.八选一数据选择器74LS151的地址线为011时,输出Y= CC. 3DD. 5D位半加器的输入和输出分别为B A. ,,A B CI 和,S COB. ,A B 和SC. ,A B 和,S CO31.半加器的求和的逻辑关系是DA.与非B.或非C.与或非D.异或32.优先编码器74LS148输入为—,输出为 、、;当使能输入,,时,输出应为 A33.在下列逻辑电路中,不是组合逻辑电路的有 C A.译码器B.数据选择器C.计数器D.数值比较器34. 能起到多路开关作用的是 CA.编码器B.译码器C.数据选择器D.数值比较器35. 能实现对一系列高低电平编成对应的二值代码的器件是A A.编码器 B.译码器 C.加法器 D.数据选择器36. 能实现将输入的二进制代码转换成对应的高低电平输出信号的是 B A.编码器 B.译码器 C.数据选择器 D.数值比较器38. 用3-8译码器设计的组合逻辑函数变量最大数为 B.3 C39. 用8选1数据选择器可设计的组合逻辑函数变量最大数为 C.3 C40. 用4片74148可扩展成的编码器是 D 线-3线 线-4线 线-5线 线-5线 41. 用4片74138可扩展成的译码器是 D 线-8线 线-16线 线-24线 线-32线42. 编码电路和译码电路中, A电路的输出是二进制代码;A. 编码B. 译码C. 编码和译码43. B 是构成组合逻辑电路的基本单元;A. 触发器B. 门电路C. 门电路和触发器44. 下列说法错误的是 C ;A. 74HC148的输入和输出均以低电平作为有效信号;B. 74HC138的输出以低电平作为有效信号;C. 7448的输出以低电平为有效信号;45. 对于3位二进制译码器,其相应的输出端共有 B 个;A. 3B. 8C. 6D. 1047. 两个1位二进制数A 和B 相比较,可以用 A 作为A > B 的输出信号Y A>B ;A. B A 'B. B A 'C. B A ⊕D. )('⊕B A48. 两个1位二进制数A 和B 相比较,可以用 B 作为A < B 的输出信号Y A<B ;A. B A 'B. B A 'C. B A ⊕D. )('⊕B A49. 两个1位二进制数A 和B 相比较,可以用 D 作为A = B 的输出信号Y A=B ;A. B A 'B. B A 'C. B A ⊕D. )('⊕B A50. 一个4选1数据选择器的地址端有 D 个;A. 8B. 1C. 3D. 251. 在8线-3线优先编码器74HC148中,扩展端EXY '的低电平输出信号表示 A ; A. “电路工作,但无编码输入” B. “电路工作,而且有编码输入”52.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是C ;A .111 B. 010 C. 000 D. 10154.已知74LS138译码器的输入三个使能端E 1=1, E 2A = E 2B =0时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是 C ;A. B. 10111111 C. D. 56、半加器和的输出端与输入端的逻辑关系是 D A 、 与非 B 、或非 C 、 与或非 D 、异或57、 TTL 集成电路 74LS138 是3 / 8线译码器,译码器为输出低电平有效,若输入为A 2 A 1 A 0 =101 时,输出: 为B ;A . 00100000 B. C. D. 00000100 58、属于组合逻辑电路的部件是A ;A 、编码器B 、寄存器C 、触发器D 、计数器 59.以下错误的是Ba .数字比较器可以比较数字大小b .实现两个一位二进制数相加的电路叫全加器c .实现两个一位二进制数和来自低位的进位相加的电路叫全加器d .编码器可分为普通全加器和优先编码器二、判断题正确打√,错误的打×1.优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效;×2.编码与译码是互逆的过程;√3.二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路;√4.液晶显示器的优点是功耗极小、工作电压低;√5.液晶显示器可以在完全黑暗的工作环境中使用;×6.半导体数码显示器的工作电流大,约10mA 左右,因此,需要考虑电流驱动能力问题;√7.共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动;√8.数据选择器和数据分配器的功能正好相反,互为逆过程;√9.用数据选择器可实现时序逻辑电路;×10.组合逻辑电路中产生竞争冒险的主要原因是输入信号受到尖峰干扰;× 11.八路数据分配器的地址输入选择控制端有8个;×12.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码. × 13.译码器哪个输出信号有效取决于译码器的地址输入信号√14.组合逻辑电路在任意时刻的输出不仅与该时刻的输入有关,,还与电路原来的状态有关;× 15.寄存器、编码器、译存器、加法器都是组合电路逻辑部件;×三、填空题1.半导体数码显示器的内部接法有两种形式:共 阴 接法和共 阳 接法; 2.对于共阳接法的发光二极管数码显示器,应采用 低 电平驱动的七段显示译码器;3.消除竟争冒险的方法有修改逻辑设计 、 滤波电容 、 加入选通电路 4.优先编码器74L S 148输入为 —,输出为、、;当使能输入,,时,输出 应为____001_________;5、 4线-10线译码器有 4个输入端, 10 个输出端, 6个不用的状态;6、 组合电路与时序电路的主要区别:7、74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出01234567Y Y Y Y Y Y Y Y 应为 ;8、驱动共阳极七段数码管的译码器的输出电平为 低 有效;四、设计与分析题1、用四输入数据选择器实现函数本题目只作为了解,不需掌握解:用代数法求;根据逻辑表达式,其有四个输入变量A、B、C、D,而四选一数据选择器只需两位地址代码和,若选A和B作为选择器的地址输入,A =、B =,余下的项可选作数据输入用;于是将表达式进行变换,变化成每项都含有A和B原变量和反变量组成的表达式;由此可知:D0=0 D1=D D2= D3=1根据得到的表达式可画出逻辑图2、用八选一数据选择器T576实现函数F;解:由于八选一数据选择器的地址输入通道选择信号有:A2 A1 A0三个;因此将ABC三个变量做地址输入信号,而D作为数据输入;因而实现函数F的关键是根据函数式确定数据输入D0 ~D7求数据输入D0~D7可以采用代数法也可采用卡诺图来求本题采用卡诺图法来求:1.首先分别画出函数和选择器的卡诺图如图5a、b;图b为取A、B、C作地址选择画出的选择器卡诺图,当ABC由000~111变化,其相应的输出数据为D0~D7,因此反映在卡诺图上相应的方格分别填入D0~D7,其余的一个变量D可组成余函数;对照图5a和b可确定D0~D7,其方法是:图b中D i对应于图a中的方格内全为1,则此D i= 1;反之,若方格内全为0,则D i= 0; 图b中D i对应于图a中的方格内有0也有1,则D i应为1格对应的输入变量的积之和此积之和式中只能含余下变量D;由此得Di为D0=0 D1=1 D2=1 D3=0 D4=1 D5=1 D6=0 D7=1其逻辑图如图6所示;3、用四选一数据选择器及门电路实现一位二进制全减运算;S i=4、如图所示为由八选一数据选择器实现的函数F; 1试写出F的表达式;2用3-8译码器74LS138及与非门实现函数F;解:12 FABCD=m0,1,2,3,5,7,8,105.写出右图所示电路输出信号Y的逻辑表达式,并说明其功能; 7分6.用8选1数据选择器74HC151产生逻辑函数Z=A C′ D+A′ B′ C D+BC+BC′ D′7分7分7.用译码器74LS138实现逻辑函数FA,B,C=(1,2,3,5,6)m9.试设计一个监视交通信号灯工作状态,逻辑电路正常工作时,任何时刻必须有一盏灯亮,而其它点亮状态时,电路发生故障,这时要求能发出故障信号,要求采用四选一数据选择器74153来实现信号灯为红R、黄A、绿G7分10.设输入变量A、B、C、D,输出为F;当A、B、C、D有三个或三个以上为1时,输出为1,输入为其它状态时,输出为0;试用与非门设计四变量的多数表决电路;7分11.设8421BCD码对应的十进制数为X,当X ≤2,或≥7时电路输出F为高电平,否则为低电平;试设计该电路,并用与非门实现之;1列出真值表; 2试写出输出信号的逻辑表达式; 3画出逻辑电路图;7分12.试用8选1数据选择器74LS151产生逻辑函数Y=AB+BC+AC,写出分析过程,画出逻辑电路图;7分13.分析组合逻辑电路功能图中门电路为与非门;7分1输出逻辑函数式;2真值表;3功能判断;14. 设计一个判断输入的3位代码能否被3整除的电路,用译码器74138实现,可适当加门电路;7分1逻辑抽象及真值表;2逻辑函数式;3形式变换;4逻辑电路图;15. 设计一个3人表决电路,A具有一票否决权,用2输入端四或非门7402实现;7分1逻辑抽象及真值表;2逻辑函数式;3形式变换;4逻辑电路图;16. 设计一个判断输入的4位代码能否被3整除的电路,用译码器74151实现;7分1逻辑抽象及真值表;2逻辑函数式;3形式变换;4逻辑电路图;17. 分析下图电路,写出输出Z 的逻辑函数式;74HC151为8选1数据选择器,输出的逻辑函数式为+''+'+''+''+'''=)()()()()(01240123012201210120A A A D A A A D A A A D A A A D A A A D Y )()()(012701260125A A A D A A A D A A A D +'+';18. 试画出用3线-8线译码器74HC138和门电路产生如下多输出逻辑函数的逻辑图;⎩⎨⎧'+''==CAB C B Y AC Y 2119. 试用4选1数据选择器74HC153产生逻辑函数BC C A C B A Y +''+''=;20. 试用8选1数据选择器74HC151产生逻辑函数C B A C B A AC Y ''+''+=;21.试用3线—8线译码器74LS138和门电路实现下列函数;8分ZA 、B 、C=AB+A C解:Z A 、B 、C =AB +A C =ABC +C +A CB +B=ABC +AB C +A BC +A B C = m1+ m3+ m6+ m7=7 6 3 1 m m m m •••22、用如图所示的8选1数据选择器74LS151实现下列函数;8分 YA,B,C,D=Σm1,5,6,7,9,11,12,13,14ST AY 7 Y 5Y 6Y 4 Y 3 Y 2 Y 1 Y 0 ST CST B A 0A 1 A 274LS138 ST AY 7Y 5Y 6Y 4 Y 3Y 2Y 1 Y 0 ST CST BA 0A 1 A 2 74LS138 CB A“1”&Z解:23.有一水箱,由大、小两台水泵M L 和M S 供水,如图所示;水箱中设置了3个水位检测元件A 、B 、C;水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平;现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作;试用74LS138加上适当的逻辑门电路控制两台水泵的运行;74LS138的逻辑功能表输 入输 出S 1 32S SA 2 A 1 A 0 0Y 1Y 2Y 3Y 4Y 5Y 6Y 7Y0 X X X X 1 1 1 1 1 1 1 1 X 1 X X X 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 01 1 11 1 1 1 1 1 1 01. 解:1输入A 、B 、C 按题中设定,并设输出M L =1时,开小水泵 M L =0时,关小水泵 M S =1时,开大水泵 M S =1时,关大水泵; 2根据题意列出真值表:A B C M L M S 0 0 0 0 0 0 0 1 0 1 0 1 0 × × 0 1 1 1 0 1 0 0 × × 1 0 1 × × 1 1 0 × × 111113由真值表化简整理得到:ABC C AB BC A C B A B M L +++==76327632m m m m m m m m M L •••=+++=C B A ABC C AB C B A C B A C B A M S ++++=+=7654176541m m m m m m m m m m M S ••••=++++=4令A=A,B=B,C=C,画出电路图:1“0101” “1111” “1111” 2“0110”时复位24.分析如下74LS153数据选择器构成电路的输出逻辑函数式;4分解:A AB B A F =+=25.试用图示3线-8线译码器74LS138和必要的门电路产生如下多输出逻辑函数;要求:1写出表达式的转换过程6分;2在给定的逻辑符号图上完成最终电路图;6分⎪⎩⎪⎨⎧+=++=+=C B A C B Y BC C B A C B A Y BC AC Y 321 解:FA BYD 0 D 1 D 2 D 3A 1 A 0 5403743127531m m m Y m m m m Y m m m Y ••=•••=••=。

数电 第二章习题答案

第二章2.1解:Vv v V V v T I m A I m A V v T V v a o B o B BS B o B 10T 3.0~0(2.017.0230103.0207.101.57.05I V 5v 1021.5201.510V 0v )(i i ≈≈∴<=⨯≈=-≈∴-=⨯+-=截止,负值,悬空时,都行)饱和-=时,=当截止时,=当都行)=饱和,,-=悬空时,都行)饱和。

-=时,=当=截止为负值时,=当V V v I m A I m A V V v T I m A I m A Vv T v b o B BS B o B BS B o B 3.0~0(2.0T 05.008.0187.87.47.05I 3.0~0(2.005.0250542.0187.87547.05I V 5v 5V 0v )(i i ∴<==-≈∴<=⨯≈=-∴2.3解:s 闭合时,输入低电平,此时ΩΩ=='≤≤'⨯=20020024.054.04.05222的最大允许值为R mA V I R V I R V IL IL ILs 断开时,输入为高电平,此时212121R K 10101.015445)(-最大允许值为R K mAV I V V R R VI R R V V IH cc IH cc IH ∴Ω==-≤+≥⨯+-=2.4解:2002.04.0I (max)I N 204.08I (max)I N OH OL ====IH M IL M G G =系数输出为高电平时,扇出=系数输出为低电平时,扇出所以,N =202.5解:为输入端的个数)分母中的=系数输出为高电平时,扇出=系数输出为低电平时,扇出2(504.024.02I (max)I N 106.116I (max)I N OH OL =⨯===IH M IL M G G 所以,N =52.6解:由于TTL 型或非门输入结构不同,每个输入端都有一个三极管个相同的或非门最多能驱动==高低5504.024.02I (max)I N 56.12162I (max)I N OH OL ∴=⨯==⨯=IH IL2.7解:根据公式:KR K K I m I V V R K mI nI V V R L IL LM OL cc L IH OH OH cc L 568.068.04.0384.05502.031.032.35(min)(max)<<∴≈⨯--='--==⨯+⨯-=+-=2.8解:K R I R R V V R V V V LM BE OL cc IH I 1.11.00I T 1321B ≥⇒≤+---=同时要满足=必须满足截止条件:时,当 K R K KR I I I R I V V R V V I I I I I m A R m A R V V BS BE OH OH cc OH B c cc I 46.41.146.443.087.0I 1I ,I I T V 0113222113133BS BS B ≤≤∴≤⇒⎪⎪⎪⎭⎪⎪⎪⎬⎫+=+=---==+=≈≥===,必须满足饱和条件:时,当β2.9解:KR K mA I I mA I R V I I I mA I mAI B c BS L c cc L R c L LM c 1.333.008.083.074.1516)1(≤≤==⇒=+-=+=⇒=⨯==可解得:同上题解法:β(2)把OC 门换成TTL 门时,若门输出为低电平时两者相同,无影响;但输出高电平时两者截然不同,OC 门向内流进(漏电流),而TTL 的电流是向外流出,I B =I RB +I OH ,I OH 为TTL 输出高电平时的输出电流。

数字电子技术基础课后习题答案第2章习题答案

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

数字电子技术基础 第02章门电路习题解

& & &

2.8

试比较TTL电路和CMOS电路的优、缺点。

解 CMOS门电路具有电路结构简单、功耗低、集成度高、抗 干扰能力强;工作速度较慢 TTL门电路工作速度快;功耗高、集成度较低、抗干扰能 力较弱

2.9 试说明下列各种门电路中哪些的输出端可以并联使用。 (1)具有推拉式输出级的TTL门电路; (2)TTL电路的OC门; (3)TTL电路的三态输出门; (4)普通的CMOS门: (5)漏极开路的CMOS门; (6)CMOS电路的三态输出门。

解:TTL输入标准值 UIH=2V (1)以基本TTL与非门为例,当输入端悬空时,T1和射极电流 iE1=0,集电极正偏,T2,T5饱和导通,相当于输入高电平情况,即 等效逻辑1 (2)uI>2V=UIH,所以为逻辑1 (3)uI>3.6V>2V=UIH,所以为逻辑1

2.4 指出图2.43中各门电路的输出是什么状态(高电平、低电平或高阻 态)。假定它们都是T1000系列的TTL门电路。 U & Y

逻辑门电路习题开关特性ttl门oc门综合mos21在图242所示各电路中当输入电压u分别为0v5v悬空时试计算输出电压u010202051102v假设成立u50751084ma1007200535maibsc10032300162mabsct饱和导通10v假设成立uuiuo2k3020k51k20k51k07v5v10va121010202051102v假设成立u50751084ma1007200535maibsc10032300162mabsct饱和导通10v假设成立uuiuo2k18k47k20k51k07v5v10vb122为什么说ttl与非门输入端在以下三种接法时在逻辑上都属于输入为0

数字电子技术第二章习题课

解 (1) Y AB BC AC AB BC AC

(2) Y ( A B)(A B )C BC ( AB A B )C B C A B C ABC

(1)

电子与信息工程学院 电子教研室

12

(2)

第2章、逻辑代数基础

题2.15用逻辑代数的基本公式和常用公式将下列逻辑函数化为最简与 或形式 (1) Y AB B A B

解:(1) F1 AD A C (2)F2 B D

电子与信息工程学院 电子教研室

6

第2章、逻辑代数基础

例1.12 用卡诺图化简下列函数为最简与或形式 (1) F1 A BC D A BCD ABC D ABCD AB CD 约束条件: A B C D A B CD A BC D A BCD AB C D 0 (2) F2 A B C D AB C D A BCD AB CD

解:Y A C A B BC A BC BC A BC

例1.11用卡诺图化简下列带有约束项函数为最简与或形式。 (1)F1 ( A, B, C, D) (2,3,6,7,8,10,12,14)

(2)F2 ( A, B, C, D) (0,1,2,3,4,6,8,9,10,1112,14) ,

F (3) 3 A B C D E

解: (1) F1 ( A B)(A B ) A B AB

(2) F2 ( A B C ) ABC ABC ABC ABC (3) F3 A B C D E A B C ( D E ) (4) F4 A B C ABC

4

第2章、逻辑代数基础

数字电子技术第2章习题解答

第2章习题解答题2-1 用真值表证明下列恒等式。

(1) ()A B C AB AC ⊕=⊕(2) ()()()()()A B A C B C A B A C ''+++=++ (3) ()0A B A B A B '⊕==⊕⊕解:将输入变量所有的取值逐一代入公式两边计算,然后将计算结果列成真值表。

如果两边的真值表相同,则等式成立。

(1)证明()A B C AB AC ⊕=⊕表JT2-1(2) 证明 ()()()()()A B A C B C A B A C ''+++=++表JT2-2(3) 证明()0A B A B A B '⊕==⊕⊕表JT2-3题2-2 证明下列逻辑等式(证明方法不限)。

(1)()()BC D D B C AD B B D '''++++=+(2) A C A B BC A C D A BC ''''''''+++=+(3) ()ABCD A B C D AB BC CD A D '''''''''+=+++ (4) ()()()A C B D B D AB BC '''+++=+解:在实际应用中,除非逻辑式很简单、而且逻辑变量数很少的情况下,一般不宜用列真值表的方法。

对多变量、复杂的逻辑等式、通常采用公式推演或公式推演与画卡诺图相结合的方法去证明。

如果有条件使用Multisim 等EDA 软件进行证明,则更简单、便捷。

(1)()()()()BC D D B C AD B BC D B C AD B BC D AB D AC D BB BC B D'''''++++=++++''''=+++++=+(2)()A C A B BC A C D A C A B BC A BC BC A BC ''''''''''''''+++=++=+=+(3)()()()()()()()()()()()AB BC CD A D AB BC CD A D A B B C C D A D A B A C BC AC AD C D ABCD A B C D '''''''''''''+++=''''''''''=++++=++++''''=+ (4)()()()()()()A C B D B D A C B BD BD A C B AB BC ''''''+++=+++=+=+题2-3已知逻辑函数Y 1和Y 2的真值表如表JT2-4(a )、(b )所示,试写出Y 1和Y 2的逻辑函数式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章一、选择题1.下列表达式中不存在竞争冒险的有 C D 。

A.Y =B +A BB.Y =A B +B CC.Y =A B C +A BD.Y =(A +B )A D2.若在编码器中有50个编码对象,则要求输出二进制代码位数为B 位。

A.5 B.6 C.10 D.503.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。

A.1 B.2 C.4 D.164.下列各函数等式中无冒险现象的函数式有 D 。

A.B A AC C B F ++=B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++= 5.函数C B AB C A F ++=,当变量的取值为 A C D 时,将出现冒险现象。

A.B =C =1 B.B =C =0 C.A =1,C =0 D.A =0,B =06.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 01 7.一个8选一数据选择器的数据输入端有 E 个。

A.1 B.2 C.3 D.4E.8 8.在下列逻辑电路中,不是组合逻辑电路的有 D 。

A.译码器 B.编码器 C.全加器 D.寄存器 9.八路数据分配器,其地址输入端有 C 个。

A.1B.2C.3D.4E.8 10.组合逻辑电路消除竞争冒险的方法有 A B 。

A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰11.101键盘的编码器输出 C 位二进制代码。

A.2 B.6 C.7 D.812.用三线-八线译码器74L S 138实现原码输出的8路数据分配器,应 A B C 。

A.A ST =1,B ST =D ,C ST =0B. A ST =1,B ST =D ,C ST =DC.A ST =1,B ST =0,C ST =DD. A ST =D ,B ST =0,C ST =013.以下电路中,加以适当辅助门电路, A B 适于实现单输出组合逻辑电路。

A.二进制译码器B.数据选择器C.数值比较器D.七段显示译码器14.用四选一数据选择器实现函数Y =0101A A A A +,应使 A 。

A.D 0=D 2=0,D 1=D 3=1 B.D 0=D 2=1,D 1=D 3=0 C.D 0=D 1=0,D 2=D 3=1 D.D 0=D 1=1,D 2=D 3=015.用三线-八线译码器74L S 138和辅助门电路实现逻辑函数Y =122A A A +,应 B 。

A.用与非门,Y =765410Y Y Y Y Y YB.用与门,Y =32Y YC.用或门,Y =32Y Y +D.用或门,Y =765410Y Y Y Y Y Y +++++16.编码电路和译码电路中,( B)电路的输入是二进制代码A.编码B.译码C.编码和译码 17.组合逻辑电路输出状态的改变( A)A.仅与该时刻输入信号的状态有关B.仅与时序电路的原状态有关C.与A 、B 皆有关18.16位输入的二进制编码器,其输出端有( C )位 A. 256 B. 128C. 4D. 319.对于四位二进制译码器,其相应的输出端共有( B )A.4个B. 16个C. 8个D. 10个20.在下列逻辑电路中,不是组合逻辑电路的有( D )A.译码器B.编码器C.全加器D.寄存器22.对于输出低电平有效的2—4线译码器来说要实现,Y=A B AB ''+的功能,应外加( D )A.或门B.与门C.或非门D.与非门23.两片8-3线优先编码器(74148)可扩展成( A )线优先编码器。

A. 16-4B. 10-5C. 16-8D. 10-824.两片3-8线译码器(74138)可扩展成( A )线译码器。

A. 4-16B. 5-10C. 8-16D.8-1025.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出70~Y Y ''=( C )26.对于三位二进制译码器,其相应的输出端共有( C ) A.4个B. 16个 C . 8个 D. 10个27.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=110时,输出70~Y Y ''=( B )28.具有3条地址输入线的选择器含(B )条数据输入线。

A.4B.8C.12D.1629.八选一数据选择器74LS151的地址线为011时,输出Y=( C ) A.0B.1C. 3DD. 5D30.1位半加器的输入和输出分别为(B )A. ,,A B CI 和,S COB. ,A B 和SC. ,A B 和,S CO31.半加器的求和的逻辑关系是(D ) A.与非B.或非C.与或非D.异或32.优先编码器74LS148输入为 — ,输出为 、、。

当使能输入, ,时,输出 应为( A )A.001B.010C.110D.01133.在下列逻辑电路中,不是组合逻辑电路的有( C )A.译码器B.数据选择器C.计数器D.数值比较器34. 能起到多路开关作用的是( C )A.编码器B.译码器C.数据选择器D.数值比较器35. 能实现对一系列高低电平编成对应的二值代码的器件是(A )A.编码器B.译码器C.加法器D.数据选择器36. 能实现将输入的二进制代码转换成对应的高低电平输出信号的是( B )A.编码器B.译码器C.数据选择器D.数值比较器38. 用3-8译码器设计的组合逻辑函数变量最大数为( B )A.2B.3C.4D.539. 用8选1数据选择器可设计的组合逻辑函数变量最大数为( C )A.2B.3C.4D.540. 用4片74148可扩展成的编码器是( D )A.8线-3线B.16线-4线C.24线-5线D.32线-5线41. 用4片74138可扩展成的译码器是( D )A.3线-8线B.4线-16线C.5线-24线D.5线-32线42. 编码电路和译码电路中,( A)电路的输出是二进制代码。

A. 编码B. 译码C. 编码和译码43. ( B )是构成组合逻辑电路的基本单元。

A. 触发器B. 门电路C. 门电路和触发器44. 下列说法错误的是( C )。

A. 74HC148的输入和输出均以低电平作为有效信号。

B. 74HC138的输出以低电平作为有效信号。

C. 7448的输出以低电平为有效信号。

45. 对于3位二进制译码器,其相应的输出端共有( B )个。

A. 3B. 8C. 6D. 1047. 两个1位二进制数A 和B 相比较,可以用( A )作为A > B 的输出信号Y (A>B )。

A.B A ' B. B A ' C. B A ⊕ D. )('⊕B A48. 两个1位二进制数A 和B 相比较,可以用( B )作为A < B 的输出信号Y (A<B )。

A.B A ' B. B A ' C. B A ⊕ D. )('⊕B A49. 两个1位二进制数A 和B 相比较,可以用( D )作为A = B 的输出信号Y (A=B )。

A.B A ' B. B A ' C. B A ⊕ D. )('⊕B A50. 一个4选1数据选择器的地址端有( D )个。

A. 8B. 1C. 3D. 251. 在8线-3线优先编码器74HC148中,扩展端EXY '的低电平输出信号表示( A )。

A. “电路工作,但无编码输入” B. “电路工作,而且有编码输入”52.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是(C )。

A .111 B. 010 C. 000 D. 10154.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( C ) 。

A. B. C. D.56、半加器和的输出端与输入端的逻辑关系是 (D ) A 、 与非 B 、或非 C 、 与或非 D 、异或57、 TTL 集成电路 74LS138 是3 / 8线译码器,译码器为输出低电平有效,若输入为A 2 A 1 A 0 =101 时,输出:为(B )。

58、属于组合逻辑电路的部件是(A )。

A 、编码器B 、寄存器C 、触发器D 、计数器 59.以下错误的是(B )a .数字比较器可以比较数字大小b .实现两个一位二进制数相加的电路叫全加器c .实现两个一位二进制数和来自低位的进位相加的电路叫全加器d .编码器可分为普通全加器和优先编码器 二、判断题(正确打√,错误的打×)1.优先编码器的编码信号是相互排斥的,不允许多个编码信号同时有效。

(× )2.编码与译码是互逆的过程。

(√ )3.二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路。

(√ )4.液晶显示器的优点是功耗极小、工作电压低。

(√ )5.液晶显示器可以在完全黑暗的工作环境中使用。

(× )6.半导体数码显示器的工作电流大,约10mA 左右,因此,需要考虑电流驱动能力问题。

(√ )7.共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

(√)8.数据选择器和数据分配器的功能正好相反,互为逆过程。

(√ )9.用数据选择器可实现时序逻辑电路。

(× )10.组合逻辑电路中产生竞争冒险的主要原因是输入信号受到尖峰干扰。

(× ) 11.八路数据分配器的地址输入(选择控制)端有8个。

(× )12.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码. (× ) 13.译码器哪个输出信号有效取决于译码器的地址输入信号(√)14.组合逻辑电路在任意时刻的输出不仅与该时刻的输入有关,,还与电路原来的状态有关。

(×) 15.寄存器、编码器、译存器、加法器都是组合电路逻辑部件。

(× ) 三、 填空题1.半导体数码显示器的内部接法有两种形式:共 阴 接法和共 阳 接法。

2.对于共阳接法的发光二极管数码显示器,应采用 低 电平驱动的七段显示译码器。

3.消除竟争冒险的方法有修改逻辑设计 、 滤波电容 、 加入选通电路 4.优先编码器74L S 148输入为 —,输出为、、。