EDA程序设计及仿真

电子技术与EDA技术实验及仿真课程设计

电子技术与EDA技术实验及仿真课程设计1、课程设计的背景电子科学技术是当今世界上最重要、最快速发展的学科之一,它在现代化建设和国防现代化中具有战略地位。

EDA技术是电子设计自动化技术的简称,它与电子技术在现代化建设中密切相关。

作为电子科学技术的一部分,EDA技术是电子设计和制造的关键技术之一。

本课程设计旨在将电子技术与EDA技术进行结合,设计出一套完整的课程,让学生通过实验和仿真,深入了解电子技术和EDA技术的核心知识、工具和方法,并能够应用它们进行电子设计和制造。

2、课程设计内容2.1 课程设计目标本课程设计旨在培养学生以下能力:•掌握电子技术基础知识,包括电路、器件、信号处理和通信等方面;•熟悉EDA工具,掌握EDA技术的基础知识,并且能够使用EDA技术进行电路设计和仿真;•具备独立完成电子设计和制造的能力,掌握最新的电子设计和制造技术。

2.2 课程设计内容本课程设计包括以下三部分内容:2.2.1 电子技术基础电子技术基础包括以下内容:•电路基础知识,包括电路元件、电路定理、电路分析方法、二极管、三极管等;•信号处理,包括信号采集、信号处理、信噪比等;•通信原理,包括调制原理、解调原理、通信链路等。

2.2.2 EDA技术基础EDA技术基础包括以下内容:•EDA技术概述,包括EDA技术的基本概念、EDA工具的分类和应用领域等;•EDA工具基础,包括电路仿真工具、PCB设计工具、原理图编辑工具等;•EDA技术应用案例,包括EDA技术在电路设计与仿真、芯片设计与验证、PCB设计与制造、嵌入式软硬设计等方面的应用案例。

2.2.3 实验与仿真实验与仿真是本课程设计的核心部分,实验与仿真内容包括以下几个方面:•电路实验,包括基础电路实验、信号处理实验、通信实验等;•EDA工具实验,包括电路仿真实验、原理图设计实验、PCB设计实验等;•项目实验,将上述实验内容有机结合起来,进行项目式实验,让学生在实践中掌握电子设计和制造的全流程。

集成电路EDA与验证技术课件:模拟集成电路设计与仿真

模拟集成电路设计与仿真

常用命令格式: (1) DEFINE 格式:DEFINE <库名> <库路径> 例: DEFINE sample /export/cadence/IC615USER5/tools.lnx86/dfII/samples/cdslib/sa mple (2) INCLUDE 格式:INCLUDE <另外一个cds.lib 的全路径>

模拟集成电路设计与仿真

图3.2 Spectre中包含的各种仿真器

模拟集成电路设计与仿真

2.精确的晶体管模型 Spectre为所有的仿真器提供一致的器件模型,这有利于 消除不同模型间的相关性,从而得到快速收敛的仿真结果。 模型的一致性也保证了器件模型在升级时可以同时应用于所 有的仿真器。 3.高效的程序语言和网表支持 Spectre仿真平台支持多种设计提取方法,并兼容绝大多 数SPICE输入平台。Spectre可以读取Spectre、SPICE以及 Verilog-A格式的器件模型,并支持标准的Verilog-AMS、 VHDL-AMS、Verilog-A、Verilog以及VHDL格式的文本输 入。

模拟集成电路设计与仿真

5.有力衔接了版图设计平台 对于完整的版图设计平台而言,Spectre是不可或缺的重 要环节,它能方便地利用提取的寄生元件参数来快速完成后 仿真(post-layout simulation)的模拟,并与前仿真(pre-layout simulation)的模拟结果作比较,紧密的连接了电路 (Schematic)和版图(layout)的设计。 6.交互的仿真模式 设计者可以在仿真过程中快速改变参数,并在不断调整 参数和模拟之中找到最佳的电路设计结果,减少电路设计者 模拟所花费的时间。

EDA技术-VHDL-四选一数据选择器程序设计与仿真实验

EDA技术-VHDL-四选⼀数据选择器程序设计与仿真实验四选⼀数据选择器程序设计与仿真实验1 实验⽬的(1) 熟悉在QuartusⅡ软件平台上建⽴⼯作库⽂件和编辑设计⽂件的⽅法。

(2) 熟悉创建⼯程⽂件⽅法。

(3) 熟悉编译前设置和启动全程编译设置的⽅法。

(4) 熟悉波形编辑器的使⽤⽅法(5) 熟悉在QuartusⅡ软件平台上对设计进⾏仿真的操作全过程(6) 会⽤VHDL语⾔设计⼀个四选⼀数据选择器。

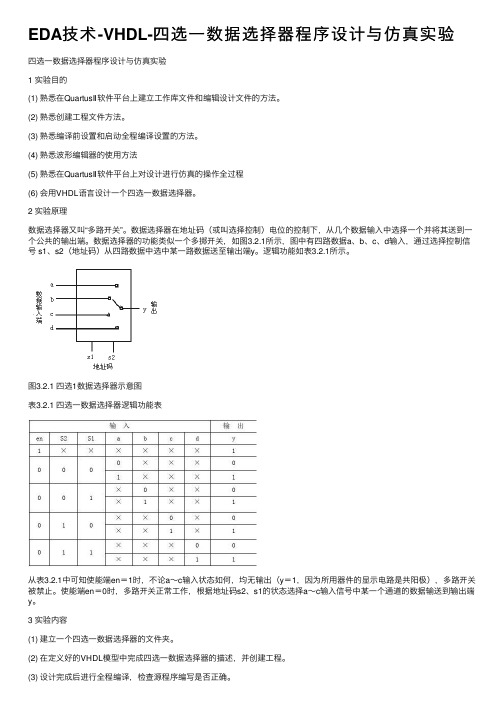

2 实验原理数据选择器⼜叫“多路开关”。

数据选择器在地址码(或叫选择控制)电位的控制下,从⼏个数据输⼊中选择⼀个并将其送到⼀个公共的输出端。

数据选择器的功能类似⼀个多掷开关,如图3.2.1所⽰,图中有四路数据a、b、c、d输⼊,通过选择控制信号 s1、s2(地址码)从四路数据中选中某⼀路数据送⾄输出端y。

逻辑功能如表3.2.1所⽰。

图3.2.1 四选1数据选择器⽰意图表3.2.1 四选⼀数据选择器逻辑功能表从表3.2.1中可知使能端en=1时,不论a~c输⼊状态如何,均⽆输出(y=1,因为所⽤器件的显⽰电路是共阳极),多路开关被禁⽌。

使能端en=0时,多路开关正常⼯作,根据地址码s2、s1的状态选择a~c输⼊信号中某⼀个通道的数据输送到输出端y。

3 实验内容(1) 建⽴⼀个四选⼀数据选择器的⽂件夹。

(2) 在定义好的VHDL模型中完成四选⼀数据选择器的描述,并创建⼯程。

(3) 设计完成后进⾏全程编译,检查源程序编写是否正确。

(4) 建⽴波形编辑⽂件并对输⼊波形进⾏编辑。

(5) 启动仿真器进⾏仿真,并分析仿真结果。

4 实验预习与思考(1) 进⼀步学习在QuartusⅡ软件平台上建⽴⼯作库⽂件和编辑设计⽂件的⽅法。

(2) 进⼀步学习建⽴波形编辑器⽂件编辑输⼊波形的⽅法。

(3) VHDL语⾔的结构体在整个程序中起什么作⽤。

5 VHDL仿真实验(1)新建⼀个⽂件夹。

本例中⽂件夹名为mux。

(2)输⼊源程序,打开计算机桌⾯上图标。

EDA设计仿真与硬件描述语言课件-6-时序逻辑描述与实现

时序逻辑的时序优化方法

优化时序逻辑设计有许多技巧。通过分析数据路径和时钟网络,以及优化时 序逻辑的延迟,我们可以提高电路性能和稳定性。了解优化方法是进行高速 电路设计的关键。

ASIC中时序逻辑的实现

讲解ASIC和FPGA技术的比较,以及如何在ASIC中实现时序逻辑。深入了解ASIC的物理细节和设计 流程,以及DL作为数字电路设计和仿真语言,有着丰富的数据类型和运算符。不仅可 以方便地描述数字电路结构、逻辑和时序关系,还能方便地模拟和验证设计。

VHDL的组合逻辑描述

介绍VHDL的组合逻辑描述,包括布尔函数和选择结构等。还会讨论如何组合多个模块和信号,以 实现复杂的数字电路设计。

EDA设计仿真与硬件描述 语言课件-6-时序逻辑描 述与实现

时序逻辑在电子设计自动化和数字电路设计中扮演着重要的角色。本课程将 涵盖时序逻辑的基本概念、VHDL描述语言和实现方法。

时序逻辑的概念和原理

讲解时序逻辑定义和分类,探讨现代数字电路设计与时序逻辑设计的密切关 系,帮助您更好地理解时序逻辑原理。

VHDL的时序逻辑描述

VHDL语言支持各种强大的时序逻辑描述功能,包括触发器,计数器和寄存器等。通过深入研究这 些描述和设计方法,可以进一步优化时序逻辑设计。

时序逻辑实现的测试方法

不同的测试方法可以评估硬件电路的性能,为您提供高质量的硬件电路设计。课程还会介绍测试 过程和方法,以及在ASIC和FPGA实现时序逻辑的具体细节。

eda仿真实验报告

eda仿真实验报告EDA仿真实验报告一、引言EDA(Electronic Design Automation)是电子设计自动化的缩写,是指利用计算机技术对电子设计进行辅助、自动化的过程。

在现代电子设计中,EDA仿真是不可或缺的一环,它可以帮助工程师验证电路设计的正确性、性能和可靠性。

本篇报告将介绍我在EDA仿真实验中的经验和收获。

二、实验背景本次实验的目标是对一个数字电路进行仿真,该电路是一个4位加法器,用于将两个4位二进制数相加。

通过仿真,我们可以验证电路设计的正确性,并观察其在不同输入情况下的输出结果。

三、实验步骤1. 电路设计:首先,我们根据给定的要求和电路原理图进行电路设计。

在设计过程中,我们需要考虑电路的逻辑关系、时序要求以及输入输出端口的定义等。

2. 仿真环境搭建:接下来,我们需要选择合适的EDA仿真工具,并搭建仿真环境。

在本次实验中,我选择了Xilinx ISE Design Suite作为仿真工具,并创建了一个仿真项目。

3. 仿真测试向量生成:为了对电路进行全面的测试,我们需要生成一组合适的仿真测试向量。

这些测试向量应该覆盖了电路的所有可能输入情况,以验证电路的正确性。

4. 仿真运行:在仿真环境搭建完成后,我们可以开始进行仿真运行了。

通过加载测试向量,并观察仿真结果,我们可以判断电路在不同输入情况下的输出是否符合预期。

5. 仿真结果分析:仿真运行结束后,我们需要对仿真结果进行分析。

通过对比仿真输出和预期结果,可以判断电路设计的正确性。

如果有不符合预期的情况,我们还可以通过仿真波形分析,找出问题所在。

四、实验结果与讨论在本次实验中,我成功完成了4位加法器的仿真。

通过对比仿真输出和预期结果,我发现电路设计的正确性得到了验证。

无论是正常情况下的加法运算,还是特殊情况下的进位和溢出,电路都能够正确地输出结果。

在实验过程中,我还发现了一些有趣的现象。

例如,在输入两个相同的4位二进制数时,电路的输出结果与输入完全一致。

eda故障仿真流程

eda故障仿真流程EDA(电子设计自动化)是电子工程领域中使用计算机来辅助设计、仿真和验证电路的过程。

在EDA中,故障仿真是其中一个重要的环节,它用来检测和修复设计中可能存在的故障。

本文将详细介绍EDA故障仿真的流程。

整个EDA故障仿真流程分为以下几个步骤:1.设计准备:在进行故障仿真之前,需要准备好设计文件和测试文件。

设计文件包括原理图、电路图、布局等相关设计信息。

测试文件包括测试向量、测试模式和故障图等。

2.故障识别:故障仿真的第一步是识别可能存在的故障。

这可以通过人工分析设计文件和测试文件的方式来进行。

故障可以包括电压异常、电流溢出、时序问题等。

3.故障建模:在识别出故障后,需要将故障转化为数学模型,以便进行仿真。

这可以通过建立故障模型和故障脚本来实现。

故障模型描述了故障的性质和影响,而故障脚本则包含了每个故障的测试向量。

4.时序约束:在进行故障仿真之前,需要对设计进行时序约束。

时序约束是指在设计中设置一些限制条件,以保证电路的准确性和稳定性。

常见的时序约束包括时钟频率、时钟延迟和时序路径等。

5.仿真运行:根据建立好的故障模型和故障脚本,进行仿真运行。

仿真软件会根据给定的测试向量和故障模式进行电路仿真,并记录仿真结果。

仿真结果可以包括输出电压、电流和时序等。

6.故障检测:在仿真运行结束后,需要对仿真结果进行故障检测。

故障检测可以通过比较仿真结果和期望结果的方式来实现。

如果仿真结果和期望结果不一致,则说明存在故障。

7.故障定位:在进行故障定位之前,需要对故障进行分类和优先级排序。

故障的分类可以根据故障模型进行,而优先级排序可以根据故障的影响和严重程度进行。

故障定位可以通过检查故障的位置和原因来实现。

8.故障修复:在定位出故障的位置和原因后,需要对故障进行修复。

故障修复可以通过调整电路参数、修改电路拓扑或更换元器件等方式来实现。

修复后需要再次进行故障仿真,以验证修复的效果。

9.后仿真评估:在进行故障修复后,需要进行后仿真评估。

EDA程序及仿真

8位全加器仿真波形图8位全加器的原理图VCC a0INPUTVCC b1INPUTVCC c0INPUTVCC a1INPUTVCC b0INPUTVCC a2INPUTVCC b2INPUTVCC a3INPUTVCC b3INPUTVCC a4INPUTVCC b4INPUTVCC a5INPUTVCC b5INPUTVCC a6INPUTVCC b6INPUTVCC a7INPUTVCC b7INPUTsum0OUTPUT sum1OUTPUT sum2OUTPUT sum3OUTPUT sum4OUTPUTsum5OUTPUTsum6OUTPUTain bin cincout sumf-adderinstain bin cincout sumf-adderinst1ain bin cincout sumf-adder inst2ain bin cincout sumf-adderinst3ain bin cincout sumf-adder inst4ain bin cincout sumf-adder inst5ain bin cincout sumf-adder inst6ain bin cincout sumf-adder inst7sum7OUTPUTcourtOUTPUT100进制计数器原理图和仿真波形图VCCenbINPUT VCCclkINPUT VCCclrINPUT q[3..0]OUTPUT q[7..4]OUTPUTDUAL COUNTER2CLKA 2CLR 2CLKB1CLR 1CLKA 1CLKB1QA 1QB 1QC 1QD 2QA 2QB 2QC 2QD74390inst AND2inst1NOTinst4NOTinst5NOTinst6NOTinst7AND4inst8AND6inst9VCCq[0]q[1]q[2]q[3]q[4]q[5]q[6]q[7]coutOUTPUT PIN_93PIN_7PIN_10PIN_50PIN_49PIN_48PIN_47PIN_42PIN_41PIN_40PIN_39频率计总体电路原理图及仿真波形enb clk clrq[3..0]q[7..4]coutcnt100instclk CNT_E NLOCK CLRctrlinst1OCTAL D-FFD1D2D3D4D6D5OE N D8D7CLKQ2Q3Q5Q4Q6Q7Q8Q174374inst2BCD TO 7SE GA B RBIN D C LTNBIN OGOD OE OF OA OB OC RBON 74248inst3BCD TO 7SE GA B RBIN D C LTNBIN OGOD OE OF OA OB OC RBON 74248inst4GNDVCCL[0]L[1]L[2]L[3]L[5]L[6]H[0]H[1]H[2]H[3]H[4]H[5]H[6]q[0]q[1]q[2]q[3]q[4]q[5]q[6]q[7]VCCclkINPUT VCCF_ININPUT q[3..0]q[7..4]L[6..0]OUTPUT H[6..0]OUTPUT P IN_93L[4]7段数码显示译码器仿真波形与电路图7段数码显示译码器元件例化程序段library ieee;use ieee.std_logic_1164.all;entity kfc isport(clock0,rst0,ena0:in std_logic;led:out std_logic_vector(6 downto 0);cout0:out std_logic);end entity kfc;architecture one of kfc iscomponent cnt4bport(clk,rst,ena:in std_logic;outy:out std_logic_vector(3 downto 0);cout:out std_logic);end component;component decl7sport(a:in std_logic_vector(3 downto 0);led7s:out std_logic_vector(6 downto 0));end component;signal tmp:std_logic_vector(3 downto 0);beginu1:cnt4b port map(clk=>clock0,rst=>rst0,ena=>ena0,outy=>tmp,cout=>cout0);u2:decl7s port map(a=>tmp,led7s=>led);end architecture one;4位二进制加法计数器程序段library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt4b isport(clk,rst,ena:in std_logic;outy:out std_logic_vector(3 downto 0);cout:out std_logic);end cnt4b;architecture one of cnt4b isbeginprocess(clk,rst,ena)variable outyi:std_logic_vector(3 downto 0);beginif rst='1' then outyi:=(others=>'0');elsif clk'event and clk='1' thenif ena='1' thenif outyi<15 then outyi:=outyi+1;else outyi:=(others =>'0');end if;end if;end if;if outyi=15 then cout<='1';else cout<='0';end if;outy<=outyi;end process;end;七段译码器library ieee;use ieee.std_logic_1164.all;entity decl7s isport(a:in std_logic_vector(3 downto 0);led7s:out std_logic_vector(6 downto 0)); end;architecture one of decl7s isbeginprocess(a)begincase a iswhen "0000" =>led7s <="0111111";when "0001" =>led7s <="0000110";when "0010" =>led7s <="1011011";when "0011" =>led7s <="1001111";when "0100" =>led7s <="1100110";when "0101" =>led7s <="1101101";when "0110" =>led7s <="1111101";when "0111" =>led7s <="0000111";when "1000" =>led7s <="1111111";when "1001" =>led7s <="1101111";when "1010" =>led7s <="1110111";when "1011" =>led7s <="1111100";when "1100" =>led7s <="0111001";when "1101" =>led7s <="1011110";when "1110" =>led7s <="1111001";when "1111" =>led7s <="1110001";when others =>null;end case;end process;end;六十进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk,rst,en:in std_logic;cq:out std_logic_vector(3 downto 0);cout:out std_logic);end cnt10;architecture one of cnt10 isbeginprocess(clk,rst,en)variable cqi:std_logic_vector(3 downto 0);beginif rst='1' then cqi:=(others=>'0');elsif clk'event and clk='1' thenif en='1' thenif cqi<9 then cqi:=cqi+1;else cqi:=(others =>'0');end if;end if;end if;if cqi=9 then cout<='1';else cout<='0';end if;cq<=cqi;end process;end;cnt6 计数器程序段library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt6 isport(clk,rst,en:in std_logic;cq:out std_logic_vector(2 downto 0);cout:out std_logic);end cnt6;architecture one of cnt6 isbeginprocess(clk,rst,en)variable cqi:std_logic_vector(2 downto 0);beginif rst='1' then cqi:=(others=>'0');elsif clk'event and clk='1' thenif en='1' thenif cqi<5 then cqi:=cqi+1;else cqi:=(others =>'0');end if;end if;end if;if cqi=5 then cout<='1';else cout<='0';end if;cq<=cqi;end process;end;。

eda 故障仿真流程

EDA 故障仿真流程EDA(Electronic Design Automation)是电子设计自动化的缩写,它是指利用计算机和特定的软件工具来辅助设计和验证电子系统的过程。

在电子系统设计过程中,故障仿真是一个非常重要的环节,它可以帮助设计工程师在设计阶段就发现和解决潜在的故障问题,从而提高产品的质量和可靠性。

本文将详细描述EDA故障仿真流程的步骤和流程。

1. 确定仿真目标和需求在进行故障仿真之前,首先需要明确仿真的目标和需求。

这包括确定仿真的范围、仿真的目的、仿真的时间和资源限制等。

例如,确定仿真的目标是验证电路的功能正确性、验证电路的时序正确性、验证电路的可靠性等。

2. 收集设计数据和规格说明在进行故障仿真之前,需要收集设计数据和规格说明。

设计数据包括电路图、原理图、布局、时序约束等。

规格说明包括功能要求、时序要求、电气要求等。

收集设计数据和规格说明的目的是为了建立仿真模型和仿真测试用例。

3. 建立仿真模型在进行故障仿真之前,需要建立仿真模型。

仿真模型是电路的数学模型,它可以准确地描述电路的行为和特性。

建立仿真模型的方法有很多种,例如,使用硬件描述语言(HDL)描述电路的行为,使用电路模拟器模拟电路的特性等。

4. 生成仿真测试用例在进行故障仿真之前,需要生成仿真测试用例。

仿真测试用例是用来验证电路功能正确性和时序正确性的输入数据。

生成仿真测试用例的方法有很多种,例如,使用随机测试生成器生成随机输入数据,使用特定模式生成器生成特定输入数据等。

5. 进行故障仿真在进行故障仿真之前,需要准备仿真环境和仿真工具。

仿真环境包括仿真平台、仿真工具、仿真模型等。

仿真工具可以根据仿真模型和仿真测试用例来模拟电路的行为和特性。

进行故障仿真的过程是将仿真测试用例输入到仿真工具中,观察仿真结果,并根据仿真结果来分析电路的故障和问题。

6. 分析仿真结果在进行故障仿真之后,需要对仿真结果进行分析。

分析仿真结果的目的是发现电路的故障和问题,并找出解决方案。

EDA课程设计-方波-三角波电路设计与仿真

EDA课程设计-方波-三角波电路设计与仿真要设计和仿真方波和三角波电路,可以按照以下步骤进行:1. 确定方波和三角波的频率和幅度,这将决定电路的参数和元件选择。

2. 方波电路设计:- 使用一个集成运算放大器(比如LM741)作为比较器,以产生方波信号。

- 将一个稳压二极管(比如1N4148)的负端连接到非反相输入端,通过一个电阻与正反相输入端相连接,以确定阈值电压。

- 通过一个电阻和一个电容将反相输入端连接到输出端,形成反馈回路,以产生滞后效应,从而消除方波的毛刺。

- 通过调整电阻和电容的数值,可以调节方波的频率和占空比。

3. 三角波电路设计:- 使用一个集成运算放大器(比如LM741)作为积分器,以产生三角波信号。

- 将二极管(比如1N4148)的阳极连接到反相输入端,通过一个电阻和一个电容将反相输入端与输出端相连接,形成积分回路。

- 通过调整电阻和电容的数值,可以调节三角波的频率和幅度。

4. 进行仿真:- 使用电路设计软件(比如LTspice)进行电路仿真,根据电路参数和元件数值,进行波形和频谱分析。

- 调整参数进行迭代,直到获得满意的仿真结果。

5. 调整电路参数和元件数值:- 可以通过改变电阻和电容的数值,来调节方波和三角波的频率和幅度。

- 可以试验不同的运放和二极管,以获得更好的性能和稳定性。

注意事项:- 在设计电路时,要注意电源的稳定性和电压范围。

- 要注意电路中的信号幅度和电压级别,以避免损坏运放器和其他元件。

- 注意电容器的极性,确保正确连接,避免损坏元件或引起电路故障。

- 在进行仿真和实验过程中,始终注意安全,并使用适当的工具和设备。

EDA仿真程序设计

EDA仿真程序设计数字时钟班级姓名学号一设计思想设计首先分三部分,首先对原始信号进行分频,输出我们所需要的时钟信号;第二部分是完成计时功能,第三部分是完成在多位数码管上进行显示的功能。

●利用分频程序将原始50MHz的时钟信号分别分为计时所需的1Hz信号和扫描显示所需的500Hz信号。

●在计时进程中,后利用加法计数器进行计时,利用时钟信号上升沿进行进位。

●在显示部分主要分为两个阶段,第一是在7段共阴极数码管上分别显示出0~9这十个数,第二是在8位扫描数码显示中实现位选。

这两个进程主要利用的均是case语句。

在进行完程序之后,在QuartusⅡ上进行验证仿真,后链接硬件下载程序进行实现。

二程序流程三主体程序介绍1分频器(原始时钟频率clk为50MHz)⑴计时分频:1Hz的clk1时钟信号process(clk)variable cnt1:integer range 0 to 49999999;beginif clk'event and clk='1' thenif cnt1=49999999 then cnt1:=0; clk1<='1';else cnt1:=cnt1+1; clk1<='0';--利用加法计数器,将周期扩大50M,频率缩小1/50M⑵显示扫描分频: 500Hz的clk2时钟信号process(clk)variable cnt2:integer range 0 to 99999;beginif clk'event and clk='1' thenif cnt2=99999 then cnt2:=0; clk2<='1';else cnt2:=cnt2+1; clk2<='0';--同理,周期扩大100000倍,频率缩小1/1000002计时程序⑴秒计时个位:process(clk1,rst)beginif rst='1' then sec1<="0000";elsif clk1'event and clk1='1' thenif sec1<"1001" thensec1<=sec1 + 1 ; s1<='0';else sec1<="0000";s1<='1';--利用计数器计时,计时时钟上升沿清零,二者共同作用创造新的计时时钟s1上升沿进位十位:process(s1,rst)beginif rst='1' then sec2<="0000";elsif s1'event and s1='1' thenif sec2<"0101" then sec2<=sec2 + 1 ;else sec2<="0000" ;--计时阶段与个位相同,只不过计时时钟变成了s1if clk1'event and clk1='1' thenif sec1=9 and sec2=5 then s2<='1';else s2<='0';--向分钟进位时只需将59s的情况单独定义即可⑵分钟计时与秒计时的程序一致。

EDA实验-- 译码器与编码器的设计与仿真

实验三译码器与编码器的设计与仿真一、实验目的:熟悉Quartus软件的基本操作,掌握用Quartus软件验证VHDL语言。

熟悉译码器与编码器所实现功能及其应用,通过实验堆译码器与编码器有更深刻理解。

一、实验内容:1.参照芯片74LS138的电路结构,用逻辑图和VHDL语言设计3-8译码器;2.参照芯片74LS148的电路结构,用逻辑图和VHDL语言设计8-3优先编码器。

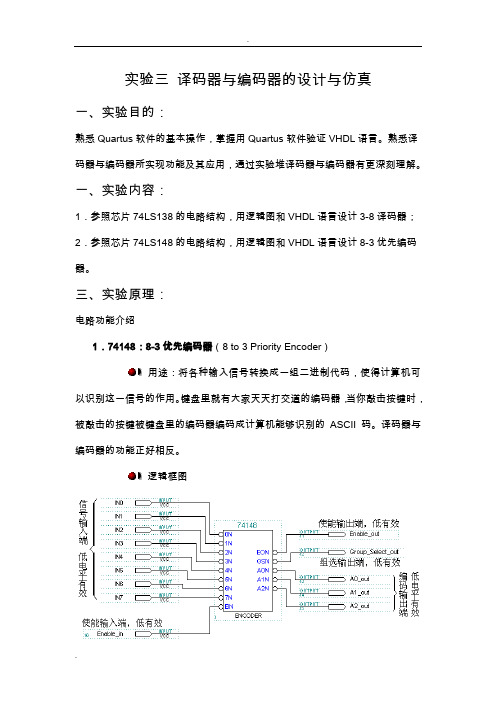

三、实验原理:电路功能介绍1.74148:8-3优先编码器(8 to 3 Priority Encoder)用途:将各种输入信号转换成一组二进制代码,使得计算机可以识别这一信号的作用。

键盘里就有大家天天打交道的编码器,当你敲击按键时,被敲击的按键被键盘里的编码器编码成计算机能够识别的ASCII码。

译码器与编码器的功能正好相反。

逻辑框图逻辑功能表逻辑表达式和逻辑图:由你来完成。

2.74138:3-8译码器(3 to 8 Demultiplexer),也叫3-8解码器用途:用一组二进制代码来产生各种独立的输出信号,这种输出信号可以用来执行不同的工作。

显示器中的像素点受到译码器的输出控制。

逻辑框图:用逻辑符号(Symbol)来解释该电路输入与输出信号之间的逻辑关系,既省事又直观。

如下图所示。

逻辑功能表:用真值表来定量描述该电路的逻辑功能。

这个表是设计3-8译码器的关键;74138的逻辑功能表如下:注:使能端G1是高电平有效;使能端G2是低电平有效,G2 = G2A AND G2B 。

代码输入端解码信号输出端低电平有效使能输入端四、实验步骤:1、译码器:(1)在Quartus软件中输入以下程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity lbz3 isport (A : in std_logic_vector(2 downto 0); Y : out std_logic_vector(7 downto 0)); end lbz3;architecture art of lbz3 isbeginY<="10000000" when(A="111")else "01000000" when(A="110")else"00100000" when(A="101")else"00010000" when(A="100")else"00001000" when(A="011")else"00000100" when(A="010")else"00000010" when(A="001")else"00000001";end art;在Quartus中对程序进行编译如下所示:从编译界面可以看到程序运行无错误;通过“RTL viewer”按钮生成综合电路图如下:(2)根据综合电路图生成如下功能仿真波形:如仿真图可以看出当A=“001”时Y=“00000010”,同理当A取其他值时Y也输出相应的值,满足译码器逻辑功能表。

EDA实验五六程序及仿真波形

1.8位数码扫描显示电路,显示输出数据直接在程序中给出LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SCAN_LED ISPORT ( CLK : IN STD_LOGIC;SG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0); --段控制信号输出BT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );--位控制信号输出END;ARCHITECTURE one OF SCAN_LED ISSIGNAL CNT8 : STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL A: INTEGER RANGE 0 TO 15;BEGINP1:PROCESS(CNT8 )BEGINCASE CNT8 ISWHEN "000" => BT <= "00000001" ;A <= 1 ;WHEN "001" => BT <= "00000010" ;A <= 3 ;WHEN "010" => BT <= "00000100" ;A <= 5 ;WHEN "011" => BT <= "00001000" ;A <= 7 ;WHEN "100" => BT <= "00010000" ;A <= 9 ;WHEN "101" => BT <= "00100000" ;A <= 11 ;WHEN "110" => BT <= "01000000" ;A <= 13 ;WHEN "111" => BT <= "10000000" ;A <= 15 ;WHEN OTHERS => NULL ;END CASE ;END PROCESS P1;P2:PROCESS(CLK)BEGINIF CLK'EVENT AND CLK = '1' THEN CNT8 <= CNT8 + 1;END IF;END PROCESS P2 ;P3:PROCESS(A)--译码电路BEGINCASE A ISWHEN 0 => SG <= "0111111";WHEN 1 => SG <= "0000110";WHEN 2 => SG <= "1011011";WHEN 3 => SG <= "1001111";WHEN 4 => SG <= "1100110";WHEN 5 => SG <= "1101101";WHEN 6 => SG <= "1111101";WHEN 7 => SG <= "0000111";WHEN 8 => SG <= "1111111";WHEN 9 => SG <= "1101111";WHEN 10 => SG <= "1110111";WHEN 11 => SG <= "1111100";WHEN 12 => SG <= "0111001";WHEN 13 => SG <= "1011110";WHEN 14 => SG <= "1111001";WHEN 15 => SG <= "1110001";WHEN OTHERS => NULL ;END CASE ;END PROCESS P3;END;仿真波形2.8位数码扫描显示电路,外部输入8个待显示的十六进制数library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity show2 isport(clk,load,en:in std_logic;din:in std_logic_vector(3 downto 0);led7s:out std_logic_vector(6 downto 0);bits:out std_logic_vector(7 downto 0));end entity show2;architecture behav of show2 issignal cnt:integer range 0 to 7;signal tmp,d1,d2,d3,d4,d5,d6,d7,d8:std_logic_vector(3 downto 0); beginp_zz:process(load)variable cn:std_logic_vector(2 downto 0);beginif load='1' and load'event thencase cn iswhen "000" => d1<=din;when "001" => d2<=din;when "010" => d3<=din;when "011" => d4<=din;when "100" => d5<=din;when "101" => d6<=din;when "110" => d7<=din;when "111" => d8<=din;when others=>null;end case;cn:=cn+1;end if;end process p_zz;p_js:process(clk)beginif clk'event and clk='1' thenif cnt<7 thencnt<=cnt+1;elsecnt<=0;end if;end if;end process p_js;p_xt:process(cnt,d1,d2,d3,d4,d5,d6,d7,d8,en) begincase cnt iswhen 0=>if en='1' then tmp<=d1;bits<="00000001";else bits<="00000000"; end if;when 1=>if en='1' then tmp<=d2;bits<="00000010";else bits<="00000000"; end if;when 2=>if en='1' then tmp<=d3;bits<="00000100";else bits<="00000000"; end if;when 3=>if en='1' then tmp<=d4;bits<="00001000";else bits<="00000000"; end if;when 4=>if en='1' then tmp<=d5;bits<="00010000";else bits<="00000000"; end if;when 5=>if en='1' then tmp<=d6;bits<="00100000";else bits<="00000000"; end if;when 6=>if en='1' then tmp<=d7;bits<="01000000";else bits<="00000000"; end if;when 7=>if en='1' then tmp<=d8;bits<="10000000";else bits<="00000000"; end if;when others=>null;end case;end process p_xt;p_ym:process(tmp)begincase tmp isWHEN "0000" =>LED7S <= "0111111" ;WHEN "0001" =>LED7S <= "0000110" ;WHEN "0010" =>LED7S <= "1011011" ;WHEN "0011" =>LED7S <= "1001111" ;WHEN "0100" =>LED7S <= "1100110" ;WHEN "0101" =>LED7S <= "1101101" ;WHEN "0110" =>LED7S <= "1111101" ;WHEN "0111" =>LED7S <= "0000111" ;WHEN "1000" =>LED7S <= "1111111" ;WHEN "1001" =>LED7S <= "1101111" ;WHEN "1010" =>LED7S <= "1110111" ;WHEN "1011" =>LED7S <= "1111100" ;WHEN "1100" =>LED7S <= "0111001" ;WHEN "1101" =>LED7S <= "1011110" ;WHEN "1110" =>LED7S <= "1111001" ;WHEN "1111" =>LED7S <= "1110001" ;WHEN OTHERS =>NULL ;end case;end process p_ym;end architecture behav;波形仿真LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DVF ISPORT ( CLK : IN STD_LOGIC;D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);FOUT : OUT STD_LOGIC);END;ARCHITECTURE one OF DVF ISSIGNAL FULL : STD_LOGIC;BEGINP_REG : PROCESS (CLK)V ARIABLE CNT8 : STD_LOGIC_VECTOR(7 DOWNTO 0):="11111111"; BEGINIF CLK'EVENT AND CLK = '1' THENIF CNT8 = "11111111" THENCNT8 :=D;FULL <= '1';ELSE CNT8 :=CNT8+1;FULL <='0';END IF;END IF;END PROCESS P_REG;P_DIV : PROCESS (FULL)V ARIABLE CNT2 : STD_LOGIC;BEGINIF FULL'EVENT AND FULL = '1'THENCNT2 := NOT CNT2;IF CNT2 = '1' THEN FOUT <= '1';ELSE FOUT <= '0';END IF;END IF ;END PROCESS P_DIV;END;仿真波形LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DVF16 ISPORT ( CLK : IN STD_LOGIC;D : IN STD_LOGIC_VECTOR(15 DOWNTO 0);FOUT : OUT STD_LOGIC);END;ARCHITECTURE one OF DVF16 ISSIGNAL FULL : STD_LOGIC;BEGINP_REG : PROCESS (CLK)VARIABLE CNT8 : STD_LOGIC_VECTOR(15 DOWNTO 0):="1111111111111111" ; BEGINIF CLK'EVENT AND CLK = '1' THENIF CNT8 = "1111111111111111" THENCNT8 :=D;FULL <= '1';ELSE CNT8 :=CNT8+1;FULL <='0';END IF;END IF;END PROCESS P_REG;P_DIV : PROCESS (FULL)VARIABLE CNT2 : STD_LOGIC;BEGINIF FULL'EVENT AND FULL = '1'THENCNT2 := NOT CNT2;IF CNT2 = '1' THEN FOUT <= '1';ELSE FOUT <= '0';END IF;END IF ;END PROCESS P_DIV;END;仿真波形。

eda课程设计仿真

eda课程设计仿真一、教学目标本课程的教学目标是使学生掌握EDA(电子设计自动化)的基本概念、工具和仿真方法,能够运用EDA工具进行电路设计和仿真分析。

具体分为以下三个部分:1.知识目标:学生需要了解EDA的发展历程、基本概念和常用工具;掌握电路图的绘制方法和仿真原理;了解FPGA和ASIC的设计流程。

2.技能目标:学生能够熟练使用至少一种EDA工具进行电路设计和仿真;能够独立完成简单的FPGA设计和验证。

3.情感态度价值观目标:培养学生对电子设计的兴趣,提高创新意识和团队合作能力。

二、教学内容根据教学目标,本课程的教学内容主要包括以下几个部分:1.EDA基本概念和工具:介绍EDA的定义、发展历程和常用工具,如Cadence、Altera和Xilinx等。

2.电路图绘制和仿真原理:讲解电路图的绘制方法、仿真原理和常用仿真分析方法。

3.FPGA和ASIC设计流程:介绍FPGA和ASIC的设计流程,包括需求分析、逻辑设计、物理设计和验证等。

4.实例讲解和练习:通过实际案例,讲解EDA工具的使用方法和电路设计技巧,并进行课堂练习。

三、教学方法为了达到教学目标,本课程将采用以下几种教学方法:1.讲授法:讲解EDA的基本概念、原理和设计流程。

2.案例分析法:通过分析实际案例,使学生掌握EDA工具的使用方法和电路设计技巧。

3.实验法:安排实验室实践环节,让学生亲手操作EDA工具,进行电路设计和仿真。

4.讨论法:课堂讨论,鼓励学生提问、分享心得,提高学生的积极性和主动性。

四、教学资源为了支持教学内容和教学方法的实施,本课程将准备以下教学资源:1.教材:选用权威、实用的EDA教材,如《电子设计自动化原理与应用》等。

2.参考书:提供相关的参考书籍,如《FPGA原理与应用》、《ASIC设计与验证》等。

3.多媒体资料:制作课件、教学视频等多媒体资料,以便于学生复习和自学。

4.实验设备:配备足够的实验设备,如计算机、EDA工具软件、FPGA开发板等。

EDA实验报告——比较电路设计与仿真

实验四 比较电路的设计与仿真一、实验目的设计比较电路并仿真。

二、实验内容用VHDL语言和利用LPM元件实现比较电路并仿真。

三、实验方法1)实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

2)实验步骤:一,VHDL实现1、建立新工程。

打开QuartusII软件平台,点击File中得New Peoject Wizar的建立一个工程,为此工程建议一个目录文件,并为此工程及文件命名,命名的名字须与实体名一致。

2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型,本次采用AlteraEPF10K20TI144_4。

3,为此次工程选取合适的EDA工具以及采用的合适VHDL语言。

本次实验采用Design Compiler , ModelSim_Altrea,和Custom,分别采用EDIF形式,VHDL形式,和VHDL形式4. 编写源代码。

点击File中的New,选择弹出选项框内的Design File 下的VHDL File,创建一个vhd格式文件,并输入编写的源代码。

源代码为:library IEEE;use IEEE.std_logic_1164.all;entity bijiao isport(a2,a1:in STD_LOGIC;b2,b1:in STD_LOGIC;f1,f2:buffer STD_LOGIC;f3:out STD_LOGIC);end bijiao;architecture bijiao_arch of bijiao isbeginf1<=(a2 and (not b2)) or (a1 and (not b1) and a2) or (a1 and (not b1) and (not b2));f2<=((not a2) and b2)or((not a2) and (not a1) and b1) or ((nota1) and b1 and b2);f3<=not(f1 or f2);end bijiao_arch;4、编译与调试。

基于EDA技术的程序设计和软件仿真及硬件实现

基于EDA技术的程序设计和软件仿真及硬件实现【摘要】本论文精简的说明《基于EDA技术的程序设计和软件仿真及硬件实现》这一大学生创新实践项目的设计要点,包括用MAX+plusII软件编写VHDL 程序、绘制GDF仿真电路图、实验箱上CPLD元器件中EPM7128SLC84-15合理利用,电路功能的调试等。

【关键词】EDA技术;MAX+plusII;VHDL语言;EPM7128SLC84-15引言EDA(Electronic Designed Automation)即电子设计自动化。

EDA技术指的是以计算机硬件和系统软件为基本工作平台,继承和借鉴前人在电路和系统、数据库、图形学、图论和拓扑逻辑、计算数学、优化理论等多学科的最新科技成果而研制成的商品化通用支撑软件和应用软件包。

EDA旨在帮助电子设计工程师在计算机上完成电路的功能设计、逻辑设计、性能分析、时序测试直至PCB(印刷电路板)的自动设计。

1.项目硬件和软件简述本创新实践项目采用复杂可编程逻辑器件,即CPLD(Complex Programmable Logic Device),本创新实践采用EPM7128SLC84-15芯片。

采用Altera公司的MAX+plusII软件作开发系统,编程采用VHDL(Very High Speed Integrated Circuits Hardware Description Language)语言,超高速集成电路硬件描述语言,VHDL语言作为一种硬件描述语言,可用于数字电路与系统的描述、模拟和自动设计与仿真等,是当今电子设计自动化的核心技术。

在创新实践中设计出多功能数字钟、秒表、液晶显示编程等子项目的VHDL 程序,软件仿真和硬件电路实现,最终在实验室实现各个子项目的功能。

程序编写后先进行软件仿真,在软件环境中实现仿真功能,连接硬件电路,实现功能。

2.多功能数字钟设计在多功能数字钟设计子项目中,GDF仿真电路图和VHDL程序,由时钟、控制、计时、数据译码、显示以及报时模块组成。

EDA实验4消抖电路的顶层设计和移位寄存器的功能仿真

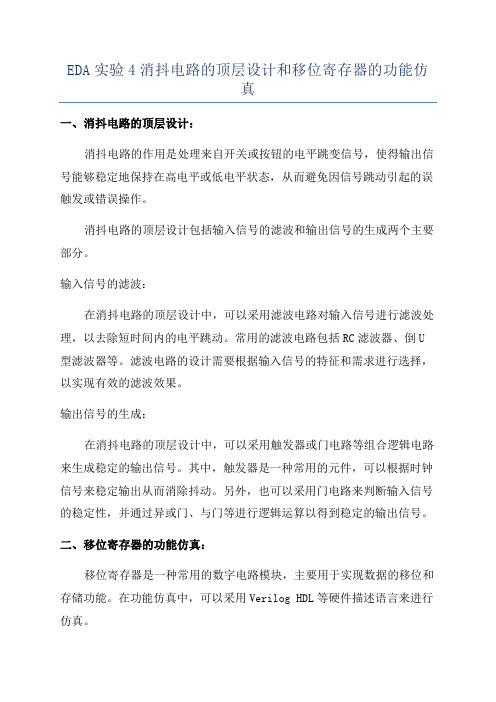

EDA实验4消抖电路的顶层设计和移位寄存器的功能仿真一、消抖电路的顶层设计:消抖电路的作用是处理来自开关或按钮的电平跳变信号,使得输出信号能够稳定地保持在高电平或低电平状态,从而避免因信号跳动引起的误触发或错误操作。

消抖电路的顶层设计包括输入信号的滤波和输出信号的生成两个主要部分。

输入信号的滤波:在消抖电路的顶层设计中,可以采用滤波电路对输入信号进行滤波处理,以去除短时间内的电平跳动。

常用的滤波电路包括RC滤波器、倒U 型滤波器等。

滤波电路的设计需要根据输入信号的特征和需求进行选择,以实现有效的滤波效果。

输出信号的生成:在消抖电路的顶层设计中,可以采用触发器或门电路等组合逻辑电路来生成稳定的输出信号。

其中,触发器是一种常用的元件,可以根据时钟信号来稳定输出从而消除抖动。

另外,也可以采用门电路来判断输入信号的稳定性,并通过异或门、与门等进行逻辑运算以得到稳定的输出信号。

二、移位寄存器的功能仿真:移位寄存器是一种常用的数字电路模块,主要用于实现数据的移位和存储功能。

在功能仿真中,可以采用Verilog HDL等硬件描述语言来进行仿真。

移位寄存器的主要功能包括数据输入、数据移位、数据输出等。

在功能仿真中,可以通过设置合适的输入数据和时钟信号,观察输出数据的变化情况,验证移位寄存器的功能是否符合设计要求。

以单向移位寄存器为例,其功能仿真的步骤如下:1.设置仿真环境:编写仿真代码,包括移位寄存器的模块声明、端口定义以及时钟信号的生成等。

2.设置输入数据:为移位寄存器的输入端设置合适的数据值,并在仿真代码中对输入进行初始化或赋值。

3.产生时钟信号:根据设计要求,为时钟信号设置合适的频率和波形,使其能够触发移位寄存器的移位操作。

4.运行仿真:根据仿真环境和输入数据,运行仿真过程。

在仿真过程中,需要记录输出端口的值,以便后续分析。

5.分析仿真结果:对仿真结果进行波形图分析,观察输出数据随时间的变化情况。

验证移位寄存器在不同输入条件下的移位和存储功能是否正确。

EDA实验 模4计数器的设计和仿真

EDA实验模4计数器的设计和仿真一、实验目的:熟练使用quartersⅡ软件,学会使用逻辑图设计模4计数器并进行仿真。

二、实验内容:用逻辑图设计模4计数器并进行仿真与分析。

三、实验方法:实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:1、绘制逻辑图。

打开QuartusII软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型。

3、编译与调试。

确定逻辑图文件为当前工程文件,点击Complier进行文件编译。

编译结果有错误或警告,则将要调试修改直至文件编译成功。

4、波形仿真及验证。

在编译成功后,点击Waveform开始设计波形。

点击“insert the node”,按照程序所述插入q[1..0],clk,任意设置各输入节点的输入波形…点击保存按钮保存。

5、时序仿真。

(具体过程,操作细节以及实验过程截图见下面具体操作,都有说明。

)6、FPGA芯片编程及验证。

(具体细节和过程看后续的实验过程的说明)四、实验过程:1、编译过程(可先绘制逻辑图再建工程,也可先建工程再建文件)a)绘制逻辑图。

打开QuartersII软件平台,点击file中的New新建一个文件。

弹出一个窗口,选择Block Diagram选项;新建文件,然后绘制实验要用到的逻辑图,双击空白处,选择要用到的器件并用适当的线把各元件连接好并进行命名,绘制的模4计数器的逻辑图如下:接着保存文件,点击File/Save as,接着建一个工程,并保存。

b)按照实验箱上FPGA的芯片名更改芯片的设置,选取芯片类型。

设置如下图所示:c)工程建好后,进行编译和调试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、二选一多路选择器

1、程序

2、RTL图

3、时序图

二、四选一多路选择器(一)四选一多路选择器A 1、程序

2、RTL图

3、时序图

(二)四选一多路选择器B 1、程序

2、RTL图

3、时序图

(三)四选一多路选择器C 1、程序

2、RTL图

3、时序图

(四)四选一多路选择器D 1、程序

2、RTL图

三、半加器(一)半加器A 1、程序

2、RTL图

(二)半加器B

1、程序

2、RTL图

(三)半加器C 1、程序

2、RTL图

四、模可控10进制计数器

1、程序

2、RTL图

3、时序图

五、异步复位十进制计数器

1、程序

2、RTL图

3、时序图

六、8位全加器

1、程序

2、RTL图

七、深入认识阻塞式赋值和非阻塞式赋值(一)阻塞式赋值

1、程序

两个程序等价

2、RTL图

3、时序图

(二)非阻塞式赋值1、程序

2、RTL图

3、时序图

八、电平触发锁存器

1、程序

2、RTL图

3、时序图

九、异步复位时钟使能触发器

1、程序

2、RTL图

3、时序图

十、同步复位时钟使能触发器

1、程序

2、RTL图

3、时序图

十一、深入理解完整条件语句和不完整条件语句(一)不完整条件语句

1、程序

2、RTL图

(二)完整条件语句

1、程序

2、RTL图

十二、同步预置功能移位寄存器1、程序

2、RTL图

3、时序图

十三、异步复位移位寄存器1、程序

2、RTL图

3、时序图

十四、8-3编码器

1、程序

2、RTL图

3、时序图

十五、三态控制电路1、程序

2、RTL图

3、时序图

十六、双向端口设计1、程序

2、RTL图

3、时序图

十七、三态总线控制电路实现4选一1、程序

2、RTL图

3、时序图

十八、四位乘法器1、程序

2、RTL图

3、时序图

十九、简单分频电路1、程序

2、RTL图

3、时序图。