DDR3内存的PCB仿真与设计

DDR3内存的PCB仿真与设计

DDR3内存的PCB仿真与设计

一、DDR3内存的PCB仿真

PCB(Printed Circuit Board,印制电路板)的设计是DDR3内存中非常重要的一步。

在进行实际制作之前,通过仿真来验证设计的正确性,可以帮助找出潜在的问题并进行优化。

1.电源噪声仿真

2.信号完整性仿真

3.时钟分布仿真

4.排布规则仿真

二、DDR3内存的PCB设计

在进行DDR3内存的PCB设计时,需要考虑以下几个方面。

1.布局设计

2.分层设计

3.时钟优化

4.信号完整性优化

5.地平面设计

良好的地平面设计可以提供稳定的地连接,减小噪声干扰。

需要合理规划地平面的宽度和连接方式,并与信号平面分层设计相结合。

总之,DDR3内存的PCB仿真和设计是提高DDR3内存性能和稳定性的重要手段。

通过仿真和设计的过程,可以找出潜在的问题并进行优化,提

高DDR3内存的性能和可靠性。

对DDR3内存的PCB设计要仔细考虑布局、分层、时钟优化、信号完整性优化和地平面设计等方面,以确保DDR3内存的正常运行。

基于DDR3的PCB设计及仿真

: l 并且数据传输 率一再被提升 在这种 情况下 , 对P C B设 计都提 出了更高的要 求, 同时也增加 了 1 ) ( I j 设计需要 考虑 的参数 随

Z 之 出现 的 存 储 器 的仿 真技 术 , 通 过 对 影 响 信 号 质 量 的 关键 因素 的 分 析 , 实 现 对 信 号 完 整性 的 仿 真 分 析 , 从而 节省 了 P CB设 计

2仿 真 分 析

i f ; , J f E! , } J l Y , H b r 4 欠 r } ‘ ( - i l l [ t l n l — S I , m・ f l f / 『 o . , _ 弛 嚣 T e k 1 ) S A 7 3 3 ( ) 4 1 ) . 1 ) I ) R 敬 州 尘 、 I 1 ) 6 0 M -  ̄ - ) c ,

1引言

啦 l 1 _ J ) 9 z = I I I I I i r g . G : { n坐 越 米 越 帙 , 对 行 器 的 数据 f 々 输能 J j ‘ 水 l 越 沫迷r ,他 i 越 越 , 逑 电路 板 I { 的! 连 乐 变僻

基 于 DDR3的 P C B 设 计 及 仿 真

牛 宾, 史黎 黎 ( 中华通 信 系统有 限责任公 司 河北 分公 司 , 河北 石 家庄 l l 5 … I )

H

【 摘 要] 随 ̄ - - H - 算机技 术的快速 发展 , 高速 存储 器技 术 已得到 广泛 应用 , 目前 市场 上主流 应用的 内存 为 1 ) 1 ) 1 3存储 器,

时 间 及 开 发 成本

n

【 关键 词】 I ) I ) R3 ; 仿真; P CB ; 高 速 传输

a

ddr3电路设计

ddr3电路设计DDR3是一种流行的内存标准,广泛应用于计算机的内存子系统中。

DDR3电路设计的关键在于确保数据传输的精确性和速度。

本文将讨论DDR3电路设计的主要方面。

首先,DDR3的电路设计必须考虑时序。

DDR3采用双倍速时钟,并使用复杂的电路实现内部时序要求。

因此,在设计DDR3电路时,需要掌握时钟源和时序分析工具,以确保电路能够在正确的时序下运行。

同时,要特别注意时序与接口匹配,特别注意输入和输出以及速度的匹配。

其次,电源稳定性也是DDR3电路设计的一个重要方面。

DDR3的工作电压为1.5V,内部时序比较严格。

如果电源不稳定,会导致内部时序失调和数据传输的不稳定。

因此,在设计DDR3电路时,需要考虑使用高品质的电源和稳压控制电路,以确保系统的电源稳定性。

第三,DDR3电路设计必须考虑阻抗匹配。

DDR3内部线路的阻抗要求非常高,以确保数据信号传输的正确性。

因此,在DDR3电路设计中,设计师必须确保阻抗匹配,包括内部线路阻抗和外部元件阻抗匹配。

通过使用高品质的PCB材料和布线方式,可以实现更好的阻抗匹配。

最后,DDR3电路设计必须考虑EMI(电磁干扰)和ESD(静电放电)等问题。

DDR3的高速数据传输和内部时序要求使其在EMI和ESD方面非常敏感。

在DDR3电路设计中,需要考虑EMI和ESD的电磁干扰特性,采用合适的滤波和抑制措施,例如使用布局合理的地和电源平面,以及使用EMI滤波器等。

总之,DDR3电路设计是一项复杂的工作,需要掌握时序、电源、阻抗、EMI和ESD等方面的知识。

采用高品质的元件、PCB材料和布线方式,可以最大限度地提高DDR3电路的精确性和速度。

DDR2与DDR3信号完整性及PCB设计

Signal Integrity and PCB layout considerations for DDR2-800 Mb/s and DDR3 MemoriesFidus Systems Inc.900, Morrison Drive, Ottawa, Ontario, K2H 8K7, CanadaChris Brennan, Cristian Tudor, Eric Schroeter, Heike Wunschmann, and Syed BokhariSession # 8.13AbstractThe paper addresses the challenge of meeting Signal Integrity (SI) and Power Integrity (PI) requirements of Printed Circuit Boards (PCBs) containing Double Data Rate 2 (DDR2) memories. The emphasis is on low layer count PCBs, typically 4-6 layers using conventional technology. Some design guidelines have been provided.1. IntroductionDDR2 usage is common today with a push towards higher speeds such as 800 Mbps [1] and more recently, 1066 Mbps. DDR3 [2] targets a data rate of 1600 Mbps. From a PCB implementation standpoint, a primary requirement is delay matching which is dictated by the timing requirement. This brings into it a number of related factors that affect waveform integrity and delay. These factors are interdependent, but where a distinction can be made, they can be termed PCB layer stackup and impedance, interconnect topologies, delay matching, cross talk, PI and timing. Cadence ALLEGRO™SI-230 and Ansoft’s HFSS™ are used in all computations.Table 1: Comparison of DDR2 and DDR3 requirementsSignals common to both technologies and a general comparison of DDR2 and DDR3 is shown in Table 1. It must be noted that “matching” includes cases where the clock net may be made longer (termed DELTA in ALLEGRO SigXP). We have assumed a configuration comprising a Controller and two SDRAMs in most illustrations that follow.2. PCB Layer stackup and impedanceIn a layer constrained implementation, a 4 layer PCB (Figure 1) is a minimum with all routing on TOP and BOTTOM layers. One of the internal layers will be a solid ground plane (GND). The other internal plane layer is dedicated to VDD. Vtt and Vref can be derived from VDD. Use of a 6-layer PCB makes the implementation of certain topologies easier. PI is also enhanced due to the reduced spacing between power and GND planes. The interconnect characteristic impedance for DDR2 implementation can be a constant. A single-ended trace characteristic impedance of 50 Ohms can be used for all single-ended signals. A differential impedance of 100 Ohms can be used for all differential signals, namely CLOCK and DQS. Further, the termination resistor pulled up to VTT can be kept at 50 Ohms and ODT settings can be kept at 50 Ohms.In the case of DDR3 however, single ended trace impedances of 40 and 60 Ohms used selectively on loaded sections of ADDR/CMD/CNTRL nets have been found to be advantageous. Further, the value of the termination resistor pulled up to Vtt needs to be optimized in combination with the trace impedance through SI simulations. Typically, it is in the range 30 – 70 Ohms. The differential trace impedance can remain at 100 Ohms.Figure 1 : Four and Six layer PCB stackup3. Interconnect TopologiesIn both cases of DDR2 and DDR3, DQ, DM and DQS signals are point-to-point and do not need any topological consideration. An exception is in the case of multi-rank Dual In Line Memory Modules (DIMMs). Waveform integrity is also easily addressed by a proper choice of drive strengths and On Die Termination (ODT). The ADDR/CMD/CNTRL signals, and sometimes the clock signal will involve a multipoint connection where a suitable topology is needed. Possible choices are indicated in Figure 2 for cases involving two SDRAMs. The Fly-By Topology is a special case of a daisy chain with a very short or no stub.For DDR3, any of these topologies will work, provided that the trace lengths are minimized. The Fly-by topology shows the best waveform integrity in terms of an increased noise margin. This can be difficult to implement on a4-layer PCB and the need for a 6-layer PCB arises. The daisy chain topology is easier to implement on a 4 layer PCB. The tree topology on the other hand requires the length of the branch AB to be very close to that of AC (Figure 2). Enforcing this requirement results in the need to increase the length of the branches which affects waveform integrity. Therefore, for DDR3 implementation, the daisy chain topology with minimized stubs proves to be best suited for 4-layer PCBs.For DDR2-800 Mbps any of these topologies are applicable with the distinction between each other being less dramatic. Again, the daisy chain proves to be superior in terms of both implementation as well as SI.Where more than two SDRAMs are present, often, the topology can be dictated by constraints on device placement. Figure 3 shows some examples where a topology could be chosen to suit a particular component placement. Of these, only A and D are best suited for 4-layer PCB implementation. Again, for DDR2-800 Mbps operations all topologies yield adequate waveform integrity. For a DDR3 implementation, in particular at 1600 Mbps, only D appears to be feasible.Vtt RtRtRtTree topology Fly-By topologyFigure 2: ADDR/CMD/CNTRL topologies with 2 SDRAMS(A)Figure 3: ADDR/CMD/CNTRL topologies with four SDRAMS4. Delay matchingImplementing matched delay is usually carried out by bending a trace in a trombone shape. Routing blockage may require layer jumping. Unfortunately, while physical interconnect lengths can be made identical in layout, electrically, the two configurations shown in Figure 4 will not be the same.The case of trombone delay has been well understood, and the case of a via is obvious. The delay of a trombone trace is smaller than the delay of a straight trace of the same center-line length. In the case of a via, the delay is more than that of a straight microstrip trace of length equal to the via length. The problem can be resolved in two different ways. In the first approach, these values can be pre-computed precisely and taken into account while delay matching. This would become a tedious exercise which could perhaps be eased with userRtRtRt(B)(C)(D)Rtdefined constraints in ALLEGRO 16.0. In the second approach, one would use means to reduce the disparity to an acceptable level.Trombone traceStraight traceL 3L 2 L 4 ≠L 1L 5Figure 4: Illustration of Trombone traces and ViasFigure 5: Circuit for estimation of trombone effect and resulting waveforms.≠Straight traceVia cross sectional viewConsider the case of a trombone trace. It is known that the disparity can be reduced by increasing the length of L3 (Figure 4). Details can be found in reference [3]. A simulation topology can be set up in SigXP to represent parallel arms of a trombone trace as coupled lines. A sweep simulation is carried out with L3 (S in Figure 5) as a variable and the largest reasonable value that reduces the delay difference with respect to a reference trace is selected. For microstrip traces, L3 > 7 times the distance of the trace to ground is needed.Delay values are affected in a trombone trace due to coupling between parallel trace segments. Another way to reduce coupling without increasing the spacing is to use a saw tooth profile. The saw tooth profile shows better performance as compared to a trombone although it eventually ends up requiring more space. In either case, it is possible to estimate the effect on delay precisely by using a modified equation for the computation of the effective trace length [3]. This would need to be implemented as a user defined constraint in ALLEGRO. Consider the case of a through hole via on the 6 layer stackup of Figure 2. Ground vias placed close to the signal vias play an important role in the delay. For the illustration, the microstrip traces on TOP and BOTTOM layers are 150 mils long, and 4 mils wide. The via barrel diameter = 8 mils, pad diameter is 18 mils and the anti-pad diameter is 26 mils.Three different cases are considered. In the first case, the interconnect with via does not have any ground vias in its immediate neighborhood. Return paths are provided at the edges of the PCB 250 mils away from the signal via. In the second case, a reference straight microstrip trace of length = 362 mils is considered. The third case is the same as case 1 with four ground vias in the neighborhood of the signal via. Computed s-parameters with 60 Ohm normalization are shown in Figure 6. It can be seen that the use of 4 ground vias surrounding the signal via makes its behavior more like a uniform impedance transmission line and improves the s21 characteristic. In the absence of a return path in the immediate neighborhood, the via impedance increases. For the present purpose, it is important to know the resulting impact on the delay.A test circuit is set up similar to Figure 5. The driver is a linear source of 60 Ohms output impedance and outputs a trapezoidal signal of rise time = fall time = 100 ps and amplitude = 1V. It is connected to each of the 3 interconnects shown in Figure 6 and the far end is terminated in a 60 Ohm load. The excitation is a periodic signal with a frequency of 800 MHz. The time difference between the driver waveform at V = 0.5 V and the waveform at the receiver gives the switched delay.Results are illustrated in Figure 7 where only the rising edge is shown. It can be seen that the delay with four neighboring ground vias differs from that of the straight trace by 3 ps. On the other hand, the difference is 8 ps for the interconnect with no ground vias in the immediate neighborhood.It is therefore clear that increasing the ground via density near signal vias will help. However, in the case of 4 layer PCBs, this will not be possible as the signal traces adjacent to the Power plane will be referenced to a Power plane. Consequently, the signal return path would depend on decoupling. Therefore, it is very important that the decoupling requirement on 4 layer PCBs addresses return paths in addition to meeting power integrity requirements.The clock net is differential in both DDR2 and DDR3. In DDR2, DQS can be either single ended or differential although it is usually implemented as differential at higher data rates. The switched delay of a differential trace is less than that of a single ended trace of identical length. Where timing computations indicate the need, the clock and DQS traces may need to be made longer than the corresponding ADDR/CMD/CNTRL nets and DATA nets. This would ensure that the clock and DQS transitions are centered on the associated ADDR/CMD/CNTRL nets and DQ nets.Since DQ and DM nets run at the maximum speed, it is desirable that all of these nets in any byte lane be routed identically, preferably without vias. Differential nets are less sensitive to discontinuities and where layer jumping is needed, the DQS and CLOCK nets should be considered first.Figure 6: s-parameters of interconnects with vias (60 Ohm normalization)Figure 7: Driver and Receiver waveforms for the 3 cases of Figure 6. (Plot colors correspond)5. CrosstalkCross talk contributes to delay uncertainty being significant for microstrip traces. This is generally reduced by increasing the spacing between adjacent traces for long parallel runs. This has the drawback of increasing the total trace length and therefore a reasonable value must be chosen. Typically the spacing should be greater than twice the trace distance to ground. Again, ground vias play an important role. Near and far end coupling levels are illustrated in Figure 8. Use of multiple ground vias reduces coupling levels by 7 dB. To derive the interconnect budget, a simulation of a victim trace with two aggressors on both sides is adequate. Using a periodic excitation on all nets will yield the cross talk induced jitter. Using a pseudo random excitation on all nets will show the effect of both cross talk as well as data dependencies. Time domain results are not shown here, but it is easily done by setting up a 5 coupled line circuit in SigXP with the spacing between traces set up for sweeping. Reasonable spacing values that keep the jitter in the waveform due to both cross talk as well as pattern dependence at an acceptable level are chosen.Figure 8: s-parameters of coupled traces (60 Ohm normalization)6. Power IntegrityPower Integrity here refers to meeting the Power supply tolerance requirement under a maximum switching condition. Failure to address this requirement properly leads to a number of problems, such as increased clock jitter, increased data dependent jitter, and increased cross talk all of which eventually reduce timing margins.The theory for decoupling has been very well understood and usually starts with the definition of a “target impedance” as [4]CurrentTransient tolerance Voltage Z et t =arg (1)An important requirement here is knowledge of the transient current under worst case switching condition. A second important requirement is the frequency range. This is the range of frequencies over which the decoupling network must ensure that its impedance value is equal to or below the required target impedance. On a printed circuit board, capacitance created by the Power-Ground sandwich and the decoupling capacitors needs to handle a minimum frequency of ~100 kHz up to a maximum frequency of ~100-200 MHz. Frequencies below 100 kHz are easily addressed by the bulk capacitance of the voltage regulator module. Frequencies above 200 MHz should be addressed by the on-die and in some cases on-package decoupling capacitance. Due to the finite inductance of the package, there is no need to provide decoupling on the PCB to handle frequencies greater than 200 MHz. The actual computation of power integrity can be very complex involving IC package details, simultaneously switched signals and the PCB power distribution network. For PCB design, the use of the target impedance approach to decoupling design is simpler and provides a practical solution with very little computational effort.The three power rails of concern are the VDD, VTT and Vref. The tolerance requirements on the VDD rail is ~ 5% and the transient current is determined as the difference between Idd7 and Idd2 as specified by JEDEC [1,4]. This is accomplished by using plane layers for power distribution and a modest number of decoupling capacitors. It is preferable to use decoupling capacitors of 10 different values distributed in the range of 10 nF to 10 uF. Further, the capacitor pad mounting structure should be designed for reduced mounted inductance.The Vref rail has a tighter tolerance, but it draws very little current. Its target impedance is easily met using narrow traces and one or two decoupling capacitors. It is important however that the capacitors be located very close to the device pins.The VTT rail proves to be challenging because it not only has a tighter tolerance, but it also draws a transient current close to that of the VDD rail. The transient current is easily calculated as described in reference [5]. Again, the target impedance requirement can be met using an increased number of decoupling capacitors.On a 4 layer PCB, the planes are too far apart and consequently the advantage of inter-plane capacitance is lost. The number of decoupling capacitors needs to be increased and higher frequency capacitors with values less than 10 nF may be needed. These computations are easily done using ALLEGRO SI Power Integrity option.7. TimingTiming computation is carried out as described in reference [6]. A table needs to be setup for the following eight cases: 1. 2. 3. 4. 5. 6. 7. 8. Write Setup analysis DQ vs. DQS Write Hold analysis DQ vs. DQS Read Setup analysis DQ vs. DQS Read Hold analysis DQ vs. DQS Write Setup analysis DQS vs. CLK Write Hold analysis DQS vs. CLK Write Setup analysis ADDR/CMD/CNTRL vs. CLK Write Hold analysis ADDR/CMD/CNTRL vs. CLKAn example is shown for the case of Write setup analysis in Table 2. Actual numbers have been omitted as they are not precisely known yet for DDR3. These numbers are obtained from data sheets of Controller and memory manufacturers. The numbers in the interconnect section are determined by SI simulations. All the eight cases need to be analyzed for DDR2. For DDR3, 5 and 6 are not needed due to its write leveling feature. In the PCB implementation, length match tolerances must ensure that the total margin is positive. ElementControllerSkew Componenta.)DQ vs. DQS skew at transmitter output b.) Data / Strobe PLL jitter a+b Setup requirement (tDSb @ Vih/Vil level) DQ slew rate DQS slew rateSetupUnitsps ps ps psCommentsFrom controller design data Used if not included in transmitter skewTotal Controller SDRAM (or DIMM)V/ns V/ns psTotal SDRAM setup requirement InterconnecttDSb + slew rate adjustmentFrom SDRAM datasheet; this number is to be adjusted based on DQ and DQS slew rates Measured as per JEDEC specification from SI simulation results Measured as per JEDEC specification from SI simulation results Includes slew rate adjustmenta.) Data Xtalk b.) DQS Xtalk c.) Length matching tolerance d.) Characteristic impedance mismatch Total Interconnect Min. Total Setup Budget Setup margin Interconnect skew (a + b + c + d) 0.24*tckps ps ps ps2 aggressors (one each side of the victim); victim – repetitive; aggressor- PRBS 2 aggressors (one each side of the victim); victim – repetitive; aggressor- PRBS Extracted from SI simulation results longest data net, worst case PVT corner can be omitted if routing of DQ and corresponding DQS signals are done on same layerps ps From SDRAM datasheet (includes clock duty cycle variation) Must be positiveMin. Total Setup Budget – (Total Controller + Total SDRAM + Total Interconnect )psTable 2: Illustration of DDR3 Write Setup timing analysis summary for DQ vs. DQS8. PCB LayoutImplementation on a PCB involves a number of tradeoffs to meet SI requirements. Often, the question is how far does one need to go? PCB layout tasks are facilitated using the following approach: 1. Set up topology and constraints in ALLEGRO Constraint Manager. 2. Design Controller BGA breakout. A controller pin arrangement with ADDR/CMD/CNTRL pins in the middle and DQ/DQS/DM byte lanes on either side is best suited. Within these groups, individual pins may need to be swapped to ensure routing with minimum cross-over. 3. Attempt routing with reduced stub length and a minimum trace spacing as obtained from cross talk simulation. Often, most stubs can be eliminated but it will not be possible for all the pins. One may try two traces between BGA pads of the memory devices. This would require narrow PCB traces which can increase manufacturing cost. Yet, it will not be possible for all signals unless micro via and via-in-pad technology is used. Complete routing with coarse length matching tolerances. 4. Place Vref decoupling capacitors close to the Vref pins. Vtt decoupling can be placed at the far end of the last SDRAM and will not come in the way of routing. VDD decoupling can be placed close to devices where possible without blocking routing channels. The smaller valued capacitors should be placed closer to the devices. With a proper decoupling design, it will not be necessary to cram all capacitors close to the devices. All decoupling capacitors should use a fan out for the footprint designed for reduced inductance. This is typically two short wide traces perpendicular to the capacitor length. This can be automated by using a user defined capacitor footprint that can be attached to all the decoupling capacitors in the schematic. 5. Implement fine length matching and insert multiple ground vias where signal traces jump layers. It is better to use the delay matching option in ALLEGRO and one must include z-axis delay. Typically, P and N nets of differential pairs should be matched with a tolerance of +/- 2ps and the tolerance for all other matched nets can be +/- 10 ps or more based on the timing margin computation.9. DIMMConsiderations described above apply to the case of PCBs containing one or more DIMMs. The only exception is that the decoupling requirement for the memories can be relaxed as it is already accounted for on the DIMM PCB. SI analysis of registered DIMMs is also much simpler where the DIMM is treated as a single load. While the routing topology for ADDR/CMD/CNTRL nets is usually a daisy chain with reduced stubs, tree topologies can also be used for registered DIMMs. Analysis of un-buffered DIMMs can become tedious as the timing requirement at all the SDRAMs must be analyzed. DIMM routing on 4-layer PCBs is relatively simpler compared to the case of SDRAMs.10. ExamplesThe detail described above has been used in the implementation of a DDR2 PCB, a DDR3 PCB and a DDR3 – DIMM PCB. The controller is from MOSAID [7] which is designed to provide both DDR2 as well as DDR3 functionality. For the SI simulations, IBIS models have been used. Models for the memories are from MICRON Technology, Inc [8]. The IBIS models for the DDR3 SDRAMs were available at 1333 Mbps speed. These were used at 1600 Mbps. For the unbuffered DDR3 DIMM (MT_DDR3_0542cc) EBD models from Micron Technology were used. All waveforms are for the typical case and are computed at the SDRAM die. The 6 layer PCB stackup of Figure 2 is used with routing on TOP and BOTTOM layers only. The memory consists of 2 SDRAMsrouted as a daisy chain. In the case of the DIMM, a single unbufferred DIMM is used. TOP/BOTTOM layer routing and Signal Integrity waveforms are shown in Figures. 9-11.Snapshots ofFigure 9: Illustration of TOP and BOTTOM layers of a DDR3 PCB with computed waveforms at the farthest SDRAM. Waveform on left is an ADDRESS net compared to that of the CLOCK net. Waveform on the right is a DATA net compared to that of a DQS net. Clock frequency = 800 MHz and data rate is 1600 Mbps.Figure 10: Illustration of TOP and BOTTOM layers of a DDR2 PCB with computed waveforms at the farthest SDRAM. Waveform on left is an ADDRESS net compared to that of the CLOCK net. Waveform on the right is a DATA net compared to that of a DQS net. Clock frequency = 400 MHz and data rate is 800 Mbps.Figure 11: Illustration of TOP and BOTTOM layers of a DDR3 – DIMM PCB with computed waveforms at the 8th (last) SDRAM on DIMM. Waveform on left is an ADDRESS net compared to that of the CLOCK net. Waveform on the right is a DATA net compared to that of a DQS net.Lastly, Figure 12 shows a comparison of computed and measured DATA eye patterns of an 800 Mbps DDR2. In all cases waveform integrity can be seen to be excellent.Figure 12: Computed (Red) and Measured (blue) waveforms of a data net of an 800 Mbps DDR2 PCB.11. ConclusionIn this paper, all aspects related to SI, and PI of DDR2 and DDR3 implementation have been described. Use of Constraint Manager in ALLEGROTM makes implementation easy. While a four layer PCB implementation of 800 Mbps DDR2 and DDR3 appears to be feasible, DDR3-1600 Mbps will prove to be challenging. It will become clearer as the memory devices become available and one has a good handle on timing numbers.References[1] DDR2 SDRAM Specification, JEDEC JESD79-2B, January 2005. [2] DDR3 SDRAM Standard, JEDEC JESD79-3, June 2007. [3] Syed Bokhari, “Delay matching on Printed Circuit Boards”, Proceedings of the CDNLIVE 2006, San Jose. [4] Larry D Smith, and Jeffrey Lee, “Power Distribution System for JEDEC DDR2 memory DIMM, Proc. IEEE EPEP conference, Princeton, N.J., pp. 121-124, October 2003. [5] Hardware and layout design considerations for DDR2 SDRAM Memory Interfaces, Freescale semiconductor Application Note, Doc. No. AN2910, Rev. 2, 03/2007. [6] DDR2 design guide for 2 DIMM systems, Technical Note, Micron Technology Inc. TN-47-01, 2003. [7] /corporate/products-services/ip/SDRAM_Controller_whitepaper_Oct_2006.pdf [8] /products/dram/ddr2/partlist.aspx?speed=DDR2-800 [9] /products/dram/ddr3/partlist.aspx?speed=DDR3-1066。

最新DDR3-硬件设计和-Layout-设计整理

DDR3硬件设计和Layout设计译自飞思卡尔官方文档Hardware and Layout DesignConsiderations for DDR3 SDRAMMemory InterfacesDocument revision historyDate Revision Changes 2015-03-29 1.0 第一次撰稿目录1 设计检查表 (3)2 终端匹配电阻功耗计算 (8)3 VREF (8)4 VTT电压轨 (8)5 DDR布线 (9)5.1 数据线— MDQ[0:63], MDQS[0:8], MDM[0:8], MECC[0:7] (9)5.2 Layout建议 (10)6 仿真 (12)7 扩展阅读 (13)8 历史版本 (13)9 声明 (13)这是一篇关于DDR3 SDRAM IP core的设计向导,出自飞思卡尔,为了实现PCB的灵活设计,我们可以采用合适的拓扑结构简化设计时的板级关联性。

飞思卡尔强烈推荐系统/板级工程师在PCB制板前进行设计验证,包括信号完整性、时序等等。

1 设计检查表如表1,罗列了DDR设计检查清单,推荐逐一检查,并在最右侧作出决策。

表1 DDR3检查清单序号描述是/否仿真1 是否最优化了①终端匹配电阻值、②信号线拓扑、③走线长度等?这些项目最好通过仿真进行优化!假如在DDR和控制器间应用了ODT(on-die termination)技术,那么在数据总线上就不需要额外的终端匹配电阻了。

DDR分组要求如下:■数据组:MDQS(8:0),(8:0),MDM(8:0),MDQ(63:0),MECC(7:0)■地址/命令组:MBA(2:0),MA(15:0),,,■控制组:(3:0),MCKE(3:0),MODT(3:0)■时钟组:MCK(5:0),(5:0)数据组走线共计72位(64bit + 8bit ECC<ECC是Error Checking and Correcting的简写,即是错误检查和纠正,这种技术多用在服务器中>)。

DDR3-硬件设计和-Layout-设计

冲和下冲等)。

终端匹配方案

设计者应该采用主流的终端匹配方案,像商业电脑主板那样的设计,ODT 终端匹配被应用在

数据总线上,地址/命令和控制线也应通过电阻连接到 VTT。当然,其它的终端匹配也是有

效的,但最好通过仿真来验证,确保信号质量满足要求。

3

终端匹配电阻的选择,其功耗是否满足芯片制造商的要求。

功耗计算 Power = x RT

4

假如数据线组增加了外部终端匹配电阻,请查看数据线组是否与其他 DDR3

信号组远离/隔离。

注:因为在 DDR3 数据组中通常优先选用内部 ODT 终端匹配,额外电阻是不

需要的。当然,假如不用 ODT 电阻,那么就需要增设外部电阻器了。

5

请查看 VTT 电阻 RT 布局是否正确,RT 终端电阻应该直接连接到 DDR 总线末端

4 / 13

序号

27

28 29 30

描述

该在同一层布线,并且保证过孔数量的一致性。

注:一些 DDR 芯片数据线接口是 32 位的。

通道 0:MDQ(7:0),MDM(0),MDQS(0),

(0)

通道 1:MDQ(15:8),MDM(1),MDQS(1),

(1)

通道 2:MDQ(23:16),MDM(2),MDQS(2),

VREF 是否合理去耦,源端和终端都应布置一个 0.1uF 电容。

VREF 参考源是否会随 VDDQ、温度、噪声变化,这个变化是否满足 JEDEC 要求。

VREF 电流是否满足系统(DDR 和处理器)需求。

如果采用电阻分压网络产生 VREF,那么请保证电阻阻值和至少 1%的精度。

Routing

建议 DDR3 布线顺序如下:

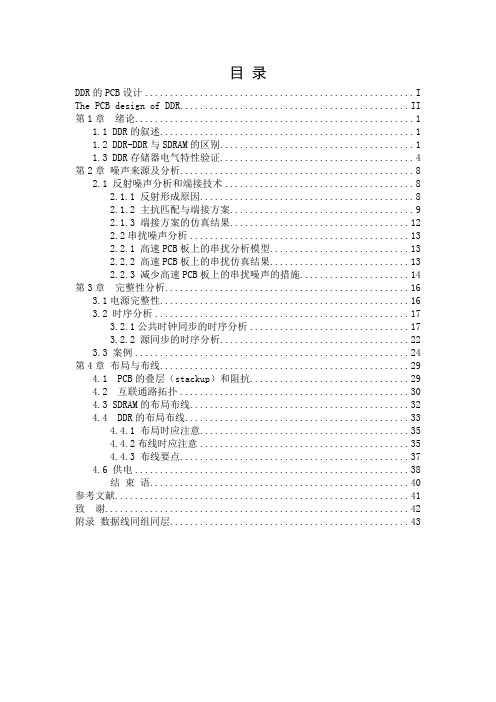

毕业设计---DDR的PCB设计

目录DDR的PCB设计 (I)The PCB design of DDR.............................................. I I 第1章绪论.. (1)1.1 DDR的叙述 (1)1.2 DDR-DDR与SDRAM的区别 (1)1.3 DDR存储器电气特性验证 (4)第2章噪声来源及分析 (8)2.1 反射噪声分析和端接技术 (8)2.1.1 反射形成原因 (8)2.1.2 主抗匹配与端接方案 (9)2.1.3 端接方案的仿真结果 (12)2.2串扰噪声分析 (13)2.2.1 高速PCB板上的串扰分析模型 (13)2.2.2 高速PCB板上的串扰仿真结果 (13)2.2.3 减少高速PCB板上的串扰噪声的措施 (14)第3章完整性分析 (16)3.1电源完整性 (16)3.2 时序分析 (17)3.2.1公共时钟同步的时序分析 (17)3.2.2 源同步的时序分析 (22)3.3 案例 (24)第4章布局与布线 (29)4.1 PCB的叠层(stackup)和阻抗 (29)4.2 互联通路拓扑 (30)4.3 SDRAM的布局布线 (32)4.4 DDR的布局布线 (33)4.4.1 布局时应注意 (35)4.4.2布线时应注意 (35)4.4.3 布线要点 (37)4.6 供电 (38)结束语 (40)参考文献 (41)致谢 (42)附录数据线同组同层 (43)DDR的PCB设计摘要:随着微电子技术和计算机技术的不断发展,DDR双通道同步动态随机存储器在通信系统中的应用越来越显得重要,而随着电子产品的集成化,对DDR在PCB中的设计要求也越来越高。

为了更好的能理解DDR,本文还与SDRAM一并做了介绍与设计。

本设计为基于DDR双通道同步动态随机存储器的PCB设计。

本文主要介绍了在对DDR的PCB设计时,所面临的信号完整性。

详尽的阐述了影响信号完整性的反射、串扰和信号完整性中的时序分析的相关理论并提出了减小反射和串扰得有效措施。

ddr3 电路设计

ddr3 电路设计

DDR3是一种双数据速率(Double Data Rate)的SDRAM(同步

动态随机存取存储器),它具有高速、高密度和低功耗的特点。

在

进行DDR3电路设计时,需要考虑以下几个方面:

1. 时序设计,DDR3内部时序非常严格,需要精确的时钟控制

和信号同步。

在电路设计中,需要确保时钟信号的准确性和稳定性,同时要考虑数据和控制信号的延迟和对齐。

2. 信号完整性,DDR3的高速传输需要考虑信号完整性,包括

信号的传输线路设计、阻抗匹配、信号串扰和噪声抑制等方面。

在

电路设计中需要合理布局PCB,减小信号传输路径的长度,采用差

分信号传输等方法来提高信号完整性。

3. 电源和接地设计,DDR3需要提供稳定的电源和接地,以确

保芯片的正常工作。

在电路设计中需要考虑电源线和接地线的布局

和连接方式,减小电源噪声和提高电源供电的稳定性。

4. 自校准和时序校准,DDR3内部具有自校准和时序校准的功能,可以校正时钟和数据信号的偏移和延迟。

在电路设计中需要考

虑这些校准功能的实现和控制。

5. 热管理,DDR3在高速运行时会产生较多的热量,需要考虑散热设计,包括散热片的设计和散热风扇等。

总之,DDR3电路设计需要全面考虑时序、信号完整性、电源和接地、自校准和时序校准、热管理等多个方面,以确保DDR3芯片的正常工作和高速稳定传输。

使用Cadence_PCB_SI应对DDR3的挑战

32

库管理

关键器件预布局

布线前规则规划

•在高速设计流程的最初阶段,硬件工程师和SI工程师需要通力合作做好PCB设 计的基本要求和关键信号的规则规划

33

关键器件预布局

•对于很多系统设计,主要芯片和接插件的布局已经预先确定了。可以优先执行 这部分元件的布局。

30

传统设计流程

项目创建和设置 原理图设计 规则获取和规划 打包原理图 PCB设计 生产文件输出

设计差异管理 库管理

31

设计同步

高速PCB设计流程

布线前规则规划 项目创建和设置

原理图输入

前仿真分析 规则驱动布局 规则驱动布线 布线后DRC检查 后仿真验证 生产文件输出

Input

Vref

10

Fly-by拓扑

•Fly-by拓扑可提高DDR3的时钟/地址/命令信号的信号完整性

DDR/DDR2 DIMM

11

写入校准(Write Leveling)

•补偿因fly-by拓扑带来的数据选通对于时钟的时序偏移

12

• 建立和保持时间的要求从数值上不再是单一值,而是随着 地址/数据信号的变化沿斜率的变化而变化

20

DDR3设计的主要挑战 - 信号质量

• 阈值电压

– 直流和交流 – 噪声裕量

• 过冲和下冲

– 幅值 – 面积

• tVAC

– 信号在阈值上停留的最小时间

• 眼图

– 计算了抖动后的有效数据窗口

• 拓扑结构

– 数据类信号:点对点拓扑 – 地址类信号:Fly-By拓扑

• 信号线阻抗

– 例如地址类信号,主干的阻抗要求是45ohm,分支的阻抗要求是60ohm – 允许的阻抗误差百分比

xilinx平台DDR3设计教程之仿真篇_中文版教程

想做个DDR设计不?想还是不想?你要知道FPGA这种东西,片内存储资源终究有限,实在谈不上海量存储。

万一哪天你想要海量存储数据了咋办?你是不是得用DRAM条子啊?什么?你还想用SRAM?今年已经2013年了童鞋~关于DRAM,或许是SDRAM,或许是DDR1(再次提醒你,2013年了已经),或许是DDR2或者DDR3。

这些条子都有一套控制协议,这套协议对不同的条子大同小异,但是里面又有各种细节的区别,这些你都搞懂了吗?没搞懂?其实,你不需要搞懂。

现在的EDA设计不需要你从基础知识开始研究。

这个时代,你要生存要发展,最佳的办法是站在巨人的肩膀上,而不是亲自长成个巨人。

DDR设计太常用了,只要你在搞FPGA,自然有人给你搞定一套IP,免费的给你用。

你不会还想自己从底层写起吧?多花些时间在没有免费IP用的协议合算法上吧。

现在进入正题:我刚刚讲的免费IP,在哪里?怎么用的?(小白问题,IP是什么,IP地址吗?)这里的IP就是Intelligence Property说白了就是xilinx里的core gen(对应于altera里面的mega wizard)这个文档就举一个例子来讲,选哪家呢?本人是xilinx和altera都来一个?条子选啥?SDR?DDR1? 各种条子全都写一套?(你以为写这个文档容易吗,是不是要连chipscope怎么用也一起出个文档啊?全部都写一套可以,先往我账户上打五千块钱,然后我再考虑考虑。

记住这个世界上没有白吃的午餐,你要看白痴都能看会的DDR教程,你就得听我在这里唠叨)本教程选择一个例子来讲,那就是xilinx平台下用DDR3(常见的笔记本内存条)接下来是你玩转这个教程所必须要准备的工具:xilinx ISE 14.1或者更高版本(不好意思,比14.1还低的版本我没试过。

vivado当然也可以,不过我是用的ISE)modelsim SE 6.6a或者更高版本(更低版本我负责的告诉你不可以,因为无法正常生成编译库,所以,6.5版本或者更低的你干脆就别装了)有鉴于这个文档的面相对象设定为连chiscope都不太会用的人,就是那种刚毕业不到一两年甚至还在校的,我必须郑重的告诉你一下这两个工具上哪里去下载:网上下载,百度股沟搜索会不会?什么?你告诉我搜不到?我给你跪了,菜鸟兄XILINX ISE 14.4这里下载http://simplecd.me/entry/L1a0enD2/破解文件:/f/62469961.htmlmodelsim 6.6这里下载(要注册和花积分的):/viewthread.php?tid=232457破解文件:/f/34760037.html(注意,时间长了以后这几个链接是可能失效的,比如你可能在2015年看到这个2013年11月写的文档,到时候可能只能自己找下载了)PPT翻了一页了,工具都装完了吗亲?已经装完了啊?很好哦,那我们就开始吧!你知道用ISE做DDR设计的第一步是啥吗?当然是打开工具了——我估计这你肯定知道打开工具之后做啥?当然是生成一个IP,对xilinx来说也就是core gen了我估计你即便是新手上路,这个也是知道的——因为我前面刚刚讲过了嘛那么core gen生成完了之后呢?是不是要仿真啊?仿真需要什么?当然是modelsim了——我还是刚刚讲过,哈哈那你知道用modelsim仿真DDR的core gen,是需要xilinx仿真库的吗?什么?你不知道啥叫仿真库?乖乖隆地洞,我还是给你讲讲啥叫仿真库吧先关于FPGA的仿真库本人不是学校里的学究,本人是工程师所以用工程师的语言告诉你啥叫仿真库FPGA本身是一种特定的芯片,这个芯片里有很多特定的基本电路单元。

最新DDR3-硬件设计和-Layout-设计整理

最新DDR3-硬件设计和-Layout-设计整理DDR3硬件设计和Layout设计译自飞思卡尔官方文档Hardware and Layout DesignConsiderations for DDR3 SDRAMMemory InterfacesDocument revision historyDate Revision Changes 2015-03-29 1.0 第一次撰稿目录1 设计检查表 (3)2 终端匹配电阻功耗计算 (8)3 VREF (8)4 VTT电压轨 (8)5 DDR布线 (9)5.1 数据线— MDQ[0:63], MDQS[0:8], MDM[0:8], MECC[0:7] (9)5.2 Layout建议 (10)6 仿真 (12)7 扩展阅读 (13)8 历史版本 (13)9 声明 (13)这是一篇关于DDR3 SDRAM IP core的设计向导,出自飞思卡尔,为了实现PCB的灵活设计,我们可以采用合适的拓扑结构简化设计时的板级关联性。

飞思卡尔强烈推荐系统/板级工程师在PCB制板前进行设计验证,包括信号完整性、时序等等。

1 设计检查表如表1,罗列了DDR设计检查清单,推荐逐一检查,并在最右侧作出决策。

表1 DDR3检查清单序号描述是/否仿真1 是否最优化了①终端匹配电阻值、②信号线拓扑、③走线长度等?这些项目最好通过仿真进行优化!假如在DDR和控制器间应用了ODT(on-die termination)技术,那么在数据总线上就不需要额外的终端匹配电阻了。

DDR分组要求如下:■数据组:MDQS(8:0),(8:0),MDM(8:0),MDQ(63:0),MECC(7:0)■地址/命令组:MBA(2:0),MA(15:0),,,■控制组:(3:0),MCKE(3:0),MODT(3:0)■时钟组:MCK(5:0),(5:0)数据组走线共计72位(64bit + 8bit ECC<="" p="">的简写,即是错误检查和纠正,这种技术多用在服务器中>)。

xilinx平台DDR3设计教程之仿真篇

想做个DDR设计不?想还是不想?你要知道FPGA这种东西,片内存储资源终究有限,实在谈不上海量存储。

万一哪天你想要海量存储数据了咋办?你是不是得用DRAM条子啊?什么?你还想用SRAM?今年已经2013年了童鞋~关于DRAM,或许是SDRAM,或许是DDR1(再次提醒你,2013年了已经),或许是DDR2或者DDR3。

这些条子都有一套控制协议,这套协议对不同的条子大同小异,但是里面又有各种细节的区别,这些你都搞懂了吗?没搞懂?其实,你不需要搞懂。

现在的EDA设计不需要你从基础知识开始研究。

这个时代,你要生存要发展,最佳的办法是站在巨人的肩膀上,而不是亲自长成个巨人。

DDR设计太常用了,只要你在搞FPGA,自然有人给你搞定一套IP,免费的给你用。

你不会还想自己从底层写起吧?多花些时间在没有免费IP用的协议合算法上吧。

现在进入正题:我刚刚讲的免费IP,在哪里?怎么用的?(小白问题,IP是什么,IP地址吗?)这里的IP就是Intelligence Property说白了就是xilinx里的core gen(对应于altera里面的mega wizard)这个文档就举一个例子来讲,选哪家呢?本人是xilinx和altera都来一个?条子选啥?SDR?DDR1? 各种条子全都写一套?(你以为写这个文档容易吗,是不是要连chipscope怎么用也一起出个文档啊?全部都写一套可以,先往我账户上打五千块钱,然后我再考虑考虑。

记住这个世界上没有白吃的午餐,你要看白痴都能看会的DDR教程,你就得听我在这里唠叨)本教程选择一个例子来讲,那就是xilinx平台下用DDR3(常见的笔记本内存条)接下来是你玩转这个教程所必须要准备的工具:xilinx ISE 14.1或者更高版本(不好意思,比14.1还低的版本我没试过。

vivado当然也可以,不过我是用的ISE)modelsim SE 6.6a或者更高版本(更低版本我负责的告诉你不可以,因为无法正常生成编译库,所以,6.5版本或者更低的你干脆就别装了)有鉴于这个文档的面相对象设定为连chiscope都不太会用的人,就是那种刚毕业不到一两年甚至还在校的,我必须郑重的告诉你一下这两个工具上哪里去下载:网上下载,百度股沟搜索会不会?什么?你告诉我搜不到?我给你跪了,菜鸟兄XILINX ISE 14.4这里下载http://simplecd.me/entry/L1a0enD2/破解文件:/f/62469961.htmlmodelsim 6.6这里下载(要注册和花积分的):/viewthread.php?tid=232457破解文件:/f/34760037.html(注意,时间长了以后这几个链接是可能失效的,比如你可能在2015年看到这个2013年11月写的文档,到时候可能只能自己找下载了)PPT翻了一页了,工具都装完了吗亲?已经装完了啊?很好哦,那我们就开始吧!你知道用ISE做DDR设计的第一步是啥吗?当然是打开工具了——我估计这你肯定知道打开工具之后做啥?当然是生成一个IP,对xilinx来说也就是core gen了我估计你即便是新手上路,这个也是知道的——因为我前面刚刚讲过了嘛那么core gen生成完了之后呢?是不是要仿真啊?仿真需要什么?当然是modelsim了——我还是刚刚讲过,哈哈那你知道用modelsim仿真DDR的core gen,是需要xilinx仿真库的吗?什么?你不知道啥叫仿真库?乖乖隆地洞,我还是给你讲讲啥叫仿真库吧先关于FPGA的仿真库本人不是学校里的学究,本人是工程师所以用工程师的语言告诉你啥叫仿真库FPGA本身是一种特定的芯片,这个芯片里有很多特定的基本电路单元。

systemSI DDR3仿真步骤

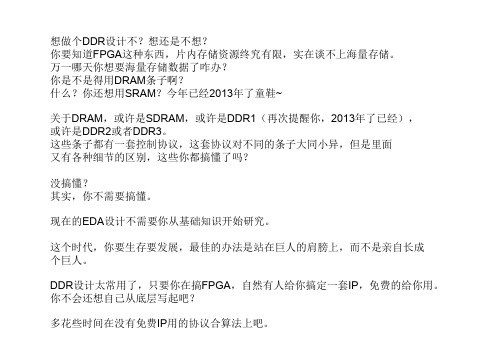

1、使用systemSI进行仿真的流程为:获取芯片IBIS模型》加载芯片IBIS模型》分配仿真bus》提取PCB S参数》配置仿真模型及参数》仿真其中提取PCB S参数的步骤为:将brd文件转化为spd文件》配置平面参数》设置电源net》选择需要仿真的net并自动生成port》设置port阻抗》仿真2、system SI IBIS模型加载步骤:其中点击1选择需要加载的IBIS模型,一个IBIS模型中可能包括多个器件型号,需要在右上方的“component”中选择对应的器件型号,然后点击bus definition定义总线(定义总线的主要作用是区分哪些信号需要仿真,并将需要仿真的信号分类为data、ctrl、addcmd三种类型),点击add添加新总线,在“Bus Type”中选择总线的类型,在“Bus Group”中设置Bus name,在“Timing Ref”中选择各个信号的参考时钟,“Edge Type”用于选择信号的触发方式,data触发方式为“BothEdges”,ctrl和addcmd的触发方式为“RiseEdge”,在“Signal Names”中选择该group中包括的信号,如果是data信号,还可以添加“Clock”即ctrl和addcmd的参考时钟,可以用于分析数据时钟与控制时钟的对应关系。

修改完成后点击OK,退出后点击“确定”分别对controller和memory进行配置,注意memory的配置需要与controller相对应,如下图3、提取PCB的S参数在开始菜单输入“SPDLinks”,打开Allegro Sigrity SPDLinks在步骤1的“Browse”中选择需要转换的.brd文件,点击“settings”进行参数设置,一般保持默认设置即可,如对参数有特殊需求,可参考help》translators》SPDLinks对相应的参数进行设置,设置完成后点击“Translate”即可生成.spd文件后,打开powerSI软件,导入.spd文件,先对层叠结构进行设置,点击“Model Extraction”中的“Check Stackup”,一般如果.brd文件中设置好了以后层叠结构会自动导入,如未导入,根据.brd文件中cross section的设置对powerSI的层叠结构进行相同的设置即可层叠结构设置完成后需设置电源网络,点击“select Nets”》“Skip setup P/G nets”进入net manager界面根据实际设计,分别选择电源网络和地网络,右键选择“classify”》“As PowerNets”或“As GroundNets”电源网络分配完成后选择需要分析的port,方法为:将所有net前方框中的对勾去掉,只保留需要仿真的网络。

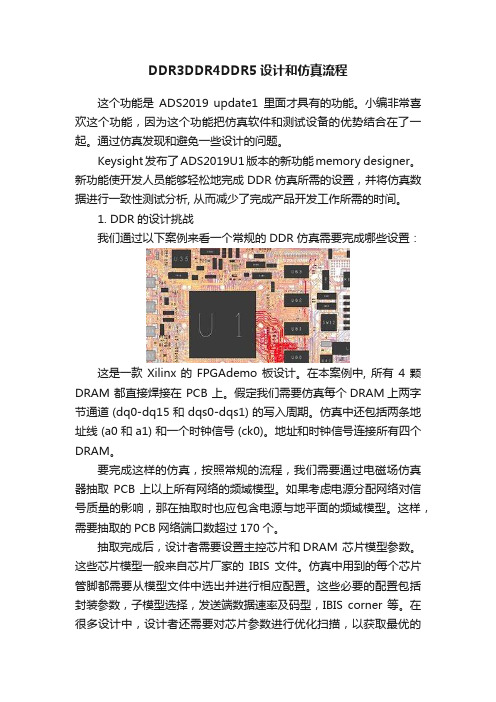

DDR3 Layout Design

Freescale SemiconductorApplication NoteThe design guidelines presented in this application note apply to products that leverage the DDR3 SDRAM IP core, and they are based on a compilation of internal platforms designed by Freescale Semiconductor, Inc. The purpose of these guidelines is to minimize board-related issues across multiple memory topologies while allowing maximum flexibility for the board designer.Freescale highly recommends that the system/board designer verify all design aspects (signal integrity, electrical timings, and so on) through simulation before PCB fabrication.Document Number:AN3940Rev. 1, 03/2010Contents1.Designer Checklist . . . . . . . . . . . . . . . . . . . . . . . . . . . 22.Termination Dissipation . . . . . . . . . . . . . . . . . . . . . . . 73.V REF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74.VTT Voltage Rail . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8yout Guidelines for the Signal Groups . . . . . . . . . . 86.Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127.Further Reading . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138.Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Hardware and Layout Design Considerations for DDR3 SDRAM Memory Interfacesby Networking and Multimedia GroupFreescale Semiconductor, Inc.Austin, TXDesigner Checklist1Designer ChecklistIn the following checklist, some of the items are phrased as question, others as requirements. In all cases, it is recommended to consider the line item and check it off in the rightmost column of Table1.Table1. DDR3 Designer’s ChecklistItem Description Yes/NoSimulation1.Have optimal termination values, signal topology, trace lengths been determined through simulation for eachsignal group in the memory implementation? If on-die termination is used at both the memories and the controller,no additional termination is required for the data group.The following unique groupings exist:1.Data Group: MDQS(8:0), MDQS(8:0), MDM(8:0), MDQ(63:0), MECC(7:0)2.Address/CMD Group: MBA(2:0), MA(15:0), MRAS, MCAS, MWE.3.Control Group: MCS(3:0), MCKE(3:0), MODT(3:0)4.Clock Group: MCK(5:0) and MCK(5:0)These groupings assume a full 72-bit data implementation (64-bit + 8 bits of ECC). Some products may onlyimplement 32-bit data and may choose to have fewer MCS, MCKE, and MODT signals. Some products supportthe optional MAP AR_OUT and MAP AR_ERR for registered DIMMs. In such cases, MAP AR_OUT should betreated as part of the ADDR/CMD group and MAPAR_ERR can be treated as an asynchronous signal.2.Does the selected termination scheme meet the AC signaling parameters (voltage levels, slew rate, andovershoot/undershoot) across all memory chips in the design?Termination SchemeIt is assumed that the designer is using the mainstream termination approach as found in commodity PC motherboards. Specifically, it is assumed that on-die termination is used for the data groups and that external parallel resistors tied to VTT are used for the Address/CMD and the control groups. Consequently, differing termination techniques may also prove valid and useful. However, they are left to the designer to validate through simulation.3.Is the worst case power dissipation for the termination resistors within the manufacturer’s rating for the selecteddevices? See Section2, “Termination Dissipation.”4.If resistor packs are used, have data lanes been isolated from the other DDR3 signal groups?Note: Because on-die termination is the preferred method for DDR3 data signals, external resistors for the datagroup should not be required. This item would only apply if the ODT feature is not used.5.Have V TT resistors been properly placed? The R T terminators should directly tie into the V TT island at the end ofthe memory bus.6.Is the differential terminator present on the clock lines for discrete memory populations? (DIMM modules containthis terminator.) Nominal range => 100–120 Ω.7.Recommend that an optional 5pF cap be placed across each clock diff pair. If DIMM modules are used, the capshould be placed as closely as possible to the DIMM connector. If discrete devices are used, the cap should beplaced as closely as possible to the discrete devices.V TT Related Items8.Has the worst case current for the V TT plane been calculated based on the design termination scheme? SeeSection2, “T ermination Dissipation.”9.Can the V TT regulator support the steady state and transient current needs of the design?Designer ChecklistTable1. DDR3 Designer’s Checklist (continued)Item Description Yes/No 10.Has the V TT island been properly decoupled with high frequency decoupling? At least one low ESL cap, or twostandard decoupling caps for each four-pack resistor network (or every four discrete resistors) should be used. Inaddition, at least one 4.7-μF cap should be at each end of the V TT island.Note: This recommendation is based on a top-layer V TT surface island (lower inductance). If an internal split isused, more capacitors may be needed to handle the transient current demands.11.Has the V TT island been properly decoupled with bulk decoupling? At least one bulk cap (100–220μF) capacitorshould be at each end of the island.12.Has the V TT island been placed at the end of the memory channel and as closely as possible to the last memorybank? Is the V TT regulator placed in close proximity to the island?13.Is a wide surface trace (~150 mils) used for the V TT island trace?14.If a sense pin is present on the V TT regulator, is it attached in the middle of the island?V REF15.Is V REF routed with a wide trace? (Minimum of 20–25 mil recommended.)16.Is V REF isolated from noisy aggressors? In addition, maintain at least a 20–25 mil clearance from V REF to othertraces. If possible, isolate V REF with adjacent ground traces.17.Is V REF properly decoupled? Specifically, decouple the source and each destination pin with 0.1uf caps.18.Does the V REF source track variations in V DDQ, temperature, and noise as required by the JEDEC specification?19.Does the V REF source supply the minimal current required by the system (memories + processor)?20.If a resistor divider network is used to generate V REF, are both resistors the same value and 1% tolerance?Routing21.The suggested routing order within the DDR3 interface is as follows:1.Data address/command2.Control3.Clocks4.PowerThis order allows the clocks to be tuned easily to the other signal groups. It also assumes an open critical layeron which clocks are freely routed.22.Global items are as follows:•Do not route any DDR3 signals overs splits or voids.•T races routed near the edge of a reference plane should maintain at least 30–40 mil gap to the edge of the reference plane.•Allow no more than 1/2 of a trace width to be routed over via antipad.23.When routing the data lanes, route the outermost (that is, longest lane first) because this determines the amountof trace length to add on the inner data lanes.24.The max lead-in trace length for data/address/command signals, are not longer than 7 inches?25.Are the clock pair assignments optimized to allow break-out of all pairs on a single critical layer?Designer ChecklistTable1. DDR3 Designer’s Checklist (continued)Item Description Yes/No 26.The DDR3 data bus consists of 9 data byte lanes (assuming ECC is used). All signals within a given byte laneshould be routed on the same critical layer with the same via count.Note: Some product implementations may only implement a 32-bit wide interface.Byte Lane 0—MDQ(7:0), MDM(0), MDQS(0), MDQS(0)Byte Lane 1—MDQ(15:8), MDM(1), MDQS(1), MDQS(1)Byte Lane 2—MDQ(23:16), MDM(2), MDQS(2), MDQS(2)Byte Lane 3—MDQ(31:24), MDM(3), MDQS(3), MDQS(3)Byte Lane 4—MDQ(39:32), MDM(4), MDQS(4), MDQS(4)Byte Lane 5—MDQ(47:40), MDM(5), MDQS(5), MDQS(5)Byte Lane 6—MDQ(55:48), MDM(6), MDQS(6), MDQS(6)Byte Lane 7—MDQ(63:56), MDM(7), MDQS(7), MDQS(7)Byte Lane 8—MECC(7:0), MDM(8), MDQS(8), MDQS(8)T o facilitate fan-out of the DDR3 data lanes (if needed), alternate adjacent data lanes onto different critical layers.See Figure1 and Figure2.Note: If the device supports ECC, Freescale highly recommends that the user implement ECC on the initialhardware prototypes.27.DDR3 data group—impedance range and spacingOption #1 (wider traces—lower trace impedance)•Single-ended impedance = 40 Ω. The lower impedance allows traces to be slightly closer with less cross-talk.•Utilize wider traces if stackup allows (7–8mils)•Spacing to other data signals = 1.5x to 2.0x•Spacing to all other non-DDR signals = 4xOption #2 (smaller traces—higher trace impedance)•Single-ended impedance = 50 Ω.•Smaller trace widths (5–6mil) can be used.•Spacing between like signals should increase to 3x (for 5mil) or 2.5x (for 6mil) respectively28.Check the following across all DDR3 data lanes:•For MPC8572 and MPC8536, are all the data lanes matched to within 0.1 inch?•For all other devices, are all the data lanes matched to within 2.0 inch?29.Is each data lane properly trace matched to within 20 mils of its respective differential data strobe? (Assumeshighest frequency operation.)30.When adding trace lengths to any of the DDR3 signal groups, ensure that there is at least 25 mils betweenserpentine loops that are in parallel.Designer ChecklistTable1. DDR3 Designer’s Checklist (continued)Item Description Yes/No 31.MDQS/MDQS differential strobe routingNote: Some product implementations may support only the single-ended version of the strobe.•Match all segment lengths between differential pairs along the entire length of the pair. T race match the MDQS/ MDQS pair to be within 10 mils.•Maintain constant line impedance along the routing path by maintaining the required line width and trace separation for the given stackup.•Avoid routing differential pairs adjacent to noisy signal lines or high speed switching devices such as clock chips.•Differential 75–95 Ω•Diff Gap = 4–5 mils (as DQS signals are not true differential...aka pseudo differentialOption #1 (wider traces—lower trace impedance)•Single-ended impedance 40 Ω. The lower impedance allows traces to be slightly closer with less cross-talk.•Utilize wider traces if stackup allows (7–8mils)•Spacing to other data signals = 2x.•If not routed on the same layer as its associated data, then 4x spacingOption #2 (smaller traces—higher trace impedance)•Single-ended impedance = 50 Ω.•Smaller trace widths (5–6mil) can be used.•Spacing between like signals (other data) should increase to 3x (for 5mil) or 2.5x (for 6mil) respectively.•Do not divide the two halves of the diff pair between layers. Route MDQS/MDQS pair on the same critical layer as its associated data lane.32.DDR3 address/command/control group—impedance range and spacing•Daisy chain from chip to chip. The routing should go from chip 0 to chip n, where chip 0 is the one that has the lower data bits DQ[0:7]… and chip n has the upper data bits. The daisy chain should end at the terminationresistors that are after chip n.•With regards to physical/spacing propertiesOption #1 (wider traces—lower trace impedance)•Single-ended impedance = 40 Ω. The lower impedance allows traces to be slightly closer with less cross-talk.•Utilize wider traces if stackup allows (7–8mils)•Spacing to other like signals = 1.5x to 2.0x•Spacing to all other non-DDR signals =3–4xOption #2 (smaller traces—higher trace impedance)•Single-ended impedance = 50 Ω.•Smaller trace widths (5–6mil) can be used.•Spacing between like signals should increase to 3x (for 5mil) or 2.5x (for 6mil) respectively•Spacing to all other non-DDR signals =3–4x•With regards to tuning•T une signals to 20 mil of the clock at each device.33.DDR3 differential clocksRoute as diff pair. With regards to diff properties, recommendations are as follows:•P-to-N tuning = 10 mils•T arget single-ended impedance 40–50 Ω. The lower impedance reduces cross-talk.•Differential 75–95 Ω•Diff Gap = set per stackupOption #1 (wider traces—lower trace impedance)•Attempt to utilize wider traces if stackup allows (7–8mils)•Spacing to other signals = 4x.Option #2 (smaller traces—higher trace impedance)•Single-ended impedance = 50 Ω.•Smaller trace widths (5–6mil) can be used.•Spacing to other signals = 4x.Designer ChecklistTable1. DDR3 Designer’s Checklist (continued)Item Description Yes/No34.Are all clock pairs routed on the same critical layer (one referenced to a solid ground plane)?35.Are all clock pairs properly trace matched to within 25 mils of each other?36.The space from one differential pair to any other trace (this includes other differential pairs) should be at least 25mils.37.If unbuffered DIMM modules are used, are all required clock pairs per DIMM slot connected?Note: Single ranked DIMM requires 1 clock pair and dual ranked DIMM requires 2 clock pairsMODT/MDIC Related Items38.Are the MODT signals connected correctly?•MODT(0), MCS(0), MCKE(0) should all go to the same physical memory bank.•MODT(1), MCS(1), MCKE(1) should all go to the same physical memory bank.•MODT(2), MCS(2), MCKE(2) should all go to the same physical memory bank.•MODT(3), MCS(3), MCKE(3) should all go to the same physical memory bank.39.Is MDIC0 connected to ground via an 40-Ω precision 1% resistor? Is MDIC1 connected to DDR power via an 40-Ωprecision 1% resistor?Miscellaneous Items40.Are the power-on reset config pins properly set for the correct DDR type?Note: Not all Freescale products support external power-on reset configuration pins for selecting the DDR type.Therefore, this item does not apply to all Freescale products.Registered DIMM Topologies (All items above still apply)41.For memory implementations that use registered DIMM modules, the board designer should attach a reset signalto the DIMM sockets. This reset signal should be derived from a ‘power good’ monitor status circuit.Note: The reset pin to the DRAM is 1.5V LVCMOS.42.Though registered DIMMs require only a single clock per bank, all DDR3 clock pairs at the DIMM connectorshould be attached (analogous to unbuffered DIMMs) so the design can also support unbuffered DIMMs withminimal changes.43.If the controller supports the optional MAPAR_OUT and MAPAR_ERR signals, ensure that they are hooked upas follows:•MAP AR_OUT (from the controller) => P AR_IN (at the RDIMM)•ERR_OUT (from the RDIMM) => MAPAR_ERR (at the controller)44.MAP AR_ERR is an open drain output from registered DIMMs. Ensure that a 4.7K pull-up to 1.5 V is present onthis signal.Discrete Memory Topologies (All items above still apply with exception of registered DIMM items)45.Construct the signal routing topologies for the groups like those found on unbuffered DIMM modules (that is,proven JEDEC topologies).46.When placing components, optimize placement of the discretes to favor the data bus (analogous to DIMMtopologies).Optional: Pin-swap within a given byte lane to optimize the data bus routes further.Caution: Do not swap individual data bits across different byte lanes.Termination Dissipation2Termination DissipationSink and source currents flow through the parallel R T resistors on the address and control groups. The worst case power dissipation for these resistors is as follows:Power =I 2×R T =(13mA)2×(47Ω)=7.9mW.Small resistors that provide dissipation of up to 1/16 W are ideal. See Section 4, “VTT V oltage Rail ,” for assumptions made for current calculations.3V REFThe current requirements for V REF are relatively small, at less than 3 mA. This reference provides a DC bias of 0.75V (V DD /2) for the differential receivers at both the controller interface and the DDR devices. Noise or deviation in the V REF voltage can lead to potential timing errors, unwanted jitter, and erratic behavior on the memory bus. To avoid these problems, V REF noise must be kept within the JEDEC specification. As such, V REF and the V TT cannot be the same plane because of the DRAM V REF buffer sensitivity to the termination plane noise. However, both V REF and V TT must share a common source supply to ensure that both are derived from the same voltage plane. Proper decoupling at each V REF pin (at the controller, at each DIMM/discrete, and at the V REF source) along with adhering to the simple layout considerations enumerated in the checklist in Table 1 prevents potential problems .Numerous off-the-shelf power IC solutions are available that provide both the V REF and V TT from acommon source. Regardless of the generation technique, V REF must track variations in V DDQ over voltage, temperature, and noise margins as required by the JEDEC specifications.47.If a single bank of x16 devices is used, let the DDR3 clocks be point-to-point. Place the series damping resistor (R S ) close to the source and the differential terminator (R DIFF ) at the input pins of the discretes.If more than five discretes are used, construct the clocks like those on unbuffered DIMM modules. Alternatively, place an external PLL between the controller and the memory to generate the additional clocks.48.If multiple physical banks are needed, double stack (top and bottom) the banks to prevent lengthy and undesirable address/cmd topologies.49.Properly decouple the DDR3 chips per manufacturer recommendations. T ypically, five low ESL capacitors per device are sufficient. For further information, see article entitled Decoupling Capacitor Calculation for a DDR Memory Channel, located on Micron’s web site.50.T o support expandability into larger devices, ensure that extra NC pins (future address pins) are connected.51.Ensure access/test points are available for signal integrity probing. This is especially critical if using blind and buried vias within the memory channel. If through-hole vias are used under the BGA devices, then generally these sites can be used for probing.52.Ensure R T , resistors on the address and control groups are located after the last DRAM chip in the-fly-by topology.53.Ensure the reset pin has been considered and connected to the proper reset logic. Note: The reset pin to the DRAM is 1.5V LVCMOS.Table 1. DDR3 Designer’s Checklist (continued)Item DescriptionYes/NoVTT Voltage Rail4V TT Voltage RailFor a given topology, the worst case V TT current should be derived. Assuming the use of a typical R T parallel termination resistor and the worst case parameters given in Table 2, sink and source currents can be calculated.The driver sources (V TT plane would sink) the following based on this termination scheme:(V DD_max –V TT_min )/(R T + R DRVR )=(1.575–0.702 V)/(47+20)=13 mA The driver sinks (V TT plane would source) the following based on this termination scheme:(V TT_max – V OL / (R T + R S + R DRVR )=(0.798–0 V)/(47+20)=12 mAA bus with balanced number of high and low signals places no real demand on the V TT supply. However, a bus with all DDR address/command/control signals low (~ 28 signals) causes a transient current demand of approximately 350 mA on the V TT rail. The V TT regulator must provide a relatively tight voltage regulation of the rail per the JEDEC specification. Besides a tight tolerance, the regulator must also allow V TT along with V REF (if driven from a common IC), to track variations in V DDQ over voltage, temperature, and noise margins.5Layout Guidelines for the Signal GroupsTo help ensure the DDR interface is properly optimized, Freescale recommends the following sequence for routing the DDR memory channel:1.Route data2.Route address/command/control3.Route clocks The data group is listed before the command, address, and control group because it operates at twice the clock speed, and its signal integrity is of higher concern. In addition, the data group constitutes the largest portion of the memory bus and comprises most of the trace matching requirements (those of the data lanes). The address/command, control, and data groups all have a relationship to the routed clock.Therefore, the effective clock lengths used in the system must satisfy multiple relationships. The designer should perform simulation and construct system timing budgets to ensure that these relationships are properly satisfied.Table 2. Worst Case Parameters for V TT Current Calculation ParameterValuesCommentV DDQ (max) 1.575 V From JEDEC spec V TT(max)0.798 V From JEDEC spec V TT(min)0.702 V From JEDEC specR DRVR 20 ΩNominally, full strength is ~ 20Ωs R T 47 ΩCan vary. T ypically 25–47Ωs.V OL0 VAssumes driver reaches 0V in the low state.Layout Guidelines for the Signal Groups 5.1Data—MDQ[0:63], MDQS[0:8], MDM[0:8], MECC[0:7]The data signals of the DDR interface are source-synchronous signals by which memory and the controller capture the data using the data strobe rather than the clock itself. When transferring data, both edges of the strobe are used to achieve the 2x data rate.An associated data strobe (DQS and DQS) and data mask (DM) comprise each data byte lane. This 11-bit signal lane relationship is crucial for routing, and Table3 depicts this relationship. When length matching, the critical item is the variance of the signal lengths within a given byte lane to its strobe. Length matching across all bytes lanes is also important and must meet the t DQSS parameter as specified by JEDEC. This is also commonly referred to as the write data delay window. Typically, this timing is considerably more relaxed than the timing of the individual byte lanes themselves.Table3. Byte Lane to Data Strobe and Data Mask MappingData Data Strobe Data Mask Lane NumberMDQ[0:7]MDQS0, MDQS0MDM0Lane 0MDQ[8:15]MDQS1, MDQS1MDM1Lane 1MDQ[16:23]MDQS2, MDQS2MDM2Lane 2MDQ[24:31]MDQS3, MDQS3MDM3Lane 3MDQ[32:39]MDQS4, MDQS4MDM4Lane 4MDQ[40:47]MDQS5, MDQS5MDM5Lane 5MDQ[48:55]MDQS6, MDQS6MDM6Lane 6MDQ[56:63]MDQS7, MDQS7MDM7Lane 7MECC[0:7]MDQS8, MDQS8MDM8Lane 8NOTEWhen routing, each row (that is, the 11-bit signal group) must be treated asa trace-matched group.5.2Layout RecommendationsFreescale strongly recommends routing each data lane adjacent to a solid ground reference for the entire route to provide the lowest inductance for the return currents, thereby providing the optimal signal integrity of the data interface. This concern is especially critical in designs that target the top-end interface speed, because the data switches at 2x the applied clock. When the byte lanes are routed, signals within a byte lane should be routed on the same critical layer as they traverse the PCB motherboard to the memories. This consideration helps minimize the number of vias per trace and provides uniform signal characteristics for each signal within the data group.To facilitate ease of break-out from the controller perspective, and to keep the signals within the byte group together, the board designer should alternate the byte lanes on different critical layers (see Figure1 and Figure2).Layout Guidelines for the Signal GroupsFigure 1. Alternating Data Byte Lanes on Different Critical Layers —Part 1Data Lane 7Data Lane 5Data Lane 3Data Lane 1Layout Guidelines for the Signal GroupsFigure 2. Alternating Data Byte Lanes on Different Critical Layers—Part 2Data Group 6Data Group 4Data Group 8Data Group 2Data Group 0Simulation6SimulationThis application note provides general hardware and layout considerations for hardware engineers implementing a DDR3 memory subsystem.The rules and recommendations in this document can serve as an initial baseline for board designers to begin their specific implementations. The fly-by memory topology and many interface frequencies are possible from the DDR3 interface, so it is highly recommended that the board designer verify that all aspects (signal integrity, electrical timings, and so on) are addressed through simulation before board fabrication.In tandem with memory vendors, Freescale provides IBIS models for simulation. The board designer can realize a key advantage in the form of extra noise and timing margins by taking the following actions:•Optimizing the clock to signal group relationships to maximize setup and hold times•Optimizing termination values. During board simulation, verify that all aspects of the signal eye are satisfied, which includes at a minimum the following:—A sufficient signal eye opening meeting both timing and AC input voltage levels—Vswing max not exceeded (or alternatively max overshoot/max undershoot)—Signal slew rate within specificationsFigure3 shows the SSTL signal waveform.Figure3. SSTL Signal WaveformFurther Reading 7Further ReadingFollowing is a list of documentation that may be useful:•DDR3 chapter of the corresponding PowerQUICC or QorIQ processor reference manual•Micron web site: . For example, Design Guide for DDR3-1066 UDIMM systems: TN_41_08•JEDEC web site: . For example, the DDR3 SDRAM specification8Revision HistoryTable4 provides a revision history for this application note.Table4. Document Revision HistoryRev.Date Substantive Change(s)Number103/2010In T able1, for item# 28, changed the second bulleted sentence as follows:For all other devices, are all the data lanes matched to within 2.0 inch?001/2010Initial public releaseDocument Number:AN3940 Rev. 103/2010Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “T ypicals” must be validated for each customer application by customer’s technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.How to Reach Us:Home Page:Web Support:/supportUSA/Europe or Locations Not Listed: Freescale Semiconductor, Inc.T echnical Information Center, EL516 2100 East Elliot RoadT empe, Arizona 852841-800-521-6274 or+1-480-768-2130/supportEurope, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH T echnical Information Center Schatzbogen 781829 Muenchen, Germany+44 1296 380 456 (English)+46 8 52200080 (English)+49 89 92103 559 (German)+33 1 69 35 48 48 (French)/supportJapan:Freescale Semiconductor Japan Ltd. HeadquartersARCO Tower 15F1-8-1, Shimo-Meguro, Meguro-kuT okyo 153-0064Japan0120 191014 or+81 3 5437 9125support.japan@Asia/Pacific:Freescale Semiconductor China Ltd. Exchange Building 23FNo. 118 Jianguo RoadChaoyang DistrictBeijing 100022China+86 10 5879 8000@For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800 441-2447 or+1-303-675-2140Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @ Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. CoreNet, QorIQ, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and word marks and the Power and logos and related marks are trademarks and service marks licensed by .© 2010 Freescale Semiconductor, Inc.。

DDR3设计总结

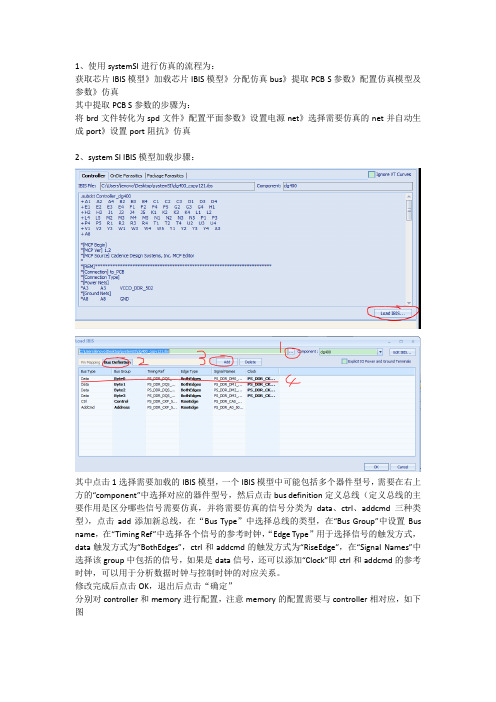

DDR3设计规范总结PCB Layout在实际的PCB设计时,考虑到SI、EMC的要求,往往有很多的折中方案。

通常,需要优先考虑对于那些对信号的完整性要求比较高的。

设计PCB 时,当考虑一下的一些相关因素,那么对于设计PCB来说可靠性就会更高。

1. 首先,要在相关的EDA工具(Cadance-Allegro)里要设置好里设置好拓扑结构和相关约束。

2. 将BGA引脚突围,将ADDR/CMD/CNTRL引脚布置在DQ/DQS/DM字节组的中间,由于所有这些分组操作,为了尽可能少的信号交叉,一些独立的管脚也许会被交换到其它区域布线。

3. 由串扰仿真的结果可知,尽量减少短线(stubs)长度。

通常,短线(stubs)是可以被削减的,但不是所有的管脚都做得到的。

在BGA焊盘和存储器焊盘之间也许只需要两段的走线就可以实现了,但是此走线必须要很细,那么就提高了PCB的制作成本,而且,不是所有的走线都只需要两段的,除非使用微小的过孔和盘中孔的技术。

最终,考虑到信号完整性的容差和成本,可能选择折中的方案。

4. 将Vref的去耦电容靠近Vref管脚摆放;Vtt的去耦电容摆放在最远的一个SDRAM外端;VDD的去耦电容需要靠近器件摆放。

小电容值的去耦电容需要更靠近器件摆放。

正确的去耦设计中,并不是所有的去耦电容都是靠近器件摆放的。

所有的去耦电容的管脚都需要扇出后走线,这样可以减少阻抗,通常,两端段的扇出走线会垂直于电容布线。

5. 当切换平面层时,尽量做到长度匹配和加入一些地过孔,这些事先应该在EDA工具里进行很好的仿真。

通常,在时域分析来看,差分线里的两根线的要做到延时匹配,保证其误差在5mil,而其它的信号要做到10mil。

4、从上所知,当频率越来越高,则对DDR信号处理要求越来越严格,所以我们统一按最严格的要求规则处理DDR信号:现阶段所面对的DDR目前大都属于DDR3类型,也有少许DDR4类型的,将来会面对更多 DDR4、 DDR5的产品我们目前比较常见的是 UDIMM 和 SODIMM ,因市场定位不一样,所以会有形状大小的区别。

DDR3DDR4DDR5设计和仿真流程

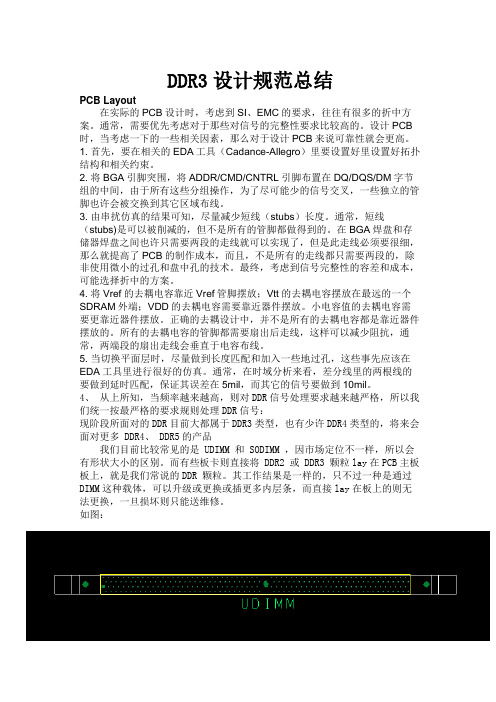

DDR3DDR4DDR5设计和仿真流程这个功能是ADS2019 update1里面才具有的功能。

小编非常喜欢这个功能,因为这个功能把仿真软件和测试设备的优势结合在了一起。

通过仿真发现和避免一些设计的问题。

Keysight发布了ADS2019U1版本的新功能memory designer。

新功能使开发人员能够轻松地完成DDR仿真所需的设置,并将仿真数据进行一致性测试分析, 从而减少了完成产品开发工作所需的时间。

1.DDR的设计挑战我们通过以下案例来看一个常规的DDR 仿真需要完成哪些设置:这是一款Xilinx的FPGAdemo板设计。

在本案例中, 所有4颗DRAM 都直接焊接在 PCB 上。

假定我们需要仿真每个DRAM上两字节通道 (dq0-dq15 和 dqs0-dqs1) 的写入周期。

仿真中还包括两条地址线 (a0 和 a1) 和一个时钟信号 (ck0)。

地址和时钟信号连接所有四个DRAM。

要完成这样的仿真,按照常规的流程,我们需要通过电磁场仿真器抽取PCB上以上所有网络的频域模型。

如果考虑电源分配网络对信号质量的影响,那在抽取时也应包含电源与地平面的频域模型。

这样,需要抽取的PCB网络端口数超过170个。

抽取完成后,设计者需要设置主控芯片和DRAM 芯片模型参数。

这些芯片模型一般来自芯片厂家的IBIS文件。

仿真中用到的每个芯片管脚都需要从模型文件中选出并进行相应配置。

这些必要的配置包括封装参数,子模型选择,发送端数据速率及码型,IBIS corner等。

在很多设计中,设计者还需要对芯片参数进行优化扫描,以获取最优的参数组合。

芯片模型设置完成后,下一步是将芯片管脚与抽取的PCB 模型端口进行连接。

在端口数目非常多时,逐个连接每个端口会是一个非常繁琐的过程,并且容易出错。

连接完成的仿真电路图如下图所示:电路连接完成后,还需设置需要的测量项。

DDR3包括之前的规范要求的测量项主要是电平和时序相关的测量。

经典DDR3PCB设计指导

经典DDR3PCB设计指导DDR3(Double Data Rate 3)是一种高速、大容量的随机存取存储器(RAM)技术,被广泛应用于各种计算机系统中。

在设计DDR3 PCB时,需要考虑信号完整性、EMI、布局、电源管理等因素,以确保系统的稳定性和性能优化。

以下是经典的DDR3PCB设计指导:1.保持信号完整性:-使用合适的信号走线宽度和间距,根据DDR3规范进行引脚布局和布线。

-控制信号的线长匹配,特别是对于时钟和命令/控制信号,通过控制线长来减小延迟。

-使用差分对来传输数据和时钟信号,并保持差分对长度相等,以最小化信号的失真和串扰。

2.使用层次布局:-使用多层PCB设计,将信号和电源/地线分开布局在不同的层次上,以减少干扰和串扰。

-高速信号层应该位于内层或表层以提高信号完整性,电源/地线可以位于内层。

3.地线规划:-根据信号引脚布局的特性,在有需要的地方增加避雷阻抗到地线。

-在信号回流点上使用地孔,以确保地线的连续性和稳定性。

-用足够的地区域保持良好的接地电流路径,以防止信号引脚之间的环形回流。

4.电源管理:-确保DDR3模块的电源电压稳定性,以避免信号和时序问题。

-确保电源管脚的降压滤波电容足够,以提供稳定的电源。

-使用布线良好的电源平面,以减少噪声和电流环路。

5.EMI控制:-在高速信号线周围添加地层和电源层,以提供屏蔽和隔离。

-使用过滤电容和磁珠来抑制电磁干扰。

-使用有源和被动的EMI抑制技术,如电磁屏蔽罩和衰减器。

6.综合考虑布局:-在布局时考虑信号走线和连接器的位置,以便在PCB上布线并连接到其他组件。

-将信号线走向控制在最短的长度,以最小化时延和损耗。

-尽量避免信号线的交叉和平行布线,以减小串扰和信号失真。

-对于高速和敏感信号,使用较短的连接线和更紧密的布局。

综上所述,经典的DDR3PCB设计指导涵盖了信号完整性、EMI控制、布局和电源管理等方面的要点。

通过遵循这些指导原则,可以最大程度地提高DDR3系统的稳定性和性能优化。

DDR3的相关设计规范

DDR3的相关设计规范DDR3是一种常见的内存技术,广泛用于计算机系统中。

在使用DDR3内存时,必须遵循一系列的设计规范,以确保系统稳定性和性能。

以下是关于DDR3的相关设计规范的一些重要内容。

一、电气特性:1.电压要求:DDR3的标准电压为1.5V,但也支持1.35V的低电压操作。

设计时必须保证提供准确的电压并控制其稳定性。

2.时钟频率:DDR3支持不同的时钟频率,包括800、1066、1333、1600等。

设计中需要根据具体需求选择合适的频率,并确保时钟信号的完整性。

3. 数据传输速率:DDR3的数据传输速率通常以MBps(兆字节每秒)为单位。

设计中需要考虑数据传输的稳定性和效率。

二、时序特性:1.存取延迟:DDR3内存的存取延迟包括列地址延迟(CL)和行地址延迟(RL),设计时需要正确配置这些延迟参数,以确保数据传输的准确性和高效性。

2.刷新周期:DDR3内存需要定期进行刷新操作,以保持存储数据的完整性。

设计中需要合理配置刷新周期,以满足DDR3内存的要求。

三、布局和信号完整性:1.PCB布局:DDR3内存的设计需要合理布局PCB,包括安排存储器芯片和其他电路元件的位置、规划数据和时钟信号的传输线路等。

良好的PCB布局可以有效减少信号干扰和传输延迟,提高系统性能。

2.连接器和插槽设计:DDR3内存的连接器和插槽设计也需要满足相关规范,以确保良好的接触和信号传输。

四、时序分析和调整:1.检查时序完整性:在DDR3设计中,需要进行时序分析以确保各个信号的时序关系。

通过综合考虑时钟、数据和控制信号,可以避免时序冲突,提高系统性能。

2.时序调整:如果时序分析发现了冲突或不稳定的信号,可以通过调整内存控制器或相关参数来解决。

时序调整需要综合考虑电气特性和时序要求,以确保稳定的数据传输。

总结起来,DDR3内存的设计规范涉及到电气特性、时序特性、布局和信号完整性等多个方面。

在设计时,必须严格遵守这些规范,以确保DDR3内存的稳定性和性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本文主要使用时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计。

1 概述当今计算机系统DDR3存储器技术已得到广泛应用,数据传输率一再被提升,现已高达1866Mbps。

在这种高速总线条件下,要保证数据传输质量的可靠性和满足并行总线的时序要求,对设计实现提出了极大的挑战。

本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。

2 DDR3介绍DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。

它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技术,明显提高了存储带宽;其工作电压为1.5V,保证相同频率下功耗更低。

DDR3接口设计实现比较困难,它采取了特有的Fly-by拓扑结构,用“Write leveling”技术来控制器件内部偏移时序等有效措施。

虽然在保证设计实现和信号的完整性起到一定作用,但要实现高频率高带宽的存储系统还不全面,需要进行仿真分析才能保证设计实现和信号质量的完整性。

3 仿真分析对DDR3进行仿真分析是以结合项目进行具体说明:选用PowerPC 64位双核CPU 模块,该模块采用Micron公司的MT41J256M16HA—125IT为存储器。

Freescale 公司P5020为处理器进行分析,模块配置内存总线数据传输率为1333MT/s,仿真频率为666MHz。

3.1仿真前准备在分析前需根据DDR3的阻抗与印制板厂商沟通确认其PCB的叠层结构。

在高速传输中确保传输线性能良好的关键是特性阻抗连续,确定高速PCB信号线的阻抗控制在一定的范围内,使印制板成为“可控阻抗板”,这是仿真分析的基础。

DDR3总线单线阻抗为50Ω,差分线阻抗为100Ω。

设置分析网络终端的电压值;对分析的器件包括无源器件分配模型;确定器件类属性;确保器件引脚属性(输入\输出、电源\地等)……3.2电路前仿真分析前仿真分析的内容主要是在PCB设计之前对电路设计的优化包括降低信号反射、过冲,确定匹配电阻的大小、走线阻抗等,通过对无源器件的各种配置分析选取出最适合的参数配置。

图1:时钟线的拓扑结构(1)DDR3总线的差分时钟分析众所周知,在差分传输中,所有信息都是由差模信号来传送的,而共模信号会辐射能量并能显著增加EMI,因此保证差分信号的质量十分重要,应使共模信号的产生降到最低。

在对差分时钟分析时不仅要关注其本身的信号质量,由于其它信号都是以差分时钟的来采样数据,因此还需关注其单调性、过冲值等。

本例中差分时钟的fly—by拓扑结构与地址总线一样为串联方式,如图l对处理器P5020驱动4个DDR3内存芯片的时钟拓扑结构,在终端进行简单的电阻匹配,在PCB板上差分走线后,进行反射分析发现接收端反射波形上下过冲较大。

在处理器输出端选用正确的下拉匹配电阻,虽电压幅值略有减少,但上下过冲明显减少消除了反射干扰,即减少了差分线的共模分量。

对比分析结果如图2。

图2:接收端DDR3的反射波形(2)验证驱动能力和ODT选项DDR3内存总线数据信号的驱动能力分为FULL和HALF两种模式,内部终端电阻(ODT)选择也有0Ω、20Ω、30Ω、40Ω、60Ω、120Ω选项,它们分别对应不同的模型用于控制信号反射的影响。

为提高信号质量、降低功耗,可通过分析不同模式选取正确的参数模型。

取数据总线对不同的ODT选项进行分析。

图3是在不同ODT设置进行分析数据信号形成的眼图波形,从图中可以看出:ODT阻抗越高,在相同驱动激励和走线等情况下转换率越高,幅度越大;在选择ODT=60Ω,其接收波形平缓信号质量最好,无明显抖动和过冲,抖动最小。

图3:数据信号眼图波形通常串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰。

它生成前向串扰与后向串扰,其对信号波形主要影响在幅度和边沿上面。

从DDR3数据总线提取3根相邻线,中间一根为被攻击网络,周围2根为攻击网络,采用3线模型进行分析,如下图4走线排列,其受害线为中间走线保持低电平,两边的为攻击线,采用128位伪随机码,根据走线的不同线宽和线间距对其进行串扰分析,看其分析结果如下表1。

图4:走线剖面图表1 串扰分析结果从表1可看出间距越大串扰影响越小,这里我们遵循的3W原则即走线边沿间距S是线宽W的3倍将大大减少串扰的影响。

但间距增大将牺牲布线空间,因此需综合考虑使在有限的空间中布线最优化。

3.3 时序分析DDR3是并行总线,其时序属源同步系统,在满足信号质量的前提下,也必须满足时序要求。

对于源同步时钟,驱动芯片的数据和时钟信号由内部电路提供即数据和时钟并行传输。

DDR3对不同的时序关系采用分组设计,其时序关系如表2。

表2 时序分组关系源同步时序计算公式:Tsetup_margin=Tvb—Tsetup—TskewThold_margin=Tva—Thold—Tskew公式中:Tsetup margin\Thold_margin:建立时间余量\保持时间余量Tvb\Tva:驱动端的建立时间和保持时间,Tsetup\Thold接收端的建立时间和保持时间Tskew:指数据、地址信号参考时钟引起的偏移。

其中Tvb\Tva,Tsetup\Th01d参数值都是能从器件手册中获取,关键是数据与选通信号飞行时间的时序偏移(skew),包含驱动端输出的偏移和在PCB板上的走线长度的偏移,需通过时序仿真非理想随机码进行分析计算得出。

以DDR3数据读写操作为例,根据下表芯片资料中的时序参数进行静态时序裕量的计算,获得PCB设计的时序控制规则。

表3 仿真所需要的时序参数(数据率:1333MHz)控制器:写操作:Tsetup_margin=0.25—0.03=0.22nsThold_margin=0.25-0.065=0.185ns读操作:Tsetup_margin = Thold_margin=(0.38*1.5-0.125)/2 - 0.125=97.5ps上述计算值是理论上的时序余量,其实源同步时序除本身芯片自身固有特性所带来的延时外还受其他因素的影响,都属于偏移范围,主要包括:(1)高速总线造成的信号完整性问题如串扰、同步开关噪声、码间干扰(ISI)等影响,需通过信号仿真分析来估算。

(2)高速总线互连所产生的时序偏斜:主要是信号总线互连链路中的布线误差,整个链路含器件封装内部走线、pcb板上走线和走线过孔等产生的时序偏差,可通过等长布线来控制其时序偏斜。

对8位数据总线DQ进行分析,选取一根数据线为受害线,其余数据线为反向伪随机码,条件设为最快驱动,在此最坏情况进行综合仿真,查看其受扰线的波形情况。

比较图5、图6后可看出此数据线受到各方面的因素综合影响,使波形眼图中的眼高和眼宽都相应减小,导致数据总线时序裕量大大减少。

上述时序裕量需减去此值再考虑其他噪声因素,结合经验留些时序余量后,就可把时序余量转换成PCB设计时的布线长度约束(约6in/ns)。

图5:DO数据总线理想波形图6:DQ数据总线最坏情况下的实际波形4 PCB设计4.1设计规则约束(1)等长约束采用分组等长方式,分组如下:数据线与DQS、DM信号组:64位数据线按8位一组,每组分别对应其各自的DQS 和DM信号;由于数据时序余量最小,组内严格控制延时,以对应的DQS为基准,等长精度在±10mil。

地址线、控制线、时钟线组:需等长控制,地址线与控制线各分支的误差±20mil,它们与时钟线误差在±100mil,差分时钟线之间±5rail。

(2)间距约束DDR3同组线间的间距保持在2倍线宽;不同组类线的间距保持在3倍线宽;DDR3线与其他jBDDR3线之间的间距应大于50mil,用于串扰控制。

(3)线宽约束根据传输线阻抗要求和印制板叠层结构计算走线线宽,设置走线线宽规则,保证阻抗的一致性。

4.2 布线技巧同组内总线尽量同层走线,时钟线与地层相邻;尽量少用过孔,如用需组内过孔数相同,保证其一致性;相邻信号走线需交叉,避免长距离的重叠走线,如相邻层间距足够大,可适当降低要求;走线避免采用直角应用45。

斜线或圆弧角走线;尽量采用3W原则走线;与电源层相邻的信号层中的高速走线应避免跨电源\地平面;电源层比地层内缩20H(H:电源层与地层的介质厚度);不允许有孤立铜的存在。

5 PCB板后仿验证DDR3的PCB设计结束后进行后仿分析,用以对前面的仿真分析进行验证。

PCB 板后仿主要是对DDR3信号质量和时序关系进行分析。

5.1 DDR3的差分时钟验证DDR3差分时钟在PCB布线后对其后仿真分析,抽取一对实际时钟走线对所走链路进行分析其波形如下图7:其单调性和上下过冲都满足要求。

图7:差分时钟PCB走线波形图8数据总线写时序5.2 DDR3的时序验证对于布线后的时序验证也是十分重要的环节。

在确定好同步信号组及对应的选通信号后利用Cadence软件的BUS setup功能进行综合分析,位数据总线及相应的DQS信号,设定时钟频率666MHz,设定相应ibis模型,加入随机码流,最终进行分析后可通过测量得到时序参数可计算时序裕量,验证PCB布线是否满足相关的时序关系。

分析结果见图8。

图8:数据总线写时序从上图8可测量出数据总线的建立时间和保持时间,根据DDR3数据相应时序进行静态时序计算,再综合考虑其余因素对时序的影响来估算包括其PCB走线长度引起的偏移等,满足其DDR3接收端的建立时间和保持时间的时序正确性,其它时序关系类似可通过此验证。

6 结束语通过上述Power PC模块的DDR3内存设计分析,了解高速信号反射、串扰、时序等因素对其设计的影响,其仿真分析成为增强计算机系统设计可靠性和稳定性的必要手段,为设计高速数字电路保驾护航。