PW183RB4800F01;中文规格书,Datasheet资料

2SC6082;中文规格书,Datasheet资料

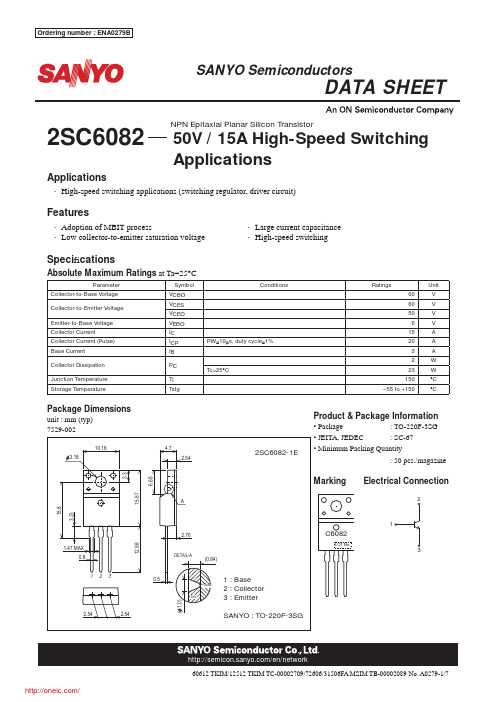

No. A0279-1/7Applications • High-speed switching applications (switching regulator, driver circuit)Features• Adoption of MBIT process•Large current capacitance • Low collector-to-emitter saturation voltage • High-speed switchingSpeci fi cationsAbsolute Maximum Ratingsat Ta=25°CParameterSymbol ConditionsRatingsUnit Collector-to-Base Voltage V CBO60V Collector-to-Emitter Voltage V CES 60V V CEO 50V Emitter-to-Base Voltage V EBO 6V Collector Current I C 15A Collector Current (Pulse)I CP PW ≤10μs, duty cycle ≤1%20A Base Current I B 3A Collector Dissipation P C 2W Tc=25°C23W Junction Temperature Tj 150°C Storage TemperatureTstg--55 to +150°CPackage Dimensionsunit : mm (typ)7529-00260612 TKIM/12512 TKIM TC-00002709/72606/31506FA MSIM TB-000020892SC6082NPN Epitaxial Planar Silicon Transistor50V / 15A High-Speed Switching ApplicationsProduct & Package Information• Package : TO-220F-3SG • JEITA, JEDEC : SC-67• Minimum Packing Quantity : 50 pcs./magazineMarkingElectrical ConnectionC6082LOT No.Electrical Characteristicsat Ta=25°CParameterSymbol ConditionsRatingsUnit mintypmaxCollector Cutoff Current I CBO V CB =40V , I E =0A 10μA Emitter Cutoff Current I EBO V EB =4V , I C =0A 10μADC Current Gain h FE 1V CE =2V , I C =330mA 200560h FE 2V CE =2V , I C =10A 50Gain-Bandwidth Product f T V CE =10V , I C=2A195MHz Output CapacitanceCob V CB =10V , f=1MHz 85pF Collector-to-Emitter Saturation Voltage V CE (sat)I C =7.5A, I B =375mA 200400mV Base-to-Emitter Saturation Voltage V BE (sat)I C =7.5A, I B =375mA 1.2V Collector-to-Base Breakdown Voltage V (BR)CBO I C =100μA, I E =0A 60V Collector-to-Emitter Breakdown Voltage V (BR)CES I C =100μA, R BE =0Ω60V V (BR)CEO I C =1mA, R BE =∞50V Emitter-to-Base Breakdown Voltage V (BR)EBO I E =100μA, I C =0A 6V Turn-On Time t on See speci fi ed Test Circuit52ns Storage Time t stg 560ns Fall Timet f37nsSwitching Time Test CircuitOrdering InformationDevicePackage Shippingmemo2SC6082-1ETO-220F-3SG50pcs./magazine Pb FreeCC I C =20I B1= --20I B2=5APW=20μsD.C.≤1%Collector-to-Emitter V oltage, V CE -- VC o l l e c t o r C u r r e n t , I C -- ACollector-to-Emitter V oltage, V CE -- VC o l l e c t o r C u r r e n t , I C -- AIT10574IT105751001000100.010.11.0100.010.11.010100100010100100010100100010Collector Current, I C -- AD C C u r r e n t G a i n , h F ECollector Current, I C-- AD C C u r r e n t G a i n , h F EBase-to-Emitter V oltage, V BE -- VC o l l e c t o r C u r r e n t , I C -- ACollector-to-Base V oltage, V CB -- VO u t p u t C a p a c i t a n c e , C o b -- p FCollector Current, I C -- AC o l l e c t o r -t o -E m i t t e r S a t u r a t i o n V o l t a g e , V C E (s a t ) -- VG a i n -B a n d w i d t h P r o d u c t , f T -- M H zCollector Current, I C -- AIT10576IT10577IT10578IT10581IT105800.10.01IT10579C o l l e c t o r -t o -E m i t t e r S a t u r a t i o n V o l t a g e , V C E (s a t ) -- VCollector Current, I C -- ACollector Current, I C -- AB a s e -t o -E m i t t e r S a t u r a t i o n V o l t a g e , V B E (s a t ) -- VIT10582321.02375IT105830.10.01Collector-to-Emitter V oltage, V CE -- VC o l l e c t o r C u r r e n t , I C -- AAmbient Temperature, Ta -- °CC o l l e c t o rD i s s i p a t i o n , P C -- WCase Temperature, Tc -- °CC o l l e c t o rD i s s i p a t i o n , P C -- WIT167110.010.11.010100IT16709IT16710Magazine Specifi cation 2SC6082-1EOutline Drawing2SC6082-1EMass (g)Unit1.8mm* For referenceThis catalog provides information as of June, 2012. Specifi cations and information herein are subject to change without notice.分销商库存信息: ONSEMI2SC6082。

RB717FT106;中文规格书,Datasheet资料

Diodes

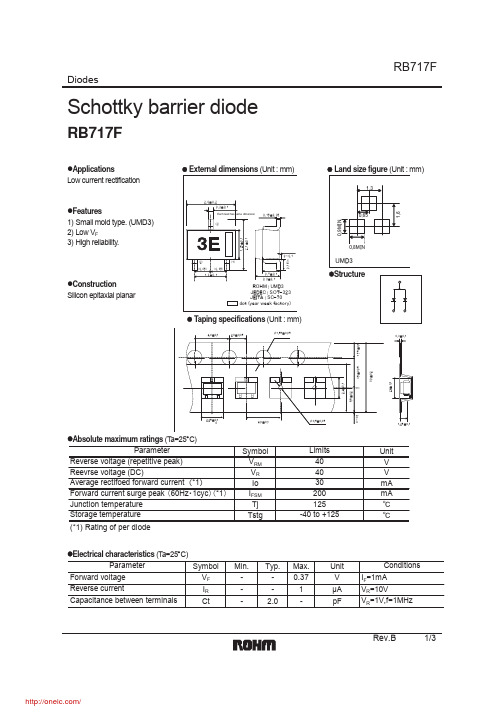

Schottky barrier diode

RB717F

zApplications Low current rectification z External dimensions (Unit : mm) z Land size figure (Unit : mm)

㪈㪅㪊

r

㪬㪤㪛㪊

r

zStructure

zConstruction Silicon epitaxial planar

㩷

㪩㪦㪟㪤㩷㪑㩷㪬㪤㪛㪊 㪡㪜㪛㪜㪚㩷㪑㩷㪪㪦㪫㪄㪊㪉㪊 㪡㪜㪠㪫㪘㩷㪑㩷㪪㪚㪄㪎㪇 㪻㫆㫋㩷㩿㫐㪼㪸㫉㩷㫎㪼㪼㫂㩷㪽㪸㪺㫋㫆㫉㫐㪀

z Taping specifications (Unit : mm)

㪈㪉㪌

㪇

㪉㪌

㪌㪇

㪎㪌

㪈㪇㪇

㪈㪉㪌

㪚㪘㪪㪜㩷㪫㪜㪤㪧㪘㪩㪘㪫㪬㪩㪜㪑㪫㪺㩿㷄㪀 㪛㪼㫉㪸㫋㫀㫅㪾㩷㪚㫌㫉㫍㪼䍼㩿㪠㫆㪄㪫㪺㪀

Rev.B

3/3

/

Appendix

Notes

No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD. The contents described herein are subject to change without notice. The specifications for the product described in this document are for reference only. Upon actual use, therefore, please request that specifications to be separately delivered. Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set. Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices. Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, no express or implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by ROHM CO., LTD. is granted to any such buyer. Products listed in this document are no antiradiation design.

FMB2222A;中文规格书,Datasheet资料

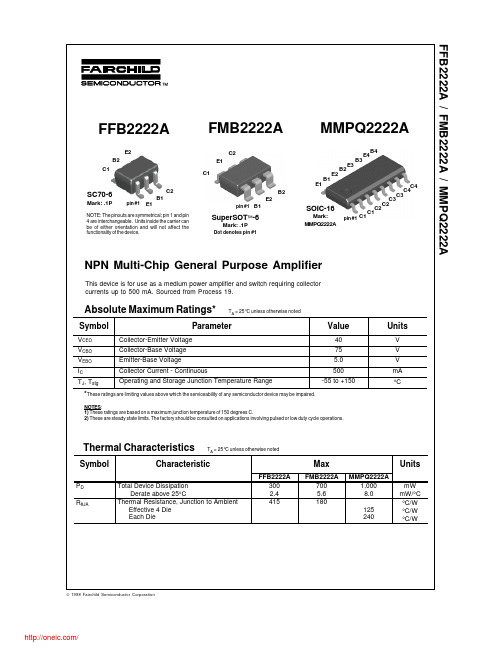

Thermal Characteristics

Symbol

PD RθJA

TA = 25°C unless otherwise noted

Characteristic

Total Device Dissipation Derate above 25°C Thermal Resistance, Junction to Ambient Effective 4 Die Each Die FFB2222A 300 2.4 415

*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

Spice Model

NPN (Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

300

VCE(sat) VBE(sat)

Collector-Emitter Saturation Voltage* Base-Emitter Saturation Voltage*

0.3 1.0 1.2 2.0

V V V V

SMALL SIGNAL CHARACTERISTICS

fT Cobo Cibo NF Current Gain - Bandwidth Product Output Capacitance Input Capacitance Noise Figure IC = 20 mA, VCE = 20 V, f = 100 MHz VCB = 10 V, IE = 0, f = 100 kHz VEB = 0.5 V, IC = 0, f = 100 kHz IC = 100 µA, VCE = 10 V, RS = 1.0 kΩ, f = 1.0 kHz 300 4.0 20 2.0 MHz pF pF dB

3342-54;3342-56;3342-07;中文规格书,Datasheet资料

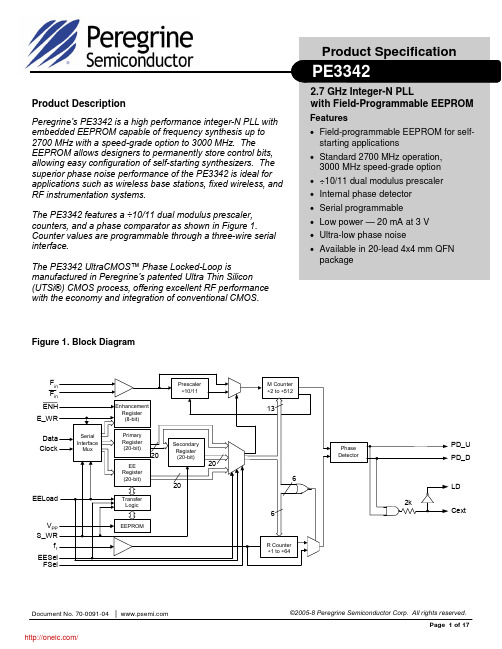

Document No. 70-0091-04 │ ©2005-8 Peregrine Semiconductor Corp. All rights reserved.(UTSi®) CMOS process, offering excellent RF performance with the economy and integration of conventional CMOS.Figure 1. Block DiagramPD_U PD_DLDCextPE3342 Product SpecificationProduct SpecificationPE3342Document No. 70-0091-04 │ ©2005-8 Peregrine Semiconductor Corp. All rights reserved.Table 4. Operating RangesTable 3. Absolute Maximum RatingsSymbol Parameter/Conditions Min Max UnitsV DD Supply voltage –0.3 +4.0 V V I Voltage on any digital input–0.3 V DD +0.3 V T StgStorage temperature range–65+85°CSymbol Parameter/Conditions MinMax UnitsV DD Supply voltage 2.85 3.15 V T A Operatingambient temperature range-40 85 °CSymbol Parameter/Conditions Min Max UnitsV ESD ESD voltage human body model (Note 1)1000 V V ESD(V PP )ESD voltage human body model (Note 1)200VNote 1: Periodically sampled, not 100% tested. Tested per MIL-STD-883, M3015 C2Table 5. ESD RatingsElectrostatic Discharge (ESD) Precautions When handling this UltraCMOS™ device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the specified rating in Table 4. Latch-Up AvoidanceUnlike conventional CMOS devices, UltraCMOS™ devices are immune to latch-up.Exceeding absolute maximum ratings may cause permanent damage. Operation should berestricted to the limits in the Operating Ranges table. Operation between operating rangemaximum and absolute maximum for extended periods may reduce reliability.PE3342 Product SpecificationProduct SpecificationPE3342Document No. 70-0091-04 │©2005-8 Peregrine Semiconductor Corp. All rights reserved.Table 7. AC CharacteristicsV DD = 3.0 V, -40° C < T A < 85° C, unless otherwise specifiedSymbol ParameterConditions Min Max UnitsControl Interface and Registers (see Figure 4)f Clk Serial data clock frequency (Note 1)10MHz t ClkH Serial clock HIGH time 30 ns t ClkL Serial clock LOW time30 ns t DSU Data set-up time to Clock rising edge 10 ns t DHLD Data hold time after Clock rising edge 10 ns t PW S_WR pulse width30 ns t CWR Clock rising edge to S_WR rising edge 30 ns t CE Clock falling edge to E_WR transition 30 ns t WRC S_WR falling edge to Clock rising edge 30 ns t EC E_WR transition to Clock rising edge30nsEEPROM Erase/Write Programming (see Figures 5 & 6)t EESU EELoad rising edge to V PP rising edge 500 ns t EEPW V PP pulse width25 30 ms t VPPV PP pulse rise and fall times(Note 2) 1 µsMain Divider (Including Prescaler)F In Operating frequency300 2700 MHz F In Operating frequency Speed-grade option (Note 3) 300 3000 MHz P FInInput level rangeExternal AC coupling-55dBmMain Divider (Prescaler Bypassed)F In Operating frequency (Note 4)50 270 MHz P FInInput level rangeExternal AC coupling (Note 4)-55dBmReference Dividerf r Operating frequency(Note 5)100MHz P fr Reference input power (Note 4)Single ended input-2dBmPhase Detectorf cComparison frequency(Note 6)20MHzSSB Phase Noise (F in = 1.3 GHz, f r = 10 MHz, f c = 1.25 MHz, LBW = 70 kHz, V DD = 3.0 V, Temp = -40° C )100 Hz Offset -75 dBc/Hz1 kHz Offset-85dBc/HzNote 1: f Clk is verified during the functional pattern test. Serial programming sections of the functional pattern are clocked at 10 MHz to verify f Clkspecification.Note 2: Rise and fall times of the V PP programming voltage pulse must be greater than 1 µs.Note 3: The maximum frequency of operation can be extended to 3.0 GHz by ordering a special speed-grade option. Please refer to Table 14,Ordering Information, for ordering details.Note 4: CMOS logic levels can be used to drive F In input if DC coupled and used in Prescaler Bypass mode. Voltage input needs to be a minimumof 0.5 Vp-p. For optimum phase noise performance, the reference input falling edge rate should be faster than 80 mV/ns. No minimum frequency limit exists when operated in this mode.Note 5: CMOS logic levels can be used to drive reference input if DC coupled. Voltage input needs to be a minimum of 0.5 Vp-p. For optimumphase noise performance, the reference input falling edge rate should be faster than 80 mV/ns.Note 6: Parameter is guaranteed through characterization only and is not tested.PE3342 Product SpecificationProduct SpecificationPE3342Document No. 70-0091-04 │ ©2005-8 Peregrine Semiconductor Corp. All rights reserved.Lock Detect OutputA lock detect signal is provided at pin LD, via the pin C EXT (see Figure 1). C EXT is the logical “NAND” of PD_U and PD_D waveforms, driven through a series 2k ohm resistor. When the loop is locked, this output will be HIGH with narrow pulses LOW. Connecting C EXT to an external shunt capacitor provides integration of this signal.The C EXT signal is sent to the LD pin through an internal inverting comparator with an open drain output. Thus LD is an “AND” function of PD_U and PD_D .Serial Data PortThe Serial Data Port allows control data to beentered into the device. This data can be directed into one of three registers: the Enhancementregister, the Primary register, and the EE register. Table 7 defines the control line settings required to select one of these destinations.Input data presented on pin 5 (Data) is clocked serially into the designated register on the rising edge of Clock. Data is always loaded LSB (B 0) first into the receiving register. Figure 4 defines the timing requirements for this process .Table 8. Serial InterfaceS_WR E_WR EELoadRegister Loaded0 0 0 Primary Register 0 1 0 Enhancement Register 0X1EE RegisterFigure 4. Serial Interface Timing DiagramE_WREELoadDataClockS_WRPE3342 Product SpecificationProduct SpecificationPE3342Document No. 70-0091-04 │ ©2005-8 Peregrine Semiconductor Corp. All rights reserved.Enhancement RegisterThe Enhancement Register is a buffered serial shift register, loaded from the Serial Data Port. It activates special test and operating modes in the PLL. The bit assignments for these modes are shown in Table 11.The functions of these Enhancement Register bits are shown in Table 12. A function becomes active when its corresponding bit is set HIGH. Note that bits 1, 2, 5, and 6 direct various data to the Dout pin, and for valid operation no more than one should be set HIGH simultaneously .The Enhancement Register is buffered to prevent inadvertent control changes during serial loading. Data that has been loaded into the register is cap-tured in the buffer and made available to the PLL on the falling edge of E_WR.A separate control line is provided to enable and disable the Enhancement mode. Functions are enabled by taking the ENH control line LOW. Note: The enhancement register bit values are unknown during power up. To avoid enabling the enhancement mode during power up, set the Enh pin high (“1”) until the enhancement register bit values are programmed to a known state.Table 12. Enhancement Register Bit AssignmentsReservedEE Register Outputf p outputPower downCounter loadMSEL outputf c outputReservedB 0B 1B 2B 3B 4B 5B 6B 7Table 13. Enhancement Register FunctionsBit FunctionDescriptionBit 0 Reserved Program to 0Bit 1 EE Register OutputAllows the contents of the EE Register to be serially shifted out Dout, LSB (B 0) first. Data is shifted on rising edge of Clock. Bit 2 f p output Provides the M counter output at Dout.Bit 3 Power down Powers down all functions except programming interface. Bit 4 Counter load Immediate and continuous load of counter programming.Bit 5 MSEL output Provides the internal dual modulus prescaler modulus select (MSEL) at Dout. Bit 6 f c output Provides the R counter output at Dout. Bit 7ReservedProgram to 0PE3342 Product Specification分销商库存信息:PSC3342-543342-563342-07。

VRF150;中文规格书,Datasheet资料

The VRF150 is a gold-metallized silicon n-channel RF power transistor de-signed for broadband commercial and military applications requiring high power and gain without compromising reliability, ruggedness, or inter-modulationdistortion.FEATURES• Improved Ruggedness V (BR)DSS = 170V• 150W with 11dB Typical Gain @ 150MHz, 50V• 150W with 18dB Typical Gain @ 30MHz, 50V • Excellent Stability & Low IMD • Common Source Con fi guration • Available in Matched Pairs• 30:1 Load VSWR Capability at Speci fi ed Operating Conditions • Nitride Passivated• Refractory Gold Metallization• High Voltage Replacement for MRF150• RoHS CompliantSymbol ParameterVRF150(MP)Unit V DSS Drain-Source Voltage170V I D Continuous Drain Current @ T C = 25°C 16A V GS Gate-Source Voltage±40V P D Total Device dissipation @ T C = 25°C 300W T STG Storage Temperature Range -65 to 150°CT JOperating Junction Temperature200Maximum Ratings All Ratings: T C =25°C unless otherwise speci fi edStatic Electrical CharacteristicsSymbol ParameterMin Typ MaxUnit V (BR)DSS Drain-Source Breakdown Voltage (V GS = 0V, I D = 100mA)170180V V DS(ON)On State Drain Voltage (I D(ON) = 10A, V GS = 10V) 2.03.0I DSS Zero Gate Voltage Drain Current (V DS = 100V, V GS = 0V) 1.0mA I GSS Gate-Source Leakage Current (V DS = ±20V, V DS = 0V) 1.0μA g fs Forward Transconductance (V DS = 10V, I D = 5A)4.5mhos V GS(TH)Gate Threshold Voltage (V DS = 10V, I D = 100mA)2.93.64.4VMicrosemi Website - 050-4936 R e v F 9-201Thermal CharacteristicsSymbol CharacteristicMin TypMax Unit R θJCJunction to Case Thermal Resistance0.60°C/WCAUTION:These Devices are Sensitive to Electrostatic Discharge. Proper Handling Procedures Should Be Followed./VRF150(MP)Dynamic CharacteristicsSymbol Parameter Test ConditionsMinTyp MaxUnitC ISS Input Capacitance V GS = 0V 420pFC oss Output CapacitanceV DS = 50V 210C rssReverse Transfer Capacitancef = 1MHz35Class A CharacteristicsSymbol Test Conditions Min Typ Max UnitG PS V DD = 50V, I DQ = 3A, P out = 150W PEP , f1 = 30MHz, f2 = 30.001MHz20dBIMD (d3)-50IMD (d9-d13)-75Functional CharacteristicsSymbol ParameterMinTyp Max Unit G PS f 1 = 30MHz, f 2 = 30.001MHz, V DD = 50V, I DQ = 250mA, P out = 150W PEP 18 dB G PS f = 150MHz, V DD = 50V, I DQ = 250mA, P out = 150W11ηD f 1 = 30MHz, f 2 = 30.001MHz, V DD = 50V, I DQ = 250mA, P out = 150W PEP 50%IMD (d3)f 1 = 30MHz, f 2 = 30.001MHz, V DD = 50V, I DQ = 250mA, P out = 150W PEP 1-32dBcIMD (d11)f 1 = 30MHz, f 2 = 30.001MHz, V DD = 50V, I DQ = 250mA, P out = 150W PEP -60ψf 1 = 30MHz, f 2 = 30.001MHz, V DD = 50V, I DQ = 250mA, P out = 150W PEP 30:1VSWR - All Phase AnglesNo Degradation in Output Power1. To MIL-STD-1311 Version A, test method 2204B, Two Tone, Reference Each ToneMicrosemi reserves the right to change, without notice, the speci fi cations and information contained herein.050-4936 R e v F 9-20101110201 10 100 250101520253035101520253035110100V DS(ON ), DRAIN-TO-SOURCE VOLTAGE (V) FIGURE 1, Output CharacteristicsI D , D R A I N C U R R E N T (A )I D , D R A I N C U R R E N T (A )VDS , DRAIN-TO-SOURCE VOLTAGE (V) FIGURE 3, Capacitance vs Drain-to-Source VoltageC , C A P A C I T A N C E (p F )V DS , DRAIN-TO-SOURCE VOLTAGE (V) FIGURE 4, Forward Safe Operating AreaI D , D R A I N C U R R E N T (V )V GS , GATE-TO-SOURCE VOLTAGE (V) FIGURE 2, Transfer CharacteristicsTypical Performance Curves/−50−45−40−35−30−25−20VRF150(MP)50-4936 R e v F 9-20100.10.20.30.40.50.60.710-510-410-3 10-2 10 1.0Z θJ C , T H E R M A L I M P E D A N C E (°C /W )RECTANGULAR PULSE DURATION (seconds)Figure 5. Maximum Effective Transient Thermal Impedance Junction-to-Case vs Pulse Duration050100150200250300P out , OUTPUT POWER (WATTS PEP)Figure 6. IMD versus P OUTI M D , I N T E R M O D U L A T I O N D I S T O R T I O N (d B )O U T P U T P O W E R (W P E P )P out , INPUT POWER (WATTS PEP)Figure 7. P OUT versus P INTypical Performance Curves/050-4936 R e v F 9-2010RFC1RFC1, C2, C8 -- Arco 463 or equivalent C3 -- 25pF, Unelco C4 -- 0.1uF, CeramicC5 -- 1.0 uF, 15 WV Tantalum C6 -- 250pF, Unelco J101C7-- 25pF, Unelco J101C9 -- Arco 262 or equivalent C10 -- 0.05uF, CeramicC11 -- 15uF, 60WV Electrolytic+ 50VDBias 0-12VRF RF OutputC2, C5, C6 - C9 -- 0.1uF SMT C3 -- 200pF ATC 700C C4 -- 15pF, ATC 700CC10 -- 10uF, 100V ElectrolyticR1, R2 -- 51 7, 1 W Carbon R3 -- 3.3 7, 1 W Carbon T1 -- 9:1 Transformer T2 -- 1:9 Transformer30 MHz test Circuit150 MHz test Circuit/050-4936 R e v F 9-2010.5” SOE Package OutlineAll Dimensions are ± .005DIMINCHES MILLIMETERS MIN MAX MIN MAX A 0.0960.99024.3925.14B0.4650.51011.8212.95C 0.2290.275 5.82 6.98D 0.2160.235 5.49 5.96E0.0840.110 2.14 2.79H0.1440.178 3.66 4.52J 0.0030.0070.080.17K 0.43511.0M45° NOM 45° NOM Q 0.1150.130 2.93 3.30R 0.2460.255 6.25 6.47U0.7200.73018.2918.54Microsemi’s products are covered by one or more of U.S. patents 4,895,810 5,045,903 5,089,434 5,182,234 5,019,522 5,262,336 6,503,786 5,256,5834,748,103 5,283,202 5,231,474 5,434,095 5,528,058 6,939,743, 7,352,045 5,283,201 5,801,417 5,648,283 7,196,634 6,664,594 7,157,886 6,939,743 7,342,262 and foreign patents. US and Foreign patents pending. All Rights Reserved.Adding MP at the end of P/N speci fi es a matched pair where V GS(TH) is matched between the two parts. V TH values are marked on the devices per the following table.Code Vth Range Code 2Vth Range A 2.900 - 2.975M 3.650 - 3.725B 2.975 - 3.050N 3.725 - 3.800C 3.050 - 3.125P 3.800 - 3.875D 3.125 - 3.200R 3.875 - 3.950E 3.200 - 3.275S 3.950 - 4.025F 3.275 - 3.350T 4.025 - 4.100G 3.350 - 3.425W 4.100 - 4.175H 3.425 - 3.500X 4.175 - 4.250J 3.500 - 3.575Y 4.250 - 4.325K3.575 - 3.650Z4.325 - 4.400V TH values are based on Microsemi measurements at datasheet conditions with an accuracy of 1.0%./分销商库存信息: MICROSEMIVRF150。

FAN4800A中文资料

FeaturesPin-to-Pin Compatible with ML4800 and FAN4800 and CM6800 and CM6800APWM Configurable for Current-mode orFeed-forward Voltage-Mode OperationInternally Synchronized Leading-Edge PFC and Trailing-Edge PWM in one ICLow Operating CurrentInnovative Switching-Charge Multiplier DividerAverage-Current-Mode for Input-Current Shaping PFC Over-Voltage and Under-Voltage Protections PFC Feedback Open-Loop ProtectionCycle-by-Cycle Current Limiting for PFC/PWMPower-on Sequence Control and Soft-StartBrownout ProtectionInterleaved PFC/PWM SwitchingFAN4801/1S/2/2L Improve Efficiency at Light Load f RTCT=4•f PFC=4•f PWM for FAN4800A andFAN4801/1Sf RTCT=4•f PFC=2•f PWM for FAN4800C andFAN4802/2LApplicationsDesktop PC Power SupplyInternet Server Power SupplyLCD TV, Monitor Power SupplyUPSBattery ChargerDC Motor Power SupplyMonitor Power Supply DescriptionThe highly integrated FAN4800A/C and FAN4801/1S/2/2L are specially designed for power supplies that consist of boost PFC and PWM. They require very few external components to achieve versatile protections / compensation. They are availablein 16-pin DIP and SOP packages.The PWM can be used in either current or voltage mode. In voltage mode, feed-forward from the PFC output bus can reduce the secondary output ripple. Compared with older productions, ML4800 and FAN4800, FAN4800A/C and FAN4801/1S/2/2L have lower operation current that save power consumption in external devices. FAN4800A/C and FAN4801/1S/2/2L have accurate 49.9% maximum duty of PWM that makes the hold-up time longer. Specifically, the brownout protection and PFC soft-start functions are notin ML4800 and FAN4800.To start evaluating FAN4800A/C, FAN4801/1S/2/2L for replacing existing FAN4800 and ML4800 boards, five things must be done before the fine-tuning procedure:1. Change R AC resister from the old value to a higherresister: between 6MΩ to 8MΩ.2. Change RT/CT pin from the existing values toR T=6.8KΩ and C T=1000pF to have f PFC=64KHz,f PWM=64KHz.3. VRMS pin needs to be 1.224V at V IN=85 V AC foruniversal input application from line input from85V AC to 270 V AC. Both poles for the V rms ofFAN4801/1S/2/2L don’t need to substantiallyslower than FAN4800; about 5 to 10 times.4. At full load, the average V EA needs to ~4.5V andthe ripple on the V EA needs to be less than 400mV.5. Soft-Start pin, the soft-start current has beenreduced to half from the FAN4800 capacitor. Related ResourcesFAN4800A/C, FAN4801/1S/2/2L — PFC/PWM Controller CombinationFAN4800AMY -40°C to +105°C Green 16-pin Small Out-Line Package (SOP) Tape & Reel FAN4800CMY -40°C to +105°C Green 16-pin Small Out-Line Package (SOP) Tape & ReelFAN4801NY -40°C to +105°C Green 16-pin Dual In-Line Package (DIP) Tube FAN4801SNY -40°C to +105°C Green 16-pin Dual In-Line Package (DIP) Tube FAN4802NY -40°C to +105°C Green 16-pin Dual In-Line Package (DIP)) Tube FAN4802LNY -40°C to +105°C Green 16-pin Dual In-Line Package (DIP)) Tube FAN4801MY -40°C to +105°C Green 16-pin Small Out-Line Package (SOP) Tape & Reel FAN4801SMY -40°C to +105°C Green 16-pin Small Out-Line Package (SOP) Tape & Reel FAN4802MY -40°C to +105°C Green 16-pin Small Out-Line Package (SOP) Tape & Reel FAN4802LMY-40°C to +105°CGreen16-pin Small Out-Line Package (SOP)Tape & ReelFor Fairchild’s definition of “green” Eco Status, please visit: /company/green/rohs_green.html .Part NumberPFC:PWM Frequency RatioBrown Out / InRange In / OutFAN4800ANY 1:1 1.05V / 1.90V N.A FAN4800AMY 1:1 1.05V / 1.90V N.A FAN4800CNY 1:2 1.05V / 1.90V N.A FAN4800CMY 1:2 1.05V / 1.90V N.A FAN4801NY 1:1 1.05V / 1.90V 1.95V / 2.45V FAN4801SNY 1:1 1.05V / 1.90V 2.80V / 3.35V FAN4802NY 1:2 1.05V / 1.90V 1.95V / 2.45V FAN4802LNY 1:2 0.90V / 1.65V 1.95V / 2.45V FAN4801MY 1:1 1.05V / 1.90V 1.95V / 2.45V FAN4801SMY 1:1 1.05V / 1.90V 2.80V / 3.35V FAN4802MY 1:2 1.05V / 1.90V 1.95V / 2.45V FAN4802LMY1:20.90V / 1.65V1.95V /2.45VPFC/PWM Controller CombinationIEA RAMPRT/CT FBPWM SS VRMS ISENSE IAC ILIMITGND OPWM OPFC VDD VREFFBPFC VEA FAN4800A/C FAN4801/1S/2/2LVDDVREFSecondaryFigure 1.Typical Application Current ModePFC/PWM Controller CombinationIEA RAMPRT/CT FBPWM SS VRMS ISENSE IAC ILIMITGND OPWM OPFC VDD VREFFBPFC VEA FAN4800A/C FAN4801/1S/2/2L VDDVREFSecondaryVREFFigure 2.Typical Application Voltage ModePFC/PWM Controller CombinationFigure 3. FAN4800A/C Function Block DiagramPFC/PWM Controller CombinationFigure 5. F – Fairchild logo Z – Plant codeX – 1 digit year code Y – 1 digit week codeTT – 2 digits die run codeT – Package type (N:DIP, M:SOP)P – Y: Green packageM – Manufacture flow codePFC/PWM Controller CombinationFigure 6. Pin Configuration (Top View )Pin DefinitionsPin #NameDescription1 IEAOutput of PFC Current Amplifier. The signal from this pin is compared with an internalsawtooth to determine the pulse width for PFC gate drive. 2 IACInput AC Current. For normal operation, this input provides current reference for the multiplier.The suggested maximum IAC is 100µA. 3 ISENSEPFC Current Sense. The non-inverting input of the PFC current amplifier and the output ofmultiplier and PFC ILIMIT comparator. 4 VRMS Line-Voltage Detection. Line voltage detection. The pin is used for PFC multiplier.5 SS PWM Soft-Start. During startup, the SS pin charges an external capacitor with a 10µA constant current source. The voltage on FBPWM is clamped by SS during startup. In the eventof a protection condition occurring and/or PWM disabled, the SS pin is quickly discharged. 6 FBPWM PWM Feedback Input. The control input for voltage-loop feedback of PWM stage. 7 RT/CT Oscillator RC Timing Connection. Oscillator timing node; timing set by R T and C T . 8 RAMPPWM RAMP Input. In current mode, this pin functions as the current sense input; when in voltage mode, it is the feed forward sense input from PFC output 380V (feedforward ramp). 9 ILIMIT Peak Current Limit Setting for PWM. The peak current limits setting for PWM. 10 GND Ground.11 OPWMPWM Gate Drive. The totem-pole output drive for PWM MOSFET. This pin is internally clamped under 15V to protect the MOSFET. 12 OPFCPFC Gate Drive. The totem pole output drive for PWM MOSFET. This pin is internally clampedunder 15V to protect the MOSFET. 13 VDDSupply. The power supply pin. The threshold voltages for startup and turn-off are 11V and9.3V, respectively. The operating current is lower than 10mA.FAN4800A/C, FAN4801/1S/2/2L — PFC/PWM Controller CombinationSymbol ParameterMin. Max. UnitV DD DC Supply Voltage30 V V H SS, FBPWM, RAMP, OPWM, OPFC -0.3 30.0 V V LIAC, VRMS, RT/CT, ILIMIT, FBPFC, VEA-0.3 7.0 V V VREF VREF 7.5 V V IEA IEA 0 V VREF +0.3 VV N ISENSE -5.0 0.7 V I AC Input AC Current 1 mA I REF VREF Output Current5 mA I PFC-OUT Peak PFC OUT Current, Source or Sink 0.5 A I PWM-OUT Peak PWM OUT Current, Source or Sink 0.5 A P D Power Dissipation T A < 50°C800mWDIP 80.80 °C/W R Θ j-a Thermal Resistance (Junction to Air) SOP 104.10 °C/WT J Operating Junction Temperature -40 +125 °C T STG Storage Temperature Range -55 +150 °C T L Lead Temperature (Soldering)+260 °C Human Body Model4.5 kV ESDElectrostatic Discharge Capability Charged Device Model1000VNotes:1. All voltage values, except differential voltage, are given with respect to GND pin.2. Stresses beyond those listed under “absolute maximum ratings “may cause permanent damage to the device.Recommended Operating ConditionsThe Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.Symbol Parameter Min. Typ. Max. UnitT AOperating Ambient Temperature-40+105°CPFC/PWM Controller CombinationOscillatorf OSC-RT/CT RT/CT FrequencyR T=6.8k Ω, C T=1000pF 240 256 268 kHz PFC & PWM Frequency606467f OSCFAN4800C,FAN4802/02L PWM FrequencyR T=6.8k Ω, C T=1000pF 120 128 134kHz f DV Voltage Stability 11V ≦ V DD ≦ 22V 2 % f DT Temperature Stability -40°C ~ +105°C2%f TVTotal Variation (PFC &PWM)(1)Line, Temperature 58 70 kHz f RV Ramp Voltage (1)Valley to Peak2.8VI Discharge Discharge Current V RAMP =0V, V RT/CT =2.5V 6.5 15.0 mAf RANGE Frequency Range (1)50 75 kHz t PFCD PFC Dead TimeR T=6.8k Ω, C T=1000pF400 600 800 nsVREFV VREF Reference Voltage I REF =0mA, C REF 0.1µF 7.4 7.5 7.6 V ΔV VREF1 Load Regulation ofReference Voltage C REF =0.1µF, I REF =0mA to 3.5mAV VDD =14V, Rise/Fall Time > 20µs 30 50 mV ΔV VREF2 Line Regulation of Reference Voltage C REF =0.1µF, V VDD =11V to 22V 25 mV ΔV VREF-DT (1)Temperature Stability -40°C ~ +105°C 0.4 0.5 % ΔV VREF-TV (1)Total Variation Line, Load, Temp 7.35 7.65 V ΔV VREF-LS(1)Long-Term Stability T J =125°C, 0 ~ 1000HRs 5 25 mV I REF-MAX . Maximum Current V VREF > 7.35V 5 mA I OS(1)Output Short Circuit25mAPFC OVP ComparatorV PFC-OVP Over-Voltage Protection 2.70 2.75 2.80 VPFC/PWM Controller Combination==V VEA-H Output High Voltage onV VEA5.8 6 V V VEA-LOutput Low Voltage on V VEA0.1 0.4 VCurrent Error Amplifier V ISENSEInput Voltage Range(ISENSE pin)(1)-1.5 0.7 V Gm I TransconductanceV NONINV =V INV , V IEA =3.75V 78 88 100 µmho V OFFSET Input Offset Voltage V VEA =0V, IAC Open-1010mVV IEA-HOutput High Voltage6.87.48.0 VV IEA-L Output Low Voltage 0.1 0.4 VI L Source Current V ISENSE =-0.6V, V IEA =1.5V 35 50 µA I H Sink Current V ISENSE =+0.6V, V IEA = 4.0V -50 -35 µAA I Open-Loop Gain(1)40 50 dB Tri-Fault Detect t FBPFC_OPEN Time to FBPFC Open (1)V FBPFC =V PFC-UVP to FBPFC OPEN,470pF from FBPFC to GND2 4 msV PFC-UVPPFC Feedback Under-Voltage Protection 0.4 0.5 0.6 VGain ModulatorI ACInput for AC Current (1)Multiplier Linear Range 0 100 µAI AC=17.67µA, V RMS=1.080VV FBPFC=2.25V, at T=25°C7.50 9.00 10.50 I AC=20µA, V RMS=1.224V V FBPFC =2.25V, at T=25°C6.307.00 7.70 I AC=25.69µA, V RMS=1.585VV FBPFC=2.25V, at T=25°C 3.80 4.20 4.60 I 51.62µA, V 3.169V GAIN GAIN Modulator (2)PFC/PWM Controller Combination=V GATE-L Gate Low Voltage V DD =15V; I O =100mA 1.5 V V GATE-H Gate High Voltage V DD =13V; I O =100mA 8 Vt r Gate Rising Time V DD =15V; C L =4.7nF; O/P=2V to 9V 40 70 120 ns t f Gate Falling Time V DD =15V; C L =4.7nF; O/P=9V to 2V4060110nsD PFC-MAX Maximum Duty Cycle V IEA <1.2V 94 97 %D PFC-MIN Minimum Duty CycleV IEA >4.5V 0 %Brown Out FAN4800A/C, FAN4801/1S/2 1.00 1.05 1.10 V V RMS-UVPVRMS Threshold LowFAN4802L 0.85 0.90 0.95 VFAN4800A/C, FAN4801/1S/2 1.85 1.90 1.95 VV RMS-UVP VRMS Threshold HighFAN4802L 1.60 1.65 1.70 V FAN4800A/C, FAN4801/1S/2750850950mVΔV RMS-UVP HysteresisFAN4802L 650 750 850 mVt UVP Under-VoltageProtection Delay Time340 410 480 msSoft StartV SS-MAX Maximum Voltage V DD 15V 9.5 10.0 10.5 VI SS Soft-Start Current10 µAPWM ILIMIT Comparator V PWM-ILIMITThreshold Voltage 0.95 1.00 1.05 V t PD Delay to Output250 nst PWM-BnkLeading-Edge BlankingTime170 250 350 nsRange (FAN4801/1S/2/2L)V RMS-L RMS AC Voltage Low When V RMS =1.95V at132Vrms 1.90 1.95 2.00 VPFC/PWM Controller Combination=====Notes:3. This parameter, although guaranteed by design, is not 100% production tested.4. Gain=K ×5.3 × (VRMS 2)-1; K=( ISENSE - I OFFSET ) × [IAC × (VEA - 0.7V)]-1; VEA (MAX.)=5.6V.PFC/PWM Controller Combination10.810.911.011.111.211.311.4-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V T H -O N (V )1.31.41.51.61.71.81.92.0-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃△V T H (V )Figure 9. V TH-ON vs. TemperatureFigure 10. ΔV TH vs. Temperature27.8627.8827.9027.9227.9427.9627.9828.0028.0228.04-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V D D -O V P (V )64.264.364.464.564.664.764.864.965.0-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃F O S C -F A N 4801/1S (k H z )Figure 11. V DD-OVP vs. TemperatureFigure 12. f OSC-FAN4801/1S vs. Temperature129.8130.0650655PFC/PWM Controller Combination-0.020.000.020.040.060.080.100.120.140.160.180.20-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃△V V R E F 2(m V )18.018.519.019.520.020.521.021.5-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃I R E F -M A X .(m A )Figure 17. ΔV VREF2 vs. TemperatureFigure 18. I REF-MAX. vs. Temperature2.7302.7322.7342.7362.7382.7402.742-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V P F C -O V P (V )250.8251.0251.2251.4251.6251.8252.0252.2-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃△V P F C -O V P (m V )Figure 19. V PFC-OVP vs. TemperatureFigure 20. ΔV PFC-OVP vs. Temperature2.3982.400 1.2701.275PFC/PWM Controller Combination0.00.51.01.52.02.53.03.54.04.5-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V O F F S E T (m V )788082848688909294-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃G m I (u m h o )Figure 25. V OFFSET vs. TemperatureFigure 26. Gm I vs. Temperature6.706.756.806.856.906.957.007.057.10-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃G A I N 25.45.55.65.75.85.96.06.1-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃R m u l (k Ω)Figure 27. GAIN2 vs. TemperatureFigure 28. Rmul vs. Temperature-1.1785-1.1780-1.1775290295PFC/PWM Controller Combination1.0381.0391.0401.0411.0421.0431.0441.0451.0461.0471.048-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V R M S -U V P (V )862.0862.5863.0863.5864.0864.5865.0865.5866.0866.5867.0867.5-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃△V R M S -U V P (m V )Figure 33. V RMS-UVP vs. TemperatureFigure 34. ΔV RMS-UVP vs. Temperature1.9311.9321.9331.9341.9351.9361.9371.9381.9391.940-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V R M S -L (V )2.4352.4362.4372.4382.4392.4402.4412.4422.4432.4442.4452.446-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V R M S -H (V )Figure 35. V RMS-L vs. TemperatureFigure 36. V RMS-H vs. Temperature1.9401.9422.4342.436PFC/PWM Controller Combination95.8895.9095.9295.9495.9695.9896.0096.0296.0496.06-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃D P F C -M A X (%)49.5049.5549.6049.6549.7049.7549.80-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃D P W M -M A X (%)Figure 41. D PFC-MAX vs. TemperatureFigure 42. D PWM-MAX vs. Temperature19.419.619.820.020.220.420.620.821.0-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃I t c (u A )1.4301.4351.4401.4451.4501.4551.460-40℃-25℃-10℃5℃20℃35℃50℃65℃80℃95℃110℃125℃V P W M -L S (V )Figure 43. I tc vs. TemperatureFigure 44. V PWM-LS vs. TemperatureFAN4800A/C, FAN4801/1S/2/2L — PFC/PWM Controller CombinationFunctional DescriptionThe FAN4800A/C and FAN4801/1S/2/2L consist of an average current controlled, continuous boost Power Factor Correction (PFC) front-end and a synchronized Pulse Width Modulator (PWM) back-end. The PWM can be used in current or voltage mode. In voltage mode, feed forward from the PFC output bus can be used to improve the line regulation of PWM. In either mode, the PWM stage uses conventional trailing-edge, duty-cycle modulation. This patented leading/trailing edge modulation results in a higher usable PFC error amplifier bandwidth and can significantly reduce the size of the PFC DC bus capacitor.The synchronization of the PWM with the PFC simplifies the PWM compensation due to the controlled ripple on the PFC output capacitor (the PWM input capacitor). The PWM section of the FAN4800A, FAN4801/1S operates at the same frequency as the PFC; and FAN4800C, FAN4802/2L operates at double with PFC.In addition to power factor correction, a number of protection features are built into this series. They include soft-start, PFC over-voltage protection, peak current limiting, brownout protection, duty cycle limiting, and under-voltage lockout (UVLO).Gain ModulatorThe gain modulator is the heart of the PFC, as the circuit block controls the response of the current loop to line voltage waveform and frequency, RMS line voltage, and PFC output voltages. There are three inputs to the gain modulator:1. A current representing the instantaneous input voltage (amplitude and wave shape) to the PFC. The rectified AC input sine wave is converted to a proportional current via a resistor and is fed into the gain modulator at IAC. Sampling current in this way minimizes ground noise, required in high-power, switching-power conversion environments. The gain modulator responds linearly to this current.2. A voltage proportional to the long-term RMS AC line voltage, derived from the rectified line voltage after scaling and filtering. This signal is presented to the gain modulator at VRMS. The output of the gain modulator is inversely proportional to VRMS (except at unusually low values of V RMS , where special gain contouring takes over to limit power dissipation of the circuit components under brownout conditions).3. The output of the voltage error amplifier, VEA. The gain modulator responds linearly to variations in this voltage. The output of the gain modulator is a current signal, in the form of a full wave rectified sinusoid at twice the line frequency. This current is applied to the virtual ground (negative) input of the current error amplifier. In this way, the gain modulator forms the reference for the current error loop and ultimately controls the instantaneous current draw of the PFC from the power line. The general form of the output of the gain 2(0.7)GAINMOD IAC VEA I K VRMS×−=×(1)Note that the output current of the gain modulator is limited around 159μA and the maximum output voltage of the gain modulator is limited to 159μA x 5.7K =0.906V. This 0.906V also determines the maximum input power.However, I GAINMOD cannot be measured directly from ISENSE. ISENSE =I GAINMOD – I OFFSET and I OFFSET can only be measured when VEA is less than 0.5V and I GAINMOD is 0A. Typical I OFFSET is around 31μA ~ 48μA.Selecting R AC for IAC PinThe IAC pin is the input of the gain modulator and also a current mirror input and requires current input. Selecting a proper resistor R AC provides a good sine wave current derived from the line voltage and helps program the maximum input power and minimum input line voltage. R AC =V IN peak x 56K Ω. For example, if the minimum line voltage is 75V AC , the R AC =75 x 1.414 x 56K Ω=6M Ω.Current Amplifier Error, IEAThe current error amplifier’s output controls the PFC duty cycle to keep the average current through the boost inductor a linear function of the line voltage. At the inverting input to the current error amplifier, the output current of the gain modulator is summed with a current, which results in a negative voltage being impressed upon the ISENSE pin.The negative voltage on ISENSE represents the sum of all currents flowing in the PFC circuit and is typically derived from a current sense resistor in series with the negative terminal of the input bridge rectifier.The inverting input of the current error amplifier is a virtual ground. Given this fact, and the arrangement of the duty cycle modulator polarities internal to the PFC, an increase in positive current from the gain modulator causes the output stage to increase its duty cycle until the voltage on ISENSE is adequately negative to cancel this increased current. Similarly, if the gain modulator’s output decreases, the output duty cycle decreases to achieve a less negative voltage on the ISENSE pin.PFC Cycle-By-Cycle Current LimiterAs well as being a part of the current feedback loop, the ISENSE pin is a direct input to the cycle-by-cycle current limiter for the PFC section. If the input voltage at this pin is less than -1.15V, the output of the PFC is disabled until the protection flip-flop is reset by the clock pulse at the start of the next PFC power cycle.FAN4800A/C, FAN4801/1S/2/2L — PFC/PWM Controller Combinationexceed safe operating limits. With such a failure, FBPFC exceeds its normal operating area. Should FBPFC go too low, too high, or open, TriFault Detect senses the error and terminates the PFC output drive. TriFault detect is an entirely internal circuit. It requires no external components to serve its protective function.PFC Over-Voltage ProtectionIn the FAN4800A/C, FAN4801/1S/2/2L, the PFC OVP comparator serves to protect the power circuit from being subjected to excessive voltages if the load changes suddenly. A resistor divider from the high-voltage DC output of the PFC is fed to FBPFC. When the voltage on FBPFC exceeds 2.75V, the PFC output driver is shut down. The PWM section continues to operate. The OVP comparator has 250mV of hysteresis and the PFC does not restart until the voltage at FBPFC drops below 2.50V. V DD OVP can also serve as a redundant PFC OVP protection. V DD OVP threshold is 28V with 1V hysteresis.Selecting PFC R senseR sense is the sensing resistor of the PFC boost converter. During the steady state, line input current x R sense equals I GAINMOD x 5.7K Ω.At full load, the average V EA needs to around 4.5V and ripple on the VEA needs to be less than 400mV. Choose the resistance of the sensing resistor: ()()−×Ω××××=×−×4.50.7 5.722 5.60.7 IN sense K IAC Gain V R Line input Power(2)where 5.6 is V EA maximum output.PFC Soft-StartPFC startup is controlled by V EA level. Before FBPFCvoltage reaches 2.4V, the V EA level is around 2.8V. At 90V AC , the PFC soft-start time is 90ms.PFC BrownoutThe AC UVP comparator monitors the AC input voltage. The FAN4800A/C, FAN4801/1S/2 disables current error amplifiers, along with their respective return points. The current-loop compensation is returned to VREF to produce a soft-start characteristic on the PFC: As the reference voltage increases from 0V, it creates a differentiated voltage on IEA, which prevents the PFC from immediately demanding a full duty cycle on its boost converter. Complete design is referred in application note AN-6078SC.There is an RC filter between R sense and ISENSE pin. There are two reasons to add a filter at the ISENSE pin: 1. Protection: During startup or inrush current conditions, there is a large voltage across R sense , which is the sensing resistor of the PFC boost converter. It requires the ISENSE filter to attenuate the energy. 2. To reduce L, the boost inductor: The ISENSE filter also can reduce the boost inductor value since the ISENSE filter behaves like an integrator before the ISENSE pin, which is the input of the current error amplifier, IEA. The ISENSE filter is an RC filter. The resistor value of the ISENSE filter is between 100Ω and 50Ω because I OFFSET x R FILTER can generate a negative offset voltage of IEA. Selecting an R FILTER equal to 50Ω keeps the offset of the IEA less than 3mV. Design the pole of ISENSE filter at f PFC /6, one sixth of the PFC switching frequency, so the boost inductor can be reduced six times without disturbing the stability. The capacitor of the ISENSE filter, C FILTER , is approximately 100nF.Figure 45. Compensation Network Connection for theVoltage and Current Error AmplifiersFAN4800A/C, FAN4801/1S/2/2L — PFC/PWM Controller Combinationline and light load or not. At the second-level PFC, there is a current of 20µA through R F2 from FBPFC pin. So the second-level PFC output voltage can be calculated as.+≅×−×1222(2.520)F F F F R R Output V uA R R (3)For example, if the second-level PFC output voltage is expected as 300V and normal voltage is 387V, according to the equation, R F2 is 28k Ω R F1 is 4.3M Ω. The programmable range of second level PFC output voltage is 340V ~ 300V.Figure 46. Two-Level PFC SchemeOscillator (R T /C T )The oscillator frequency is determined by the values of R T and C T , which determine the ramp and off-time of the oscillator output clock://1RT CT RT CT DEADf t t =+ (4)The dead time of the oscillator is derived from the following equation: /1ln 3.8RT CT T T VREF t C R VREF −⎛⎞=××⎜⎟−⎝⎠(5)at V REF =7.5V and t RT/CT =CT x RT x 0.56.The dead time of the oscillator is determined using: derived directly from a current sensing resistor or current transformer in the primary of the output stage. It is thereby representative of the current flowing in the converter’s output stage. I LIMIT , which provides cycle-by-cycle current limiting, is typically connected to RAMP in such applications. For voltage-mode operation and certain specialized applications, RAMP can be connected to a separate RC timing network to generate a voltage ramp against which FBPWM is compared. Under these conditions, the use of voltage feed-forward from the PFC bus can assist in line regulation accuracy and response. As in current-mode operation, the I LIMIT input is used for output stage over-current protection. No voltage error amplifier is included in the PWM stage, as this function is generally performed on the output side of the PWM’s isolation boundary. To facilitate the design of opto-coupler feedback circuitry, an offset has been built into the PWM’s RAMP input that allows FBPWM to command a 0% duty cycle for input voltages below typical 1.5V.PWM Cycle-By-Cycle Current LimiterThe ILIMIT pin is a direct input to the cycle-by-cycle current limiter for the PWM section. Should the input voltage at this pin ever exceed 1V, the output flip-flop is reset by the clock pulse at the start of the next PWM power cycle. When the I LIMIT triggers the cycle-by-cycle bi-cycle current, it limits the PWM duty cycle mode and the power dissipation is reduced during the dead-short condition.V IN OK ComparatorThe V IN OK comparator monitors the DC output of the PFC and inhibits the PWM if the voltage on FBPFC is less than its nominal 2.4V. Once the voltage reaches 2.4V, which corresponds to the PFC output capacitor being charged to its rated boost voltage, the soft-start begins.PWM Soft-Start (SS)PWM startup is controlled by selection of the external capacitor at soft-start. A current source of 10µA supplies the charging current for the capacitor andFAN4800A/C, FAN4801/1S/2/2L — PFC/PWM Controller CombinationPWM Control (RAMP)When the PWM section is used in current mode, RAMP is generally used as the sampling point for a voltage, representing the current in the primary of the PWM’s output transformer. The voltage is derived either from a current sensing resistor or a current transformer. In voltage mode, RAMP is the input for a ramp voltage generated by a second set of timing components (R RAMP , C RAMP ) that have a minimum value of 0V and a peak value of approximately 6V. In voltage mode, feed forward from the PFC output bus is an excellent way to derive the timing ramp for the PWM stage.Generating V DDAfter turning on the FAN4800A/C, FAN4801/1S/2/2L at 11V, the operating voltage can vary from 9.3V to 28V. The threshold voltage of the V DD OVP comparator is 28V and its hysteresis is 1V. When V DD reaches 28V, OPFC is LOW, and the PWM section is not disturbed. There are two ways to generate V DD : use auxiliary power supply around 15V or use bootstrap winding to self-bias the FAN4800A/C, FAN4801/1S/2/2L system. The bootstrap winding can be taped from the PFC boost choke or the transformer of the DC-to-DC stage.Leading/Trailing ModulationConventional PWM techniques employ trailing-edge modulation, in which the switch turns on right after the trailing edge of the system clock. The error amplifier output is then compared with the modulating ramp up. The effective duty cycle of the trailing edge modulation is determined during the on-time of the switch.In the case of leading-edge modulation, the switch is turned off exactly at the leading edge of the system clock. When the modulating ramp reaches the level of the error amplifier output voltage, the switch is turned on. The effective duty-cycle of the leading-edge modulation is determined during off-time of the switch.。

BFG425W,115;中文规格书,Datasheet资料

MAX. 10 4.5 30 135 120

UNIT V V mA mW fF GHz dB dB

IC = 25 mA; VCE = 2 V; f = 2 GHz; Tamb = 25 C IC = 25 mA; VCE = 2 V; f = 2 GHz; Tamb = 25 C IC = 2 mA; VCE = 2 V; f = 2 GHz; S = opt CAUTION

1. Gmax is the maximum power gain, if K > 1. If K < 1 then Gmax = MSG; see Figs 6, 7 and 8. 2. ZS is optimized for noise; ZL is optimized for gain.

2010 Sep 15

MIN. 10 4.5 1 50

TYP. 80 300 575 95 25 20 17 0.8 1.2 12 22

MAX. 15 120

UNIT V V V nA fF fF fF GHz dB dB dB dB dBm dBm

Fig.6

Maximum stable gain as a function of collector current; typical values.

2010 Sep 15

5

/

NXP Semiconductors

Product specification

15

10 10 5

0 1 10 IC (mA)

102

0 0 10 20 30 IC (mA) 40

VCE = 2 V; f = 2 GHz; Tamb = 25 C.

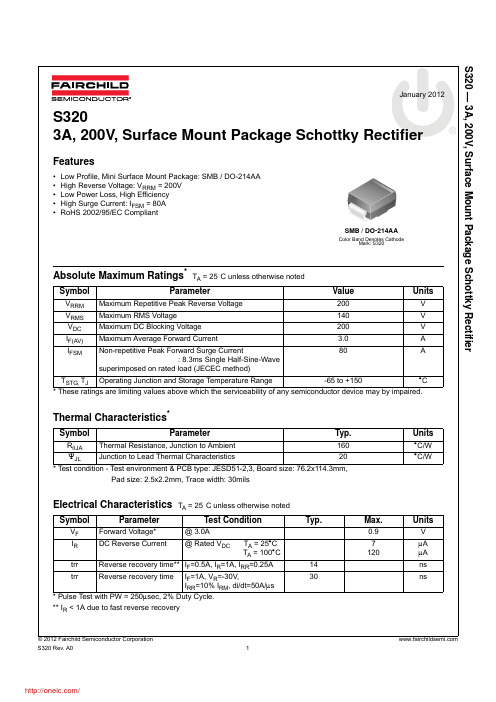

S320;中文规格书,Datasheet资料

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

1000 100 10 1 0.1 0.01 1E-3 20

T =100 oC A

T =75 oC A

T =25 oC A

40

60

80

100

120

Percent of Rated Peak Voltage, [%]

Reverse Current, I [uA] R

Instantaneous Forward Current, I [A] F

Figure 1. DC Forward Current Derating Curve

MBT2222ADW1T1G;中文规格书,Datasheet资料

VCEO VCBO VEBO

IC ESD

40

Vdc

75

Vdc

6.0

Vdc

600

mAdc

HBM Class 2 MM Class B

THERMAL CHARACTERISTICS

Characteristic

Symbol

Max

Unit

Total Package Dissipation (Note 1), TA = 25°C

© Semiconductor Components Industries, LLC, 2009

1

October, 2009 − Rev. 4

/

Publication Order Number: MBT2222ADW1T1/D

MBT2222ADW1T1G

ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise noted) Characteristic

Output Capacitance

(VCB = 10 Vdc, IE = 0, f = 1.0 MHz)

Input Capacitance

(VEB = 0.5 Vdc, IC = 0, f = 1.0 MHz)

Inp1.0 mAdc, VCE = 10 Vdc, f = 1.0 kHz) (IC = 10 mAdc, VCE = 10 Vdc, f = 1.0 kHz)

td

−

10

ns

tr

−

25

ts

−

225

ns

tf

−

60

/

2

hFE, DC CURRENT GAIN

MJW18020G;中文规格书,Datasheet资料

10.0

Ic/Ib = 5.0

10.0

Ic/Ib = 10

1.0 TJ = 25°C

TJ = −20°C

1.0 TJ = 25°C

TJ = −20°C

VBE, VOLTAGE (VOLTS)

VBE, VOLTAGE (VOLTS)

TJ = 125°C

0.1

0.001

0.01

0.1

1.0

10

100

IC, COLLECTOR CURRENT (A)

(IC = 3 Adc, VCE = 5 Vdc) (IC = 10 Adc VCE = 2 Vdc) (IC = 20 Adc VCE = 2 Vdc) (IC = 10 mAdc VCE = 5 Vdc)

(TC = 125°C) (TC = 125°C) (TC = 125°C)

Base−Emitter Saturation Voltage (IC = 10 Adc, IB = 2 Adc) (IC = 20 Adc, IB = 4 Adc)

PD

250

W

2.0

W/_C

Operating and Storage Junction Temperature Range

TJ, Tstg −65 to +150 _C

THERMAL CHARACTERISTICS

Characteristic

Symbol

Max

Unit

Thermal Resistance, Junction−to−Case

30 AMPERES 1000 VOLTS BVCES 450 VOLTS BVCEO, 250 WATTS

1 2 3

US5U38TR;中文规格书,Datasheet资料

Transistor1/52.5V Drive Pch+SBD MOSFETUS5U38z StructureSilicon P-channel MOSFET Schottky Barrier DIODEz Features1) The US5U38 combines Pch MOSFET with a Schottky barrier diode in a TUMT5 package. 2) Low on-resistance with fast switching. 3) Low voltage drive (2.5V).4) Built-in schottky barrier diode has low forward voltage.z Applications SwitchingzPackaging specificationsz Absolute maximum ratings (T a=25°C)V RM V R I F I FSM Tj ParameterV V DSS Symbol −20V V GSS ±12A I D±1.0A I DP ±4.0A I S−0.4A I SP −4.0V 20A 0.7A 3.0°C150°CTch 150V 25Limits Unit Channel temperature <Di><MOSFET>W / ELEMENT P D 0.7Power dissipationW / TOTALP D 1.0°CTstg−55 to +150Power dissipationRange of storage temperature<MOSFET AND Di>Drain-source voltage Gate-source voltage Drain current Continuous PulsedContinuous PulsedSource current (Body diode)Repetitive peak reverse voltage Reverse voltage Forward currentForward current surge peak Junction temperature ∗1∗1∗3∗2W / ELEMENT P D0.5Power dissipation∗3∗3∗1 Pw ≤10µs, Duty cycle ≤1% ∗2 60Hz •1cyc. ∗3 Mounted on a ceramic boardz Dimensions (Unit : mm)Transistor2/5z Electrical characteristics (T a=25°C)V SD−−−1.2VI S =−0.4A, V GS =0VForward voltageParameterSymbol Min.Typ.Max.Unit Conditions<Body diode (source −drain)>V F −−0.49V I F =0.7A I R −−200µAV R =20VReverse currentForward voltage ParameterSymbol Min.Typ.Max.Unit Conditions<Di >Transistor3/5z Electrical characteristic curvesFig.1 Typical Transfer CharacteristicsGATE −SOURCE VOLTAGE : -V GS [V ]D R A I N C U R R E N T : −I D (A )Fig.2 Static Drain −Source On −State Resistance vs.Drain Current ( Ι )100100010000DRAIN CURRENT : −I D [A ]S T A T I C D R A I N −S O U R C E O N −S T A T E R E S I S T A N C E : R D S (o n )[m Ω]Fig.3 Static Drain −Source On −State Resistance vs.Drain Current ( ΙΙ )DRAIN CURRENT : −I D [A ]S T A T I C D R A I N −S O U R C E O N −S T A T E R E S I S T A N C E : R D S (o n )[m Ω]100100010000Fig.4 Static Drain −Source On −StateResistance vs.Drain −Current ( ΙΙΙ )DRAIN CURRENT : −I D [A ]S T A T I C D R A I N −S O U R C E O N −S T A T E R E S I S T A N C E : R D S (o n )[m Ω]2505007501000S T A T I C D R A I N −S O U R C E O N −S T A T E R E S I S T A N C E GATE −SOURCE VOLTAGE : −V GS [V ]Fig.5 Static Drain −Source On −StateResistance vs.Gate −Source Voltage: R D S (o n )[m Ω]Fig.6 Static Drain −Source On −State Resistance vs.Drain CurrentDRAIN CURRENT : −I D [A ]S T A T I C D R A I N -S O U R C E O N −S T A T E R E S I S T A N C E : R D S (o n )[m Ω]SOURCE −DRAIN VOLTAGE : −V SD [V ]Fig.7 Reverse Drain Current vs. Source-Drain Current R E V E R S E D R A I N C U R R E N T :−I S [A ]DRAIN −SOURCE VOLTAGE : −V DS [V ]Fig.8 Typical Capactitance vs.Drain −Source VoltageC A P A C I T A N C E : C [pF ]DRAIN CURRENT : −I D [A ]Fig.9 Switching CharacteristicsS W I T C H I N G T I M E : t [n s ]Transistor4/5Fig.10 Dynamic Input Characteristics4TOTAL GATE CHARGE : Qg [nC ]G A T E -S O U R C E V O L T A G E : -V G S [V ]1235z Notice1. SBD has a large reverse leak current compared to other type of diode. Therefore; it would raise a junction temperature, and increase a reverse power loss. Further rise of inside temperature would cause a thermal runaway .This built-in SBD has low V F characteristics and therefore, higher leak current. Please consider enough the surrounding temperature, generating heat of MOSFET and the reverse current.2. This product might cause chip aging and breakdown under the large electrified environment. Please consider to design ESD protection circuit.0.010.11101001000100001000000510152025REVERSE VOLTAGE : VR [V]R E V E R S E C U R R E N T : I R [u A ]Fig.11 Reverse Current vs. Reverse Voltage0.0010.010.11Fig.12Forward Current vs.Forward VoltageFORWARD VOLTAGE : V F (V)F O R W A R D C U R R E N T : I F (A )Transistor5/5z Measurement circuitsFig.13 Switching Time Measurement CircuitFig.14 Switching WaveformsFig.15 Gate Charge Measurement CircuitIFig.16 Gate Charge WaveformsV GSV GAppendix1-Rev2.0Thank you for your accessing to ROHM product informations.More detail product informations and catalogs are available, please contact your nearest sales office.ROHM Customer Support SystemTHE AMERICAS / EUROPE / ASIA / JAPANContact us : webmaster@rohm.co.jpAppendix分销商库存信息: ROHMUS5U38TR。

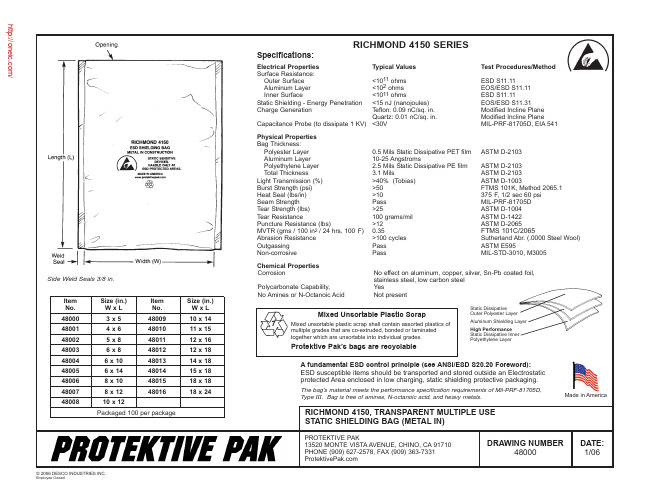

48000;48001;48002;48003;48004;中文规格书,Datasheet资料

Protektive Pak’s bags are recyclable

A fundamental ESD control principle (see ANSI/ESD S20.20 Foreword): ESD susceptible items should be transported and stored outside an Electrostatic protected Area enclosed in low charging, static shielding protective packaging.

Байду номын сангаас

<15 nJ (nanojoules) Teflon: 0.09 nC/sq. in. Quartz: 0.01 nC/sq. in. Capacitance Probe (to dissipate 1 KV) <30V

Physical Properties Bag Thickness: Polyester Layer Aluminum Layer Polyethylene Layer Total Thickness Light Transmission (%) Burst Strength (psi) Heat Seal (lbs/in) Seam Strength Tear Strength (lbs) Tear Resistance Puncture Resistance (lbs) MVTR (gms / 100 in2 / 24 hrs, 100°F) Abrasion Resistance Outgassing Non-corrosive Chemical Properties Corrosion Polycarbonate Capability, No Amines or N-Octanoic Acid

BFT92W,115;中文规格书,Datasheet资料

2

45 o

MLB548

1.0

90 o

VCE = 10 V; IC = 15 mA.

Fig.10 Common emitter input reflection coefficient (s11), typical values.

90 o

135 o

45 o

180 o

40 MHz 50 40 30 20 10 3 GHz

Fig.6

Gain as a function of collector current, typical values.

Fig.7

Gain as a function of collector current, typical values.

50 gain (dB) 40 G UM 30 MSG

MLB546

1 C re (pF) 0.8

6 fT (GHz) 4 V CE = 10 V 5V

MLB543

0.6

0.4

2

0.2

0 0 4 8 12 16 20 VCB (V)

0 1 10 I C (mA) 10 2

IC = 0; f = 1 MHz.

f = 500 MHz; Tamb = 25 C.

Fig.4

DISCRETE SEMICONDUCTORS

DATA SHEET

BFT92W PNP 4 GHz wideband transistor

Product specification May 1994

/

NXP Semiconductors

Product specification

0 0 10 20 I C (mA) 30

VCE = 10 V; Tj = 25 C.

DS1603;中文规格书,Datasheet资料

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: /errata .FEATURES§ Two 32-bit counters keep track of real -time and elapsed time§ Counters keep track of seconds for over 125 years§ Battery powered counter counts seconds from the time battery is attached until V BAT is less than 2.5V§ V CC powered counter counts seconds while V CC is above V TP and retains the count in the absence of V CC under battery backup power § Clear function resets selected counter to 0 § Read/write serial port affords low pin count § Powered internally by a lithium energy cell that provides over 10 years of operation§ One-byte protocol defines read/write, counter address and software clear function§ Self-contained crystal provides an accuracy of ±2 min per month§ Operating temperature range of 0°C to +70°C § Low-profile SIP module§ Underwriters Laboratory (UL) recognized PIN ASSIGNMENTPIN DESCRIPTIONRST- Reset CLK - ClockDQ - Data Input/Output GND - Ground V CC - +5VOSC - 1Hz Oscillator Output NC- No ConnectDESCRIPTIONThe DS1603 is a real -time clock/elapsed time counter designed to count seconds when V CC power is applied and continually count seconds under battery backup power with an additional counter regardless of the condition of V CC . The continuous counter can be used to derive time of day, week, month, and year by using a software algorithm. The V CC powered counter will automatically record the amount of time that V CC power is applied. This function is particularly useful in determining the operational time of equipment in which the DS1603 is used. Alternatively, this counter can also be used under software control to record real -time events. Communication to and from the DS1603 takes place via a 3-wire serial port. A 1-byte protocol selects read/ write functions, counter clear functions and oscillator trim. The device contains a 32.768kHz crystal that will keep track of time to within ±2 min/mo. An internal lithium energy source contains enough energy to power the continuous seconds counter for over 10 years.OPERATIONThe main elements of the DS1603 are shown in Figure 1. As shown, communications to and from the elapsed time counter occur over a 3-wire serial port. The port is activated by driving RST to a high state.V CC RST DQ NC CLK OSC GND DS1603Elapsed Time Counter Moduleselect, register clear, and oscillator trim information. Each bit is serially input on the rising edge of the clock input. After the first eight clock cycles have loaded the protocol register with a valid protocol additional clocks will output data for a read or input data for a w rite. V CC must be present to access the DS1603. If V CC < V TP, the DS1603 will switch to internal power and disable the serial port to conserve energy. When running off of the internal power supply, only the continuous counter will continue to count and the counter powered by V CC will stop, but retain the count, which had accumulated when V CC power was lost. The 32-bit V CC counter is gated by V CC and the internal 1Hz signal.PROTOCOL REGISTERThe protocol bit definition is shown in Figure 2. Valid protocols and the resulting actions are shown in Table 1. Each data transfer to the protocol register designates what action is to occur. As defined, the MSB (bit 7 which is designated ACC) selects the 32-bit continuous counter for access. If ACC is a logical 1 the continuous counter is selected and the 32 clock cycles that follow the protocol will either read or write this counter. If the counter is being read, the contents will be latched into a different register at the end of protocol and the latched contents will be read out on the next 32 clock cycles. This avoids reading garbled data if the counter is clocked by the oscillator during a read. Similarly, if the counter is to be written, the data is buffered in a register and all 32 bits are jammed into the counter simultaneously on the rising edge of the 32nd clock. The next bit (bit 6 which is designated AVC) selects the 32–bit V CC active counter for access. If AVC is a logical 1 this counter is selected and the 32 clock cycles that follow will either read or write this counter. If both bit 7 and bit 6 are written to a logic high, all clock cycles beyond the protocol are ignored and bit 5, 4, and 3 are loaded into the oscillator trim register. A value of binary 3 (011) will give a clock accuracy of ±120 seconds per month at +25°C. Increasing the binary number towards 7 will cause the real-time clock to run faster. Conversely, lowering the binary number towards 0 will cause the clock to run slower. Binary 000 will stop the oscillator completely. This feature can be used to conserve battery life during storage. In this mode the internal power supply current is reduced to 100 nA maximum. In applications where oscillator trimming is not practical or not needed, a default setting of 011 is recommended. Bit 2 of protocol (designated CCC) is used to clear the continuous counter. When set to logic 1, the continuous counter will reset to 0 when RST is taken low. Bit 1 of protocol (designated CVC) is used to clear the V CC active counter. When set to logical 1, the V CC active counter will reset to 0 when RST is taken low. Both counters can be reset simultaneously by setting CCC and CVC both to a logical 1. Bit 0 of the protocol (designated RD) determines whether the 32 clocks to follow w ill write a counter or read a counter. When RD is set to a logical 0 a write action will follow when RD is set to a logical 1 a read action will follow. When sending the protocol, 8 bits should always be sent. Sending less than 8 bits can produce erroneous results. If clearing the counters or trimming the oscillator, the data transfer can be terminated after the 8-bit protocol is sent. However, when reading or writing the counters, 32 clock cycles should always follow the protocol.RESET AND CLOCK CONTROLAll data transfers are initiated by driving the RST input high. The RST input has two functions. First, RST turns on the serial port logic, which allows access to the protocol register for the protocol data entry. Second, the RST signal provides a method of terminating the protocol transfer or the 32-bit counter transfer. A clock cycle is a sequence of a rising edge followed by a falling edge. For write inputs, data must be valid during the rising edge of the clock. Data bits are output on the falling edge of the clock when data is being read. All data transfers terminate if the RST input is transitioned low and the DQ pin goes to a high-impedance state. RST should only be transitioned low while the clock is high to avoid disturbing the last bit of data. All data transfers must consist of 8 bits when transferring protocol only or 8 + 32 bits when reading or writing either counter. Data tran sfer is illustrated in Figure 3.DATA INPUTFollowing the 8-bit protocol that inputs write mode, 32 bits of data are written to the selected counter on the rising edge of the next 32 CLK cycles. After 32 bits have been entered any additional CLK cycles will be ignored until RST is transitioned low to end data transfer and then high again to begin new data transfer.DATA OUTPUTFollowing the eight CLK cycles that input read mode protocol, 32 bits of data will be output from the selected counter on the next 32 CLK cycles. The first data bit to be transmitted from the selected 32-bit counter occurs on the falling edge after the last bit of protocol is written. When transmitting data from the selected 32-bit counter, RST must remain at high level as a transition to low level will terminate data transfer. Data is driven out the DQ pin as long as CLK is low. When CLK is high the DQ pin is tristated. OSCILLATOR OUTPUTPin 6 of the DS1603 module is a 1Hz output signal. This signal is present only when V CC is applied and greater than the internal power supply. However, the output is guaranteed to meet TTL requirement only while V CC is within normal limits. This output can be used as a 1-second interrupt or time tick needed in some applications.INTERNAL POWERThe internal battery of the DS1603 module provides 35mAh and will run the elapsed time counter for over 10 years in the absence of power.PIN DESCRIPTIONSV CC, GND – DC power is provided to the device on these pins. V CC is the +5V input. When 5V is applied within normal limits, the device is fully accessible and data can be written and read. When a 3V battery is connected to the device and V CC is below 1.25 x V BAT, reads and writes are inhibited. As V CC falls below V BAT the continuous counter is switched over to the internal battery.CLK (Serial Clock Input) – CLK is used to synchronize data movement on the serial interface.DQ (Data Input/Output) – The DQ pin is the bi-directional data pin for the 3-wire interface.RST (Reset) – The reset signal must be asserted high during a read or a write.OSC (One Hertz Output Signal) – This signal is only present when Vcc is at a valid level and the oscillator is enabled.Figure 1. ELAPSED TIME COUNTER BLOCK DIAGRAMFigure 2. PROTOCOL BIT MAP7 6 5 4 3 2 1 0ACC AVC OSC2 OSC1 OSC0 CCC CVC RDTable 1. VALID PROTOCOLSPROTOCOLACTIONACC AVC OSC2 OSC1 OSC0 CCC CVC RDFUNCTION ReadContinuous Counter 1 0 X X X X X 1Output continuouscounter on the 32 clocksfollowing protocol.Oscillator trim registeris not updated. Countersare not reset.WriteContinuous Counter 1 0 X X X X X 0Input data to continuouscounter on the 32 clocksfollowing protocol.Oscillator trim registeris not updated. Countersare not reset.Read V CCActive Counter 0 1 X X X X X 1Output V CC activecounter on the 32 clocksfollowing protocol,oscillator trim registeris not updated. Countersare not reset.Write V CCActive Counter 0 1 X X X X X 0Input data to continuouscounter on the 32 clocksfollowing protocol.Oscillator trim registeris not updated. Countersare not reset.ClearContinuous Counter 0 0 X X X 1 X XResets the continuouscounter to all zeros atthe end of protocol.Oscillator trim registeris not updated.Clear V CCActive Counter 0 0 X X X X 1 XResets the V CC activecounter to all zeros atthe end of protocol.Oscillator trim registeris not updated.Set Oscillator Trim Bits 1 1 A B C X X 0Sets the oscillator trimregister to a value ofABC. Counters areunaffected.X = Don’t CareFigure 3. DATA TRANSFERTIMING DIAGRAM: READ/WRITE DATA TRANSFERNote: t CL, t CH, t R, and t F apply to both read and write data transfer.ABSOLUTE MAXIMUM RATINGSVoltage Range on Any Pin Relative to Ground -0.3V to +7.0VOperating Temperature Range 0°C to +70°CStorage Temperature Range -40°C to +70°CSoldering Temperature Range See IPC/JEDEC J-STD-020A (See Note 11)This is a stress rating only and functional operation of the device at these or any other conditions beyond t h ose indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time can affect reliability.RECOMMENDED DC OPERATING CONDITIONS (0°C to +70°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Supply Voltage V CC 4.5 5.0 5.5 V 1 Logic 1 Input V IH 2.0 V CC + 0.3 V 1 Logic 0 Input V IL-0.3 0.8 V 1DC ELECTRICAL CHARACTERISTICS (0°C to +70°C; V CC = 5V ±10%) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Input Leakage I LI-1 +1 µAI/O Leakage I LO-1 +1 µALogic 1 Output V OH 2.4 V 2 Logic 0 Output V OL0.4 V 3 Active Supply Current I CC 1 mA 4 Timekeeping Current I CC150 µA 5 Battery Trip Point V TP 3.0 4.5 V 9 CAPACITANCE (T A = +25°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Input Capacitance C I 5 pFI/O Capacitance C I/O10 pF(T A = +25°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Expected Datat DR10 years 10 Retention TimeNOTES:1) All voltages are referenced to ground.2) Logic 1 voltages are specified at a source current of 1mA.3) Logic 0 voltages are specified at a sink current of 4mA.4) I CC is specified with the DQ pin open.5) I CC1 is specified with V CC at 5.0V and RST = GND.6) Measured at V IH= 2.0V or V IL = 0.8V.7) Measured at V OH = 2.4V or V OL - 0.4V.8) Load capacitance = 50pF.9) Battery trip point is the point at which the V CC powered counter and the serial port stops operation.The battery trip point drops below the minimum once the internal lithium energy cell is exhausted. 10) The expected t D R is defined as accumulative time in the absence of V CC with the clock oscillatorrunning.11) Real-time clock modules can be successfully processed through conventional wave-solderingtechniques as long as temperature exposure to the lithium energy source contained within does not exceed +85°C. Post-solder cleaning with water-washing techniques is acceptable, provided that ultrasonic vibration is not used.DS1603DS1603 7-PIN MODULEPKG7-PIN DIM MIN MAX A IN. MM 0.830 21.08 0.850 21.59 B IN. MM 0.650 16.51 0.670 17.02 C IN. MM 0.310 7.87 0.330 8.38 D IN. MM 0.015 0.38 0.030 0.76 E IN. MM 0.110 2.79 0.140 3.56 F IN. MM 0.015 0.38 0.021 0.53 G IN. MM 0.090 2.29 0.110 2.79 H IN. MM 0.105 2.67 0.135 3.43 J IN. MM 0.360 9.14 0.390 9.91分销商库存信息: MAXIMDS1603。

ATTINY20-SSUR;中文规格书,Datasheet资料