基于Verilog的下三角矩阵求逆设计与实现

FPGA 用Verilog HDL实现三角波,三相方波程序

FPGA——用Verilog HDL进行三角波和三相方波的编写三角波module triangle(inputsys_clk,output [2:0]sda);reg[3:0]a=0;regai=0;always@(posedgesys_clk)beginif(ai==0)begina=a+1;if(a==7)ai<=1;endelsebegina=a-1;if(a==0)ai<=0;endendassignsda[0]=a[0];assignsda[1]=a[1];assignsda[2]=a[2];endmodule三相方波第一种方法:modulepwmabc(inputsys_clk,output [2:0]abc);regtriga=0;regtrigb=1;regtrigc=0;reg[15:0] cnt1=0;reg[15:0] cnt2=20;reg[15:0] cnt3=40;always@(negedgesys_clk)beginif(cnt1>59)begintriga=~triga;cnt1<=1;endelsecnt1<=cnt1+1;if(cnt2>59)begintrigb=~trigb;cnt2<=1;endelsecnt2<=cnt2+1;if(cnt3>59)begintrigc=~trigc;cnt3<=1;endelsecnt3<=cnt3+1;endassignabc[0]=triga;assignabc[1]=trigb;assignabc[2]=trigc;endmodule第二种方法module fangbo0(inputsys_clk,output [2:0]sda);reg [31:0]halftemple_counter0=0;reg [31:0]halftemple_counter1=0;reg [31:0]halftemple_counter2=0;reg [1:0]temple_clk0=1;//第一相的初始值是高电平(初始的高低电平是根据我给你看的相位图来的)reg [1:0]temple_clk1=1;//第二相的初始值是高电平reg [1:0]temple_clk2=0;//第三相的初始值是底电平//我在设计三相方波的时候用的比较笨的方法,就是三相方波一项一项的来设置。

用verilog编写的反z变换程序【优质】

/************************************************************************ -----------------------------------------------------------------------**** zigzag.v************ Author: Latha Pillai** Senior Applications Engineer**** Video Applications** Advanced Products Group** Xilinx, Inc.**** Copyright (c) 2001 Xilinx, Inc.** All rights reserved**** Date: April. 10, 2002**** RESTRICTED RIGHTS LEGEND**** This software has not been published by the author, and** has been disclosed to others for the purpose of enhancing** and promoting design productivity in Xilinx pro ducts.**** Therefore use, duplication or disclosure, now and in the** future should give consideration to the productivity** enhancements afforded the user of this code by the author's** efforts. Thank you for using our products !**** Disclaimer: THESE DESIGNS ARE PROVIDED "AS IS" WITH NO WARRANTY** WHATSOEVER AND XILINX SPECIFICALLY DISCLAIMS ANY** IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR** A PARTICULAR PURPOSE, OR AGAINST INFRINGEMENT.** Module: zigzag_decode :The zigzag module is used to read out the quanized dct input in a zigzag order. There are two different zigzag scanning modes in MPEG2. The scanning mode is chosen by the "scan_type" input. Scan_type = 0 chooses the default scanning mode which is also the mode used in MPEG1. MPEG2 has an alternate scanning mode which is chosen when scan_type = 1. The 2 scanning modes for an 8x8 block is as shown below0 1 5 6 14 15 22 282 4 7 13 16 26 29 423 8 12 17 25 30 41 439 11 18 24 31 40 44 5310 19 23 32 39 45 52 5420 22 33 38 46 51 55 6021 34 37 47 50 56 59 6135 36 48 49 57 58 62 630 4 6 20 22 36 38 521 5 7 21 23 37 39 532 8 19 24 34 40 50 543 9 18 25 35 41 51 5510 17 26 30 42 46 56 6011 16 27 31 43 47 57 6112 15 28 32 44 48 58 6213 14 29 33 45 49 59 63The scanning order requires that some of the later coeeficients be available in the beginning. For example, in alternate scanning mode, the 56th coeeficient is read in at the 13th clock. Also some of the initial coefficients are read out later in the cycle. For example, in alternate scanning mode, the 7th coefficient is read out only in the 52th clock cycle. Due to this nature, it is safer to have all the 64 coefficient available for 64 clock cycles. This is ensured by the memread_rdy signal. This signal waits for 64 clocks before reading out from zigzag_in_reg1. By this time, all the 64 coefficients would have been stored in this memory and they are held there for 64 clocks.Since the input data zigzag_in is continuous, we get a new value for the 1st coefficient at the 65th clock. Since the reading from zigzag_in_reg1 would not be complete by the 65th clock, a second memory , zigzag_in_reg2, is used to store the next set of 64 coefficients. After reading the 64 values from zigzag_in_reg1, the next 64 values are read from zigzag_in_reg2. This selection is done using the toggle_mem signal. This signal holds a '0' or '1' for 64 clocks and then switches.The values are read out from the memories depending on the value of scan_mem. Scan_mem is a register used to hold the 2 different kinds of scanning orders. Scan_type signal chooses between the 2 scanning orders.**********************************************************************///scale factor --- how many bits ?`timescale 1ns/1psmodule zigzag_decode ( CLK,RST,rdy_in,zigzag_in,scan_type,qdct_out);input CLK;input RST;input[11:0] zigzag_in; /* 11 bit output from DCT block */input rdy_in; /* ready signal , starts quantization process after DCT is done for the block */input scan_type; /* used to choose b/n intra(0) & non-intra(1)blocks */output [11:0] qdct_out; /* quantised output value *//* signals */reg[6:0] cnt64;reg memread_rdy;reg toggle_mem;reg[6:0] scan_mem;reg[11:0] zigzag_in_reg1[63:0];reg[11:0] zigzag_in_reg2[63:0];reg[11:0] zigzag_out;/*****************************************************************************//* scan_type register. This register is used to store the 2 different kinds of scan mode.Normal scan mode (0) is used for MPEG1 and MPEG2. Alternate scan mode (1) is used in MPEG2for intra coded blocks */always @ (posedge CLK)beginif (scan_type == 1'b0)begincase (cnt64)1 : begin scan_mem <= 7'd 0; end2 : begin scan_mem <= 7'd 1; end3 : begin scan_mem <= 7'd 8; end4 : begin scan_mem <= 7'd 16; end5 : begin scan_mem <= 7'd 9; end6 : begin scan_mem <= 7'd 2; end7 : begin scan_mem <= 7'd 3; end 8 : begin scan_mem <= 7'd 10; end9 : begin scan_mem <= 7'd 17; end 10 : begin scan_mem <= 7'd 24; end11 : begin scan_mem <= 7'd 32; end 12 : begin scan_mem <= 7'd 25; end13 : begin scan_mem <= 7'd 18; end 14 : begin scan_mem <= 7'd 11; end15 : begin scan_mem <= 7'd 4; end 16 : begin scan_mem <= 7'd 5; end17 : begin scan_mem <= 7'd 12; end 18 : begin scan_mem <= 7'd 19; end19 : begin scan_mem <= 7'd 26; end 20 : begin scan_mem <= 7'd 33; end21 : begin scan_mem <= 7'd 40; end 22 : begin scan_mem <= 7'd 48; end23 : begin scan_mem <= 7'd 41; end 24 : begin scan_mem <= 7'd 34; end25 : begin scan_mem <= 7'd 27; end 26 : begin scan_mem <= 7'd 20; end27 : begin scan_mem <= 7'd 13; end 28 : begin scan_mem <= 7'd 6; end29 : begin scan_mem <= 7'd 7; end 30 : begin scan_mem <= 7'd 14; end31 : begin scan_mem <= 7'd 21; end 32 : begin scan_mem <= 7'd 28; end35 : begin scan_mem <= 7'd 49; end 36 : begin scan_mem <= 7'd 56; end 37 : begin scan_mem <= 7'd 57; end 38 : begin scan_mem <= 7'd 50; end 39 : begin scan_mem <= 7'd 43; end 40 : begin scan_mem <= 7'd 36; end 41 : begin scan_mem <= 7'd 29; end 42 : begin scan_mem <= 7'd 22; end 43 : begin scan_mem <= 7'd 15; end 44 : begin scan_mem <= 7'd 23; end 45 : begin scan_mem <= 7'd 30; end 46 : begin scan_mem <= 7'd 37; end 47 : begin scan_mem <= 7'd 44; end 48 : begin scan_mem <= 7'd 51; end 49 : begin scan_mem <= 7'd 58; end 50 : begin scan_mem <= 7'd 59; end 51 : begin scan_mem <= 7'd 52; end 52 : begin scan_mem <= 7'd 45; end 53 : begin scan_mem <= 7'd 38; end 54 : begin scan_mem <= 7'd 31; end 55 : begin scan_mem <= 7'd 27; end 56 : begin scan_mem <= 7'd 46; end 57 : begin scan_mem <= 7'd 53; end 58 : begin scan_mem <= 7'd 60; end 59 : begin scan_mem <= 7'd 61; end 60 : begin scan_mem <= 7'd 54; end 61 : begin scan_mem <= 7'd 47; end 62 : begin scan_mem <= 7'd 55; end 63 : begin scan_mem <= 7'd 62; end 64 : begin scan_mem <= 7'd 63; e nd endcaseendelse if (scan_type == 1'b1)begincase (cnt64)1 : begin scan_mem <= 7'd 0; end2 : begin scan_mem <= 7'd 8; end3 : begin scan_mem <= 7'd 16; end4 : begin scan_mem <= 7'd 24; end5 : begin scan_mem <= 7'd 1; end6 : begin scan_mem <= 7'd 9; end7 : begin scan_mem <= 7'd 2; end8 : begin scan_mem <= 7'd 10; end9: begin scan_mem <= 7'd 17; end 10 : begin scan_mem <= 7'd 25; end 11 : begin scan_mem <= 7'd 32; end 12 : begin scan_mem <= 7'd 40; end 13 : begin scan_mem <= 7'd 48; end 14 : begin scan_mem <= 7'd 56; end 15 : begin scan_mem <= 7'd 4; end 16 : begin scan_mem <= 7'd 49; end 17 : begin scan_mem <= 7'd 41; end 18 : begin scan_mem <= 7'd 33; end 19 : begin scan_mem <= 7'd 26; end 20 : begin scan_mem <= 7'd 18; end 21 : begin scan_mem <= 7'd 3; end 22 : begin scan_mem <= 7'd 11; end 23 : begin scan_mem <= 7'd 4; end 24 : begin scan_mem <= 7'd 12; end 25 : begin scan_mem <= 7'd 19; end 26 : begin scan_mem <= 7'd 27; end 27 : begin scan_mem <= 7'd 34; end 28 : begin scan_mem <= 7'd 42; end 29 : begin scan_mem <= 7'd 50; end 30 : begin scan_mem <= 7'd 58; end 31 : begin scan_mem <= 7'd 35; end 32 : begin scan_mem <= 7'd 43; end 33 : begin scan_mem <= 7'd 51; end 34 : begin scan_mem <= 7'd 59; end 35 : begin scan_mem <= 7'd 20; end 36 : begin scan_mem <= 7'd 28; end 37 : begin scan_mem <= 7'd 5; end 38 : begin scan_mem <= 7'd 13; end 39 : begin scan_mem <= 7'd 6; end 40 : begin scan_mem <= 7'd 14; end 41 : begin scan_mem <= 7'd 21; end 42 : begin scan_mem <= 7'd 29; end 43 : begin scan_mem <= 7'd 36; end 44 : begin scan_mem <= 7'd 44; end 45 : begin scan_mem <= 7'd 52; end 46 : begin scan_mem <= 7'd 60; end 47 : begin scan_mem <= 7'd 37; end 48 : begin scan_mem <= 7'd 45; end 49 : begin scan_mem <= 7'd 53; end 50 : begin scan_mem <= 7'd 61; end 51 : begin scan_mem <= 7'd 22; end 52 : begin scan_mem <= 7'd 30; end 53 : begin scan_mem <= 7'd 7; end 54 : begin scan_mem <= 7'd 15; end 55 : begin scan_mem <= 7'd 23; end 56 : begin scan_mem <= 7'd 31; end59 : begin scan_mem <= 7'd 54; end 60 : begin scan_mem <= 7'd 62; end61 : begin scan_mem <= 7'd 39; end 62 : begin scan_mem <= 7'd 47; end63 : begin scan_mem <= 7'd 55; end 64 : begin scan_mem <= 7'd 63; endendcaseendend/*****************************************************************************//* zigzag_in_reg1 and zigzag_in_reg2 are used to store the quantised DCT values encoded in zigzag order. Both registers use store the same DCT values. Data from reg1 is read out in the zigzag order and data from reg2 is read out in the alternate scan order */initialbeginzigzag_in_reg1[0] <= 12'b0; zigzag_in_reg1[1] <= 12'b0;zigzag_in_reg1[2] <= 12'b0; zigzag_in_reg1[3] <= 12'b0;zigzag_in_reg1[4] <= 12'b0; zigzag_in_reg1[5] <= 12'b0;zigzag_in_reg1[6] <= 12'b0; zigzag_in_reg1[7] <= 12'b0;zigzag_in_reg1[8] <= 12'b0; zigzag_in_reg1[9] <= 12'b0;zigzag_in_reg1[10] <= 12'b0; zigzag_in_reg1[11] <= 12'b0;zigzag_in_reg1[12] <= 12'b0; zigzag_in_reg1[13] <= 12'b0;zigzag_in_reg1[14] <= 12'b0; zigzag_in_reg1[15] <= 12'b0;zigzag_in_reg1[16] <= 12'b0; zigzag_in_reg1[17] <= 12'b0;zigzag_in_reg1[18] <= 12'b0; zigzag_in_reg1[19] <= 12'b0;zigzag_in_reg1[20] <= 12'b0; zigzag_in_reg1[21] <= 12'b0;zigzag_in_reg1[22] <= 12'b0; zigzag_in_reg1[23] <= 12'b0;zigzag_in_reg1[24] <= 12'b0; zigzag_in_reg1[25] <= 12'b0;zigzag_in_reg1[26] <= 12'b0; zigzag_in_reg1[27] <= 12'b0;zigzag_in_reg1[28] <= 12'b0; zigzag_in_reg1[29] <= 12'b0;zigzag_in_reg1[30] <= 12'b0; zigzag_in_reg1[31] <= 12'b0;zigzag_in_reg1[32] <= 12'b0; zigzag_in_reg1[33] <= 12'b0;zigzag_in_reg1[34] <= 12'b0; zigzag_in_reg1[35] <= 12'b0;zigzag_in_reg1[36] <= 12'b0; zigzag_in_reg1[37] <= 12'b0;zigzag_in_reg1[38] <= 12'b0; zigzag_in_reg1[39] <= 12'b0;zigzag_in_reg1[40] <= 12'b0; zigzag_in_reg1[41] <= 12'b0;zigzag_in_reg1[42] <= 12'b0; zigzag_in_reg1[43] <= 12'b0;zigzag_in_reg1[44] <= 12'b0; zigzag_in_reg1[45] <= 12'b0;zigzag_in_reg1[46] <= 12'b0; zigzag_in_reg1[47] <= 12'b0;zigzag_in_reg1[48] <= 12'b0; zigzag_in_reg1[49] <= 12'b0;zigzag_in_reg1[50] <= 12'b0; zigzag_in_reg1[51] <= 12'b0;zigzag_in_reg1[52] <= 12'b0; zigzag_in_reg1[53] <= 12'b0;zigzag_in_reg1[54] <= 12'b0; zigzag_in_reg1[55] <= 12'b0;zigzag_in_reg1[56] <= 12'b0; zigzag_in_reg1[57] <= 12'b0;zigzag_in_reg1[58] <= 12'b0; zigzag_in_reg1[59] <= 12'b0;zigzag_in_reg1[60] <= 12'b0; zigzag_in_reg1[61] <= 12'b0;zigzag_in_reg1[62] <= 12'b0; zigzag_in_reg1[63] <= 12'b0;zigzag_in_reg2[0] <= 12'b0; zigzag_in_reg2[1] <= 12'b0;zigzag_in_reg2[2] <= 12'b0; zigzag_in_reg2[3] <= 12'b0;zigzag_in_reg2[4] <= 12'b0; zigzag_in_reg2[5] <= 12'b0;zigzag_in_reg2[6] <= 12'b0; zigzag_in_reg2[7] <= 12'b0;zigzag_in_reg2[8] <= 12'b0; zigzag_in_reg2[9] <= 12'b0;zigzag_in_reg2[10] <= 12'b0; zigzag_in_reg2[11] <= 12'b0;zigzag_in_reg2[12] <= 12'b0; zigzag_in_reg2[13] <= 12'b0;zigzag_in_reg2[14] <= 12'b0; zigzag_in_reg2[15] <= 12'b0;zigzag_in_reg2[16] <= 12'b0; zigzag_in_reg2[17] <= 12'b0;zigzag_in_reg2[18] <= 12'b0; zigzag_in_reg2[19] <= 12'b0;zigzag_in_reg2[20] <= 12'b0; zigzag_in_reg2[21] <= 12'b0;zigzag_in_reg2[22] <= 12'b0; zigzag_in_reg2[23] <= 12'b0;zigzag_in_reg2[24] <= 12'b0; zigzag_in_reg2[25] <= 12'b0;zigzag_in_reg2[26] <= 12'b0; zigzag_in_reg2[27] <= 12'b0;zigzag_in_reg2[28] <= 12'b0; zigzag_in_reg2[29] <= 12'b0;zigzag_in_reg2[30] <= 12'b0; zigzag_in_reg2[31] <= 12'b0;zigzag_in_reg2[32] <= 12'b0; zigzag_in_reg2[33] <= 12'b0;zigzag_in_reg2[34] <= 12'b0; zigzag_in_reg2[35] <= 12'b0;zigzag_in_reg2[36] <= 12'b0; zigzag_in_reg2[37] <= 12'b0;zigzag_in_reg2[38] <= 12'b0; zigzag_in_reg2[39] <= 12'b0;zigzag_in_reg2[40] <= 12'b0; zigzag_in_reg2[41] <= 12'b0;zigzag_in_reg2[42] <= 12'b0; zigzag_in_reg2[43] <= 12'b0;zigzag_in_reg2[44] <= 12'b0; zigzag_in_reg2[45] <= 12'b0;zigzag_in_reg2[46] <= 12'b0; zigzag_in_reg2[47] <= 12'b0;zigzag_in_reg2[48] <= 12'b0; zigzag_in_reg2[49] <= 12'b0;zigzag_in_reg2[50] <= 12'b0; zigzag_in_reg2[51] <= 12'b0;zigzag_in_reg2[52] <= 12'b0; zigzag_in_reg2[53] <= 12'b0;zigzag_in_reg2[54] <= 12'b0; zigzag_in_reg2[55] <= 12'b0;zigzag_in_reg2[56] <= 12'b0; zigzag_in_reg2[57] <= 12'b0;zigzag_in_reg2[58] <= 12'b0; zigzag_in_reg2[59] <= 12'b0;zigzag_in_reg2[60] <= 12'b0; zigzag_in_reg2[61] <= 12'b0;zigzag_in_reg2[62] <= 12'b0; zigzag_in_reg2[63] <= 12'b0;end/* store zigzag input in the scan order: pipe1 */always @ (posedge CLK)if (rdy_in == 1'b1 && toggle_mem == 1'b0)zigzag_in_reg1[scan_mem]<= zigzag_in;else if (rdy_in == 1'b1 && toggle_mem == 1'b1)zigzag_in_reg2[scan_mem]<= zigzag_in;/* read out quantised DCT values in the counter 64 order :pipe2*/ always @ (posedge CLK)beginif (memread_rdy == 1'b1 && toggle_mem == 1'b1)qdct_out <= zigzag_in_reg1[cnt64];else if (memread_rdy == 1'b1 && toggle_mem == 1'b0)qdct_out <= zigzag_in_reg2[cnt64];else qdct_out <= 8'b0;end/* END MEMORY SECTION *//*****************************************************************************/always @ (posedge CLK or posedge RST)beginif (RST)begincnt64 <= 7'b0;endelse if (cnt64 < 7'b1000001)begincnt64 <= cnt64 + 1;endelsebegincnt64 <= 7'b0000001;endend/*****************************************************************************//* memread_rdy goes active 64 clks after rdy_in is active. This is to make sure that all the 64 zigzag input values are stored in the memory before reading it out in the clock order or decoding the zigzag order.*/always @ (posedge CLK or posedge RST)beginif (RST)beginmemread_rdy <= 1'b0;endelse if (rdy_in == 1'b1)beginif (cnt64 == 7'b1000000)memread_rdy <= 1'b1;elsememread_rdy <= memread_rdy ;endend/*****************************************************************************//* toggle_mem switches states every 64 clock cycles. This signal is used to choose between the 2 zigzag_in_reg memories. Due to zigzag order in which data is stored in, it is moreefficient to have all the 64 data ready in the memory before reading it out. Since the input data is continuous, while reading out is done from one memory, the input data is redirected to the 2nd memory for the next 64 cycles.*/always @ (posedge CLK or posedge RST)beginif (RST)begintoggle_mem <= 1'b0;endelse if (rdy_in == 1'b1)beginif (cnt64 == 7'b1000000)toggle_mem <= ~toggle_mem;elsetoggle_mem <= toggle_mem ;endend/*****************************************************************************/ endmodule以下是附加文档,不需要的朋友下载后删除,谢谢班主任工作总结专题8篇第一篇:班主任工作总结小学班主任特别是一年级的班主任,是一个复合性角色。

下三角矩阵的逆简单算法

下三角矩阵的逆简单算法下三角矩阵的逆简单算法下三角矩阵是指在一个方阵中,除了主对角线及其上方的元素外,其余元素都为零的矩阵。

下三角矩阵的逆矩阵也是一个下三角矩阵。

本文将介绍一种简单的算法来求解下三角矩阵的逆。

一、定义1.1 下三角矩阵在一个方阵中,如果该方阵除了主对角线及其上方的元素外,其余元素都为零,则该方阵被称为下三角矩阵。

1.2 逆矩阵设A为n级方阵,若存在n级方阵B,使得AB=BA=E(E为单位矩阵),则称B是A的逆矩阵,记作A-1。

二、求解方法2.1 算法思路设A是一个n×n的下三角矩阵,则有:$$A = \begin{bmatrix}a_{11} & 0 & 0 & \cdots & 0 \\a_{21} & a_{22} & 0 & \cdots & 0 \\a_{31} & a_{32} & a_{33} & \cdots & 0 \\\vdots & \vdots & \vdots& \ddots&\vdots\\ a_{n1} & a_{n2} & a_{n3} & \cdots & a_{nn} \end{bmatrix}$$设A的逆矩阵为B,则有:$$B = \begin{bmatrix}b_{11} & 0 & 0 & \cdots & 0 \\b_{21} & b_{22} & 0 & \cdots & 0 \\b_{31} & b_{32} & b_{33} & \cdots & 0 \\\vdots&\vdots&\vdots&\ddots&\vdots\\b_{n1}&b_{n2}&b_{n3}&\cdots&b_{nn}\end{bmatrix}$$则有:$$AB = BA = E$$即:$$\begin{aligned}a_{11}b_{11}&=1\\a_{21}b_{11}+a_{22}b_{21}&=0\\a_{31}b_{11}+a_{32}b_{21}+a_33*b_31 &=0\\...\\a_n1*b_11+a_n2*b_21+a_n3*b_31+...+a_nn*b_nn &=1\\ \end{aligned}$$由此可得到如下的求解方法。

verilog矩阵求逆运算单元

saribbon creater 用法

在Verilog中,实现矩阵求逆运算单元需要使用线性查找算法。

以下是一个简单的矩阵求逆运算单元的Verilog代码示例:```verilog

module matrix_inv(

input [3:0][3:0] mat,

output reg [3:0][3:0] inv

);

reg [3:0][3:0] adj;

reg [3:0][3:0] temp;

always @(mat) begin

adj = mat;

temp = adj;

inv = 0;

for (int i=0; i<4; i=i+1) begin

for (int j=0; j<4; j=j+1) begin

if (adj[i][j] != 0) begin

inv[i][j] = 1/adj[i][j];

for (int k=0; k<4; k=k+1) begin

if (k != j) begin

adj[i][k] = adj[i][k] * -inv[i][j];

end

end

end else begin

inv[i][j] = 0;

end

end

end

end

endmodule

```

这个模块接受一个4x4的矩阵作为输入,并输出其逆矩阵。

它使用线性查找算法来计算逆矩阵,该算法通过迭代地更新输入矩阵的每个元素来计算逆矩阵。

注意,这个模块没有进行错误检查,例如检查输入矩阵是否可逆。

在实际应用中,您可能需要添加额外的逻辑来处理这些情况。

verilog 获取稀疏矩阵求逆算法

verilog 获取稀疏矩阵求逆算法

摘要:

1.引言

2.稀疏矩阵与逆矩阵

3.逆矩阵求解方法

4.基于Verilog 的求逆算法实现

5.总结

正文:

1.引言

矩阵求逆是线性代数中的一个重要概念,逆矩阵可以用于矩阵的行列式计算、线性方程组求解等。

对于稀疏矩阵,由于其特殊的结构,求逆算法相对于稠密矩阵更为高效。

本文将介绍一种基于Verilog 的稀疏矩阵求逆算法。

2.稀疏矩阵与逆矩阵

稀疏矩阵是一种特殊的矩阵,其非零元素占据较小的篇幅。

由于稀疏矩阵的特殊性,可以采用压缩存储的方式进行存储,从而节省空间。

逆矩阵是矩阵的一种逆运算,求逆矩阵的过程就是寻找一个矩阵,使得该矩阵与原矩阵的乘积等于单位矩阵。

3.逆矩阵求解方法

对于稀疏矩阵的求逆,常用的方法有高斯消元法、LU 分解法等。

这些方法都可以通过迭代的方式求解逆矩阵。

其中,LU 分解法由于具有较好的数值稳定性,在实际应用中更为广泛。

4.基于Verilog 的求逆算法实现

本文将以LU 分解法为例,介绍如何基于Verilog 实现稀疏矩阵求逆算法。

首先,需要对稀疏矩阵进行LU 分解,将矩阵分解为下三角矩阵与上三角矩阵的乘积。

然后,利用高斯消元法求解逆矩阵。

最后,将求得的逆矩阵进行存储。

5.总结

本文介绍了基于Verilog 的稀疏矩阵求逆算法,通过LU 分解法与高斯消元法实现。

该方法可以有效地应用于硬件实现中,对于稀疏矩阵的求解具有较高的效率。

下三角矩阵求逆矩阵的例子

下三角矩阵求逆矩阵的例子

1、上三角矩阵的逆矩阵

将上三角矩阵划分成块矩阵,如上图所示,则其逆矩阵结果如下回图。

答

2、下三角矩阵的逆矩阵

将下三角矩阵划分成块矩阵,如上图所示,则其逆矩阵结果如下图。

3、只有主对角线不为零的矩阵

主对角元素取倒数,原位置不变。

4、只有副对角线不为零的矩阵

副对角元素取倒数,位置颠倒。

示例如下:

扩展资料

矩阵求逆的求法

(1)初等变换法,通过初等变换将A矩阵变换成单位矩阵,则对应的单位矩阵变换成B矩阵,B矩阵即为A矩阵的逆矩阵,(A I)->(I B);

(2)伴随阵法,公式为:;

(3)利用定义求逆矩阵

设A、B都是n阶方阵,如果存在n阶方阵B使得AB=BA=E,则称A为可逆矩阵,而称B为A的逆矩阵。

(4)恒等变形法

恒等变形法求逆矩阵的理论依据为逆矩阵的定义,此方法也常用

与矩阵的理论推导上,就是通过恒等变形把要求的值化简出来,题目中的逆矩阵可以不求,利用,把题目中的逆矩阵化简掉。

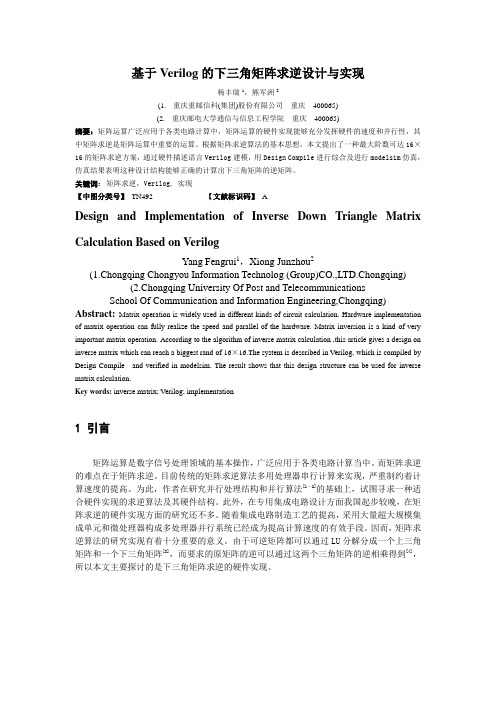

基于Verilog的下三角矩阵求逆设计与实现

基于Verilog的下三角矩阵求逆设计与实现杨丰瑞1,熊军洲2(1.重庆重邮信科(集团)股份有限公司重庆400065)(2.重庆邮电大学通信与信息工程学院重庆400065)摘要:矩阵运算广泛应用于各类电路计算中,矩阵运算的硬件实现能够充分发挥硬件的速度和并行性,其中矩阵求逆是矩阵运算中重要的运算。

根据矩阵求逆算法的基本思想,本文提出了一种最大阶数可达16×16的矩阵求逆方案,通过硬件描述语言Verilog建模,用Design Compile进行综合及进行modelsim仿真,仿真结果表明这种设计结构能够正确的计算出下三角矩阵的逆矩阵。

关键词:矩阵求逆,Verilog, 实现【中图分类号】TN492 【文献标识码】ADesign and Implementation of Inverse Down Triangle Matrix Calculation Based on VerilogYang Fengrui1,Xiong Junzhou2(1.Chongqing Chongyou Information Technolog (Group)CO.,LTD.Chongqing)(2.Chongqing University Of Post and TelecommunicationsSchool Of Communication and Information Engineering,Chongqing) Abstract: Matrix operation is widely used in different kinds of circuit calculation. Hardware implementation of matrix operation can fully realize the speed and parallel of the hardware. Matrix inversion is a kind of very important matrix operation. According to the algorithm of inverse matrix calculation ,this article gives a design on inverse matrix which can reach a biggest rand of 16×16.The system is described in Verilog, which is compiled by Design Compile and verified in modelsim. The result shows that this design structure can be used for inverse matrix calculation.Key words: inverse matrix; Verilog; implementation1 引言矩阵运算是数字信号处理领域的基本操作,广泛应用于各类电路计算当中。

下三角复矩阵求逆的ASIC 设计及实现

下三角复矩阵求逆的ASIC设计及实现熊洋郑建宏重庆邮电大学 400065摘要:本论文提出了一种便于ASIC实现的矩阵求逆算法,可以完成对1到16维下三角复矩阵的求逆运算,并用Verilog硬件描述语言进行实现。

利用SMIC 0.13um工艺库和Synopsys 公司的Design Compiler工具对代码进行了综合,并进行了低功耗优化,最后使用Modelsim 工具对代码进行了仿真验证,得到的结果同C代码模拟的结果完全一致,证明本模块完全可以达到预期目的。

关键词:ASIC;矩阵求逆;下三角复矩阵;Verilog;综合;仿真ASIC Designing and Implementation of Lower Triangular Complex Matrix InverseXiong Yang Zheng JianhongChong Qing University of Posts and Telecommunications 400065Abstract:This Paper presents a kind of matrix inverse arithmetic suitable for ASIC implementation, which could process 1~16 dimension lower triangular complex matrix, and is coded by Verilog HDL. Using SMIC 0.13um process library,we synthesis the codes by Design Compiler and optimize the power. At last, we verify the function of the module using Modelsim, and the result of Modelsim simulation is consonant with c code simulation, which prove that our module achieve anticipative goals.Key words:ASIC;matrix inverse;lower triangular complex matrix;Verilog;Synthesis;simulation 1、概述矩阵运算是很多科学运算和工程运用中的常见运算,大多数科学计算都可以归结为矩阵问题,在实际工程项目中更是如此。

一种下三角复矩阵求逆方法的IP设计与实现

一种下三角复矩阵求逆方法的IP设计与实现佚名【期刊名称】《电子测试》【年(卷),期】2011(000)010【摘要】矩阵运算是很多科学运算中的常见运算,矩阵求逆在矩阵运算中有着举足轻重的作用,在数字信号处理过程中常常被运用到。

本文根据一种便于ASIC实现的矩阵求逆算法,提出了一种最大阶数为16阶复矩阵求逆的IP设计串行实现方法。

首先本文分析了算法的特殊性,然后提出此IP设计方法的实现思路和结构,最后用Verilog语言进行实现并用Modelsim进行仿真验证,证明了此方法能够正确实现高速流水的矩阵求逆运算,并且易于修改矩阵规模,控制更方便,实现更容易,适用于工程应用及科学研究。

%Matrix inversion plays a significant role in matrix operation area,which is always applied to digital signal processing.Based on a matrix algorithm which suitable for ASIC implementation,this paper present a serial design method,whose maximum dimension is 16.Firstly it analyzed the particularity of the algorithm,then it offered the design structure and method.Finally it was coded by verilog HDL and simulated using Modelsim3.0,which proves this method can rapidly correctly finish the operation and easier to modify,control,and suitable for the engineering application and scientific research.【总页数】4页(P9-12)【正文语种】中文【中图分类】TP311.52【相关文献】1.三角矩阵求逆的一种方法 [J], 杨明顺2.基于Verilog的下三角矩阵求逆设计与实现 [J], 杨丰瑞;熊军洲3.一种基于约化因子上三角矩阵求逆的FPGA实现方法 [J], 周杨;王佳薇;黄志洪;杨海钢4.下三角复矩阵求逆的ASIC设计及实现 [J], 熊洋;郑建宏5.一种基于约化因子上三角矩阵求逆的FPGA实现方法 [J], 周杨;王佳薇;黄志洪;杨海钢;;;;;;因版权原因,仅展示原文概要,查看原文内容请购买。

任意维矩阵求逆的FPGA设计与实现

任意维矩阵求逆的FPGA设计与实现王锐胡永华马亮杜福慧(合肥工业大学微电子设计研究所 wangrui@)摘要:矩阵运算广泛应用于各类电路计算中,矩阵运算的硬件实现能够充分发挥硬件的速度和并行性。

其中矩阵求逆是矩阵运算中重要的运算,针对目前多维矩阵难以设计的情况,本文提出了一种任意维矩阵求逆的硬件实现方法,实验达到了预期目标。

任意维矩阵求逆的硬件实现在数字信号处理领域将具有广泛的应用前景。

关键字:任意维矩阵求逆 LU分解现场可编程门阵列Abstract: Matrix operation is widely used in different kinds of circuit calculation. Hardware implementation of matrix operation can fully realize the speed and parallel of the hardware. Matrix inversion is a kind of very important matrix operation. Due to the difficulty of design of multi-dimension matrix, a kind of hardware implementation method of arbitrary dimension matrix inversion is proposed and the result of the experiment can meet the requirement. The hardware implementation of arbitrary dimension matrix inversion would have more widely application prospect in digital signal processing field.Keyword: arbitrary dimension matrix inversion LU decomposition FPGA 矩阵运算是数字信号处理领域内的基本操作,广泛应用于各类电路计算中,在诸如DCT 变换、LDPC编解码领域应用非常广泛。

verilog求倒数-ROM实现方法

verilog求倒数-ROM实现方法采用线性逼近法结合32段线性查找表的方式来实现1/z的计算。

首先将1/32-1/64的定点化数据存放到ROM中,ROM中存放的是扩大了2^20 次方的数字四舍五入后的整数部分。

n值越大,精度越大,误差越小。

这里取n=20;ROM中存储的数据是1/(32+i)*2^20的四舍五入的整数部分。

32-64间的数据可以通过查表来实现,其他的数据则采用的是线性逼近的方法。

线性逼近的步骤为:1.确定最高非零比特位的位置2.对z进行左移或者右移,得到zp3.zp查找ROM,得到1/zp,以及1/(zp+1),4.求的1/zp-1/(zp+1),为误差A5.N=z-zp*2^(m-5)6.B=A/2^(m-5)*N7.将扩大的部分缩小回去,或者缩小了的放大回去,那么1/z=(1/zp-B)*(1/2^(m-5))代码插入:module top_inv(input clk,syn_rst,input [20:0]dataa,input [20:0]datab,//input [20:0]ampout,output reg [19:0]inv// output reg done);reg [4:0] address1;reg [4:0 ]address2;wire [4:0] m;// wire done;reg [19:0]invr;reg [20:0] ampout_r;reg [20:0] ampout_r1;wire [20:0] ampout;reg [20:0] ampoutr1,ampoutr2,ampoutr3,ampoutr4; wire [19:0] inv_r1;wire [19:0] inv_r2;reg [20:0] diff_r;reg [19:0] diffr;reg [19:0] diff;reg [19:0] N;reg [19:0] N1;reg en;always @(posedge clk or negedge syn_rst)beginif(~syn_rst)beginampoutr1<=21'd0;ampoutr2<=21'd0;ampoutr3<=21'd0;ampoutr4<=21'd0;endelseampoutr1<=ampout;ampoutr2<=ampoutr1;ampoutr3<=ampoutr2;ampoutr4<=ampoutr3;endreg [19:0] inv_r1t1,inv_r1t2,inv_r1t3; always@(posedge clk or negedge syn_rst) beginif(~syn_rst)begininv_r1t1<=0;inv_r1t2<=0;inv_r1t3<=0;endelsebegininv_r1t1<=inv_r1;inv_r1t2<=inv_r1t1;inv_r1t3<=inv_r1t2;endendreg [4:0] mt1,mt2,mt3,mt4,mt5;always@(posedge clk or negedge syn_rst) beginif(~syn_rst)beginmt1<=0;mt2<=0;mt3<=0;mt4<=0;mt5<=0;endelsebeginmt1<=m;mt2<=mt1;mt3<=mt2;mt4<=mt3;mt5<=mt4;endendreg sel;reg selr1,selr2;always @(posedge clk or negedge syn_rst) beginif(~syn_rst)begindiff<=0;diffr <= 0;ampout_r<='b0;ampout_r1<=0;address1<='b0;address2<='b0;en<=0;sel<=0;endelsebegin// if(done)//beginif((ampout>=32)&&(ampout<=64)) beginampout_r<=0;ampout_r1<=0;address1<=ampoutr3-32; address2<= 0;diff <= 0;diffr <= 0;N <= 0;N1<= 0;en<=0;//不需要计算m的值sel<=0;selr1<=0;selr2<=0;endelsebeginen<=1;//需要计算m的值if(m>5)begin// ampoutrr<=ampout;ampout_r<=ampoutr1>>(m-5); ampout_r1<=ampout_r;//zp address1<=ampout_r-32;///inv_r1 address2<=ampout_r-31;///inv_r2 diff <= inv_r1-inv_r2;diffr <=diff;N1<=ampout_r1<<(mt2-5);N<=ampoutr4-N1;selr1<=1;selr2 <= selr1;sel <= selr2;endif(m<5)begin//ampoutrr<=ampout;ampout_r<=ampoutr1<<(5-m);// mt4 mt3 mt2ampout_r1 <= ampout_r;// N N1 ampout_r1address1<=ampout_r-32;///mt4 inv_r1address2<=ampout_r-31;//inv_r1t3 inv_r2 mt1diff <= inv_r1-inv_r2;//diff_r<<diffr<<diff<<address<<ampout_r<< m <<ampoutdiffr <=diff; // ampoutr3 ampoutr2 ampoutr1N1<=ampout_r1>>(5-mt2);N<=ampoutr4-N1;selr1<=1;selr2 <= selr1;sel <= selr2;endendend// endend// assign diff=sel?(inv_r1-inv_r2):'b0;//assign N=sel?(ampout-N1):0;//assign diff_r = en?(diff*N>>(m-5)):0;//assign diff_r = (m>5)?(diff*N>>(m-5)):(diff*N<<(5-m));// assign inv = sel?(inv_r1-diff_r)>>(m-5):inv_r1;always@(posedge clk or negedge syn_rst)beginif(~syn_rst)begin// done<=0;diff_r<=0;endelsebeginif(sel) beginif(m>5)begindiff_r <= diffr*N>>(mt4-5);invr<=(inv_r1t3-diff_r)>>(mt5-5);// done<=1;endelse begindiff_r <= diffr*N<<(5-mt4);invr<=(inv_r1t3-diff_r)<<(5-mt5);// done<=1;endendelsebegindiff_r<=0;invr<=inv_r1t3;endendendalways@(posedge clk or negedge syn_rst) beginif(~syn_rst)beginendelsebeginif(invr)inv<= invr;elseinv<=inv;endend//ROM 核的例化rom u_rom(.clk(clk),.address1(address1),.address2(address2),.inv_r1(inv_r1),.inv_r2(inv_r2)//,//.c(c));//例化寻找最高非零位not_0 u_not_0 (// port map - connection between master ports and signals/registers.ampout(ampout),.clk(clk),.m(m),.en(en),.syn_rst(syn_rst));complex_abs u_comlex_abs(.syn_rst(~syn_rst),.dataa(dataa),.datab(datab),.ampout(ampout));endmodule那么最终的仿真结果:如果直接查询的话,结果输出延时一个时钟周期,如果线性逼近的方法得到,延时3-5个时钟周期,这里周期设定为20ns;占用资源报告:增加一个求平方根的模块以后的仿真结果(数据输入后,一共需要约10个时钟周期才可以计算出一个平方更求导数值)。

矩阵求逆运算的VLSI实现

matrix fast inverse

calculation and get high precision.

。

Key words:systolic array;matrix inversion;LU deeompose;VLSl

0引 言

●

矩阵运算是科学与工程计算中的基本问题,科学 计算中有很大一部分可以归结为矩阵运算,而矩阵运 算的难点在于矩阵求逆。传统的矩阵求逆算法多用处 理器串行计算来实现,严重制约着计算速度的提高。 为加快矩阵求逆的运算速度,可以采用硬件实现的方 法。在这一方面,已经有很多人进行了深入研究,特别 是使用基于心动阵列的方法来构造电路结构,使用十 分广泛【1--3]。这些论文研究的重点是通过对相应算法 的研究改进,最大限度地提高资源的利用效率及时空 复杂度,而忽略电路结构本身的硬件实现难度。例如 文献[2]中使用QR分解的方法来实现矩阵求逆,提出 的电路结构非常紧凑,复用率非常高,但是基本处理单 元需要完成的运算非常复杂,不但涉及比较复杂的乘 除运算,还需要进行开平方操作,这不仅增加了硬件开 销,更主要的是大大增加了硬件实现的难度。事实上, 很多时候工程上涉及的矩阵求逆对硬件开销及速度并

-222·

计算机技术与发展

元素的各个乘数研“(i=歹+1,歹+2,…,歹=竹一1,歹 =n),然后将它们沿水平方向向右传送,参加内积步 计算,最后由阵列右端输出。至整个计算结束时,PE。 中所存数据是【,的元素U“,而阵列的第i行输出是矩 阵L的第,z—i列元素。在L矩阵元素输出之后,通过 控制信号的设定,紧接着输出【,的元素,阵列的第i行 输出的是矩阵U的第i行元素。

顶部按列输入,其中a{(m)比a自晚一个时钟周期输 入。计算后,所得到的上三角矩阵U的元素存于各个 PE之中。当A的第一行元素经过到第一行PE时,它们 被存入第一行相应PE之中,之后的各行元素经过第 一行PE时,只进行相应的变换而不再存入PE之中。 A的第二行元素经过第一行PE变换后存人第二行相 应的PE当中,之后各行元素经过第二行PE时也只进 行相应变换后流向下一行PE。以此类推,直至A矩阵 第佗行元素(经过了,l一1次变换)存入第珂行PE为 止。第i行左端的圆形PE依次产生消去第i列下三角

下三角矩阵的逆简单算法

下三角矩阵的逆简单算法引言在线性代数中,矩阵是一种常见且重要的数学对象。

矩阵的逆是矩阵计算中的一个重要部分,能够帮助我们解线性方程组和进行向量空间的变换。

本文将讨论下三角矩阵的逆以及一种简单的算法用于求解。

我们首先介绍下三角矩阵的定义和性质,然后详细描述逆矩阵的概念和求解方法。

下三角矩阵下三角矩阵是一种特殊的矩阵,其中所有的非零元素都出现在主对角线及其下面的位置。

下三角矩阵具有以下的特点: - 所有的主对角线上的元素都不为零。

- 所有的主对角线上方的元素都为零。

- 矩阵的右上方的元素都为零。

下三角矩阵的一般形式如下:[]其中,a ij表示矩阵中第i行第j列的元素。

下三角矩阵的逆矩阵的逆是指满足乘积为单位矩阵的矩阵。

对于下三角矩阵的逆,我们可以使用简单的算法来求解。

首先,我们需要明确下面的定理:定理:下三角矩阵的逆也是下三角矩阵。

基于这个定理,我们可以设计一个简单的算法来求解下三角矩阵的逆。

以下是该算法的伪代码:1.初始化一个和原矩阵大小相同的单位矩阵作为逆矩阵。

2.从上到下便利每一行,从左到右遍历每一列。

3.对于每一个元素a ij,如果i=j,则将逆矩阵中相应位置的元素设为1。

4.对于每一个元素a ij,如果i>j,则逆矩阵中相应位置的元素为以下公式的结果: [ b_{ij} = -{k=j+1}^{i} a{ik} b_{kj} ] 其中,b表示逆矩阵中的元素。

5.返回逆矩阵作为结果。

这个算法通过对下三角矩阵的每个元素进行逆推来计算逆矩阵的元素值。

值得注意的是,由于逆矩阵也是下三角矩阵,所以我们只需要计算下三角矩阵的下半部分即可。

算法的正确性证明我们需要对上述算法进行正确性的证明。

以下是一个简要的证明过程:命题:上述算法能够正确地求解下三角矩阵的逆。

证明:我们通过对算法的每个步骤进行推导来证明算法的正确性。

•步骤1:初始化逆矩阵为单位矩阵,这是正确的,因为单位矩阵乘以任何矩阵都会得到原矩阵。

下三角分块矩阵求逆

下三角分块矩阵求逆在线性代数中,矩阵求逆是一个重要的运算。

其中,三角分块矩阵是一种特殊的矩阵形式,它具有一定的结构性质,可以简化求逆运算的复杂度。

本文将介绍三角分块矩阵的基本概念,并探讨如何求解其逆矩阵。

我们来了解一下什么是三角分块矩阵。

三角分块矩阵是指一个矩阵被分成多个子矩阵,并且这些子矩阵按照特定的规则排列成一个整体。

通常情况下,三角分块矩阵可以分为上三角和下三角两种形式。

上三角形式的三角分块矩阵中,主对角线以下的元素全为零;而下三角形式的三角分块矩阵中,主对角线以上的元素全为零。

三角分块矩阵的结构性质使其在求逆运算中具有独特的优势。

接下来,我们来探讨如何求解三角分块矩阵的逆矩阵。

对于上三角形式的三角分块矩阵,我们可以利用回代法进行求解。

回代法是一种逐步迭代的方法,从最后一行开始,逐行计算逆矩阵的每一行。

具体步骤如下:1. 从最后一行开始,求解最后一行的逆矩阵;2. 将最后一行的逆矩阵与上一行的元素进行相乘,得到上一行的逆矩阵;3. 重复上述步骤,直到计算得到整个逆矩阵。

对于下三角形式的三角分块矩阵,我们可以利用类似的方法进行求解。

不同之处在于,我们需要从第一行开始,逐行计算逆矩阵的每一行。

在实际应用中,三角分块矩阵的求逆运算可以大大简化计算的复杂度。

这是因为三角分块矩阵的结构性质使得回代法的计算过程可以高效地进行。

此外,三角分块矩阵的求逆运算还可以通过并行计算来进一步提高计算速度。

需要注意的是,三角分块矩阵求逆的过程并不总是可行的。

在某些情况下,三角分块矩阵可能不存在逆矩阵。

这通常发生在主对角线上的某个子矩阵不可逆时。

因此,在进行三角分块矩阵求逆之前,我们需要对矩阵的结构进行仔细的分析,以确定是否存在逆矩阵。

总结起来,三角分块矩阵求逆是一个重要而有挑战性的运算。

通过合理利用三角分块矩阵的结构性质,我们可以简化求逆运算的复杂度,并提高计算效率。

然而,我们需要注意到求逆的可行性,并在实际应用中进行适当的分析和判断。

下三角分块矩阵求逆

下三角分块矩阵求逆在线性代数中,矩阵求逆是一个重要的运算,它可以帮助我们解决许多实际问题。

其中一种特殊的矩阵结构是三角分块矩阵。

本文将介绍什么是三角分块矩阵以及如何对其进行求逆运算。

我们来了解一下什么是三角分块矩阵。

三角分块矩阵是指一个矩阵被分成几个对角块,而其他位置上的元素均为零的矩阵。

这种结构在某些问题中具有很好的性质,可以简化运算过程。

三角分块矩阵通常可以分为上三角分块矩阵和下三角分块矩阵两种。

对于一个上三角分块矩阵,它的对角线上方的元素均为零,而对角线上的元素则可以是任意的矩阵。

同样地,下三角分块矩阵的对角线下方的元素为零,对角线上的元素可以是任意的矩阵。

我们将以上三角分块矩阵为例进行讲解。

要求一个上三角分块矩阵的逆矩阵,我们可以使用分块矩阵求逆的方法。

具体步骤如下:我们将上三角分块矩阵表示为以下形式:A = [A11 A12 A13;0 A22 A23;0 0 A33]其中,A11、A12、A13、A22、A23和A33都是矩阵。

接下来,我们将对A进行求逆运算。

我们要求A11的逆矩阵。

因为A11是一个矩阵,我们可以使用相应的方法来求解它的逆矩阵。

假设A11的逆矩阵为B11,那么我们有:A11 * B11 = I其中,I是单位矩阵。

接下来,我们将计算A22-A23 * B11 * A12的逆矩阵。

我们可以使用舒尔补的方法来求解它的逆矩阵。

假设A22-A23 * B11 * A12的逆矩阵为B22,那么我们有:(A22 - A23 * B11 * A12) * B22 = I依此类推,我们可以继续求解A33的逆矩阵。

我们可以将所有的逆矩阵组合起来,得到A的逆矩阵:A^-1 = [B11 -B11 * A12 * B22 -B11 * A13 * B33;0 B22 -B22 * A23 * B33;0 0 B33 ]通过以上步骤,我们成功地求得了上三角分块矩阵A的逆矩阵。

同样地,对于下三角分块矩阵也可以使用类似的方法进行求解。

下三角矩阵的从逆

下三角矩阵的从逆

下三角矩阵是一个方阵,其对角线以下的所有元素都不为零(或者说,对角线以上的元素都为零)。

对于下三角矩阵,它的逆矩阵有一些特殊的性质。

首先,一个下三角矩阵的逆矩阵(如果存在的话)也是下三角矩阵。

这一点对于上三角矩阵也同样成立。

要求一个下三角矩阵的逆矩阵,通常可以使用标准的逆矩阵计算方法,如高斯消元法或者利用行列式和伴随矩阵的方法。

不过,对于下三角矩阵,有一些更高效的算法可以利用其特殊结构来加速计算。

在计算下三角矩阵的逆矩阵时,需要注意矩阵的非奇异性(即可逆性)。

一个矩阵是可逆的,当且仅当它的行列式不为零。

对于下三角矩阵,其行列式等于对角线上元素的乘积。

因此,如果对角线上有任何一个元素为零,那么该下三角矩阵就是奇异的,不可逆的。

具体的下三角矩阵求逆的算法可能比较复杂,涉及到矩阵运算和线性代数的知识。

在实际应用中,通常会使用数值计算软件或者编程库来进行矩阵求逆的操作,这些软件和库通常已经优化了相关的算法,以提高计算的效率和准确性。

请注意,以上信息是基于一般的线性代数知识,并没有提供具体的下三角矩阵求逆的公式或者算法步骤。

在实际应用中,应该根据具体的问题和需求选择合适的数值计算方法或者软件工具来进行计算。

矩阵求逆运算的VLSI实现

矩阵求逆运算的VLSI实现

郭春煊;毛志刚;谢憬

【期刊名称】《计算机技术与发展》

【年(卷),期】2008(18)5

【摘要】矩阵运算广泛应用于各类电路计算中,矩阵运算的硬件实现能够充分发挥硬件的速度和并行性.其中矩阵求逆是矩阵运算中重要的运算.为加速矩阵求逆,研究构造出一种非常易于实现的基于心动阵列的矩阵求逆的电路结构.通过硬件描述语言Verilog建模,VCS仿真及用Design Compile进行综合,结果表明这种并行结构能快速实现矩阵求逆,且运算精度较高.

【总页数】5页(P219-223)

【作者】郭春煊;毛志刚;谢憬

【作者单位】上海交通大学,微电子学院,上海,200240;上海交通大学,微电子学院,上海,200240;上海交通大学,微电子学院,上海,200240

【正文语种】中文

【中图分类】TP301.6

【相关文献】

1.有限域求逆器的设计与VLSI实现 [J], 沈晓强;郭阳

2.分块矩阵的行列式运算与求逆运算 [J], 聂永红

3.一种用于矩阵求逆的原位替换算法及硬件实现 [J], 张多利; 蒋雯; 叶紫燕; 宋宇鲲; 汪健

4.基于浮点数的正定矩阵求逆硬件实现 [J], 林立芃;王仁平;王景铭;宋传亮;朱梓杰;

詹家立

5.基于脉动阵列的LU算法矩阵求逆VLSI结构 [J], 孙泉;赵明;张秀君

因版权原因,仅展示原文概要,查看原文内容请购买。

改进的矩阵求逆的FPGA设计和实现

改进的矩阵求逆的FPGA设计和实现

李颖异

【期刊名称】《中国有线电视》

【年(卷),期】2006(000)007

【摘要】通过对上三角矩阵求逆算法的研究,提出一种优化的适合FPGA实现的并行求逆的结构,并运用Verilog硬件描述语言对其建模,通过硬件仿真工具QuartusII对其进行编译仿真,仿真结果表明,改进的并行结构能够在n个时钟周期内完成n阶上三角矩阵的求逆.

【总页数】3页(P673-675)

【作者】李颖异

【作者单位】电子科技大学,四川,成都,610054

【正文语种】中文

【中图分类】TN949.197

【相关文献】

1.一种基于改进的Block-FFT算法的联合检测矩阵求逆算法 [J], 刘正堂;任修坤;胡捍英

2.多载荷识别频响函数矩阵求逆法的改进算法 [J], 田燕;王菁;郑海起

3.自适应波束形成采样矩阵求逆算法的改进 [J], 杨亦凡;王华奎;柯恒英

4.任意维矩阵求逆的FPGA设计与实现 [J], 王锐;胡永华;马亮;杜福慧

5.对逆矩阵由等价标准形求逆方法的改进 [J], 杨静

因版权原因,仅展示原文概要,查看原文内容请购买。

cordic算法求角度的verilog实现 -回复

cordic算法求角度的verilog实现-回复Cordic算法是一种常用于计算三角函数和超越函数的高效算法。

它的高效性和精度使其成为数字信号处理、图像处理、通信系统等领域的重要工具。

在本篇文章中,我们将探讨Cordic算法在Verilog中的实现,并一步一步地解释其原理和实现细节。

首先,让我们来了解Cordic算法的基本原理。

Cordic算法的核心思想是将一个复杂的旋转操作分解为多个简单的旋转操作的叠加。

通过不断迭代这些简单的旋转操作,我们可以逐步逼近目标旋转角度。

Cordic算法最初是由Volder于1959年提出的,后来由Cordic团队在1968年对其进行改进和完善。

Cordic算法的关键是通过旋转向量和旋转角度的迭代叠加来求解旋转角度。

假设我们要求解的旋转角度为θ,我们可以将θ分解为多个简单角度的叠加,即θ=θ1+θ2+...+θn。

为了简化运算,Cordic算法将旋转角度限定在[-π/2,π/2]范围内,并使用四个象限旋转来处理不同的角度范围。

在Verilog中,我们可以使用固定点数表示来实现Cordic算法。

固定点表示使用固定位宽和小数位数来表示实数,可以提高计算的精度和效率。

下面是Cordic算法在Verilog中的实现步骤:1. 定义输入和输出:首先,我们需要定义输入和输出的信号。

输入信号是所要求解的旋转角度θ,输出信号是计算得到的旋转角度的固定点表示。

2. 初始化参数:接下来,我们需要初始化Cordic算法所需的参数。

这些参数包括旋转向量[x, y]和旋转角度的近似值。

初始时,旋转向量为[1, 0],旋转角度的近似值为0。

3. 迭代计算:通过不断迭代计算,我们可以逐步逼近目标旋转角度。

在每一次迭代中,我们使用以下步骤进行计算:a. 计算旋转向量的模长:利用乘法和加法操作,我们可以计算旋转向量的模长。

b. 更新旋转向量:将旋转向量按照当前迭代的旋转角度进行旋转操作。

c. 更新旋转角度的近似值:将当前迭代的旋转角度与上一次迭代的旋转角度相加,得到新的旋转角度的近似值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Verilog的下三角矩阵求逆设计与实现杨丰瑞1,熊军洲2(1.重庆重邮信科(集团)股份有限公司重庆400065)(2.重庆邮电大学通信与信息工程学院重庆400065)摘要:矩阵运算广泛应用于各类电路计算中,矩阵运算的硬件实现能够充分发挥硬件的速度和并行性,其中矩阵求逆是矩阵运算中重要的运算。

根据矩阵求逆算法的基本思想,本文提出了一种最大阶数可达16×16的矩阵求逆方案,通过硬件描述语言Verilog建模,用Design Compile进行综合及进行modelsim仿真,仿真结果表明这种设计结构能够正确的计算出下三角矩阵的逆矩阵。

关键词:矩阵求逆,Verilog, 实现【中图分类号】TN492 【文献标识码】ADesign and Implementation of Inverse Down Triangle Matrix Calculation Based on VerilogYang Fengrui1,Xiong Junzhou2(1.Chongqing Chongyou Information Technolog (Group)CO.,LTD.Chongqing)(2.Chongqing University Of Post and TelecommunicationsSchool Of Communication and Information Engineering,Chongqing) Abstract: Matrix operation is widely used in different kinds of circuit calculation. Hardware implementation of matrix operation can fully realize the speed and parallel of the hardware. Matrix inversion is a kind of very important matrix operation. According to the algorithm of inverse matrix calculation ,this article gives a design on inverse matrix which can reach a biggest rand of 16×16.The system is described in Verilog, which is compiled by Design Compile and verified in modelsim. The result shows that this design structure can be used for inverse matrix calculation.Key words: inverse matrix; Verilog; implementation1 引言矩阵运算是数字信号处理领域的基本操作,广泛应用于各类电路计算当中。

而矩阵求逆的难点在于矩阵求逆。

目前传统的矩阵求逆算法多用处理器串行计算来实现,严重制约着计算速度的提高。

为此,作者在研究并行处理结构和并行算法[1~2]的基础上,试图寻求一种适合硬件实现的求逆算法及其硬件结构。

此外,在专用集成电路设计方面我国起步较晚,在矩阵求逆的硬件实现方面的研究还不多。

随着集成电路制造工艺的提高,采用大量超大规模集成单元和微处理器构成多处理器并行系统已经成为提高计算速度的有效手段。

因而,矩阵求逆算法的研究实现有着十分重要的意义。

由于可逆矩阵都可以通过LU分解分成一个上三角矩阵和一个下三角矩阵[3],而要求的原矩阵的逆可以通过这两个三角矩阵的逆相乘得到[4],所以本文主要探讨的是下三角矩阵求逆的硬件实现。

2 算法介绍假设以下矩阵A 为原矩阵,1-A 是A 的逆矩阵,n 是A 的维数。

则: 110...001 (00)0 (00)0...1E A A -==⨯11112122212212120...00...0...0...0..............................n n nn n n nn a b a a b b a a a b b b =⨯ 由矩阵的乘法可知:,,,()i i j i k k j k jc a b ==*∑ (j<=i )而:0,=j i c (j i ≠); 1,=j i c ( j i = )根椐以上可知,可首先得到一些初始值:i i i i a b ,,/1= (i=1,2,…,n)然后可得出计算1-A 其他值的递推公式: ∑-=*-=1,,,,)(1i j k j k k i i i j i b a a b =1,,,()i i i i k k j k j b a b -=-*∑(i=1,2,…,n ; j=1,2….,i -1) 3 硬件实现3.1 总体设计结构本文所设计的矩阵求逆算法模块(matrix_top )共分为:接口模块(regif ),控制模块(ctrl),地址产生模块(addrgen),运算处理模块(proc ),和存储器模块(mem )。

其中存储器模块包括输入存储器模块(inbuf )和输出存储器模块(outbuf )。

总体结构图如图1所示:图1 总体结构图3.2 模块介绍3.2.1接口模块(regif)与外部的ZSP总线相连实现接口功能,数据通过接口模块写入到输入存储器或是控制寄存器中,当zio_sel为高电平时,写入数据到输入寄存器中,当zio_sel 为低电平时,写入数据到控制寄存器中,控制寄存器指示矩阵的维数和启动信号;当运算完成,数据都存放到输出寄存器后,此接口模块产生一个中断,通知ZSP从输出存储器(outbuf)中读出数据。

3.2.2控制模块(ctrl)为一个状态数为5的有限状态机,产生整个运算状态信息,控制运算的进行。

如图2所示图2 ctrl模块中状态机示意图当处于IDLE(即空闲)状态时,表示运算还未开始或是运算结束,此时finish信号为零。

一旦接收到来自接口模块的启动运算信号时,即转为CHECK状态,CHECK状态用于对原矩阵对角线上的数据求倒数,并找出最大值,根据所求的最大值计算出矩阵归一化时的移位个数,当求得此归一化的移位个数时,即转为DIAG状态。

DIAG状态表示对原矩阵对角线上的数据进行求倒运算,并根据归一化的移动个数进行截位,此运算完成后,即转为OTHER 状态,根据前面所述原理计算非对角线上的数据,全部数据运算完毕后,发出一个finish 信号,并转入FINISH状态。

FINISH状态根据信号finish的反馈信号,对finish信号进行清零,并转入到下一个状态,即IDLE状态。

3.2.3地址产生模块(addrgen)该模块主要用于产生读写数据的地址。

当处于CHECK和DIAG两个状态时,该模块产生原矩阵对角线上的地址和逆矩阵对角线的地址。

当处于计算非对角线的数据时,该模块根据矩阵在存储器中存放的位置(矩阵数据在存储器中按行存放)及计算原理,依次计算时原矩阵和逆矩阵的读地址和逆矩阵的写数据地址。

3.2.4处理模块(proc)对矩阵进行求逆运算,从输入存储器中读取原矩阵的信息,求逆后将所得的结果数据存入到输出矩阵中。

直接利用存在的除法器和乘法器[5~6],根据前述算法介绍部分的计算原理,进行运算。

先调用除法器作流水线除法,求出逆矩阵对角线上的数据(对原矩阵对角线上的数据求倒数),并找出其中最大值,根据此最大值的符号位数计算归一化的移位个数;然后计算逆矩阵对角线上的数据,利用所求的归一化移位个数进行归一化操作,并将结果存入到输出存储器;计算完对角线上的数据之后,根据算法介绍部分的算法描述调用乘法器将非对角线上的数据算出并归一化存入到输出存储器。

3.2.5 存储器模块(mem)分为输入存储器(inbuf)和输出存储器(outbuf)两个部分。

输入存储器(inbuf)用来接收ZSP传送的数据,存放为原矩阵,只存放矩阵的下三角阵,在运算的过程中,输入存储器根据地址产生模块(addrgen)产生的地址和片选信号将数据依次输出到处理模块(proc);输出存储器(outbuf)用来接收从处理模块(proc)送来的结果数据,存放为逆矩阵,只存放矩阵的下三角阵,在运算的过程中,输出存储器也不断地根据地址产生模块(addrgen)产生的地址和片选信号将数据依次输出到处理模块(proc)进行计算,输出存储器(outbuf)的数据可由ZSP直接读出。

3.3硬件模块实现框图如图3所示图3 硬件模块实现框图3.4 硬件资源及运行时间直接利用已设计的乘法器和除法器,用到的乘法器资源为6个,除法器资源为1个。

该矩阵求逆电路完成一次16×16的矩阵求逆运算所需时钟周期为1000个时钟周期。

4仿真验证电路的仿真采用MENTOR公司的ModelSim5.5d软件,图4为输入一个16×16的原矩阵,图5为该原矩阵下所求得的结果,可以看出,当计算完毕,发出一个中断信号matrix_irq (为高电平),然后zrdata依次读出输出存储器(outbuf)中的数据,经验结果是正确的。

图4 modelsim仿真波形(输入原矩阵)图5 modelsim仿真波形(输出逆矩阵)5 结束语本文提出了一种用于下三角矩阵求逆的并行计算阵列,阵列中各处理模块单元之间的互联规则简单,此设计能够充分发挥硬件的速度,且易于修改矩阵的规模,适用于科学研究和工程应用中矩阵求逆的实时求解。

作者用Verilog语言对本设计进行了描述[7],并用SYNOPSYS公司的DC及modelsim对其进行综合和仿真,最终结果表明此硬件结构能够正确地求解出下三角矩阵的逆。

参考文献[1] K.Hwang, F.A.Briggs. Computer Architecture and Parallel Processing. McGraw-Hill,1994.[2] 陈国良. 并行算法的设计与分析. 高等教育出版社,1994.[3] 黄廷祝,钟守铭,李正良. 矩阵理论[M]. 北京:高等教育出版社,2003.[4] 同济大学数学教研室. 线性代数[M]. 北京:高等教育出版社,1993.[5] Ma G K, Taylor F J. Multiplier Policies for Digital Signal Processing[J]. IEEE A SSPMagazine,1990,7(1):6~20.[6] 傅志晖,程东方,梅其元等. 32位浮点阵列乘法器的设计及算法比较.微电子学,2003,33(3).[7] 夏宇闻. Verilog数字系统设计教程.第2版.北京航空航天大学出版社,2008.作者简介:杨丰瑞(1963-),男,重庆人,教授,主研移动通信,电信新业务等;熊军洲(1985-),男,湖北安陆人,硕士生,主研移动通信。