OCM143中文资料

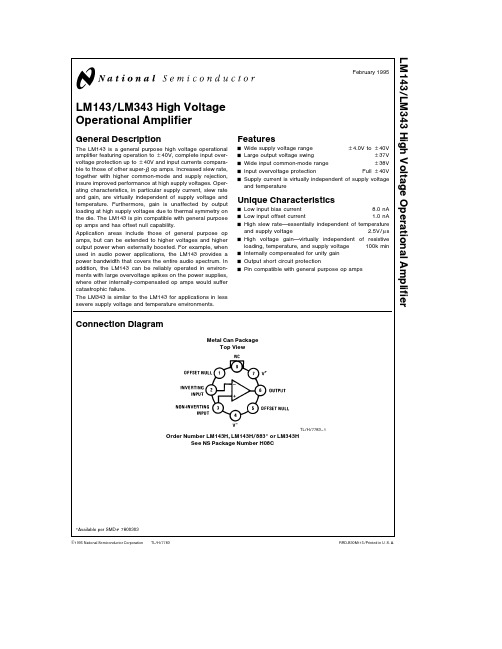

LM143中文资料

Electrical Characteristics (Note 3)

Parameter Input Offset Voltage Input Offset Current Input Bias Current Supply Voltage Rejection Ratio Output Voltage Swing Large Signal Voltage Gain Common-Mode Rejection Ratio Input Voltage Range Supply Current (Note 5) Short Circuit Current Slew Rate Power Bandwidth Unity Gain Frequency Input Offset Voltage Input Offset Current Input Bias Current Large Signal Voltage Gain Output Voltage Swing Conditions Min TA e 25 C TA e 25 C TA e 25 C TA e 25 C TA e 25 C RL t 5 kX TA e 25 C VOUT e g 10V RL t 100 kX TA e 25 C TA e 25 C TA e 25 C TA e 25 C TA e 25 C AV e 1 TA e 25 C VOUT e 40 Vp-p RL e 5 kX THD s 1% TA e 25 C TA e Max TA e Min TA e Max TA e Min TA e Max TA e Min RL t 100 kX TA e Max RL t 100 kX TA e Min RL t 5 0 kX TA e Max RL t 5 0 kX TA e Min 50k 50k 22 22 08 18 50 16 150k 220k 26 25 22 100k 80

NSBC114EDXV6T1G资料

NSBC114EDXV6T1,NSBC114EDXV6T5Preferred DevicesDual Bias Resistor TransistorsNPN Silicon Surface Mount Transistors with Monolithic Bias Resistor NetworkThe BRT (Bias Resistor Transistor) contains a single transistor with a monolithic bias network consisting of two resistors; a series base resistor and a base−emitter resistor. These digital transistors are designed to replace a single device and its external resistor bias network. The BRT eliminates these individual components by integrating them into a single device. In the NSBC114EDXV6T1series, two BRT devices are housed in the SOT−563 package which is ideal for low power surface mount applications where board space is at a premium.Features•Simplifies Circuit Design •Reduces Board Space•Reduces Component Count •Lead−Free Solder Plating •These are Pb−Free DevicesMAXIMUM RATINGS(T A = 25°C unless otherwise noted, common for Q 1 and Q 2)RatingSymbol Value Unit Collector-Base Voltage V CBO 50Vdc Collector-Emitter Voltage V CEO 50Vdc Collector CurrentI C100mAdcTHERMAL CHARACTERISTICSCharacteristic(One Junction Heated)Symbol Max Unit Total Device Dissipation; T A = 25°C Derate above 25°CP D 357 (Note 1)2.9 (Note 1)mW mW/°C Thermal Resistance, Junction-to-AmbientR q JA 350 (Note 1)°C/W Characteristic(Both Junctions Heated)Symbol Max Unit Total Device Dissipation; T A = 25°C Derate above 25°CP D 500 (Note 1)4.0 (Note 1)mW mW/°C Thermal Resistance, Junction-to-AmbientR q JA 250 (Note 1)°C/W Junction and Storage Temperature RangeT J , T stg−55 to +150°C1.FR−4 @ Minimum PadPreferred devices are recommended choices for future use and best overall value.DEVICE MARKING INFORMATIONSee specific marking information in the device marking table on page 2 of this data sheet.Device PackageShipping †ORDERING INFORMATIONNSBC1xxxDXV6T1SOT−563*4000/Tape & ReelNSBC1xxxDXV6T5SOT−563*8000/Tape & ReelNSBC1xxxDXV6T1G SOT−563*4000/Tape & Reel NSBC1xxxDXV6T5G SOT−563*8000/Tape & Reel *This package is inherently Pb−Free.†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.DEVICE MARKING, ORDERING, AND RESISTOR VALUESDevice†Package*Marking R1 (k W)R2 (k W) NSBC114EDXV6T1SOT−5637A1010NSBC124EDXV6T1SOT−5637B2222NSBC144EDXV6T1SOT−5637C4747NSBC114YDXV6T1SOT−5637D1047NSBC114TDXV6T1 (Note 2)SOT−5637E10∞NSBC143TDXV6T1 (Notes 2)SOT−5637F 4.7∞NSBC113EDXV6T1 (Note 2)SOT−5637G 1.0 1.0NSBC123EDXV6T1 (Notes 2)SOT−5637H 2.2 2.2NSBC143EDXV6T1 (Notes 2)SOT−5637J 4.7 4.7NSBC143ZDXV6T1 (Notes 2)SOT−5637K 4.747NSBC124XDXV6T1 (Notes 2)SOT−5637L2247NSBC123JDXV6T1 (Note 2)SOT−5637M 2.247NSBC115EDXV6T1 (Notes 2)SOT−5637N100100 NSBC144WDXV6T1 (Notes 2)SOT−5637P4722†The “G’’ suffix indicates Pb−Free package available.*This package is inherently Pb−Free.2.New resistor combinations. Updated curves to follow in subsequent data sheets.ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, common for Q1 and Q2)Characteristic Symbol Min Typ Max Unit OFF CHARACTERISTICSCollector-Base Cutoff Current (V CB = 50 V, I E = 0)I CBO−−100nAdc Collector-Emitter Cutoff Current (V CE = 50 V, I B = 0)I CEO−−500nAdcEmitter-Base Cutoff Current NSBC114EDXV6T1 (V EB = 6.0 V, I C = 0)NSBC124EDXV6T1NSBC144EDXV6T1NSBC114YDXV6T1NSBC114TDXV6T1NSBC143TDXV6T1NSBC113EDXV6T1NSBC123EDXV6T1NSBC143EDXV6T1NSBC143ZDXV6T1NSBC124XDXV6T1NSBC123JDXV6T1NSBC115EDXV6T1NSBC144WDXV6T1I EBO−−−−−−−−−−−−−−−−−−−−−−−−−−−−0.50.20.10.20.91.94.32.31.50.180.130.20.050.13mAdcCollector-Base Breakdown Voltage (I C = 10 m A, I E = 0)V(BR)CBO50−−Vdc Collector-Emitter Breakdown Voltage (Note 3) (I C = 2.0 mA, I B = 0)V(BR)CEO50−−Vdc 3.Pulse Test: Pulse Width < 300 m s, Duty Cycle < 2.0%ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, common for Q1 and Q2) (Continued)Characteristic Symbol Min Typ Max Unit ON CHARACTERISTICS (Note 4)DC Current Gain NSBC114EDXV6T1 (V CE = 10 V, I C = 5.0 mA)NSBC124EDXV6T1NSBC144EDXV6T1NSBC114YDXV6T1NSBC114TDXV6T1NSBC143TDXV6T1NSBC113EDXV6T1NSBC123EDXV6T1NSBC143EDXV6T1NSBC143ZDXV6T1NSBC124XDXV6T1NSBC123JDXV6T1NSBC115EDXV6T1NSBC144WDXV6T1h FE356080801601603.08.0158080808080601001401403503505.01530200150140150140−−−−−−−−−−−−−−Collector-Emitter Saturation Voltage(I C = 10 mA, I B = 0.3 mA)(I C = 10 mA, I B = 5 mA)NSBC113EDXV6T1/NSBC123EDXV6T1(I C = 10 mA, I B = 1 mA)NSBC114TDXV6T1/NSBC143TDXV6T1NSBC143EDXV6T1/NSBC143ZDXV6T1/NSBC124XDXV6T1V CE(sat)−−0.25VdcOutput Voltage (on)(V CC = 5.0 V, V B = 2.5 V, R L = 1.0 k W)NSBC114EDXV6T1NSBC124EDXV6T1NSBC114YDXV6T1NSBC114TDXV6T1NSBC143TDXV6T1NSBC113EDXV6T1NSBC123EDXV6T1NSBC143EDXV6T1NSBC143ZDXV6T1NSBC124XDXV6T1NSBC123JDXV6T1 (V CC = 5.0 V, V B = 3.5 V, R L = 1.0 k W)NSBC144EDXV6T1 (V CC = 5.0 V, V B = 5.5 V, R L = 1.0 k W)NSBC115EDXV6T1 (V CC = 5.0 V, V B = 4.0 V, R L = 1.0 k W)NSBC144WDXV6T1V OL−−−−−−−−−−−−−−−−−−−−−−−−−−−−0.20.20.20.20.20.20.20.20.20.20.20.20.20.2VdcOutput Voltage (off)(V CC = 5.0 V, V B = 0.5 V, R L = 1.0 k W)(V CC = 5.0 V, V B = 0.050 V, R L = 1.0 k W)NSBC113EDXV6T1(V CC = 5.0 V, V B = 0.25 V, R L = 1.0 k W)NSBC114TDXV6T1NSBC143TDXV6T1NSBC143ZDXV6T1V OH 4.9−−VdcInput Resistor NSBC114EDXV6T1NSBC124EDXV6T1NSBC144EDXV6T1NSBC114YDXV6T1NSBC114TDXV6T1NSBC143TDXV6T1NSBC113EDXV6T1NSBC123EDXV6T1NSBC143EDXV6T1NSBC143ZDXV6T1NSBC124XDXV6T1NSBC123JDXV6T1NSBC115EDXV6T1NSBC144WDXV6T1R17.015.432.97.07.03.30.71.53.33.315.41.547032.910224710104.71.02.24.74.7222.2100471328.661.113136.11.32.96.16.128.62.8613061.1k WResistor Ratio NSBC114EDXV6T1/NSBC124EDXV6T1/NSBC144EDXV6T1/NSBC115EDXV6T1NSBC114YDXV6T1NSBC114TDXV6T1/NSBC143TDXV6T1NSBC113EDXV6T1/NSBC123EDXV6T1/NSBC143EDXV6T1NSBC143ZDXV6T1NSBC124XDXV6T1NSBC123JDXV6T1NSBC144WDXV6T1R1/R20.80.17−0.80.0550.380.0381.71.00.21−1.00.10.470.0472.11.20.25−1.20.1850.560.0562.64.Pulse Test: Pulse Width < 300 m s, Duty Cycle < 2.0%Figure 1. Derating Curve300200150100500T A , AMBIENT TEMPERATURE (°C)250P D , P O W E R D I S S I P A T I O N (m W )V i n , I N P U T V O L T A G E (V O L T S )I C , C O L L E C T O R C U R R E N T (m A )h F E , D C C U R R E N T G A I N (N O R M A L I Z E D )Figure 2. V CE(sat) versus I CI C , COLLECTOR CURRENT (mA)1010.1Figure 3. DC Current GainFigure 4. Output Capacitance 10.10.010.001I C , COLLECTOR CURRENT (mA)V C E (s a t ), M A X I M U M C O L L E C T O R V O L T A G E (V O L T 100010010I C , COLLECTOR CURRENT (mA)Figure 5. Output Current versus Input Voltage1001010.10.010.001V in , INPUT VOLTAGE (VOLTS)Figure 6. Input Voltage versus Output Current4312V R , REVERSE BIAS VOLTAGE (VOLTS)C o b , C A P A C I T A N C E (p F )I C , COLLECTOR CURRENT (mA)Figure 11. Input Voltage versus Output Current0.001V C E (s a t ), M A X I M U M C O L L E C T O R V O L T A G E (V O L T 0.010.1143210C o b , C A P A C I T A N C E (p F )V i n , I N P U T V O L T A G E (V O L T S )V in , INPUT VOLTAGE (VOLTS)Figure 14. Output Capacitance 100I C , COLLECTOR CURRENT (mA)Figure 15. Output Current versus Input Voltage10.80.60.40.20V R , REVERSE BIAS VOLTAGE (VOLTS)C o b , C A P A C I T A N C E (p F )Figure 16. Input Voltage versus Output Current1010.10.01V C E (s a t ), M A X I M U M C O L L E C T O R V O L T A G E (V O L T1010.143.532.521.510.50V R , REVERSE BIAS VOLTAGE (VOLTS)V i n , I N P U T V O L T A G E (V O L T S )V C E (s a t ), M A X I M U M C O L L E C T O R V O L T A G E (V O L T S )Figure 19. Output Capacitance Figure 20. Output Current versus Input VoltageV in , INPUT VOLTAGE (VOLTS)C o b , C A P A C I T A N C E (p F )Figure 21. Input Voltage versus Output CurrentI C , COLLECTOR CURRENT (mA)PACKAGE DIMENSIONSH EDIM MIN NOM MAX MILLIMETERS A 0.500.550.60b 0.170.220.27C D 1.50 1.60 1.70E 1.10 1.20 1.30e 0.5 BSC L 0.100.200.301.50 1.60 1.700.0200.0210.0230.0070.0090.0110.0590.0620.0660.0430.0470.0510.02 BSC0.0040.0080.0120.0590.0620.066MIN NOM MAX INCHESSOT−563, 6 LEAD CASE 463A−01ISSUE FNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETERS3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.ǒmm inchesǓSCALE 20:1*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*0.080.120.180.0030.0050.007ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

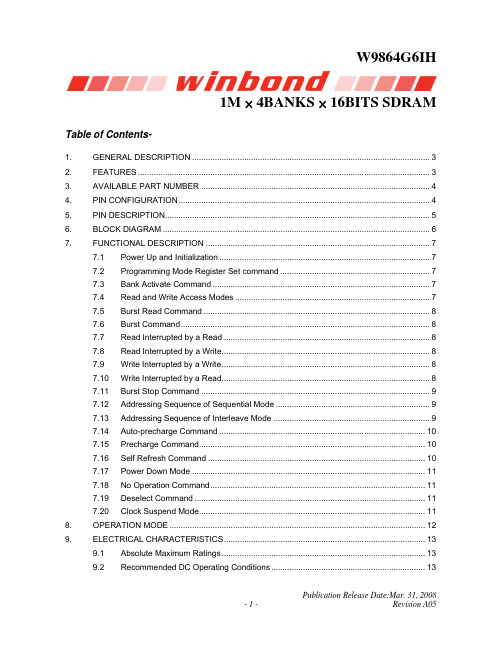

W9864G6IH-6中文资料

1M × 4BANKS × 16BITS SDRAM Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.AVAILABLE PART NUMBER (4)4.PIN CONFIGURATION (4)5.PIN DESCRIPTION (5)6.BLOCK DIAGRAM (6)7.FUNCTIONAL DESCRIPTION (7)7.1Power Up and Initialization (7)7.2Programming Mode Register Set command (7)7.3Bank Activate Command (7)7.4Read and Write Access Modes (7)7.5Burst Read Command (8)7.6Burst Command (8)7.7Read Interrupted by a Read (8)7.8Read Interrupted by a Write (8)7.9Write Interrupted by a Write (8)7.10Write Interrupted by a Read (8)7.11Burst Stop Command (9)7.12Addressing Sequence of Sequential Mode (9)7.13Addressing Sequence of Interleave Mode (9)7.14Auto-precharge Command (10)7.15Precharge Command (10)7.16Self Refresh Command (10)7.17Power Down Mode (11)7.18No Operation Command (11)7.19Deselect Command (11)7.20Clock Suspend Mode (11)8.OPERATION MODE (12)9.ELECTRICAL CHARACTERISTICS (13)9.1Absolute Maximum Ratings (13)9.2Recommended DC Operating Conditions (13)9.3Capacitance (13)9.4DC Characteristics (14)9.5AC Characteristics and Operating Condition (15)10.TIMING WAVEFORMS (18)10.1Command Input Timing (18)10.2Read Timing (19)10.3Control Timing of Input/Output Data (20)10.4Mode Register Set Cycle (21)11.OPERATINOPERATING TIMING EXAMPLE (22)11.1Interleaved Bank Read (Burst Length = 4, CAS Latency = 3) (22)11.2Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge) (23)11.3Interleaved Bank Read (Burst Length = 8, CAS Latency = 3) (24)11.4Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge) (25)11.5Interleaved Bank Write (Burst Length = 8) (26)11.6Interleaved Bank Write (Burst Length = 8, Auto-precharge) (27)11.7Page Mode Read (Burst Length = 4, CAS Latency = 3) (28)11.8Page Mode Read/Write (Burst Length = 8, CAS Latency = 3) (29)11.9Auto-precharge Read (Burst Length = 4, CAS Latency = 3) (30)11.10Auto-precharge Write (Burst Length = 4) (31)11.11Auto Refresh Cycle (32)11.12Self Refresh Cycle (33)11.13Bust Read and Single Write (Burst Length = 4, CAS Latency = 3) (34)11.14Power-down Mode (35)11.15Auto-precharge Timing (Write Cycle) (36)11.16Auto-precharge Timing (Read Cycle) (37)11.17Timing Chart of Read to Write Cycle (38)11.18Timing Chart of Write to Read Cycle (38)11.19Timing Chart of Burst Stop Cycle (Burst Stop Command) (39)11.20Timing Chart of Burst Stop Cycle (Precharge Command) (39)11.21CKE/DQM Input Timing (Write Cycle) (40)11.22CKE/DQM Input Timing (Read Cycle) (41)12.PACKAGE SPECIFICATION (42)12.154L TSOP (II)-400 mil (42)13.REVISION HISTORY (43)1. GENERAL DESCRIPTIONW9864G6IH is a high-speed synchronous dynamic random access memory (SDRAM), organized as 1M words × 4 banks × 16 bits. W9864G6IH delivers a data bandwidth of up to 200M words per second. For different application, W9864G6IH is sorted into the following speed grades: -5, -6, -7/-7S. The -5 parts can run up to 200MHz/CL3. The -6 parts can run up to 166MHz/CL3. The -7/-7S parts can run up to 143MHz/CL3. And the grade of -7S with t RP = 18nS.Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle.The multiple bank nature enables interleaving among internal banks to hide the precharging time.By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9864G6IH is ideal for main memory in high performance applications.2. FEATURES• 3.3V± 0.3V for -5/-6 speed grades power supply• 2. 7V~3.6V for -7/-7S speed grades power supply• 1,048,576 words × 4 banks × 16 bits organization•Self Refresh Current: Standard and Low Power•CAS Latency: 2 & 3•Burst Length: 1, 2, 4, 8 and full page•Sequential and Interleave Burst•Byte data controlled by LDQM, UDQM•Auto-precharge and controlled precharge•Burst read, single write operation•4K refresh cycles/64mS• Interface: LVTTL•Packaged in TSOP II 54-pin, 400 mil using Lead free materials with RoHS compliant3. AVAILABLE PART NUMBERPART NUMBERSPEEDSELF REFRESH CURRENT (MAX.)OPERATING TEMPERATUREW9864G6IH-5 200MHz/CL3 2 mA 0°C ~ 70°C W9864G6IH-6 166MHz/CL3 2 mA 0°C ~ 70°C W9864G6IH-7 143MHz/CL3 2 mA 0°C ~ 70°C W9864G6IH-7S 143MHz/CL32 mA0°C ~ 70°C4. PIN CONFIGURATION5. PIN DESCRIPTION6. BLOCK DIAGRAM7. FUNCTIONAL DESCRIPTION7.1 Power Up and InitializationThe default power up state of the mode register is unspecified. The following power up and initialization sequence need to be followed to guarantee the device being preconditioned to each user specific needs.During power up, all V DD and V DDQ pins must be ramp up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power up voltage must not exceed V DD + 0.3V on any of the input pins or V DD supplies. After power up, an initial pause of 200 µS is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power up, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. An additional eight Auto Refresh cycles (CBR) are also required before or after programming the Mode Register to ensure proper subsequent operation.7.2 Programming Mode Register Set commandAfter initial power up, the Mode Register Set Command must be issued for proper device operation. All banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of RAS, CAS, CS and WE at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued following the mode register set command once a delay equal to t RSC has elapsed. Please refer to the next page for Mode Register Set Cycle and Operation Table.7.3 Bank Activate CommandThe Bank Activate command must be applied before any Read or Write operation can be executed. The operation is similar to RAS activate in EDO DRAM. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must not be less than the RAS to CAS delay time (t RCD). Once a bank has been activated it must be precharged before another Bank Activate command can be issued to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device (t RC). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time (t RRD). The maximum time that each bank can be held active is specified as t RAS(max.).7.4 Read and Write Access ModesAfter a bank has been activated, a read or write cycle can be followed. This is accomplished by setting RAS high and CAS low at the clock rising edge after minimum of t RCD delay. WE pin voltage level defines whether the access cycle is a read operation (WE high), or a write operation (WE low). The address inputs determine the starting column address. Reading or writing to a different row within an activated bank requires the bank be precharged and a new Bank Activate command be issued. When more than one bank is activated, interleaved bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between multiple banks, seamless data access operation among many different pages can be realized. Read or Write Commands can also be issued to the same bank or between active banks on every clock cycle.7.5 Burst Read CommandThe Burst Read command is initiated by applying logic low level to CS and CAS while holding RAS and WE high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The Mode Register sets type of burst (sequential or interleave) and the burst length (1, 2, 4, 8, full page) during the Mode Register Set Up cycle. Table 2 and 3 in the next page explain the address sequence of interleave mode and sequence mode.7.6 Burst CommandThe Burst Write command is initiated by applying logic low level to CS, CAS and WE while holding RAS high at the rising edge of the clock. The address inputs determine the starting column address. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. Data supplied to the DQ pins after burst finishes will be ignored.7.7 Read Interrupted by a ReadA Burst Read may be interrupted by another Read Command. When the previous burst is interrupted, the remaining addresses are overridden by the new read address with the full burst length. The data from the first Read Command continues to appear on the outputs until the CAS Latency from the interrupting Read Command the is satisfied.7.8 Read Interrupted by a WriteTo interrupt a burst read with a Write Command, DQM may be needed to place the DQs (output drivers) in a high impedance state to avoid data contention on the DQ bus. If a Read Command will issue data on the first and second clocks cycles of the write operation, DQM is needed to insure the DQs are tri-stated. After that point the Write Command will have control of the DQ bus and DQM masking is no longer needed.7.9 Write Interrupted by a WriteA burst write may be interrupted before completion of the burst by another Write Command. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.7.10 Write Interrupted by a ReadA Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is activated. The DQs must be in the high impedance state at least one cycle before the new read data appears on the outputs to avoid data contention. When the Read Command is activated, any residual data from the burst write cycle will be ignored.7.11 Burst Stop CommandA Burst Stop Command may be used to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank, if the burst length is full page. Use of the Burst Stop Command during other burst length operations is illegal. The Burst Stop Command is defined by having RAS and CAS high with CS and WE low at the rising edge of the clock. The data DQs go to a high impedance state after a delay, which is equal to the CAS Latency in a burst read cycle, interrupted by Burst Stop.7.12 Addressing Sequence of Sequential ModeA column access is performed by increasing the address from the column address which is input to the device. The disturb address is varied by the Burst Length as shown in Table 2.7.14 Auto-precharge CommandIf A10 is set to high when the Read or Write Command is issued, then the auto-precharge function is entered. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge automatically before all burst read cycles have been completed. Regardless of burst length, it will begin a certain number of clocks prior to the end of the scheduled burst cycle. The number of clocks is determined by CAS Latency.A Read or Write Command with auto-precharge cannot be interrupted before the entire burst operation is completed for the same bank. Therefore, use of a Read, Write, or Precharge Command is prohibited during a read or write cycle with auto-precharge. Once the precharge operation has started, the bank cannot be reactivated until the Precharge time (t RP) has been satisfied. Issue of Auto-Precharge command is illegal if the burst is set to full page length. If A10 is high when a Write Command is issued, the Write with Auto-Precharge function is initiated. The SDRAM automatically enters the precharge operation two clocks delay from the last burst write cycle. This delay is referred to as write t WR. The bank undergoing auto-precharge cannot be reactivated until t WR and t RP are satisfied. This is referred to as t DAL, Data-in to Active delay (t DAL = t WR + t RP). When using the Auto-precharge Command, the interval between the Bank Activate Command and the beginning of the internal precharge operation must satisfy t RAS(min).7.15 Precharge CommandThe Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is entered when CS, RAS and WE are low and CAS is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or all banks simultaneously. Three address bits, A10, BS0, and BS1 are used to define which bank(s) is to be precharged when the command is issued. After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time (t RP).7.16 Self Refresh CommandThe Self Refresh Command is defined by having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. All banks must be idle prior to issuing the Self Refresh Command. Once the command is registered, CKE must be held low to keep the device in Self Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The device will exit Self Refresh operation after CKE is returned high. A minimum delay time is required when the device exits Self Refresh Operation and before the next command can be issued. This delay is equal to the t AC cycle time plus the Self Refresh exit time.If, during normal operation, AUTO REFRESH cycles are issued in bursts (as opposed to being evenly distributed), a burst of 4,096 AUTO REFRESH cycles should be completed just prior to entering and just after exiting the self refresh mode.7.17 Power Down ModeThe Power Down mode is initiated by holding CKE low. All of the receiver circuits except CKE are gated off to reduce the power. The Power Down mode does not perform any refresh operations, therefore the device can not remain in Power Down mode longer than the Refresh period (t REF) of the device.The Power Down mode is exited by bringing CKE high. When CKE goes high, a No Operation Command is required on the next rising clock edge, depending on t CK. The input buffers need to be enabled with CKE held high for a period equal to t CKS(min.) + t CK(min.).7.18 No Operation CommandThe No Operation Command should be used in cases when the SDRAM is in a idle or a wait state to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.7.19 Deselect CommandThe Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when CS is brought high, the RAS, CAS, and WE signals become don't Care.7.20 Clock Suspend ModeDuring normal access mode, CKE must be held high enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends any clocked operation that was currently being executed. There is a one clock delay between the registration of CKE low and the time at which the SDRAM operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.8. OPERATION MODEFully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 1 shows the truth table for the operation commands.Table 1 Truth Table (Note (1), (2))Notes:(1) v = valid, x = Don't care, L = Low Level, H = High Level(2) CKEn signal is input leve l when commands are provided.(3) These are state of bank designated by BS0, BS1 signals.(4) Device state is full page burst operation.(5) Power Down Mode can not be entered in the burst cycle.When this command asserts in the burst cycle, device state is clock suspend mode.9. ELECTRICAL CHARACTERISTICS9.1 Absolute Maximum RatingsNOTESUNIT PARAMETER SYMBOLRATINGInput, Column Output Voltage V IN, V OUT-0.3 ~ V DD+ 0.3V 1Power Supply Voltage V DD, V DDQ -0.3 ~ 4.6 V 1Operating Temperature T OPR 0 ~ 70 °C 1Storage Temperature T STG -55 ~ 150 °C 1Soldering Temperature (10s) T SOLDER 260 °C 11 Power Dissipation P D 1 WShort Circuit Output Current I OUT 50 mA1 Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliabilityof the device.9.2 Recommended DC Operating Conditions(T A = 0 to 70°C for -5/-6/-7/-7S)UNITNOTESMAX.PARAMETER SYM.MIN.TYP.Supply Voltage (Normal operation) V DD 3.0 3.3 3.6 V 2Supply voltage (for –7/-7S) V DD 2.7- 3.6 V 2 Supply Voltage for I/O Buffer V DDQ 3.0 3.3 3.6 V 2Supply Voltage for I/O Buffer (for -7/-7S) V DDQ 2.7- 3.6 V 2Input High Voltage V IH 2.0- V DD + 0.3 V 2Input Low Voltage V IL -0.3- 0.8 V 2Note: V IH(max) = V DD/ V DDQ+1.5V for pulse width < 5 nSV IL(min) = V SS/ V SSQ-1.5V for pulse width < 5 nS9.3 Capacitance(V DD =3V±0.3V for-5/-6, V DD = 2.7V-3.6V for -7/-7S , T A = 25 °C, f = 1 MHz)Note: These parameters are periodically sampled and not 100% tested9.4 DC Characteristics(V DD = 3V±0.3V for-5/-6 ,V DD = 2.7V-3.6V for -7/-7S on T A = 0 to 70°C)NOTESUNITMIN.PARAMETER SYMBOLMAX.Input Leakage CurrentI I(L) -5 5 µA(0V ≤V IN≤ V DD, all other pins not under test = 0V)Output Leakage Currentl O(L) -5 5 µA(Output disable, 0V ≤ V OUT≤ V DDQ)LVTTL Output ″H″ Level VoltageV OH 2.4 - V(I OUT = -2 mA)LVTTL Output“L″ Level VoltageV OL - 0.4 V(I OUT = 2 mA)9.5 AC Characteristics and Operating Condition(V DD =3V±0.3V for-5/-6, V DD = 2.7V-3.6V for -7/-7S on T A = 0 to 70°C) (Notes: 5, 6)-5 -6 -7 -7SPARAMETER SYM. MIN. MAX. MIN.MAX. MIN.MAX.MIN.MAX.UNIT NOTESRef/Active to Ref/ActiveCommand Period t RC 55 60 65 65 Active to precharge Command Period t RAS 40 10000042 10000045 10000045 100000 Active to Read/Write Command Delay Time t RCD 15 18 20 20 nSRead/Write(a) to Read/ Write(b) Command Periodt CCD 1 1 1 1 t CK Precharge to Active(b) Command Period t RP 15 18 20 18Active(a) to Active(b) Command Periodt RRD 10 12 14 14 nSWrite Recovery TimeCL* = 2CL* = 3t WR2 2 2 2 t CKCLK Cycle TimeCL* = 210 1000 7.5 1000 10 100010 1000 CL* = 3t CK 5 1000 6 1000 7 10007 1000CLK High Levelt CH 2 2 2 29 CLK Low Level t CL 2 2 2 29 Access Time from CLKCL* = 2 - 6 6 6CL* = 3 t AC4.5 55.5 5.5 10 Output Data Hold Time t OH 2 2 2 2 10 Output Data HighImpedance Time t HZ 2 5 2 6 2 7 2 7 7 Output Data Low Impedance Time t LZ 0 0 0 0 10 Power Down Mode Entry Timet SB 0 5 0 6 0 7 0 7 Transition Time of CLK (Rise and Fall) t T 1 1 1 1 Data-in-Set-up Time t DS 1.5 1.5 1.5 1.5 9 Data-in Hold Time t DH 1 1 1 1 9 Address Set-up Time t AS 1.5 1.5 1.5 1.5 9 Address Hold Time t AH 1 1 1 1 9 CKE Set-up Time t CKS 1.5 1.5 1.5 1.5 9 CKE Hold Time t CKH 1 1 1 1 9 Command Set-up Time t CMS 1.5 1.5 1.5 1.5 9 Command Hold Timet CMH 1 1 11nS 9AC Characteristics and Operating Condition, continued-5 -6 -7-7SPARAMETER SYM. MIN. MAX. MIN.MAX.MIN.MAX.MIN.MAX.UNIT NOTESRefresh Time t REF 64 64 64 64 mS Mode Register SetCycle Time t RSC 10 14 14 14 nS Exit self refresh to ACTIVE Commandt XSR 70 72 75 75 nSNotes:1.Operation exceeds “Absolute Maximum Ratings” may cause permanent damage to the devices.2. All voltages are referenced to V SS‧2.7V~3.6V power supply for -7/-7S speed grade.3. These parameters depend on the cycle rate and listed values are measured at a cycle rate with the minimum values of t CK and t RC .4. These parameters depend on the output loading conditions. Specified values are obtained with output open.5. Power up sequence please refer to "Functional Description" section described before.6. AC Test Load diagram.7. t HZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output level.8. These parameters account for the number of clock cycles and depend on the operating frequencyof the clock, as follows the number of clock cycles = specified value of timing/ clock period (count fractions as whole number)(1)t CH is the pulse width of CLK measured from the positive edge to the negative edge referenced to V IH (min.).t CL is the pulse width of CLK measured from the negative edge to the positive edge referenced to V IL (max.).(2)A.C Latency Characteristics9. Assumed input rise and fall time (t T ) = 1nS.If tr & tf is longer than 1nS, transient time compensation should be considered,i.e., [(tr + tf)/2-1]nS should be added to the parameter( The t T maximum can’t be more than 10nS for low frequency application. )10. If clock rising time (t T) is longer than 1nS, (t T/2-0.5)nS should be added to the parameter.10. TIMING WAVEFORMS 10.1 Command Input Timing10.2 Read Timing10.3 Control Timing of Input/Output Data10.4 Mode Register Set Cycle11. OPERATINOPERATING TIMING EXAMPLE11.1 Interleaved Bank Read (Burst Length = 4, CAS Latency = 3)11.2 Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge)11.3 Interleaved Bank Read (Burst Length = 8, CAS Latency = 3)11.4 Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge)11.5 Interleaved Bank Write (Burst Length = 8)11.6 Interleaved Bank Write (Burst Length = 8, Auto-precharge)11.7 Page Mode Read (Burst Length = 4, CAS Latency = 3)11.8 Page Mode Read/Write (Burst Length = 8, CAS Latency = 3)11.9 Auto-precharge Read (Burst Length = 4, CAS Latency = 3)11.10 Auto-precharge Write (Burst Length = 4)11.11 Auto Refresh Cycle11.12 Self Refresh Cycle11.13 Bust Read and Single Write (Burst Length = 4, CAS Latency = 3)11.14 Power-down Mode11.15 Auto-precharge Timing (Write Cycle)11.16 Auto-precharge Timing (Read Cycle)11.17 Timing Chart of Read to Write Cycle11.18 Timing Chart of Write to Read Cycle11.19 Timing Chart of Burst Stop Cycle (Burst Stop Command)11.20 Timing Chart of Burst Stop Cycle (Precharge Command)11.21 CKE/DQM Input Timing (Write Cycle)11.22 CKE/DQM Input Timing (Read Cycle)Publication Release Date:Mar. 31, 200812. PACKAGE SPECIFICATION12.1 54L TSOP (II)-400 milPublication Release Date:Mar. 31, 2008Publication Release Date:Mar. 31, 200813. REVISION HISTORYVERSION DATEPAGEDESCRIPTIONP01 Sep. 14, 2007 All Create preliminary data sheet A01 Dec. 12, 2007 AllInitial formal data sheetA02Dec. 24, 20073, 4, 13, 14,15, 16Remove -6I speed grade13Revise overshoot/undershoot pulse widthBefore V IH (max.) = V CC /V CCQ +1.2V for pulse width < 5 nS After V IH (max.) = V CC /V CCQ +1.2V for pulse width < 3 nS Before V IL (min.) = V SS /V SSQ -1.2V for pulse width < 5 nS After V IL (min.) = V SS /V SSQ -1.2V for pulse width < 3 nSA03Jan. 29, 20083, 4, 15Revise -7/-7S parts AC parameter CLK cycle time of CL2 t CK value from 7nS to 7.5nSA04Feb. 26, 200815Revise -6 part AC parameter Access Time from CLK of CL2 t AC value from 5.5nS to 6nS13Revise overshoot/undershoot pulse widthBefore V IH (max.) = V CC /V CCQ +1.2V for pulse width < 3 nS After V IH (max.) = V CC /V CCQ +1.5V for pulse width < 5 nS Before V IL (min.) = V SS /V SSQ -1.2V for pulse width < 3 nS After V IL (min.) = V SS /V SSQ -1.5V for pulse width < 5 nSA05Mar. 31, 200815Revise -7/-7S parts AC parameter CLK cycle time of CL2 t CK value from 7.5nS to 10nSImportant NoticeWinbond products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.。

DTC143ECA中文资料

DTC143ESA

TO-92S

l Any changing of specification will not be informed individua

01-Jun-2002 Rev. A

Page 1 of 2

DTC143EE/DTC143EUA/DTC143EKA DTC143ECA/TC143ESA

Elektronische Bauelemente

NPN Digital Transistors (Built-in Resistors)

Absolute maximum ratings(Ta=25℃)

Parameter Supply voltage Input voltage Output current Power dissipation Junction temperature Storage temperature

Typ Max. 0.5 Unit V V mA µA Conditions VCC=5V ,IO=100µA VO=0.3V ,IO=20 mA IO/II=10mA/0.5mA VI=5V VCC=50V ,VI=0 VO=5V ,IO=10mA 4.7 1 250 6.11 1.2 MHz KΩ

PIN CONNENCTIONS AND MARKING

DTC143EE DTC143EUA

SOT-523

Abbreviated symbol: 23

SOT-323

Abbreviated symbol: 23

DTC143EKA

DTA114ECA DTC143ECA

SOT-23-3L Abbreviated symbol: 23 SOT-23 Abbreviated symbol: 23

ISO 14341 2020 焊接材料—非合金钢和细晶粒钢气体保护焊焊丝和熔敷金属 分类(中文版)

ISO 14341:2020焊接材料—非合金钢和细晶粒钢气体保护焊焊丝和熔敷金属—分类狮子十之八九译目录前言介绍1 范围2 引用标准(略)3 名词和术语4分类5 符号和要求5.1产品/工艺方法的符号标识5.2全焊缝金属强度和延伸率的符号标识5.3全焊缝金属冲击性能的符号标识5.4保护气体的符号标识5.5焊丝化学成分的符号标识6力学试验6.1预热和道间温度6.2焊接条件和焊道顺序6.3焊后热处理(PWHT)条件7化学分析8圆整方法9复验10供货技术条件11名称示例文献(略)ISO(国际标准化组织)是一个世界范围内的国家标准学会(ISO成员组织)的联合体。

制定国际标准的工作经由ISO技术委员会归口负责。

每个成员组织开发一个项目,由此便形成一个技术委员会,此成员组织有权代表该技术委员会。

国际组织、政府与非政府机构协同ISO共同参与工作。

ISO针对于电工标准化所有事宜和国际电工委员会(IEC)紧密合作。

本文件的制订和进一步修订程序在ISO/IEC 指令中第1部分中有描述,须特别注意针对不同类型的ISO文件,有不同的审批标准。

本文件的起草符合ISO/IEC 指令中第2部分的相关规则(见/directives)。

请注意本文件有些部分可能涉及专利权。

ISO不识别这些专利权。

关于制订该文件所涉专利权的细节,见ISO 专利声明清单(见/patent)。

本文档中使用的任何商业名称都是为了方便用户而提供的信息,而不是一种认可。

关于标准的自愿性质、ISO特定术语的含义以及与符合性评估有关的表达的含义,以及关于ISO 在技术性贸易壁垒(TBT)中遵守世界贸易组织(WTO)原则的信息,见/iso/foreword.html。

本标准是由技术委员会ISO/TC44,焊接及相关工艺和SC3委员会,焊接填充材料,与欧洲标准化委员会(CEN)的CEN/TC121技术委员会合作技术委员会制订的,以上合作是基于ISO和CEN之间的技术协议(维也纳协议)。

1439-3;1439-4;中文规格书,Datasheet资料

PLATING Gold/Gold Tin/Tin Tin/Gold

PLATING OPTIONS

CONTACT

BODY SPRING

Gold

Gold

Tin/Lead Tin/Lead

Tin/ Lead

Gold

RoHS Compliant

Non-Compliant

.015 (.38) - .021 (.53) PIN - PRESS FIT

contact maintains retention after multiple insertions • Ideal for mounting transistors, resistors, diodes, IC’s and similar miniature components • Custom micro jacks manufactured to your specifications • Other platings available upon request

1641A 1641B 1641C .122 (3.1)

NON-RoHS

Mtg.

GOLD/GOLD TIN/TIN TIN/GOLD Hole

CAT. NO. CAT. NO. CAT. NO. Dia.

1697 1698 1699 .063 (1.60)

.025 (.64) - .037 (.94) PIN - SOLDER MOUNT

6-FINGER CLOSED ENTRY CONTACT

GOLD/GOLD TIN/TIN TIN/GOLD Hole

CAT. NO. CAT. NO. CAT. NO. Dia.

1603 1606 1607 .052 (1.32)

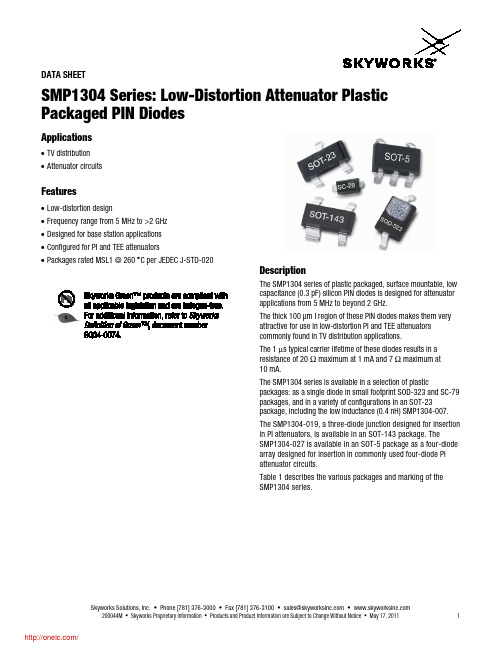

SMP1304-004LF;SMP1304-027LF;中文规格书,Datasheet资料

DATA SHEETSMP1304 Series: Low-Distortion Attenuator Plastic Packaged PIN DiodesApplications•TV distribution•Attenuator circuitsFeatures•Low-distortion design•Frequency range from 5 MHz to >2 GHz•Designed for base station applications•Configured for PI and TEE attenuators•Packages rated MSL1 @ 260°C per JEDEC J-STD-020DescriptionThe SMP1304series of plastic packaged, surface mountable, lowcapacitance (0.3 pF) silicon PIN diodes is designed for attenuatorapplications from 5 MHz to beyond 2 GHz.The thick 100 μm I region of these PIN diodes makes them veryattractive for use in low-distortion PI and TEE attenuatorscommonly found in TV distribution applications.The 1 μs typical carrier lifetime of these diodes results in aresistance of 20 Ωmaximum at 1 mA and 7 Ωmaximum at10 mA.The SMP1304series is available in a selection of plasticpackages: as a single diode in small footprint SOD-323 and SC-79package s, and in a variety of configurations in an SOT-23package, including the low inductance (0.4 nH) SMP1304-007.The SMP1304-019, a three-diode junction designed for insertionin PI attenuators, is available in an SOT-143 package. TheSMP1304-027 is available in an SOT-5 package as a four-diodearray designed for insertion in commonly used four-diode PIattenuator circuits.Table 1 describes the various packages and marking of theSMP1304 series.Skyworks Solutions, Inc. • Phone [781] 376-3000• Fax [781] 376-3100 • sales@ • 200044M• Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • May 17, 20111DATA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 2May 17, 2011 • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • 200044M(Sn/Pb) packaging is not recommended for new designs .Innovation to Go™Select Linear Products (indicated by ♦) now available for purchase online.SMP1304-007The inductance of the SMP1304-007 is effectively reduced to 0.4 nH compared to the 1.5 nH of the standard configuration. The lower inductance is particularly beneficial when the diodes are used as shunt -connected switches at frequencies >500 MHz where inductance is the primary limitation on maximum switch isolation.To achieve the effective 0.4 nH, the SMP1304-007 must be inserted in the microstrip circuit board with a gap in the trace as shown in Figure 1. Because of the polarity of the diode junction, the low inductance can only be achieved with the cathode connected to ground.Figure 1. SOT-23 Package Trace GapFigure 2. SMP1304-019 Package (PI)SMP1304-019 PI Attenuator PIN DiodesThe SMP1304-019 uses three PIN diode junctions in an SOT -143 package (see Figure 2). The junctions are configured for ease ofinsertion in PI attenuator circuits in common use from 10 MHz to >1 GHz. The SMP1304-019 PIN diode junction was designed for low capacitance, a wide resistance dynamic range, and low distortion performance.Electrical and Mechanical SpecificationsThe absolute maximum ratings of the SMP1304 series are provided in Table 2. Electrical specifications are provided in Table 3. Resistance versus temperature measurements are provided in Table 4.Typical performance characteristics of the SMP1304 series are illustrated in Figures 3 to 6. Package dimensions are shown in Figures 7 to 15 (odd numbers), and tape and reel dimensions are provided in Figures 8 to 16 (even numbers).Package and Handling InformationInstructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.The SMP1304 series is rated to Moisture Sensitivity Level 1 (MSL1) at 260 °C. It can be used for lead or lead -free soldering. For additional information, refer to the Skyworks Application Note, Solder Reflow Information , document number 200164 Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.DA TA SHEET • SMP1304 SERIESNote:Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.CAUTION: Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times. TheSMP1304 series PIN diodes are Class 1C ESD devices.Table 3. SMP1304 Series Electrical Specifications (Note 1)Note 1:Performance is guaranteed only under the conditions listed in this Table.Note 2:The SMP1304-019 and SMP1304-027 maximum capacitance is 0.45 pF.Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 200044M• Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • May 17, 20113DATA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 4May 17, 2011 • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • 200044MTypical Performance CharacteristicsFigure 3. Series Resistance vs Current @ 100 MHzFigure 5. Capacitance vs Reverse VoltageFigure 4. DC CharacteristicFigure 6. Conductance vs Frequency and Reverse VoltageDA TA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 200044M • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • May 17, 20115Figure 7. SC-79 Package Dimension DrawingFigure 8. SC-79 Tape and Reel DimensionsDATA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 6May 17, 2011 • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • 200044MFigure 9. SOD-323 Package Dimension DrawingFigure 10. SOD-323 Tape and Reel DimensionsDA TA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 200044M • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • May 17, 20117Figure 11. SOT-5 Package Dimension DrawingFigure 12. SOT-5 Tape and Reel DimensionsDATA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 8May 17, 2011 • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • 200044MFigure 13. SOT-23 Package Dimension DrawingFigure 14. SOT-23 Tape and Reel DimensionsDA TA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 200044M • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • May 17, 20119Figure 15. SOT-143 Package Dimension DrawingFigure 16. SOT-143 Tape and Reel DimensionsDATA SHEET • SMP1304 SERIESSkyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@ • 10May 17, 2011 • Skyworks Proprietary I nformation • Products and Product Information are Subject to Change Without Notice • 200044MCopyright © 2002-2007, 2009, 2010, 2011 Skyworks Solutions, Inc. All Rights Reserved.Information in this document is provided in connection with Skyworks Solutions, Inc. (“Skyworks”) products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products orinformation provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON -INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.Skyworks products are not intended for use in medical, lifesaving or life -sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operati on ofproducts outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.Skyworks, the Skyworks symbol, and “Breakthrough Simplicity” are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third -party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at , are incorporated by reference.分销商库存信息:SKYWORKS-SOLUTIONSSMP1304-004LF SMP1304-027LF。

SEN-R-956-003中文资料

TECHNICAL DATA SHEET 4200…SURFACE MOUNT DIE WITH HEAT ABSORBING STANDOFF TERMINAL STRIPS TRANSIENT VOLTAGE SUPPRESSOR 500 WATT SERIES Glass Passivated Die Plus Dual Heat StripsFeatures:• Low Profile• Broad Voltage Range Available - - 6.8 to 200 Volts • Broad Spectrum Transient Suppression• Rapid Response - - 4 nanoseconds typical• Built-in Heat Absorbing Terminations• Electrically Similar to Mil-Prf-19500/516 Applications:• Connector I/O Surge Suppression• Data Line Protection Description: This is a bipolar transient voltage suppressor series extending from 6.8 volts to 200 volts intended for surface mount applications.Each device comes as a “Cell” with its own heat absorbing terminals pre-bonded at high temperature. This permits mounting on printed circuit boards that cannot provide their own heat sinking. Each terminal is silver plated and is solderable permitting solder down attachment with a very small footprint. Each unit is bi-symmetrical so any orientation can be used.ELECTRICAL CHARACTERISTICSPARAMETER SYMBOL Test Conditions Min TYP Max.Units Response Turn-on Time ton 2 5 nsTransient Energy Pulse (Cell) Ep 1 10uS rise, I= 0.5Ip at t=100us (exponentialdecay)1500 WTransient Energy Pulse (Cell) Ep 2 10uS rise, I= 0.5Ip at t=1.0mS (exponentialdecay)500 WTransient Energy Pulse (Cell) Ep 3 10uS rise, I= 0.5Ip at t=10mS (exponentialdecay)150 WTransient Energy Pulse (Cell) Ep 4 10uS rise, I= 0.5Ip at t=50mS (exponentialdecay)70 WTransient Energy Pulse(Cell)Ep 5 10uS rise, I= 0.5Ip at t=50mS (step pulse) 50 W Electrical Parameters See TableMaximum SolderTemperatureTmax 10 second exposure 300 ºC Thermal Resistance (J-C) ΤJC Assume heat sink on terminal strip ends 18 30 ºC/WNote 1: “Die Only” configuration requires user to provide adequate energy absorption. Note 2: Terminal strips are 0.009” to 0.011” thick copper with nickel and silver plate.0.034"0.039"Typ0.052"0.056"0.0115"0.0155"Bipolar Die OnlySEN-R-956-XXX 500Watt TVS SeriesNominal Vz min Vz max TC (nom) Ir max Part Vz Iz @ Iz @ Iz of Vz Vr @ Vr Vcc Ip Number (V) (mA) (V) (V) (%.°C) (V) (uA) (V) (A) SEN-R-956-001 6.8 10 6.40 7.25 0.050 5.0 1600 9.2 54.3 SEN-R-956-002 7.2 10 6.67 7.67 0.060 6.0 1600 10.3 48.5 SEN-R-956-003 7.8 10 7.22 8.30 0.060 6.5 1000 11.2 44.6 SEN-R-956-004 8.4 10 7.78 8.95 0.060 7.0 400 12.0 41.7 SEN-R-956-005 9.0 1 8.33 9.58 0.070 7.5 200 12.9 38.8 SEN-R-956-006 9.6 1 8.89 10.23 0.070 8.0 100 13.6 36.8 SEN-R-956-007 10 1 9.44 10.82 0.070 8.5 20 14.4 34.7 SEN-R-956-008 11 1 10.00 11.50 0.080 9.0 10 15.4 32.5 SEN-R-956-009 12 1 11.10 12.80 0.080 10.0 5 17.0 29.4 SEN-R-956-010 13 1 12.20 14.00 0.080 11.0 5 18.2 27.5 SEN-R-956-011 14 1 13.30 15.50 0.085 12.0 5 19.9 25.1 SEN-R-956-012 15 1 14.40 16.50 0.085 13.0 5 21.5 23.3 SEN-R-956-013 17 1 15.60 17.90 0.085 14.0 5 23.2 21.6 SEN-R-956-014 18 1 16.70 19.20 0.090 15.0 5 24.4 20.5 SEN-R-956-015 19 1 17.80 20.50 0.090 16.0 5 26.0 19.2 SEN-R-956-016 20 1 18.90 21.70 0.090 17.0 5 27.6 18.1 SEN-R-956-017 22 1 20.00 23.30 0.095 18.0 5 29.2 17.1 SEN-R-956-018 24 1 22.20 25.50 0.095 20.0 5 32.4 15.4 SEN-R-956-019 26 1 24.40 28.00 0.095 22.0 5 35.5 14.1 SEN-R-956-020 29 1 26.70 30.70 0.095 24.0 5 38.9 12.9 SEN-R-956-021 31 1 28.90 33.20 0.095 26.0 5 42.1 11.9 SEN-R-956-022 33 1 31.10 35.80 0.095 28.0 5 45.4 11.0 SEN-R-956-023 36 1 33.30 38.30 0.095 30.0 5 48.4 10.3 SEN-R-956-024 39 1 36.70 42.20 0.100 33.0 5 53.3 9.4 SEN-R-956-025 43 1 40.00 46.00 0.100 36.0 5 58.1 8.6 SEN-R-956-026 48 1 44.40 51.10 0.100 40.0 5 64.5 7.8 SEN-R-956-027 51 1 47.80 54.90 0.100 43.0 5 69.4 7.2 SEN-R-956-028 54 1 50.00 57.50 0.100 45.0 5 72.7 6.9 SEN-R-956-029 57 1 53.30 61.30 0.100 48.0 5 77.4 6.5 SEN-R-956-030 61 1 56.7 65.2 0.100 51.0 5 82.4 6.1 SEN-R-956-031 65 1 60.0 69.0 0.100 54.0 5 87.1 5.7 SEN-R-956-032 69 1 64.4 74.1 0.105 58.0 5 93.6 5.3 SEN-R-956-033 72 1 66.7 76.7 0.105 60.0 5 96.8 5.2 SEN-R-956-034 76 1 71.1 81.8 0.105 64.0 5 103.0 4.9 SEN-R-956-035 84 1 77.8 89.5 0.110 70.0 5 113.0 4.4 SEN-R-956-036 90 1 83.3 95.8 0.110 75.0 5 121.0 4.1 SEN-R-956-037 93 1 86.7 99.7 0.110 78.0 5 126.0 4.0 SEN-R-956-038 101 1 94.4 108.2 0.110 85.0 5 137.0 3.6 SEN-R-956-039 108 1 100.0 115.5 0.110 90.0 5 146.0 3.4 SEN-R-956-040 120 1 111.0 128.0 0.110 100.0 5 162.0 3.1 SEN-R-956-041 131 1 122.0 140.5 0.110 110.0 5 177.0 2.8 SEN-R-956-042 143 1 133.0 153.0 0.110 120.0 5 193.0 2.6 SEN-R-956-043 155 1 144.0 165.5 0.110 130.0 5 209.0 2.4 SEN-R-956-044 180 1 167.0 192.5 0.110 150.0 5 243.0 2.1 SEN-R-956-045 192 1 178.0 205.0 0.110 160.0 5 259.0 1.9 SEN-R-956-046 203 1 189.0 217.5 0.110 170.0 5 275.0 1.81Time (s)Clamp Power vs Time for Sensitron 500W TVS SeriesTime (mS)Exponential Decay Pulse WaveformRated Vz of Device (V)Reverse Junction Capacitance for Sensitron 500W TVSSENSITRONSEMICONDUCTORTECHNICAL DATADISCLAIMER:1- The information given herein, including the specifications and dimensions, is subject to change without prior notice to improve product characteristics. Before ordering, purchasers are advised to contact the Sensitron Semiconductor sales department for the latest version of the datasheet(s).2- In cases where extremely high reliability is required (such as use in nuclear power control, aerospace and aviation, traffic equipment, medical equipment, and safety equipment), safety should be ensured by using semiconductor devices that feature assured safety or by means of users’ fail-safe precautions or other arrangement.3- In no event shall Sensitron Semiconductor be liable for any damages that may result from an accident or any other cause during operation of the user’s units according to the datasheet(s). Sensitron Semiconductor assumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in the datasheets.4- In no event shall Sensitron Semiconductor be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.5- No license is granted by the datasheet(s) under any patents or other rights of any third party or Sensitron Semiconductor.6- The datasheet(s) may not be reproduced or duplicated, in any form, in whole or part, without the expressed written permission of Sensitron Semiconductor.7- The products (technologies) described in the datasheet(s) are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.。

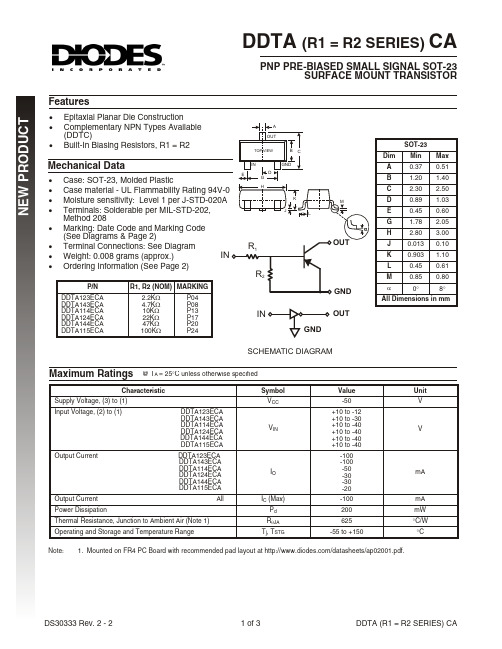

DDTA143ECA中文资料

2005 S

Jan

Feb March Apr

May Jun

1

2

3

4

5

6

2006 T

2007 U

Jul Aug Sep

7

8

9

2008 V

2009 W

Oct

Nov Dec

O

N

D

DS30333 Rev. 2 - 2

2 of 3

DDTA (R1 = R2 SERIES) CA

NEW PRODUCT

Pd, POWER DISSIPATION (MILLIWATTS)

Output Current

All

Power Dissipation

Thermal Resistance, Junction to Ambient Air (Note 1)

Operating and Storage and Temperature Range

Symbol VCC

VIN

IO

IC (Max) Pd RqJA

J 0.013

K 0.903 1.10

L

0.45 0.61

M

0.85 0.80

a

0°

8°

All Dimensions in mm

SCHEMATIC DIAGRAM

Maximum Ratings @ TA = 25°C unless otherwise specified

Characteristic

hFE, DC CURRENT GAIN (NORMALIZED)

TYPICAL CURVES - DDTA143ECA

250

200

150

100

PDTC143ET中文资料

1.2

IE = ie = 0; VCB = 10 V; f = 1 MHz −

−

2.5 pF

1999 Apr 15

3

元器件交易网

Philips Semiconductors

NPN resistor-equipped transistor

Product specification

1999 Apr 15

4

元器件交易网

Philips Semiconductors

NPN resistor-equipped transistor

PACKAGE OUTLINE Plastic surface mounted package; 3 leads

Product specification

open emitter open base open collector

Tamb ≤ 25 °C; note 1

Note 1. Transistor mounted on an FR4 printed-circuit board.

MIN.

− − −

MAX. 50 50 10

UNIT V V V

−

30

• Inverter circuit configurations without use of external resistors.

DESCRIPTION

NPN resistor-equipped transistor in a SOT23 plastic package. PNP complement: PDTA143ET.

Fig.3 DC current gain as a function of collector current; typical values.

HGTG18N120BND_NL中文资料

TC = 150oC

IC = 18A, VGE = 15V

TC = 25oC TC = 150oC

IC = 150µA, VCE = VGE

VGE = ±20V

TJ = 150oC, RG = 3Ω, VGE = 15V, L = 200µH, VCE(PK) = 1200V

IC = 18A, VCE = 600V

HGTG18N120BND 1200

54 26 160 ±20 ±30 100A at 1200V 390 3.12 -55 to 150 260 8 15

UNITS V

A A A V V

W W/oC

oC oC µs µs

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

• Low Conduction Loss

Packaging

JEDEC STYLE TO-247

E C G

COLLECTOR (FLANGE)

G

E

FAIRCHILD SEMICONDUCTOR IGBT PRODUCT IS COVERED BY ONE OR MORE OF THE FOLLOWING U.S. PATENTS

GE通用C1433说明书

对于欧洲客户 “CE”标志表明本产品符合欧洲在安全、健 康、环保、以及客户保护方面的要求。带有

“CE”标志的相机专供在欧洲销售。

此符号[划叉的轮式垃圾箱 WEEE Annex IV]标志 表示在欧盟国家单独回收的废旧电气和电子装 置。请勿将本设备作为家庭垃圾丢弃。请使用您 所在国家(地区)的回收系统正确废弃本产品。

色彩效果............................................................................ 23

使用模式............................................................. 24

安全预防措施

相机注意事项:

不要在下列地点存放或使用相机:

• 在雨中,或者在非常潮湿和多灰尘的地方。 • 在相机容易受阳光直接照射的地方,或者温度高的

地方(如夏天密闭的汽车内)。 • 靠近强磁场的地方,如电机、变压器或磁铁等附

近。

不要将相机放在潮湿表面上,也不要放在水滴或沙粒 容易落到相机上的地方,否则可能会导致无法修复的 故障。 若长时间不使用相机,建议取出电池和存储卡且放在 干燥的环境中。 如果将相机从寒冷位置迅速移到温暖位置,相机内部 可能会出现凝结现象。我们建议您在打开相机电源之 前,等待一段时间。 对于录制内容的丢失没有补偿。当由于相机或录制介 质等工作不正常而导致无法播放录制内容时,录制内 容丢失,将无法补偿。

TVR14751中文资料

Lead Wire Style and Coating S Straight Lead; Epoxy Coating I Inner Kink Lead; Epoxy Coating L Straight Lead; Silicone Coating P Inner Kink Lead; Silicone Coating ::

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

1200

600

Rated Power

(W) 0.02 0.02 0.02 0.02 0.02 0.02 0.02 0.02 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25

Ip 10/1000

(A)

(J)

2.5

0.9Байду номын сангаас

2.5

1.1

2.5

1.4

2.5

1.7

2.5

2.1

2.5

2.5

2.5

3.1

2.5

3.6

10

5.5

10

6.5

10

7.8

10

9.7

10 11.7

LEICA CM1850-中文版

3

目录

1.

1.1 1.2 1.3 1.4

重要信息 ...................................................................................................................................................6

Leica Biosystems Nussloch GmbH Heidelbergery 电话:+49 (62 24) 143-0 传真:+49 (62 24) 143-268 网址: Leica C M 1850 – 冷冻切片机

保证特征仅由我们和我们的客户之间达成的 合同条款确定。徕卡公司保留更改技术规格 和制造工艺的权利,恕不另行通知。只有这 样,才有可能不断提高我们的产品采用的技 术和制造技艺。 本文档受著作权法保护。本文档一切版权均 属 Leica Biosystems Nussloch GmbH 所有。 以印刷、影印、缩影、网络摄像或其它方法 – 包括任何电子系统和媒介 – 复制本文档的文本和插图 (或其任何部分) 需 要事先征得 Leica Biosystems Nussloch GmbH 的明确书面许可。 仪器序列号和制造年份请参见仪器背面的 铭牌。 © Leica Biosystems Nussloch GmbH

选址要求 ..................................................................................................................................................... 14 搬运到所需地点 ....................................................................................................................................... 14 标准配置 ..................................................................................................................................................... 15 安装手轮 ..................................................................................................................................................... 16 连接电源 ..................................................................................................................................................... 17 操作前 ......................................................................................................................................................... 17 Leica CM1850 — 概述 .......................................................................................................................... 18 电源开关和自动主电源保险丝 ............................................................................................................ 20 开启仪器 ..................................................................................................................................................... 20 控制面板 1 .................................................................................................................................................. 21 设定目标值 ................................................................................................................................................ 21 设置时间 ..................................................................................................................................................... 21 设置自动除霜时间 (冷冻箱) .................................................................................................................. 22 选择冷冻箱温度 ....................................................................................................................................... 22 启动 Peltier 元件 ....................................................................................................................................... 23 速冻架的手动除霜 ................................................................................................................................... 23 冷冻箱手动除霜 ....................................................................................................................................... 24 显示锁定 ..................................................................................................................................................... 24 控制面板 2 — 电动粗进 ..................................................................................................................... 25

DTC143XCA中文资料

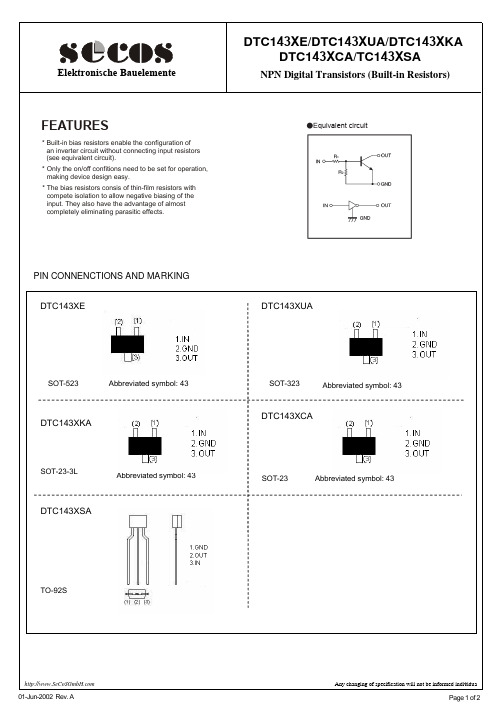

DTC143XE/DTC143XUA/DTC143XKA DTC143XCA/TC143XSA

Elektronische Bauelemente

NPN Digital Transistors (Built-in Resistors)

FEATURES

* Built-in bias resistors enable the configuration of an inverter circuit without connecting input resistors (see equivalent circuit). * Only the on/off confitions need to be set for operation, making device design easy. * The bias resistors consis of thin-film resistors with compete isolation to allow negative biasing of the input. They also have the advantage of almost completely eliminating parasitic effects.

Symbol VCC VIN IO IC(MAX) Pd Tj Tstg

Symbol VI(off) VI(on) VO(on) II IO(off) GI R1 R2/R1 fT 30 3.29 1.7 2.5 Min.

Limits (DTC143X ) E UA CA 50 -7~+20 100 100 150 200 150 -55~150

0.1

0.3 1.8 0.5

Typical Characteristics

ZXM63N03NXTA中文资料

1S E M I C O N D U C T O R SZXMD63N03XISSUE 1 - OCTOBER 2005DUAL 30V N-CHANNEL ENHANCEMENT MODE MOSFETSUMMARYV (BR)DSS =30V; R DS(ON)=0.135; I D =2.3A DESCRIPTIONThis new generation of high density MOSFETs from Zetex utilizes a unique structure that combines the benefits of low on-resistance with fast switching speed.This makes them ideal for high efficiency,low voltage,power management applications.FEATURES•Low on-resistance •Fast switching speed •Low threshold •Low gate drive•Low profile SOIC packageAPPLICATIONS•DC - DC converters•Power management functions •Disconnect switches •Motor controlORDERING INFORMATIONDEVICEREEL SIZE (inches)TAPE WIDTH(mm)QUANTITY PER REEL ZXM63N03NXTA 712embossed 1,000ZXM63N03NXTC1312embossed4,000DEVICE MARKINGZXM63N03MSOP8Pin-outTop viewZXMD63N03XS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20052THERMAL RESISTANCEPARAMETERSYMBOL VALUE UNIT Junction to Ambient (a)(d)R θJA 143°C/W Junction to Ambient (b)(d)R θJA 100°C/W Junction to Ambient (a)(e)R θJA120°C/WNOTES:(a) For a device surface mounted on 25mm x 25mm FR4 PCB with high coverage of single sided 1oz copper, in still air conditions (b) For a device surface mounted on FR4 PCB measured at t р10 secs.(c) Repetitive rating - pulse width limited by maximum junction temperature. Refer to Transient Thermal Impedance graph.(d) For device with one active die.(e) For device with two active die running at equal power.ABSOLUTE MAXIMUM RATINGSPARAMETERSYMBOL LIMIT UNIT Drain-Source Voltage V DSS 30V Gate-Source Voltage V GS±20VContinuous Drain Current(V GS =4.5V;T A =25°C)(b)(d)(V GS =4.5V;T A =70°C)(b)(d)I D 2.31.8A Pulsed Drain Current (c)(d)I DM 14A Continuous Source Current (Body Diode)(b)(d)I S 1.5A Pulsed Source Current (Body Diode)(c)(d)I SM 14A Power Dissipation at T A =25°C (a)(d)Linear Derating FactorP D 0.876.9W mW/°C Power Dissipation at T A =25°C (a)(e)Linear Derating FactorP D 1.048.3W mW/°C Power Dissipation at T A =25°C (b)(d)Linear Derating FactorP D 1.2510W mW/°C Operating and Storage Temperature RangeT j :T stg-55 to +150°CZXMD63N03XS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20053CHARACTERISTICSZXMD63N03XS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20054ELECTRICAL CHARACTERISTICS (at T amb =25°C unless otherwise stated)PARAMETER SYMBOLMIN.TYP.MAX.UNITCONDITIONSSTATICDrain-Source Breakdown Voltage V (BR)DSS 30V I D =250µA,V GS =0V Zero Gate Voltage Drain Current I DSS 1µA V DS =30V,V GS =0V Gate-Body LeakageI GSS 100nA V GS =Ϯ20V,V DS =0V Gate-Source Threshold Voltage V GS(th) 1.0V I D=250µA,V DS =V GS Static Drain-Source On-State Resistance (1)R DS(on)0.1350.200ΩΩV GS =10V,I D =1.7A V GS =4.5V,I D =0.85A Forward Transconductance (3)g fs1.9SV DS =10V,I D =0.85ADYNAMIC (3)Input Capacitance C iss 290pF V DS =25V,V GS =0V,f=1MHzOutput CapacitanceC oss 70pF Reverse Transfer Capacitance C rss20pFSWITCHING (2)(3)Turn-On Delay Time t d(on) 2.5ns V DD =15V,I D =1.7A R G =6.1Ω,R D =8.7Ω(Refer to test circuit)Rise Timet r 4.1ns Turn-Off Delay Time t d(off)9.6ns Fall Timet f 4.4ns Total Gate Charge Q g 8nC V DS =24V,V GS =10V,I D =1.7A(Refer to test circuit)Gate-Source Charge Q gs 1.2nC Gate Drain Charge Q gd2nCSOURCE-DRAIN DIODE Diode Forward Voltage (1)V SD 0.95V T j =25°C,I S =1.7A,V GS =0VReverse Recovery Time (3)t rr 16.9ns T j =25°C,I F =1.7A,di/dt=100A/µsReverse Recovery Charge(3)Q rr9.5nCNOTES:(1) Measured under pulsed conditions. Width=300µs. Duty cycle ®2% .(2) Switching characteristics are independent of operating junction temperature.(3) For design aid only, not subject to production testing.ZXMD63N03XS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20055TYPICAL CHARACTERISTICSZXMD63N03XS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20056TYPICAL CHARACTERISTICSZXMD63N03XS E M I C O N D U C T O R SISSUE 1 - OCTOBER 20057EuropeZetex GmbHStreitfeldstraße 19D-81673 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49europe.sales@AmericasZetex Inc700 Veterans Memorial Hwy Hauppauge, NY 11788USATelephone: (1) 631 360 2222Fax: (1) 631 360 8222usa.sales@Asia PacificZetex (Asia) Ltd3701-04Metroplaza Tower 1Hing Fong Road, Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494asia.sales@Corporate Headquarters Zetex Semiconductors plc Zetex Technology ParkChadderton, Oldham, OL9 9LL United KingdomTelephone (44) 161 622 4444Fax: (44) 161 622 4446hq@These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.For the latest product information,log on to ©Zetex Semiconductors plc 20051PACKAGE DETAILSPAD LAYOUT DETAILSDIMMillimeters InchesMINMAX MIN MAX A 0.91 1.110.0360.044A10.100.200.0040.008B 0.250.360.0100.014C 0.130.180.0050.007D 2.953.050.1160.120e 0.65NOM 0.0256e10.33NOM 0.0128E 2.95 3.050.1160.120H 4.78 5.030.1880.198L 0.410.660.0160.026°0°6°0°6°PACKAGE DIMENSIONS。

143是什么意思

143是什么意思143的中文含义是我爱你或者我想你、我喜欢你。

因为英文i love you的英文字母分别是一位数、四位数、三位数。

143什么意思143的中文含义是我爱你或者我想你、我喜欢你。

因为英文i love you的英文字母分别是一位数、四位数、三位数。

我爱你是中国的汉语,一般用于一人向爱慕的另一个人表白,也可以用于亲人间是一个人对另一个人的感情表达!143是“我爱你”的代号,尤其在上世纪90年代的呼机上盛行。

这个代号是基于这个短语中每个单词的字母数量来创造的:I (1), love (4), you(3)。

143代表什么意思1、1代表什么意思必须忠于自己,接受自己想要金钱、情感等等所有层面都最求独立自主的梦想,并且努力让梦想成真。

因为他们唯有达成了目标,才能发挥影响力。

必须走出一条能达到完全独立的路,最好早一点学到自己的人生功课,这样将能在拥有独立的同时也享有快乐。

2、4代表什么意思从精神的角度看人生,了解生命是一个不断变化的过程,接纳生死看淡人生,这样他们能减轻对安全感和风险产生的恐惧。

他们可尝试着改变,视改变为契机,利用天分重建稳定并追求更进一步的成长。

3、3代表什么意思数字3代表的含义即是快速及行动,拥有极强行动力的人,在行动的时候,如果速度快,会让他们显得很急躁,并变得比较情绪化和坏脾气。

应该时常提醒自己不要急躁,要按照步骤一步一步的行动。

数字3是一个属于男性性格的数字,容易冲动,任情且不专情。

有很好的表达能力,但是他们在表达时,却时常不经大脑,因而造成乱说话或说错话。

他们做事和说话都会极度夸张,一点小事情就会很紧张,同时亦喜欢抱怨,怀疑自己,很容易愤怒。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

OCM1M 2, 1M 3 SERIESLow ON-resistance Type Optical MOS Relay For DC Load OnlyGENERAL DESCRIPTIONThe OCM1M 2 and OCM1M 3 Series are optical MOS relays for DC load only. The input portion is an infrared light emitting diode. The output portion uses a combination of VD-MOS (Vertical Diffusion MOS) FETs and photodiode arrays. The device is encased in an extremely small 6-pin plastic DIP or SMD-type (gull-wing) package.The optical MOS relay switch may be used in applications that currently use mechanical relay switches, but offers smaller size, noise-free switching, and electronic circuit compatibility because of its non-mechanical operation. Optical MOS relay switches also dissipate less power than equivalent bipolar devices at lower switching frequencies.FEATURES•Infinitesimally small control voltage•High reliability due to non-contact and optical operation •No chattering or switch bounces •No mechanical switching noises•Small size and easy mounting (6-pin plastic DIP or SMD-type [gull-wing] package)APPLICATIONS•Telecommunications equipment •Measurement equipment •Home electronics•Automatic meter reading equipment•Other applications requiring small size or high performance •Other applications requiring non-contact switchesE2P0045-37-X3This version: Jan. 1998Previous version: May. 1997元器件交易网PIN CONFIGURATION(Unit: mm)• DIP Type• SMD Type (gull-wing)• Pin Connection Diagram1: Anode2: Cathode 3: NC 4: Drain 5: Source 6: Source(LED)(LED)(MOS FET)(MOS FET)(MOS FET)• Through hole (Bottom view)• Mounting pad (Top view)+15-00°+15-00°8.682.54 5.081.26.4± 0.55.68±0.255.93±0.25±0.2±0.10.5±0.2±0.37.62±0.150.25±0.033.65±0.24.75M A X0.8±0.22.8±0.35yrqe5.088.68±0.51.2±0.22.54±0.10.5±0.26.4±0.33.65±0.24.0±0.20.25±0.031.1±0.41.1±0.49.9±0.6yrq eABSOLUTE MAXIMUM RATINGSProduct NameParameterSymbolCondition Unit OCM102OCM103I n p u t C h a r a c t e r i s t i c sDerating Factor of Continuous Forward Current I F Pulse width 100 m s Cycle 10 msPulse width 1 ms 1shot(Ambient temperature Ta=25°C )OCM112OCM113OCM122OCM123OCM142OCM143Continuous Forward Current Peak Forward Current Reverse Voltage Power Dissipation Load Voltage Load Current Derating Factor of Load Current Surge Load Current Power Dissipation Storage TemperatureOperating Temperature Isolation Voltage Total Power DissipationO u t p u t C h a r a c t e r i s t i c sD I F I FM V R P DL V OFF I ON D I ON I SUG P D P totV IO T opr T stgmA mA/°CA V mW V mA mA/°C A mW mWV(rms)°C °C50Refer to [Derating Factor of Continuous Forward Current] of characteristics data0.55200350Refer to [Derating Factor of Load Current] of characteristics data3.53003251500OCM1224000OCM123–40 to +85–40 to +100400200OCM142OCM143100450OCM112OCM11360500OCM102OCM103751.5ELECTRICAL CHARACTERISTICSProduct NameParameterSymbolCondition Unit OCM102OCM103I n p u t C h a r a c t e r i s t i c sReverse CurrentV F V OFF =50 V f=1 MHz (Ambient temperature Ta=25°C )OCM112OCM113OCM122OCM123OCM142OCM143Forward Voltage Recovery Input CurrentOn-resistance Off-state Leakage Current Output Terminal Capacitance O u t p u t C h a r a c t e r i s t i c sI RI FRR ONI OFF C OUT Min.m A mAW mA pF 1.0100.21.01.03.00.30.225Max.I F =10 mA V V R =5 V Max. 1.3Operation Input Current I FA mA 5I ON =100 mA Max.V OFF =Rating I ON =100 m A Min.*1Min. 1.5 4.50.70.5Typ. 2.06.21.00.75Max.I F =10 mA I ON =100 mATime to flow current is within one second*2V OFF =Rating Max.Typ.355070Input-to-output Capacitance C IO pF 1.3f=1 MHz Typ.t ON Turn-on Time Typ.0.3Max.I F =10 mA I ON =100 mAms 1.0t OFFTurn-off TimeTyp.0.2Max.ms1.0C o u p l i n g C h a r a c t e r i s t i c s *3*3*1 : Can correspond to special specification I FA <3.0 mA *2 : Can correspond to special specification I OFF <1.0 nA*3 : Can correspond to special specification t ON / t OFF <0.5 msTYPICAL CHARACTERISTICS•Derating Factor of Continuous Forward Current•Derating Factor of Load Current•Operation Input Current vs.Ambient Temperature•Recovery Input Current vs.Ambient Temperature•On-resistance vs. Ambient Temperature 1•On-resistance vs. Ambient Temperature 20–400501003010204050–0.5 mA/°CTemperature Ta (°C )C o n t i n u o u s F o r w a r d C u r r e n t I F (m A )600–40050100300100200400500Temperature Ta (°C )C o n t i n u o u s L o a d C u r r e n t I O N (m A )600–40050100Temperature Ta (˚C )O p e r a t i o n I n p u t C u r r e n t I F A (m A )–40050100Temperature Ta (°C )R e c o v e r y I n p u t C u r r en t I F R (m A )–40050100Temperature Ta (°C )O n -r e s i s t a n c e R O N (W )0050100102468Temperature Ta (°C)O n -r e s i s t a n c e R O N (W )–40•Turn-on/Turn-off Time vs.Ambient Temperature•Off-state Leakage Current vs.Ambient Temperature•Continuous Forward Current vs.On-resistance 1•Continuous Forward Current vs.Turn-on/Turn-off Time•Output Terminal Capacitance vs.Applied Voltage•Continuous Forward Current vs.On-resistance 2–400501000.010.110.001Temperature Ta (°C )T u r n -o n / T u r n -o f f T i m e (m s )050100Temperature Ta (°C )–4000512341020Input Current I F (mA)O n -r e s i s t a n c e R O N (W )001024681020Input Current I F (mA)O n -r e s i s t a n c e R O N (W )1100.2Input Current I F (mA)T u r n -o n / T u r n -o f f T i m e (m s )10100Applied Voltage (V)1010011O u t p u t T e r m i n a l C a p a c i t a n c e C o u t (p F )1000•Load Current vs. Voltage•Example Circuit for Measuring Turn-on/Turn-off TimeI FV OUTV OUT5000.20.40.60.81.0400300200100Voltage (V )L o a d C u r r e n t I O N (m A )。