KIC9208N中文资料

ks0108中文资料

电子发烧友 电子技术论坛点阵图形液晶显示模块HD61202控制器使用手册目录注意事项----------------------------------------------------------------------------------------------------------------------------2第一章、关于HD61202 及其兼容控制驱动器的一般介绍----------------------------------4一、HD61202 及其兼容控制驱动器的特点-------------------------------------------------------------------------4二、HD61202 及其兼容控制驱动器的引脚功能-------------------------------------------------------------------4三、HD61202 及其兼容控制驱动器的时序-------------------------------------------------------------------------6四、HD61202 及其兼容控制驱动器显示RAM 的地址结构-----------------------------------------------------7五、HD61202 及其兼容控制驱动器的指令系统-------------------------------------------------------------------7第二章:内藏HD61202 及其兼容控制驱动器图形液晶显示模块的电路结构特点-------------------------------------------------------------------------------------9第三章:内藏HD61202 及其兼容控制驱动器图形液晶显示模块的应用用----------------------------------------------------------------11注意事项十分感谢您购买我公司的产品。

Microchip PD69200、PD69210和PD69220 PoE 控制器的LED流接口简介

AN3528BT PoE LED Stream InterfaceIntroductionThe LED stream feature supports IEEE 802.3bt PoE port status LEDs for products based on the Microchip PD69200, PD69210 or PD69220 PoE controllers. The LED stream is a serial bit stream between the PoE Controller, dedicated circuit, and the LED, as shown in the following figure.The shift registers in the dedicated circuit extract the ports LEDs status out of the stream. Up to 48 logical ports are supported.Figure 1. LED Interface ApplicationAN3528 Table of ContentsIntroduction (1)1.Description (3)2.LED Stream Operational Modes (4)2.1.Unicolor Indication Mode (4)2.2.Bicolor Indication Mode (4)3.Detailed Schematics (5)4.Revision History (11)The Microchip Website (12)Product Change Notification Service (12)Customer Support (12)Microchip Devices Code Protection Feature (12)Legal Notice (12)Trademarks (13)Quality Management System (13)Worldwide Sales and Service (14)Description 1. DescriptionThe LED Stream feature is software configurable by individual mask 0x20. See the PD692x0 Serial CommunicationProtocol User Guide for more information.Mask 0x20 comprises three LED parameters:•LED Stream Type: select one of the three serial stream types.–0: LED Stream Disabled—Port indication is disabled.–1: Unicolor LED Stream—Single color led indication is transmitted per logical port.–2: Bicolor LED Stream—Dual color indication is transmitted per logical port.The following table lists a set of commands that sets the LED stream types.Table 1-1. Set Individual Mask 0x20Figure 1-1. Set Individual Mask2. LED Stream Operational ModesThe serial bit of the LED Stream has three operation modes configured via the LED Stream type.The two modes are: Unicolor and Bicolor.2.1 Unicolor Indication ModeLogical port status is indicated by a single color per port LED, typically in green.The LED stream communication data structure is as follow:Figure 2-1. Unicolor Indication48 PortsThe stream data contains 48 bits – a single bit per each logical port.Port#47 data is transmitted first and port #0 data is transmitted last.LEDs indication, corresponding to the logical port status, is described in Table 1-1.2.2 Bicolor Indication ModePort status is indicated by bicolored LED per each logical port, typically in green and yellow).The LED stream serial data structure is as follows.Figure 2-2. Bicolor Indication48p ortsThe serial LED stream supports 48 ports. The ports LEDs state is sent sequentially to all ports, two bits per logicalport, giving a total of 96 bits.Port #47 data is transmitted first and port #0 data is transmitted last.LEDs indication, corresponding to the logical port status, is described in Table 1-1.LED Stream Operational Modes3. Detailed SchematicsFigure 2-1 describes the detailed schematics of the LED stream application for unicolored indication with 24 ports and bicolored indication with 12 ports. The schematic is based on the block diagram shown in Figure 1.Figure 3-1. Bicolored LED Stream Interface with PD692x0The following table lists the bill of material for LED Stream Interface, Bicolored. Table 3-1. Bill of Material for LED Stream Interface, BicoloredRevision History 4. Revision HistoryThe revision history describes the changes that were implemented in the document. The changes are listed byrevision, starting with the most current publication.The Microchip WebsiteMicrochip provides online support via our website at /. This website is used to make files and information easily available to customers. Some of the content available includes:•Product Support – Data sheets and errata, application notes and sample programs, design resources, user’s guides and hardware support documents, latest software releases and archived software•General Technical Support – Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing•Business of Microchip – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representativesProduct Change Notification ServiceMicrochip’s product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.To register, go to /pcn and follow the registration instructions.Customer SupportUsers of Microchip products can receive assistance through several channels:•Distributor or Representative•Local Sales Office•Embedded Solutions Engineer (ESE)•Technical SupportCustomers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.Technical support is available through the website at: /supportMicrochip Devices Code Protection FeatureNote the following details of the code protection feature on Microchip devices:•Microchip products meet the specification contained in their particular Microchip Data Sheet.•Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.•There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operatingspecifications contained in Microchip’s Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.•Microchip is willing to work with the customer who is concerned about the integrity of their code.•Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as “unbreakable.”Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.Legal NoticeInformation contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets withyour specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer’s risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.TrademarksThe Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, , Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, , PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial QuadI/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.All other trademarks mentioned herein are property of their respective companies.© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.ISBN: 978-1-5224-6309-2Quality Management SystemFor information regarding Microchip’s Quality Management Systems, please visit /quality.Worldwide Sales and Service。

EV14Y36A评测板用户指南说明书

EV14Y36A EV14Y36A Evaluation Board User Guide IntroductionThe EV14Y36A evaluation board is developed based on Microchip’s PD69210 and PD69208 (PD69208M/PD69208T4/PD69204T4) Power over Ethernet (PoE) chipset for use with Microchip’s VSC56xx Ethernet switch development boards. The board operates on 24 4-pair PoE ports (two pairsets) based on the IEEE® 802.3bt specification.Microchip’s PD69208M/PD69208T4/PD69204T4 PoE manager IC integrates power, analog, and state-of-the-art logic into a single 56-pin, plastic QFN package. The device is used in Ethernet switches and midspans/injectors to allow network devices to share power and data over the same Ethernet cable.The PD69208M/PD69208T4 device is an eight-port, and the PD69204T4 device is a four-port, mixed-signal andhigh‑voltage PoE driver. With the PD69210 external MCU, it performs as a Power Sourcing Equipment (PSE) system. Microchip’s PD69210 PoE controller is a cost-effective and pre-programmed MCU designed to implement the Enhanced Mode PoE system.The PD69208M/PD69208T4/PD69204T4 and PD69210 chipset supports PoE Powered Device (PD) detection, power-up, and protection according to IEEE 802.3af/at/bt standards and a legacy/pre-standard PD detection.It provides real-time PD protection through the following mechanisms: overload, under-load, over-voltage, over-temperature, and short circuit, and enables operation in a Standalone mode. It also executes all real-time functions as specified in IEEE 802.3at and IEEE 802.3bt standards, including PD detection (AF and AT).The PD69208M/PD69208T4/PD69204T4 device supports supply voltages between 32 V and 57 V without additional power sources. A system that powers over four pairs is implemented by combining two ports of PD69208M/T4and PD69204T4, enabling an extra feature for simple and low-cost, high-power PD devices. Ongoing monitoring of system parameters for the host software is available through communication. For higher reliability, internal thermal protection is implemented in the chip. The PD69208M/PD69208T4/PD69204T4 is the most integrated PSE IC including internal MOSFET and sense resistor to achieve a low-power dissipation.The PD69210 features an eSPI bus for each PD69208M/PD69208T4/PD69204T4. It is based on the Microchip D21 family. The PD69210 utilizes an I2C or UART interface to the host CPU. It is designed to support the software thatis field-upgradable through the communication interface. The evaluation system provides designers with the required environment to evaluate the performance.The evaluation system has the following features.•Interface to SparX VSC56xx switch development board•Two connector gangs (each contains 12 4-pair ports)•Switch domain isolated from PoE domain•PoE controller manual Reset and serial communication settings•LED status indication for all ports (LED–stream)•Single power source•0 °C to 40 °C operating temperature•RoHS compliantFigure 1. EV14Y36A Evaluation Board and DimensionsFigure 2. EV14Y36A Evaluation System Block DiagramControl Signals:1-Reset2-Ports disableTable of Contents Introduction (1)1.Overview (4)1.1.Power (4)1.2.Interface and Control (5)1.3.LED Indication (8)2.Installation and Settings (9)2.1.Ports Matrix (9)2.2.Fuses (10)2.3.Connectors J7, J9, and J10 (11)2.4.Schematics (11)3.Revision History (12)The Microchip Website (13)Product Change Notification Service (13)Customer Support (13)Microchip Devices Code Protection Feature (13)Legal Notice (14)Trademarks (14)Quality Management System (15)Worldwide Sales and Service (16)1. OverviewThis section provides the basic overview of the EV14Y36A evaluation board.1.1 PowerThe Evaluation Board (EVB) is powered by a single source via the DC connector J8. The input voltage level can be selected according to the IEEE 802.3 PoE standards.•IEEE 802.3af: 44 V DC to 57 V DC•IEEE 802.3at: 50 V DC to 57 V DC•IEEE 802.3bt: 50 V DC to 57 V DC for type 3 and 52 V DC to 57 V DC for type 4.The recommended voltage level is 55 V DC that covers all PoE standards.The EVB has two power domains:•PoE domain, which is fed directly by the main supply, and it is the power domain provided by the J9 and J10 connectors.•Isolated 3.3 V DC, which feeds PD69210, LED-stream, and serial communication peripherals. The isolated 3.3 V DC is generated by motherboard, provided by the J7 connector (a DC/DC module).Note: The EVB DC is polarity sensitive. The correct polarity is shown in the following figure.Important: The DC connector J8 is limited to current level up to 24 A (4 x 6 A per pin). If higher current is needed, the two via holes next to J8 can be used by soldering a cable to it. The two via holes support up to 40 A to feed the whole EVB.Figure 1-1. Power via Holes1.2 Interface and ControlThis section describes the set-up procedures for serial communication, reset push-button, PoE ports disable, and power good input (PGD0–PGD3).1.2.1 Serial Communication SettingsThe EVB supports serial communication with the PD69210 by UART and I2C, to allow a user-friendly experience using Microchip’s dedicated GUI.Two different I2C address can be set by the host:•When the host sets the address pin to 3.3 V (‘1’), the PD69210 I2C address is set to 0x3C.•When the host sets the address pin to 0 V (‘0’), the PD69210 I2C address is set to 0x1C.To change I2C address, R439 should be installed according to the following table (while R411 is not installed). The EVB is set to I2C address 0x3C (R439=7.5K, R441=20K).When R439 and R441 are not installed, the PD69210 is set to UART.The following figure shows I2C address settings.Figure 1-2. I2C Address Settings DiagramTable 1-1. I2C Address Settings1.2.2 Reset Push–button SettingsThe push–button is connected to the Reset pin of the PD69210 (Pin 26). Pressing on switch SW4 connects the Reset pin to GND. The host can reset the board by setting this pin to ‘0’.The following figure shows switch SW4.Figure 1-3. Reset Control Diagram1.2.3 PoE Ports Disable SettingsThe jumper J12 is connected to the Disable pin of the PD69210 (Pin 4). When the jumper J12 is installed, the Disable pin is connected to GND. The host can disable all port by setting this pin to ‘0’.The following figure shows the J12 jumper settings.Figure 1-4. Ports Disable Control Jumper DiagramFigure 1-5. I2C Bus Test Point and Control Signals1.2.4 Power Good Input (PGD0–PGD3) SettingsThe EVB supports feeding from up to four power supplies, which includes 16 power banks (bank0 to bank15). Each power supply must generate a digital signal (3.3 V DC), which indicates the power supply is active. The generateddigital signal must be connected to one of the PGD pins of PD69208 (pins 41, 46, 47, and 56).On the EVB, four PGD pins are pulled–down with a 10K resistor to DGND, which sets the default power bank to0x00. To set a different bank than 0x00, the user can use the PG0-PG3 tests points, located next to U3.Figure 1-6. PGD0-PGD3 Test Points DiagramFigure 1-7. PGD0-PGD3 Test Points1.3 LED IndicationThe following table lists the evaluation board status indication LEDs.Table 1-2. LED List2. Installation and SettingsThis section describes the installation and operation settings of the EV14Y36A evaluation board.Take the following precautions before starting the installation.•Ensure that the power supply of the board is turned off before plugging in the DC connecter.•Ensure the correct polarity of the power supply cable. The polarity of the power supply cable is as shown in Figure 1-1.•Install the EVB into the motherboard using both ports connectors (J9 and J10) and signal connector (J7).•Turn the main supply ON after the DC connector is plugged in.•After turning on the EVB DC power supply, turn on the motherboard power supply.2.1 Ports MatrixEnsure that the ports matrix is configured according to the following table.Table 2-1. Ports Matrix2.2 FusesOn the main board, there are eight fuses for the PD69208, located on top and bottom side, close to the output portconnectors J9 and J10. The fuse is connected on the Vport_Negpin of each port.IEC62368-1 Ed2 (released in October 2018 and effective December 2020) requires per port fuses for a system power supply greater than 250 W.Figure 2-1. Fuses—Top ViewFigure 2-2. Fuses—Bottom ViewImportant: U1 (PD69208T4 #1) is not populated. Therefore, the EVB supports 8 2-pair ports and 16 4-pair ports. The following figure shows the unconnected pins 1, 7, 9, 15, 17, 23, 25, and 31 in J9.Figure 2-3. Unconnected Pins in J92.3Connectors J7, J9, and J10The EV14Y36A EVB contains three connectors that are connected to the host motherboard.•The J7 carries isolated 3.3 V, control signals, communication signals, and the isolated ESPI signals.Figure 2-4. Connector J7 Pinout Diagram•The J9 and J10 carry the 24 PoE ports that have high PoE current.Signals named VPORT_NEG_OUTn and VPORT_NEG_OUT_Un are connected to the physical ports of PD69208.The current can reach up to 1 A.Figure 2-5. Connector J9 Pinout DiagramFigure 2-6. Connector J10 Pinout Diagram2.4 SchematicsThe full schematics of the EVB are available on the Microchip website .Installation and SettingsRevision History 3. Revision HistoryThe Microchip WebsiteMicrochip provides online support via our website at /. This website is used to make files and information easily available to customers. Some of the content available includes:•Product Support – Data sheets and errata, application notes and sample programs, design resources, user’s guides and hardware support documents, latest software releases and archived software•General Technical Support – Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing•Business of Microchip – Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representativesProduct Change Notification ServiceMicrochip’s product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.To register, go to /pcn and follow the registration instructions.Customer SupportUsers of Microchip products can receive assistance through several channels:•Distributor or Representative•Local Sales Office•Embedded Solutions Engineer (ESE)•Technical SupportCustomers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.Technical support is available through the website at: /supportMicrochip Devices Code Protection FeatureNote the following details of the code protection feature on Microchip devices:•Microchip products meet the specifications contained in their particular Microchip Data Sheet.•Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.•There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data Sheets. Attempts to breach these codeprotection features, most likely, cannot be accomplished without violating Microchip’s intellectual property rights.•Microchip is willing to work with any customer who is concerned about the integrity of its code.•Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is “unbreakable.” Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products.Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act.If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.Legal NoticeInformation contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.THIS INFORMATION IS PROVIDED BY MICROCHIP “AS IS”. MICROCHIP MAKES NO REPRESENTATIONSOR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORYOR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer’s risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.TrademarksThe Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A. Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, , Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge,In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, , PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.All other trademarks mentioned herein are property of their respective companies.© 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.ISBN: 978-1-5224-7942-0Quality Management SystemFor information regarding Microchip’s Quality Management Systems, please visit /quality.Worldwide Sales and Service。

Skyworks Solutions SKY77807 四频带LTE电源放大器模块产品概述说明书

PRODUCT SUMMARYSKY77807 Quad-Band Power Amplifier Module for FDD/TDD LTE (Tx Bands 7, 38, 40, 41)Applications•Multi-band 4G handsets •Long Term Evolution (LTE)-Up to 20 MHz bandwidth/ 100resource blocks Features•Envelope Tracking(ET)FDD band•Average Power Tracking (APT) for TDD/FDD bands•50 ohm input/output impedance with internal DC-blocking •Fully programmable Mobile Industry Processor Interface digital control •Continuous bias control for3G/4G PA High Power Mode via MIPI/RFFE interface•Low Supply voltage•Low voltage support (0.6 V) for APT/SMPS applications •Low Leakage current in power-down mode •Temperature Sensor •Integrated TDD TX-Rx switch for single SAW architecture •Low voltage support forAPT/SMPS applications •Small, low profile package-4.0x 3.0x 1.0 (Max.) mm-24-pad configurationDescriptionThe SKY77807Quad-Band Power Amplifier Module (PAM) is a fully matched, 24-pad surface mount module developed for 4G LTE applications. The PAM consists of PA blocks, input and output matching, and a MIPI standard logic control block for multiple power control levels, output input switch control in a single 4.0mm x 3.0mm x 1.0 (Max.)mm package.The SKY77807uses an enhanced architecture to cover multiple bands and meet the spectral linearity requirements of LTE QPSK and 16QAM modulations with up to 20 MHz bandwidth and up to 100 resource block allocations. Output power is controlled by varying the input power and VCC is adjusted using an ET modulator or DCDC converter to maximize efficiency for each power level. Extremely low leakage current maximizes handset standby time.Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100•*********************•203049C• Skyworks Proprietary Information. • Products and product information are subject to change without notice. • January 13, 20141Ordering InformationProduct Name Order Number Evaluation Board Part NumberSKY77807SKY77807© 2013,Skyworks Solutions, Inc. All Rights Reserved.Information in this document is provided in connection with Skyworks Solutions, Inc. (“Skyworks”) products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects,errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters. Skyworks, the Skyworks symbol, and “Breakthrough Simplicity” are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at , are incorporated by reference.。

模块化仪器的广泛选择

√ 4-10

2

DAQ

3

PXI

4

模块仪器

5

GPIB及 总线扩展

6

PAC

7

运动控制

8

实时 分布式I/O

9

远程I/O

10

串行通信

型号 模拟输出 DAC分辨率 更新率 输出范围 输出阻抗 偏移范围

标准波形

任意波形存储 采样时钟调制

SYNC/Marker 10MHz基准频率输入 正弦输出 页码

PXI-7921 两线多路

切换器 24(两线) 48(单线)

DPDT(2路C类) 2 A@30 VDC

220VDC,125VAC 50VA,60W 2A

10μA@10mVDC 最大100mΩ 1024步 125次/秒 √ √ 4-19

PXI-7931 4组2x4 两线制矩阵模

块 32(两线) DPDT(2路C类) 2A@30 VDC 220VDC,125VAC 50 VA, 60 W

BNC, SMB 512 MB

±5 V, ±1 V 50 Ω, 1.5 MΩ

30 MHz

<-80 dB, DC to 1MHz BNC, SMB

512 MB, 128 MB

-

2通道(PXI-9820)

√

√

√

√

√

√

√

√

√I-9812(A)/PCI-9810 PCI

4通道 20 MS/s

PXI-9816/9826/9846

简介

凌华科技PXI/PCI-9816/9826/9846是4通道16位10MS/s,20MS/s,40MS/s采样数字化仪,专为输入信号频率高 达20MHz的高频和高动态范围的信号而设计。模拟输入范围可以通过编程设置为±1V/±0.2V或±5V/±0.4V。 配备了容量高达512MB的板载内存的PXI/PCI-9816/9826/9846,摆脱了PCI总线的约束,使之能储存更长时间 的波形。

LM9820CCWM资料

Connection Diagrams

VREFVREFMID VREF+ RefBypass OSR OSG OSB AGND VA SampCLK

1 2 3 4 5 6 7 8 9 10

LM9810 & LM9820

20 19 18 17 16 15 14 13 12 11

DGND VD MCLK D5 D4 D3 D2 (SCLK) D1 (Latch) D0 (SDI) NewLine

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) LM9810CCWM LM9810CCWMX LM9820CCWM LM9820CCWMX Package 20 Pin Wide SOIC 20 Pin Wide SOIC, Tape & Reel 20 Pin Wide SOIC 20 Pin Wide SOIC, Tape & Reel

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=+5.0VDC, fMCLK=24MHz, Rs=25Ω. Boldface limits apply for TA=TJ=TMIN to TMAX; all other limits TA=TJ=25°C. (Notes 7, 8, & 12) Symbol Parameter Conditions Typical (Note 9) Limits (Note 10) Units (Limits)

Full Channel Linearity (Note 14) INL DNL Integral Non-Linearity Error (Note 11) Differential Non-Linearity ±0.9 ±0.40 LSB LSB

NI 9208 16通道、±20mA、24位模拟输入模块数据手册说明书

DAT ASHEET NI 920816-Channel, ±20 mA, 24-Bit Analog Input Module•16 channels, current inputs,500 S/s•High-resolution mode with50/60 Hz rejection; Vsuppins for external powerrouting (2 A/30 V max)•±20 mA, 24-bit resolution•250 Vrms, CAT II, channel-to-earth isolation (springterminal); 60 VDC, CAT I,channel-to-earth isolation(DSUB)•DSUB or spring-terminalconnectivity•-40 °C to 70 °C operatingrange, 5 g vibration, 50 gshockThe NI 9208 current input C Series module has 16 channels of ±20 mA input with built-in50/60 Hz rejection for noise rejection.The NI 9208 has a standard 37-pin DSUB connection for use with available cables and connector blocks, or the NI 9937 DSUB connector kit. The NI 9937 contains a DSUB to screw terminal accessory as well as a protective shell. With this kit, you can create a custom cable that plugs directly into the module, eliminating the need for a separate terminal block.Kit ContentsAccessories• NI 9208• NI 9208 Getting Started Guide• NI 9940 Backshell Connector Kit (Spring Terminal)• NI 9923 Screw-Terminal Block (DSUB)NI C Series OverviewNI provides more than 100 C Series modules for measurement, control, and communication applications. C Series modules can connect to any sensor or bus and allow for high-accuracy measurements that meet the demands of advanced data acquisition and control applications.•Measurement-specific signal conditioning that connects to an array of sensors and signals •Isolation options such as bank-to-bank, channel-to-channel, and channel-to-earth ground •-40 °C to 70 °C temperature range to meet a variety of application and environmental needs•Hot-swappableThe majority of C Series modules are supported in both CompactRIO and CompactDAQ platforms and you can move modules from one platform to the other with no modification. CompactRIOCompactRIO combines an open-embedded architecturewith small size, extreme ruggedness, and C Seriesmodules in a platform powered by the NI LabVIEWreconfigurable I/O (RIO) architecture. Each systemcontains an FPGA for custom timing, triggering, andprocessing with a wide array of available modular I/O tomeet any embedded application requirement. CompactDAQCompactDAQ is a portable, rugged data acquisition platformthat integrates connectivity, data acquisition, and signalconditioning into modular I/O for directly interfacing to anysensor or signal. Using CompactDAQ with LabVIEW, youcan easily customize how you acquire, analyze, visualize, andmanage your measurement data.2| | NI 9208 DatasheetSoftwareLabVIEW Professional Development System for Windows•Use advanced software tools for large project development•Generate code automatically using DAQ Assistant and InstrumentI/O Assistant•Use advanced measurement analysis and digital signal processing•Take advantage of open connectivity with DLLs, ActiveX, and .NETobjects•Build DLLs, executables, and MSI installersNI LabVIEW FPGA Module•Design FPGA applications for NI RIO hardware•Program with the same graphical environment used for desktop andreal-time applications•Execute control algorithms with loop rates up to 300 MHz•Implement custom timing and triggering logic, digital protocols, andDSP algorithms•Incorporate existing HDL code and third-party IP including Xilinx IPgenerator functions•Purchase as part of the LabVIEW Embedded Control and MonitoringSuiteNI LabVIEW Real-Time Module•Design deterministic real-time applications with LabVIEWgraphical programming•Download to dedicated NI or third-party hardware for reliableexecution and a wide selection of I/O•Take advantage of built-in PID control, signal processing, andanalysis functions•Automatically take advantage of multicore CPUs or setprocessor affinity manually•Take advantage of real-time OS, development and debuggingsupport, and board support•Purchase individually or as part of a LabVIEW suiteNI 9208 Datasheet| © National Instruments| 3CircuitryV VThe input signals are scanned, amplified, conditioned, and then sampled by a single 24-bit ADC. The module provides overvoltage protection for each channel. Only one channel can be in an overvoltage condition at a time.NI 9208 SpecificationsThe following specifications are typical for the range -40 °C to 70 °C unless otherwise noted.All voltages are relative to COM unless otherwise noted.Caution Do not operate the NI 9208 in a manner not specified in this document.Product misuse can result in a hazard. You can compromise the safety protection built into the product if the product is damaged in any way. If the product is damaged, return it to NI for repair.Input CharacteristicsNumber of channels 16 analog input channels ADC resolution 24 bits Type of ADC Delta-Sigma Sampling mode ScannedInput rangeMinimum ±21.5 mA Typical±22 mA4 | | NI 9208 DatasheetConversion time (per channel)High-resolution mode52 msHigh-speed mode 2 msOvervoltage protection, channel-to-COM±30 V maximum on one channel at a time Vsup pinsCurrent 2 A maximumV oltage30 V maximumInput impedance85 ΩInput noiseHigh-resolution mode50 nArmsHigh-speed mode200 nArmsStabilityGain drift20 ppm/°COffset drift62 nA/°CNMRR (High-resolution mode only)50 Hz66 dB60 Hz68 dBPower RequirementsPower consumption from chassisActive mode282 mW maxSleep mode25 μW maxThermal dissipation (at 70 °C)Active mode 1.29 W maxSleep mode0.72 W max1Range equals 22 mANI 9208 Datasheet| © National Instruments| 5Physical CharacteristicsIf you need to clean the module, wipe it with a dry towel.Tip For two-dimensional drawings and three-dimensional models of the C Seriesmodule and connectors, visit /dimensions and search by module number.Push-in spring-terminal wiringGauge0.14 mm2 to 1.5 mm2 (26 AWG to 16 AWG)copper conductor wireWire strip length10 mm (0.394 in.) of insulation stripped fromthe endTemperature rating90 °C minimumWires per spring terminal One wire per spring terminal; two wires perspring terminal using a 2-wire ferrule Ferrules0.14 mm2 to 1.5 mm2Connector securementSecurement type Screw flanges providedTorque for screw flanges0.2 N · m (1.80 lb · in.)WeightNI 9208 with spring terminal161 g (5.7 oz)NI 9208 with DSUB144 g (5.1 oz)NI 9208 with Spring Terminal Safety VoltagesConnect only voltages that are within the following limits:IsolationChannel-to-channel NoneChannel-to-earth groundContinuous250 Vrms, Measurement Category IIWithstand up to 4,000 m3,000 Vrms, verified by a 5 s dielectricwithstand testMeasurement Category II is for measurements performed on circuits directly connected to the electrical distribution system. This category refers to local-level electrical distribution, such as that provided by a standard wall outlet, for example, 115 V for U.S. or 230 V for Europe.Caution Do not connect the NI 9208 to signals or use for measurements withinMeasurement Categories III or IV.6| | NI 9208 DatasheetNI 9208 with DSUB Safety VoltagesConnect only voltages that are within the following limits:IsolationChannel-to-channel NoneChannel-to-earth groundContinuous60 VDC, Measurement Category IWithstand up to 2,000 m1,000 Vrms, verified by a 5 s dielectricwithstand testMeasurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as MAINS voltage. MAINS is a hazardous live electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulated low-voltage sources, and electronics.Caution Do not connect the NI 9208 with DSUB to signals or use formeasurements within Measurement Categories II, III, or IV.Note Measurement Categories CAT I and CAT O are equivalent. These test andmeasurement circuits are not intended for direct connection to the MAINS buildinginstallations of Measurement Categories CAT II, CAT III, or CAT IV. Hazardous LocationsU.S. (UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, AEx nA IIC T4Canada (C-UL)Class I, Division 2, Groups A, B, C, D, T4;Class I, Zone 2, Ex nA IIC T4Europe (ATEX) and International (IECEx)Ex nA IIC T4 GcSafety and Hazardous Locations StandardsThis product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:•IEC 61010-1, EN 61010-1•UL 61010-1, CSA 61010-1•EN 60079-0:2012, EN 60079-15:2010•IEC 60079-0: Ed 6, IEC 60079-15; Ed 4NI 9208 Datasheet| © National Instruments| 7•UL 60079-0; Ed 6, UL 60079-15; Ed 4•CSA 60079-0:2011, CSA 60079-15:2012Note For UL and other safety certifications, refer to the product label or the OnlineProduct Certification section.Electromagnetic CompatibilityThis product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:•EN 61326-1 (IEC 61326-1): Class A emissions; Industrial immunity•EN 55011 (CISPR 11): Group 1, Class A emissions•EN 55022 (CISPR 22): Class A emissions•EN 55024 (CISPR 24): Immunity•AS/NZS CISPR 11: Group 1, Class A emissions•AS/NZS CISPR 22: Class A emissions•FCC 47 CFR Part 15B: Class A emissions•ICES-001: Class A emissionsNote In the United States (per FCC 47 CFR), Class A equipment is intended foruse in commercial, light-industrial, and heavy-industrial locations. In Europe,Canada, Australia and New Zealand (per CISPR 11) Class A equipment is intendedfor use only in heavy-industrial locations.Note Group 1 equipment (per CISPR 11) is any industrial, scientific, or medicalequipment that does not intentionally generate radio frequency energy for thetreatment of material or inspection/analysis purposes.Note For EMC declarations and certifications, and additional information, refer tothe Online Product Certification section.Caution For EMC compliance, operate the NI 9208 with DSUB with shieldedcables.CE ComplianceThis product meets the essential requirements of applicable European Directives, as follows:•2014/35/EU; Low-V oltage Directive (safety)•2014/30/EU; Electromagnetic Compatibility Directive (EMC)•2014/34/EU; Potentially Explosive Atmospheres (ATEX)Online Product CertificationRefer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit /8| | NI 9208 Datasheetcertification, search by model number or product line, and click the appropriate link in the Certification column.Shock and VibrationTo meet these specifications, you must panel mount the system.Operating vibrationRandom (IEC 60068-2-64) 5 g rms, 10 Hz to 500 HzSinusoidal (IEC 60068-2-6) 5 g, 10 Hz to 500 HzOperating shock (IEC 60068-2-27)30 g, 11 ms half sine; 50 g, 3 ms half sine;18 shocks at 6 orientations EnvironmentalRefer to the manual for the chassis you are using for more information about meeting these specifications.Operating temperature-40 °C to 70 °C(IEC 60068-2-1, IEC 60068-2-2)-40 °C to 85 °CStorage temperature(IEC 60068-2-1, IEC 60068-2-2)Ingress protection IP40Operating humidity (IEC 60068-2-78)10% RH to 90% RH, noncondensing Storage humidity (IEC 60068-2-78)5% RH to 95% RH, noncondensing Pollution Degree2Maximum altitudeFor NI 9208 with spring terminal4,000 mFor NI 9208 with DSUB2,000 mIndoor use only.Environmental ManagementNI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.For additional environmental information, refer to the Minimize Our Environmental Impact web page at /environment. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.NI 9208 Datasheet| © National Instruments| 9Waste Electrical and Electronic Equipment (WEEE) EU Customers At the end of the product life cycle, all NI products must bedisposed of according to local laws and regulations. For more information abouthow to recycle NI products in your region, visit /environment/weee.电子信息产品污染控制管理办法(中国RoHS)中国客户National Instruments符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。

E2SCA18-7.999M中文资料(ECLIPTEK)中文数据手册「EasyDatasheet - 矽搜」

(5 DigitsMaximum + Decimal)

HC-49/UP

规格如有更改,恕不另行通知.

CR44

.

08/08

包装选择

空白=散装,TR =卷带式

频率

负载电容

S =串联谐振 XX = XXpF并联谐振

动作模式 /水晶切割 A =基本/ AT, B =三次泛音/ AT D =基本/ BT

外形尺寸 ALL DIMENSIONS IN MILLIMETERS

建议焊盘布局 ALL DIMENSIONS IN MILLIMETERS

电气特性

频率范围频率ຫໍສະໝຸດ 差 /稳定性在工作温 度范围

工作温度范围

老化( 25°C)

存储温度范围

并联电容

绝缘电阻

驱动电平

负载电容(C

)

3.579545MHz为50.000MHz

为±50ppm /±100ppm(标准),±30ppm/为±50ppm(AT切割只),±15ppm/±30ppm(AT切割只),

环境/机械特性

PARAMETER

ESD敏感性

精细泄漏测试 可燃性 总泄漏测试 机械冲击 耐湿性 湿度敏感度 耐焊接热 抗溶剂 可焊性 温度循环 振荡

SPECIFICATION

MIL-STD-883,方法3015,1级,HBM:1500V MIL-STD-883,方法1014,条件A UL94-V0 MIL-STD-883,方法1014,条件C MIL-STD-202,方法213,条件C MIL-STD-883,法1004 J-STD-020, MSL1 MIL-STD-202,方法210,满足条件K MIL-STD-202,方法215 MIL-STD-883,方法2003 MIL-STD-883,方法1010,条件B MIL-STD-883,方法2007条件A

PD69208_AN_211_v1_0

IntroductionThis application note provides detailed information and circuitry design guidelines for the implementation of a 48-port Power over Ethernet (PoE) system, based on Microsemi’s™ PD69208 8-channel or PD69204 4-channel PoE manager and PD69200 PoE Controller. A layout guideline for PoE system based on PD69208 is also included in this document.This document enables designers to integrate PoE capabilities, as specified in IEEE802.3af, IEEE802.3at and PoH standards, into an Ethernet switch.PD69208/4 PoE manager implements real time functions as specified in the standards, including detection, classification, port-status monitoring, and system level activities such as power management and MIB (Management Information Base) support for system management. The PoE manager is designed to detect and disable disconnected PDs (Powered Devices), using DC disconnection methods, as specified in the standards.The PD69208/4 provides PD real time protection through the following mechanisms: overload, under load, over voltage and short-circuit.PD69208/4 share the same design, package and features. The only different between PD69208 and PD69204 is the number of ports.An evaluation board (P/N PD-IM-7648) can be ordered.Applicable Documents♦IEEE 802.3af-2003 standard, DTE Power via MDI♦IEEE802.3at-2009 standard, DTE Power via MDI♦PD69208 and PD69200 datasheet, catalogue number DS_PD69208♦Serial Communication Protocol user guide catalogue number PD63000_UG Features♦IEEE 802.3af-2003 standard compliant♦IEEE802.3at-2009 standard compliant♦Power over HDBasT standard compliant (60W/95W)♦Configurable AT/AF modes♦Configurable standard/tiny cap detection mode♦Supports pre-standard PD detection♦Supports Cisco devices detection♦Single DC voltage input (44 – 57V DC)♦Two & three event classification♦Voltage monitoring/protection♦Low power dissipation♦Internal sense resistor (0.1Ω)♦Internal MOSFET with Low R DS_ON(~0.24Ω)♦Internal power on reset♦Only one external front end component per port♦Includes Reset input from hosting system♦Four direct address configuration pins♦Continuous port monitoring and system data ♦Configurable load current setting♦On-chip thermal protection♦Built in 3.3V DC and 5V DC regulators♦Emergency power management supporting sixteen configurable power banks♦Can be cascaded to up to 12 PoE devices (48 logical ports in 4pairs configuration).♦Supports 4 pair connection♦Wide temperature range: -40° to +85°C MSL1,RoHS compliantaA♦♦2C ♦Isolation Circuit for ESPI bus.ESPI BusThe Enhanced Serial Peripheral Interface (ESPI) bus, used for internal communication, includes the following lines:♦MOSI (Master Out/Slave In) provides communication from PoE Controller toPD69208♦MISO (Master In/Slave Out) provides communication from PD69208 to PoEController♦SCK is the serial clock generated by the Controller♦CS (Chip Select) is utilized by PoE Controller to transmit data simultaneously to allPD69208 ICs, while only chosen PoE managerresponds backControlRefer to Figure 3.♦An xReset_IN control signal driven by Host CPU is used to reset the PoE system♦An xDisable_ports control signal driven by Host CPU is used to disable all PoE ports atonceIndications♦An xSystem_ok signal is generate by The PoE Controller, indicates that the input mainvoltage is within range this pin is determinedby 15 byte serial communication protocol.♦An xInt_out interrupt signal, utilized to indicate PoE events.♦An I2C_Message_Ready indicates signals message is ready to be read by Host Communication FlowHost CPU issues commands, utilizing a dedicated Serial Communication Protocol to the PoE Controller.PoE Controller converts Serial Communication Protocol to ESPI Communication and sends it via isolation is a basic requirement of IEEE PoE standards.Main SupplyPoE system operates within a range of 44 to 57V DC (802.3at port's range is 50 to 57V DC). To comply with UL SELV regulations, maximum output voltage should not exceed 60V DC.GroundsSeveral grounds are utilized in the system.♦PoE Domain Analog♦PoE Domain Digital♦Chassis♦Host Domain FloatingDigital and analog grounds are electrically same ground, however, to reduce noise coupling, grounds are physically separated and connected only at a single point.Chassis ground is connected to switch’s chassis ground. This ground plane should be 1500V rms isolated from PoE circuitry.PoE controller relates to Host domain floating ground which is isolated from PoE domain grounds. 5V DC and 3.3 V DC RegulatorsEach PD69208 has a 5V DC and a 3.3V DC regulators providing up to 6mA each. These currents are utilized for powering components in the PoE domain; those components must also be isolated from the switch circuitry by 1500V rms.An external boost transistor can be added to the 5V DC regulator’s output (instead of R166) to increase the current (see Error! Reference source not found.). The transistor can provide a total of 30mA to the PoE Controller and to the isolation circuits. This total current is the sum of the 5V and 3.3V currents.Detailed Circuit DescriptionThere are two control lines driven by Host CPU to PoE Controller:PoE Controller Circuitry Refer to Figure 8.LED support for port status indication is accomplished by utilizing the ESPI bus (SCK andBus behavior is 1Mhz synchronous serial communication (clock, data) in one direction (write is not used, the pin must be connected to GND or VDD. Figure 5 illustrates the connections between power supplies’ logic signals and PoE Manager.222120192423MSC PD69208DATE CODEFigure 6: 8-ports Front End componentsshould use a 2C R93.( Figure 8) This resistor sets the analog level into pin #22 (I2C_ADDR_Meas_ADC0), as specified in the following table.configuration process is further explained in the not theCopyright © 2015 MicrosemiPage 11 of 23Rev. 1.0, 05 Jan 2015Analog Mixed Signal GroupOne Enterprise Aliso Viejo, CA 92656 USACONFIDENTIALTable 2: Main Block Components***Fuses per port are not required for use in circuits with total power level of up to 3kW. That's because PD69208 is UL 2367 (category QVRQ2) recognized component and fulfills limited power source (LPS) requirements of latest editions of IEC60950-1 and EN60950-1.Figure 17: Output Ports Design DetailsLayout GuidelinesMicrosemi’s PD69208 PoE Manager is designed to simplify the integration of PoE-circuitry, based on the IEEE PoE standards, into switches. The pin-out arrangement has been configured for optimal PCB routing.Figure 18 describes the various circuits and elements surrounding the PD69208 PoE Manager in the block diagram. This block diagram includes the following peripheral elements, identified by numbers:♦5 V Voltage source (V AUX5) (1)♦ 3.3 V Voltage source (V AUX3P3) (2)♦Power Good Inputs (3)♦Output capacitor used for filtering (4)♦ESPI Bus, ESPI Address Lines (5)Note The V AUX5supply may include an external transistor connected to pin 20, destined to increase current drive for external circuitry. To prevent heat from being transferred to the PD69208, place this transistor away from the PoE Managers. Locating PoE Circuitry in a SwitchTo minimize the length of high current traces, as well as RFI pick-up, place the PoE circuitry as close as possible to the switch’s pulse transformers. The circuit can be fully integrated into the switch’s PCB, or can be easily placed on top of the switch's using daughter board. Typical integration of PoE modules inside a switch is shown in Error! Reference source not found.and Error! Reference source not found.Ground and Power PlanesSince the PoE solution is a mixed-signal (analog and digital) circuitry, special care must be taken when routing the ground and power signals lines. The reference design assumes a four layer board: top, mid1, mid2, bottom. The main planes are Vmain/AGND, DGND.Ground planes are crucial for proper operation and should be designed in accordance with the following guidelines, as illustrated in Error! Reference source not found.:♦Separate analog and digital grounds, with a gap of at least 40 mils♦Analog ground plane (AGND) is utilized to transfer the heat generated by thePD69208 (see Thermal Pad Definition andDesign).♦The AGND should be located on external layer♦Earth ground is used to tie in the metal frame of the RJ-45 connectors. This groundis to be routed separately and connected tothe s witch’s metal chassis/enclosure♦To prevent ground loop currents, use onlya single connection point between thedigital and analog grounds as shown inError! Reference source not found.♦To connect various DGND points and to enable stable impedance to the ESPI bustraces, extend the digital ground (DGND)surface under pins 41 – 56 of the PD69208Managers♦ A focal interconnection point for the digital and analog grounds should be located atabout the middle of the overlappingsection♦Leave spacing for a ceramic 1 nF bypass capacitor + two parallel and inversedSchottky diodes near each PoE Manager(Error!between the analog and digital layers. Thecapacitors form low impedance paths fordigital driving signals♦The power and return (ground) planes for the 48V supply must be designed to carrythe system maximum continuous current,based on the design capacity. Minimize DCpower losses on these planes by using awide copper lands. When implementingthe PoE circuitry on a daughter board, thehigh current does not have to be routedthrough the daughter board but only thereturn path as can be note from Figure 19 Current Flow through the PoE applicationSee Figure 19The port's DC current flows in an application utilizing a PoE daughter board (DB) as follow:1. Coming from the switch's power supply positive to the center taps of the line transformer via a mother board wide trace (not through the DB)2. From the center tap of the line transformer via the switch's RJ45 to the PD side3. The return current from the PD flows via the RJ45 and the line transformer to the DB PoE circuitry.4. From the DB analog ground (AGND) the current flows back to the switch's power supply negative via harnessNote The positive port's heavy current flows directly to the PD side without going through the PoE Managers on the DB.Specific Component PlacementPeripheral ComponentsTo minimize heat transfer among various components a gap between them should be maintained. The following are suggested gaps however any gap can be used as long as the designer monitors the thermal performance during the design and follows the maximum temperatures allowed at the various components. ♦Minimum gap between PD69208 ICs should be 50mm♦Minimum gap between PD69208 to PoE controller should be 30mm♦Minimum gap between PD69208 to NPN transistor regulator (if used) should be50mm.PoE Controller and PeripheralsRefer to the Freescale Semiconductor MKL15Z128VFM4 Data Sheet, for recommendations related to the PoE controller layout guidelines.The following guidelines are destined for the integration of the PoE Controller into a PoE circuit.♦Locate the filtering capacitors for VDD and for VDDA close to power and ground pins.♦Termination resistors for the outgoing ESPI digital lines should be located close to therespective driving pins.PD69208 PoE Manager and Peripherals♦The side of the PoE Manager that includes pins 41 to 56 should face the digital ground(DGND plane.) The pins function ascommunication and control pins for theManager (connect between the PoEManager and the PoE controller viaisolation circuitry)♦Locate theManager supply input close to the relevantpin. In cases where two bypass capacitorsare placed on the same line, locate thelower value capacitor closer to the pin onthe same layer and place the higher valuecapacitor at a more distant location.♦Locate VAUX5 and VAUX3P3 0.1 µF and4.7 µF filtering capacitors as close aspossible to the PoE Manager pins 20 and22 respectively.Vmain CapacitorsIt's a good design to have 3 x 47uF capacitors over Vmain in order to prevent noise and spikes events to penetrant into Vmain rail.(note 4 Figure 7). Conductor RoutingGeneral GuidelinesConductor (or printed lands) routing is to be performed as practiced in general layout guidelines, specifically:♦Conductors that deliver a digital signal are to be routed between the analog and thedigital ground planes.♦Avoid routing analog signals above the digital ground.Specific Requirements for Clock and Sensitive SignalsIssues that require special design considerations: ♦The IREF resistor (connects to pin 24), used for current reference, is directly connectedpath.♦Carefully route the ESPI communication clock (SCK) line coming from the PoEController so that it will not disturb otherlines. Two ground lines (connected toDGND) could be routed alongside the clockline to isolate it from the rest of the lines. Port OutputsFor robust design, the ports output traces are to be 45-mil wide so as to handle maximum current and port power.♦H owever to obtain a 10° C (maximum) copper rise under 0.6A per port, set the minimum width for traces in accordance with the layer location and copper thickness:♦F or two ounce copper, external layer: 15 mils♦F or two ounce copper, internal layer: 20 mils♦F or one ounce copper, external layer: 25 mils♦F or one ounce copper, internal layer: 30 mils♦F or 1/2 ounce copper, external layer: 30 mils♦F or 1/2 ounce copper, internal layer: 55 mils (20° C copper rise)♦T he ports output traces must be short and parallel to each other, to reduce RFI pickup and to keep the series resistance low.♦T he PoE ports outputs must be connected to the switch’s pulse transformers as shown in Figure 17. The common mode choke and ‘Bob-Smith’ termination (resistor-capacitor) to chassis ground are optional and used to reduce RFI noise. The circuit is to be located as close as possible to the pulse transformer.Thermal Pad Definition and DesignThe PD69208 utilizes a thermal dissipation exposed pad in a 56-pin 8 x 8 mm QFN package. The package isFor proper heat dissipation, the following footprint / layout guidelines must be followed:All thermal vias are to be connected to the AGND area under the PD69208♦Via diameterinto the vias from the component side can result in voids during the solder process and this must be avoided.A。

SEMIKRON ESD9L系列电路保护扇形电阻说明书

ESD9L, SESD9L Series Transient Voltage SuppressorsESD Protection Diodes with Ultra−Low CapacitanceThe ESD9L Series is designed to protect voltage sensitive components that require ultra−low capacitance from ESD and transient voltage events. Excellent clamping capability, low capacitance, low leakage, and fast response time, make these parts ideal for ESD protection on designs where board space is at a premium. Because of its low capacitance, it is suited for use in high frequency designs such as USB 2.0 high speed and antenna line applications.Specification Features:•Ultra Low Capacitance 0.5 pF •Low Clamping V oltage•Small Body Outline Dimensions:0.039″ x 0.024″(1.00 mm x 0.60 mm)•Low Body Height: 0.016″ (0.4 mm)•Stand−off V oltage: 3.3 V , 5 V •Low Leakage•Response Time is Typically < 1.0 ns •IEC61000−4−2 Level 4 ESD Protection•S and SZ Prefixes for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q101Qualified and PPAP Capable•These Devices are Pb−Free and are RoHS CompliantMechanical Characteristics:CASE: V oid-free, transfer-molded, thermosetting plasticEpoxy Meets UL 94 V−0LEAD FINISH: 100% Matte Sn (Tin)MOUNTING POSITION: AnyQUALIFIED MAX REFLOW TEMPERATURE: 260°CDevice Meets MSL 1 RequirementsMAXIMUM RATINGSRatingSymbolValue Unit IEC 61000−4−2 (ESD)ContactAir±10±15kVTotal Power Dissipation on FR−5 Board (Note 1) @ T A = 25°C P D 150mW Storage Temperature Range T stg −55 to +150°CJunction Temperature Range T J −55 to +150°C Lead Solder Temperature − Maximum(10 Second Duration)TL 260°CStresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.FR−5 = 1.0 x 0.75 x 0.62 in.See Application Note AND8308/D for further description of survivability specs.Device PackageShipping †ORDERING INFORMATIONSOD−923CASE 514ABESD9LxxxST5G SOD−923(Pb−Free)8000/T ape & Reel MARKING DIAGRAMSee specific marking information in the device marking column of the Electrical Characteristics tables starting on page 2 of this data sheet.DEVICE MARKING INFORMATION†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.X = Specific Device Code M = Date Code*Date Code orientation and/or position may vary depending upon manufacturing location.PIN 1.CATHODE2.ANODE12122SESD9LxxxST5G SOD−923(Pb−Free)8000/T ape & Reel SZESD9LxxxST5GSOD−923(Pb−Free)8000/T ape & ReelELECTRICAL CHARACTERISTICS(T A = 25°C unless otherwise noted)Symbol ParameterI PP Maximum Reverse Peak Pulse Current V C Clamping Voltage @ I PP V RWM Working Peak Reverse VoltageI R Maximum Reverse Leakage Current @ VRWM V BR Breakdown Voltage @ I T I T Test Current I F Forward Current V F Forward Voltage @ I F P pk Peak Power DissipationCMax. Capacitance @ V R = 0 and f = 1.0 MHz*See Application Note AND8308/D for detailed explanations of datasheet parameters.ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 1.0 V Max. @ I F = 10 mA for all types)Device*Device Marking V RWM (V)I R (m A)@ VRWM V BR (V) @ I T (Note 2)I T C (pF)V C (V)@ I PP = 1 AV CMax Max Min mA Typ Max Max Per IEC61000−4−2(Note 4)ESD9L3.3ST5G 6** 3.3 1.0 4.8 1.00.50.99.0Figures 1 and 2See Below ESD9L5.0ST5GD5.01.05.41.00.50.99.8Figures 1 and 2See Below*Includes S and SZ-prefix devices where applicable.**Rotated 180°.2.V BR is measured with a pulse test current I T at an ambient temperature of 25°C.3.Surge current waveform per Figure 5.4.For test procedure see Figures 3 and 4 and Application Note AND8307/D.Figure 1. ESD Clamping Voltage Screenshot Positive 8 kV Contact per IEC61000−4−2Figure 2. ESD Clamping Voltage Screenshot Negative 8 kV Contact per IEC61000−4−2IEC 61000−4−2 Spec.Level Test Volt-age (kV)First Peak Current (A)Current at 30 ns (A)Current at 60 ns (A)127.5422415843622.51264830168IEC61000−4−2 WaveformFigure 3. IEC61000−4−2 SpecOscilloscopeThe following is taken from Application NoteAND8308/D − Interpretation of Datasheet Parameters for ESD Devices.ESD Voltage ClampingFor sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000−4−2 waveform. Since the IEC61000−4−2 was written as a pass/fail spec for largersystems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes. For more information on how ON Semiconductor creates these screenshots and how to interpret them please refer to AND8307/D.Figure 5. 8 X 20 ms Pulse Waveform1009080706050403020100t, TIME (m s)% O F P E A K P U L S E C U R R E N TPACKAGE DIMENSIONSSOD−923CASE 514AB ISSUE CNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.DIM MIN NOM MAX MILLIMETERS A 0.340.370.40b 0.150.200.25c 0.070.120.17D 0.750.800.85E 0.550.600.650.95 1.00 1.05L 0.19 REF H E 0.0130.0150.0160.0060.0080.0100.0030.0050.0070.0300.0310.0330.0220.0240.0260.0370.0390.0410.007 REFMIN NOM MAX INCHEScADIMENSIONS: MILLIMETERS*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*See Application Note AND8455/D for more mounting details 2X0.252XOUTLINE2X0.08X YTOP VIEW2XBOTTOM VIEWL2XL20.050.100.150.0020.0040.006ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent PUBLICATION ORDERING INFORMATION。

Analog Devices ADTL082A ADTL082J ADTL084J 双通道操作电路模

Rev. BInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.引脚配置OUT A1–IN A2+IN A3–V4+V8OUT B7–IN B6+IN B5ADTL082JTOP VIEW(Not to Scale)6275-1OUT A1–IN A2+IN A3–V4+V8OUT B7–IN B6+IN B5ADTL082ATOP VIEW(Not to Scale)6275-2OUT A1–IN A2+IN A3+V4OUT D14–IN D13+IN D12–V11+IN B5+IN C10–IN B6–IN C9OUT B7OUT C8ADTL084JTOP VIEW(Not to Scale)6275-3ADTL084A1234567–IN A+IN A+VOUT B–IN B+IN BOUT A141312111098–IN D+IN D–VOUT C–IN C+IN COUT DTOP VIEW(Not to Scale)6275-4低成本、JFET输入运算放大器ADTL082/ADTL084产品特性TL082/TL084兼容低输入偏置电流:10 pA(最大值)失调电压5.5 mV(最大值,ADTL082A/ADTL084A)9 mV(最大值,ADTL082J/ADTL084J)工作电压:±15 V低噪声:16 nV/√Hz宽带宽:5 MHz压摆率:20 V/μs共模抑制比(CMRR):80 dB(最小值)总谐波失真: 0.001%电源电流:1.2 mA(典型值)单位增益稳定应用通用放大功率控制和监测有源滤波器工业/过程控制数据采集采样保持电路积分器输入缓冲图1. 8引脚SOIC_N(R-8)图2. 8引脚MSOP(RM-8)图3. 14引脚SOIC_N(R-14)图4. 14引脚TSSOP(RU-14)概述ADTL082和ADTL084均为具有业界领先性能的JFET输入放大器,其性能优于TL08x器件。

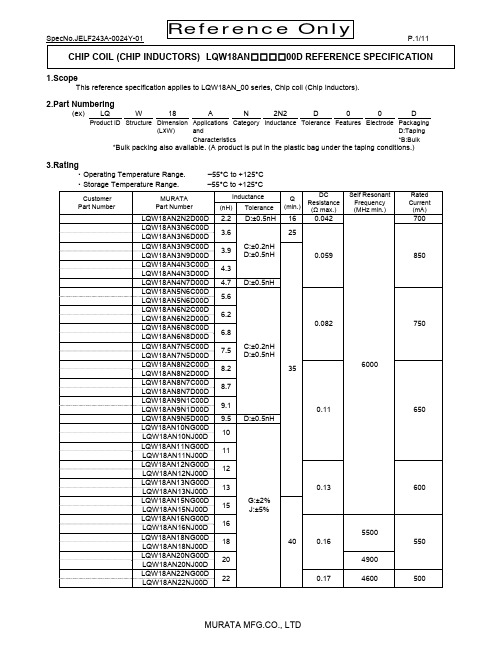

MURATA LQW18AN_00系列芯片电容器(芯片电感)产品说明书