AD815_05中文资料

PC815中文资料

2 3 4 0.9 ± 0.2 1.2 ± 0.3

5

6.5 ± 0.5

1

2 3 4 0.9 ± 0.2 1.2 ± 0.3

5

6

1

2 3 1 3 5 2 4 6 7 9 11 8 10 12

4 5 6 Anode Cathode Emitter Collector

19.82 ± 0.5 2.7 ± 0.5

0.26 ± 0.1 θ θ = 0 to 13 ˚ θ

0.5 ± 0.1

PC835

Anode mark 2.54 ± 0.25

12 11 10

PC845

Internal connection diagram 12 11 10 9 8 7 6.5 ± 0.5 Anode mark

16 15

Internal connection diagram 14 13 12 11 10 9 1 3 5 7 Anode 2 4 6 8 Cathode 9 11 13 15 Emitter 10 12 14 16 Collector

10 000 5 000 Peak forward current I FM ( mA ) 2 000 1 000 500 200 100 50 20 10 5

5

Fig. 4 Forward Current vs. Forward Voltage

500 200 Forward current IF ( mA ) 100 50 20 10 5 2 1 T a = 75˚C 50˚C 25˚C 0˚C - 25˚C

PC815 Serise

PC815 Series

..

s Features

High Sensitivity, High Density Mounting Type Photocoupler

851-IH12-10PZ51中文资料(SOURIAU)中文数据手册「EasyDatasheet - 矽搜」

Z RZ

后壳

支承螺母 直电缆夹

90°电缆夹

直电缆夹无焊盘圈 直壳灌封

90°后壳灌封

直适配器 直壳热缩套管 直可拆卸后盖热缩套管 直可拆卸后盖屏幕终端 和热收缩套管 直可拆卸后盖屏幕终端 和热收缩套管 直后壳与密封函 直后壳与密封压盖和电缆夹 短壳屏幕终端 和热收缩套管 直适配器电动变桨访问

பைடு நூலகம்

弹

焊锡版本

see table

8 - 10 - 12 - 14 - 16 - 18 - 20 - 22 - 24

see table p 18

方向: 强制性后缀:

规格:

P = male - S = female normal (not included in part number) W, X, Y, Z, see table p 19

environmental version : aluminium alloy plating : - olive green cadmium

电

- blackanodised

• Dielectric withstanding voltage :

- white cadmium

• at standard pressure :

- satin finish bright nickel

mated and unmated connectors

- zinc cobalt (olive green)

- 1 500 Vrmsbetween size 20 contacts(service 1)

hermetic version : steel

16 橄榄绿镀镉身体

40 白色镀镉身体

34 非防护税触点,橄榄绿镀镉壳 34A 防护税触点,橄榄绿镀镉壳

AD815AVR中文资料

800

TMIN – TMAX Input Offset Voltage Drift Differential Offset Voltage TMIN – TMAX Differential Offset Voltage Drift –Input Bias Current TMIN – TMAX +Input Bias Current TMIN – TMAX Differential Input Bias Current TMIN – TMAX Open-Loop Transresistance TMIN – TMAX INPUT CHARACTERISTICS Differential Input Resistance Differential Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio Differential Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS Voltage Swing TMIN – TMAX TMIN – TMAX Single Ended, RLOAD = 25 Ω Differential, RLOAD = 50 Ω TMIN – TMAX RLOAD = 5 Ω RLOAD = 10 Ω +Input –Input ± 15 ± 15 ± 15 ±5 ± 5, ± 15 ± 5, ± 15 ± 15 ±5 ± 15 ± 15 ± 15 ±5 ± 15 ± 15 ± 15 ± 15 ±5 ± 15 ±5 ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ±5 ± 15

OCP8151规格书中文版

Package Type Carrier Width(W)

Pitch(P)

Reel Size(D)

SOP-8L

12.0±0.1 mm

4.0±0.1 mm

330±.1 mm

Note: Carrier Tape Dimension, Reel Size and Packing Minimum

Packing Minimum 2500pcs

Page 5 - 10

Rev 1.0 May.23, 2012

OCP8151

高精度原边反馈恒流转换器

应用信息

OCP8151是一款高精度离线式专用LED恒流驱动器,可应用于输出功率7W以内的LED恒流驱动电源。它采用原边 反馈技术,无需TL431、光耦和反馈电路便能实现很好的线电压调整率和负载调整率,极大的节约了系统成本和尺寸空 间。

-

V

2

uA

Page 4 - 10

Rev 1.0 May.23, 2012

典型参数特征

18

17

16

15

14

Vcc_th(V)

13

12

11

10

9

8

-40

-10

20

50

80

Temperature(℃)

芯片启动电压对温度的变化

110

140

2

1.6

1.2

0.8

0.4

ΔIOUT(%)

0

-0.4

-0.8

-1.2

推荐工作范围

符号

参数

范围

单位

VCC

电源电压

8.0~17.5

V

TA

工作环境温度

PMC150, PMS150 datasheet V005_CN

PMC150/PMS150 系列

8 位 IO 类型单片机

重要声明

应广科技保留权利在任何时候变更或终止产品,建议客户在使用或下单前与应广科技或代理商 联系以取得最新、最正确的产品信息。

应广科技不担保本产品适用于保障生命安全或紧急安全的应用,应广科技不为此类应用产品承 担任何责任。关键应用产品包括,但不仅限于,可能涉及的潜在风险的死亡,人身伤害,火灾或严 重财产损失。

2. 系统概述和方框图 ................................................................................................................................. 7 3. 引脚功能说明 ........................................................................................................................................ 8

4. 器件电气特性 ...................................................................................................................................... 10 4.1 直流交流电气特性 ........................................................................................................................ 10 4.2 绝对最大值 ................................................................................................................................... 11 4.3 IHRC 频率与 VDD 关系曲线图 .................................................................................................... 12 4.4 ILRC 频率与 VDD 关系曲线图..................................................................................................... 12 4.5 IHRC 频率与温度关系曲线图 ...................................................................................................... 13 4.6 工作电流与 VDD、系统时钟 CLK=IHRC/n 曲线图 ....................................................................... 13 4.7 工作电流与 VDD、系统时钟 CLK=ILRC/n 曲线图........................................................................ 14 4.8 最低工作电流与 VDD、系统时钟 CLK=ILRC/n 曲线图 ................................................................ 15 4.9 引脚拉高电阻曲线图..................................................................................................................... 15 4.10 引脚输出驱电流(Ioh)与灌电流(Iol) 曲线图 ................................................................................. 16 4.11 引脚输出输入高电压与低电压(VIH / VIL) 曲线图 ......................................................................... 16

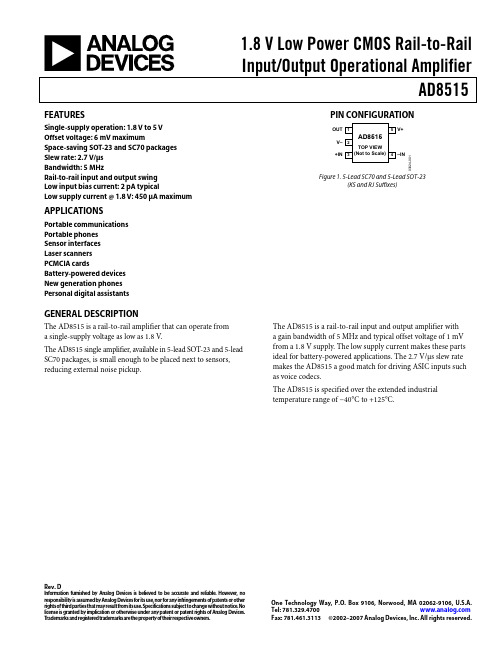

AD8515

REVISION HISTORY

7/07—Rev. C to Rev. D Updated Format..................................................................Universal Updated Package Designator Throughout.................................... 1 Changes to Table 1, Supply Current/Amplifier ............................ 3 Changes to Table 2, Supply Current/Amplifier ............................ 4 Changes to Table 3, Large Signal Voltage Gain, Power Supply Rejection Ratio, and Supply Current/Amplifier........................... 5 Changes to Figure 10........................................................................ 8 Changes to Figure 35...................................................................... 14 Updated Outline Dimensions ....................................................... 16 Changes to Ordering Guide .......................................................... 16 3/05—Rev. B to Rev. C Changes to Specifications ................................................................ 2 Changes to Ordering Guide ............................................................ 5 4/03—Rev. A to Rev. B Change to Figure 5 ......................................................................... 12 2/03—Rev. 0 to Rev. A Added new SC70 Package .................................................Universal Changes to Features ..........................................................................1 Changes to General Description .....................................................1 Changes to Pin Configuration .........................................................1 Changes to Specifications.................................................................2 Changes to Absolute Maximum Ratings........................................5 Changes to Ordering Guide .............................................................5 Changes to TPC 3..............................................................................6 Changes to TPC 10............................................................................7 Changes to TPC 13............................................................................8 Changes to TPC 27......................................................................... 10 Changes to TPC 28......................................................................... 10 Added new TPC 29 ........................................................................ 10 Changes to Functional Description ............................................. 11 Updated to Outline Dimensions .................................................. 14 8/02—Revision. 0: Initial Version

AD8253ARMZ中文资料

Mil

Low

Grade Power

High Speed PGA

AD82201 AD82311 AD620 AD6271 AD8250

AD8221 AD85531 AD621 AD6231 AD8251

AD8222 AD85551 AD524 AD82231 AD8253

AD82241 AD85561 AD526Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113

©2008 Analog Devices, Inc. All rights reserved.

It has a high bandwidth of 10 MHz, low THD of −110 dB, and fast settling time of 780 ns (maximum) to 0.001%. Offset drift and gain drift are guaranteed to 1.2 μV/°C and 10 ppm/°C, respectively, for G = 1000. In addition to its wide input common voltage range, it boasts a high common-mode rejection of 100 dB at G = 1000 from dc to 20 kHz. The combination of precision dc performance coupled with high speed capabilities makes the AD8253 an excellent candidate for data acquisition. Furthermore, this monolithic solution simplifies design and manufacturing and boosts performance of instrumentation by maintaining a tight match of internal resistors and amplifiers.

OCP8153规格书中文版

3. 恒流设置

芯片通过将CS端的电压与内部1V阈值电压进行比较来设定变压器原边峰值电流Ipkp:

I pkp

=

1 RCS

LED输出电流IO根据如下公式计算:

Io

=

1* 6

np ns

* I pkp

其中Ipkp为原边峰值电流,np为变压器原边的匝数,ns为变压器副边的匝数。

(5) (6)

4. 元件参数设置

OCP8153

高精度原边反馈恒流转换器

电气参数(测试条件:如无特殊说明,TA =25℃,VCC=12V)

符号 电源电压

VCC_TH VUVLO VOVP VCC_CLAMP 电流采样 VCS_TH TONMIN 工作电流 IST IOP FB 反馈 TDEMAG_Min

VFB TOFFDLY RLNC 最大占空比 DMAX T FSHORT 过温保护 TSD TSD_HYS 驱动级 RDS(ON) BVDSS IDSS

6. PCB设计

设计PCB时遵循以下几点: (1) VCC的旁路电容要紧靠芯片VCC引脚 (2) 电流采样电阻的功率地线尽可能短,和其它地线分头接到BULK电容的地端。 (3) 尽可能减小大电流环路的面积,以减小EMI辐射。 (4) FB脚的分压电阻要尽可能靠近FB脚。

Page 7 - 9

Ver 1.1 April. 01, 2013

变压器电感量根据系统工作频率、输出电压和输出电流按照以下公式选择:

Ls

=

VO 18 * IO

*F

(7)

其中F为系统工作频率,通常设置范围:20KHz ~ 80KHz之间,中心点设置在40KHz ~ 48KHz之间,以利EMI测试。

根据实际需要选择合适的工作频率,然后按照公式(7)计算副边电感量,最后根据匝比关系计算原边及辅助绕组

KT815A中文资料

DISCRETE SEMICONDUCTOR Transistors70 • Bipolar Transistors (continued)PartPin to PinCompatibilityPolarity РC max, W V CB max, V V CE max,V V EBmax,VI Cmax, m Аh FEV CE sat,VI CBO, μАF T, МHzNf, dB Package (Pads)KT6136A 2N3906 PNP 0.625 40 40 5 200 100…3000.40.05 250 TO-92KT6137A 2N3904 NPN 0.625 60 40 6 200 100…3000.30.05 300 TO-92 BC182BC182ABC182BNPN 0.5 60 50 6 100 120…450120…220200…4500.60.015 150 10 TO-92 BC183BC183ABC183BBC183CNPN 0.5 45 30 6 100 110…800110…220200…450420…8000.60.015 150 10 TO-92 КТ607А-4КТ607Б-42N4073 NPN 1.5 40 30 40 35 30 35 4 150 0.1 1000 700 TO-92 BC639 NPN 0.625 100 80 5 1500 ≥25 0.50.1 100 TO-92 BC640 PNP 0.625 100 80 5 1500 ≥250.50.1 100 TO-92 КТ646А КТ646БКТ646В2SC495 2CS496 NPN 1.0 60 40 40 60 40 40 4 1000 40…200 >150 150…3400.850.250.2510 10 0.05 250 TO-126 KT660A KT660Б BC337 BC338 NPN 0.5 50 30 45 30 5 800 110...220200 (450)0.5 1.0 200 TO-92КТ805АМ КТ805БМ КТ805ВМ КТ805ИМ KSD362 KSD773 NPN 30 300 45 30 5 5000 V KER >15>15>15 >252.53.0 1.0 TO-92 KT814AKT814БKT814BKT814ГBD136 BD138 BD140 PNP 10 40 50 70 100 5 1500 40…27540…27540…27530…2750.650 40 TO-126 KT815AKT815БKT815BKT815ГBD135 BD137 BD139 NPN 10 40 50 70 100 5 1500 40…27540…27540…27530…2750.650 40 TO-126 KT816AKT816БKT816BKT816ГBD234 BD236 BD238 PNP 25 40 45 60 100 5 3000 25…2750.6100 3.0 TO-126 KT817AKT817БKT817BKT817ГBD233 BD235 BD237 NPN 25 40 45 60 100 5 3000 25...2750.6100 3.0 TO-126 КТ8126А1 КТ8126Б1 MJE13007 MJE13006 NPN 80 700 600 400 300 9 8000 8...60 1.01000 4.0 TO-220 КТ8164А КТ8164Б MJE13005 MJE13004 NPN 75 700 600 400 300 9 4000 8...40 1.01000 TO-220 КТ8170А1 КТ8170Б1 MJE13003 MJE13002 NPN 40 700 600 400 300 9 9 1500 8 (40)1.01000 4.0 TO-126 КТ8176АКТ8176БКТ8176ВTIP31A TIP31B TIP31C NPN 40 60 80 100 60 80 100 5 3000 >25 1.2 3.0 TO-220DISCRETE SEMICONDUCTORTransistors71• Bipolar Transistors (continued)Part Pin to PinCompatibility Polarity РC max, W V CB max,V V CE max,V V EB max,V I Cmax,m А h FE V CE sat, VI CBO, μАF T, МHz Nf, dB Package (Pads) КТ8177АКТ8177БКТ8177ВTIP32A TIP32B TIP32C PNP 40 60 80 100 60 80 100 5 3000 >25 1.2 3.0 TO-220 КТ8212А КТ8212БКТ8212ВTIP41С TIP41B TIP41A NPN 65 60 80 100 60 80 100 5 6000 15…75 1.5 I CES =400 3.0 TO-220КТ8213А КТ8213БКТ8213ВTIP42C TIP42B TIP42A PNP 65 60 80 100 60 80 100 5 6000 15…75 1.5 I CES =400 3.0 TO-220MJE2955 PNP 75 70 60 5 1000020…100 1.1 1000 TO-220 MJE3055 NPN 75 70 60 5 1000020…100 1.1 1000 TO-220 КТ738А КТ739А TIP3055 TIP2955 NPN PNP 90 70 60 5 1500020…100 1.1 1000 TO-218 КТ732А КТ733А MJE4343 MJE4353 NPN PNP 125 160 160 7 160008…15 2.0 750 1.0 TO-218 КТ8224А КТ8224Б* BU2508A BU2508DNPN 100 1500700 7.5 8000 4…7 1.0 I ebo=1.0 100..187 TO-218КТ8225ABU941ZP NPN 155 350 5 15000>300 1.8 Veb=5.0V Iebo=20 TO-218 КТ8228А КТ8228Б* BU2525A BU2525DNPN 125 1500800 7.5 12000 5.0…9.5 5.0 I ebo=1.0 80…150 TO-218КТ8229А TIP35F NPN 125 180 180 5 2500015…75 1.8 I ceo = 1.0 3.0 TO-218 КТ8230А TIP36F PNP 125 180 180 5 2500015…75 1.8 1.0 3.0 TO-218 КТ8261А BUD44D2 NPN 25 700 400 9 2000 >10 0.65 0.1 TO-126 BUL44D2 NPN 40 700 400 9 5000 >10 0.65 0.1 TO-220 КТ8247А BUL45D2 NPN 75 700 400 12 5000 >22 0.5 100 TO-220КТ8248А BU2506F NPN 90 Vcek 1500700 7.5 5000 3.8…9.0 3.0 Icek, mA1.0TO-218 KT538A MJE13001 NPN 0.7 600 400 9 0.5 5…90 0.5 1000 4 TO-92 КТ8248А1 BU2506F NPN 90 Ucek 1500 700 7.5 5000 3.8…9.0 3.0 Icek,мА1.0 TO-218KT8290A BUH100 NPN 100 700 400 9 10000 >10 1.0 0.1 ТО-220 КТ8255А BU407 NPN 60 330 160 6 7000 >15 1.0 1.0 ТО-220 KT8270A MJE13001 NPN 0.7 600 400 9 0.5 5…90 0.5 1000 4 TO-126KT8296AKT8296БKT8296ВKT8296ГKSD882R KSD882O KSD882Y KSD882G NPN 10 40 30 5 3000 60…120100…200160…320200…4000.5 100 TO-126 KT8297AKT8297БKT8297ВKT8297ГKSB772R KSB772O KSB772Y KSB772G PNP 10 40 30 5 3000 60…120100…200160…320200…4000.5 100 TO-126KT872A KT872Б KT872B KT872Г* with clampingdiodeBU508А BU508 BU508DNPN1001500150012001500700 700 600 70061000>61.0 5.0 1.0 1.04.0TO-218KT928A 2N2218 NPN 0.5 60 60 5 0.8 20…100 1.0 5.0 250 TO-126KT928Б 2N2219 NPN 0.5 60 60 5 0.8 50…200 1.0 5.0 250 TO-126 KT928B 2N2219ANPN 0.5 75 75 5 0.8 100…300 1.0 1.0 250TO-126 KT940AKT940БKT940BBF459 BF458 NPN 10 300 250 160 3002501605 100 >25 1.0 0.05 TO-126 КТ969А BF469 NPN 6 300 250 5 100 50…250 1.0 0.05 60TO-126DISCRETE SEMICONDUCTOR Transistors72 • Power Bipolar Darlington TransistorsPart Pin to PinCompatibilityPolarityРC max, W V CB max, V V CE max, V V EB max, V I Cmax, m А h FE V CE sat, VICBO,μА F T, МHzPacka-ge KT8115AKT8115БKT8115BTIP127 TIP126 TIP125 PNP 65 100 80 60 100 80 60 5 5000 >1000 2.0 200 4 TO-220KT8116AKT8116БKT8116BTIP122 TIP121 TIP120 NPN 65 100 80 60 100 80 60 5 5000 >1000 2.0 200 4 TO-220КТ8214АКТ8214БКТ8214ВTIP110 TIP111 TIP112 NPN 50 60 80 100 60 80 100 5 2000 >500 2.5 1000 TO-220КТ8215АКТ8215БКТ8215ВTIP115 TIP116 TIP117 PNP 50 60 80 100 60 80 100 5 2000 >500 2.5 1000 TO-220KT8156A КТ8156Б BU807 NPN 60 330 150 2006 8000 >100 1.5 1000 TO-220KT8158AKT8158БKT8158BBDV65A BDV65B BDV65C NPN 125 60 80 100 60 80 100 5 12000>1000 2.0 400 TO-218KT8159AKT8159БKT8159ВBDV64A BDV64B BDV64C PNP 125 60 80 100 60 80 100 5 12000>1000 2.0 400 TO-218КТ8225А BU941ZP NPN 155 350 350 5 15000>300 2.7 100 TO-218КТ8251А BDV65F NPN 125 180 180 5 10000>100 2.0 0.4 TO-218KT972AKT972БKT972BKT972ГBD875 NPN 8.0 60 45 60 60 60 45 60 60 5 2000 >750 >750 750…5000 750…5000 1.5 1.5 1.5 0.95 200 TO-126KT973AKT973БKT973BBD876 PNP 8.0 60 45 60 60 45 60 5 2000 >750 >750 750…5000 1.5 1.5 1.5 200 TO-126• Unijunction TransistorsPart Pin to Pin Compatibility P max,W Vb, b2 max, V Ie pulse, A Ie rev, μA Veb sat,V ηPackage KT132A KT132Б 2N2646 2N2647 0.3 35 2.0 12.0 0.2 3.5 0.56…0.75 0.68…0.82 Case 22A-01KT133A KT133Б 2N4870 2N4871 0.3 35 1.5 1.0 2.5 0.56…0.75 0.70…0.85TO-92• Logic Level N-Channel MOSFETsPart Pin to Pin Compatibility Vds max, V Rds (on) Ohm Id max, A Vgs max, VP max, W Vgs (th),VPackageКП723Г IRLZ44 60 0.028 50 ±10 150 1.0…2.0 TO-220 КП727В IRLZ34 60 0.05 30 ±10 88 1.0…2.0 TO-220 КП744Г IRL520 100 0.27 9.2 ±10 60 1.0…2.0 TO-220 КП745Г IRL530 100 0.22 15 ±10 88 1.0…2.0 TO-220 КП746Г IRL540 100 0.077 28 ±10 150 1.0…2.0 TO-220 КП737Г IRL630 200 0.4 18 ±10 50 1.0…2.0 TO-220 КП750Г IRL640 200 0.18 18 ±1050 1.0…2.0 TO-220КП775А КП775БКП775В2SK2498А-В 60 55 60 0.009 0.009 0.011 50 ±20150 1.0…2.01.0…2.0 1.0…2.0TO-220DISCRETE SEMICONDUCTORTransistors73• Low Power MOSFETsPartPin to Pin Compatibility P max, W Vgs max, V Vds max,V Vgs(off), V Rds(on), Ohm Id max, A g fs,A/VPackageКП501А КП501Б КП501ВZVN2120 0.5 ±202402002001.0…3.0 1.0…3.0 10 10 15 10 >0.1 TO-92 КП502А BSS124 1.0 ±10 400 1.5…2.5 28 0.12 0.1 TO-92 КП503А BSS129 1.0 ±10400 1.5…2.5 28 0.12 0.1 TO-92КП504А КП504БКП504ВКП504ГКП504ДКП504ЕBSS88 1.0 1.0 0.7 0.7 0.7 0.7 ±102502502001802002000.6…1.2 8 8 8 10 8 8 0.32 0.14 TO-92 КП505А КП505БКП505ВКП505ГBSS295 1.0 1.0 1.0 0.7 ±1050506080.8…2.0 0.8…2.0 0.8…2.0 0.4…0.8 0.3 0.3 0.3 1.2 1.4 0.5 0.5 0.5 TO-92 КП507A BSS315 1.0 ±20 -50 -0.8…-2.00.8 -1.1 TO-92 КП508A BSS92 1.0 ±20-240 -0.8…-2.020 -0.15 TO-92КП509А9 КП509Б9КП509В9BSS131 0.36 0.50 0.36 ±142402402000.8…-2.0 0.6…-1.2 0.8…-2.0 16 8 16 0.1 0.25 0.1 0.06 0.14 0.06 SOT-23 КП510A9 IRML2402 0.54 ±12 20 0.7…-1.6 0.25 1.2 1.3 SOT-23 КП511A КП511Б TN0535 TN0540 0.75 ±20 350 400 0.8…-2.0 22 0.14 0.125 TO-92 КП523А КП523Б BSS297 1.0 1.0 ±20 ±14 200 200 0.8…2.0 0.8…2.0 2.0 4.0 0.48 0.34 0.5 0.5TO-92 КП214А9 2N7002LT1 0.2 ±40 60 1.0…2.5 7.5 0.115 0.08 SOT-23• Power N-Channel MOSFETsPartPin to Pin Compatibility Vds max, V Rds (on), Ohm Id max, AVgs max,V P max, W Vgs (th),VPackageКП723АКП723БКП723ВIRFZ44 IRFZ45 IRFZ40 60 60 50 0.028 0.035 0.028 50 50 50 ±20 150 2.0…4.0 TO-220 КП726А КП726Б BUZ90A BUZ90 600 2.0 1.6 4.0 4.5 ±20 75 2.0…4.0 TO-220 КП727А КП727Б BUZ71 IRFZ34 50 60 0.1 0.05 14 30±20 75 2.0…4.0 TO-220 КП728Г1,Г2 КП728С1,С2КП728Е1,Е2BUZ80A 700650 600 5.0 4.0 3.0 3.0 ±20 75 2.0…4.0 TO-220 КП739АКП739БКП739ВIRFZ14 IRFZ10 IRFZ15 60 50 60 0.2 0.2 0.3 10 10 8.3 ±20 43 2.0…4.0 TO-220 КП740АКП740БКП740ВIRFZ24 IRFZ20 IRFZ25 60 50 60 0.1 0.1 0.12 17 17 14 ±20 60 2.0…4.0 TO-220 КП741А КП741Б IRFZ48 IRFZ46 60 50 0.018 0.024 50 ±20 190 1502.0…4.0 TO-220 КП742А КП742Б STH75N06 STH80N05 60 50 0.014 0.012 75 80±20200 2.0…4.0 TO-218DISCRETE SEMICONDUCTOR Transistors74 • Power N-Channel MOSFETs (continued)PartPin to Pin Compatibility Vds max, V Rds (on), Ohm Id max, A Vgs max, VP max, W Vgs (th),VPackageКП743А КП743БКП743ВIRF510 IRF511 IRF512 100 80 100 0.54 0.54 0.74 5.6 5.6 4.9 ± 20 43 2.0…4.0 TO-220TO-126 КП743А1 100 0.54 5.5 ±2040 2.0…4.0 TO-126 КП744А КП744БКП744ВIRF520 IRF521 IRF522 100 80 100 0.27 0.27 0.36 9.2 9.2 8.0 ±20 60 2.0…4.0 TO-220 КП745А КП745БКП745ВIRF530 IRF531 IRF532 100 80 100 0.16 0.16 0.23 14.0 14.0 12.0 ±20 88 2.0…4.0 TO-220 КП746А КП746БКП746ВIRF540 IRF541 IRF542 100 80 100 0.077 0.077 0.1 28.0 28.0 25.0 ±20 150 2.0…4.0 TO-220 КП747А IRFP150 100 0.055 41.0 ±20230 2.0…4.0 TO-218 КП748А КП748БКП748ВIRF610 IRF611 IRF612 200 150 200 1.5 1.5 2.4 3.3 3.3 2.6 ±20 36 2.0…4.0 TO-220 КП749А КП749БКП749ВIRF620 IRF621 IRF622 200 150 200 0.8 0.8 1.2 5.2 5.2 4.0 ±20 50 2.0…4.0 TO-220 КП737А КП737БКП737ВIRF630 IRF634 IRF635 200 250 200 0.4 0.45 0.68 9.0 8.1 6.5 ±20 74 2.0…4.0 TO-220 КП750А КП750БКП750ВIRF640 IRF641 IRF642 200 150 200 0.18 0.18 0.22 18.0 18.0 16.0 ±20 125 2.0…4.0 TO-220 КП731А КП731БКП731ВIRF710 IRF711 IRF712 400 350 400 3.6 3.6 5.0 2.0 2.0 1.7 ±20 36 2.0…4.0 TO-220 КП751А КП751БКП751ВIRF720 IRF721 IRF722 400 350 400 1.8 1.8 2.5 3.3 3.3 2.8 ±20 50 2.0…4.0 TO-220 КП752А КП752Б КП752В Pilot ProductionIRF730 IRF731IRF732400 350 400 1.0 1.0 1.5 5.5 5.5 4.5 ±20 74 2.0…4.0 TO-220КП753АКП753Б КП753ВPilot ProductionIRF830 IRF831 IRF832 500 450 500 1.5 1.5 2.0 4.5 4.5 4.0 ±20 74 2.0…4.0 TO-220КП771А STP40N10100 0.04 40 ±20150 2.0…4.0 TO-220 КП776А КП776Б КП776В КП776Г Pilot ProductionIRF740 IRF741 IRF742 IRF744400 350 400 4500.55 0.55 0.8 0.6310.0 10.0 8.3 8.8±20 125 2.0…4.0 TO-220DISCRETE SEMICONDUCTORTransistors75• Power N-Channel MOSFETs (continued)Part Pin to Pin Compatibility Vds max, VRds (on),Ohm Id max, A Vgs max,V P max, W Vgs (th),VPackageКП777А КП777Б КП777ВPilot ProductionIRF840IRF841IRF842 500 450 500 0.85 0.85 1.1 8.0 8.0 7.0±20 125 2.0…4.0 TO-220КП778А IRFP250 200 0.085 30.0 ±20190 2.0…4.0 TO-220КП779А Pilot ProductionIRFP450 500 0.4 14.0 ±20190 2.0…4.0 TO-220 КП780АКП780Б КП780В IRF820 IRF821IRF822500 450 500 3.0 3.0 4.0 2.5 2.5 2.2 ±20 50 2.0…4.0 TO-220 КП781АPilot ProductionIRFP350 400 0.3 16.0 ±20 190 2.0…4.0 TO-220 КП783АPilot Production IRF3205 55 0.008 70.0 ±20200 2.0…4.0 TO-220 КП786А Pilot ProductionBUZ80A 800 3.0 4.0 ±20100 2.0…4.0 TO-220 КП787А Pilot Production BUZ91A 600 0.9 8.0 ±20150 2.0…4.0 TO-220 КП789А Pilot ProductionBUZ111S 320 0.008 80.0 ±20250 2.1…4.0 TO-220• Power P-Channel MOSFETsPart Pin to Pin Compatibility Vds max, V Rds (on), Ohm Id max, A Vgs max, V P max, W Vgs (th),VPackageКП784A IRF9Z34 -60 0.14 -18.0 ±20 88 -2.0…-4.0 TO-220 КП785A IRF9540 -100 0.20 -19.0 ±20 150 -2.0…-4.0 TO-220 КП796АUnderDevelopmentIRF9634 -250 1.0 -4.3 ±20 74 -2.0…-4.0 TO-220。

SN75HVD05中文资料

ORDERING INFORMATION SIGNALINGIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2004, Texas Instruments Incorporated。

8AD15印制电路板的布线设计

8.2.10 差分对布线子规那么(nà me)设置

【Differential Pairs Routing】(差分对布线)规那么主要用于对一组差分对设置 相应的参数(cānshù),设置窗口如以下图。

第二十八页,共34页。

8.2.11 规那么(nà me)设置导游

第二十九页,共34页。

【Routing Topology】〔布线拓扑〕规那么主要用于设置自动布线时导线 (dǎoxiàn)的拓扑网络逻辑。

第二十二页,共34页。

8.2.5 布线(bù xiàn)优先级子规那么设置

【Routing Priority】〔布线(bù

xiàn)优先级〕规那么主要用于设置PCB网络表中布通网络布线(bù

删除不用要的过孔。自动布线进程中,系统有时会运用过多的过孔来完成布线,而过孔在发作电 容的同时,往往也会因加工进程中的毛刺而发作电磁辐射,因此,应尽量添加过孔。

2.手工调整的方法

手工调整可以采用系统提供的相关菜单命令,如取消(qǔxiāo)布线命令、肃清网络命令等,也可

以直接运用一些编辑操作,如选中、删除、复制等。值得一提的是,关于某些不需求删除但需求

8.2 自动布线规那么设置 8.2.1 电气规那么设置 8.2.2 布线规那么设置 8.2.3 导线宽度规那么及优先级的设置 8.2.4 布线拓扑(tuò pū)子规那么设置 8.2.5 布线优先级子规那么设置 8.2.6 布线层子规那么设置 8.2.7 布线拐角子规那么设置 8.2.8 过孔子规那么设置 8.2.9 扇出布线子规那么设置 8.2.10 差分对布线子规那么设置 8.2.11 规那么设置导游

第三页,共34页。

8.1.1 放置(fàngzhì)焊盘

AD8065中文资料

Portable battery-powered applications Waveform generators Analog processing Instrumentation applications Programmable amplifiers and attenuators Digitally controlled calibration Programmable filters and oscillators Composite video Ultrasound Gain, offset, and voltage trimming

元器件交易网

AD5429/AD5439/AD5449

TABLE OF CONTENTS

Specifications..................................................................................... 3 Timing Characteristics..................................................................... 5 Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7 Pin Configuration and Function Descriptions............................. 8 Terminology ...................................................................................... 9 Typical Performance Characteristics ........................................... 10 General Description ....................................................................... 15

AD815ARB-24中文资料

AD815

coupling transformer with a greater than 1:1 turns ratio. The low harmonic distortion of –66 dB @ 1 MHz into 200 Ω combined with the wide bandwidth and high current drive make the differential driver ideal for communication applications such as subscriber line interfaces for ADSL, HDSL and VDSL. The AD815 differential slew rate of 900 V/µs and high load drive are suitable for fast dynamic control of coils or transformers, and the video performance of 0.05% and 0.45° differential gain and phase into a load of 25 Ω enable up to 12 back-terminated loads to be driven. Three package styles are available, and all work over the industrial temperature range (–40°C to +85 °C). Maximum output power is achieved with the power package available for through-hole mounting (Y) and surface-mounting (VR). The 24-lead SOIC (RB) is capable of driving 26 dBm for full rate ADSL with proper heat sinking.

ADC08D500资料

ADC08D500High Performance,Low Power,Dual 8-Bit,500MSPS A/D ConverterGeneral DescriptionThe ADC08D500is a dual,low power,high performance CMOS analog-to-digital converter that digitizes signals to 8bits resolution at sampling rates up to 800MSPS.Consum-ing a typical 1.4Watts at 500MSPS from a single 1.9Volt supply,this device is guaranteed to have no missing codes over the full operating temperature range.The unique folding and interpolating architecture,the fully differential compara-tor design,the innovative design of the internal sample-and-hold amplifier and the self-calibration scheme enable a very flat response of all dynamic parameters beyond Nyquist,producing a high 7.5ENOB with a 250MHz input signal and a 500MHz sample rate while providing a 10-18B.E.R.Output formatting is offset binary and the LVDS digital outputs are compliant with IEEE 1596.3-1996,with the exception of an adjustable common mode voltage between 0.8V and 1.2V.Each converter has a 1:2demultiplexer that feeds two LVDS buses and reduces the output data rate on each bus to half the sampling rate.The two converters can be interleaved and used as a single 1GSPS ADC.The converter typically consumes less than 3.5mW in the Power Down Mode and is available in a 128-lead,thermally enhanced exposed pad LQFP and operates over the Indus-trial (-40˚C ≤T A ≤+85˚C)temperature range.Featuresn Internal Sample-and-Holdn Single +1.9V ±0.1V Operationn Choice of SDR or DDR output clocking n Interleave Mode for 2x Sampling Rate n Multiple ADC Synchronization Capability n Guaranteed No Missing Codesn Serial Interface for Extended Controln Fine Adjustment of Input Full-Scale Range and Offset nDuty Cycle Corrected Sample ClockKey Specificationsn Resolution8Bitsn Max Conversion Rate 500MSPS (min)n Bit Error Rate10-18(typ)n ENOB @250MHz Input 7.5Bits (typ)n DNL±0.15LSB (typ)nPower Consumption —Operating1.4W (typ)—Power Down Mode3.5mW (typ)Applicationsn Direct RF Down Conversion n Digital Oscilloscopes n Satellite Set-top boxes n Communications Systems nTest InstrumentationBlock Diagram20121453May 2005High Performance,Low Power,Dual 8-Bit,500MSPS A/D Converter©2005National Semiconductor Corporation Ordering InformationIndustrial Temperature Range (-40˚C <T A <+85˚C)NS PackageADC08D500CIYB 128-Pin Exposed Pad LQFPADC08D500EVALEvaluation BoardPin Configuration20121401*Exposed pad on back of package must be soldered to ground plane to ensure rated performance.A D C 08D 500 2Pin Descriptions and Equivalent CircuitsPin FunctionsPin No.Symbol Equivalent Circuit Description3OutV/SCLK Output Voltage Amplitude and Serial Interface Clock.Tie this pin high for normal differential DCLK and data amplitude. Ground this pin for a reduced differential output amplitude and reduced power consumption.See Section1.1.6.When the extended control mode is enabled,this pin functions as the SCLK input which clocks in the serial data.See Section1.2for details on the extended control mode.See Section1.3for description of the serial interface.4OutEdge/DDR/SDATADCLK Edge Select,Double Data Rate Enable and Serial DataInput.This input sets the output edge of DCLK+at which theoutput data transitions.(See Section1.1.5.2).When this pin isfloating or connected to1/2the supply voltage,DDR clockingis enabled.When the extended control mode is enabled,thispin functions as the SDATA input.See Section1.2for detailson the extended control mode.See Section1.3for descriptionof the serial interface.15DCLK_RST DCLK Reset.A positive pulse on this pin is used to reset and synchronize the DCLK outs of multiple converters.See Section1.5for detailed description.26 29PDPDQPower Down Pins.A logic high on the PD pin puts the entiredevice into the Power Down Mode.A logic high on the PDQpin puts only the"Q"ADC into the Power Down mode.30CAL Calibration Cycle Initiate.A minimum80input clock cycles logic low followed by a minimum of80input clock cycles high on this pin initiates the self calibration sequence.See Section2.4.2for an overview of self-calibration and Section2.4.2.2fora description of on-command calibration.14FSR/ECE Full Scale Range Select and Extended Control Enable.In non-extended control mode,a logic low on this pin sets the full-scale differential input range to650mV P-P.A logic high on this pin sets the full-scale differential input range to870mV P-P.See Section1.1.4.To enable the extended control mode,whereby the serial interface and control registers are employed,allow this pin to float or connect it to a voltage equal to V A/2.See Section1.2for information on the extended control mode.127CalDly/DES/SCSCalibration Delay,Dual Edge Sampling and Serial InterfaceChip Select.With a logic high or low on pin14,this pinfunctions as Calibration Delay and sets the number of clockcycles after power up before calibration begins(See Section1.1.1).With pin14floating,this pin acts as the enable pin forthe serial interface input and the CalDly value becomes0b(short delay with no provision for a long power-up calibrationdelay).When this pin is floating or connected to a voltageequal to V A/2,DES(Dual Edge Sampling)mode is selectedwhere the"I"input is sampled at twice the clock rate and the"Q"input is ignored.See Section1.1.5.1.ADC08D5003Pin Descriptions and Equivalent Circuits(Continued)Pin Functions Pin No.SymbolEquivalent CircuitDescription1819CLK+CLK-LVDS Clock input pins for the ADC.The differential clock signal must be a.c.coupled to these pins.The input signal is sampled on the falling edge of CLK+.See Section 1.1.2for a description of acquiring the input and Section 2.3for an overview of the clock inputs.1110.2223V IN I+V IN I−.V IN Q+V IN Q−Analog signal inputs to the ADC.The differential full-scale input range is 650mV P-P when the FSR pin is low,or 870mV P-P when the FSR pin is high.7V CMOCommon Mode Voltage.The voltage output at this pin is required to be the common mode input voltage at V IN +and V IN −when d.c.coupling is used.This pin should be grounded when a.c.coupling is used at the analog inputs.This pin is capable of sourcing or sinking 100µA.See Section 2.2.31V BG Bandgap output voltage capable of 100µA source/sink.126CalRunCalibration Running indication.This pin is at a logic high when calibration is running.32R EXTExternal bias resistor connection.Nominal value is 3.3k-Ohms (±0.1%)to ground.See Section 1.1.1.3435Tdiode_P Tdiode_N Temperature Diode Positive (Anode)and Negative (Cathode)for die temperature measurements.See Section 2.6.2.A D C 08D 500 4Pin Descriptions and Equivalent Circuits(Continued)Pin FunctionsPin No.Symbol Equivalent Circuit Description83/78 84/77 85/76 86/75 89/72 90/71 91/70 92/69 93/68 94/67 95/66 96/65 100/61 101/60 102/59 103/58DI7−/DQ7−DI7+/DQ7+DI6−/DQ6−DI6+/DQ6+DI5−/DQ5−DI5+/DQ5+DI4−/DQ4−DI4+/DQ4+DI3−/DQ3−DI3+/DQ3+DI2−/DQ2−DI2+/DQ2+DI1−/DQ1−DI1+/DQ1+DI0−/DQ0−DI0+/DQ0+I and Q channel LVDS Data Outputs that are not delayed inthe output pared with the DId and DQdoutputs,these outputs represent the later time samples.These outputs should always be terminated with a100Ωdifferential resistor.104/57 105/56 106/55 107/54 111/50 112/49 113/48 114/47 115/46 116/45 117/44 118/43 122/39 123/38 124/37 125/36DId7−/DQd7−DId7+/DQd7+DId6−/DQd6−DId6+/DQd6+DId5−/DQd5−DId5+/DQd5+DId4−/DQd4−DId4+/DQd4+DId3−/DQd3−DId3+/DQd3+DId2−/DQd2−DId2+/DQd2+DId1−/DQd1−DId1+/DQd1+DId0−/DQd0−DId0+/DQd0+I and Q channel LVDS Data Outputs that are delayed by oneCLK cycle in the output pared with theDI/DQ outputs,these outputs represent the earlier timesample.These outputs should always be terminated with a100Ωdifferential resistor.79 80OR+OR-Out Of Range output.A differential high at these pinsindicates that the differential input is out of range(outside therange±325mV or±435mV as defined by the FSR pin).82 81DCLK+DCLK-Differential Clock outputs used to latch the output data.Delayed and non-delayed data outputs are suppliedsynchronous to this signal.This signal is at1/2the input clockrate in SDR mode and at1/4the input clock rate in the DDRmode.2,5,8, 13,16,17,20, 25,28, 33,128V A Analog power supply pins.Bypass these pins to ground.ADC08D5005Pin Descriptions and Equivalent Circuits(Continued)Pin Functions Pin No.SymbolEquivalent CircuitDescription40,51,62,73,88,99,110,121V DROutput Driver power supply pins.Bypass these pins to DR GND.1,6,9,12,21,24,27,41GNDGround return for V A .42,53,64,74,87,97,108,119DR GNDGround return for V DR .52,63,98,109,120NC No Connection.Make no connection to these pins.A D C 08D 500 6Absolute Maximum Ratings(Notes1, 2)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage(V A,V DR) 2.2V Voltage on Any Input Pin−0.15V to(V A+0.15V) Ground Difference|GND-DR GND|0V to100mV Input Current at Any Pin(Note3)±25mA Package Input Current(Note3)±50mA Power Dissipation at T A=85˚C 2.0W ESD Susceptibility(Note4)Human Body Model Machine Model 2500V 250VSoldering Temperature,Infrared,10seconds(Note5)235˚C Storage Temperature−65˚C to+150˚C Operating Ratings(Notes1,2)Ambient Temperature Range−40˚C≤T A≤+85˚C Supply Voltage(V A)+1.8V to+2.0V Driver Supply Voltage(V DR)+1.8V to V A Analog Input Common ModeVoltage V CMO±50mV V IN+,V IN-Voltage Range(Maintaining Common Mode)200mV to V A Ground Difference(|GND-DR GND|)0V CLK Pins Voltage Range0V to V A Differential CLK Amplitude0.4V P-P to2.0V P-P Package Thermal ResistancePackageθJAθJC(Top ofPackage)θJ-PAD(ThermalPad) 128-LeadExposed PadLQFP25˚C/W10˚C/W 2.8˚C/WConverter Electrical CharacteristicsThe following specifications apply after calibration for V A=V DR=+1.9V DC,OutV=1.9V,V IN FSR(a.c.coupled)=differential 870mV P-P,C L=10pF,Differential,a.c.coupled Sinewave Input Clock,f CLK=500MHz at0.5V P-P with50%duty cycle,V BG= Floating,Non-Extended Control Mode,SDR Mode,R EXT=3300Ω±0.1%,Analog Signal Source Impedance=100ΩDifferen-tial.Boldface limits apply for T A=T MIN to T MAX.All other limits T A=25˚C,unless otherwise noted.(Notes6,7)Symbol Parameter Conditions Typical(Note8)Limits(Note8)Units(Limits)STATIC CONVERTER CHARACTERISTICSINL Integral Non-Linearity DC Coupled,1MHz Sine WaveOveranged±0.3±0.9LSB(max)DNL Differential Non-Linearity DC Coupled,1MHz Sine WaveOveranged±0.15±0.6LSB(max)Resolution with No Missing Codes8BitsV OFF Offset Error-0.45−1.50.5LSB(min)LSB(max)V OFF_ADJ Input Offset Adjustment Range Extended Control Mode±45mV PFSE Positive Full-Scale Error(Note9)−0.6±25mV(max) NFSE Negative Full-Scale Error(Note9)−1.31±25mV(max) FS_ADJ Full-Scale Adjustment Range Extended Control Mode±20±15%FS NORMAL MODE(non DES)DYNAMIC CONVERTER CHARACTERISTICSFPBW Full Power Bandwidth Normal(non DES)Mode 1.7GHz B.E.R.Bit Error Rate10-18Error/SampleGain Flatness d.c.to500MHz±0.5dBFSENOB Effective Number of Bits f IN=50MHz,V IN=FSR−0.5dB7.5Bitsf IN=100MHz,V IN=FSR−0.5dB7.57.1Bits(min) f IN=248MHz,V IN=FSR−0.5dB7.57.1Bits(min)SINAD Signal-to-Noise Plus DistortionRatiof IN=50MHz,V IN=FSR−0.5dB47dBf IN=100MHz,V IN=FSR−0.5dB4744.5dB(min)f IN=248MHz,V IN=FSR−0.5dB4744.5dB(min)ADC08D5007Converter Electrical Characteristics(Continued)The following specifications apply after calibration for V A =V DR =+1.9V DC ,OutV =1.9V,V IN FSR (a.c.coupled)=differential 870mV P-P ,C L =10pF,Differential,a.c.coupled Sinewave Input Clock,f CLK =500MHz at 0.5V P-P with 50%duty cycle,V BG =Floating,Non-Extended Control Mode,SDR Mode,R EXT =3300Ω±0.1%,Analog Signal Source Impedance =100ΩDifferen-tial.Boldface limits apply for T A =T MIN to T MAX .All other limits T A =25˚C,unless otherwise noted.(Notes 6,7)SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)NORMAL MODE (non DES)DYNAMIC CONVERTER CHARACTERISTICSSNRSignal-to-Noise Ratiof IN =50MHz,V IN =FSR −0.5dB48dB f IN =100MHz,V IN =FSR −0.5dB 4845.3dB (min)f IN =248MHz,V IN =FSR −0.5dB 47.545.3dB (min)THDTotal Harmonic Distortionf IN =50MHz,V IN =FSR −0.5dB-55dB f IN =100MHz,V IN =FSR −0.5dB -55−47.5dB (max)f IN =248MHz,V IN =FSR −0.5dB -55−47.5dB (max)2nd HarmSecond Harmonic Distortionf IN =50MHz,V IN =FSR −0.5dB−60dB f IN =100MHz,V IN =FSR −0.5dB −60dB f IN =248MHz,V IN =FSR −0.5dB −60dB 3rd HarmThird Harmonic Distortionf IN =50MHz,V IN =FSR −0.5dB−65dB f IN =100MHz,V IN =FSR −0.5dB −65dB f IN =248MHz,V IN =FSR −0.5dB −65dB SFDRSpurious-Free dynamic Rangef IN =50MHz,V IN =FSR −0.5dB55dB f IN =100MHz,V IN =FSR −0.5dB 5547.5dB (min)f IN =248MHz,V IN =FSR −0.5dB5547.5dB (min)IMDIntermodulation Distortion f IN1=121MHz,V IN =FSR −7dB f IN2=126MHz,V IN =FSR −7dB -50dBOut of Range Output Code (In addition to OR Output high)(V IN +)−(V IN −)>+Full Scale 255(V IN +)−(V IN −)<−Full Scale0INTERLEAVE MODE (DES Pin 127=Float)-DYNAMIC CONVERTER CHARACTERISTICSFPBW (DES)Full Power Bandwidth Dual Edge Sampling Mode 900MHz ENOB Effective Number of Bits f IN =100MHz,V IN =FSR −0.5dB 7.47.0Bits (min)f IN =248MHz,V IN =FSR −0.5dB 7.47.0Bits (min)SINAD Signal to Noise Plus Distortion Ratiof IN =100MHz,V IN =FSR −0.5dB 46.343.9dB (min)f IN =248MHz,V IN =FSR −0.5dB 46.343.9dB (min)SNR Signal to Noise Ratio f IN =100MHz,V IN =FSR −0.5dB 46.744.1dB (min)f IN =248MHz,V IN =FSR −0.5dB 46.744.1dB (min)THD Total Harmonic Distortion f IN =100MHz,V IN =FSR −0.5dB -58-49dB (min)f IN =248MHz,V IN =FSR −0.5dB -58-49dB (min)2nd Harm Second Harmonic Distortion f IN =100MHz,V IN =FSR −0.5dB -60dB f IN =248MHz,V IN =FSR −0.5dB -60dB 3rd Harm Third Harmonic Distortion f IN =100MHz,V IN =FSR −0.5dB -64dB f IN =248MHz,V IN =FSR −0.5dB -64dB SFDRSpurious Free Dynamic Rangef IN =248MHz,V IN =FSR −0.5dB 5747dB(min)f IN =248MHz,V IN =FSR −0.5dB5747dB(min)ANALOG INPUT AND REFERENCE CHARACTERISTICSV INFull Scale Analog Differential Input RangeFSR pin 14Low 650570mV P-P (min)730mV P-P (max)FSR pin 14High870790mV P-P (min)950mV P-P (max)V CMIAnalog Input Common Mode VoltageV CMOV CMO −50V CMO +50mV (min)mV (max)A D C 08D 500 8Converter Electrical Characteristics(Continued)The following specifications apply after calibration for V A=V DR=+1.9V DC,OutV=1.9V,V IN FSR(a.c.coupled)=differential 870mV P-P,C L=10pF,Differential,a.c.coupled Sinewave Input Clock,f CLK=500MHz at0.5V P-P with50%duty cycle,V BG= Floating,Non-Extended Control Mode,SDR Mode,R EXT=3300Ω±0.1%,Analog Signal Source Impedance=100ΩDifferen-tial.Boldface limits apply for T A=T MIN to T MAX.All other limits T A=25˚C,unless otherwise noted.(Notes6,7)Symbol Parameter Conditions Typical(Note8)Limits(Note8)Units(Limits)ANALOG INPUT AND REFERENCE CHARACTERISTICSC IN Analog Input Capacitance,Normaloperation(Notes10,11)Differential0.02pFEach input pin to ground 1.6pF Analog Input Capacitance,DESMode(Notes10,11)Differential0.08pFEach input pin to ground 2.2pFR IN Differential Input Resistance10094Ω(min) 106Ω(max)ANALOG OUTPUT CHARACTERISTICSV CMO Common Mode Output Voltage 1.260.951.45V(min)V(max)V CMO_LVL V CMO input threshold to set DCCoupling modeV A=1.8V0.60VV A=2.0V0.66VTC V CMO Common Mode Output VoltageTemperature CoefficientT A=−40˚C to+85˚C118ppm/˚CC LOADV CMOMaximum V CMO load Capacitance80pFV BG Bandgap Reference OutputVoltageI BG=±100µA 1.261.201.33V(min)V(max)TC V BG Bandgap Reference VoltageTemperature CoefficientT A=−40˚C to+85˚C,I BG=±100µA28ppm/˚CC LOAD V BG Maximum Bandgap ReferenceLoad Capacitance80pFTEMPERATURE DIODE CHARACTERISTICS∆V BE Temperature Diode Voltage 192µA vs.12µA,T J=25˚C71.23mV 192µA vs.12µA,T J=85˚C85.54mVCHANNEL-TO-CHANNEL CHARACTERISTICSOffset Error Match1LSBPositive Full-Scale Error Match Zero offset selected in ControlRegister1LSBNegative Full-Scale Error Match Zero offset selected in ControlRegister1LSBPhase Matching(I,Q)F IN=1.0GHz<1DegreeX-TALK Crosstalk from I(Agressor)to Q(Victim)ChannelAggressor=867MHz F.S.Victim=100MHz F.S.−71dBX-TALK Crosstalk from Q(Agressor)to I(Victim)ChannelAggressor=867MHz F.S.Victim=100MHz F.S.-71dBCLOCK INPUT CHARACTERISTICSV ID Differential Clock Input Level Sine Wave Clock0.60.42.0V P-P(min)V P-P(max) Square Wave Clock0.60.42.0V P-P(min)V P-P(max)I I Input Current V IN=0or V IN=V A±1µAC IN Input Capacitance(Notes10,11)Differential0.02pFEach input to ground 1.5pFADC08D500 9Converter Electrical Characteristics(Continued)The following specifications apply after calibration for V A =V DR =+1.9V DC ,OutV =1.9V,V IN FSR (a.c.coupled)=differential 870mV P-P ,C L =10pF,Differential,a.c.coupled Sinewave Input Clock,f CLK =500MHz at 0.5V P-P with 50%duty cycle,V BG =Floating,Non-Extended Control Mode,SDR Mode,R EXT =3300Ω±0.1%,Analog Signal Source Impedance =100ΩDifferen-tial.Boldface limits apply for T A =T MIN to T MAX .All other limits T A =25˚C,unless otherwise noted.(Notes 6,7)SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)DIGITAL CONTROL PIN CHARACTERISTICS V IH Logic High Input Voltage (Note 12)0.85x V A V (min)V IL Logic Low Input Voltage(Note 12)0.15x V AV (max)C INInput Capacitance (Notes 11,13)Each input to ground1.2pF DIGITAL OUTPUT CHARACTERISTICSV ODLVDS Differential Output VoltageMeasured differentially,OutV =V A ,V BG =Floating,(Note 15)710400mV P-P (min)920mV P-P (max)Measured differentially,OutV =GND,V BG =Floating,(Note 15)510280mV P-P (min)720mV P-P (max)∆V O DIFF Change in LVDS Output Swing Between Logic Levels±1mV V OS Output Offset Voltage,see Figure 1V BG =Floating 800mV V OS Output Offset Voltage,see Figure 1V BG =V A (Note 15)1200mV ∆V OS Output Offset Voltage Change Between Logic Levels ±1mV I OS Output Short Circuit Current Output+&Output-connected to 0.8V−4mA Z O Differential Output Impedance 100OhmsV OH Cal_Run H level output I OH =-400uA (Note 12) 1.65 1.5V V OLCal_Run L level outputI OH =400uA (Note 12)0.150.3V POWER SUPPLY CHARACTERISTICS I AAnalog Supply CurrentPD =PDQ =LowPD =Low,PDQ =High PD =PDQ =High 5613401.8665408mA (max)mA mA I DROutput Driver Supply CurrentPD =PDQ =LowPD =Low,PDQ =High PD =PDQ =High 2001120.012275157mA (max)mA (max)mA P DPower ConsumptionPD =PDQ =LowPD =Low,PDQ =High PD =PDQ =High1.40.83.5 1.781.0W (max)W mW PSRR1 D.C.Power Supply Rejection Ratio Change in Full Scale Error with change in V A from 1.8V to 2.0V 30dB PSRR2A.C.Power Supply Rejection Ratio248MHz,50mV P-P riding on V A 51dBAC ELECTRICAL CHARACTERISTICS f CLK1Maximum Input Clock Frequency Normal Mode (non DES)or DES Mode800500MHz (min)f CLK2Minimum Input Clock Frequency Normal Mode (non DES)200MHz f CLK2Minimum Input Clock Frequency DES Mode450MHz Input Clock Duty Cycle 200MHz ≤Input clock frequency ≤800MHz (Normal Mode)(Note 12)502080%(min)%(max)Input Clock Duty Cycle450MHz ≤Input clock frequency ≤800MHz (DES Mode)(Note 12)502080%(min)%(max)t CL Input Clock Low Time (Note 12)500400ps (min)t CHInput Clock High Time(Note 12)500400ps (min)A D C 08D 500 10Converter Electrical Characteristics(Continued)The following specifications apply after calibration for V A=V DR=+1.9V DC,OutV=1.9V,V IN FSR(a.c.coupled)=differential 870mV P-P,C L=10pF,Differential,a.c.coupled Sinewave Input Clock,f CLK=500MHz at0.5V P-P with50%duty cycle,V BG= Floating,Non-Extended Control Mode,SDR Mode,R EXT=3300Ω±0.1%,Analog Signal Source Impedance=100ΩDifferen-tial.Boldface limits apply for T A=T MIN to T MAX.All other limits T A=25˚C,unless otherwise noted.(Notes6,7)Symbol Parameter Conditions Typical(Note8)Limits(Note8)Units(Limits)AC ELECTRICAL CHARACTERISTICSDCLK Duty Cycle(Note12)504555%(min)%(max)t RS Reset Setup Time(Note12)150ps t RH Reset Hold Time(Note12)250pst SD Syncronizing Edge to DCLK OutputDelayf CLKIN=500MHzf CLKIN=200MHz3.533.85nst RPW Reset Pulse Width(Note11)4Clock Cycles(min)t LHT Differential Low to High TransitionTime10%to90%,C L=2.5pF250pst HLT Differential High to Low TransitionTime10%to90%,C L=2.5pF250pst OSK DCLK to Data Output Skew 50%of DCLK transition to50%ofData transition,SDR Modeand DDR Mode,0˚DCLK(Note12)±50ps(max)t SU Data to DCLK Set-Up Time DDR Mode,90˚DCLK(Note12)2ns t H DCLK to Data Hold Time DDR Mode,90˚DCLK(Note12)2nst AD Sampling(Aperture)Delay Input CLK+Fall to Acquisition ofData1.3nst AJ Aperture Jitter0.4ps rmst OD Input Clock to Data Output Delay(in addition to Pipeline Delay)50%of Input Clock transition to50%of Data transition3.1nsPipeline Delay(Latency)(Notes11,14)DI Outputs13Clock CyclesDId Outputs14DQ OutputsNormal Mode13DES Mode13.5DQd OutputsNormal Mode14DES Mode14.5Over Range Recovery TimeDifferential V IN step from±1.2V to0V to get accurate conversion1Input ClockCyclet WU PD low to Rated AccuracyConversion(Wake-Up Time)500nsf SCLK Serial Clock Frequency(Note12)100MHzt SSU Data to Serial Clock Setup Time(Note12) 2.5ns(min)t SH Data to Serial Clock Hold Time(Note12)1ns(min) Serial Clock Low Time4ns(min)Serial Clock High Time4ns(min)t CAL Calibration Cycle Time 1.4x105Clock Cyclest CAL_L CAL Pin Low Time See Figure9(Note11)80Clock Cycles(min)t CAL_H CAL Pin High Time See Figure9(Note11)80Clock Cycles(min)t CalDly Calibration delay determined by pin127See Section1.1.1,Figure9,(Note15)225Clock Cycles(min)ADC08D500Converter Electrical Characteristics(Continued)The following specifications apply after calibration for V A =V DR =+1.9V DC ,OutV =1.9V,V IN FSR (a.c.coupled)=differential 870mV P-P ,C L =10pF,Differential,a.c.coupled Sinewave Input Clock,f CLK =500MHz at 0.5V P-P with 50%duty cycle,V BG =Floating,Non-Extended Control Mode,SDR Mode,R EXT =3300Ω±0.1%,Analog Signal Source Impedance =100ΩDifferen-tial.Boldface limits apply for T A =T MIN to T MAX .All other limits T A =25˚C,unless otherwise noted.(Notes 6,7)SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)AC ELECTRICAL CHARACTERISTICS t CalDlyCalibration delay determined by pin 127See Section 1.1.1,Figure 9,(Note 15)231Clock Cycles(max)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.There is no guarantee of operation at the Absolute MaximumRatings.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:All voltages are measured with respect to GND =DR GND =0V,unless otherwise specified.Note 3:When the input voltage at any pin exceeds the power supply limits (that is,less than GND or greater than V A ),the current at that pin should be limited to 25mA.The 50mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25mA to two.This limit is not placed upon the power,ground and digital output pins.Note 4:Human body model is 100pF capacitor discharged through a 1.5k Ωresistor.Machine model is 220pF discharged through ZERO Ohms.Note 5:See AN-450,“Surface Mounting Methods and Their Effect on Product Reliability”.Note 6:The analog inputs are protected as shown below.Input voltage magnitudes beyond the Absolute Maximum Ratings may damage this device.20121404Note 7:To guarantee accuracy,it is required that V A and V DR be well bypassed.Each supply pin must be decoupled with separate bypass capacitors.Additionally,achieving rated performance requires that the backside exposed pad be well grounded.Note 8:Typical figures are at T A =25˚C,and represent most likely parametric norms.Test limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 9:Calculation of Full-Scale Error for this device assumes that the actual reference voltage is exactly its nominal value.Full-Scale Error for this device,therefore,is a combination of Full-Scale Error and Reference Voltage Error.See Transfer Characteristic Figure 2.For relationship between Gain Error and Full-Scale Error,see Specification Definitions for Gain Error.Note 10:The analog and clock input capacitances are die capacitances only.Additional package capacitances of 0.65pF differential and 0.95pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 11:This parameter is guaranteed by design and is not tested in production.Note 12:This parameter is guaranteed by design and/or characterization and is not tested in production.Note 13:The digital control pin capacitances are die capacitances only.Additional package capacitance of 1.6pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 14:Each of the two converters of the ADC08D500has two LVDS output buses,which each clock data out at one half the sample rate.The data at each bus is clocked out at one half the sample rate.The second bus (D0through D7)has a pipeline latency that is one clock cycle less than the latency of the first bus (Dd0through Dd7)Note 15:Tying V BG to the supply rail will increase the output offset voltage (V OS )by 400mv (typical),as shown in the V OS specification above.Tying V BG to the supply rail will also affect the differential LVDS output voltage (V OD ),causing it to increase by 40mV (typical).A D C 08D 500Specification DefinitionsAPERTURE(SAMPLING)DELAY is that time required after the fall of the clock input for the sampling switch to open.The Sample/Hold circuit effectively stops capturing the input sig-nal and goes into the“hold”mode the aperture delay time (t AD)after the clock goes low.APERTURE JITTER(t AJ)is the variation in aperture delay from sample to sample.Aperture jitter shows up as input noise.Bit Error Rate(B.E.R.)is the probability of error and is defined as the probable number of errors per unit of time divided by the number of bits seen in that amount of time.A B.E.R.of10-18corresponds to a statistical error in one bit about every four(4)years.CLOCK DUTY CYCLE is the ratio of the time that the clock wave form is at a logic high to the total time of one clock period.DIFFERENTIAL NON-LINEARITY(DNL)is the measure of the maximum deviation from the ideal step size of1LSB. Measured at500MSPS with a ramp input.EFFECTIVE NUMBER OF BITS(ENOB,or EFFECTIVE BITS)is another method of specifying Signal-to-Noise and Distortion Ratio,or SINAD.ENOB is defined as(SINAD−1.76)/6.02and says that the converter is equivalent to a perfect ADC of this(ENOB)number of bits.FULL POWER BANDWIDTH(FPBW)is a measure of the frequency at which the reconstructed output fundamental drops3dB below its low frequency value for a full scale input.GAIN ERROR is the deviation from the ideal slope of the transfer function.It can be calculated from Offset and Full-Scale Errors:Positive Gain Error=Offset Error−Positive Full-Scale ErrorNegative Gain Error=−(Offset Error−Negative Full-Scale Error)Gain Error=Negative Full-Scale Error−Positive Full-Scale Error=Positive Gain Error+Negative Gain Error INTEGRAL NON-LINEARITY(INL)is a measure of the deviation of each individual code from a straight line through the input to output transfer function.The deviation of any given code from this straight line is measured from the center of that code value.The best fit method is used. INTERMODULATION DISTORTION(IMD)is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time. It is defined as the ratio of the power in the second and third order intermodulation products to the power in one of the original frequencies.IMD is usually expressed in dBFS. LSB(LEAST SIGNIFICANT BIT)is the bit that has the smallest value or weight of all bits.This value isV FS/2nwhere V FS is the differential full-scale amplitude of650mV or870mV as set by the FSR input and"n"is the ADC resolution in bits,which is8for the ADC08D500.LVDS DIFFERENTIAL OUTPUT VOLTAGE(V OD)is the absolute value of the difference between the V D+&V D-outputs;each measured with respect to Ground.LVDS OUTPUT OFFSET VOLTAGE(V OS)is the midpoint between the D+and D-pins output voltage;ie.,[(V D+)+(V D-)]/2.MISSING CODES are those output codes that are skippedand will never appear at the ADC outputs.These codescannot be reached with any input value.MSB(MOST SIGNIFICANT BIT)is the bit that has thelargest value or weight.Its value is one half of full scale. NEGATIVE FULL-SCALE ERROR(NFSE)is a measure ofhow far the last code transition is from the ideal1/2LSBabove a differential−870mV with the FSR pin high,or1/2LSB above a differential−650mV with the FSR pin low.Forthe ADC08D500the reference voltage is assumed to beideal,so this error is a combination of full-scale error and reference voltage error.OFFSET ERROR(V OFF)is a measure of how far the mid-scale point is from the ideal zero voltage differential input.Offset Error=Actual Input causing average of8k samples to result in an average code of127.5.OUTPUT DELAY(t OD)is the time delay after the falling edgeof DCLK before the data update is present at the output pins.OVER-RANGE RECOVERY TIME is the time required afterthe differential input voltages goes from±1.2V to0V for the converter to recover and make a conversion with its rated accuracy.PIPELINE DELAY(LATENCY)is the number of clock cycles between initiation of conversion and when that data is pre-sented to the output driver stage.New data is available atevery clock cycle,but the data lags the conversion by the Pipeline Delay plus the t OD.POSITIVE FULL-SCALE ERROR(PFSE)is a measure ofhow far the last code transition is from the ideal1-1/2LSBbelow a differential+870mV with the FSR pin high,or1-1/2LSB below a differential+650mV with the FSR pin low.Forthe ADC08D500the reference voltage is assumed to beideal,so this error is a combination of full-scale error and reference voltage error.POWER SUPPLY REJECTION RATIO(PSRR)can be oneof two specifications.PSRR1(DC PSRR)is the ratio of the change in full-scale error that results from a power supply voltage change from1.8V to2.0V.PSRR2(AC PSRR)is a measure of how well an a.c.signal riding upon the powersupply is rejected from the output and is measured with a248MHz,50mV P-P signal riding upon the power supply.It isthe ratio of the output amplitude of that signal at the output toits amplitude on the power supply pin.PSRR is expressed indB.SIGNAL TO NOISE RATIO(SNR)is the ratio,expressed indB,of the rms value of the input signal at the output to the20121446FIGURE1.ADC08D500。

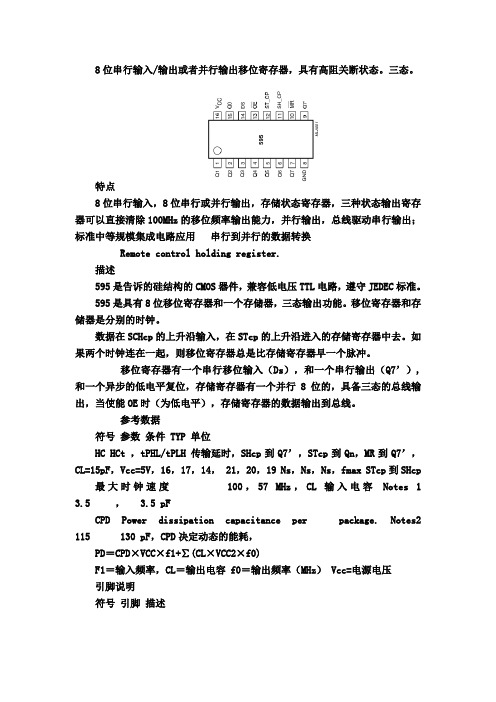

595芯片中文资料

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点8位串行输入,8位串行或并行输出,存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力,并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register.描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据符号参数条件 TYP 单位HC HCt ,tPHL/tPLH 传输延时,SHcp到Q7’,STcp到Qn,MR到Q7’,CL=15pF,Vcc=5V,16,17,14, 21,20,19 Ns,Ns,Ns,fmax STcp到SHcp 最大时钟速度100,57 MHz,CL 输入电容Notes 1 3.5 , 3.5 pFCPD Power dissipation capacitance per package. Notes2 115 130 pF,CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述Q0…Q7 15, 1, 7 并行数据输出,GND 8 地,Q7’ 9 串行数据输出,MR 10 主复位(低电平),SHCP 11 移位寄存器时钟输入,STCP 12 存储寄存器时钟输入,OE 13 输出有效(低电平),DS 14 串行数据输入,VCC 16 电源功能表输入输出功能SHCP STCP OE MR DS Q7’ Qn× × L ↓ × L NC MR为低电平时紧紧影响移位寄存器× ↑ L L × L L 空移位寄存器到输出寄存器× × H L × L Z 清空移位寄存器,并行输出为高阻状态↑ × L H H Q6’ NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

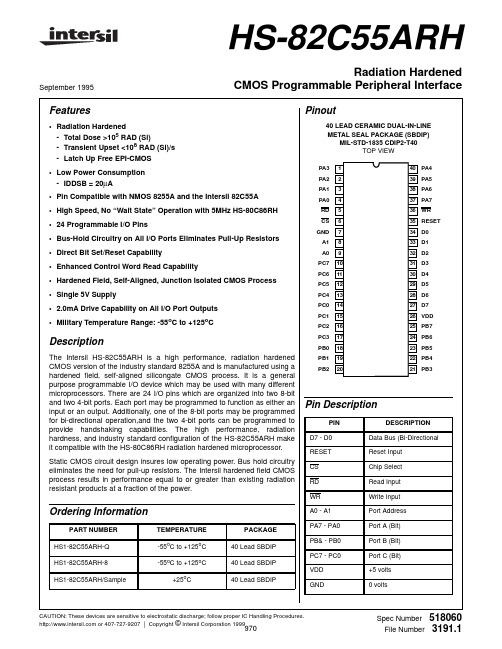

82C55

TEMPERATURE -55oC to +125oC -55oC to +125oC

+25oC

PACKAGE 40 Lead SBDIP 40 Lead SBDIP 40 Lead SBDIP

PA7 - PA0 PB& - PB0 PC7 - PC0 VDD GND

Port A (Bit) Port B (Bit) Port C (Bit) +5 volts 0 volts

• 24 Programmable I/O Pins

• Bus-Hold Circuitry on All I/O Ports Eliminates Pull-Up Resistors

• Direct Bit Set/Reset Capability

• Enhanced Control Word Read Capability

Description

The Intersil HS-82C55ARH is a high performance, radiation hardened CMOS version of the industry standard 8255A and is manufactured using a hardened field, self-aligned silicongate CMOS process. It is a general purpose programmable I/O device which may be used with many different microprocessors. There are 24 I/O pins which are organized into two 8-bit and two 4-bit ports. Each port may be programmed to function as either an input or an output. Additionally, one of the 8-bit ports may be programmed for bi-directional operation,and the two 4-bit ports can be programmed to provide handshaking capabilities. The high performance, radiation hardness, and industry standard configuration of the HS-82C55ARH make it compatible with the HS-80C86RH radiation hardened microprocessor.

AD815大电流差动驱动器的特点与应用

AD815大电流差动驱动器的特点与应用

吴星明

【期刊名称】《国外电子元器件》

【年(卷),期】1997(000)010

【摘要】介绍了AD815大电流差动驱动器的特点和主要技术指标并且讨论了四种典型应用电路。

【总页数】3页(P10-12)

【作者】吴星明

【作者单位】四川英世模拟器件有限公司

【正文语种】中文

【中图分类】TN722.77

【相关文献】

1.大电流4通道LED驱动器LT3476及其应用 [J], 钱怀风

2.AD815大电流差动驱动器的特点与应用 [J], 吴星明

3.面向升压、降压或降压-升压型大电流LED应用的45V、2.3A LED驱动器可提供150℃最高结温并采用QFN封装 [J],

4.汽车最新的大电流LED应用需要坚固和低噪声LED驱动器 [J], Jeff Gruetter

5.大功率应用的集成化8位MCU——这种MCU具有大电流驱动器和高压驱动器,可用于汽车系统等多种领域 [J], 范东华

因版权原因,仅展示原文概要,查看原文内容请购买。

L15S8中文资料

‡ KLC series fuses are recommended for replacement use only.

KLC 1 KLC 2 KLC 3 KLC 4 KLC 5 KLC 6 KLC 7 KLC 8 KLC 10 KLC 12 KLC 15 KLC 171⁄2 KLC 20 KLC 25 KLC 30 KLC 35 KLC 40 KLC 45 KLC 50 KLC 60 KLC 70 KLC 80 KLC 90 KLC 100 KLC 110 KLC 125 KLC 150 KLC 175 KLC 200 KLC 225 KLC 250 KLC 300 KLC 350 KLC 400 KLC 450 KLC 500 KLC 600 KLC 700 KLC 800 L70S 10 L70S 15 L70S 20 L70S 25 L70S 30 L70S 35 L70S 40 L70S 50 L70S 60 L70S 70 L70S 80 L70S 90 L70S 100 L70S 125 L70S 150 L70S 175 L70S 200 L70S 225 L70S 250 L70S 300 L70S 350 L70S 400 L70S 450 L70S 500 L70S 600 L70S 700 L70S 800

s

s

APPLICATIONS

Designed specifically for supplementary protection of semiconducting devices such as silicon controlled rectifiers (SCR’s), diodes, thyristors, triacs, transistors, and similar solid-state devices. These devices are used in power equipment including variable speed drives, power rectifiers, UPS systems, DC power supplies, and in a wide range of electronic equipment. May be used wherever extremely fast-acting, current-limiting fuses with no time delay are required.

HAL815中文数据手册

HAL 815目录页码章节3 1.简介3 1.1.主要应用3 1.2.特点4 1.3.标号代码4 1.4.工作结温范围(T J)4 1.5.霍尔传感器产品代码4 1.6.可焊性4 1.7.引脚连接及简略描述5 2.功能描述5 2.1.一般功能7 2.2.数字信号处理和EEPROM 9 2.3.校准程序9 2.3.1.一般程序10 2.3.2.角辨向器的校准11 3.规范11 3.1.外形尺寸11 3.2.敏感区域尺寸11 3.3.敏感区域位置12 3.4.最大绝对额定值12 3.5.推荐运行条件13 3.6.电特性14 3.7.磁特性14 3.8.断路识别14 3.9.过压和欠压识别15 3.10.典型特征17 4.应用笔记17 4.1.应用电路17 4.2.并行使用2只HAL81517 4.3.温度补偿18 4.4.欠压18 4.5.外围温度18 4.6.EMC和ESD19 5.传感器的编程19 5.1.编程脉冲的定义19 5.2.报文的定义21 5.3.报文22 5.4.数字格式23 5.5.寄存器信息23 5.6.编程信息2数据手册可编程线性霍尔传感器1.简介HAL815是Micronas 公司可编程线性霍尔传感器系列中的新成员。

作为HAL800系列传感器的新成员,它具有开路,过压欠压检测,且可以对并行连接在同一供电电压上的不同传感器分别编程。

HAL815是一个基于霍尔效应的单线性输出通用磁场传感器。

该传感器的设计和生产采用亚微米CMOS技术,它常结合旋转或移动磁体来测量角度或距离。

主要特征如磁场范围,灵敏度,静态输出电压(在B=0mT时的输出电压),且可以通过编程一个非易失性存储器来改变输出电压范围。

该传感器具有比率输出特性,即输出电压与磁通量和供电电压成正比。

HAL815具有带一个开关偏置补偿的温度补偿霍尔极板,一个A/D转化器,数字信号处理单元,一个带输出驱动的D/A转换器,一个带冗余和标准数据锁存的EEPROM存储器,一个用于对EPROM读写的串行,所有引脚都具有保护功能等特点。

单片机AT89S51与ADC0809设计一个数字电压表

1.实验任务利用单片机AT89S51与ADC0809设计一个数字电压表,能够测量0-5V 之间的直流电压值,四位数码显示,但要求使用的元器件数目最少。

2.电路原理图图1.28.13.系统板上硬件连线a) 把“单片机系统”区域中的P1.0-P1.7与“动态数码显示”区域中的ABCDEFGH端口用8芯排线连接。

b) 把“单片机系统”区域中的P2.0-P2.7与“动态数码显示”区域中的S1S2S3S4S5S6S7S8端口用8芯排线连接。

c) 把“单片机系统”区域中的P3.0与“模数转换模块”区域中的ST端子用导线相连接。

d) 把“单片机系统”区域中的P3.1与“模数转换模块”区域中的OE端子用导线相连接。

e) 把“单片机系统”区域中的P3.2与“模数转换模块”区域中的EOC端子用导线相连接。

f) 把“单片机系统”区域中的P3.3与“模数转换模块”区域中的CLK端子用导线相连接。

g) 把“模数转换模块”区域中的A2A1A0端子用导线连接到“电源模块”区域中的GND端子上。

h) 把“模数转换模块”区域中的IN0端子用导线连接到“三路可调电压模块”区域中的VR1端子上。

i) 把“单片机系统”区域中的P0.0-P0.7用8芯排线连接到“模数转换模块”区域中的D0D1D2D3D4D5D6D7端子上。

4.程序设计内容i. 由于ADC0809在进行A/D转换时需要有CLK信号,而此时的ADC0809的CLK是接在AT89S51单片机的P3.3端口上,也就是要求从P3.3输出CLK信号供ADC0809使用。

因此产生CLK信号的方法就得用软件来产生了。

ii. 由于ADC0809的参考电压VREF=VCC,所以转换之后的数据要经过数据处理,在数码管上显示出电压值。

实际显示的电压值(D/256*VREF) 5.汇编源程序(略)6.C语言源程序#include <AT89X52.H>unsigned char code dispbitcode[]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f};unsigned char code dispcode[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x00};unsigned char dispbuf[8]={10,10,10,10,0,0,0,0};unsigned char dispcount;unsigned char getdata;unsigned int temp;unsigned char i;sbit ST=P3^0;sbit OE=P3^1;sbit EOC=P3^2;sbit CLK=P3^3;void main(void){ST=0;OE=0;ET0=1;ET1=1;EA=1;TMOD=0x12;TH0=216;TL0=216;TH1=(65536-4000)/256; TL1=(65536-4000)%256; TR1=1;TR0=1;ST=1;ST=0;while(1){if(EOC==1){OE=1;getdata=P0;OE=0;temp=getdata*235; temp=temp/128;i=5;dispbuf[0]=10;dispbuf[1]=10;dispbuf[2]=10;dispbuf[3]=10;dispbuf[4]=10;dispbuf[5]=0;dispbuf[6]=0;dispbuf[7]=0;while(temp/10){dispbuf[i]=temp%10; temp=temp/10;i++;}dispbuf[i]=temp;ST=1;ST=0;}}}void t0(void) interrupt 1 using 0{CLK=~CLK;}void t1(void) interrupt 3 using 0{TH1=(65536-4000)/256;TL1=(65536-4000)%256;P1=dispcode[dispbuf[dispcount]];P2=dispbitcode[dispcount];if(dispcount==7){P1=P1 | 0x80;}dispcount++;if(dispcount==8){dispcount=0;}}利用单片机AT89S51与ADC0809设计一个数字电压表2008-05-22 14:521.实验任务利用单片机AT89S51与ADC0809设计一个数字电压表,能够测量0-5V之间的直流电压值,四位数码显示,但要求使用的元器件数目最少。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R1 = 15⍀

VIN = 4Vp-p

110⍀

G = +10 499⍀

VD = 40Vp-p

RL 120⍀

VOUT = 40Vp-p

100⍀

AMP2 1/2 AD815

–15V

R2 = 15⍀ 1:2 TRANSFORMER

Figure 2. Subscriber Line Differential Driver

TOP VIEW 19 7 (Not to Scale) 18 8 17

+IN1 9 –IN1 10 OUT1 11 –VS 12

16 +IN2 15 –IN2 14 OUT2 13 +VS

NC = NO CONNECT *HEAT TABS ARE CONNECTED TO THE POSITIVE SUPPLY.

元器件交易网

AD815–SPECIFICATIONS (@ T = +25؇C, V = ؎15 V dc, R

A S

FB

= 1 k⍀ and RLOAD = 100 ⍀ unless otherwise noted)

VS ± 15 ±5 ± 15 ±5 ± 15 ± 15 ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ± 15 ± 15 ±5 ± 15 Min 100 90 AD815A Typ Max 120 110 40 10 900 70 –66 1.85 1.8 19 0.05 0.45 5 10 20 0.5 0.5 10 10 2 10 1.0 0.5 5.0 8 15 30 2 4 5 90 150 5 5 75 100 Units MHz MHz MHz MHz V/µs ns dBc nV/√Hz pA/√Hz pA/√Hz % Degrees mV mV mV µV/°C mV mV mV µV/°C µA µA µA µA µA µA MΩ MΩ MΩ Ω pF ±V ±V dB dB ±V ±V ±V ±V mA A Ω dB ± 18 30 40 40 55 V mA mA mA mA dB

–40 TOTAL HARMONIC DISTORTION – dBc –50 –60 –70 –80 –90 –100 RL = 50⍀ (DIFFERENTIAL) RL = 200⍀ (DIFFERENTIAL) VS = ؎15V G = +10 VOUT = 40V p-p

100⍀

1/2 AD815 AMP1

Model DYNAMIC PERFORMANCE Small Signal Bandwidth (–3 dB) Bandwidth (0.1 dB) Differential Slew Rate Settling Time to 0.1% NOISE/HARMONIC PERFORMANCE Total Harmonic Distortion Input Voltage Noise Input Current Noise (+I IN) Input Current Noise (–I IN) Differential Gain Error Differential Phase Error DC PERFORMANCE Input Offset Voltage

பைடு நூலகம்

combined with the wide bandwidth and high current drive make the differential driver ideal for communication applications such as subscriber line interfaces for ADSL, HDSL and VDSL. The AD815 differential slew rate of 900 V/µs and high load drive are suitable for fast dynamic control of coils or transformers, and the video performance of 0.05% and 0.45° differential gain and phase into a load of 25 Ω enable up to 12 back-terminated loads to be driven. The 24-lead SOIC (RB) is capable of driving 26 dBm for full rate ADSL with proper heat sinking.

800

TMIN – TMAX Input Offset Voltage Drift Differential Offset Voltage TMIN – TMAX Differential Offset Voltage Drift –Input Bias Current TMIN – TMAX +Input Bias Current TMIN – TMAX Differential Input Bias Current TMIN – TMAX Open-Loop Transresistance TMIN – TMAX INPUT CHARACTERISTICS Differential Input Resistance Differential Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio Differential Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS Voltage Swing TMIN – TMAX TMIN – TMAX Single Ended, R LOAD = 25 Ω Differential, R LOAD = 50 Ω TMIN – TMAX RLOAD = 10 Ω +Input –Input ± 15 ± 15 ± 15 ±5 ± 5, ± 15 ± 5, ± 15 ± 15 ±5 ± 15 ± 15 ± 15 ± 15 ± 15 ± 15 ±5 ± 15 ±5 ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ± 5, ± 15 ±5 ± 15

57 80 11.0 1.1 21 22.5 400

7 15 1.4 13.5 3.5 65 100 11.7 1.8 23 24.5 500 1.0 13 –65

Output Current1 RB-24 Short Circuit Current Output Resistance MATCHING CHARACTERISTICS Crosstalk POWER SUPPLY Operating Range2 Quiescent Current

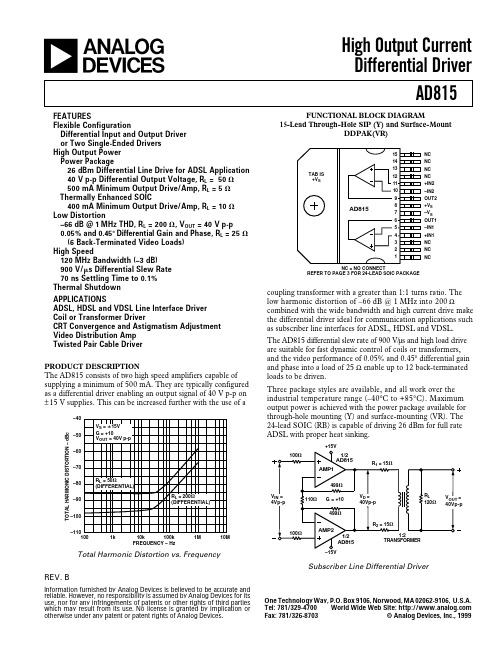

High Output Current Differential Driver AD815

FUNCTIONAL BLOCK DIAGRAM

NC 1 NC 2 NC 3 NC 4 5 THERMAL HEAT TABS +VS* 6 24 NC 23 NC 22 NC 21 NC

AD815

20 THERMAL HEAT TABS +VS*

+15V

The AD815 consists of two high speed amplifiers capable of supplying a minimum of 500 mA. They are typically configured as a differential driver enabling an output signal of 40 V p-p on ± 15 V supplies. This can be increased further with the use of a coupling transformer with a greater than 1:1 turns ratio. The low harmonic distortion of –66 dB @ 1 MHz into 200 Ω

–110 100 1k 10k 100k FREQUENCY – Hz 1M 10M

Figure 1. Total Harmonic Distortion vs. Frequency

REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 Fax: 781/461-3113 © 2005 Analog Devices, Inc. All rights reserved.

元器件交易网

a

FEATURES Flexible Configuration Differential Input and Output Driver or Two Single-Ended Drivers Industrial Temperature Range High Output Power Thermally Enhanced SOIC 400 mA Minimum Output Drive/Amp, RL = 10 ⍀ Low Distortion –66 dB @ 1 MHz THD, RL = 200 ⍀, V OUT = 40 V p-p 0.05% and 0.45؇ Differential Gain and Phase, R L = 25 ⍀ (6 Back-Terminated Video Loads) High Speed 120 MHz Bandwidth (–3 dB) 900 V/s Differential Slew Rate 70 ns Settling Time to 0.1% Thermal Shutdown APPLICATIONS ADSL, HDSL, and VDSL Line Interface Driver Coil or Transformer Driver CRT Convergence and Astigmatism Adjustment Video Distribution Amp Twisted Pair Cable Driver GENERAL DESCRIPTION