Altium Designer Summer 09 AD9 PCB LAYOUT布线设计规则说明

AltiumDesignerSummer09使用教程讲解

操作教程

把Altium Designer Summer 09转化成中文

刚装好的DXP是英文的,我们需要把它转化成中 文

1.选择DXP选项卡中的Preferences选项

在DXP System-General中选择Use Localzed resources

点击Place按钮可以放置元 件

安装元件库

点击元件库,在这里可以安装一些常用的元件库或 封装库,安装Library\Pcb\Dual-In-Line Package.PcbLib

查找元件

如果在常用元件库中找不到想要元件,可以点击查找按钮, 然后在文本框中输入元件名字,范围选择路径中的库,路 径选择你的安装目录,如下图。

其它很有用的按钮还有地、电源、放置元件、放 置端口、忽略检查等等,鼠标悬停在上面可以得 到按钮的信息

所有悬空的引脚最好接上”忽略ERC检查“标志

编译原理图文件

编译一个原理图文件就是 在设计文档中检查原理图 和电气规则错误

点击项目管理-Compile Document(编译文档) 可以进行编译

如果系统找到了这个 封装,会在下面的预 览中见到它

把单片机设置为DIP40,把MAX118设置 为DIP-28/D38.7

修改封装

复位电路

复位电路就用我们之 前画的按键复位电路

找到开关SW-PB和相 应的电容电阻添加

晶振部分

晶振部分由一个无源 晶振和两个电容组成

选中晶振(XTAL), 摆放好电容和地,把 两端连到单片机的18、 19号口上

放置单片机

查找并放置AT89C55WD(或P89C54X2BN)和 MAX118EPI。

修改封装

PCB设计教程Altium_Designer_Summer_09

2009-11-1 20:32

图6-2新建电路原理图

添加电路原理图到工程当中

如果添加到工程中的电路原理图以空文档的形式被打开,可以通过在工程文件名上点击右键并且在工程面板中选择Add Existing to Project 选项,选择空文档并点击 Open。更简单的方法是,还可以在Projects面板中简单地用鼠标拖拽拉空白文档到工程文档列表中的面板中。该电路原理图在Source Documents工程目录下,并且 已经连接到该工程。

画电路原理图

接下来可以开始画电路原理图。本章将使用如图6-3所示的电路图为例进行讲解。这个电路是由两个2N3904三极管组成的非稳态多谐振荡器。

图6-3 非稳态多谐振荡器

加载元件和库

Altium Designer为了管理数量巨大的电路标识,电路原理图编辑器提供了强大的库搜索功能。虽然元件都在默认的安装库中,但是还是很有必要知道如何通过从库中 去搜索元件。按照下面的步骤来加载和添加图6-3电路所需的库。 首先我们来查找型号为2N3904的三极管。 1.点击Libraries标签显示Library面板,如图6-4。 2.在Library面板中点击Search in按钮,或者通过选择Tools>>Find Component,来打开Libraries Search对话框,如图6-5所示。 3.对于这个例子必须确定在Options设置中,Search in 设置为Components。对于库搜索存在不同的情况,使用不同的选项。 4.必须确保Scope设置为Libraries on Path 并且Path包含了正确的连接到库的路径。如果在安装软件的时候使用了默认的路径,路径将会是Library。可以通过点击文 件浏览按钮来改变库文件夹的路径。对于这个例子还需得确保Include Subdirectories复选项框已经勾选。 5.为了搜索所有3904的所有索引,在库搜索对话框的搜索栏输入*3904*。使用*标记来代替不同的生厂商所使 用的不同前缀和后缀。 6.点击Search 按钮开始搜索。搜索启动后,搜索结果将在库面板中显示。

Altium Designer Summer 09使用教程

把DXP转化成中文

重新启动DXP,就变成中文版的了

创建一个新项目

在文件-创建菜单中选择项目-PCB项目

再在同样的地方选择创建新原理图文件,我们就 可以开始编辑原理图了 下图展示了当几个文件和编辑器同时打开并且窗 口进行平铺时的界面。

开始一个原理图设计

在你开始绘制电路图之前首先要做的是设置正确的文档选 项。完成以下步骤: 从菜单选择设计-文档选项,文档选项对话框打开。在此 我们需要修改的是将图纸大小设置为标准A4格式。

按Shift+F查找相似对象 在提示框内Comment 项选择Same后再单击 “应确定会出提示框, 在Hide项单击取消打“√”,原理 图界面就同步显示参数。 单击右上角“×”关闭提 示框,修改成功。

添加PCB文件

在开始PCB设计之前, 需要把PCB文件添加 到项目中来。 点击Project面板,在 已有的项目上点击右 键,就可以追加新文 件或者已有文件到项 目中来了

编辑原理图元件库

许多时候,在现有的库中找不到我们所需要的元 件,这时候,就需要自己新建一个元件 点击文件-创建-库-原理图库

放置单片机

查找并放置AT89C55WD(或P89C54X2BN)和 MAX118EPI。

修改封装

有的时候,选用的元件封装并不是我们想要的, 这时候,可以双击元件修改元件属性 看到元件属性对话框的右下角,查看是否有类型 为Footprint的项,如果有,则编辑,否则追加一 项。

模数转换器部分

在Miscellaneous Connectors.IntLib(常 用连接器件中找到 MHDR1X2(2口连接 器)作为信号的输入 部分 将数据线连入总线 将A0、A1、A2和单片 机的P2.0、 P2.1、 P2.2相连作为选通地 址

Altium Designer Summer 09使用教程资料

模数转换器部分

? 把WR连到单片机的 WR,CS连到P2.7, RD连到单片机的 RD, INT连到 INT0 (P3.2 ), 右图中是利用网络标 签来完成这种连接的

? 别忘了电源部分,将 芯片的电源和地连上机的 电源和地都接上

? 将单片机的引脚写上 相应的网络标签

? 将每个引脚对应的总线引脚标出(D0-D7)

模数转换器部分

? 在Miscellaneous Connectors.IntLib (常 用连接器件中找到 MHDR1X2 (2口连接 器)作为信号的输入 部分

? 将数据线连入总线 ? 将A0、A1、A2和单片

机的P2.0、 P2.1、 P2.2相连作为选通地 址

把DXP转化成中文

? 重新启动DXP,就变成中文版的了

创建一个新项目

? 在文件-创建菜单中选择项目 -PCB项目

? 再在同样的地方选择创建新原理图文件,我们就 可以开始编辑原理图了

? 下图展示了当几个文件和编辑器同时打开并且窗 口进行平铺时的界面。

开始一个原理图设计

? 在你开始绘制电路图之前首先要做的是设置正确的文档选 项。完成以下步骤:

复位-更新变化表

更新变化

? 点击“使变化生效”按钮,可以看到“检查”一 栏都打上了勾

更新变化

? 这时点击“执行变化”按钮,可以看到“完成” 一栏都打上了勾,这时候,标识符已经自动添加 完毕

编译原理图文件

? 仔细检查原理图文件, 如果无误的话就可以 编译了,如果编译信 息里面没有 Error(错 误),那么原理图就 画好了

添加电源线约束

? 右键点击Routing/Width,新建规则并命名。 ? 选择网络,选取对象+5V ? 将Minimum、Preferred 和 Maximum宽度栏改为25mil

Altium Designer Summer 09使用教程资料[文字可编辑]

![Altium Designer Summer 09使用教程资料[文字可编辑]](https://img.taocdn.com/s3/m/7c8cabd7ad02de80d5d84048.png)

? 放置元件之后,双击元件会出现元件属性对话框,如下图。 ? 我们一般需要注意的是写标识符,选择是否镜像,输入元件参数和选

择PCB封装

11

放置导线

? 按空格键可以旋转元件 ? 放置元件之后,接下来就是把它们

连接起来。 ? 注意右上的工具条(如右中图),

第一个按钮是放置导线,点击它, 光标将变为十字形状。 ? 将光标放在R1的上端。当你放对位 置时,一个红色的连接标记(大的 星形标记)会出现在光标处。这表 示光标在元件的一个电气连接点上。 ? 左击固定第一个导线点。移动光标 你会看见一根导线从光标处延伸到 固定点。 ? 将光标移到R1的右边C3的左端, 左击在该点固定导线。在第一个和 第二个固定点之间的导线就放好了。

Altium Designer Summer 09

操作教程

1

把Altium Designer Summer 09 转化成中文 ? 刚装好的DXP是英文的,我们需要把它转化成中

文 ? 1.选择DXP选项卡中的 Preferences 选项

2

? 在DXP System-General中选择Use Localzed resources

28

复位-更新变化表

18

修改封装

? 在库名中选中 DualIn-Line Package.PcbLib (请 先安装此库),在名 称中输入 DIP-40

? 如果系统找到了这个 封装,会在下面的预 览中见到它

? 把单片机设置为 DIP40,把MAX118 设置 为DIP-28/D38.7

19

修改封装

20

复位电路

? 复位电路就用我们之 前画的按键复位电路

? 把EA接高电平 ? 最后,把所有不用的

Altium_Designer_Summer_09批量修改元件参数

总结归纳的一些修改技巧,分享如何在Altium Designer 中运用查找编辑集体整批修改功能Altium Designer 提供了非常强大搜索修改功能,有List 和Inspector 等对话框,可以在原理图或PCB 文件中对器件进行集体修改。

在原理图文件中,左键选中器件,右键点击,在拖出的菜单里左键选中Find Similar Objects, 则出现选中界面,在这个界面里,所有的选项都可以设置为约束条件来进行查找,比如,在Description行,在ANY 栏里点一下,在Any 旁的箭头的选项中选为SAME,点击OK,就可以找出所有同一个描述的器件;Current Footprint 行箭头的选项中选为SAME,点击OK 这样就可以找出所有同一个封装的器件;Part Comment 行箭头的选项中选为SAME,点击OK 这样就可以找出所有同一个注释的器件,等等,如此设置可以进行各种各样的搜索。

点击OK 以后,就会跳出搜索结果界面。

如下图所示,如图所示,这是以Part Comment 为条件找到的三个符合条件对象,这时,如果我想一起修改着三个器件的属性,比如说封装,只要将DIP14 改为SOP14,然后在Inspector 界面其他地方左键点击,则修改就有效了。

如果要一个个修改的话,可以左键点击View\Workspace Panel\SCH\List,则进入列表界面,如下图所示,在列表界面里就可以一个个对所选的器件进行修改。

在PCB 文件中,左键选中器件,右键点击,在拖出的菜单里左键选中Find Similar Objects,则出现选中界面,在这个界面里,所有的选项都可以设置为约束条件来进行查找,比如,在CurrentFootprint 行,在Any 栏里点一下,在Any 旁的箭头的选项中选为SAME,点击OK,就可以找出所有同一个封装的器件;Part Comment 行在Any 栏里点一下,在Any 旁的箭头的选项中选为SAME,点击OK 这样就可以找出所有同一个注释的器件,等等,如此设置可以进行各种各样的搜索。

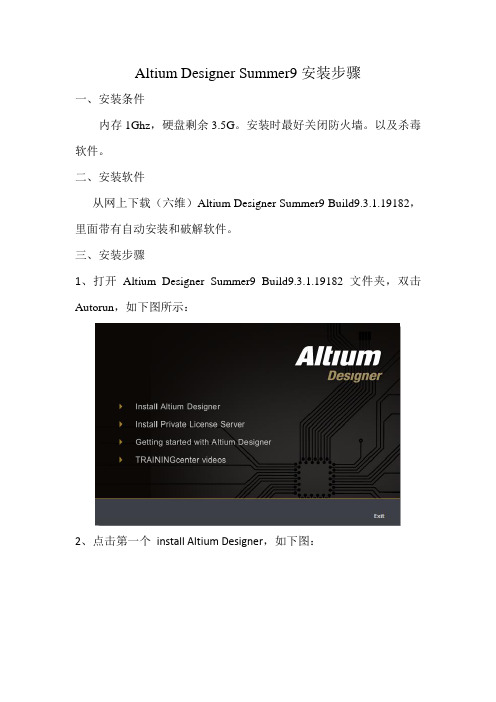

Altium Designer Summer9安装步骤

Altium Designer Summer9安装步骤一、安装条件内存1Ghz,硬盘剩余3.5G。

安装时最好关闭防火墙。

以及杀毒软件。

二、安装软件从网上下载(六维)Altium Designer Summer9 Build9.3.1.19182,里面带有自动安装和破解软件。

三、安装步骤1、打开Altium Designer Summer9 Build9.3.1.19182文件夹,双击Autorun,如下图所示:2、点击第一个install Altium Designer,如下图:点击next,选择I accept the license agreement,点击Next,点击Next,如果安装在C盘,直接点击Next即可,如果安装在D盘,点击Browse,如下,将C改成D即可,点击ok,Next,如下,点击Next,如下,点击Next,等待完成,安装完成四、破解步骤1、打开Altium Designer Summer9 Build9.3.1.19182文件夹中的AD9-Crack文件夹,运行AD9KeyGen,如下图,2、点击“打开模板”,加载ad9.ini(在AD9-Crack文件夹中),如想修改注册名,只需修改:TransactorName=horosehorose用你自己的名字替换,其它参数在单机版的情况下无需修改3、点击“生成协议”,保存生成的alf文件到你的安装目录下,如下,在这里保存名字为abc.alf.如下,点击保存,如下,4、运行AD9-Crack文件夹中的ads09crack,对安装目录下的dxp.exe文件补丁,注意运行破解时软件没有运行点击Patch,如下点击Y,在安装目录下找到dxp.exe,如下点击打开,如下点击Exit 退出。

5、启动DXP,运行菜单DXP->My Account,如下,点击Add Standalone License file,在安装目录下选择.alf文件,如下打开即可,破解成功。

altiumdesignersummer09出现的问题解决方案【最新精选】

altium designer Summer09出现的问题解决方案在编译原理图时,引脚和连线旁边出现很多红线,提示error:signal with no driver。

原理图没有加入到Project里。

第一次导入没问题,但是改了个元件的封装,在更新一下(Design—Update SCH),点击导入时出现Unkown Pin。

解决方案一:把第一张PCB删掉,新建一个PCB再倒入。

解决方案二:把改过的元件在PCB中删除,再倒入。

以上问题本应该是没问题的,但是可能是我们使用的盗版软件的原因。

用altium designer画完图编译后,出现几百警告,几乎的所有的都是Off grid pin画的图在项目中去编译,独立的不能编译,如果文件不在项目中的话,就会出现你说的不在网络的提示。

你的元件没有在原理图上真正形成电气上的连接。

你的元件库没有被软件别。

没有你建一个项目文件,把你的原理图放在里去做编译,这样就不会出错了。

是因为你原理图中的元件引脚尺寸和你设置的栅格尺寸不对应,导致系统无法识别而报错,引脚长度尺寸必需设置成栅格尺寸的整数倍!!!你把你做的原理图元件重新再画一遍,再编译,问题解决双面板应该都有哪些Layer?Top Layer 顶层铜皮,双面板必须要Bottom Layer 底层铜皮,双面板必须要Top OverLayer 顶层丝印,一般需要,也有节约成本不做的。

Bottom OverLayer 底层丝印,一般不需要,底层放原件的话,也可以加。

Top/Bottom Soldermask 顶层底层阻焊层,就是“绿油”,一般需要,也有节约成本不做的。

Mechinical 1/4 机械层1/4,板边以及板内开槽,1无金属化,4有金属化。

Keepout 禁止布线区域,不自动布线的话可以不要。

然而中国的现实是用Keepout做板框成了行规,你要正规地给他们机械层往往还不会做了。

Top/Bottom Pastemask 顶层底层钢板层,如果要批量焊接SMD器件的板子,需要定做钢板,这两层不在PCB上,是生产需要的工装.Multilayer 多层,在所有层上都存在的东西,比如直插器件的焊盘,这层一般是必须的,不要试图关闭它。

AltiumDesignerSummer09网络版使用方法

Altium Designer Summer 09网络版使用方法

打开软件点击DXP—my account弹出图1对话框

图1

之后点击界面中的”设置私人license服务器”选项,弹出图2对话框

图2

一般默认使用主服务器,在服务器列表下拉选择安装license的服务器名和IP 地址,若未搜索到,可手动输入IP地址尝试激活,如下所示:

在服务器地址中填入服务器的IP地址.选择用户地址之后点击确定搜寻服务器.之后会搜到可用的license,之后点击use使用license.如图3所示.

当授权的使用量达到上限,还有人需要授权的时候,就需要某个只需要查看当前图纸,不需要修改的人.把自己的license在图3中点击release即可释放出一个可用的license.供后

一个人使用了.。

Altium Designer Summer 09(AD9)快捷键

1. PCB设计快捷键(单次按键)星号—在交互布线的过程中,按此键则换层并自动添加过孔。

这很常用。

空格键在交互布线的过程中,切换布线方向。

这很常用。

1-04 Backspace键在交互布线(手动布线)的过程中,放弃上一步操作。

很常用。

1-05 主键盘上的1 在交互布线的过程中,切换布线方法(设定每次单击鼠标布1段线还是2段线)。

1-06 主键盘上的2 在交互布线的过程中,添加一个过孔,但不换层。

1-07 Q 在公制和英制之间切换。

1-08 Delete 删除已被选择的对象。

2. PCB设计快捷键(组合按键)组合按键是指,先按住第一个键不放,然后按下第二个键,再放开这两个键。

组合键用+号表示。

例如Shift+S表示,先按住Shift键不放,然后按下S键,再放开这两个键。

2-01 Shift+S 切换单层显示和多层显示。

2-02 Shift+空格键在交互布线的过程中,切换布线形状。

2-03 Shift+C 清除当前过滤器。

(当显示一片灰暗时,可恢复正常显示)2-04 Ctrl+鼠标左键高亮显示同网络名的对象(鼠标左键必须点到有网络名的对象)2-05 Ctrl+R 一次复制,并可连续多次粘贴。

2-06 Ctrl+C 复制2-07 Ctrl+V 粘贴2-08 Ctrl+S 保存文档。

3. PCB设计快捷键(多次按键)多次按键是指,先按下第一个键并放开,然后按下第二个键并放开,以此类推。

多次按键用逗号“,”表示。

多次按键有很多,但是完全可以自己找到。

在PCB设计状态下,随便按下A~Z中的一个字母(第一次按键),便弹出一个与该字母相关的快捷菜单,菜单提示中的带下划线的字母便是第二次按键。

3-01 J,L 定位到指定的坐标的位置。

这时要注意确认左下角的坐标值,如果定位不准,可以放大视图并重新定位,如果还是不准,则需要修改栅格吸附尺寸。

(定位坐标应该为吸附尺寸的整数倍)3-02 J,C 定位到指定的元件处。

在弹出的对话框内输入该元件的编号。

AltiumDesignerSummer09AD9PCBLAYOUT布线设计规则说明.pdf

一. 网络类(Net Classes)的组建:方法一:原理图中执行Place——Directives——Net Class按Tab键,设置好相关名称属性回车,每个归属此类网络均要放置。

方法二:PCB中执行Design——Classes…命令,按下图右键执行Net Classes——Add Class命令会生产New Class,右键更名成所需要的网络类名称,单击添加归属于此网络类的网络成员。

二. 差分网络类(Differential Pair Classes)的组建:方法一:原理图中执行Place——Directives——Differential Pair按Tab键,设置好相关名称属性回车,每个归属此类网络均要放置。

方法二:步骤1:PCB中执行Design——Classes…命令,按下图右键执行Differential Pair Classes——Add Class命令会生产New Class,右键更名成所需要的差分网络类名称,单击添加归属于此网络类的网络成员(前提是需要事先建立差分对网络)。

步骤2:建立差分对网络,PCB中执行View——Workspace Panels——PCB——PCB命令打开PCB面板,面板切换至Differential Pairs Editor,点击选择相应的差分网络类后再点击按钮Add,输入自定义的网络差分对名称,同时设置定义好对应的差分网络(Positive Net和Negative Net)。

也可以通过双击Differential Pairs Editor面板中的差分网络类或执行Design——Classes…命令,把所建立的差分网络对归属到对应的差分网络类。

三. ROOM相关:1. ROOM的组建:主要目的是用于设置个别器件内部的铺铜或布线间距。

PCB中执行Design ——Rooms——Place Rectangular Room命令,按Tab键,设置好相关名称属性,在PCB中相应的器件封装上面画好Room区域。

Altium Designer Summer 09安装说明

注意:仅适用于Build 9.3.1.19182

大小: 187.3 KB

大小: 27.4 KB

大小: 14.7 KB

大小: 20.3 KB

大小: 12.1 KB

大小: 25 KB

大小: 51.7 KB

大小: 34.9 KB

大小: 187.3 KB

大小: 11.8 KB

查看图片附件

horose用你自己的名字替换,其它参数在单机版的情况下无需修改;

2 点击“生成协议”,保存生成的alf文件到你的安装目录下;

3 运行ads09crack,到自己安装目录下的dxp.exe文件补丁,注意运行破解时软件没有运

行;

4. 启动DXP,运行菜单DXP->My Account,点击Add Standalone License file,加载

3运行ads09crack到自己安装目录下的dxpexe文件补丁注意运行破解时软件没有运行

1 打开 AltiumDesignerSummeபைடு நூலகம்9Build9.3.1.19182Crack,运行AD9KeyGen,点击“打开模板”,加载ad9.ini,

如想修改注册名,只需修改:

TransactorName=horose

[整理]Altium Designer Summer 09在PCB文件中显示布线网络的颜色

![[整理]Altium Designer Summer 09在PCB文件中显示布线网络的颜色](https://img.taocdn.com/s3/m/bc57458065ce050876321360.png)

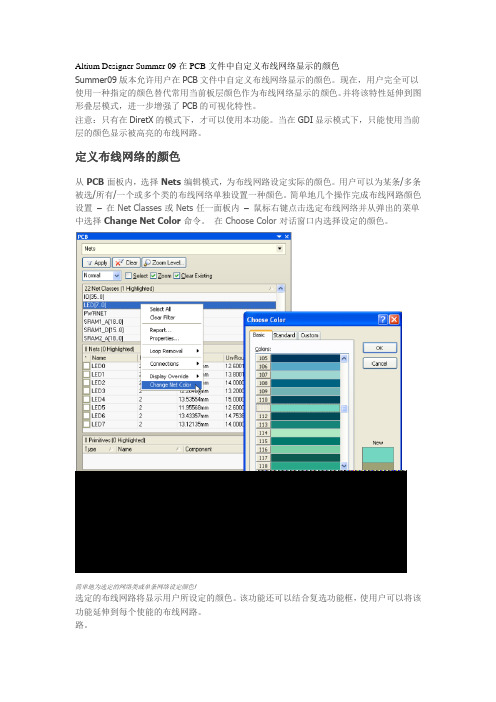

Altium Designer Summer 09在PCB文件中自定义布线网络显示的颜色Summer09版本允许用户在PCB文件中自定义布线网络显示的颜色。

现在,用户完全可以使用一种指定的颜色替代常用当前板层颜色作为布线网络显示的颜色。

并将该特性延伸到图形叠层模式,进一步增强了PCB的可视化特性。

注意:只有在DiretX的模式下,才可以使用本功能。

当在GDI显示模式下,只能使用当前层的颜色显示被高亮的布线网路。

定义布线网络的颜色从PCB面板内,选择Nets编辑模式,为布线网路设定实际的颜色。

用户可以为某条/多条被选/所有/一个或多个类的布线网络单独设置一种颜色。

简单地几个操作完成布线网路颜色设置–在Net Classes或Nets任一面板内–鼠标右键点击选定布线网络并从弹出的菜单中选择Change Net Color命令。

在Choose Color对话窗口内选择设定的颜色。

简单地为选定的网络类或单条网络设定颜色!选定的布线网路将显示用户所设定的颜色。

该功能还可以结合复选功能框,使用户可以将该功能延伸到每个使能的布线网路。

路。

选择布线网络的叠层颜色。

图形叠层模式关于为用户指定的布线网络设定叠层颜色功能,现在用户可以选择新的网络颜色高亮模式。

网络高亮将通过Base Pattern对话窗口管理,共有6种图形模式可供用户选择。

(DXP?Preferences).指定高亮布线网络的基础图形。

表1 通过示例介绍每种图形模式的使用情况。

设定的叠层颜色为!ExOverrideNetColor.png!.表1. 可用的基础图形列表.示例图形描述None (Layer Color) 忽略布线网络颜色设定,只显示布线层的默认颜色.Solid (Override Color)使用布线网络用户设定的颜色, 完全覆盖原来的布线网络。

Star在布线网络上使用小的星形图形, 原布线网络的颜色仍然可见。

Checker Board在布线网络上使用小的方形图形, 原布线网络的颜色仍然可见。

《印制电路板的设计与制造》-习题答案

习题答案项目一思考与练习1.Altium Designer Summer 09主要由哪几部分操作系统组成?答:Altium Designer Summer 09主要由以下4大部分组成,①原理图设计系统(SCH)②印刷电路板设计系统(PCB)③FPGA系统④VHDL系统,其中前两个系统最常用。

2.在Altium Designer Summer 09软件中,不同编辑器之间是怎样切换的?答:对于未打开的文件,在“Project”面板中双击不同的文件,这样打开不同的文件即可在不同的编辑器之间切换。

对于以打开的文件,单击“Project”面板中不同的文件或单击工作窗口最上面的文件标签即可在不同的编辑器之间切换。

3.电路板设计主要包括哪两个阶段?答:电路板设计主要包括两个阶段:原理图绘制和PCB设计。

4.简述原理图的设计流程。

答:原理图绘制的基本流程如图所示。

7.简述PCB设计流程。

答:PCB的设计的基本流程如图所示。

8.简述元件布局的基本原则。

答:(1)元件放置的层面:单面板元件一律放在顶层;双面板或多层板元件绝大多数放在顶层,个别元件如有特殊需要可以放在底层。

(2)元件的布局应考虑到元件之间的连接特性,先确定特殊元件的位置,然后根据电路的功能单元,对电路的全部元器件进行布局。

(3)在确定特殊元件的位置时要遵守以下原则:①尽可能缩短高频元器件之间的连线,设法减少它们的分布参数和相互间的电磁干扰。

易受干扰的元器件不能相互挨得太近,输入和输出元件应尽量远离。

②某些元器件或导线之间可能有较高的电位差,应加大它们之间的距离,以免放电引出意外短路。

带高电压的元器件应尽量布置在调试时手不易触及的地方。

③对于电位器、可调电感线圈、可变电容器、微动开关等可调元件的布局应考虑整机的结构要求。

若是机内调节,应放在印制板上方便于调节的地方;若是机外调节,其位置要与调节旋钮在机箱面板上的位置相适应。

④应留出电路板定位孔及固定支架所占用的位置。

AltiumDesignerSummer09生成集成库——遇到的问题

AltiumDesignerSummer09生成集成库——遇到的问题在Altium Designer Summer 09安装目录之下的Library:D:\Program Files (x86)\Altium Designer Summer 09\Library 建立一个用户自己的文件夹用于放置集成库。

具体步骤:第一步新建集成库单击菜单【File】【New】【Project】【Integrated Library】即可新建一个集成库。

第二步新建原理图库单击菜单【File】【New】【Library】【Schematic Library】即可新建一个原理图库。

第三步新建PCB库单击菜单【File】【New】【Library】【Pcb ibrary】即可新建一个PCB库。

编辑结束自己的Schematic Library、Pcb ibrary之后,分别保存于上面目录之下的文件夹之下。

Integrated Library也是如此。

在这个过程中,遇到的问题是:D:\Program Files (x86)\Altium Designer Summer09\Library\SunnyLib目录下的集成库:Sunny_Integrated_Library,在Altium Designer Summer 09 库面板添加时,ERROR 无法正常添加。

解决的办法是:点击:第一个或是第二个。

在Projects面板内选中要编译的库,右键,单击在其菜单内选择Compile Document***库名***即可开始编译,错误会信息将在Messages框内自动弹出,无错误会信息时将不会弹出Messages信息框。

小注:如果是编译原理图封装库和PCB封装库,系统会自动添加在Libraries面板内,库可以直接调用了。

建议:还是直接编译集成库Integrated Library,这样在原来的目录下,sunnylib文件夹下会多出一个文件夹Project Outputs for Sunny_Integrated_Library,其中Sunny_Integrated_Library这个集成库可以手动添加在Libraries 面板内。

AltiumDesignerSummer09(AD9)快捷键要点

AltiumDesignerSummer09(AD9)快捷键要点1. PCB设计快捷键(单次按键)星号—在交互布线的过程中,按此键则换层并自动添加过孔。

这很常用。

空格键在交互布线的过程中,切换布线方向。

这很常用。

1-04 Backspace键在交互布线(手动布线)的过程中,放弃上一步操作。

很常用。

1-05 主键盘上的1 在交互布线的过程中,切换布线方法(设定每次单击鼠标布1段线还是2段线)。

1-06 主键盘上的2 在交互布线的过程中,添加一个过孔,但不换层。

1-07 Q 在公制和英制之间切换。

1-08 Delete 删除已被选择的对象。

2. PCB设计快捷键(组合按键)组合按键是指,先按住第一个键不放,然后按下第二个键,再放开这两个键。

组合键用+号表示。

例如Shift+S表示,先按住Shift键不放,然后按下S键,再放开这两个键。

2-01 Shift+S 切换单层显示和多层显示。

2-02 Shift+空格键在交互布线的过程中,切换布线形状。

2-03 Shift+C 清除当前过滤器。

(当显示一片灰暗时,可恢复正常显示)2-04 Ctrl+鼠标左键高亮显示同网络名的对象(鼠标左键必须点到有网络名的对象)2-05 Ctrl+R 一次复制,并可连续多次粘贴。

2-06 Ctrl+C 复制2-07 Ctrl+V 粘贴2-08 Ctrl+S 保存文档。

3. PCB设计快捷键(多次按键)多次按键是指,先按下第一个键并放开,然后按下第二个键并放开,以此类推。

多次按键用逗号“,”表示。

多次按键有很多,但是完全可以自己找到。

在PCB设计状态下,随便按下A~Z中的一个字母(第一次按键),便弹出一个与该字母相关的快捷菜单,菜单提示中的带下划线的字母便是第二次按键。

3-01 J,L 定位到指定的坐标的位置。

这时要注意确认左下角的坐标值,如果定位不准,可以放大视图并重新定位,如果还是不准,则需要修改栅格吸附尺寸。

(定位坐标应该为吸附尺寸的整数倍)3-02 J,C 定位到指定的元件处。

PCB设计入门[中文资料]Altium Designer Summer 09

![PCB设计入门[中文资料]Altium Designer Summer 09](https://img.taocdn.com/s3/m/d8d3ba6648d7c1c708a145b2.png)

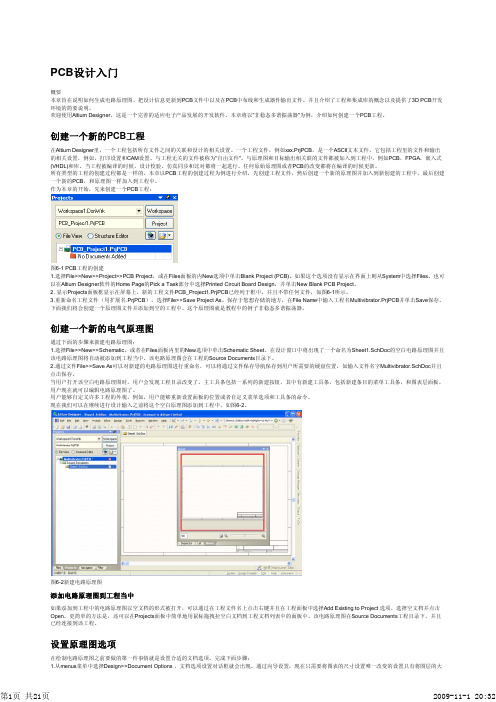

PCB设计入门概要本章旨在说明如何生成电路原理图、把设计信息更新到PCB文件中以及在PCB中布线和生成器件输出文件。

并且介绍了工程和集成库的概念以及提供了3D PCB开发环境的简要说明。

欢迎使用Altium Designer,这是一个完善的适应电子产品发展的开发软件。

本章将以"非稳态多谐振荡器"为例,介绍如何创建一个PCB工程。

创建一个新的PCB工程在Altium Designer里,一个工程包括所有文件之间的关联和设计的相关设置。

一个工程文件,例如xxx.PrjPCB,是一个ASCII文本文件,它包括工程里的文件和输出的相关设置,例如,打印设置和CAM设置。

与工程无关的文件被称为"自由文件"。

与原理图和目标输出相关联的文件都被加入到工程中,例如PCB,FPGA,嵌入式(VHDL)和库。

当工程被编译的时候,设计校验、仿真同步和比对都将一起进行。

任何原始原理图或者PCB的改变都将在编译的时候更新。

所有类型的工程的创建过程都是一样的。

本章以PCB工程的创建过程为例进行介绍,先创建工程文件,然后创建一个新的原理图并加入到新创建的工程中,最后创建一个新的PCB,和原理图一样加入到工程中。

作为本章的开始,先来创建一个PCB工程:图6-1 PCB工程的创建1.选择File>>New>>Project>>PCB Project,或在Files面板的内New选项中单击Blank Project (PCB)。

如果这个选项没有显示在界面上则从System中选择Files。

也可以在Altium Designer软件的Home Page的Pick a Task部分中选择Printed Circuit Board Design,并单击New Blank PCB Project。

2. 显示Projects面板框显示在屏幕上。

新的工程文件PCB_Project1.PrjPCB已经列于框中,并且不带任何文件,如图6-1所示。

Altium_Designer_Summer_09精简教程(附英改中方法)

第一单元:PROTEL的启动、文件的建立1、启动Altium Designer Summer 09:双击桌面上的Altium Designer Summer 09图标或点击开始菜单中的Altium Designer Summer 09图标都可启动Altium Designer。

2、新建一个工作空间:点击file-new-design workspace。

3、保存工作空间:点击File或Workspace按钮,---Save design workspace,选择存盘路径,并将文件命名为mydesign.DsnWrk保存。

4、在deising workspac面板上新建一个工程文件:点击project或workspace按钮,---Add project---PCB Project.5、保存Project工程文件:点击File---save project, 选择存盘路径,并将文件命名为PCB_Project1.PrjPCB保存。

6、在PCB_Project1.PrjPCB工程文件中添加SCH和PCB两个文件:点击File或右键PCB_Project1.PrjPCB,---Add new to project ---schematic,然后用相同方法再添加PCB即可。

然后分别保存这两个文件即可。

第二单元:SCH库和PCB库的建立1、建立一个原理图元件库和一个印制板图封装库:右键PCB_Project1.PrjPCB,---Add new to project ---schematic library.用相同的方法再添加一PCB Library.2、在SCH LIBRARY中添加一个电阻和一个LED元件:修改altium designer 9.2 Miscellaneous Devices.SchLib库或者99se Miscellaneous Devices.SCHLIB库的元件为我所用。

并给这二个元件添加相应的PCB封装库(在SCH LIBRARY面板中,双击Res1或LED0,在弹出的Library componetnt properties面板中的右下脚,点击Add----Footprint,在PCB MODEL中点击Browse,在libraries中,点击下三角,选取我的PCB图封装库.PcbLib,把电阻的封装选为AXIAL0.5;将发光二极管的封装选为LED)。

Altium-Designer-Summer-09-使用手册(更新版)

Altium Designer Summer 09 使用手册1.运行Altium Designer Summer 092.新建工程。

①. 建立PCB Project (\PCB Project),对工程进行保存(尽量用所设计板子的功能来命名。

)②. 向工程中添加原理图(Schematic)和PCB图。

有两种方法:一种是选定工程右键单击,通过“Add New to Project”分别添加“Schematic”、“PCB”,命名与工程名相同再分别保存在工程中;另一种是点击工具栏“\Schematic”、”\PCB”,以同样的方法命名保存,再通过鼠标将两个文件拖入工程中。

*若设计的原理图的元件比较多,可以在一个工程中建立多个“Schematic”文件,以所有功能模块来命名保存。

3. 装载元件库在软件右下角单机快捷菜单的System→Libraries打开元件库面板,单击Libraries…→Installed→Install…,找到所需使用的库所在的目录,选中库并单击打开;或者直接把鼠标放到右上角的“Libraries”图标上,出现元件库面板。

如图1所示:图1 元件库的转载4.放置元器件点击右上角的“Libraries”出现libraries面板,在面板中选择元件库,再选择需要的元件的名字和封装,最后点击“Place”;也可以点击“Search”出现Libraries Search面板,设定路径,输入所以所以元器件的名字,再点击左下角“Search”,最后选择元器件再点击“Place”。

如图2所示:图2 放置元器件Available Libraries:搜索可用的库,即已经导入的库。

Libraries on path:设置搜索的元器件所在库的路径5.元器件连线如果是长路径连线,可以在两个相连的元器件的两个引脚引出一段,然后放上相同的网络标号。

如果是两端都有多个引脚用总线相连,则每两端也必须放相同的网络标号。

Altium Designer Summer 09在PCB文件中显示布线网络的颜色

Altium Designer Summer 09在PCB文件中自定义布线网络显示的颜色Summer09版本允许用户在PCB文件中自定义布线网络显示的颜色。

现在,用户完全可以使用一种指定的颜色替代常用当前板层颜色作为布线网络显示的颜色。

并将该特性延伸到图形叠层模式,进一步增强了PCB的可视化特性。

注意:只有在DiretX的模式下,才可以使用本功能。

当在GDI显示模式下,只能使用当前层的颜色显示被高亮的布线网路。

定义布线网络的颜色从PCB面板内,选择Nets编辑模式,为布线网路设定实际的颜色。

用户可以为某条/多条被选/所有/一个或多个类的布线网络单独设置一种颜色。

简单地几个操作完成布线网路颜色设置–在Net Classes或Nets任一面板内–鼠标右键点击选定布线网络并从弹出的菜单中选择Change Net Color命令。

在Choose Color对话窗口内选择设定的颜色。

简单地为选定的网络类或单条网络设定颜色!选定的布线网路将显示用户所设定的颜色。

该功能还可以结合复选功能框,使用户可以将该功能延伸到每个使能的布线网路。

路。

选择布线网络的叠层颜色。

图形叠层模式关于为用户指定的布线网络设定叠层颜色功能,现在用户可以选择新的网络颜色高亮模式。

网络高亮将通过Base Pattern对话窗口管理,共有6种图形模式可供用户选择。

(DXP?Preferences).指定高亮布线网络的基础图形。

表1 通过示例介绍每种图形模式的使用情况。

设定的叠层颜色为!ExOverrideNetColor.png!.表1. 可用的基础图形列表.图形描述示例None (Layer Color) 忽略布线网络颜色设定, 只显示布线层的默认颜色.Solid (Override Color)使用布线网络用户设定的颜色, 完全覆盖原来的布线网络。

Star在布线网络上使用小的星形图形, 原布线网络的颜色仍然可见。

Checker Board 在布线网络上使用小的方形图形, 原布线网络的颜色仍然可见。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

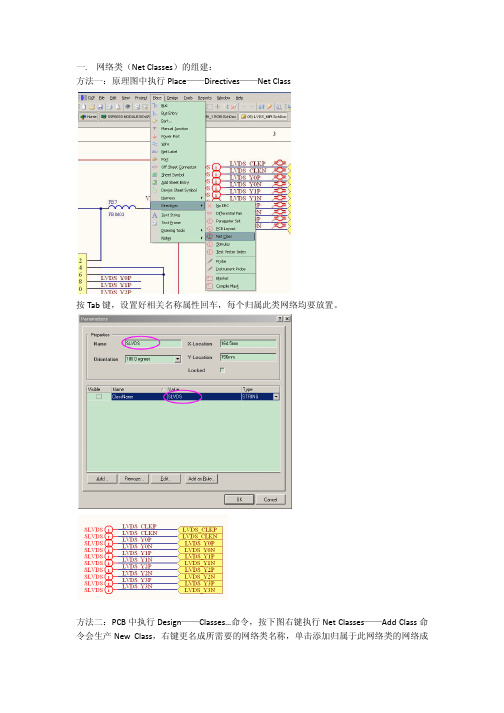

一. 网络类(Net Classes)的组建:

方法一:原理图中执行Place——Directives——Net Class

按Tab键,设置好相关名称属性回车,每个归属此类网络均要放置。

方法二:PCB中执行Design——Classes…命令,按下图右键执行Net Classes——Add Class命令会生产New Class,右键更名成所需要的网络类名称,单击添加归属于此网络类的网络成

员。

二. 差分网络类(Differential Pair Classes)的组建:

方法一:原理图中执行Place——Directives——Differential Pair

按Tab键,设置好相关名称属性回车,每个归属此类网络均要放置。

方法二:

步骤1:PCB中执行Design——Classes…命令,按下图右键执行Differential Pair Classes——Add Class命令会生产New Class,右键更名成所需要的差分网络类名称,单击添加归属于此网络

类的网络成员(前提是需要事先建立差分对网络)。

步骤2:建立差分对网络,PCB中执行View——Workspace Panels——PCB——PCB命令打开PCB面板,面板切换至Differential Pairs Editor,点击选择相应的差分网络类后再点击按钮Add,输入自定义的网络差分对名称,同时设置定义好对应的差分网络(Positive Net和Negative Net)。

也可以通过双击Differential Pairs Editor面板中的差分网络类或执行Design——Classes…命令,把所建立的差分网络对归属到对应的差分网络类。

三. ROOM相关:

1. ROOM的组建:主要目的是用于设置个别器件内部的铺铜或布线间距。

PCB中执行Design ——Rooms——Place Rectangular Room命令,按Tab键,设置好相关名称属性,在PCB中相应的器件封装上面画好Room区域。

2. 原理图导入PCB时是否生产单页ROOM

在PCB中执行Project——Project Options…

把下图中框选的勾选项来决定是否生成原理图单页ROOM

1. 间距(Clearance)设置:

2. 线宽(Width )设置:

3. 差分对布线(Differential Pairs Routing)设置:

4.

5.

6.

7. 设计规则优先级的调整:同一类规则的优先级栏数字越小则优先级越高,可以通过调整面

板左下角的Priorties按钮调整优先级。

五. PCB网络等长及阻抗说明:

1. MDIO差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1070mil,误差+/-10mil,起始参照网络差分组MDIO3_P/N;

2. GMAC网络组: 阻抗50欧,线宽距7/7mil,网络等长2455mil,误差+/-10mil,起始参照网络GMAC_RXDV;

3. LCD MIPI差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1785mil,误差+/-10mil,起始参照网络差分组MIPI_D3P/N;

4. SLVDS差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1620mil,误差+/-10mil,起始参照网络差分组LVDS_Y0P/N;

5. SDCARD0网络组: 阻抗50欧,线宽距7/7mil,网络等长1380mil(参照SD0_CLK网络),加上上拉布线网络等长1535mil,误差+/-10mil;

6. RGB_M1网络组:使用板对板连接器SCSI40P_1.27_MALE,封装PIN针脚四行,行距75mil,因连接器内部针脚长度差异,PCB布线时每行需要依次增减75mil以调整布线总长。

起始布线参照网络LCD_CLK;

[ LCD_R7,LCD_R5,LCD_R3,LCD_R1,LCD_CLK ] ,阻抗50欧,线宽距7/7mil,网络等长3100mil,误差+/-10mil;

[ LCD_G0,LCD_R6,LCD_R4,LCD_R2,LCD_R0 ] ,阻抗50欧,线宽距7/7mil,网络等长3100-75x1=3025mil,误差+/-10mil;

[ LCD_G2,LCD_G4,LCD_G6,LCD_B0,LCD_B2 ,LCD_B4,LCD_B6,LCD_DE,LCD_HSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3100-75x2=2950mil,误差+/-10mil;

[ LCD_G1,LCD_G3,LCD_G5,LCD_G7,LCD_B1 ,LCD_B3,LCD_B5,LCD_B7,LCD_VSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3100-75x3=2875mil,误差+/-10mil;

7. DLVDS差分网络组: 差分阻抗100欧,线宽距6/9mil,差分网络等长1110mil,误差+/-10mil,起始参照网络差分组RXINO+/-;

8. B_RGB网络组:使用板对板连接器SCSI40P_1.27_FEMALE,封装PIN针脚四行,行距75mil,因连接器内部针脚长度差异,PCB布线时每行需要依次增减75mil以调整布线总长。

起始布线参照网络LCD_DE;

[ LCD_G1,LCD_G3,LCD_G5,LCD_G7,LCD_B1 ,LCD_B3,LCD_B5,LCD_B7,LCD_VSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长2140-75x1=2065mil,误差+/-10mil;

[ LCD_G2,LCD_G4,LCD_G6,LCD_B0,LCD_B2 ,LCD_B4,LCD_B6,LCD_DE,LCD_HSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长2140mil,误差+/-10mil;

[ LCD_G0,LCD_R6,LCD_R4,LCD_R2,LCD_R0 ] ,阻抗50欧,线宽距7/7mil,网络等长2140+75x1=2215mil,误差+/-10mil;

[ LCD_R7,LCD_R5,LCD_R3,LCD_R1,LCD_CLK ] ,阻抗50欧,线宽距7/7mil,网络等长2140+75x2=2290mil,误差+/-10mil;

9. RGB_M2网络组:使用板对板连接器SCSI40P_1.27_MALE,封装PIN针脚四行,行距75mil,因连接器内部针脚长度差异,PCB布线时每行需要依次增减75mil以调整布线总长。

起始布线参照网络LCD_R0;

[ LCD_R7,LCD_R5,LCD_R3,LCD_R1,LCD_CLK ] ,阻抗50欧,线宽距7/7mil,网络等长3025+75x1=3100mil,误差+/-10mil;

[ G0,LCD_R6,LCD_R4,LCD_R2,LCD_R0 ] ,阻抗50欧,线宽距7/7mil,网络等长3025mil,误差+/-10mil;

[ G2,G4,G6,B0,B2 ,B4,B6,LCD_DE,LCD_HSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3025-75x1=2950mil,误差+/-10mil;

[ G1,G3,G5,G7,B1 ,B3,B5,B7,LCD_VSYNC ] ,阻抗50欧,线宽距7/7mil,网络等长3025-75x2=2875mil,误差+/-10mil;

六. 走线式铺铜网络备注,避免遗忘:

1. BL-VDD_TF_3V3

2. TL-VSYS_IN

3. BL-VSYS_IN

4. BL-D3V3_HUB

5. BL-VDD_PHY_3V3

6. TL-VDD_5V4

7. BL_I2S_D3V3

8. TL_VDD_5V TL_VDD_5V

9. TL_NetD5_2

10. BL_VDD_5V BL_VDD_5V

11. TL_VDD_CORE

12. BL_VDD_12V。