基于FPGA的DDS波形发生器的设计.

基于FPGA的DDS波形发生器

基于FPGA的DDS波形发生器DDS波形发生器设计•功能描述•输入输出描述•顶层划分•o顶层模块说明o设计思想说明•子模块描述•o分频模块o相位累加器模块o存储模块o D/A转换模块•验证方案•顶层模块代码片功能描述1.具有产生正弦波、三角波、方波、锯齿波四种周期性波形的功能。

2.输出波形的频率范围为61Hz-915Hz,频率分辨率1Hz。

3.由外界按键输入选择产生波形的种类、频率。

输入输出描述顶层划分顶层模块说明1.fenpin:用于将系统时钟分成所需时钟。

2.addr: 用于相位累加。

3.rom: 用于将相位转化成幅度。

4.pmodDA2:用于将数字量转化成模拟量。

设计思想说明1.选择端和频率控制端在时钟控制下,用相位累加器输出的地址,作为查找表的输入,得到各种波形的数字量输出。

2.数字量输出作为D/A模块的输入,得到模拟量的输出,连接示波器进行观察,若波形不理想可以用示波器上的数字滤波器,用低通滤波器,选择上限截止频率进行观察。

子模块描述分频模块本次设计需要1MHz,所以首先对系统时钟(50MHz)来进行分频,使其为1MHz来正常相位模块。

相位累加器模块相位累加器由14位地址加法器与14位累加寄存器构成。

每来一个时钟脉冲, 地址加法器将频率控制字与累加寄存器出的累加相位数据相加, 并把相加后的结果送至累加寄存器的输入端。

累加寄存器将上一时钟周期作用后所产生的新的相位数据反馈到地址加法器的输入端,使地址加法器在下一时钟的作用下继续与频率控制字相加,这样, 相位累加器在时钟的作用下, 进行相位累加, 当相位累加器累加满量时就会产生一次溢出, 完成一个周期性的动作, 这个周期也就是 DDS信号的一个频率周期(基频)。

备注:因为我的rom地址线为10位(因为存的点越多,精度越高,但同时使用资源也在成几何倍数增长),频率控制4位,所以想要采样到我存到rom中的所有点的话,必须要相位累加器的位宽不小于14位。

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

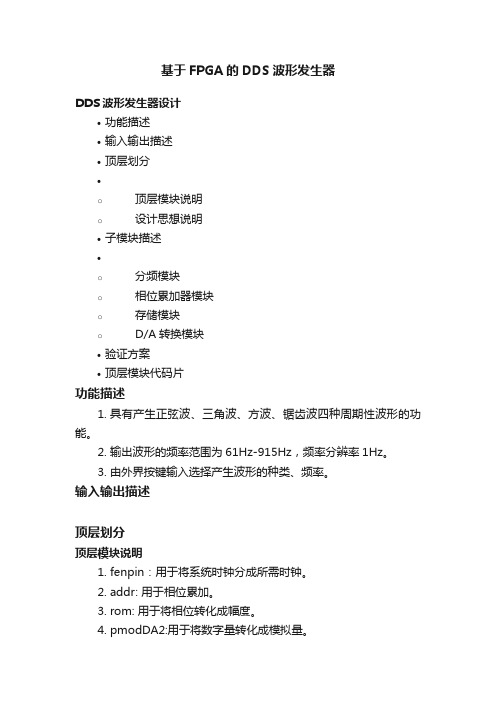

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于FPGA的DDS信号发生器的设计

基于 FPGA 的 DDS 信号发生器的设计发布时间:2022-11-15T12:38:52.851Z 来源:《中国科技信息》2022年第7月14期作者:陈慰安[导读] DDS是一种新的频率合成技术,陈慰安广东省博罗县质量技术监督检测所广东省惠州市 516100摘要:DDS是一种新的频率合成技术,也是一种新的信号生成技术。

该方法具有频率分辨率高、频率转换快、相位变化时能保持相位连续,易于实现频率、相位、振幅等数字调制。

因此,DDS在现代电子设备尤其是通信领域中得到了广泛的应用。

关键词:FPGA;DDS信号发生器;设计1FPGA和DDS相关概述FPGA(FieldProgrammableGateArray)是一种高集成度、高速度、高存储能力的器件。

该方法能够有效地实现DDS技术,极大地改善了功能信号发生器的工作效率,并大幅度降低了电子设备的制造成本。

传统的信号源电路采用模拟电路、单片机或DDS专用的芯片。

尽管其应用领域广泛,但是仍然有很多缺点,例如:设计方案成本高,输出波形类型少,输出信号频率控制不灵活,系统升级困难等。

传统的信号源存在两大问题。

一种是调节电压调节器来调节输出的频率,使其难以调节到一个固定的数值;另外,脉冲的工作周期是不能调节的。

DDS技术是目前世界上最主要的一种数字技术,它有很多优势。

DDS技术是一种低功耗、低成本、高转换频率和高分辨率的频率合成技术。

通常,DDS技术有如下几种产生信号的方法:①集成电路功能信号发生器通常能用于产生信号,但是它的功能不全、可用性低、精度低、不能满足高频信号的需要。

②利用MCU的功能产生器来完成:MAX038的优势在于生成高频信号并生成不同的波形,但是MAX038的输出频率是由模拟信号控制的。

该方法既要实现对信号的变换,又要对其进行控制。

由于步长的增大,导致了频率的精确度下降,使得电路变得更为复杂。

DDS技术是一种新的频率合成技术,它与前面所说的信号产生方式相比,可以直接进行DDS芯片的合成,具有操作简单、节约资源等优点。

基于FPGA的DDS信号发生器设计

《FPGA高级应用》期末考试题目基于FPGA的DDS信号发生器设计学名熊金齐专业班级电信工程13-01学号541301031041院(系)电子信息工程学院目录1.方案选择与方案论证 02.系统功能与原理 (1)2.1 DDS的基本原理 (1)2.2 参数确定 (2)3.硬件电路设计 (5)3.1 分频器 (3)3.2 总体原理图 (3)3.3 DDS的FPGA实现 (4)3.4 D/A转换电路 (4)4. 软件设计 (5)4.1 Verilog程序设计 (5)4.2总程序流程设计图 (5)4.3子程序流程图 (5)5.结果分析 (5)5.1 波形仿真 (6)5.2.输出波形 (6)6.设计小结 (7)附录 (8)摘要波形发生器己成为现代测试领域应用最为广泛的通用仪器之一,代表了波形发生器的发展方向。

随着科技的发展,对波形发生器各方面的要求越来越高。

近年来,直接数字频率合成器(DDS)由于其具有频率分辨率高、频率变换速度快、相位可连续变化等特点,在数字通信系统中已被广泛采用而成为现代频率合成技术中的佼佼者。

本次设计的是多功能信号发生器,它能够产生方波,三角波,锯齿波和正弦波四种基本波形。

结合DDS技术,通过对FPGA的编程实现产生多种波,本电路是通过键盘扫描判断,进入相应的功能程序,然后实现频率调节,波形转换,幅度控制的。

本次设计中我负责的是波形输出模块,通过调节要输出方波,三角波,锯齿波和正弦波四种基本波形。

关键字:波形发生器,直接数字频率合成器,现场可编程门阵列1.方案选择与方案论证数据输入:方案一:4x4矩阵键盘优点:由8个I\O口检测16个按键,可以大大节省I\O口资源。

缺点:控制时序较复杂,增加编程和调试的难度。

方案二:独立按键优点:控制时序较简单,较易于编程与调试。

缺点:比较浪费I\O口资源。

方案三:拨码开关优点:控制时序简单,易于编程和调试。

缺点:比较浪费I\O口资源。

通过比较各种因素,我选择方案一,波形输出:方案一:存储波形数据的ROM/RAM + DAC0832优点:1.可以显示复杂波形2.可以有效控制输出波形的频率,幅度及相位3.节省FPGA内部的逻辑资源4.可以简单的切换波形5.使波形输出方式单一化,降低了编程难度缺点:要消耗一定的ROM/RAM资源方案二:存储波形数据的ROM/RAM + 分频器输出矩形波+ DAC0832优点:1.可以显示复杂波形2.可以有效控制输出波形的频率,幅度及相位3.节省FPGA内部的逻辑资源4.可以较简单的切换波形缺点:矩形波的频率,幅度和相位的调节需要另设相位累加电路,消耗一定的逻辑资源方案三:case语句+ 分频器输出矩形波+ DAC0832优点:在数据传输的反应速度上,在所需速度很快时占优势缺点:1.大量浪费FPGA内部的逻辑资源2. 波形数据较大时,会给代码的调试和维护带来不便。

基于单片机和FPGA的DDS任意波形信号发生器的设计

基于单片机和FPGA的DDS任意波形信号发生器的设计摘要:本文主要对任意波形信号发生器的软硬件设计进行了相关的研究,并提出了一种新的设计思路,以现场可编程器件FPGA和单片机芯片为核心,设计任意波形信号发生器的硬件连线电路和编写相关软件程序,实现了上位机对硬件模块部分产生任意波形信号的控制。

关键词:信号发生器任意波形AT89C51FPGA1 引言任意波形发生器是电子技术领域应用最为广泛的电子测量仪器,它是信号源发展方向的代表。

由于DDS技术的查找合成波形的方法能够满足产生任意波形的要求,所以,目前大多数生产任意波形发生器的厂家都利用DDS技术来实现任意波形发生器。

本设计采用TMEL公司的单片机芯片和Xilinx公司的Virtex-Ⅱ系列FPGA芯片来实现任意波形信号发生器硬件部分的电路设计,采用美国NI公司的Labwindows/CVI作为开发平台,开发一个任意波形信号发生器的波形编辑软件,从而实现任意波形信号发生器软件模块对硬件模块产生相应波形信号的控制。

2 系统硬件设计在不影响功能的情况下,本设计简化了硬件部分的电路设计,把设计分成了多个实现模块,主要有单片机实现模块和FPGA实现模块。

单片机实现模块主要是由ATMEL公司的AT89C51芯片实现,该模块是用来完成数据传输、通信和控制数据处理电路工作等功能的。

FPGA实现模块是由Xilinx公司的FPGA芯片XC2V3000结合一些其他电路实现的,主要是用来完成DDS数据处理,实现任意波形的输出。

2.1单片机实现模块本设计选用ATMEL公司的单片机芯片AT89C51,AT89C51采用ATMEL技术,与MCS-51指令集和输出管脚相兼容,是一种高效微控制器。

本设计利用AT89C51主要是来控制显示、键盘以及FPGA电路。

单片机芯片AT89C51与液晶显示器的连线图如图1所示,AT89C51与液晶显示器通过P0口和P2口的部分位连接实现,并通过AT89C51芯片的和功能端实现读写控制。

【毕业设计】基于FPGA的DDS信号发生器-精品.

基于FPGA 的DDS 波形发生器姓名:张怡专业班级:电子2班指导教师:易诗摘要波形发生器己成为现代测试领域应用最为广泛的通用仪器之一,代表了波形发生器的发展方向。

随着科技的发展,对波形发生器各方面的要求越来越高。

近年来, 直接数字频率合成器(DDS )由于其具有频率分辨率高、频率变换速度快、相位可连续变化等特点, 在数字通信系统中已被广泛采用而成为现代频率合成技术中的佼佼者。

现场可编程门阵列(FPGA )设计灵活、速度快,在数字专用集成电路的设计中得到了广泛的应用,由于现场可编程门阵列(FPGA具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS 技术,极大的提高波形发生器的性能,降低生产成本。

在现代电子器件, 通信技术, 医学成像, 无线 PCS/ PCN系统, 雷达, 卫星通信中,具有很广泛的应用。

本文首先介绍了DDS 波形发生器的研究背景和DDS 的理论。

然后详尽地叙述了在以FPGA 芯片为主的硬件平台上设计,编程实现一个DDS 信号源,并产生不同通信中用到的调制信号(ASK,FSK ,PSK, 最后通过JTAG 方式将产生的三种调制信号数据传送到电脑上, 借助Quartus2软件中的嵌入式逻辑仪对结果进行观察与分析。

通过分析结果表明,本设计达到了预定的要求,证明了采用软硬结合的方式,结合DDS 技术,通过对FPGA 的编程实现产生多种波形(如ASK ,FSK ,PSK )的DDS 的方法是可行的。

关键词:直接数字频率合成DDS 现场可编程门阵列FPGA 波形发生器DDS waveform generator based on FPGA Abstract: Waveform generator has become a modern field test one of the most widely used general-purpose equipment, on behalf of the waveform generator development. With the development of technology in all aspects of the waveform generators have become increasingly demanding. In recent years, direct digital synthesizers (DDS has a frequency resolution because of its high-frequency conversion speed, continuous changes in the phase characteristics in digital communication systems have been widely used in modern frequency synthesis technology to become the leader in . Field-programmable gate array (FPGA design flexibility, high speed, in digital ASIC design has been widely used, due to field-programmable gate array (FPGA with high integration, high-speed, large capacity memory can be realized functional characteristics, can effectively achieve DDS technology, which greatly improve the performance of waveform generator and reduce production costs.This paper introduces the DDS waveform generator of the research background and DDS theory. Then introduce a detailed design based on FPGA, programming a DDS signal source, and produce different modulation signals used in communication, such as ASK,FSK,PSK. The last sending the three kind of modulation signals to computer by serial communication, then using Quartus2 software embedded logic analyzer on the results of observation and analysis. By analyzing the results, it show that the design meets the requirements intended to.And Proved that using Flex way to programming the FPGA to produce a variety of waveforms (such as ASK, FSK, PSK of DDS is feasible.Keywords :DDS FPGA Waveform Generator目录第1章前言 (1)1.1课题背景 (1)1.2国内外波形发生器发展现状 (1)1.2.1波形发生器的发展现状 (1)1.2.2国内外波形发生器产品比较 (2)1.2.3研究波形发生器的目的及意义 (2)1.3本文研究主要内容 (2)本章小结 (2)第2章 DDS 波形发生器理论介绍 (3)2.1 频率合成技术 (3)2.1.1频率合成技术发展与分类 (3)2.1.2频率合成技术指标 (4)2.1.3频率合成的技术现状 (5)2.2 DDS基本原理与特点 (6)2.2.1 DDS基本原理 (6)2.2.2 DDS优点 (7)2.2.3 DDS缺点 (7)本章小结 (7)第3章数字调制信号介绍 (8)3.1概述 (8)3.2调制方式 (8)3.3 ASK幅移键控 . (9)3.4 PSK相移键控 (10)3.5 FSK 频移键控 (11)本章小结 (11)第四章开发平台介绍................................................................................................124.1 硬件平台FPGA 介绍 (12)4.1.1 FPGA简介 (12)4.1.2 FPGA工作原理 (12)4.1.3 本系统所用开发板简介 (13)4.2 软件平台Quartus II介绍 (14)本章小结 (14)第5章系统实现........................................................................................................155.1电路整体设计 (15)5.2 PLL模块 (16)5.2.1 PLL背景简介 (16)5.2.2 本系统中的PLL 模块 (16)5.3 异步串口模块 (18)5.3.1 背景介绍 (18)5.3.2 本系统中的异步串口模块 (18)5.4 NCO模块 (19)5.4.1 NCO背景介绍 (19)5.4.2 本系统中的NCO 模块 (19)5.5 用户自定义模块 (20)5.5.1 ASK/PSK选择模块 (20)5.5.2 FSK选择模块 (21)5.6 电路运行结果分析 (22)本章小结 (23)总结..............................................................................................................................24致谢..............................................................................................................................25参考文献......................................................................................................................26成都理工大学2011届本科毕业设计(论文)第1章前言1.1课题背景在频率合成领域中, 直接数字合成(Direct Digital Synthesizer ,简称:DDS 是近年来新的技术, 它从相位的角度出发直接合成所需波形。

基于FPGA的DDS信号发生器的设计与实现

基于FPGA的DDS信号发⽣器的设计与实现⼀、实现环境 软件:Quartus II 13.0 硬件:MP801⼆、DDS基本原理 DDS(Direct Digital Synthesizer)即数字合成器,是⼀种新型的频率合成技术,具有相对带宽⼤,频率转换时间短,分辨率⾼和相位连续性好等优点。

较容易实现频率、相位及幅度的数控调制,⼴泛应⽤于通信领域。

DDS的实现⽰意图如下图所⽰: 1、将需要合成的信号的数据存储在rom中,合成待输出信号的⽅法请参考: 2、dds_control实现的功能是将存储在rom中的待合成的信号的数据按照⼀定的规则取出来: dds_control主要由相位累加和频率累加来实现,简单的说,通过控制相位累加和频率累加来实现从rom中取出不同时刻的数据。

(1)相位累加器位数为N位(24~32),相位累加器把正弦信号在相位上的精度定义为N位,其分辨率位1/2N ,决定⼀个波形的起始时刻在哪个点; (2)频率累加器⽤来控制每隔⼏个点从rom中取⼀个数据,决定⼀个波形的频率; (3)若DDS的时钟频率为F clk ,频率控制字fword = 1,则输出频率为 F out = F clk/2N,这个频率相当于“基频”,若fword = B,则输出频率 F out = B * F clk/2N。

因此理论上由以上三个参数就可以得出任意的 f o 输出频率,且可以得出频率分辨率由时钟频率和累加器的位数决定的结论。

当参考时钟频率越⾼,累加器位数越⾼,输出频率分辨率就越⾼。

3、从FPGA中出来的信号都是数字信号(dds_control输出的信号都为数字信号),需要通过dac芯⽚来将数字信号转换为模拟信号,这样将dac芯⽚输出的信号接⼊到⽰波器中,才能看到波形; 4、举例说明频率控制和相位控制: 如上图所⽰,这个是⼀个由33个点构成的正弦波信号,(rom_addr,rom_data),纵坐标为存储在rom中的正弦波信号,横坐标为dds_control ⽣成的地址信号。

基于FPGA的DDS波形发生器设计

另外还经常需要 两路正弦信号不仅具有相同的频率, 同时要有确定的相位差。因此基于 F G P A的 D S D 波形

及 噪声性 能 已接 近并达 到锁 相频 率合 成器 相 当的水

专用集成电路( SC ,P A有更短的开发周期 , A I )F G 如

果产品数量不大 ,P A更有低成本的优势。F G FG PA 擅长逻辑和高速可并行运算 , 不是通用 D P芯片可 S 比拟的, 一般单片机更是望尘莫及。 直接数字频率合成 ( 简称 D S D) 技术是一种新的 全数字的频率合成技术 ,从相位的角度出发直接合

一

D S的主要优点有 :1频率转换快, D () 一般在纳 秒级 () 2 分辨率高( ) 3频率合成范围宽 () 4 相位噪声

1 电路 的构成

设 计 主 要 是 基 于 F G 的 D S波形 发 生 器 的 PA D

低, 信号纯度高( ) 5 可控制相位 , 在频率变换 时也能

实现, 要求输 出频率范 围在 1 z 5 H , H ~ M z采用 E 2 8 PC 保持相位联系( ) 6 生成的正弦/ 余弦信号正交特性好 硬件为核心平 台, 再加上 F G P A的外围电路 , 利用至 等。与此同时 , F G 用 P A设计 D S电路 比采用专用 顶 向下的方法 , D 将数字频率合成器(D )存储器和 D S、

发生器, 具有一定的实际意义。以 F G P A芯片 E 2 8 28 8 P C Q 0C 为核心 , 辅以必要 的模拟 电路 , V r g 在 e l 编写 i o 的程序控制下, 构成 了一个基于直接数字频率合成技 术的波形发生器。 【 关键词】P A; D ; F G D S 波形发生器

基于FPGA的DDS信号发生器的设计

设计与分析・Sheji yu Fenxi基于F P GA 的DDS 信号发生器的设计蒋小军(湖南铁道职业技术学院,湖南株洲412001)摘要:直接数字频率合成器(DDS )广泛应用于航空控制、通信、电子测量及研究等领域。

现提出一种DDS 信号发生器,釆用EDA 自顶向下的设计方法,在Q-artus 3集成开发环境中利用原理图和调用PLM 宏功能模块完成软件设计,并通过FPGA 进行硬件测试。

关键词:FPGA ;直接数字频率合成器(DDS) ; PLM引言直接数字频率合成器(DDS), 一种 的频率合成技术和信号生方法,的频率 率, 实现频率的快速切换,并且在变能 ,实现频率、 和 的数控调制。

,在现代电子 及设的频率源设计中,在通信领域,DDS 的应用 广泛。

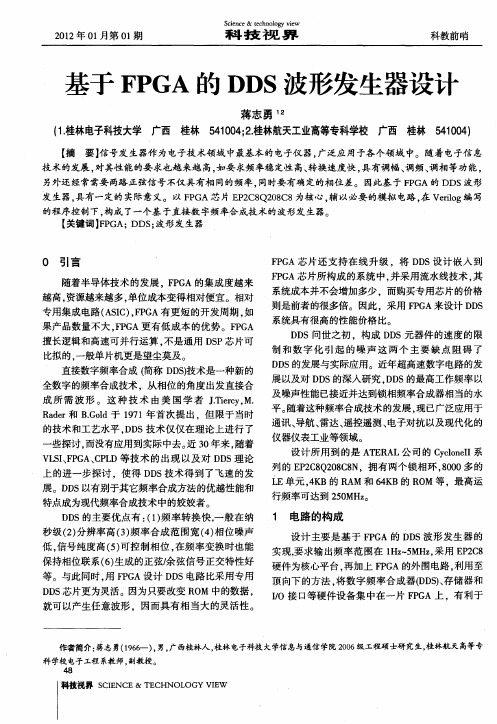

1系统的整体设计方案设计的一个DDS 信号发生器,如图1所示,它器、 调制器、 ROM 和D/A 换模块 成。

1ROM 中的mif 数件, 生 、方、 等 信号。

器 DDS 的核心,完成 的功能, 器的量!又由于!与输出频率血的B3=2g 血,器的频率字输入。

当系忌2$时等于尤频率字 在图1中 :过了一 器, 频率字改变加器的。

系统时钟图1 DDS 信号发生器结构调制器接 器的 出,在 一, 用于信号的 调制,如PSK (相移键控)等,在 用 , 一个固定的字数 S 字 最好也用步 器 步。

注意,字输入的数 宽 &与频率字$往往 不相等的,波数字储ROMG表)完成仏(凤)的换,也 理解成 到 的换,的 调制器的输出,事实上就是ROM 的地址出送往D/A ,转化模拟信号。

于 调制器的出数 宽&也ROM 的地址宽,因此在实际的DDS 结构中$往往很大,而&为10位左右。

2电路设计DDS 信号发生器电路原理图图2所示,法器ADDER32、 器REG32、数据波形ROM 三大功能子模块组成。

图2电路原理图(1) 32位加法器ADDER32。

基于FPGA的波形产生器

基于 FPGA 的 DDS 波形发生器设计本课程设计的题目是:基于FPGA的波形产生器。

设计内容是以Xilinx Spartan 3E实验板为控制核心,用直接数字频率合成技术(DDS),经板上DA转换输出模拟信号,实现频率和输出电压峰-峰值都可调。

本设计要求完成的基本功能是:1)具有产生正弦波、方波、三角波三种周期性波形的功能。

2)输出波形的频率范围为100Hz-20kHz(非正弦波频率按10次谐波计算)。

重复频率可调,频率步进间隔≤100Hz。

3)输出波形幅度范围0-3V(峰峰值),可按步进0.1V(峰峰值)调整。

4)由外界按键输入选择产生波形的种类、频率与幅度。

5)界面显示输出波形的类型、重复频率(周期)和幅度等信号参数。

课程设计目的通过本课程设计加深对“基于Vrilog HDL的FPGA设计基础”理论学习的理解;熟悉相关EDA工具的使用;掌握FPGA数字电路设计流程;掌握PS2键盘工作原理;掌握液晶显示工作原理;掌握RS232串口通信工作原理。

【概述】将现场可编程逻辑器件 FPGA 和 DDS 技术相结合,具体的体现了基于VHDL 语言的灵活设计和修改方式是对传统频率合成实现方法的一次重要改进。

FPGA器件作为系统控制的核心,其灵活的现场可更改性,可再配置能力,对系统的各种改进非常方便,在不更改硬件设计部分电路的基础上还可以进一步提高系统的性能。

文章给出仿真结果,经过验证本设计能够达到其预期性能指标。

【系统设计部分】·1 整个设计组织结构DDS基本原理DDS建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。

DDS基本原理框图如图1所示。

除了滤波器(LPF)之外,DDS系统都是通过数字集成电路实现的,易于集成和小型化。

系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,为各组成部分提供同步时钟。

基于FPGA的DDS波形发生器

基于FPGA的DDS波形发生器秦怀宇【摘要】DDS are widely used in the field of telecommunication and electronic equipment. DDS is the key technique to achieve all-digital equipment. The paper has completed the waveform simulation of sine-wave signal, triangle-wave signal, modulated signal with Quartus II. It has also performed the hardware design and implementation of waveform generator by means of Altera's high-performance MCU EP2C35.%DDS广泛应用于电信与电子仪器领域,是实现设备全数字化的关键技术.文章应用Quartus II 软件完成正弦波信号、三角波型号、调制信号的波形仿真,并以Altera的FPGA核心板EP2C35,完成DDS波形发生器的硬件设计与实现.【期刊名称】《价值工程》【年(卷),期】2011(030)024【总页数】2页(P130-131)【关键词】直接数字合成;现场可编程门阵列;Quartus Ⅱ;波形发生器【作者】秦怀宇【作者单位】江苏科技大学张家港校区电气与信息工程学院,张家港215600【正文语种】中文【中图分类】TN920 引言波形发生器是一种广泛应用于电子电路、自动控制和科学试验等领域的信号源。

比如电参量的测量、雷达、通信、电子对抗和电子系统、宇航和遥控遥测技术等等,从某种意义上说高品质信号源更是实现高性能指标的关键,很多现代电子设备和系统的功能都直接依赖于所用信号源的性能,因此高品质信号源被喻为电子系统的“大脑”。

【最新版】基于FPGA的DDS信号发生器的研究本科毕业设计

毕业论文基于FPGA的DDS信号发生器的研究第1章绪论1.1 课题背景频率检测是电子测量领域的最基本也是最重要的测量之一,频率信号抗干扰强,易于传输,可以获得较高的测量精度,所以频率方法的研究越来越受到重视[1]。

在频率合成领域中,直接数字合成(Direct Digital Synthesizer,简称:DDS)是近年来新的技术, 它从相位的角度出发直接合成所需波形。

它是由美国人J.Tierncy首先提出来的,是一种以数字信号处理理论为基础,从相位概念出发直接合成所需波形的一种新的全数字技术的频率合成方法[2]。

其主要优点有:频率改变速度快、频率分辨率高、输出相位连续、可编程、全数字化便于集成等,目前使用最广泛的一种DDS频率合成方式是利用高速存储器将正弦波的M个样品存在其中,然后以查找的方式按均匀的速率把这些样品输入到高速数模转换器,变成所设定频率的正弦波信号[3]。

近30年来,随着超大规模集成、现场可编程门阵列(Field Programmable Gate Array,简称:FPGA)、复杂可编程器件(Complex programmable Logic Device,简称:CPLD)等技术的出现以及对DDS 理论上的进一步探讨,使得DDS技术得到了飞速的发展。

它已广泛应用于通讯、雷达、遥控测试、电子对抗、以及现代化的仪器仪表工业等许多领域。

DDS的数字部分,即相位累加器和查表,被称为数控振荡器(NCO)[4]。

波形发生器即通常所说的信号发生器是一种常用的信号源,和示波器、电压表、频率计等仪器一样是最普遍、最基本也是应用最广泛的的电子仪器之一,几乎所有电参量的测量都要用到波形发生器。

不论是在生产还是在科研与教学上,波形发生器都是电子工程师信号仿真试验的最佳工具。

随着现代电子技术的飞速发展,现代电子测量工作对波形发生器的性能提出了更高的要求,不仅要求能产生正弦波、方波等标准波形,还能根据需要产生任意波形,且操作方便,输出波形质量好,输出频率范围宽,输出频率稳定度、准确度及分辨率高,频率转换速度快且频率转换时输出波形相位连续等。

基于FPGA的DDS信号发生器设计

2 信号发生器的 F P G A 逻辑控制设计

D D S 信号发生器 的 F P GA 逻 辑 控 制 部 分 主 要 由 相 位 累 加 器 、R OM 波 形 存 储 器 组 成 。 本 设 计 采 用 N = 3 2, c = f , 、 输 出 信 号 幅 值 范 围 频 率 范 围 5 0MH z 0~1 0 V 1 H z~ , 波形可设为三角波 、 矩形波 、 正弦波 、 锯齿波等 。 1 0 0 k H z 2 . 1 F P G A 查表预处理 系统设计的三角 波 和 矩 形 波 可 分 别 通 过 调 用 D 触 发 器 和

的频率准确可调 , 频 率 合 成 要 产 生 所 需 的 纯 净 频 率 信 号 。 常 用的频率合成方法有 基 于 锁 相 环 原 理 实 现 的 间 接 合 成 法 、 模 拟直接合成法和数字直接合成法 。 ,D )具 直接数字频率合成 ( D i r e c t D i i t a l S n t h e s i z e r D S g y 有极高的频率分辨 率 、 极 快 的 频 率 捷 变 速 度 、 频 率 捷 变 时 相 位连续 、 相位噪声低 、 集 成 度 高 和 可 灵 活 产 生 多 种 信 号 等 传

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第19卷第3期2010年6月淮阴工学院学报Journal of Huaiyin Institute of Technology Vol.19No.3Jun.2010基于FPGA 的DDS 波形发生器的设计李景,李慧(淮阴工学院电子与电气工程学院,江苏淮安223003)PC 部分采用DELPHI 语言完成摘要:DDS 波形发生器的设计原理分为两个部分,即PC 机部分和FPGA 模块部分。

其中,经串口向FPGA 发送波形以及频率参数;FPGA 部分由VHDL 语言完成,作为系统的控制核心,根据接收到的波形以设计,及频率参数信息,采用DDS 产生相应的波形。

关键词:VHDL ;DDS ;频率;核心;中图分类号:TP386.1文献标识码:A文章编号:1009-7961(2010)03-0041-04The Design of DDS Wave Generator Based on FPGALI Jing ,LI Hui(Faculty of Electronic and Electrical Engineering ,Huaiyin Institute of Technology ,Huai'an Jiangsu 223003,China )Abstract :This paper introduces the theory about how to design DDS wave generator ,the system of which is di-vided into two parts :PC part and FPGA module part.The design about PC part is accomplished by DELPHI language.The parameter of wave form and frequency is sent to FPGA module by PC part.The part of FPGA module by the way of the control core is designed by using VHDL.And at the same time FPGA generates rele-vant wave by using DDS theory according to the information about the parameter of wave and frequency received from PC part.Key words :VHDL ;DDS ;frequency ;core0引言波形发生器是一种常用的信号源,广泛用于11.1DDS 设计原理DDS 基本结构科学研究、生产实践和教学实践等领域。

如设计汽车制造、生物医药、传感器仿真、制造模和测试、型等。

目前,波形发生器大多由振荡器、放大器、衰减器、指示器和调制器组成。

这种传统设计方法硬件连线复杂,可靠性较差。

而硬件描述语言VHDL 和可编程器件的广泛应用打破了硬件和软件的屏障。

基于VHDL 语言,以EDA 技术作为开发手段来设计波形发生器得到广泛应用。

本设计正是运用DDS 技术的一种基于FPGA 的DDS 波形信号发生器的设计,并用硬件描述语言VHDL 编用Delphi 语言来设程实现系统的软件部分设计,计系统的PC 机界面部分,在实验箱上采用DDS 实现正弦波、三角波、锯齿波等波形的产生。

收稿日期:2010-06-07DDS [1]基本原理是建立在采样定理的基础上,它首先对需要产生的信号波形进行采样和量化,然后存入存储器作为待产生信号波形的数据表。

输出信号波形时,电路在一个高稳定时钟信号的控制下从数据表中依次读出信号波形的数据,产生数字化的信号,这个信号再通过DAC 转换成所需的模拟信号波形。

低通滤波器使输出信号的频谱纯净。

它主要由标准参考频率源、相位累加器、波形存储器、数模转换器、低通平滑滤波器构成。

1.2DDS 工作原理DDS 技术的核心是相位累加器,每到来一个时钟信号,相位累加器的输出就增加一个步长的相位增加量,相位增加量的大小由频率控制字来作者简介:李景(1981-),女,江苏徐州人,硕士在读,主要研究方向为电气控制。

42淮阴工学院学报2010年确定。

频率控制字(FSW )实际上是相位增量值(二进制编码),作为相位累加器的累加值。

频率控制字K 在每一个时钟周期与相位累加器累加一次,得到的相位值被送到ROM 中对其进行查表,ROM 的输出送到D /A转换器,D /A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

低通滤波器用于滤除不需要的取以便输出频谱纯净的各种信号。

样分量,当频率合成器正常工作时,在标准频率参考源的控制下(频率控制字决定了相应的相位增量),相位累加器则不断地对该相位增量进行线性累加,当相位累加器积满量时就会产生一次溢出,从而完成一个周期性的动作,这个动作周期即是DDS 合成信号的一个频率周期。

如果相位累加器的位数为N ,频率控制字内的相位增量为K ,参考时钟频率为f C ,则DDS 系统输出信号的频率f O 为:f O =f C ˑ K /2N输出信号的频率分辨率△f O 为:N△f O =f C /22.22.2.1PC 机部分界面设计部分PC 控制部分主要是使用高级语言Delphi 编程实现,设计界面如图2所示。

图2PC 机控制界面2.2.2子程序设计(1)(2)系统采用串行通信控件TCOMM 。

首先对串,“确定”行口进行初始化键按下后,对波形以及频率进行编码,组合为一个字节数据(高4位表示波形,低4位表示频率),通过串行口进行发送。

程序设计如下:form1.Comm1.PortOpen :=true ;//打开串行口if form1.RadioButton2.Checked =true then be-gin //正弦波if form1.ComboBox1.ItemIndex =0then send [0]:=¥01//频率93.75赫兹else if form1.ComboBox1.ItemIndex =1then send [0]:=¥02//频率187.5赫兹…else send [0]:=¥09;//频率843.75赫兹endelse if form1.RadioButton1.Checked =true then begin //方波…endelse if form1.RadioButton4.Checked =true then begin //三角波…endelse if form1.RadioButton3.Checked =true then begin //锯齿波因此,当输入所需频率时,经转换成频率控制字去驱动FPGA 工作,从而产生所需波形的频率。

22.1系统软件设计总体结构介绍DDS 波形信号发生器主要由四个部分组成。

(1)PC 机控制部分;(2)存取数据和直接数字频率合成部分;(3)DAC 进行D /A转换部分;(4)LPF 滤波器部分。

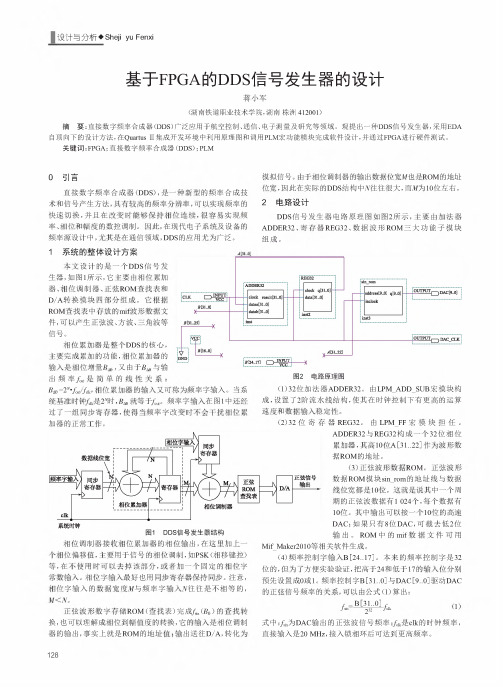

如图1所示,直接数字频率合成部分是整个系统的核心部分,产生的数字信号通过芯片内部集成的D /A转换器变成模拟波形,再通过低通滤波器平滑后产生所需要的各种信号。

图1系统总体设计结构原理图第3期李景,李慧:基于FPGA 的DDS 波形发生器的设计43…end ;form1.Comm1.OutputByte (send [0]);//发送命令2.32.3.1FPGA 部分软件设计总体设计原理系统FPGA 部分的原理图如图3所示。

图3系统FPGA 部分原理图2.3.2相位累加模块设计end if ;end if ;end process ;Q <=TEMP_Q_0;2.3.4波形选择模块设计[2]本部分采用典型的CASE 语句进行译码,程本部分主要完成相位的累加功能,设计程序如下:process (REG_Q,A )beginTEMP <=REG +A ;———相位累加end process ;process (CLK ,CLR )begin if CLR ='1'thenREG <="000000" ;———系统数据清零elsif rising_edge(CLK )then if CE ='1'thenREG <=TEMP ;———锁存输出end if ;end if ;end process ;Q <=REG_Q;2.3.3寄存器模块设计本部分主要完成地址以及数据的锁存,以6位地址锁存为例,设计程序如下:process (CLK ,CLR )beginif CLR ='1'thenTEMP_Q_0<=(others =>'0');———系统数据清零elsif rising_edge(CLK )thenif CE ='1'thenTEMP_Q_0<=DATA ;———锁存序设计如下:case bx iswhen "00" =>———正弦波…--输出正弦波数据when "01" =>———方波…--输出方波数据when "10" =>…———输出三角波数据when others =>…———输出锯齿波数据end case ;2.3.5串行通信模块接收部分设计串行通信的实质就是通过串行口在波特率发生器的作用下逐位接收数据,然后转化为并行数据输出。

核心部分设计程序如下:if clk1x'event and clk1x ='0'thenstd_logic_vector(no_bits_rcvd)>=" 0000" and std_logic_vector(no_bits_rcvd)<="1000" thenrsr (7downto 1)<=rsr (6downto 0);rsr (0)<=rxd2;———串行移位elsif std_logic_vector(no_bits_rcvd)="1001"44淮阴工学院学报2010年then——并行接收rbr <=rsr ;—end if ;end if ;//将串行数据转化为并行数据。

2.3.6系统仿真以正弦波为例,我们对波形进行了系统仿真,输出为正弦波仿真波形如图4所示。

从图中可以看出,输出数据的变化规律为稳定的正弦规律。

图4正弦波仿真图[J ].国外电子测量技术,2010(4):44-47.[3]潘松.EDA 技术实用教程[M ].北京:科学出版社,2005.[4]蒋小燕.EDA 技术及VHDL [M ].南京:东南大学出版2008.社,[5]罗朝霞,.北京:高书莉.CPLD /FPGA设计及应用[M ]2007.人民邮电出版社,[6]范逸之,陈立元.Delphi 与RS -232串行通信控制[M ].北京:清华大学出版社,2002.(责任编辑:尹晓琦)3结束语通过实际的现场调试,实现了基于FPGA 的DDS 波形发生器的功能,信号输出稳定,控制精度高,控制界面人性化,具有很强的实用价值。