UDZS4.3B中文资料

USB-2404 4通道24位156KHz SPS同步采集16路DI,16路DO卡用户手册说明书

USB-24044通道24位156KHz SPS同步采集16路DI,16路DO卡用户手册北京新超仁达科技有限公司20122.10201版权所有(C)北京新超仁达科技有限公司2012在无北京新超仁达科技有限公司优先书面授权书前提下,此出版物任何一个部分不可通过任何形式进行复制、修改和翻译。

对于非法复制、修改和翻译商业行为,将根据国家知识产权相关法律追求其法律责任。

从此文件发布日期起,在此发表的是当前或者拟定的信息。

由于我们会不断对产品进行改进和增加特征,此出版物中的信息如有变动恕不另行通知。

一、前言 (3)二、概述 (3)三、产品应用 (3)四、性能特点 (3)五、技术参数 (4)六、工作原理 (4)6.1、逻辑框图 (4)6.2、工作原理简述 (4)6.3、触发模式 (5)6.3.1、软启动: (5)6.3.2、外触发: (5)6.4、SDRAM中数据存放顺序 (5)6.5、FIFO容量 (5)6.6、批量数据的传输 (5)七、信号定义 (6)7.1、模拟输入输出引脚定义 (6)7.2、数字量输入、输出引脚定义 (7)7.3、ID设置:(四位拨码开关SW设置) (8)7.4、双极性模拟量输入的电压换算 (8)八、常用信号连接 (9)8.1、外部模拟输入差分信号 (9)8.2、数字量输入 (9)8.3、数字量输出 (9)九、软件 (10)9.1、驱动安装 (10)9.2、测试程序 (13)9.3、函数调用说明 (13)9.3.1、库中部分函数说明: (13)9.3.2、函数调用注意事项 (18)9.4、DLL函数全部是WINAPI调用约定的,即__stdcall接口 (18)9.5、驱动文件 (18)十、编程指导 (18)10.1、VC程序编程说明 (18)10.2、VB程序编程说明 (19)10.3、LabVIEW程序编程说明 (20)10.4、Delphi程序编程说明 (20)十一、维修服务 (21)11.1、产品完整性 (21)11.2、维修 (21)11.3、服务 (21)一、前言信息社会的发展,在很大程度上取决于信息与信号处理技术的先进性。

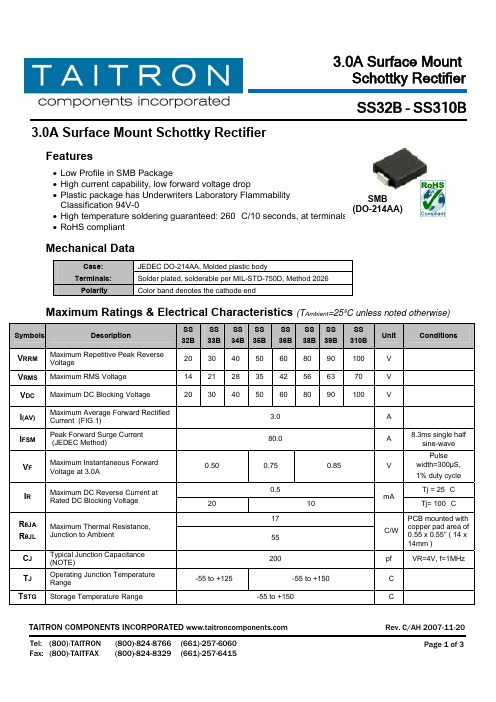

SS34B中文资料

TAITRON COMPONENTS MEXICO, S.A .DE C.V.

BOULEVARD CENTRAL 5000 INTERIOR 5 PARQUE INDUSTRIAL ATITALAQUIA, HIDALGO C.P. 42970 MEXICO Tel: +52-55-5560-1519 Fax: +52-55-5560-2190

Instantaneous Reverse current (mA) IR Reverse Leakage Current (mA)

Number of Cycles at 60Hz Fig.4- Typical Reverse Characteristics

Instantaneous Forward Voltage (V) Percentage of Peak Reverse Voltage (%) Fig.5- Typical Junction Capacitance

IF(AV) Average Rectified Current (A) Instantaneous Forward current (A)

Fig.2- Max. Non-Repetitive Forward Surge Current

Ambient Temperature Ta (°C) Fig.3- Typical Forward Characteristics

TAITRON COMPONENTS INCORPORATED REPRESENTAÇÕES DO BRASIL LTDA

RUA DOMINGOS DE MORAIS,ห้องสมุดไป่ตู้2777, 2.ANDAR, SALA 24 SAÚDE - SÃO PAULO-SP 04035-001 BRAZIL Tel: +55-11-5574-7949 Fax: +55-11-5572-0052

三汇 S3A03 系列 4G DTU 用户手册说明书

三汇S3A03系列4G DTUVersion 1.0.1杭州三汇信息工程有限公司目录目录 (i)表格检索 (iii)图片检索 (iv)版本修订记录 (v)前言 (1)第1章产品概述 (2)1.1产品说明 (2)1.2特性 (3)1.3原理框图 (4)第2章产品包装 (6)2.1概述 (6)2.2包装清单 (6)2.3安装与接口说明 (6)2.3.1外形尺寸 (6)2.3.2天线与SIM卡安装 (7)2.3.3DB9接口定义说明 (8)2.3.4DB9母头转9P端子接线说明 (8)2.3.5DI和DO说明 (9)2.3.6状态指示灯说明 (9)第3章参数配置 (11)3.1如何开始使用PC端软件进行配置 (11)3.2主配置界面介绍 (12)3.3配置项详细介绍 (13)3.3.1APN(运营商网络设定) (13)3.3.2公网服务器设置 (13)3.3.3数据传输模式设置 (13)3.3.4联络机制(心跳包)设定 (13)3.3.4.1心跳包 (14)3.3.4.2注册包 (14)3.3.4.3链路保持机制(必看) (14)3.3.4.3.1心跳机制 (14)3.3.4.3.2发送或接收超时 (14)3.3.4.3.3自动重启 (15)3.3.4.3.4Modem死机自动重启 (15)3.3.5短信号码设置 (15)3.3.6输出开关量DO设置 (15)3.3.7输入开关量DI (16)3.3.8常用功能 (16)3.3.8.1设备参数查询 (16)3.3.8.2配置的导入和导出 (16)3.3.8.3信号强度查询 (16)3.3.8.4DTU波特率设置 (16)第4章典型应用流程 (17)4.1利用开关量输入产生报警 (17)4.2利用开关量输出驱动继电器 (17)4.3SMS短信透传 (17)4.4DTU数据透传 (17)第5章联网测试 (18)5.1方法1. (18)5.2方法2 (19)5.2.1登入路由器 (19)5.2.2添加转发规则 (19)5.2.3获取路由器公网IP (20)附录A 技术/销售支持 (21)表格检索表1 :术语缩写 (1)表2 :产品选型 (3)表3 :产品特性 (3)表4 :DB9公头接口定义 (8)表5 :指示灯说明 (9)图片检索图1:S3A03正面 (2)图2:S3A03配件图 (3)图3:安装尺寸图 (6)图4:S3A03结构件说明 (7)图5:DI和DO外接电路示意图 (9)版本修订记录前言本文档描述了S3A03系列DTU的相关说明及参数配置。

UDZ6.8B中文资料

Fig.3 Zener voltage temp.coefficient characteristics

元器件交易网

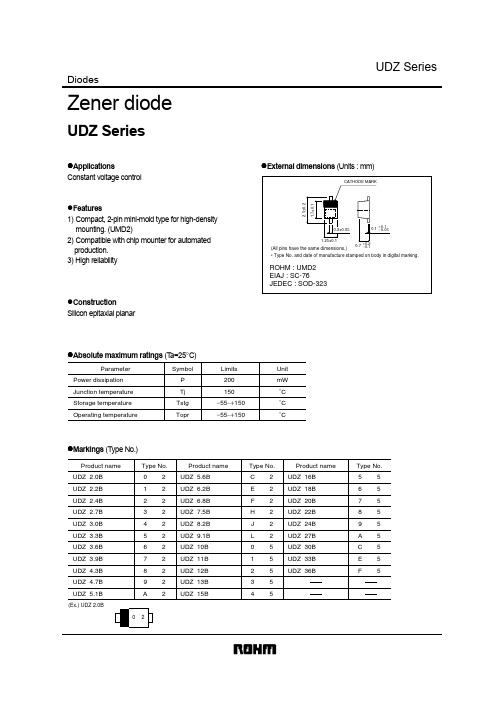

UDZ Series

Diodes

Zener diode

UDZ Series

!Applications Constant voltage control !External dimensions (Units : mm)

THODE MARK

2.5±0.2

!Features 1) Compact, 2-pin mini-mold type for high-density mounting. (UMD2) 2) Compatible with chip mounter for automated production. 3) High reliability

ROHM : UMD2 EIAJ : SC-76 JEDEC : SOD-323

!Construction Silicon epitaxial planar

!Absolute maximum ratings (Ta=25°C)

Parameter Power dissipation Junction temperature Storage temperature Operating temperature Symbol P Tj Tstg Topr Limits 200 150 −55∼+150 −55∼+150 Unit mW ˚C ˚C ˚C

Product name UDZ 5.6B UDZ 6.2B UDZ 6.8B UDZ 7.5B UDZ 8.2B UDZ 9.1B UDZ 10B UDZ 11B UDZ 12B UDZ 13B UDZ 15B

CS42438_07中文资料

FEATURESSix 24-bit A/D, Eight 24-bit D/A Converters ADC Dynamic Range–105 dB Differential –102 dB Single-Ended DAC Dynamic Range–108 dB Differential –105 dB Single-Ended ADC/DAC THD+N–-98 dB Differential –-95 dB Single-EndedCompatible with Industry-Standard TimeDivision Multiplexed (TDM) Serial InterfaceDAC Sampling Rates up to 192 kHz ADC Sampling Rates up to 96 kHzProgrammable ADC High-Pass Filter for DCOffset CalibrationLogarithmic Digital Volume Control Hardware Mode or Software I²C ® & SPI ™ Supports Logic Levels Between 5V and 1.8VGENERAL DESCRIPTIONThe CS42438 CODEC provides six multi-bit analog-to-digital and eight multi-bit digital-to-analog delta-sigma converters. The CODEC is capable of operation with ei-ther differential or single-ended inputs and outputs, in a 52-pin MQFP package.Six fully differential, or single-ended, inputs are avail-able on stereo ADC1, ADC2, and ADC3. When operating in Single-Ended Mode, an internal MUX be-fore ADC3 allows selection from up to four single-ended inputs. Digital volume control is provided for each ADC channel, with selectable overflow detection.All eight DAC channels provide digital volume control and can operate with differential or single-ended outputs.An auxiliary serial input is available for an additional two channels of PCM data.The CS42438 is available in a 52-pin MQFP package in Commercial (-10°C to +70°C) and Automotive (-40°C to +105°C) grades. The CDB42438 Customer Demonstra-tion board is also available for device evaluation and implementation suggestions. Please refer to “Ordering Information” on page 61 for complete ordering information.The CS42438 is ideal for audio systems requiring wide dynamic range, negligible distortion and low noise, such as A/V receivers, DVD receivers, and automotive audio systems.CS42438TABLE OF CONTENTS1. PIN DESCRIPTIONS - SOFTWARE MODE (6)1.1 Digital I/O Pin Characteristics (8)2. PIN DESCRIPTIONS - HARDWARE MODE (9)3. TYPICAL CONNECTION DIAGRAMS (11)4. CHARACTERISTICS AND SPECIFICATIONS (13)RECOMMENDED OPERATING CONDITIONS (13)ABSOLUTE MAXIMUM RATINGS (13)ANALOG INPUT CHARACTERISTICS (COMMERCIAL) (14)ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE) (15)ADC DIGITAL FILTER CHARACTERISTICS (16)ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL) (17)ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE) (18)COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (20)SWITCHING SPECIFICATIONS - ADC/DAC PORT (21)SWITCHING CHARACTERISTICS - AUX PORT (22)SWITCHING SPECIFICATIONS - CONTROL PORT - I²C MODE (23)SWITCHING SPECIFICATIONS - CONTROL PORT - SPI FORMAT (24)DC ELECTRICAL CHARACTERISTICS (25)DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS (25)5. APPLICATIONS (26)5.1 Overview (26)5.2 Analog Inputs (27)5.2.1 Line-Level Inputs (27)5.2.1.1 Hardware Mode (27)5.2.1.2 Software Mode (27)5.2.2 ADC3 Analog Input (28)5.2.3 Hardware Mode (29)5.2.4 Software Mode (29)5.2.5 High-Pass Filter and DC Offset Calibration (29)5.2.5.1 Hardware Mode (29)5.2.5.2 Software Mode (29)5.3 Analog Outputs (30)5.3.1 Initialization (30)5.3.2 Line-Level Outputs and Filtering (30)5.3.3 Digital Volume Control (32)5.3.3.1 Hardware Mode (32)5.3.3.2 Software Mode (32)5.3.4 De-Emphasis Filter (32)5.4 System Clocking (33)5.4.1 Hardware Mode (33)5.4.2 Software Mode (33)5.5 CODEC Digital Interface (33)5.5.1 TDM (33)5.5.2 I/O Channel Allocation (34)5.6 AUX Port Digital Interface Formats (34)5.6.1 Hardware Mode (34)5.6.2 Software Mode (34)5.6.3 I²S (34)5.6.4 Left-Justified (35)5.7 Control Port Description and Timing (35)5.7.1 SPI Mode (35)5.7.2 I²C Mode (36)5.8 Recommended Power-Up Sequence (37)5.8.1 Hardware Mode (37)5.8.2 Software Mode (38)5.9 Reset and Power-Up (38)5.10 Power Supply, Grounding, and PCB Layout (38)6. REGISTER QUICK REFERENCE (39)7. REGISTER DESCRIPTION (41)7.1 Memory Address Pointer (MAP) (41)7.1.1 Increment (INCR) (41)7.1.2 Memory Address Pointer (MAP[6:0]) (41)7.2 Chip I.D. and Revision Register (Address 01h) (Read Only) (41)7.2.1 Chip I.D. (CHIP_ID[3:0]) (41)7.2.2 Chip Revision (REV_ID[3:0]) (41)7.3 Power Control (Address 02h) (42)7.3.1 Power Down ADC Pairs (PDN_ADCX) (42)7.3.2 Power Down DAC Pairs (PDN_DACX) (42)7.3.3 Power Down (PDN) (42)7.4 Functional Mode (Address 03h) (43)7.4.1 MCLK Frequency (MFREQ[2:0]) (43)7.5 Miscellaneous Control (Address 04h) (43)7.5.1 Freeze Controls (FREEZE) (43)7.5.2 Auxiliary Digital Interface Format (AUX_DIF) (43)7.6 ADC Control & DAC De-Emphasis (Address 05h) (44)7.6.1 ADC1-2 High-Pass Filter Freeze (ADC1-2_HPF FREEZE) (44)7.6.2 ADC3 High Pass Filter Freeze (ADC3_HPF FREEZE) (44)7.6.3 DAC De-Emphasis Control (DAC_DEM) (44)7.6.4 ADC1 Single-Ended Mode (ADC1 SINGLE) (44)7.6.5 ADC2 Single-Ended Mode (ADC2 SINGLE) (44)7.6.6 ADC3 Single-Ended Mode (ADC3 SINGLE) (45)7.6.7 Analog Input Ch. 5 Multiplexer (AIN5_MUX) (45)7.6.8 Analog Input Ch. 6 Multiplexer (AIN6_MUX) (45)7.7 Transition Control (Address 06h) (45)7.7.1 Single Volume Control (DAC_SNGVOL, ADC_SNGVOL) (45)7.7.2 Soft Ramp and Zero Cross Control (ADC_SZC[1:0], DAC_SZC[1:0]) (46)7.7.3 Auto-Mute (AMUTE) (46)7.7.4 Mute ADC Serial Port (MUTE ADC_SP) (47)7.8 DAC Channel Mute (Address 07h) (47)7.8.1 Independent Channel Mute (AOUTX_MUTE) (47)7.9 AOUTX Volume Control (Addresses 08h- 0Fh) (47)7.9.1 Volume Control (AOUTX_VOL[7:0]) (47)7.10 DAC Channel Invert (Address 10h) (48)7.10.1 Invert Signal Polarity (INV_AOUTX) (48)7.11 AINX Volume Control (Address 11h-16h) (48)7.11.1 AINX Volume Control (AINX_VOL[7:0]) (48)7.12 ADC Channel Invert (Address 17h) (49)7.12.1 Invert Signal Polarity (INV_AINX) (49)7.13 Status (Address 19h) (Read Only) (49)7.13.1 CLOCK ERROR (CLK ERROR) (49)7.13.2 ADC Overflow (ADCX_OVFL) (49)7.14 Status Mask (Address 1Ah) (49)8. EXTERNAL FILTERS (50)8.1 ADC Input Filter (50)8.1.1 Passive Input Filter (51)8.1.2 Passive Input Filter w/Attenuation (52)9. ADC FILTER PLOTS (54)10. DAC FILTER PLOTS (56)11. PARAMETER DEFINITIONS (58)12. REFERENCES (59)13. PACKAGE INFORMATION (60)13.1 Thermal Characteristics (60)14. ORDERING INFORMATION (61)15. REVISION HISTORY (61)LIST OF FIGURESFigure 1.Typical Connection Diagram (Software Mode) (11)Figure 2.Typical Connection Diagram (Hardware Mode) (12)Figure 3.Output Test Circuit for Maximum Load (19)Figure 4.Maximum Loading (19)Figure 5.TDM Serial Audio Interface Timing (21)Figure 6.Serial Audio Interface Slave Mode Timing (22)Figure 7.Control Port Timing - I²C Format (23)Figure 8.Control Port Timing - SPI Format (24)Figure 9.Full-Scale Input (28)Figure 10.ADC3 Input Topology (28)Figure 11.Audio Output Initialization Flow Chart (31)Figure 12.Full-Scale Output (32)Figure 13.De-Emphasis Curve (33)Figure 14.TDM Serial Audio Format (34)Figure 15.AUX I²S Format (34)Figure 16.AUX Left-Justified Format (35)Figure 17.Control Port Timing in SPI Mode (36)Figure 18.Control Port Timing, I²C Write (36)Figure 19.Control Port Timing, I²C Read (37)Figure 20.Single to Differential Active Input Filter (50)Figure 21.Single-Ended Active Input Filter (50)Figure 22.Passive Input Filter (51)Figure 23.Passive Input Filter w/Attenuation (52)Figure 24.Active Analog Output Filter (53)Figure 25.Passive Analog Output Filter (53)Figure 26.SSM Stopband Rejection (54)Figure 27.SSM Transition Band (54)Figure 28.SSM Transition Band (Detail) (54)Figure 29.SSM Passband Ripple (54)Figure 30.DSM Stopband Rejection (54)Figure 31.DSM Transition Band (54)Figure 32.DSM Transition Band (Detail) (55)Figure 33.DSM Passband Ripple (55)Figure 34.SSM Stopband Rejection (56)Figure 35.SSM Transition Band (56)Figure 36.SSM Transition Band (detail) (56)Figure 37.SSM Passband Ripple (56)Figure 38.DSM Stopband Rejection (56)Figure 39.DSM Transition Band (56)Figure 40.DSM Transition Band (detail) (57)Figure 41.DSM Passband Ripple (57)Figure 42.QSM Stopband Rejection (57)Figure 44.QSM Transition Band (detail) (57)Figure 45.QSM Passband Ripple (57)LIST OF TABLESTable 1. I/O Power Rails (8)Table 2. Hardware Configurable Settings (26)Table 3. AIN5 Analog Input Selection (29)Table 4. AIN6 Analog Input Selection (29)Table 5. MCLK Frequency Settings (33)Table 6. Serial Audio Interface Channel Allocations (34)Table 7. MCLK Frequency Settings (43)Table 8. Example AOUT Volume Settings (47)Table 9. Example AIN Volume Settings (48)1.PIN DESCRIPTIONS - SOFTWARE MODEPin Name#Pin DescriptionSCL/CCLK1Serial Control Port Clock (Input) - Serial clock for the control port interface.SDA/CDOUT2Serial Control Data I/O (Input/Output) - Input/Output for I²C data. Output for SPI data.AD0/CS3Address Bit [0]/ Chip Select (Input) - Chip address bit in I²C Mode. Control signal used to select the chip in SPI Mode.AD1/CDIN4Address Bit [1]/ SPI Data Input (Input) - Chip address bit in I²C Mode. Input for SPI data.RST5Reset (Input) - The device enters a low-power mode and all internal registers are reset to their default settings when low.VLC6Control Port Power (Input) - Determines the required signal level for the control port interface. See “Digital I/O Pin Characteristics” on page8.FS7Frame Sync (Input) - Signals the start of a new TDM frame in the TDM digital interface format. VD8Digital Power (Input) - Positive power supply for the digital section.DGND9,18Digital Ground (Input) -VLS10Serial Port Interface Power (Input) - Determines the required signal level for the serial port inter-faces. See “Digital I/O Pin Characteristics” on page8.SCLK11Serial Clock(Input) - Serial clock for the serial audio interface. Input frequency must be 256 x Fs. MCLK12Master Clock (Input) - Clock source for the delta-sigma modulators and digital filters.ADC_SDOUT13Serial Audio Data Output (Output) - TDM output for two’s complement serial audio data.DAC_SDIN14DAC Serial Audio Data Input (Input) - TDM Input for two’s complement serial audio data.AUX_LRCK15Auxiliary Left/Right Clock (Output) - Determines which channel, Left or Right, is currently active on the Auxiliary serial audio data line.AUX_SCLK16Auxiliary Serial Clock(Output) - Serial clock for the Auxiliary serial audio interface.AUX_SDIN17Auxiliary Serial Input (Input) - The 42438 provides an additional serial input for two’s comple-ment serial audio data.AOUT1 +,-AOUT2 +,-AOUT3 +,-AOUT4 +,-AOUT5 +,-AOUT6 +,-AOUT7 +,-AOUT8 +,-20,1921,2224,2325,2628,2729,3031,3233,34Differential Analog Output (Output) - The full-scale differential analog output level is specified in the Analog Characteristics specification table. Each positive leg of the differential outputs may also be used single-ended.AGND35,48Analog Ground (Input) - Ground reference for the analog section.VQ36Quiescent Voltage (Output) - Filter connection for internal quiescent reference voltage. VA37,46Analog Power (Input) - Positive power supply for the analog section.AIN1 +,-AIN2 +,-AIN3 +,-AIN4 +,-AIN5 +,-AIN6 +,-39,3841,4043,4245,4450,4952,51Differential Analog Input (Input) - Signals are presented differentially to the delta-sigma modula-tors. The full-scale input level is specified in the Analog Characteristics specification table. Single-ended inputs may be applied to the positive terminals when the ADCx SINGLE bit is enabled.Once in Single-Ended Mode, the negative terminal of AIN1-AIN4 must be externally driven tocommon mode. See below for a description of AIN5-AIN6 in Single-Ended Mode.AIN5 A,B AIN6 A,B 50,4952,51Single-Ended Analog Input (Input) - In Single-Ended Mode, an internal analog mux allowsselection between two channels for both analog inputs AIN5 and AIN6 (see Sections 7.6.6-7.6.8 for details). The unused leg of each input is internally connected to common mode. The full-scale input level is specified in the Analog Characteristics specification table.FILT+47Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling cir-cuits.1.1Digital I/O Pin CharacteristicsVarious pins on the CS42438 are powered from separate power supply rails. The logic level for each input should adhere to the corresponding power rail and should not exceed the maximum ratings.Power Rail Pin NameSW/(HW)I/O Driver ReceiverVLC RST Input- 1.8 V - 5.0 V, CMOS SCL/CCLK(AIN5_MUX)Input- 1.8 V - 5.0 V, CMOS, with HysteresisSDA/CDOUT (AIN6_MUX)Input/Output1.8 V - 5.0 V, CMOS/Open Drain 1.8 V - 5.0 V, CMOS, with HysteresisAD0/CS(MFREQ)Input- 1.8 V - 5.0 V, CMOS AD1/CDIN(ADC3_HPF)Input- 1.8 V - 5.0 V, CMOS VLS MCLK Input- 1.8 V - 5.0 V, CMOS LRCK Input- 1.8 V - 5.0 V, CMOSSCLK Input- 1.8 V - 5.0 V, CMOSADC_SDOUT3 (ADC3_SINGLE)Input/Output1.8 V - 5.0 V, CMOS-DAC_SDIN Input- 1.8 V - 5.0 V, CMOS AUX_LRCK Output 1.8 V - 5.0 V, CMOS-AUX_SCLK Output 1.8 V - 5.0 V, CMOS-AUX_SDIN Input- 1.8 V - 5.0 V, CMOSTable 1. I/O Power Rails2.Pin Name#Pin DescriptionAIN5_MUX AIN6_MUX 12Analog Input Multiplexer (Input) - Allows selection between the A and B single-ended inputs of ADC3.MFREQ3MCLK Frequency (Input) - Sets the required frequency range of the input Master Clock.ADC3_HPF4ADC3 High-Pass Filter Freeze (Input) - When this pin is driven high, the internal high-pass filter will be disabled for ADC3.The current DC offset value will be frozen and continue to be subtractedfrom the conversion result.RST5Reset (Input) - The device enters a low-power mode and all internal registers are reset to their default settings when low.VLC6Control Port Power (Input) - Determines the required signal level for the control port interface. See “Digital I/O Pin Characteristics” on page8.FS7Frame Sync (Input) - Signals the start of a new TDM frame in the TDM digital interface format. VD8Digital Power (Input) - Positive power supply for the digital section.DGND9,18Digital Ground (Input) - Ground reference for the digital section.VLS10Serial Port Interface Power (Input) - Determines the required signal level for the serial port inter-faces. See “Digital I/O Pin Characteristics” on page8.SCLK11Serial Clock(Input) - Serial clock for the serial audio interface. Input frequency must be 256 x Fs. MCLK12Master Clock (Input) - Clock source for the delta-sigma modulators and digital filters.ADC_SDOUT13Serial Audio Data Output (Output) - TDM output for two’s complement serial audio data.DAC_SDIN14DAC Serial Audio Data Input (Input) - TDM Input for two’s complement serial audio data.AUX_LRCK15Auxiliary Left/Right Clock (Output) - Determines which channel, Left or Right, is currently active on the Auxiliary serial audio data line.AUX_SCLK16Auxiliary Serial Clock(Output) - Serial clock for the Auxiliary serial audio interface.AUX_SDIN17Auxiliary Serial Input (Input) - The 42438 provides an additional serial input for two’s comple-ment serial audio data.AOUT1 +,-AOUT2 +,-AOUT3 +,-AOUT4 +,-AOUT5 +,-AOUT6 +,-AOUT7 +,-AOUT8 +,-20,1921,2224,2325,2628,2729,3032,31,33,34Differential Analog Output (Output) - The full-scale differential analog output level is specified in the Analog Characteristics specification table. Each positive leg of the differential outputs mayalso be used single-ended.AGND35,48Analog Ground (Input) - Ground reference for the analog section.VQ36Quiescent Voltage (Output) - Filter connection for internal quiescent reference voltage. VA37,46Analog Power (Input) - Positive power supply for the analog section.AIN1 +,-AIN2 +,-AIN3 +,-AIN4 +,-AIN5 +,-AIN6 +,-39,3841,4043,4245,4450,4952,51Differential Analog Input (Input) - Signals are presented differentially to the delta-sigma modula-tors. The full-scale input level is specified in the Analog Characteristics specification table. Single-ended inputs may be applied to the positive terminals when the ADCx SINGLE bit is enabled.Once in Single-Ended Mode, the negative terminal of AIN1-AIN4 must be externally driven tocommon mode. See below for a description of AIN5-AIN6 in Single-Ended Mode.AIN5 A,B AIN6 A,B 50,4952,51Single-Ended Analog Input (Input) - In Single-Ended Mode, an internal analog mux allowsselection between two channels for both analog inputs AIN5 and AIN6 (see Sections 7.6.6-7.6.8 for details). The unused leg of each input is internally connected to common mode. The full-scale input level is specified in the Analog Characteristics specification table.FILT+47Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling cir-cuits.3.TYPICAL CONNECTION DIAGRAMSFigure 1. Typical Connection Diagram (Software Mode)Figure 2. Typical Connection Diagram (Hardware Mode)4.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS(AGND=DGND=0 V, all voltages with respect to ground.)ABSOLUTE MAXIMUM RATINGS(AGND = DGND = 0 V; all voltages with respect to ground.)WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.Notes:1.Typical Analog input/output performance will slightly degrade at VA = 3.3 V.2.The ADC_SDOUT may not meet timing requirements in Double-Speed Mode.3.Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not causeSCR latch-up.4.The maximum over/under voltage is limited by the input current.ParametersSymbol MinMax Units DC Power Supply Analog (Note 1)VA 3.14 5.25V Digital VD 3.14 3.47V Serial Audio Interface (Note 2)VLS 1.71 5.25V Control Port Interface VLC 1.71 5.25V Ambient TemperatureCommercial -CMZAutomotive -DMZT A-10-40+70+105°C °CParametersSymbol Min Max Units DC Power SupplyAnalogDigitalSerial Port Interface Control Port InterfaceVA VD VLS VLC -0.3-0.3-0.3-0.3 6.06.06.06.0V V V V Input Current(Note 3)I in -±10mA Analog Input Voltage (Note 4)V IN AGND-0.7VA+0.7V Digital Input Voltage Serial Port Interface (Note 4)Control Port InterfaceV IND-S V IND-C -0.3-0.3VLS+ 0.4VLC+ 0.4V V Ambient Operating Temperature (power applied)T A -50+125°C Storage TemperatureT stg-65+150°C(Test Conditions (unless otherwise specified): T A=-10to+70°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale input sine wave: 1 kHz through the active input filter in Figure 20 on page 50 and Figure 21 on page 50; Measurement Bandwidth is 10Hz to 20kHz.)Differential Single-EndedParameter Min Typ Max Min Typ Max Unit Fs=48 kHz, 96 kHzDynamic Range A-weightedunweighted40 kHz bandwidth unweighted 9996-10510299---96931029996---dBdBdBTotal Harmonic Distortion + Noise -1dB (Note 5) -20dB-60dB40 kHz bandwidth -1 dB -----98-82-42-90-92--------95-79-39-90-89---dBdBdBdBADC1-3 Interchannel Isolation-90--90-dB ADC3 MUX Interchannel Isolation-90--90-dB DC AccuracyInterchannel Gain Mismatch-0.1--0.1-dB Gain Drift-±100--±100-ppm/°C Analog InputFull-Scale Input Voltage 1.06*VA 1.12*VA 1.18*VA0.53*VA0.56*VA0.59*VA Vpp Differential Input Impedance (Notes 6 & 8)232932kΩSingle-Ended Input Impedance(Notes 7 & 8)---232932kΩCommon Mode Rejection Ratio (CMRR)-82----dB(Test Conditions (unless otherwise specified): T A =-40 to +85°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale input sine wave: 1 kHz through the active input filter in Figure 20 on page 50 and Figure 21 on page 50; Measurement Bandwidth is 10Hz to 20kHz.)Notes:5.Referred to the typical full-scale voltage.6.Measured between AINx+ and AINx-.7.Measured between AINxx and AGND.8.The input impedance scales inversely proportionate to the sample rate of the ADC modulatorDifferentialSingle-Ended ParameterMin Typ MaxMin Typ MaxUnitFs=48 kHz, 96 kHz Dynamic RangeA-weighted unweighted 40 kHz bandwidth unweighted 9794-10510299---9491-1029996---dB dBdBTotal Harmonic Distortion + Noise -1dB(Note 5) -20dB-60dB40 kHz bandwidth -1 dB-----98-82-42-87-90--------95-79-39-87-87---dB dB dB dB ADC1-3 Interchannel Isolation -90--90-dB ADC3 MUX Interchannel Isolation -85--85-dB DC AccuracyInterchannel Gain Mismatch -0.1--0.1-dB Gain Drift -±100--±100-ppm/°C Analog InputFull-Scale Input Voltage 1.04*VA 1.12*VA 1.20*VA 0.52*VA 0.56*VA 0.60*VA Vpp Differential Input Impedance (Notes 6 & 8)232932k ΩSingle-Ended Input Impedance(Notes 7 & 8)---232932k ΩCommon Mode Rejection Ratio (CMRR)-82----dBADC DIGITAL FILTER CHARACTERISTICSNotes:9.Filter response is guaranteed by design.10.Response is clock-dependent and will scale with Fs. Note that the response plots (Figures 26to 33) havebeen normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.Parameter (Notes 9, 10)MinTypMaxUnitSingle-Speed Mode (Note 10)Passband (Frequency Response) to -0.1 dB corner0-0.4896Fs Passband Ripple --0.08dB Stopband0.5688--Fs Stopband Attenuation 70--dB Total Group Delay-12/Fs-sDouble-Speed Mode (Note 10)Passband (Frequency Response) to -0.1 dB corner0-0.4896Fs Passband Ripple --0.16dB Stopband0.5604--Fs Stopband Attenuation 69--dB Total Group Delay-9/Fs-sHigh-Pass Filter Characteristics Frequency Response -3.0 dB -0.13 dB -120--Hz Hz Phase Deviation @ 20Hz-10-Deg Passband Ripple --0dB Filter Settling Time -105/Fss(Test Conditions (unless otherwise specified): T A=-10 to +70°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale 997 Hz output sine wave (see Note 12) into passive filter in Figure 26 on page 54 and active filter in Fig-ure 26 on page 54; Measurement Bandwidth is 10Hz to 20kHz.)ParameterDifferentialMin Typ MaxSingle-EndedMin Typ Max UnitFs = 48 kHz, 96 kHz, 192 kHz Dynamic Range18 to 24-Bit A-weightedunweighted 16-Bit A-weightedunweighted 10299--1081059996----9996--1051029693----dBdBdBdBTotal Harmonic Distortion + Noise18 to 24-Bit0 dB-20 dB-60 dB 16-Bit0 dB-20 dB-60 dB -------98-85-45-93-76-36-92-----------95-82-42-90-73-33-89-----dBdBdBdBdBdBInterchannel Isolation (1 kHz)-100--100-dB Analog OutputFull-Scale Output 1.235•VA 1.300•VA 1.365•VA0.618•VA0.650•VA0.683•VA Vpp Interchannel Gain Mismatch-0.10.25-0.10.25dB Gain Drift-±100--±100-ppm/°C Output Impedance-100--100-ΩDC Current draw from an AOUT pin(Note 11)--10--10μA AC-Load Resistance (R L)(Note 13)3--3--kΩLoad Capacitance (C L)(Note 13)--100--100pF(Test Conditions (unless otherwise specified): T A =-40to +85°C; VD = VLS = VLC = 3.3V±5%, VA = 5V±5%; Full-scale 997 Hz output sine wave (see Note 12) in Figure 26 on page 54 and Figure 26 on page 54; Measure-ment Bandwidth is 10Hz to 20kHz.)Notes:11.Guaranteed by design. The DC current draw represents the allowed current draw from the AOUT pindue to typical leakage through the electrolytic DC-blocking capacitors.12.One-half LSB of triangular PDF dither is added to data.13.Guaranteed by design. See Figure 3. R L and C L reflect the recommended minimum resistance andmaximum capacitance required for the internal op-amp's stability and signal integrity. In this circuit to-pology, C L will effectively move the dominant pole of the two-pole amp in the output stage. Increasing this value beyond the recommended 100 pF can cause the internal op-amp to become unstable. See “External Filters” on page 50 for a recommended output filter.ParameterDifferentialMin Typ MaxSingle-EndedMin Typ MaxUnitFs = 48 kHz, 96 kHz, 192 kHz Dynamic Range18 to 24-Bit A-weightedunweighted16-Bit A-weightedunweighted10097--1081059996----9794--1051029693----dB dB dB dB Total Harmonic Distortion + Noise18 to 24-Bit 0 dB-20 dB-60 dB16-Bit 0 dB-20 dB-60 dB-------98-85-45-93-76-36-90------------95-82-42-90-73-33-87-----dB dB dB dB dB dB Interchannel Isolation (1 kHz)-100--100-dBAnalog Output Full-Scale Output 1.210•VA 1.300•VA 1.392•VA 0.605•VA 0.650•VA 0.696•VA Vpp Interchannel Gain Mismatch -0.10.25-0.10.25dB Gain Drift -±100--±100-ppm/°C Output Impedance -100--100-ΩDC Current draw from an AOUT pin (Note 11)--10--10μAAC-Load Resistance (R L ) (Note 13)3--3--k ΩLoad Capacitance (C L )(Note 13)--100--100pFFigure 3. Output Test Circuit for Maximum Load Figure 4. Maximum LoadingCOMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSENotes:14.Response is clock-dependent and will scale with Fs. Note that the response plots (Figures 34to 45) havebeen normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.15.Single- and Double-Speed Mode Measurement Bandwidth is from Stopband to 3 Fs.Quad-Speed Mode Measurement Bandwidth is from Stopband to 1.34 Fs.16.De-emphasis is only available in Single-Speed Mode.Parameter (Notes 9, 14)MinTypMaxUnitSingle-Speed ModePassband (Frequency Response)to -0.05dB corner to -3dB corner00--0.47800.4996Fs Fs Frequency Response 10Hz to 20kHz -0.2-+0.08dB StopBand0.5465--Fs StopBand Attenuation (Note 15)50--dB Group Delay-10/Fs -sDe-emphasis Error (Note 16)Fs = 32kHz Fs = 44.1 kHz Fs = 48 kHz------+1.5/+0+0.05/-0.25-0.2/-0.4dB dB dBDouble-Speed ModePassband (Frequency Response)to -0.1dB corner to -3dB corner00--0.46500.4982Fs Fs Frequency Response 10Hz to 20kHz -0.2-+0.7dB StopBand0.5770--Fs StopBand Attenuation (Note 15)55--dB Group Delay -5/Fs-sQuad-Speed ModePassband (Frequency Response)to -0.1dB corner to -3dB corner00--0.3970.476Fs Fs Frequency Response 10Hz to 20kHz -0.2-+0.05dB StopBand0.7--Fs StopBand Attenuation (Note 15)51--dB Group Delay - 2.5/Fs-sSWITCHING SPECIFICATIONS - ADC/DAC PORT(Inputs: Logic 0 = DGND, Logic 1 = VLS, ADC_SDOUT C LOAD = 15 pF.)Notes:17.After powering up the CS42438, RST should be held low after the power supplies and clocks are settled.18.See Table 7 on page 43 for suggested MCLK frequencies.19.VLS is limited to nominal 2.5 V to 5.0V operation only.20.ADC does not meet timing specification for Quad-Speed Mode.Parameters Symbol Min Max UnitsSlave ModeRST pin Low Pulse Width(Note 17)1-ms MCLK Frequency 0.51250MHz MCLK Duty Cycle(Note 18)4555%Input Sample Rate (FS pin)Single-Speed ModeDouble-Speed Mode (Note 19)Quad-Speed Mode (Note 20)F s F s F s 45010050100200kHz kHz kHz SCLK Duty Cycle 4555%SCLK High Time t sckh 8-ns SCLK Low Timet sckl 8-ns FS Rising Edge to SCLK Rising Edge t fss 5-ns SCLK Rising Edge to FS Falling Edget fsh 16-ns DAC_SDIN Setup Time Before SCLK Rising Edge t ds 3-ns DAC_SDIN Hold Time After SCLK Rising Edge t dh 5-ns DAC_SDIN Hold Time After SCLK Rising Edge t dh15-ns ADC_SDOUT Hold Time After SCLK Rising Edge t dh210-ns ADC_SDOUT Valid Before SCLK Rising Edget dval15-nsFigure 5. TDM Serial Audio Interface Timing。

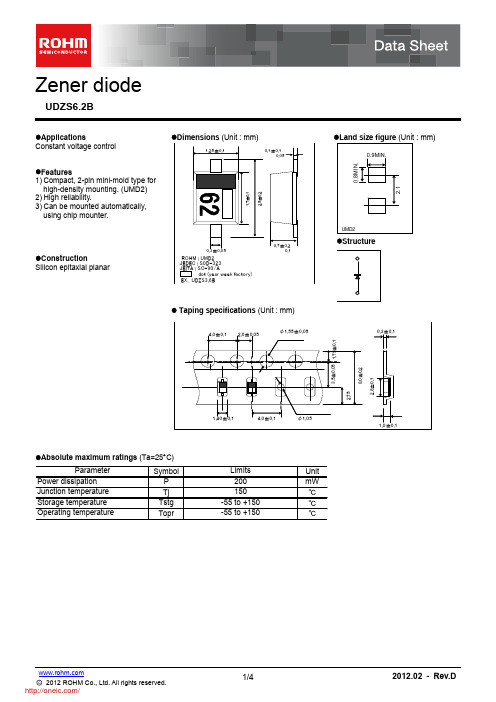

UDZSTE-176.2B;中文规格书,Datasheet资料

UDZS6.2B

Applications Constant voltage control Features 1) Compact, 2-pin mini-mold type for high-density mounting. (UMD2) 2) High reliability. 3) Can be mounted automatically, using chip mounter. Dimensions (Unit : mm)

VR(V) 1.0 1.0 1.0 1.0 1.5 2.5 3.0 3.5 4.0 5.0 6.0 7.0 8.0 9.0 10.0 11.0 12.0 13.0 15.0 17.0 19.0 21.0 23.0 25.0 27.0

Type No. TYPE UDZS 3.6B UDZS 3.9B UDZS 4.3B UDZS 4.7B UDZS 5.1B UDZS 5.6B UDZS 6.2B UDZS 6.8B UDZS 7.5B UDZS 8.2B UDZS 9.1B UDZS 10B UDZS 11B

0.1 0.001

0.01

0.1

1

10

100

TIME:t(ms) PRSM-TIME CHARACTERISTICS 1000 Rth(j-a)

100

Rth(j-c)

10

Mounted on epoxy board IM=10mA IF=100mA

1

1ms time

300us

0.1 0.001

0.01

/

2.1

UDZS6.2B

Electrical characteristics (Ta=25C)

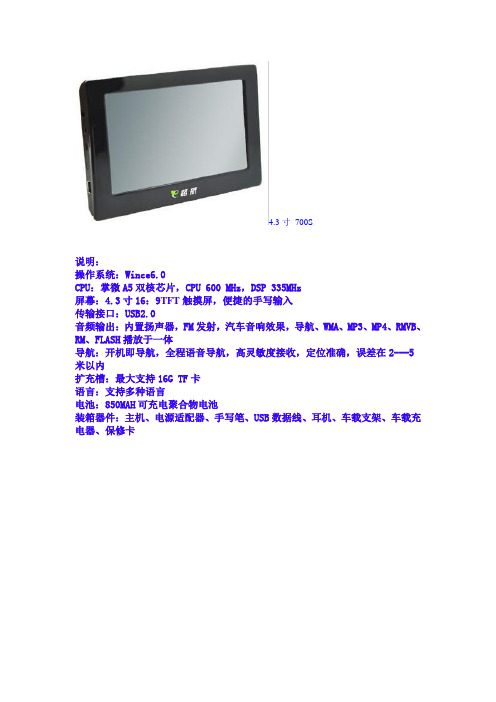

4.3 、5.0 、7.0寸导航参数

4.3寸700S说明:操作系统:Wince6.0CPU:掌微A5双核芯片,CPU 600 MHz,DSP 335MHz屏幕:4.3寸16:9TFT触摸屏,便捷的手写输入传输接口:USB2.0音频输出:内置扬声器,FM发射,汽车音响效果,导航、WMA、MP3、MP4、RMVB、RM、FLASH播放于一体导航:开机即导航,全程语音导航,高灵敏度接收,定位准确,误差在2---5米以内扩充槽:最大支持16G TF卡语言:支持多种语言电池:850MAH可充电聚合物电池装箱器件:主机、电源适配器、手写笔、USB数据线、耳机、车载支架、车载充电器、保修卡新增主要功能特色:1、主界面可以支持滑动动画翻页;2、提示的窗口可以拖动;3、小图标FM和喇叭音量调节分开,点喇叭小图标可进入音量设置;4、支持内存释放功能;5、语言增加繁体,变为中文简体-中文繁体-英文;6、系统设置下系统资源,支持看到内核版本号;7、已设置的时间关机后,可以保存。

8、内置存储空间为4G;9、TF卡支持16G,针对某些卡可以支持32G;10、支持RM视频格式;11、支持开机画面在系统设置中直接升级更改;12、原文件管理更改为GPS路径设置。

使用及配件注意事项:1、车充和座充请随机配套的,确保USB端口第4引脚悬空,不要和5V短接!2、地图请用能支持WinCE6.0平台的,端口和之前的不同,端口请设置为:COM1,波特率只要是标准的就OK。

3、USB连接线,请务必确保是专用USB连接线,要求编织屏蔽地,内阻小于0.4欧!5.0寸E900T型号和功能对应关系:E900T:带FM + 新固定电子狗预警功能功能说明:操作系统:Wince6.0CPU:掌微A5双核芯片,CPU 600 MHz,DSP 335MHz屏幕:5寸16:9高清TFT屏和手写触摸屏,便捷的手写输入传输接口:USB2.0音频输出:内置扬声器,FM发射,汽车音响效果,导航、WMA、MP3、MP4、RMVB、RM、FLASH播放于一体导航:开机即导航,全程语音导航,高灵敏度接收,定位准确,误差在2---5米以内扩充槽:最大支持16G TF卡语言:支持多种语言电池:1200MAH可充电聚合物电池机器尺寸:135*88.6*12.8 mm装箱器件:主机、电源适配器、手写笔、USB数据线、耳机、车载支架、车载充电器、保修卡新增主要功能特色:1、支持后台电子狗功能,任何功能界面下均能及时提醒固定预警点;2、提示的窗口可以拖动;3、小图标FM和喇叭音量调节分开,点喇叭小图标可进入音量设置;4、语言增加繁体,变为中文简体-中文繁体-英文;5、系统设置下系统资源,支持看到内核版本号;6、已设置的时间关机后,可以保存。

VS1053B中文资料应用

• EarSpeaker 空间效果注 2 处理

• 低音和高音控制 • 只用一个单独的 12..13MHz 时钟运作 • 也可以使用一个 24..26MHz 时钟运作 • 内建 PLL 时钟乘法器 • 低功耗运作 • 芯片内建高质量和通道间无相位误差的立体声 DAC • 过零交叉注 3(Zero‐cross)侦测和平滑的音量调整 • 立体声耳机驱动器可以驱动一个 30Ω 的负载 • 安静的电源通断功能 • 可扩展外部 DAC 的 I2S 接口 • 分离的模拟、数字、IO 供电电源 • 供用户代码和数据使用的片内 RAM • 用于控制和数据的串行接口 • 可以作为从模式的辅助处理器使用 • 特殊应用可使用 SPI FLASH 存储器引导 • 可用于调试的 UART 接口 • 可用软件增加新功能和提供最多 8 个 GPIO • 符合 RoHS 无铅标准的封装(绿色)

4.2 推荐工作值 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.3 模拟电路特性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

UDA1341TS中文资料

UDA1341TS学习wince音频驱动开发 2009-04-02 14:02:58 阅读48 评论0 字号:大中小7. 功能描述(FUNCTIONAL DESCRIPTION)7.1 系统时钟(System clock)UDA1341TS 只能使用从片模式,这就意味着在所有应用中系统设备必须给它提供系统时钟.系统时钟频率是可选择的,可为了256fs,384fs或512fs.系统时钟必须对数字接口信号锁定频率(The system clock must be locked in frequency to the digital interface signals)7.2 针脚兼容性(Pin compatibility)UDA1341TS部分针脚与UDA1340M和UDA1344TS兼容,印刷电路板从UDA1340M升级到UDA1341TS比较简单.与UDA1340M兼容的针脚在FIG.3中标明.7.3 模拟前端(Analog front end)UDA1341TS的模拟前端由两个立体声模数转换器组成,每个转换器有两个通道,通道2有一个可编程增益放大器(PGA),PGA被用来预放大输入通道2的麦克风信号.输入通道1有一个可选择的0或6dB的增益级,通过L3-接口来控制.在这种方式下,1V或2V(有效值)的输入信号(如从一个CD源中输出)可以在输入通道1上串联一个12千欧的外部电阻来支持.下表给出了它的应用模式.使用输入增益级的应用模式--------------------------------------------------------------------------------------------------------电阻(12千欧) 输入增益开关最大输入电压使用0 dB 2V(有效值)输入信号 ps:如果这里没有必要支持2V输入信号,外接电阻就不应被使用使用6 dB 1V(有效值)输入信号不使用 0 dB 1V(有效值)输入信号不使用 6 dB 0.5V(有效值)输入信号---------------------------------------------------------------------------------------------------------7.4 可编程增益放大器(Programmable Gain Amplifier(PGA))PGA可以通过L3接口设置为-3,0,3,9,15,21或27dB7.5 模数转换器(Analog-to-Digital Converter(ADC))UDA1341TS的立体声模数转换器由两个三阶增量调制器组成.它们有一个改进的里齐码结构使用不同的开关电容.过取样率为128.7.6 数字自动增益控制(Digital Automatic Gain Control(AGC))当有一个麦克风信号输入到通道2时,输入通道2有一个数字自动增益控制来压缩动态范围.数字AGC可以用L3接口打开.在打开的状态下压缩动态范围.通过L3接口用户可以设置AGC的参数:启动时间,衰减时间和输出电平.当AGC设置为关时,输入通道2的增益可以手工设置.在这种情况下PGA和AGC组合在一起.输入通道2的范围从-3到60.5dB以0.5dB步进.7.7 自动增益控制状态检测(AGC status detection)当自动增益控制的增益级低于8dB时,数字自动增益中的自动增益状态信号变为高,这个信号可以被用来通过L3接口给PGA一个新的增益设置,或者驱动一个LED.7.8 数字混音器(digital Mixer)两个立体声模数转换器(包括AGC)有四种模式:*只使用ADC1(用做线路输入);输入通道2关闭*只使用ADC2,包括PGA和数字AGC(用做麦克风输入);输入通道1关闭*ADC1+ADC2混合模式,包括PGA和AGC*ADC1+ADC2 double differential 模式(提升ADC性能)要点:为了防止线路输入间串扰,在double differential模式下不应该有信号应用到麦克风输入.在所有模式下(除了double differential模式)一个参考电压一直在ADC的输入上有效,而在double differential模式下却没有.在混合模式下,通道1和通道2的ADC的输出信号可以经L3接口通过一定系数混合.混合系数的范围从0到负无穷dB以1.5dB步进.7.9 抽取滤波器(Decimation filter(ADC))从128fs开始的抽取可以分两阶段进行.第一个阶段实现3阶sin x/x 特性. (The first stage realizes 3rd order sinx/x characteristic), 以16为基抽取.第二个步骤由3个半带滤波器组成,每一个以2为因子抽取.抽取滤波器特性--------------------------------------------------------------------------------项(ITEM) 条件(CONDITIONS) 值(V ALUE(db))通频带波纹0到0.45fs ±0.05抑制频带 >0.55fs -60动态范围0到0.45fs 108总增益输入通道1;0 dB输入 -1.16--------------------------------------------------------------------------------7.10 过载检测(Overload detection(ADC))过载检测这个名字虽合适但有一点不正确.实际上,它的输出表明输出数据比最大可能的数字变化大-1dB(实际上是-1.16dB).无论何时,在何声道.在这种条件下OVERFL输出被强制为高电平持续至少512fs时钟周期(当fs=44.1 kHZ时为11.6ms).每次过载后超时被复位.7.11 静音(Mute(ADC))在从掉电模式后恢复或打开系统时钟时,引脚DATAO的串行数据输出保持低电平直到从抽取滤波器来的有效数据可用.这个时间取决于是否选择了直流消除滤镜.*直流消除关闭 t=1021/fs; 当fs=44.1kHZ时t=23.2ms*直流消除开启 t=12288/fs;当fs=44.1kHZ时t=279ms7.12 内插滤波器(Interpolation filter(DAC))数字滤波器插值从1fs到128fs用一个级联的递归滤波器和一个有限推进响应滤镜.插值滤镜特性-------------------------------------------------项条件值(dB)通带波纹0到0.45fs ±0.03抑制频带 >0.55fs -50动态范围0到0.45fs 108------------------------------------------------7.13峰值检波器(Peak detector)在再现时,内置了峰值检波器.峰值检测位置可以在声音特征设置之前或之后通过L3-接口来设置.峰值检波器实现成像是一个峰值保持检波器,这就表明最高的音级被保存直到被L3-接口读出.在读出后峰值电平寄存器被复位.7.14 快速静音(Quick mute)一个硬件静音可能通过固定的QMUTE引脚激活.当QMUTE设置为高电平时,输出信号被减弱为0.设置QMUTE为低电平时, 快速静音无效.7.15 噪音整形器(Noise shaper(DAC))三阶噪音整形器运行频率为128fs.它将频带内的量化噪声转换成音频带之上的频率.这种噪音整形技术可以提供高信噪比.噪音整形器输出通过一个DAC流滤波器转换成模拟信号. 7.16 DAC流滤波器(Filter Stream Digital-to-Analog Converter(FSDAC))DAC滤波器是一个半数字重构滤镜,可将噪音整形器的一位数据流转换成模拟电压输出.滤镜系数采取当前源并且合计在运算放大器的虚拟地上.这种方法可以达到很高的信噪比和低时钟抖动敏感.因为DAC的内置滤波功能,所以不需要一个后置滤波器.板上放大器将DAC流滤波器的当前输出转换成一个能驱动线路输入的输出电压信号.7.17 多格式输入/输出接口(Multiple format input/output interface)UDA1341TS 支持下列数据格式:*IIS总线,字长可以达到20bits*最高有效位有效的串行格式,字长可达20位.*最低有效位有效的串行格式,字长为16,18或20位*最高有效位有效的输出和最低有效位有效的16,18,20位输入.左声道和右声道字长是时间多工化的.格式如图FIG4所示UDA1341TS允许双倍速数据检测.在这种情况下,重低音,高音和去加重特性不能被使用.然而,音量控制和软静音仍可控.双倍速检测可以通过L3接口设置.位时钟频率必须小于等于64倍字选频率.7.18 L3接口(L3-interface)信息按照L3格式通过微控制器总线进行传输,在这种格式下有两种不同的操作模式,地址模式和传输模式.地址模式需要通过L3总线选择一个设备并且为数据传输模式定义目的寄存器.数据传输可以有两个方向:输入到UDA1341TS中以编码它的声音处理和系统控制特性,或从UDA1341TS中输出来提供峰值.7.19地址模式地址模式用来选择一个设备为了之后的数据传输,并且定义目的寄存器,地址模式被描述为L3MODE保持低电平并且经过8个L3CLOCK脉冲.伴随着8个数据位.基本时序如图FIG.5所示.(L3CLOCK为低电平时进行同步)数据位7到2表示了一个六位的设备地址,第7位为最高有效位,第2位为最低有效位.UDA1341TS的地址是000101.数据位0到1表示之后传输的数据类型(表4).如果UDA1341TS接收了一个不同的地址命令,它会取消所作的选择BIT1 BIT0 MODE TRANSFER0 0 DATA0 直接编址寄存器:音量,重低音,高音,峰值检测位置,去加重,静音和模式扩展编址寄存器:数字混音器控制,自动增益控制,麦克灵敏度控制,输入增益,自动增益时间常数及输出等级0 1 DATA1 读出峰值(从UDA1341TS读到微控制器)1 0 STATUS 复位,系统时钟频率,数据输入格式,直流滤波器,输入增益开关,输出增益开关极性控制,双倍速和电源控制1 1 未使用7.20 数据传输模式在址址模式下激活的选择仍然有效,直到UDA1341TS接收到一个新的地址指令.数据传输的基本时序本质上与地址模式相同,在FIG6中给出 (L3MODE保持高电平,L3CLOCK高电平同步),注意"L3DATA写"指出数据传输从微控制器到UDA1341TS并且"L3DATA峰值读" 指出数据以相反的方向传输.最大的输入时钟和数据传输速率为64fs.所有的传输都是基于8位字节,数据在接收到一个字节的第八位后存储到UDA1341TS中.多字节传输可参照Fig.77.21 编码音频处理及其它特性音频处理和其它特性值存储在独立的寄存器中,通过选择传输的数据类型来对寄存器进行第一道选取,这通过地址模式中的第0位和第1位来完成,第二道选取由数据字节的2或3个最高有效位(第7-6位或7-5位)完成.数据字节中的其它位(BIT5-0,BIT4-0)表示要被存放到已选寄存器的值.对于UDA1341TS 来说可以选取以下模式.*STATUS在这种模式下,复位,系统时钟频率,数据输入格式,直流滤波器,输入增益开关,输出增益开关,极性控制,双倍速和电源控制等特性可以被设置.*DATA0在这种模式下有两种地址模式:直接编址模式和扩展编址模式.直接编址模式使用数据字节的两个最高有效位.在这种地址模式下,音量,重底音,高音,峰值位置, 去加重,静音,模式等特性可以被直接控制.扩展编址模式被用来控制数字混音器,自动增益控制,麦克灵敏度,输入增益,自动增益控制时间系数,自动增益控制输出等级等特性,一个扩展地址可以通过EA寄存器(3位)来设置,扩展寄存器中的值可以通过写数据到ED寄存器(5位)来设置.*DATA1在这种模式下,检测到的峰值可以被读出.Table 5 默认设置符号(SYMBOL) 特性(FEATURE) 设置或值(SETTING OR V ALUE)******Status******OGS 输出增益开关(Output gain switch) 0 dBIGS 输入增益开关(Input gain switch) 0 dBPAD 模数转换极性(Polarity of ADC) 不反转(non-inverting)PDA 数模转换极性(Polarity of DAC) 不反转(non-inverting)DS 双倍速(Double speed) 单倍速(single speed)PC 电源控制(Power control ADC and DAC) 开启(on)******直接控制(Direct control)*******VC 音量控制(V olume control) 0 dBBB 重低音(Bass boost) 0 dBTR 高音(Treble) 0 dBPP 峰值检测位置(Peak detection position) 在音调特性之后(after the tone features)DE 去加重(De-emphasis) 无去加重(no de-emphasis)MT 静音(Mute) 不静音(no mute)M 模式开关(Mode switch) 平坦(flat)******扩展地址编码(Extended programming)******MA 混音器增益通道1(Mixer gain channel 1) -6 dBMB 混音器增益通道2(Mixer gain channel 2) -6 dBMS 麦克敏感度(MIC sensitivity) 0 dBMM 混音器模式开关双微分模式?(double differential mode)AG 自动增益控制(AGC control) 关闭自动增益(disable AGC)AT 自动增益控制启动及衰减时间(AGC attack and decay time) 11ms 和100msAL 自动增益控制输出等级(AGC output level) -9 dB FS7.21.1 STATUS 控制'STATUS'类型数据传输BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 | 寄存器选择(REGISTERSELECTED)------------------------------------------------------------------------------------------------------ 0 RST SC1 SC0 IF2 IF1 IF0 DC RST= 复位(reset)SC=系统时钟频率(system clock frequency(2位))IF=数据输入格式(data input format(3位)) DC=直流滤波器(DC-filter)------------------------------------------------------------------------------------------------------- 1 OGS IGS PAD PDA DS PC1 PC0 OGS=输出增益(6dB)开关(output gain switch) IGS=输入增益(6dB)开关(input gain switch)PAD=ADC极性(polarity of ADC)PDA=DAC极性(polarity of DAC)DS=双倍速(double speed)PC=电源控制(power control)(2位)-------------------------------------------------------------------------------------------------------- 7.21.1.1 复位(Reset)1位值,使用默认设置(系统时钟频率除外)初始化L3寄存器.0: 不复位 1: 复位7.21.1.2 系统时钟频率(System clock frequency)两位值,用来选择外部时钟频率.-----------------------------------------SC1 | SC0 | FUNCTION0 0 512fs0 1 384fs1 0 256fs1 1 未使用------------------------------------------7.21.1.3 直流滤波器(DC-filter)一位值用来使能数字直流滤波器0: 不使用 1:使用7.21.1.4 数据输入格式(Data input format)3位值用来选择数据输入格式-------------------------------------------------------------------------------------IF2 IF1 IF0 FUNCTION0 0 0 IIS总线(IIS-BUS)0 0 1 最低有效位对齐的16位(LSB-justified 16 bits)0 1 0 最低有效位对齐的18位(LSB-justified 18 bits)0 1 1 最低有效位对齐的20位(LSB-justified 20 bits)1 0 0 最高有效位对齐(MSB-justified)1 0 1 最低有效位对齐的16位输入和最高有效位对齐的输出(LSB-justified 16 bits input and MSB-justified output)1 1 0 最低有效位对齐的18位输入和最高有效位对齐的输出(LSB-justified 18 bits input and MSB-justified output)1 1 1 最低有效位对齐的20位输入和最高有效位对齐的输出(LSB-justified 20 bits input and MSB-justified output)---------------------------------------------------------------------------------------7.21.1.5 输出增益开关(Output gain switch)一位值用来控制数模转换器输出增益开关0: 0 dB 1: 6 dB7.21.1.6 输入增益开关(Input gain switch)一位值用来控制模数转换器开关0: 0 dB 1: 6 dB7.21.1.7 模数转换器极性(Polarity of ADC)一位值用来控制模数转换器极性.0: 不反转 1: 反转7.21.1.8 数模转换器极性(Polarrity of DAC)一位值用来控制数模转换器极性.0: 不反转 1: 反转7.21.1.9 双倍速(Double speed)一位值用来使能双倍速再现(playback)0: 单倍速 1: 双倍速7.21.1.10 电源控制(Power control)两位值用来禁用数模转换器和/或模数转换器节电模式.--------------------------------------FUNCTIONPC1 PC0ADC DAC--------------------------------------0 0 off off0 1 off on1 0 on off1 1 on on--------------------------------------7.21.2 DATA0 直接控制DATA0类型数据传输( Data transfer of type ‘DATA0’)------------------------------------------------------------------BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 REGISTER SELECTED0 0 VC5 VC4 VC3 VC2 VC1 VC0 VC = 音量控制(volume control (6 bits))0 1 BB3 BB2 BB1 BB0 TR1 TR0 BB = 低音增强(bass boost (4 bits))TR = 高音(treble (2 bits))1 0 PP DE1 DE0 MT M1 M0 PP = 峰值检测位置(peak detection position)DE = 去加重(de-emphasis (2 bits))MT = 静音(mute)M = 模式选择(mode switch (2 bits))1 1 0 0 0 EA2 EA1 EA0 EA=扩展地址(extended address (3 bits))1 1 1 ED4 ED3 ED2 ED1 ED0 ED = 扩展数据(extended data (5 bits))7.21.3 DATA0扩展编程寄存器(DATA0 EXTENDED PROGRAMMING REGISTERS) 扩展控制寄存器(Extended control registers)EA2 EA1 EA0 ED4 ED3 ED2 ED1 ED0 REGISTER SELECTED0 0 0 MA4 MA3 MA2 MA1 MA0 MA=混音器增益通道1(mixer gain channel 1 (5 bits)) 0 0 1 MB4 MB3 MB2 MB1 MB0 MB=混音器增益通道2(mixer gain channel 2 (5 bits)) 0 1 0 MS2 MS1 MS0 MM1 MM0 MS=麦克风敏感度(MIC sensitivity (3 bits))MM=混音器模式(mixer mode (2 bits))1 0 0 AG 0 0 IG1 IG0 AG=自动增益控制(AGC control)IG=输入放大器增益通道2(input amplifier gain channel 2 (2 bits))1 0 1 IG6 IG5 IG4 IG3 IG2 IG=输入放大器增益通道2(input amplifier gain channel 2 (5 bits))1 1 0 AT2 AT1 AT0 AL1 AL0 AT=自动增益控制时间常数(AGC time constant (3 bits))AL=自动增益控制输出电平(AGC output level (2 bits))7.21.4 DATA1 控制(DATA1 CONTROL)'DATA1'数据传输类型BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 读出数据(READ-OUT DATA)PL5 PL4 PL3 PL2 PL1 PL0 峰值电平(peak level value(6 bits))。

UDA1341TSDB中文资料

UDA1341TS

THERMAL CHARACTERISTICS DC CHARACTERISTICS AC CHARACTERISTICS (ANALOG) AC CHARACTERISTICS (DIGITAL) APPLICATION INFORMATION PACKAGE OUTLINE SOLDERING Introduction to soldering surface mount packages Reflow soldering Wave soldering Manual soldering Suitability of surface mount IC packages for wave and reflow soldering methods DATA SHEET STATUS DEFINITIONS DISCLAIMERS

• I2S-bus, MSB-justified and LSB-justified format compatible • Three combinational data formats with MSB data output and LSB 16, 18 or 20 bits data input • 1fs input and output format data rate. 1.3 DAC digital sound processing

• Digital dB-linear volume control (low microcontroller load) • Digital tone control, bass boost and treble • Digital de-emphasis for 32, 44.1 or 48 kHz audio sample frequencies (fs) • Soft mute. 1.4 Advanced audio configuration

AO4459中文资料

AO4459中⽂资料SymbolTyp Max 33406275R θJL 1824Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-Ambient ASteady-State °C/W AO4459AO4459SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.5-1.85-2.5V I D(ON)-30A 3846T J =125°C53685872m ?g FS 11S V SD -0.78-1V I S-3.5A C iss 668830pF C oss 126pF C rss 92pF R g69?Q g (10V)12.716nC Q g (4.5V) 6.4nC Q gs 2nC Q gd 4nC t D(on)7.7ns t r 6.8ns t D(off)20ns t f 10ns t rr 2230ns Q rr15nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.DYNAMIC PARAMETERS Maximum Body-Diode Continuous CurrentGate resistanceV GS =0V, V DS =0V, f=1MHzV GS =0V, V DS =-15V, f=1MHz Input Capacitance Output Capacitance Turn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.5?, R GEN =3?Turn-Off Fall TimeTurn-On DelayTime SWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-6.5Am ?V GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-6.5AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward VoltageI DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-24V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =-6.5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-6.5AReverse Transfer Capacitance I F =-6.5A, dI/dt=100A/µs A: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using < 300µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev0 Sept 2006AO4459AO4459。

UDZ3.3B中文资料

元器件交易网

UDZ Series

Diodes

!Electrical characteristic curves (Ta=25°C)

5.1 5.6

100m

6.2

6.8

8.2 9.1

7.5

15

11

10

12

13

16

18

20

20

10m

1m

ZENER CURRENT : IZ (A)

Product name UDZ 16B UDZ 18B UDZ 20B UDZ 22B UDZ 24B UDZ 27B UDZ 30B UDZ 33B UDZ 36B

Type No. 5 6 7 8 9 A C E F 5 5 5 5 5 5 5 5 5

元器件交易网

UDZ Series

Product name UDZ 5.6B UDZ 6.2B UDZ 6.8B UDZ 7.5B UDZ 8.2B UDZ 9.1B UDZ 10B UDZ 11B UDZ 12B UDZ 13B UDZ 15B

Type No. C E F H J L 0 1 2 3 4 2 2 2 2 2 2 5 5 5 5 5

!Markings (Type No.)

Product name UDZ 2.0B UDZ 2.2B UDZ 2.4B UDZ 2.7B UDZ 3.0B UDZ 3.3B UDZ 3.6B UDZ 3.9B UDZ 4.3B UDZ 4.7B UDZ 5.1B

(Ex.) UDZ 2.0B 0 2

Type No. 0 1 2 3 4 5 6 7 8 9 A 2 2 2 2 2 2 2 2 2 2 2

0.10

Iz=5mA

DWS3-45B中文资料

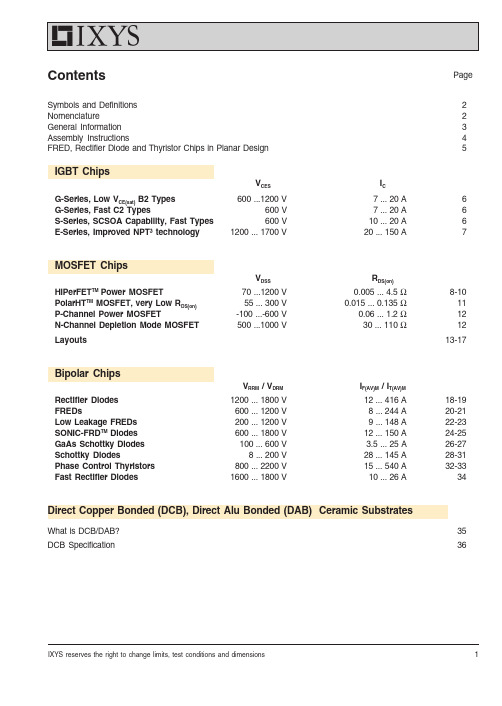

1IXYS reserves the right to change limits, test conditions and dimensions ContentsPage Symbols and Definitions 2Nomenclature2General Information 3A ssembly Instructions4FRED, Rectifier Diode and Thyristor Chips in Planar Design5IGBT ChipsV CESI CG-Series, Low V CE(sat) B2 Types 600 ...1200 V7 ... 20 A 6G-Series, Fast C2 Types600 V 7 ... 20 A 6S-Series, SCSOA Capability, Fast Types 600 V10 ... 20 A 6E-Series, Improved NPT³ technology1200 ... 1700 V20 ... 150 A7MOSFET ChipsV DSSR DS(on)HiPerFET TM Power MOSFET70 ...1200 V 0.005 ... 4.5 Ω8-10PolarHT TM MOSFET, very Low R DS(on)55 ... 300 V 0.015 ... 0.135 Ω11P-Channel Power MOSFET-100 ...-600 V 0.06 ... 1.2 Ω12N-Channel Depletion Mode MOSFET 500 ...1000 V30 ... 110 Ω12Layouts13-17Bipolar ChipsV RRM / V DRMI F(AV)M / I T(AV)M Rectifier Diodes 1200 ... 1800 V 12 ... 416 A 18-19FREDs600 ... 1200 V 8 ... 244 A 20-21Low Leakage FREDs 200 ... 1200 V 9 ... 148 A 22-23SONIC-FRD TM Diodes 600 ... 1800 V 12 ... 150 A 24-25GaAs Schottky Diodes 100 ... 600 V 3.5 ... 25 A 26-27Schottky Diodes8 ... 200 V 28 ... 145 A 28-31Phase Control Thyristors 800 ... 2200 V 15 ... 540 A 32-33Fast Rectifier Diodes1600 ... 1800 V10 ... 26 A34Direct Copper Bonded (DCB), Direct Alu Bonded (DAB) Ceramic SubstratesWhat is DCB/DAB?35DCB Specification362© 2004 IXYS All rights reservedSymbols and DefinitionsC ies Input capacitance of IGBT C iss Input capacitance of MOSFET-di/dt Rate of decrease of forward current I C DC collector current I D Drain currentI FForward current of diodeI F(AV)M Maximum average forward current at specified T h I FSM Peak one cycle surge forward current I GT Gate trigger current I R Reverse currentI RM Maximum peak recovery current I TForward current of thyristorI T(AV)M Maximum average on-state current of a thyristor at specified T hI TSM Maximum surge current of a thyristor R DS(on)Static drain-source on-state resistance R thjc Thermal resistance junction to case r TSlope resistance of a thyristor or diode (for power loss calculations) T case Case temperature T h Heatsink temperaturet fiCurrent fall time with inductive load T j , T (vj)Junction temperatureT jm , T (vj)m Maximum junction temperature t rrReverse recovery time of a diode V CE(sat)Collector-emitter saturation voltage V CES Maximum collector-emitter voltage V DRM Maximum repetitive forward blocking voltage of thyristorV DSS Drain-source break-down voltage V F Forward voltage of diode V R Reverse voltageV RRM Maximum peak reverse voltage of thyristor or diodeV T On-state voltage of thyristorV T0Threshold voltage of thyristors or diodes (for power loss calculation only)Chip and DCB Ceramic Substrates Data book Edition 2004Published by IXYS Semiconductor GmbH Marketing CommunicationsEdisonstraße 15, D-68623 Lampertheim© IXYS Semiconductor GmbH All Rights reserved As far as patents or other rights of third parties are concerned, liability is only assumed for chips and DCB parts per se, not for applications, processes and circuits implemented with components or assemblies. Terms of delivery and the right to change design or specifications are reserved.NomenclatureIGBT and MOSFET DiscreteIXSD 40N60A (Example)IX IXYSDie technology E NPT 3 IGBTF HiPerFETTM Power MOSFETG Fast IGBTS IGBT with SCSOA capability T Standard Power MOSFET D Unassembled chip (die)40Current rating, 40 = 40 A N N-channel type PP-channel type60Voltage class, 60 = 600 Vxx MOSFETA Prime RDS(on) for standard MOSFET Q Low gate charge dieQ2Low gate charge die, 2nd generation P PolarHTTM Power MOSFET L Linear Mode MOSFET IGBT--No letter, low VCE(sat)A Or A2, std speed type B Or B2, high speed typeCOr C2, very high speed type W-CWP 55-12/18(Thyristor Example)WPackage typeC Chip functionC = Silicon phase control thyristor W Unassembled chip PProcess designatorP = Planar passivated chip cathode on top55Current rating value of one chip in A 12/18Voltage class, 12/18 = 1200 up to 1800 VDiode and Thyristor ChipsC-DWEP 69-12(Diode Example)C Package typeD Chip functionD = Silicon rectifier diode W Unassembled chipEPProcess designatorEP = Epitaxial rectifier diodeN = Rectifier diode, cathode on top P = Rectifier diode, anode on topFN = Fast Rectifier diode, cathode on top FP = Fast Rectifier diode, anode on top69Current rating value of one chip in A -12Voltage class, 12 = 1200 V 001947 TS2/765/17557Registration No.:0019473IXYS reserves the right to change limits, test conditions and dimensions General Informations for ChipsWhen mounting Power Semiconductor chips to a header, ceramic substrate or hybrid thick film circuit, the solder system and the chip attach process are very important to the reliability and performance of the final product. This brochure provides several guidelines that describe recommended chip attachment pro-cedures. These methods have been used successfully for many years at IXYS.Available forms of chip packingsIXYS offers various options.Please order from one of the following possibilities:Packaging Options Delivery formC-...*Chips in tray (Waffle Pack);Electrically testedT-...*Chips in wafer, unsawed;Bipolar = 5" (125 mm ∅) wafer;Electrically tested, rejects are inked W-...*Chips in wafer on foil, sawed;Bipolar = 5" (125 mm ∅) wafer;Electrically tested, rejects are inked...* must be amended by the exact chip type designation.Packing, Storage and HandlingChips should be transported in their original containers. All chip transfer to other containers or for assembly should be done only with rubber-tipped vacuum pencils. Contact with human skin (or with a tool that has been touched by hand) leaves an oily residue that may adversely impact subsequent chip attach or reliability.At temperatures below 104°F (40°C), there is no limitation on storage time for chips in sealed original packages. Chips removed from original packages should be assembled immediately. The wetting ability of the contact metallization with solder can be preserved by storage in a clean and dry nitrogen atmosphere.The IGBT and MOSFET Chips are electrostatic discharge (ESD) sensitive. Normal ESD precautions for handling must be observed.Prior to chip attach, all testing and handling of the chips must be done at ESD safe work stations according to DIN IEC 47(CO) 701.Ionized air blowers are recommended for added ESD protection.Contamination of the chips degrades the assembly results.Finger prints, dust or oily deposits on the surface of the chips have to be absolutely avoided.Rough mechanical treatment can cause damage to the chip.Electrical TestsThe electrical properties listed in the data sheet presume correctly assembled chips. Testing ofnon-assembled chips requires the following precautions:-High currents have to be supplied homogeneously to the whole metallized contact area.-Kelvin probes must be used to test voltages at high currents-Applying the full specified blocking or reverse voltage may cause arcing across the glass passivated junction termination, because the electrical field on top of the passivation glass causes ionization of the surrounding air. This phenomenon can be avoided by usinginert fluids or by increasing the pressure of the gas surrounding the chip to values above 30 psig (2 bars).General Rules for AssemblyThe linear thermal expansion coefficient of silicon is very small compared to usual contact metals. If a large area metallized silicon chip is directly soldered to a metal like copper, enormous shear stress is caused by temperature changes (e.g. when cooling down from the solder temperature or by heating during working conditions) which can disrupt the solder mountdown.If it is found that larger chips are cracking during mountdown or in the application, then the use of a low thermal expansion coefficient buffer layer, e.g. tungsten, molybdenum or Trimetal ®, for strain relief should be considered. An alternative solution is to soft-solder these larger chips to DCB ceramic substrates because of their matching thermal expansion coefficients.4© 2004 IXYS All rights reservedMOS/IGBT ChipsRecommended Solder SystemIXYS recommends a soft solder chip attach using a solder composition of 92.5 % Pb, 5 % Sn and 2.5 % Ag. The maximum chip attach temperature is 460°C for MOSFET and 360°C for HiPerFET TM and IGBT.Wire BondingIt is recommended to use wire of diameter not greater than 0.38 mm (0.015") for bonding to the source emitter and gate pads. Multiple wires should be used in place of thicker wire to handle high drain or emitter currents. See tables for number of recommended wire bonds. At smaller gate pads 0.15 mm is recommended.Thermal Response TestingTo assure good chip attach processing, thermal response testing per MIL STD 750, Method 3161 or equivalent should be performed.Bipolar ChipsAssemblingIXYS bipolar semiconductor chips have a soft-solderable, multi-layer metallization (Ti/Ni/Ag) on the bottom side and, on top, either the same metallization scheme or an alumunium layer sufficiently thick for ultrasonic bonding. Note that the last layer of metal for soldering is pure silver.Regardless of their type all chips possess the same glass passivated junction termination system on top of the chip. For that reason they can be easily chip bonded or they can all be simply soldered to a flat contacting electrode in accordance to the General Rules on Page 3. All kinds of the usual soft solders with melting points below 660°F (350°C) can be used thanks to their pure silver top metal.Solders with high melting points are preferable due to their better power cycling capability, i.e. they are more resistant to thermal fatigue.Soldering temperature should not exceed 750°F (400°C). The maximum temperature should not be applied for more than five minutes.As already mentioned above the electrical properties quoted in the data sheets can only be obtained with properly assembled chips.This is only possible when all contact materials to be soldered together are well wetted and the solder is practically free of voids.A simple means to achieve good solder connections is to use a belt furnace running with a process gas containing at least 10 %Hydrogen in Nitrogen.Other approved methods are also allowed, provided that the above mentioned temperature-time-limits are not exceeded and temperature shocks above 930°F/min (500 K/min) are avoided.We do not recommend the use of fluxes for soldering!Ultrasonic Wire BondingChips provided with a thick aluminium layer are designed for ultrasonic wire bonding. Wire diameters up to 500 µm can be used dependent on chip types. Setting wires in parallel and application of stitch bonding lead to surge current ratings comparable to soldered chips.CoatingAlthough the chips are glass passivated, they must be protected against arcing and environmental influences. The coating material that is in contact with the chip surface must have the following properties:- elasticity (to prevent mechanical stress)- high purity, no contamination with alkali metals - good adhesion to metals and glass passivation.Assembly Instructions5IXYS reserves the right to change limits, test conditions and dimensionsFRED, Rectifier Diode and Thyristor Chips in Planar DesignFast Recovery Epitaxial Diodes (FRED)Power switches (IGBT, MOSFET, BJT, GTO) for applications in electronics are only as good as their associated free-wheeling diodes. At increasing switching frequencies, the proper functioning and efficiency of the power switch, aside from conduction losses,is determined by the turn-off behavior of the diode (characterized by Q rr , I RM and t rr - Fig. 1.Rectifier Diode and Thyristor ChipsThe figures 3 a-c show cross sectional views of the diode and thyristor chips in the passivation area. All thyristor and diode chips (DWN, DWFN,CWP) are fabricated using separation diffusion processes so that all junctions terminate on the topside of the chip. Now the entire bottom surfaces of all chips are available for soldering onto a DCB or other ceramic substrate without a molybdenum strain buffer. The elimination of the strain buffer and its solder joint reduces thermal resistance and increases blocking voltage stability. The junction termination areas are passivated with glass, whose thermal expansion coefficient matches that of silicon. All silicon chips increasingly use planar technology with guard rings and channel stoppers to reduce electric fields on the chip surface.The contact areas of the chips have vapor deposited metal layers which contribute substantially to their high power cycle capability. All chips are processed on silicon wafers of 5" diameter and diced after a wafer sample test which auto-matically marks chips not meeting the electrical specification.The chip geometry is square or rectangular.Fig. 3a-cCross sections of Chips in the passivation area a) Diode chip, type DWN, DWFN b) Diode chip, type DWP, DWFP c) Thyristor chip, type CWPThe reverse current character-istic following the peak reverse current I RM is another very im-portant property. The slope of the decaying reverse current di rr /dt results from design para- meters (technology and dif-fusion of the FRED chip Fig. 2. In a circuit this current slope, in conjunction with parasitic induc-tances (e.g. connecting leads, causes over-voltage spikes and high frequency interference vol-tages.The higher the di rr /dt ("hard recovery" or "snap-off" behavior) the higher is the resulting additional stress for both the diode and the paralleled switch. A slow decay of the reverse current ("soft recovery" behavior), is the most desirable characteristic, and this is designed into all FRED. The wide range of available blocking voltages makes it possible to apply these FRED as output rectifiers in switch-mode power supplies (SMPS) as well as protective and free-wheeling diodes for power switches in inverters and welding power supplies.MetalizationFig. 1:Current and voltage during turn-on andturn-offswitching of fast diodesFig. 2:Cross section of glassivated planar epitaxial diode chip with seperation diffusion (type DWEP)Epitaxie Sch ich t n -Sub stra t n+KathodeAnodeGuard ringSubstrate n+Epitaxy layer n-CathodeAnode Glasspassivation p n n +GlasspassivationGuard ring Metalization Fig. 3b)MetalizationChannel-stopperGlasspassivationGuard ring EmitterFig. 3c)Fig. 3a)18© 2004 IXYS All rights reservedRectifier DiodesTypeV RRMVDWN 5800 -DWP 51200DWN 21200 -DWN 91800DWN 17 DWP 17DWN 21DWP 21DWN 35DWP 35DWN 50DWP 50DWN 75DWP 75DWN 110DWP 110DWN 340DWN 1081600 -1Mounted on DCB19© 2004 IXYS All rights reservedDWNDWPRectifier DiodesTypeDWN 5DWP 5DWN 2•DWN 9•DWN 17 •DWP 17•DWN 21•DWP 21•DWN 35•DWP 35•DWN 50•DWP 50DWN 75•DWP 75•DWN 110•DWP 110•DWN 340•DWN 108•s o l d e r a b l e20© 2004 IXYS All rights reserved FRED - F ast R ecovery E pitaxial DiodesTypeV RRMVDWEP 27-02200DWEP 37-02DWEP 77-02DWEP 8-06600DWEP 12-06DWEP 15-06DWEP 23-06DWEP 25-06DWEP 35-06DWEP 55-06DWEP 75-06DWEP 3-101000DWEP 10-10DWEP 18-10DWEP 20-10DWEP 30-10DWEP 50-101 Mounted on DCB21© 2004 IXYS All rights reserved FRED - F ast R ecovery E pitaxial DiodesTypeDWEP 27-02•DWEP 37-02•DWEP 77-02••DWEP 8-06•DWEP 12-06••DWEP 15-06••DWEP 23-06••DWEP 25-06••DWEP 35-06••DWEP 55-06•DWEP 75-06••DWEP 3-10•DWEP 10-10•DWEP 18-10•DWEP 20-10•DWEP 30-10••DWEP 50-10•s o l d e r a b l eb o n d a b l e22© 2004 IXYS All rights reservedLow Leakage Fast Recovery Epitaxial DiodesTypeV RRM VDWLP 4-02200DWLP 15-02DWLP 15-02B DWLP 25-02DWLP 4-03300DWLP 8-03DWLP 15-03DWLP 15-03A DWLP 23-03DWLP 23-03A DWLP 55-03DWLP 75-03DWLP 8-04400DWLP 15-04DWLP 23-04DWLP 55-04DWLP 75-04DWLP 150-04DWLP 4-066001Mounted on DCB23© 2004 IXYS All rights reservedLow Leakage Fast Recovery Epitaxial DiodesTypeDWLP 4-02•DWLP 15-02•DWLP 15-02B •DWLP 25-02•DWLP 4-03•DWLP 8-03•DWLP 15-03•DWLP 15-03A •DWLP 23-03•DWLP 23-03A •DWLP 55-03••DWLP 75-03•DWLP 8-04•DWLP 15-04•DWLP 23-04•DWLP 55-04••DWLP 75-04••DWLP 150-04••DWLP 4-06•s o l d e r a b l eb o n d a b l e24© 2004 IXYS All rights reserved SONIC-FRD TMDiodesTypeV DWHP 8-06 F in design DWHP 15-06 F 600DWHP 23-06 FDWHP 56-06 F DWHP 69-06 F DWHP 150-06 F in design DWHFP 15-12 F 1200DWHFP 23-12 F DWHFP 56-12 F DWHFP 56-12 S DWHFP 69-12 F DWHFP 69-12 S DWHFP 150-12 S DLFP 55-17 S 1700DLFP 68-17 S DLFP 150-17 S DLFP 200-17 S 1Mounted on DCB25© 2004 IXYS All rights reserved SONIC-FRD TMDiodesTypeDWHP 8-06 F DWHP 15-06 F DWHP 23-06 F DWHP 56-06 F DWHP 69-06 F DWHP 150-06 F DWHFP 15-12 F DWHFP 23-12 FDWHFP 56-12 F DWHFP 56-12 SDWHFP 69-12 F DWHFP 69-12 S DWHFP 150-12 S DLFP 55-17 S DLFP 68-17 S DLFP 150-17 S DLFP 200-17 S s o l d e r a b l e26© 2004 IXYS All rights reservedGaAs Schottky DiodesTypeV RRMVDWGS04-01A 100DWGS10-01C DWGS04-018A 180DWGS04-018CDWGS10-018ADWGS10-018C DWGS20-018A DWGS20-018C DWGS04-025A 250DWGS04-025C DWGS10-025A DWGS10-025C DWGS20-025A DWGS20-025C DWGS04-03A 300DWGS04-03C DWGS10-03A27© 2004 IXYS All rights reservedGaAs Schottky DiodesD W GS04-01A D W GS10-01CD W GS04-018A D W GS04-018C D W GS10-018A D W GS10-018C D W GS20-018A D W GS20-018C D W GS04-025A D W GS04-025C D W GS10-025A D W GS10-025C D W GS20-025A D W GS20-025C D W GS04-03A D W GS04-03C D W GS10-03A s o l d e r a b l e28© 2004 IXYS All rights reservedSchottky DiodesTypeV RRMVDWS 39-08D DWS 9-15B 15DWS 19-15B DWS 29-15B DWS 7-30B 30DWS 17-30B DWS 27-30B DWS 37-30B DWS 217-30B DWS 3-45B 45DWS 4-45A DWS 13-45B DWS 14-45A DWS 23-45B DWS 24-45A DWS 33-45B 1Mounted on DCB29© 2004 IXYS All rights reservedSchottky DiodesTypeDWS 39-08D •DWS 9-15B •DWS 19-15B •DWS 29-15B •DWS 7-30B •DWS 17-30B •DWS 27-30B•DWS 37-30B •DWS 217-30B •DWS 3-45B •DWS 4-45A •DWS 13-45B •DWS 14-45A •DWS 23-45B ••DWS 24-45A •DWS 33-45B ••s o l d e r a b l eb o n d a b l e30© 2004 IXYS All rights reservedSchottky DiodesTypeV RRMVDWS 5-60A 60DWS 15-60BDWS 25-60BDWS 35-60B DWS 25-80B 80DWS 36-80A DWS 2-100A 100DWS 12-100A DWS 22-100A DWS 32-100A DWS 1-150A 150DWS 11-150A DWS 21-150A DWS 31-150A DWS 1-180A 1801 Mounted on DCB31© 2004 IXYS All rights reservedSchottky DiodesTypeDWS 5-60A •DWS 15-60B •DWS 25-60B •DWS 35-60B •DWS 25-80B •DWS 36-80A •DWS 2-100A •DWS 12-100A •DWS 22-100A •DWS 32-100A ••DWS 1-150A •DWS 11-150A •DWS 21-150A •DWS 31-150A •DWS 1-180A •s o l d e r a b l eb o n d a b l e32© 2004 IXYS All rights reservedPhase Control ThyristorsTypeV DRM V RRMVCWP 7-CG 800 -CWP 81200CWP 8-CG CWP 35CWP 16-CG 1200 -CWP 21-CG 1600 -CWP 22-CG CWP 24CWP 25-CG CWP 411200 -CWP 501800CWP 55CWP 71CWP 130CWP 180CWP 341CWP 3471Mounted on DCB33© 2004 IXYS All rights reservedPhase Control Thyristors...-CG typesTypeCWP 7-CG ••CWP 8••CWP 8-CG•CWP 35••CWP 16-CG ••CWP 21-CG ••CWP 22-CG ••CWP 24••CWP 25-CG ••CWP 41••CWP 50••CWP 55••CWP 71••CWP 130••CWP 180••CWP 341•CWP 347•s o l d e r a b l eb o n d a b l e34© 2004 IXYS All rights reservedDWFN DWFPFast Rectifier DiodesTypeV RRMVDWFN 2-16/181600 -DWFN 9-16/181800DWFN 17-16/18DWFP 17-16/18DWFN 21-16/18DWFN 35-16/181 Mounted on DCBTypeo l d e r a b l e。

CSC-246AE数字式备用电源自投入装置说明书-V2.01S

CSC-246A/E数字式备用电源自投入装置说明书CSC-246A/E数字式备用电源自投入装置说明书CD2012075编制: 张华年校核:王彦辉标准化审查: 李连昌审定:邹卫华出版号:V2.01S文件代号:0SF.457.016出版日期:2012年3月版权所有:北京四方继保自动化股份有限公司注:本公司保留对此说明书修改的权利。

如果产品与说明书有不符之处,请您及时和我公司联系,我们将为您提供相应的服务。

技术支持服务热线电话:传真:重要提示感谢您使用北京四方继保自动化股份有限公司的产品。

为了安全、正确、高效地使用本装置,请您务必注意以下重要提示:1)本说明书仅适用于CSC-246A/E数字式备用电源自投入装置,其配套的程序版本为V2.01及其以上兼容版本。

2)请仔细阅读本说明书,并按照说明书的规定整定、调试和操作。

如有随机资料,请以随机资料为准。

3)为防止装置损坏,严禁带电插拔装置各插件、触摸印制电路板上的芯片和器件。

4)请使用合格的测试仪器和设备对装置进行试验和检测。

5)装置如出现异常或需维修,请及时与本公司服务热线联系。

6)本装置的出厂操作密码是:8888。

目录第一篇装置技术说明 (4)1概述 (4)1.1 适用范围 (4)1.2 装置主要特点 (4)1.3 装置执行的标准 (6)2技术条件 (7)2.1 环境条件 (7)2.2 电气绝缘性能 (7)2.3 机械性能 (7)2.4 电磁兼容性 (7)2.5 安全性能 (8)2.6 功率消耗 (8)2.7 输出触点容量 (8)2.8 装置主要技术参数 (8)3装置硬件 (10)3.1 装置结构 (10)3.2 装置外观图 (10)3.3 装置插件布置图 (11)3.4 采样插件 (11)3.5 CPU插件 (11)3.6 通信管理插件 (11)3.7 开入插件 (12)3.8 开出插件 (12)3.9 操作插件 (12)3.10 电源插件 (12)4装置软件 (13)4.1 保护程序整体结构 (13)4.2 数字化功能 (13)4.3保护功能 (13)4.4 零序电流保护 (13)4.5 过电流保护 (14)4.6 过负荷联切功能 (15)4.7 备投功能概述 (15)4.8 遥控开出 (19)4.9 智能终端及控制回路检测 (19)4.10 MU异常对保护的影响 (19)第二篇用户使用说明 (20)5开箱检查 (20)6安装调试 (20)6.1 安装 (20)6.2 通电前的检查 (20)6.3 装置通电检查 (21)7定值清单及整定说明 (29)7.1 CSC-246A/E装置定值清单及其整定说明 (29)8装置端子说明 (33)8.1 开入端子说明 (33)8.2 电源插件端子说明 (33)9人机接口及其操作 (34)9.1 装置面板布置图 (34)9.2 正常运行显示 (34)9.3 装置模拟量显示含义 (35)9.4 装置菜单结构 (36)10运行维护 (38)10.1 装置投运前检查 (38)10.2 运行中的注意事项 (38)10.3 设备更换保护软件或保护CPU板后的操作 (39)10.4 设备更换MASTER软件或MASTER板后的操作 (39)10.5 定值固化方式、定值区切换方式、打印方式等的说明 (39)11保护报文汇总 (41)11.1 装置告警信息 (41)11.2 运行异常信息 (41)11.3 GOOSE和MU告警信息 (42)12运输、贮存 (43)13订货须知 (43)14附录1:字符和中文字符集 (44)14.2 ASCII 16进制字符表 (44)14.3 中文字符表 (45)15附图 (52)15.1 CPU简化原理图 (52)15.2 MASTER板简化原理图 (53)15.3 开出2插件原理图 (54)15.4 操作插件原理图 (55)15.5 电源插件原理图 (56)15.6 CSC-246A/E装置背板端子图 (57)第一篇装置技术说明1概述1.1适用范围CSC-246A/E数字式备用电源自投入装置适用于数字化变电站。

DE34中文说明

2.5.1

TCH话务

BCFSIG控制维护单元信令

TRXSIGTRX信令

2.5.2

TS

Bit used in Timeslot

1 2

3 4

5 6

7 8

0

1

TCH

TCH

TCH

TCH

TRX1

2

TCH

TCH

TCH

TCH

3

TCH

TCH

TCH

TCH

TRX2

4

TCH

TCH

TCH

TCH

5

TCH

TCH

TCH

TCH

1.8

1.9

1.10

1.11

1.12

每一单元都有它的位置, 在研究BTS的告警时, 单元板的位置以附加信息的形式表现出来, 应该根据告警的

附加信息来确定是什么位置出现的问题

1.13

2.

2.1

2.1.1

2.1.2

panel ST connector, switch on the ST power, and make the following settings:

TCH

TCH

TRX10

20

TCH

TCH

TCH

TCH

21

TCH

TCH

TCH

TCH

TRX11

22

TCH

TCH

TCH

TCH

23

TCH

TCH

TCH

TCH

TRX12

24

TCH

TCH

TCH

TCH

25

26

TRX12SIG

BCF12SIG

3843B中文资料

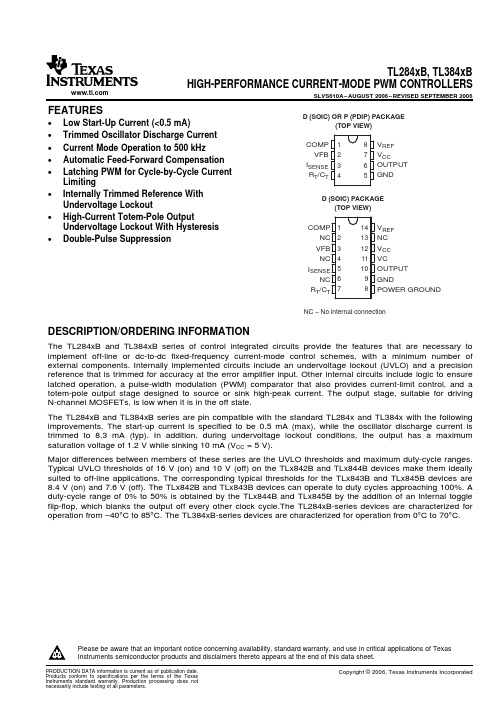

TL284xB, TL384xB HIGH-PERFORMANCE CURRENT-MODE PWM CONTROLLERS

SLVS610A – AUGUST 2006 – REVISED SEPTEMBER 2006

FEATURES

• Low Start-Up Current (<0.5 mA) • Trimmed Oscillator Discharge Current • Current Mode Operation to 500 kHz • Automatic Feed-Forward Compensation • Latching PWM for Cycle-by-Cycle Current

TOP-SIDE MARKING TL2842BP TL2843BP TL2844BP TL2845BP 2842B

2843B

2844B

2845B

TL2842B

TL2843B

TL2844B

TL2845B TL3842BP TL3843BP TL3844BP TL3845BP 3842B

3843B

3844B

FUNCTIONAL BLOCK DIAGRAM

34 V NOM 5 GND

−+

UVLO

5-V VREF EN

8 VREF

RT/CT 4

2.5 V OSC

VREF Good

Logic

Internal Bias

6 OUTPUT

T

2 VFB COMP 1

Error Amplifier

+ −

2R

R

1V

ISENSE 3 A. Pin numbers shown are for the 8-pin D package.

三位半数字万用表电路课程设计

河北建筑工程学院课程设计报告书课程名称:《电子技术》综合课程设计学院:电气工程学院专业:班级:学号:学生姓名:指导教师:职称:年月日目录一、课程设计的目的 (2)二、设计要求及技术指标 (2)三、设计方案及原理 (2)四、测试部分电路设计 (3)(1)数字电压表原理框图 (3)电压衰减电路 (3)单相桥式整流滤波电路 (4)基准电压模块 (5)3 1/2位A/D电路模块 (5)字形译码驱动电路模块 (6)显示电路模块 (6)(2)实验电路工作过程及芯片简介 (7)工作过程 (7)三位半A/D转换器MC14433 (8)七段锁存-译码-驱动器MC4511 (8)七路达林顿驱动器阵列MC1413 (9)高精度低漂移能隙基准电源MC1403 (9)五、总电路图及电路分析 (9)六、元器件清单.................................... (10)七、组装、调试内容 (11)八、设计心得和体会 (11)九、参考文献 (12)十、电路搭建完成的照片 (13)第一章课程设计目的课程设计主要目的:是通过电子技术的综合设计,熟悉一般电子电路综合设计过程、设计要求、应完成的工作内容和具体的设计方法。

通过设计也有助于复习、巩固以往的学习模电、数电内容,达到灵活应用的目的。

在设计完成以后,还要将设计的电路进行安装、调试以加强学生的动手能力。

在此过程中培养从事设计工作的整体观念。

课程设计应强调以能力培养为主,在独立完成设计任务同时应注意多方面能力的培养与提高,主要包括以下方面:独立工作能力和创造力;●综合运用专业及基础知识,解决实际工程技术问题的能力;●查阅图书资料、产品手册和各种工具书的能力;●熟悉常用电子仪器操作使用和测试方法;●工程绘图能力;●写技术报告和编制技术资料的能力。

●培养同学之间合作与交流的能力;●电路检测与故障排查能力;第二章设计要求及技术指标具体要求:1、利用所学知识,通过上网或到图书馆查阅资料,设计三个实现数字万用表的方案;只要求写出实现原理,画出原理功能框图,描述其功能。

WishboneB中文完整版精编版

W i s h b o n e B中文完整版集团企业公司编码:(LL3698-KKI1269-TM2483-LUI12689-ITT289-Wishbone b3中文版本文详细介绍了Wishbone标准,主要参考了Wishbone标准B.3版本的核心内容,感兴趣的读者可去下载英文原文。

一、片上总线技术综述随着超大规模集成电路的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管。

如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和外设等数块芯片实现的功能集成起来,由单片集成电路构成功能强大的、完整的系统,这就是我们通常所说的片上系统。

IP复用是片上系统时代的核心技术之一。

由于IP核的设计千差万别,它们要能够直接连接,就要遵守相同的接口标准。

在片上系统中,处理器核和所有外设通过共享总线互通互联,因此这些IP核必须遵守相同的总线规范。

总线规范定义的是IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP 核的功能和接口如何实现。

一个片上总线规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系。

芯片与电路板的资源和环境的不同,导致片上总线与板上总线存在若干明显差异,包括:①片上总线多采用单向信号线,而板上总线多采用三态信号。

片上三态总线无论在功耗、速度、可测性上都存在很大缺陷,而且一旦出现多驱动情况便会损毁芯片(比如若应该输出"Z"的信号实际输出为"1",而另有一个信号输出为"0",就形成一个低电阻通路,导致局部电流过大,热量难以及时释放,从而增加芯片功耗和大大降低芯片寿命)。

由于片上布线资源较为丰富,因此片上总线多采用单向信号线。

由于电路板上布线资源较为昂贵,因此板上总线多采用三态总线,但是由于三态总线的功耗问题和速度限制,目前板上总线也在向串行和非三态方向发展,如USB和PCI Express。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

mA 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0

Max. 1000 1000 1000 800 500 200 100 60 60 60 60 60 60 80 80 0 80 80 100 100 120 150 200 250 300

-0.04

-0.06

-0.08

0

10

20

30

40

ZENER VOLTAGE - TEMP. (V)

- 785 -

ELECTRICAL CHARACTERISTICS (TA=25OC

Device Device Marking Code 62 72 82 92 A2 C2 E2 F2 H2 J2 L2 05 15 25 35 45 55 65 75 85 95 A5 C5 E5 F5 Zener Voltage Vz (V) Min. UDZS 3.6B UDZS 3.9B UDZS 4.3B UDZS 4.7B UDZS 5.1B UDZS 5.6B UDZS 6.2B UDZS 6.8B UDZS 7.5B UDZS 8.2B UDZS 9.1B UDZS 10B UDZS 11B UDZS 12B UDZS 13B UDZS 15B UDZS 16B UDZS 18B UDZS 20B UDZS 22B UDZS 24B UDZS 27B UDZS 30B UDZS 33B UDZS 36B 3.600 3.890 4.170 4.550 4.980 5.490 6.060 6.650 7.280 8.020 8.850 9.770 Max. 3.845 4.160 4.430 4.750 5.200 5.730 6.330 6.930 7.600 8.360 9.230 10.210 IZ mA 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0 5.0

SOD-323F

Mechanical Data

Case: SOD-323F, Plastic Terminals: Solderable per MIIL-STD-202, Method 208 Polarity: Cathode band Marking: Date Code and Type Code or Date Code only Type Code: See table on Page 2 Weight: 0.01 grams (approx.)

UDZS SERIES

Surface Mount Zener Diode

Voltage Range 3.6 to 36 Volts 200m Watts Power Dissipation

Features

Compact, 2-pin mini-mold type for high-density mounting. (UMD2) Non-wire bonding structure improves. High demand voltage range (3.6V~36V) is manufactured on high-efficient non-wire bonding production line

(mA) 1.0 1.0 1.0 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5

Max 10 5 5 2 2 1 1 0.5 0.5 0.5 0.5 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1 0.1

- 786 -

Power Dissipation (Note 1) Junction Temperature Range Maximum Instantaneous Forward Voltage @ 100mA Operating and Storage Temperature Range

Symbol Pd TJ VF TSTG

0.094(2.40) 0.102(2.60)

Dimensions in inches and (millimeters)

0.073(1.85) 0.069(1.75)

Value 200 -55 to + 150 1.3 -55 to + 150

Units mW O C V O C

Note: 1. Device Mounted on Ceramic PCB, 7.6mm x 9.4mm x 0.87mm with Pad Areas 25mm2

0.016(0.4) 0.008(0.2) 0.006(0.15) 0.002(0.05) 0.051(1.3) 0.047(1.2) 0.035(0.9) 0.031(0.8)

Maximum Ratings and Electrical Characteristics

Rating at 25℃ambient temperature unless otherwise specified. Maximum Ratings Type Number

20

22

24

27

30

33

36

ZENER CURRENT, Iz (A)

1m 100

4.7 4.3 3.6

10 1 100n 10n

0

5

10

15

20

ZENER VOLTAGE, Vz (V)

25

30

35

40

FIG.2- DERATING CURVE

300

FIG.3- COEFFICIENT CHARACTERISTICS

- 784 -

RATINGS AND CHARACTERISTIC CURVES (UDZS SERIES)

FIG.1-ZENER VOLTAGE CHARACTERISTICS

100m 10m

5.1 5.6 .2 6.8 5 .2 .1 10 12 13 6 7. 8 9 11 3.9

15

16

18

Notes: 1. The Zener Voltage (Vz) is measured 40ms after power is supplied. 2. The operating resistances (Zz, Zzk) are measured by superimposing a minute altemating current on th requlated current (Iz).

0.10

Iz = 5mA

POWER DISSIPATION Pd (mA)

200

TEMP. COEFFICIENT CHARACTERISTICS (% / OC)

250

0.08

Iz = 500 A

0.06

150

0.04

100

0.02

50

0.00

0

0

25

50

75

100

o

125

150

-0.02

AMBIENT TEMPERATURE. ( C)

unless otherwise noted)

Rising Operating

Operating Resistance ZZ(Ohms) IZ

Resistance

ZZK(Ohms) IZ

Reverse Current IR(uA) VR

Max. 100 100 100 100 80 60 60 40 30 30 30 30 30 30 37 42 50 65 85 100 120 150 200 250 300

V 1 1 1 1 2 3 3 4 4 5 6 7 8 9 10 11 12 13 15 17 19 21 23 25 27

10.760 11.220 11.740 12.240 12.910 13.490 14.340 14.980 15.850 16.510 17.560 18.350 19.520 20.390 21.540 22.470 23.720 24.780 26.190 27.530 29.190 30.690 32.150 33.790 35.070 36.870