采用fpga实现发电机组频率测量计的设计

基于FPGA的数字频率计的设计

沈 磊 , 善 化 ( 徽 理 工 大 学 电气 与信 息 工 程 学 院 , 徽 淮 南 2 2 0 ) 姚 安 安 3 0 1

S e e, o Sh n h a( e、 i I n fr t nE gn e igC l g , h i nv ri f h nLi Ya a — u El t dI omai n ie r ol e (r a a n o n e An u i s yo U e t

t n a t A of r ca f r Max pls Im a fc ur t a d i fa ED on s t o r wa e lto m + u I . nua t es i h r war lc r i uibo r。 wnla t e p o ed e t h P A s e ee ti cr t c c a d. do O ds “ f l r C ur o t e F G

现场 可 编 程 门 阵

图 1数 字频 率计 的原 理 框 图

片 F G (idPorm b a s Ⅱ 广 P AFe rga malG t a l e eA

列) 片上 , 个 系统 非 常 精 简 , 够 达 到 I 的 技术 指 标 。 芯 整 并能 川样 根

据 不 同 的需要 还 可以 重新 编 程 下载 , 行 升 级} 进 I 。

S in e& T c n l yAn u Hu ia 3 0 1 ce c e h oo . h i an n2 2 0 1 g

摘 要 : 硬件描 述语 言 V D 对 频率t 用 H L t 系统进 行设 计 , 此程序 在 E A软件平 台 M D pu I 上编 译仿 真后 , 作 lsI 制 出其 硬件 电路板 , 再将 程序 下载 到 F G P A模块 中实现 。 件设 计 中只需一 个下载 芯片 E 2 5 剩余 皆是输 入输 出部 硬 PC , 分, 包括 时钟 和数码 管驱动 以及发 光二檄 管 , 大大 地简化 了电 路结构 的复杂性 。 又提高 了电路 的稳 定性 。

计算机毕业论文_基于FPGA的等精度频率计的设计与实现

目录前言...............................................................1 第一章 FPGA及Verilog HDL..........................................2 1.1 FPGA简介.....................................................2 1.2 Verilog HDL 概述.............................................2 第二章数字频率计的设计原理........................................3 2.1 设计要求.....................................................3 2.2 频率测量.....................................................3 2.3.系统的硬件框架设计..............................................4 2.4系统设计与方案论证............................................5 第三章数字频率计的设计............................................8 3.1系统设计顶层电路原理图........................................8 3.2频率计的VHDL设计.............................................9 第四章软件的测试...............................................15 4.1测试的环境——MAX+plusII.....................................15 4.2调试和器件编程...............................................15 4.3频率测试.....................................................16基于FPGA的等精度频率计的设计与实现摘要:本文详细介绍了一种基于FPGA的高精度频率计。

基于FPGA的数字频率计实验报告(能测占空比)

基于FPGA的数字频率计设计学院:专业:班级:姓名:学号:审阅老师:评分:目录一、课程设计目的 (3)二、设计任务 (3)三、功能要求与技术指标 (3)四、数字频率计工作原理概述 (3)五.数字频率计实现方法 (4)六.结论与误差分析 (11)七.VHDL程序: (12)一、课程设计目的熟悉EDA工具,掌握用VHDL语言进行数字系统设计的基本方法和流程,提高工程实践能力。

二、设计任务设计一数字频率计,用VHDL语言描述,用QuartusII工具编译和综合,并在实验板上实现。

三、功能要求与技术指标1.基本功能要求(1)能够测量出方波的频率,其范围50Hz~50KHz。

(2)要求测量的频率绝对误差±5Hz。

(3)将测量出的频率以十进制格式在实验板上的4个数码管上显示。

(4)测量响应时间小于等于10秒。

以上(1)~(4)基本功能要求均需实现。

2.发挥部分(1)提高测量频率范围,如10Hz~100KHz或更高、更低频率,提高频率的测量绝对值误差,如达到±1Hz。

(2)可以设置量程分档显示,如X1档(显示范围1Hz~9999Hz),X10档(显示范围0.001KHz~9.999KHz),X100档(显示范围0.100KHz~999.9KHz)...可以自定义各档位的范围。

量程选择可以通过按键选择,也可以通过程序自动选择量程。

(3)若是方波能够测量方波的占空比,并通过数码管显示。

以上(1)~(3)发挥功能可选择实现其中的若干项。

四、数字频率计工作原理概述1.数字频率计简介在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

而数字频率计是采用数字电路制成的实现对周期性变化信号的频率的测量。

2.常用频率测量方法:方案一采用周期法。

通过测量待测信号的周期并求其倒数,需要有标准倍的频率,在待测信号的一个周期内,记录标准频率的周期数,这种方法的计数值会产生最大为±1个脉冲误差,并且测试精度与计数器中记录的数值有关,为了保证测试精度,测周期法仅适用于低频信号的测量。

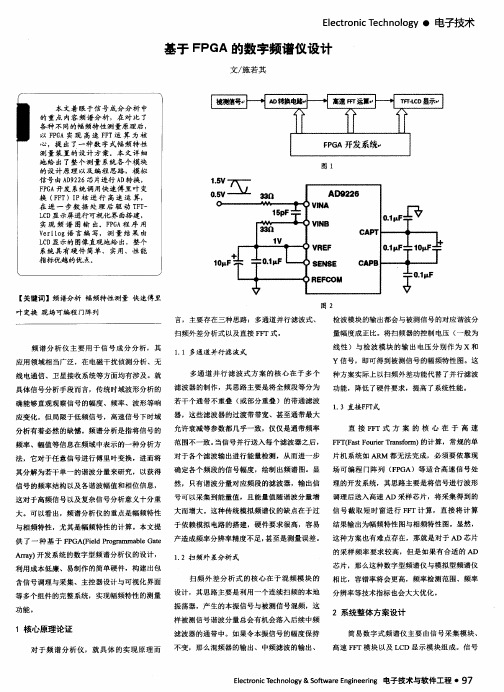

基于FPGA的数字频谱仪设计

理 的开发 系统,其思路主要是将信号进行波形 调理后送 入高速 AD采 样芯片,将采集得到 的

F T计 算 ,直 接将 计 算 可以看 出,频谱分析仪 的重 点是 幅频特 性 大而增大 。这种传统模拟频谱 仪的缺点在于过 信 号截 取短 时 窗进行 F 结果输 出为幅频特性图与相频特性 图。显然 , 频特性,尤其是幅频特性 的计算 。本文 提 于依赖模拟 电路 的搭建 ,硬件 要求很高,容 易

通信、卫星接收系统等方 面均有 涉及。就

: 信号分析手段而言 ,传统 时域波 形分析的 够 直观观察信号 的幅度 、频 率、波形等响 : 化,但局限于低频信 号,高速信 号下时域

器 ,这些滤波器 的过渡 带带宽、甚至通带最大

有着必然的缺憾 。频谱分析是指将信 号的 允许衰减等参数都 几乎 一致,仅仅是通带频率

开发系统 的数 字型频谱分析仪 的设计 ,

成本低廉、易制作 的简单硬件 ,构 建出包 号调理与采集、主控器设计与可视化界面

相 比,容错 率将 会更高 ,频率检测范 围、频 率

分辨率等技术指标也会大大优化 。

个 组件 的完整系统 ,实现幅频特性 的测量

2系统整体 方案设计

简 易数字式频 谱仪主要 由信号采 集模块 、 高速 F F T模块 以及 L C D 显示 模块组 成。信号

、

幅值等信息在频域 中表示 的一种 分析 方

范围不一致 。 当信号并行送入每个滤波器之后 , 对于各个滤波输 出进行 能量检 测,从而进一步

它对于任意信号进行傅里 叶变换 ,进而 将

F P GA)等适 合高速 信号 处 解 为若干单一的谐波分量来研 究,以获得 确定各个频段 的信 号幅度 ,绘制出频谱 图 显 场 可编程 门阵列 ( 的频率结构 以及各谐波幅值和相位信 息, 于高频信号 以及复杂信号分析意义 十分 重 然,只有谐波分量对应频 段的滤波器 ,输 出信

基于FPGA的等精度频率计单片系统设计

S T R 0F WA E

国际 I T传媒品牌

基于F G 的等精度矿 业大 学信 息与 电气 工程 学院 ,江 苏 徐州 ) 中

摘 要 : 章首 先叙 述 了等精 度 频 率 测 量法 的原 理 , 进行 误 差 分 析 , 后 用 V ro 文 并 然 elgHDL语 言编 程 设 计 出频率 计 的核 i 心模 块 , 结合 85 单 片机 I 实现 了等精度 频 率计 单 片系 统, 01 P核 并在 DE 2开 发板 上对 系 统进行 验 证。该 频 率计 的测量 范 围为 o1 . Hz~IO OMHz测 量全域相对误差恒为百万分之一 , 际使用证 明本设计具有 良好 的可靠性 , , 实 可用于实验 室或其他频率测量项 目。 关键词 :F GA; P 等精度 ; 频率计 ; 知识产权 核 中图分类号 : N9 T 8 文献标识码 : A D 03 6 ̄i n10 -9 02 1 .1 1 Oh1 . 9 .s.0 36 7 .0 2 . 3 9 s 00

c mo t ri 0 1 y me e .Hz~ 1 0 s 0 MHz a d t er s l t n i ls a n n a mi i n T ed sg e y o tri fh g l b l y a d Ca e , n e o u i s e st n o e i l o , h e i n d c m me e so i h r i i t n Ol h o h l e a i b

数 测 频 法 和 周 期 测 频 法 , 点分 析 多 周 期 同 步 测 频 法 的工 作 原 重

理 。

传统 的数 字频率测量方法 有脉 冲计数法和周期 测频法 , 但

基于FPGA的数字频率计的设计与实现

基于 F G P A的数 字频 率计的设计 与实现

张兆莉 。 等

基于 F G P A的数 字频 率计的设计与实现

De in a d Re l a in o gi l r q en y M e e s d on F GA sg n ai t fDi t e u c t rBa e P z o a F

文献 标识码 :A

A s a t i t ' un ym t ei e i P A d v l m n sf a - s 1 si r u e .T e1H l zi u m aue bt c :A dg a f q e e e r s nd w t F G e e p e t o w r Q  ̄u t d c d h z— p t esrd r il e i ed g h o t e 1i no MH n

p le sg aso h ii lie u n y mee a s d frme s rn rq e c us in l fte dgt i q e c trc n beu e o a u ig fe u n y,p ro a ' eid,p lewi h a d d t ai u s dt n uy rto,ec T e ts rs l tby t. h e t e ut sa l s d s a 7 3 sv n s g n umei u e ,a d te me s rn a g s ma wi h d o e uo t al. T a u n ro se u lt r iply O1 e e —e me tn rc tb s n h a uig r n e y be s t e v ra tmai l c c y heme s r g er ri q a o o i

(完整版)基于FPGA的等精度频率计的设计与实现毕业设计

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

目前常用的测频方案有三种:方案一:完全按定义式F=NT进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX 的个数,则有公式可得Fx=1ГX=NTR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1T(频率=1周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГXTR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

方案三:等精度测频,按定义式F=NT进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1ГX=NTR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

fpga 频率变换 实现方法

fpga 频率变换实现方法

FPGA(现场可编程门阵列)是一种可以进行并行处理的集成电路,其频率

变换可以通过以下几种方法实现:

1. 时钟分频器:FPGA内部通常包含一些内置的时钟分频器,可以将输入的时钟信号进行分频,从而得到不同频率的输出信号。

在FPGA开发工具中,可以通过配置时钟分频器的参数来改变分频比,从而实现频率变换。

2. 时钟生成器:FPGA内部还可以生成一些高精度的时钟信号,这些时钟信号可以通过配置时钟生成器的参数来改变其频率。

在FPGA开发工具中,可以使用内建的时钟生成器来生成所需的时钟信号。

3. 数字控制振荡器(Digital Controlled Oscillator,DCO):DCO是一种数字控制的振荡器,可以通过改变控制字来改变其振荡频率。

在FPGA开发工具中,可以通过配置DCO的参数来改变其振荡频率,从而实现频率变换。

4. 查找表(LUT):FPGA内部还可以使用查找表来实现频率变换。

查找表可以根据输入的地址选择相应的输出值,从而实现不同的频率变换。

在FPGA开发工具中,可以通过配置查找表的参数来改变输出值,从而实现频率变换。

5. 硬件描述语言:在FPGA开发过程中,可以使用硬件描述语言(如Verilog或VHDL)来实现频率变换的逻辑电路。

通过编写相应的代码,可

以实现不同的频率变换功能。

在FPGA开发工具中,将代码进行编译和综合后生成相应的配置文件,然后将配置文件下载到FPGA中即可实现频率变换。

以上是FPGA实现频率变换的几种常见方法,具体实现方式可以根据实际需求和开发环境进行选择。

基于FPGA的等精度频率计设计

设 计 和 编 程 变 得更 加 适 应 现 代 社 会 技 术 发 展 、更 加 快 速精 确 。

F P G A( 现场 可 编程 门 阵列 ) , 这 种可 编 程逻 辑 器件 是 在较 早 期 出 现 的逻 辑 器 件 的基础 上 逐 步 转 变 而来 的 , 其是 为 专 用集成 电路 范 围 中 的一 类部 分 设计 电路 而 出现 的 , 既 处理 了设 计 电路 的缺 点 , 也 战 胜 了早 期器 件 中的 门单 元 电路 数 量缺 少 的 毛病 。 设计 人 员能够 依 照各种 各样 的配置 模 式 , 选 择 使用 不 同 的编程 方 式 ,

2 0 1 3 年第2 4 期总第 1 4 4 期

S_率计设 计

高 锐 1 3 0 0 3 3 ) ( 长 春职业技 术 学 院 。 吉 林 长春 摘 要 本 文使 用 自上 而下 的 E D A 技 术设 计 方法 , 对 频 率计 的 总体设 计进 行 了功 能模块 和子 模 块划 分 。说 明了各功 能

1 等 精 度测 量方法 工 作原 理

频 率 是 电信 号 最常 用 特 性 , 它的 测 量 对于 电子 电路 来 说 也

是 最 必 需和 最 重要 的 。 因为 频 率 信号 本 身 的特 点决 定 了其 测量 结 果 大 都能 够 取到 较 高 的精 度 , 因而 频 率 信 号 的测 量方 法 的 实 现 在 实 践 中变 得越 来 越 重要 。在 实 际工 程 项 目里 , 也 需要 把相 应 的 物 理参 数和 相 关 参 数都 替变 为频 率 才 能 较好 的完成 测 量 工

基于FPGA和单片机的高精度数字频率计的设计与实现

基于FPGA和单片机的高精度数字频率计的设计与实现1. 引言1.1 背景介绍数字计数器是一种广泛应用于科学研究、工程技术和日常生活中的仪器设备,用于测量信号的频率、周期和脉冲数量等。

随着科技的不断发展,对于数字频率计的精度和性能要求也越来越高。

传统的数字频率计主要基于单片机或专用芯片的设计,存在精度受限、功能单一等问题。

而基于FPGA和单片机的高精度数字频率计能够充分发挥FPGA在并行计算和高速数据处理方面的优势,结合单片机的灵活性和易编程性,实现更高精度、更丰富功能的数字频率测量。

本文基于FPGA和单片机,设计并实现了一种高精度数字频率计,具有高度精准、快速响应的特点。

通过软硬件结合的设计思路,实现了数字信号频率的精确测量,同时在硬件设计和软件设计上都进行了详细优化和实现。

系统测试结果表明,该数字频率计具有较高的测量精度和稳定性,在实验中取得了良好的效果和准确的测量数据。

此设计不仅具有实用价值,还对数字频率计的进一步研究和应用具有一定的参考意义。

1.2 研究意义随着科技的发展,对于频率计的要求也越来越高,需要具备更高的精度、更快的响应速度和更广泛的适用范围。

设计和实现基于FPGA 和单片机的高精度数字频率计具有重要的研究意义。

通过本文的研究,可以深入了解数字频率计的工作原理和设计方法,为高精度频率计的研究和应用提供参考和借鉴。

本文的研究成果还可以为提高电子测量仪器的性能,推动数字频率计技术的发展做出重要的贡献。

本文的研究具有重要的理论和实践意义。

1.3 研究现状当前,数字频率计在电子测量领域具有重要的应用价值,其精度和稳定性对于提高测量精度和准确性至关重要。

目前,数字频率计的研究主要集中在硬件设计和软件算法的优化上。

在硬件设计方面,传统的数字频率计主要采用FPGA(现场可编程门阵列)作为核心控制器,实现高速、高精度的频率测量。

通过合理的电路设计和时序控制,可以实现更稳定和准确的频率计算。

在软件设计方面,研究者们致力于优化频率计算算法,提高频率计算的速度和精度。

基于FPGA的高精度频率计设计实验报告

基于FPGA的高精度频率计设计实验一.实验目的1.熟悉数字存储示波器基本工作原理。

2.掌握硬件测频和测周的基本原理。

3.掌握在现有综合实践平台上开发DSO硬件频率计模块的方案及流程。

二.实验内容1.结合数据采集、存储和触发模块的FPGA代码,理解DSO的基本工作原理。

2.编写FPGA代码完善DSO的频率计模块,实现高精度测频和测周功能。

三.预备知识1.了解综合实践平台硬件结构。

2.熟悉Xilinx ISE Design Suite 13.2开发环境使用方法。

3.熟悉Verilog HDL硬件描述语言的语法及运用。

四.实验设备与工具硬件:测试技术与嵌入式系统综合实践平台,PC机Pentium100 以上,XILINX USB调试下载器。

软件:PC机Win XP操作系统,Xilinx ISE Design Suite 13.2开发环境五.实验步骤1. 打开工程文件SYPT_FPGA.xise2. 打开freq_measure.v和period_measure.v文件,先根据定义好的模块端口输入输出信号,结合测频和测周的原理,在提示添加代码处补充代码:a. 测频模块(freq_measure.v)测频模块的基本功能是测量闸门时间内被测信号的脉冲个数。

实现过程如下:(1)由标准时钟计数产生一个预设闸门信号,然后用被测信号同步预设闸门信号产生实际闸门信号;要求:预设闸门时间可根据用户选择信号(select_parameter)在50ms、100ms、1s、10s 中切换。

具体代码如下图。

(2)标准时钟和被测信号在实际闸门内计数。

标准时钟的计数结果N s放到mea_cnt_fs 中,被测信号的计数结果为N x放到mea_cnt_fx中,输出以上计数结果,并同时输出测频完成标志mea_flag,具体代码如下图。

b. 测周模块(period_measure.v)测周模块的基本功能是把被测信号作为闸门信号,在它的一个周期的时间内,对标准时钟信号计数。

在FPGA上用VHDL实现数字频率计 实验报告

数字系统设计实验报告一、设计要求:1、(1)频率测量范围10Hz~1MHz(2)量程自动转换,量程分为10KHz (1s) 、100KHz (0.1s) 、1MHz (10ms)三档。

转换规则如下:当读数大于9999时,频率计处于超量程状态,下一次测量时,量程自动增大一档;当读数小于0999时,频率计处于欠量程状态,下一次测量时,量程自动减小一档(3)数据采用记忆显示方式,即计数过程中不显示数据,待计数过程结束以后,显示计数结果,并将此显示结果保持到下一次计数结束。

(4)用发光二极管显示量程二、方案选则1测量原理:当预置门控信号为高电平时,启动计数器,被测信号(频率为fx) 计数当预置门控信号为低电平时,关闭计数器设在一次预置门控时间Tg内对被测信号计数值为Nx,则fx= Nx / Tg2具体方案:本设计中将2MHz的时钟分三次频,分别作为防抖电路的周期信号、显示模块片选信号、计数及锁存模块闸门信号。

防抖电路滤去窄波,显示模块用模4计数器来分别输出四位测量结果。

计数器通过在0.1s内对输入信号的高电平(发生期)进行计数来得出结果,并且为了达到换挡目的,测量时计六位数,通过结果选择档位进行输出。

二、原理图三、总体电路图四、流程图五、设计清单1、防抖电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY debounce ISPORT(key,cp: IN STD_LOGIC; --复位键imp:OUT STD_LOGIC); --去掉窄波后输出END debounce;ARCHITECTURE base OF debounce ISSIGNAL ql,q2:STD_LOGIC;BEGINPROCESS(cp)BEGINIF cp'event AND cp='1'THENq2<=ql; ql<=key;END IF;END PROCESS;imp<=ql AND NOT q2;END base;时序仿真波形:2、分频电路LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY dividefre4 ISPORT(cp_2m:IN STD_LOGIC; --2MHzcpl:OUT STD_LOGIC; --200Hzcp2:OUT STD_LOGIC; --25Hzcp3:OUT STD_LOGIC); --5HzEND dividefre4;ARCHITECTURE behavior OF dividefre4 IS SIGNAL tout:INTEGER RANGE 0 TO 4999; --5000分频SIGNAL toutl:INTEGER RANGE 0 TO 7; --8分频SIGNAL tout2:INTEGER RANGE 0 TO 39; --40分频SIGNAL cp_1:STD_LOGIC;SIGNAL cp_2:STD_LOGIC;SIGNAL cp_3:STD_LOGIC;SIGNAL cp:STD_LOGIC;BEGINPROCESS(cp_2m) –分出400Hz时钟BEGINIF(cp_2m'event AND cp_2m='1')THENIF tout=4999 THENtout<=0;ELSE tout<=tout+1;END IF;IF tout=2499 THENcp<='0';ELSE cp<='1';END IF;END IF;END PROCESS;PROCESS(cp) --200Hz时钟BEGINIF(cp'event AND cp='1')THENcp_1<=NOT cp_1;END IF;END PROCESS;PROCESS(cp_1) --25Hz时钟和5HzBEGINIF(cp_1'event AND cp_1='1')THENIF toutl=7 THEN toutl<=0;ELSE toutl<=toutl+1;END IF;IF toutl=3 THENcp_2<='1';ELSIF toutl=7 THEN cp_2<='0'; --8分频得25Hz END IF;IF tout2=39 THEN tout2<=0; --40分频得5HzELSE tout2<=tout2+1;END IF;IF tout2=39 THENcp_3<='1';ELSIF tout2=19 THEN cp_3<='0';END IF;END IF;END PROCESS;cpl<=cp_1;cp2<=cp_2;cp3<=cp_3;END behavior;仿真波形:(因原程序所分频倍数太大,所以这里将5000倍分频降至50倍)3、计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY fretest ISPORT(enable:IN STD_LOGIC; --使能cp3:IN STD_LOGIC; --闸门INput:IN STD_LOGIC; --被测信号reset:IN STD_LOGIC; --复位信号overflow:OUT STD_LOGIC; --大于1000kHzPlay0,playl,play2,play3:OUT INTEGER RANGE 0 TO 9;decimal:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));--小数点,即档位END fretest;ARCHITECTURE behavior OF fretest ISSIGNAL r0_1,r1_1,r2_1,r3_1,r4_1,r5_1:INTEGER RANGE 0 TO 9;BEGINPROCESS(INput,enable,reset,cp3)BEGINIF enable='0'THEN NULL; --不测量ELSIF(input'event AND input='1')THEN --检测被测信号IF reset='1'THEN --同步复位,高电平有效overflow<='0';r0_1<=0;r1_1<=0;r2_1<=0;r3_1<=0;r4_1<=0;r5_1<=0;ELSIF cp3='0'THEN --闸门为0时清零Overflow<='0';r0_1<=0;r1_1<=0;r2_1<=0;r3_1<=0;r4_1<=0;r5_1<=0;ELSE --闸门为高电平计数r0_1<=r0_1+1;IF r0_1=9 THEN r1_1<=r1_1+1;r0_1<=0;IF(r1_1=9)THEN r2_1<=r2_1+1;r1_1<=0;IF(r2_1=9)THEN r3_1<=r3_1+1;r2_1<=0;IF(r3_1=9)THEN r4_1<=r4_1+1;r3_1<=0;IF(r4_1=9)THEN r5_1<=r5_1+1;r4_1<=0;IF(r5_1=9)THEN r5_1<=0;overflow<='1'; --大于1000kHz END IF;END IF;END IF;END IF;END IF;END IF;END IF;END IF;END PROCESS;PROCESS(r5_1,r4_1)BEGINIF r5_1=0 AND r4_1=0 THEN --为小于9999Hz时play0<=r0_1;playl<=r1_1;play2<=r2_1;play3<=r3_1;decimal<="100";ELSIF r5_1=0 THEN --为几十kHz时play0<=r1_1;playl<=r2_1;play2<=r3_1;play3<=r4_1;decimal<="010";ELSE --为几百kHz时play0<=r2_1;playl<=r3_1;play2<=r4_1;play3<=r5_1;decimal<="001";END IF;END PROCESS;END behavior;仿真波形4、锁存器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY frelatch ISPORT(reset:IN STD_LOGIC; --复位cp3:IN STD_LOGIC; --时钟Overflow: IN STD_LOGIC; --大于1000kHz表示play0,playl,play2,play3:IN INTEGER RANGE 0 TO 9;decimal:IN STD_LOGIC_VECTOR(2 DOWNTO 0);--小数点overlatch:OUT STD_LOGIC; --大于1000kHzp0latch,pllatch,p21atch,p31atch:OUT INTEGER RANGE 0 TO 9; delatch:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));--小数点END frelatch;ARCHITECTURE behavior OF frelatch ISBEGINPROCESS(cp3,reset)BEGINIF reset='1'THENoverlatch<='0';p0latch<=0;pllatch<=0;p21atch<=0;p31atch<=0;delatch<=decimal;ELSIF cp3'event AND cp3='0'THENoverlatch<=overflow;p0latch<=play0;pllatch<=playl;p21atch<=play2;p31atch<=play3;delatch<=decimal;END IF;END PROCESS;END behavior;仿真波形5、显示模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;ENTITY display ISPORT( cpl:IN STD_LOGIC; --时钟overflow:IN STD_LOGIC; --高于1000kHz标志p0,p1,p2,p3:IN INTEGER RANGE 0 TO 9;--BCD码输入 show:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--7段码输出 sel:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));--位扫描码END dISplay;ARCHITECTURE behavior OF display ISSIGNAL count: INTEGER RANGE 0 TO 3;SIGNAL sel_1:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(cpl)BEGINIF(cpl'event AND cpl='1') THENIF count=3 THEN count<=0;ELSEcount<=count+1;END IF;END IF;END PROCESS;PROCESS(count)BEGINCASE count ISWHEN 0=>sel_1<="1110"; --第0位WHEN 1=>sel_1<="1101"; --第1位WHEN 2=>sel_1<="1011"; --第2位WHEN 3=>sel_1<="0111"; --第3位END CASE;END PROCESS;PROCESS(overflow,sel_1)BEGINIF(overflow='1')THENshow<="0110111"; --高于1000kHz,显示HELSIF(sel_1(0)='0')THEN --第0位数码管译码CASE p0 ISWHEN 0=>show<="1111110";--显示0,a-gWHEN 1=>show<="0110000";--1WHEN 2=>show<="1101101";--2WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111";WHEN 9=>show<="1110011";END CASE;ELSIF(sel_1(1)='0')THEN --第1位译码 CASE p1 ISWHEN 0=>show<="1111110";WHEN 1=>show<="0110000";WHEN 2=>show<="1101101";WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111"; WHEN 9=>show<="1110011";END CASE;ELSIF(sel_1(2)= '0')THEN --第2位译码 CASE p2 ISWHEN 0=>show<="1111110";WHEN 1=>show<="0110000";WHEN 2=>show<="1101101";WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111";WHEN 9=>show<="1110011";END CASE;ELSIF(sel_1(3)='0')THEN --第3位译码 CASE p3 ISWHEN 0=>show<="1111110";WHEN 1=>show<="0110000";WHEN 2=>show<="1101101";WHEN 3=>show<="1111001";WHEN 4=>show<="0110011";WHEN 5=>show<="1011011";WHEN 6=>show<="0011111";WHEN 7=>show<="1110000";WHEN 8=>show<="1111111";WHEN 9=>show<="1110011";END CASE;END IF;END PROCESS; sel<=sel_1; END behavior; 仿真波形。

基于FPGA的高精度频率计设计

基于FPGA的高精度频率计设计摘要频率计是一种应用非常广泛的电子仪器,也是电子测量领域中的一项重要内容,而高精度的频率计的应用尤为广泛。

目前宽范围、高精度数字式频率计的设计方法大都采用单片机加高速、专用计数器芯片来实现。

传统的频率测量利用分立器件比较麻烦,精度又比较低,输入信号要求过高,很不利于高性能场合应用。

本论文完成了高精度数字频率计硬件设计和软件设计。

该数字频率计主要包括FPGA和单片机两大部分。

其中FPGA部分又可分为数据测量模块、FPGA和单片机接口模块、FPGA和数码管动态扫描部分。

FPGA部分采用verilog语言编写了电路的各模块电路,选用了当前比较流行的EDA开发软件Quartus II作为开发平台,所有模块程序均通过了编译和功能仿真验证。

对测频系统的设计流程、模型的建立和仿真做出了具体详细的研究,验证了该系统的正确性。

单片机部分采用C51编写了控制软件。

本设计中以FPGA器件作为系统控制的核心,其灵活的现场可更改性,可再配置能力,对系统的各种改进非常方便,在不更改硬件电路的基础上还可以进一步提高系统的性能。

关键词:频率计,单片机,FPGA,电子设计自动化Design of High-accuracy Digital Frequency MeterBased on FPGAABSTRACTFrequency meter is a kind of electronic instrument applied widely. A kind of high-accuracy digital frequency meter is designed based on FPGA in this paper.At present extends the scope,the high accuracy digital frequency meter's design method to use the monolithic integrated circuit to add, the special-purpose counter chip mostly to realize high speed.The design of system hardware and system software is accomplished in the paper. System consists of FGPA and MCU. The circuit based on FPGA includes following some parts: data acquisition module, interface between FPGA and MCU, module scanning number tube. Every circuit module is realized by verilog.The platform of development is Quartus II and all modules procedure is demonstrated by compiling and simulation. Detailed research of design flow, model establishment and system simulation is done. The correctness of the system is demonstrated. The software based on MCU is programmed by C51.In this design takes the systems control by the FPGA component the core, its nimble scene alterability, may dispose ability again, is convenient to system's each kind of improvement, in does not change in hardware circuit's foundation also to be possible to further enhance system's performance.The system has the advantage of high-accuracy and convenience. It’s practicability of frequency meter is well.KEY WORDS: Frequency meter, MCU, FPGA, electronic design automation目录摘要........................................................................................................................................ I ABSTRACT .............................................................................................................................. I I 第1章绪论 (1)1.1研究背景及意义 (1)1.2国内外研究现状 (1)1.2.1 频率计的测量方法 (1)1.3EDA技术简介 (3)1.4本论文内容及安排 (4)第2章频率测量方法与原理 (6)2.1直接测频法 (6)2.2利用电路的频率特性进行测量 (7)2.2.1 电桥法测频 (8)2.2.2 谐振法测频 (8)2.2.3 频率—电压转换法测频 (8)2.3等精度测量法 (8)2.4本章小结 (10)第3章系统总体设计方案 (11)3.1频率计系统设计任务与分析 (11)3.1.1 频率计系统设计任务要求 (11)3.1.2 频率计系统设计任务分析 (11)3.2系统总体设计方案 (11)3.3FPGA内部功能模块设计 (12)3.4本章小结 (14)第4章系统的硬件电路设计 (15)4.1FPGA部分的硬件设计 (15)4.1.1 FPGA简介 (15)4.1.2 FPGA芯片的选型 (15)4.2单片机部分的硬件电路设计 (17)4.2.1 单片机的选型原则 (17)4.2.2 单片机控制电路的设计 (18)4.3外围电路设计 (19)4.3.1 键盘接口电路 (19)4.3.2 显示电路 (19)4.3.3 电源电路 (20)4.3.4 信号放大整形电路 (20)4.3.4 其它电路 (21)4.4本章小结 (22)第5章系统的软件设计 (23)5.1VERILOG HDL语言简介 (23)5.2QUARTUS II软件简介 (24)5.3基于EDA技术的设计方法 (25)5.3.1 自底向上的设计方法 (25)5.3.2 自顶向下的设计方法 (26)5.4FPGA内部功能模块设计 (26)5.4.1 D触发器模块 (27)5.4.2 32位高速计数器模块 (28)5.4.3 二选一选择器模块 (29)5.4.4 并—串转换接口模块 (31)5.4.5 串—并转换接口模块 (31)5.4.6 二进制数到8421BCD码转换模块 (32)5.4.7 LED动态扫描显示控制模块 (33)5.5单片机部分的软件设计 (35)5.6本章小结 (36)第6章结论 (37)致谢 (39)参考文献 (40)附录I 顶层原理图 (42)附录II VERILOG程序源代码 (43)基于FPGA的高精度频率计设计 1第1章绪论1.1 研究背景及意义在电子测量技术领域内,频率是一个最基本的参数。

一种基于FPGA的高精度频率测量电路设计

一种基于FPGA的高精度频率测量电路设计摘要:介绍了一种基于FPGA的采用等精度测量方法的频率测量电路设计。

阐述了等精度频率测量的原理与方法,介绍了射频信号调理方法、分频电路设计、高稳晶振的选择与射频信号放大电路设计。

经实际应用证明,该频率测量电路在0.5MHz到1.2GHz频率范围内,频率测量精度可达到5×10-8,符合实际应用的要求。

关键词:FPGA;等精度测量;高稳晶振;信号放大中文引用格式:0 引言频率测量电路广泛应用于通信系统收信机、发信机性能指标测试。

频率是指在单位时间内周期信号变化的次数。

频率通常用符号f来表示,其基本单位为Hz,在无线电技术中,经常使用kHz、MHz以及GHz来作为频率单位[1]。

常用的频率测量方法有直接计数法、模拟内插法与等精度测量法。

等精度测量法首先给出宽度一定的预置闸门脉冲,利用D触发器实现预置闸门时间与被测信号同步从而使闸门时间是被测信号整数倍,同时统计闸门时间内标准信号脉冲个数,从而得到被测信号频率,等精度频率测量存在标准信号±1Hz误差,通过提高标准信号频率可以减小测量误差。

等精度频率测量可以实现整个测试频段等精度测量。

1 等精度测频原理采用等精度测频法实现频率测量,利用两个计数器分别对被测信号和标准时钟进行计数,而且这两个计数器的使能信号是将预制闸门信号经由被测信号同步而产生,保证闸门时间是被测信号周期的整数倍。

因此消除了对被测信号计数所产生的±1Hz误差。

测量原理框图如图1所示。

图1 频率测量原理框图预置闸门时间为T,经过D触发器处理后变为与被测信号同步的实际闸门T1。

标准时钟频率为f0,计数值为N0,被测信号计数值为Nx,被测信号频率为f0×Nx / N0。

被测信号的相对测量误差与闸门时间和标准时钟频率有关,频率测量精度≤1/(T1×f0)。

2 系统软硬件设计系统由硬件与软件两部分组成。

硬件包括FPGA信号处理电路、射频信号输入衰减电路、分频电路、信号调理电路、高稳晶振电路与显示电路。

基于fpga的数字频率计设计

基于FPGA的数字频率计设计随着科学技术的不断进步,数字电子技术在各个领域都得到了广泛的应用。

其中,FPGA(现场可编程门阵列)作为一种灵活、可编程、可重构的数字电路设备,具有较高的性能和灵活性,被广泛应用于数字信号处理、通信、图像处理等各个领域。

本篇文章将介绍基于FPGA的数字频率计设计。

一、概述数字频率计是一种用于测量信号频率的设备,可以方便快速地获取信号的频率信息。

传统的数字频率计通常采用微处理器或专用集成电路来实现,但是这些方案在某些应用场景下存在着局限性。

使用FPGA来设计数字频率计,既可以充分利用FPGA的灵活性和并行性,又可以实现高性能和低功耗的设计。

二、基于FPGA的数字频率计设计原理基于FPGA的数字频率计主要通过计数器和时钟信号来实现。

其设计原理可以分为以下几个步骤:1. 时钟信号同步:通过FPGA内部的PLL(锁相环)模块,可以实现时钟信号的同步和稳定。

2. 信号输入:将待测信号输入FPGA,可以通过外部接口或模拟输入模块实现。

3. 计数器设计:利用FPGA内部的计数器模块,对输入信号进行计数,从而获取信号的频率信息。

4. 频率计算:根据计数器的计数值和时钟信号的周期,可以计算出输入信号的频率信息。

三、基于FPGA的数字频率计设计实现基于上述原理,可以利用FPGA内部的逻辑资源,设计出一个高性能的数字频率计。

具体实现步骤如下:1. 确定输入信号的接口:选择适合的输入接口,可以是数字信号接口、模拟信号接口或者通用IO口。

2. 设计计数器模块:根据待测信号的频率范围和精度要求,设计合适的计数器模块,可以结合FPGA的时钟管理模块实现高精度计数。

3. 编写频率计算算法:根据计数器得到的计数值和时钟信号的周期,设计频率计算算法,可以采用移位运算、累加运算等实现高效的频率计算。

4. 实现显示与输出:设计合适的显示模块和输出接口,将测得的频率信息在显示屏或者外部设备上进行输出。

四、基于FPGA的数字频率计设计应用基于FPGA的数字频率计设计可以广泛应用于各种领域,如通信、测控、仪器仪表等。

基于FPGA自适应数字频率计的设计

( 武汉理工大学 自动化学院, 湖北 武汉 4 0 7 ) 3 0 0 摘 要: 介绍一种以 F G Fe rga mal G t Ary为核心 , 于硬件描述语言 V L的数字频率计设计与 P A( id Porm be a r ) l e a 基 HD

中图 分 类号 :N 4 T 7 文 献 标识 码 : A 文 章 编 号 :6 2- 8 (07 0 - 1 I0 1 7- 94 2 0 )2 04 -4 - 4 -

Auo-dut gd tlcmo trbsd O P t- jsi i a y mee ae H F GA a n

CE EN S a g z i h n - h ,HU n - i n , HU i - o Ro g- a g q t e sng

(c olo u m tn Wu a nvr t o eh o g , hn 4 0 7 ,hn ) S ho fA t a o , hn U i s y f c nl y Wua 3 0 0 C ia o i e i T o

但价格不菲 。为适应实际工作的需要 , 本文在简述

得这个周期性信号的重复变化次数 Ⅳ,则其频率可 衰示 为 N 。 数字频率计测频率的原理框 图可示如图 1a。 () 其 中脉冲形成电路 的作用是 : 将被测信号变成脉冲

频率测量的基本原理和方法 的基础上 , 提供一种基 于 FG P A的数字频率计的设计和实现过程 ,本方案 不但切实可行 , 而且具有 成本低廉 、 小巧轻便 、 便于

维普资讯

第 0 7 3月 3 3卷第 期 20 年 2

C I A ME S R ME T I HN 【 Y H N A中国测试技术 U E N EC 0 0G

基于FPGA的频率计电路设计

D s g o i C i i r q e c 0 n e a e n F G e i n f C r U n F e u n y C u t r B s s o P A t

韩团军

H nT a jn a un u

( 陕西理工学院,陕西 汉 中 73 0 ) 200 (hn x n v r iy o eh o o y h a x I zo g 7 30 ) S a n i U ie s t f T cn lg ,Sa n it n h n 2 0 0 a

摘

要 : 文介绍 了数字频率计设计的基本原理 , 本 对频率计所采用各种硬件除法进行 了比较 , 提出 了 倍频计数法测量数 字

高频的实现 方案 , 并给 出了频率计设计 的硬 件电路原理和软件 实现 , 结果表 明这 种方法实现 了频率计 的高速和高精度 。

关键词 : 频率计; 倍频 ; 计数法 中图分类号 :M 3 T 95 文献标识码 : A 文章编号: 6 1 4 9- 2 1 )- 1 4 0 1 7 - 72 (0 0i 0 8 - 3

0 引 言

波电路和最后的数据显示电路 。

2 1 C c oe F G . yl n P A芯片内部 电路设计思想

本研究 利用了 F G P A的集成度高 、 稳定性可靠 、 可直接 编 程的优点, 采用倍频计数法应 用 FG 设 计频 率计 电路, PA 相对

( 控制部分 电路设计 思想 : 1 ) 由于要求每 0 1s . 输出数 m 据一 次, 也就 是说每 0Is . 计数 一次, m 计数完后 重新 开始 计

hi h pe and g -s ed hi - cu ac f qu c c u e gh ac r y re en y o nt r.

基于FPGA与单片机的等精度频率计的设计

c h i p m i c r o c o m p u t e r . T h i s s y s t e m w a s ma i n  ̄c o mp o s e d o f he t s i g n a l a mp l i i f c a t i o n s h a p i n g c i r c u i t , s i n le g - c h i p mi c r o c o m p u t e r

中图分类号 : T N 4 9 2 文献标识码 : A 文 章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 3 ) 2 2 — 0 1 7 1 — 0 3

De s i g n o f e q ua l pr e c i s i o n c y mo me t e r b a s e d o n FPGA a nd S CM

Ab s t r a c t : Ac c o r d i n g t o t h e p i r n c i p l e o f e q u a l p r e c i s i o n me a s u r e me n t , a c y mo me t e r wa s d e s i g n e d b a s e d o n F P GA a n d s i n g l e -

基于FPGA的等精度频率计设计

基 准 时 钟 ቤተ መጻሕፍቲ ባይዱ 号

CNT1 CNT1 cLK CNT1 ENA

实 验 证 明 ,通 过 该 方 法并 采 用 10MH 的工 0 z

C ut[ 10 o nl3 】

CLR

作 频 率 实 现 一个 8 B D 的 串行 减 法 运 算 ,其 位 C 码

维普资讯

第9 卷

第 1 期 1

电子元 嚣 件 焘 用

Elc rn cCo o e t De i eAp l ain e t i mp n n & o vc pi t s c o

Vo . No 1 1 .1 9

NO .20 V 07

码 分 为P 宽为4 个 的二 进制 数 ,然 后从低 位开 始相 减 ,并 在P 时钟 周 期 内 完成 减 法操 作 。如果 输 个

入 的操 作 数 位 数 为 8 ,那 么 串行B D码减 法器 即 C 可在 8 时钟周期 内完成8 C 码减 法运算 。 个 位B D

成 时基 控制 闸门 。然后 测 量 闸门输 出的计 数 脉

2 串行 B D 除 法 C 码

以上 三 种 方 案均 用 到 了定 义式 :F N T = / ,也

来进 行 : 方 法 一 :完 全 按 定 义 式 F Ⅳ 7 行 测 量 。 = /1 进 被 测信 号 经 放 大 整形 以形 成 时标 ,晶振 经 分 频形 成 时 基 。然 后 用 时基 开 闸 门 ,累计 时标 的个 数 ,则 由公 式 可得 :F= /xN T 。此 方案  ̄ I = /R r 为传统 的测 频方 案 ,其测 量精 度将 随被测 信 号频

变 化 ,但测 量 精度将 不会 随着 被 测信 号频 率 的下

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

采用fpga实现发电机组频率测量计的设计

1 引言

在现代社会中,电资源成为人们生活当中不可缺少的一部分,而发电机和电动机在电力系统中扮演着非常重要的角色。

在很多场合,需要对电机组和电网的频率进行测量。

目前,频率测量的电路系统很多,这里介绍一种数字电路测频:基于fpga的发电机组的频率测量计。

随着电子技术的不断发展和进步,以eda为代表的数字电路设计发生很大变化。

在设计方法上,已经从“电路设计—硬件搭试—焊接”的传统设计方式到“功能设计—软件模拟—下载调试”的电子自动化设计模式。

在这种状况下,以硬件描述语言(hardware descrtption language)和逻辑综合为基础的自顶向下的电子设计方法得到迅速发展。

verilog hdl语言是目前应用最广泛的硬件描述语言,它是在c 语言的基础上发展起来的,语法较为自由灵活、拥有广泛的学习群体、资源比较丰富,且轻易学简单易懂。

本文发电机组频率测量计的设计是在verilog hdl语言的基础上展开的,源程序经过altera 公司的quartusⅱ5.0软件完成了综合、仿真(功能仿真和时序仿真),fpga(field programmable gate array,现场可编程门阵列) 选用的是cyclone系列的ep1c3t144c6器件。

2 频率测量电路

2.1频率测量的总体电路

采用电压互感器取来自于发电机组端电压或电网电压的测频输入信号,经削波、滤波处理后,变成幅度基本不变的稳定波形,经放大电路将信号放大整形,再用电压比较电路将具有正负幅值的方波变成只有正幅值的方波信号。

然后,通过光电耦合器使fpga的数字系统与输入信号隔离。

fpga数字系统利用标准的1hz信号对隔离后的方波信号的脉冲个数进行计数,得到信号的频率数,该频率数经数码管显示。

由于发电机组的频率与发电机组端电压有关系,可以从频率的变化得到发电机组端电压的变化。

从系统总体框图如图1所示,从中可以看出,该fpga 数字系统与输入通道隔离,因而大大提高了系统硬件的抗干扰能力。

图1 系统总体框图

2.2频率测量的原理

频率测量的原理是计算每秒钟待测信号的脉冲个数,也就是利用标准的1hz (周期为1s) 脉宽信号对输入的待测信号的脉冲进行计数,1秒计数结束后对采集到脉冲个数送到数码管显示。

测频控制器有3个输入信号:samplefreq为标准的脉冲信号,reset是复位控制信号,start是开始测量信号;3个输出信号:endmeasure是结束测量信号(计数复位和转换复位),gate是答应计数信号(即门控信号),enableconvert是开始转换信号。

控制流程是先对频率计复位,再开始测量,在samplefreq信号的上升沿,gate 信号使能使计数器开始工作,到samplefreq的下一个上升沿,gate反转成低电平使计数器停止计数,同时enableconvert使转换器开始转换二进制数(转换时间低于1s)。

转换结束后,十进制数经过7段显示译码器译码,然后在数码管中显示所测信号的频率。

由于enableconvert信号的使用使数码管数据显示稳定,不会

出现闪烁。

进行下次测量之前要对频率计进行复位,使数码管的数字显示清零,为下次显示做预备。

本文设计的数字频率计有六个模块组成:测频控制模块(control)、十分频模块(divfreq)、二进制计数器模块(counter)、锁存器模块(latch)、二进制到十进制的转换器模块(bit2bcd)、7段显示译码器模块(led_encoder)。

3 频率测量计的设计

本次设计采用verilog hdl语言,运用自顶向下的设计理念。

将系统按功能按层次化分,首先定义顶层功能模块,并在顶层功能模块内部的连接关系和对外的接口关系进行了描述, 而功能块的逻辑功能和具体实现形式则由下一层模块来描述。

整个设计分两步:第一步利用quartus ⅱ5.0图形块输入方式设计顶层模块,顶层图形块如图2所示;第二步在顶层模块中为每个图形块生成硬件描述语言(verilog hdl),然后在生成的verilog hdl设计文件中,对低层功能模块的功能进行描述设计。

图2 顶层图形块

3.1 测频控制模块设计

这是三输入三输出模块,测频控制模块波形仿真如图3所示,如用verilog hdl描述为:

module control (clk,reset,start,enableconvert,gate,endmeasure);

input reset,start,clk;

output enableconvert,gate,endmeasure;

reg enableconvert,gate,endmeasure;

always @ (posedge clk posedge reset)

begin

if (reset)

begin

endmeasure <= 1'b1 ;

enableconvert <=1'b0 ;

gate <= 1'b0 ;

end

else

begin

endmeasure <= 1'b0 ;

if (start)

begin

gate <= ~gate ;

enableconvert <= gate ;

end

end

end

endmodule

图3 测频控制器波形仿真时序图

3.2 二进制到十进制的转换器模块设计

本设计,需要转换时钟convertfreq信号对转换模块进行时序控制,由于要在1s 内完成转换,则转换时钟convertfreq的频率应该选用高频频信号,即转换时钟convertfreq的频率是标准时钟samplefreq信号10分频得到的。

为了对本设计进行波形仿真,取输入的10位二进制数bin[9..0]为10’b0000011001(十进制为25)。

图4为二进制到十进制的转换器的仿真时序图:

图4 二进制到十进制的转换器的仿真时序图

4 仿真和调试

通过上述的描述,从各个模块独立的角度对其进行了仿真,结果表明设计符合要求。

为了保证系统的整体可靠性,对整个系统做了仿真,仿真时序图如图5所示:

图5 系统仿真时序图

其中,ledd,ledc,ledb,leda是译码的结果要在7段数码管上显示,0010010(显示为2)、0100100(显示为5)。

将设计的频率测量计下载到目标芯片ep1c3t144c6中,并在gw48实验箱上进行的模拟仿真,当输入频率为1 hz~1023 hz的信号时,频率测量计所测的频率完全准确,当频率高于1023hz时,系统报警,同时频率显示为0。

5 结束语

基于fpga设计的发电机组频率测量计,系统在整体上采用光电耦合器的隔离方式,提高系统的抗干扰能力和稳定性。

该系统具有线路简单可靠、通用性强、稳定度高等优点,可广泛应用于频率电压变换器、转速继电器。

该设计的fpga数字系统部分使用verilog hdl语言,给出核心程序,并可以通过verilog hdl语言的综合工具进行相应硬件电路的生成,具有传统逻辑设计方法所无法比拟的优越性。

经过仿真后,验证设计是成功的, 达到预期结果。

同时这种方法设计的数字电子系统可移植性强、可更改性好。

假如需要的频率测量范围需要扩大,不需要硬件变化只需改变软件就可以,相对非常方便。