Analysis of Checksum-Based Execution Schemes for Pipelined Processors

Objectives

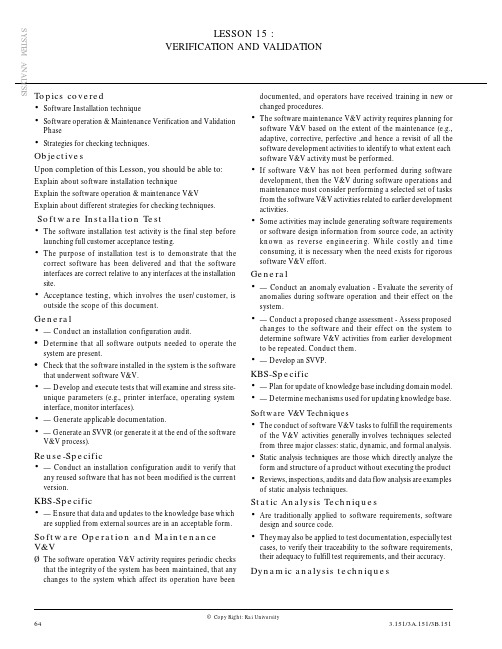

SYSTEM ANALYSISLESSON 15 :VERIFICATION AND VALIDATIONTopics covered•Software Installation technique•Software operation & Maintenance Verification and ValidationPhase•Strategies for checking techniques.ObjectivesUpon completion of this Lesson, you should be able to :Explain about software installation technique Explain the software operation & maintenance V&V Explain about different strategies for checking techniques.Software Installation Test•The software installation test activity is the final step beforelaunching full customer acceptance testing.•The purpose of installation test is to demonstrate that thecorrect software has been delivered and that the software interfaces are correct relative to any interfaces at the installation site.•Acceptance testing , which involves the user/customer, isoutside the scope of this document.General •— Conduct an installation configuration audit.•Determine that all software outputs needed to operate thesystem are present.•Check that the software installed in the system is the softwarethat underwent software V&V.•— Develop and execute tests that will examine and stress site-unique parameters (e.g., printer interface, operating system interface, monitor interfaces).•— Generate applicable documentation.•— Generate an SVVR (or generate it at the end of the softwareV&V process).Reuse-Specific•— Conduct an installation configuration audit to verify thatany reused software that has not been modified is the current version.KBS-Specific•— Ensure that data and updates to the knowledge base whichare supplied from external sources are in an acceptable form.Software Operation and Maintenance V&VØThe software operation V&V activity requires periodic checks that the integrity of the system has been maintained, that any changes to the system which affect its operation have beendocumented, and operators have received training in new or changed procedures.•The software maintenance V&V activity requires planning forsoftware V&V based on the extent of the maintenance (e.g.,adaptive, corrective, perfective ,and hence a revisit of all the software development activities to identify to what extent each software V&V activity must be performed.•If software V&V has not been performed during softwaredevelopment, then the V&V during software operations and maintenance must consider performing a selected set of tasks from the software V&V activities related to earlier development activities.•Some activities may include generating software requirementsor software design information from source code, an activity known as reverse engineering. While costly and time consuming, it is necessary when the need exists for rigorous software V&V effort.General•— Conduct an anomaly evaluation - Evaluate the severity ofanomalies during software operation and their effect on the system.•— Conduct a proposed change assessment - Assess proposedchanges to the software and their effect on the system to determine software V&V activities from earlier development to be repeated. Conduct them.•— Develop an SVVP.KBS-Specific•— Plan for update of knowledge base including domain model.•— Determine mechanisms used for updating knowledge base.Software V&V Techniques•The conduct of software V&V tasks to fulfill the requirementsof the V&V activities generally involves techniques selected from three major classes: static, dynamic, and formal analysis.•Static analysis techniques are those which directly analyze theform and structure of a product without executing the product•Reviews, inspections, audits and data flow analysis are examplesof static analysis techniques.Static Analysis Techniques•Are traditionally applied to software requirements, softwaredesign and source code.•They may also be applied to test documentation, especially testcases, to verify their traceability to the software requirements,their adequacy to fulfill test requirements, and their accuracy.Dynamic analysis techniquesSYSTEM ANALYSIS•Involve execution, or simulation, of a development activityproduct to detect errors by analyzing the response of a product to sets of input data .•For these techniques, the output values, or ranges of values,must be known.•Testing is the most frequent dynamic analysis technique.Prototyping, especially during the software requirements V&V activity, can be considered a dynamic analysis technique; in this case the exact output is not always known but enough knowledge exists to determine if the system response to the input stimuli meets system requirements.•Formal analysis is the use of rigorous mathematical techniques to analyze the algorithms of a solution .•Sometimes the software requirements may be written in a formal specification language (e.g., VDM, Z) which can be verified using a formal analysis technique like proof-of-correctness.•The term formal often is used to mean a formalized process,that is, a process that is planned, managed, documented, and is repeatable. In this sense, all software V&V techniques are formal,but do not necessarily meet the definition of the mathematical techniques involving special notations and languages.Strategies for Choosing Techniques•Some software V&V techniques used during softwarerequirements V&V tasks are control flow analysis, data flow analysis, algorithm analysis, and simulation.•Control and data flow analysis are most applicable for real timeand data driven systems.•These flow analyses transform logic and data requirements textinto graphic flows which are easier to analyze than the text.PERT, state transition, and transaction diagrams are examples of control flow diagrams.•Algorithm analysis involves re-derivation of equations or evaluation of the suitability of specific numerical techniques.•Simulation is used to evaluate the interactions of large, complex systems with many hardware, user, and other interfacing software units.•Some software V&V techniques used during software designV&V tasks include algorithm analysis, database analysis, sizing and timing analysis, and simulation.•Algorithm analysis examines the correctness of the equationsor numerical techniques as in the software requirements activity,but also examines truncation and round-off effects, numerical precision of word storage and variables (e.g., single- vs.extended-precision arithmetic), and data typing influences.•Database analysis is particularly useful for programs that storeprogram logic in data parameters.• A logic analysis of these data values is required to determinethe effect these parameters have on program control. Sizing and timing analysis is useful for real-time programs having response time requirements and constrained memory execution space requirements.•Some software V&V techniques used during code V&V tasksare control flow analysis, database analysis, regression analysis,and sizing and timing analysis.•For large code developments, control flow diagrams showingthe hierarchy of main routines and their sub functions are useful in understanding the flow of program control.•Database analysis is performed on programs with significantdata storage to ensure common data and variable regions are used consistently between all call routines.•Data integrity is enforced and no data or variable can be accidentally overwritten by overflowing data tables. Data typing and use are consistent throughout all program elements.•Regression analysis is used to reevaluate software requirements and software design issues whenever any significant code change is made.•This technique ensures project awareness of the original system requirements.•Sizing and timing analysis is done during incremental codedevelopment and compared against predicted values. Significant deviations between actual and predicted values is a possible indication of problems or the need for additional examination.•Another area of concern to software V&V is the ability ofcompilers to generate object code that is functionally equivalent to the source code, that is, reliance on the correctness of the language compiler to make data dependent decisions about abstract programmer coded information.•For critical applications, this problem is solved by validatingthe compiler or by validating that the object code produced by the compiler is functionally equivalent to the source.•Code reading is another technique that may be used for sourcecode verification. An expert reads through another programmer’s code to detect errors. In an experiment conducted at the National Aeronautics and Space Administration Goddard Space Flight Center, code reading was found to be more effective than either functional testing or structural testing.•The reason was attributed to the expertise of the readers who,as they read the code, were simulating its execution and were able to detect many kinds of errors.•Other techniques commonly used are walkthroughs,inspections and reviews.•These tasks occur in interactive meetings attended by a team which usually includes at least one member from the development group. Other members may belong to the development group or to other groups involved in software development.•The duration of these meetings is usually no more than a fewhours in which code is examined on a line-by-line basis. In these dynamic sessions, it may be difficult to examine the code thoroughly for control logic, data flow, database errors, sizing,timing and other features which may require considerable manual or automated effort. Advance preparation for these activities may be necessary and includes code analysis techniques.•The results of these techniques provide appropriate engineeringinformation for discussion at meetings where code is evaluated.SYSTEM ANALYSIS•Regardless of who conducts or participates in walkthroughs and inspections, software V&V analyses may be used tosupport these meetings.• A comprehensive test management approach to testing recognizes the differences in strategies and in objectives forunit, software integration, and software system test.•Unit test verifies the design and implementation of software units. Software integration test verifies functional requirementsas the software units are integrated.•Special attention is focused on software, hardware, and operator interfaces. Software system test validates the entire softwareprogram against system requirements and software performanceobjectives. Software system tests validate that the softwareexecutes correctly within its stated operating environment.•The software’s ability to deal properly with anomalies and stress conditions is emphasized.•These tests are not intended to duplicate or replace the user and development group’s test responsibilities, but insteadsupplement the development testing to test behavior notnormally tested by the user or development group.•Effective testing requires a comprehensive understanding of the system. Such understanding develops from systematicallyanalyzing the software’s concept, requirements, design, andcode.•By knowing internal software details, software V&V testing is effective at probing for errors and weaknesses that reveal hiddenfaults.•This is considered structural, or white-box, testing. It often finds errors for which some functional, or black-box, test casescan produce the correct output despite internal errors.•Functional test cases execute part or all of the system to validate that the user requirement is satisfied; these test cases cannotalways detect internal errors that will occur under specialcircumstances.•Another software V&V test technique is to develop test cases that violate software requirements.•This approach is effective at uncovering basic design assumption errors and unusual operational use errors.•The process of planning functional test cases requires a thorough examination of the functional requirements.•An analyst who carefully develops those test cases is likely to detect errors and omissions in the software requirements.•In this sense test planning can be effective in detecting errors and can contribute to uncovering some errors before testexecution.•The planning process for testing must take into account the specific objectives of the software V&V for the software andthe impact of different test strategies in satisfying theseobjectives.•Frequently, the most effective strategy may be to combine two or more strategies.•Criticality analysis may be used to identify software V&V techniques to address high-risk concerns.•The selection of V&V techniques for use on each critical area of the program is a method of tailoring the intensity of the software V&V against the type of risk present in each area of the software.•For example, software V&V would apply algorithm analysis to critical numerical software functions, and techniques such as sizing and timing analysis, data and control flow analysis and interface analysis to real-time executive functions. Descriptions of Techniques The following are summary descriptions of techniques taken from [BAHILL], [BEN], [EWICS3], [KIRANI], [NBS93], [NGUYEN], [NIST209], [NIST5589], [NUREG6316], [OKEEFE], [OLEARY], [TURING], [VOAS91,92,95], [WALLACE94], and [WILEY]. Algorithm analysis examines the logic and accuracy of the software requirements by translating algorithms into some language or structured format. The analysis involves rederiving equations or evaluating the suitability of specific numerical techniques. It checks that algorithms are correct, appropriate, stable, and meet all accuracy, timing, and sizing requirements. Algorithm analysis examines the correctness of the equations and numerical techniques, truncation and rounding effects, numerical precision of word storage and variables (single vs. extended-precision arithmetic), and data typing influences. Issues: accuracy; algorithm efficiency; correctness; consistency in computation; error propagation; numerical roundoff; numerical stability; space utilization evaluation; system performance prediction; timing.Analytic modeling provides performance evaluation and capacity planning information on software design. It represents the program logic and processing of some kind of model and analyzes it for sufficiency. Issues: accuracy; algorithm efficiency; bottlenecks; error propagation; feasibility; modeling; numerical roundoff; numerical stability; processing efficiency; system performance prediction.Back-to-back testing detects test failures by comparing the output of two or more programs implemented to the same specification. The same input data is applied to two or more program versions and their outputs are compared to detect anomalies. Any test data selection strategy can be used for this type of testing, although random testing is well suited to this approach. Also known as comparison testing. Issues: anomalies or discrepancies between versions.Boundary value analysis detects and removes errors occurring at parameter limits or boundaries. The input domain of the program is divided into a number of input classes. The tests should cover the boundaries and extremes of the classes. The tests check that the boundaries of the input domain of the specification coincide with those in the program. The value zero, whether used directly or indirectly, should be used with special attention (e.g., division by zero, null matrix, zero table entry). Usually, boundary values of the input produce boundary values for the output. Test cases should also be designed to force the output to its extreme values. If possible, a test case which causes output to exceed the specification boundary values should be specified. If output is a sequence of data, special attention should be given to the first and last elements and to lists containing zero, one, and two elements. Issues: algorithm analysis; array size; inconsistencies between limits; specification error.SYSTEM ANALYSISCode reading involves an expert reading through another programmer’s code to detect errors. The individual is likely to perform a pseudo-execution (mentally) of the code to pick up errors before compilation. Issues: correctness; misuse of variables;omitted functions; parameter checking; poor programming practices; redundancy.Control flow analysis transforms text describing software requirements into graphic flows where they can be examined for correctness. It checks that the proposed control flow is free of problems (e.g., unreachable or incorrect software design). Control flow analysis is used to show the hierarchy of main routines and their subfunctions and checks that the proposed control flow is free of problems (e.g., unreachable or incorrect code elements). It detects poor and potentially incorrect program structures. Issues:assertion testing/violations; bottlenecks; boundary test cases;branch and path identification; branch testing; cell structure of units; correctness; software design evaluation; error propagation;expected vs. actual results; file sequence error; formal specification evaluation; global information flow and consistency; hierarchical interrelationship of units; inaccessible code; software integration tests; inter-unit structure; loop invariants; path testing; processing efficiency; retest after change; system performance prediction; test case preparation; unit tests.Coverage analysis measures how much of the structure of a unit or system has been exercised by a given set of tests. System level coverage measures how many of the unit parts of the system have been called by a test set. Code coverage measures the percentage of statements, branches, or lines of code (LOC) exercised by a test set. Issues: unit tests, software integration tests, software system tests.Critical timing/flow analysis checks that the process and control timing requirements are satisfied by modeling those aspects of the software design. Issues: modeling; synchronization; timing.Database analysis ensures that the database structure and access methods are compatible with the logical design. It is performed on programs with significant data storage to ensure that common data and variable regions are used consistently between all calling routines; that data integrity is enforced and no data or variable can be accidentally overwritten by overflowing data tables; and that data typing and use are consistent throughout the program. Issues:access protection; data characteristics and types; software design evaluation; file sequence error; global information flow; processing efficiency; space utilization evaluation; unit tests.Data flow analysis is important for designing the high level (process) architecture of applications. It can check for variables that are read before they are written, written more than once without being read, and written but never read. Issues: assertion testing/violations; bottlenecks; boundary test cases; branch and path identification; branch testing; cell structure of units; data characteristics; environment interaction; error propagation;evaluation of program paths; expected vs actual results; file sequence error; global information flow and consistency; hierarchical interrelationship of units; inter-unit structure; loop invariants;processing efficiency; retest after changes; software design evaluation; software integration tests; system performance prediction; test case preparation; uninitialized variables; unused variables; variable references.Decision (truth) tables provide a clear and coherent analysis of complex logical combinations and relationships. This method uses two-dimensional tables to concisely describe logical relationships between boolean program variables. Issues: logic errors.Desk checking involves the examination of the software design or code by an individual, usually an expert other than the author, for obvious errors. It can include looking over the code for obvious defects, checking for correct procedure interfaces, reading the comments to develop a sense of what the code does and then comparing it to its external specifications, comparing comments to software design documentation, stepping through with input conditions contrived to “exercise” all paths including those not directly related to the external specifications, and checking for compliance with programming standards and conventions. Issues:anachronistic data; calls to subprograms that do not exist; data fields unconstrained by data boundaries; failure to implement the design; failure to save or restore registers; improper nesting of loops and branches; improper program linkages; improper sequencing of processes; incomplete predicates; incorrect access of array components; inefficient data transport; infinite loops;initialization faults; input-output faults; instruction modification;inverted predicates; mismatched parameter lists; missing labels or code; missing validity tests; misuse of variables; prodigal programming; unauthorized recursion; undeclared variables;unreachable code; unreferenced labels.ReviewSoftware Installation techniqueSoftware operation & Maintenance Verification and Validation PhaseStrategies for checking techniques.]Various TechniquesQuestionsExplain about Software Installation technique 12345Explain about operation and maintenance V&V.12345Explain about software V&V techniques.12345SYSTEM ANALYSIS Discuss the various types of techniques used in V&V.12345ReferencesHeuring, Vincent P.Computer systems design and architectureDelhi : Pearson Education Asia, 1997 Whitten, Jeffrey L.Systems analysis and design methods5th ed. New Delhi : Galgotia Publications, 2001 Shelly, Gary B.Systems analysis and design3rd ed. New Delhi : Galgotia Publications, 1999 Awad, Elias M.Systems analysis and designNew Delhi : Galgotia Publications, 1997 Hoffer, Jeffrey A.Modern systems analysis and design2nd ed. Delhi : Pearson Education Asia, 2000 Sarkar, A.K.Systems analysis, data processing andquantitative techniquesNew Delhi : Galgotia Publications, 1997 Hawryszkiewycz, IgorIntroduction to systems analysis & design4th ed. New Delhi : Prentice Hall of India, 2002。

爱立信告警处理

建议人

告警标题

爱立信 wnms\超级管理员 爱立信 wnms\超级管理员 爱立信 wnms\超级管理员

AXE PARAMETER DATABASE FAULT BACKUP INFORMATION FAULT BLOCKING RESTRICTION ON ROUTES SUPERVISION

爱立信 爱立信 爱立信 爱立信

AP PROCESS REINITIATED AP FAULT IO STORAGE SPACE WARNING

爱立信 爱立信 爱立信 爱立信

wnms\超级管理员 wnms\超级管理员 wnms\超级UT FAULT AP REBOOT CP AP COMMUNICATION FAULT AP DIAGNOSTIC FAULT

GROUP SWITCH CLM CONTROL GROUP SWITCH FAULT

爱立信 wnms\超级管理员 爱立信 wnms\超级管理员

DISTRIBUTED GROUP SWITCH TRAFFIC RESTRICTIONS GROUP SWITCH UNIT MANUALLY BLOCKED

爱立信 wnms\超级管理员 爱立信 wnms\超级管理员 爱立信 wnms\超级管理员

DIGITAL PATH FAULT SUPERVISION SEMIPERMANENT CONNECTION FAULT VOLUME LIMIT EXCEEDED

爱立信 wnms\超级管理员 爱立信 wnms\超级管理员

CCITT7 EVENT REPORTING THRESHOLD REACHED CCITT7 DISTURBANCE SUPERVISION LIMIT REACHED

一种针对半导体制造工艺的全面动态取样方案

电子技术• Electronic Technology88 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】动态取样 工艺风险 Cpk1 介绍现如今随着半导体制造过程的复杂性不断提升,采用科学有效的工艺管控方法来帮助快速侦测并改进异常工艺表现是非常重要的。

工艺管控方法中最有效的方法就是改进取样方案。

通过高效的取样方案,能够快速检测到工艺的偏离,并实现改进和预防措施。

目前业界常用的取样方法是在初始阶段建立,之后根据需要人工改变频率。

本文介绍了一种新的动态取样解决方案,通过采用工艺风险评估并配合多种因素作用,实现针对不同工艺风险的取样决定。

2 全面动态取样方案全面动态取样系统是基于工艺状况、机台情况、工艺不确定性、异常事件信号以及量测机台产能来调整取样率的。

我们根据工艺风险将取样方案分成三个区间,即低-基准-高。

当工艺流程处在一个较低的风险级时,取样在低频率下进行,反之将在高频率下进行。

如果线上工艺流程表现出向高风险发展的趋势,取样率会随着提升,并伴随改进方案的实施,从而减少风险产品的数量。

反之取样率会随之降低,量测机台的产能得到缓解,同时低取样率也能够缩短制造工艺的周期。

本文的取样方案是以传统方案作为框架并配合动态改变取样率实现的。

下面对各影响因素作介绍:2.1 工艺状况整体的工艺状况代表了生产出满足客户需求的产品的能力。

线上量测的图表是一个表现工艺状况好坏的重要指标,而Cpk 又是表现工艺能力的重要参数,我们基于Cpk 的表现来判断工艺流程的风险级别,高风险的将会一种针对半导体制造工艺的全面动态取样方案文/陈彧触发高取样率。

2.2 机台情况机台情况是影响整体工艺风险的重要因素。

当机台接近它们的维护周期时,机台性能会出现退化,这种情况会给工艺带来额外的风险,因此取样方案也要做相应的调整。

机台的风险会随着定期维护的周期发生着变化,当机台越接近维护的时间前后,机台的风险会随着增加。

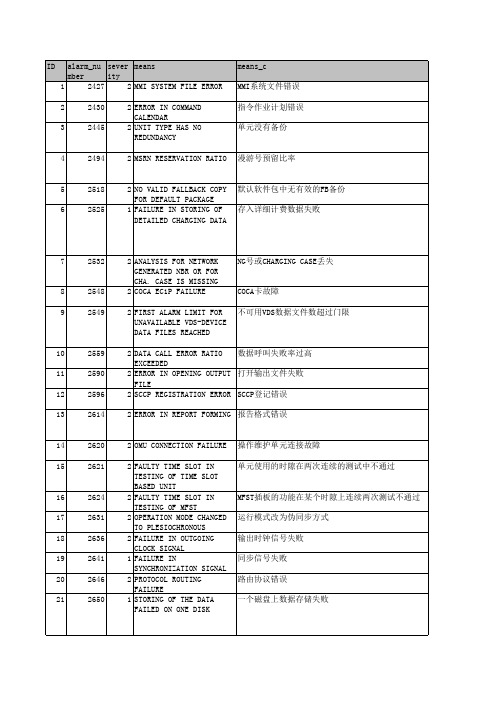

NOKIA告警宝典

看为WO-EX的CSSU单元)

数据可能丢失!保证VDS的连接指向,保存计费数据,先进行主备切换后再对备用单元进行重启动作.要频繁切换,且注意切换顺序.(SP-WO)

总线连接及状态.

时隙路由配置

间的电缆连接

故障期间的文件拷入该硬盘,以保证数据文件的正确传送.

复之前不要重启主用单元,以避免数据重写.

致性.

重新用ZII?命令将报告连至disk文件(逻辑文件为FRAUDREP),用MXR(MSC中)和MJR (HLR中)增加TCP/IP地址和端口

能是硬件存在故障,用ISI及ISC命令检查并将DISK状态改为WO-BU(注意解决硬件故障后需要update内存中的SOMAFI文件到DISK) 4.确认硬盘故障则按正障引起,应按正确的操作方法进行更换.

4.从另一正常的DISK上拷贝整个目录(IPS)

5.将硬盘状态改回WO-BU

6.允许文件更新(DUR,DBR)

确认硬盘故障则按正确的操作步骤进行更换.。

FTMCTRL 32位(P)ROM EDAC校验和编程应用说明书

FTMCTRL: 32-bit (P)ROM EDAC Checksum ProgrammingApplication note2018-04-17Doc. No GRLIB-AN-0011Issue 1.0M S -T P L T -1-1-0Date:2018-04-17Page: 2 of 9CHANGE RECORDIssue Date Section / Page Description1.02018-04-17All First issue.TABLE OF CONTENTS1INTRODUCTION (3)1.1Scope of the document (3)1.2Reference documents (3)2ABBREVIATIONS (3)3OVERVIEW (4)3.1Overview (4)3.2FTMCTRL PROM EDAC (5)3.3Sources of memory accesses (5)3.4Programming parallel checkbits (6)3.5Alternatives (6)4CONTROLLING THE PARALLEL CHECKBIT BUS (7)4.1UT699, UT699E and UT700 (7)4.2GR712RC (7)4.3GR740 (8)4.4LEON3FT-RTAX (8)4.5Other designs with FTMCTRL (8)5GRMON (8)Date:2018-04-17Page: 3 of 91INTRODUCTION1.1Scope of the documentThis document describes programming of parallel EDAC checksum (also referred to as checkbits in this document) in systems that make use of the FTMCTRL memory controller. The focus is on programming checksums for non-volatile memories, specifically parallel NOR Flash, that require special address and data sequences to issue commands to the memory devices.Parallel EDAC checksum is only used when EDAC protection is enabled with 32-bit data width. 1.2Reference documents[RD1]GRLIB IP Core User's Manual, Cobham Gaisler AB, http s:///grip.pdf [RD2]GRLIB-AN-0011-flash32 software package, available viahttps:///notes2ABBREVIATIONSBCH Bose–Chaudhuri–Hocquenghem, class of cyclic error-correcting codes EDAC Error Correction And DetectionFTMCTRL Fault-Tolerant Memory controllerMCFG Memory Configuration Register, control register for memory controllerTCB Test Check Bits, field in FTMCTRL MCFG2 register3OVERVIEW3.1OverviewThe FTMCTRL memory controller is commonly used in LEON3FT and LEON4FT processor devices and also in custom designs based on the GRLIB IP library [RD1].The memory controller is a combined 8/16/32-bit memory controller that provides a bridge between external memory and the on-chip bus and is configured through memory-mapped registers referred to as the Memory Configuration (MCFG) registers. The memory controller can handle four types of devices: PROM, asynchronous static ram (SRAM), synchronous dynamic ram (SDRAM) and memory mapped I/O devices (IO). The PROM, SRAM and SDRAM areas can be EDAC-protected using a (39,7) BCH code. The BCH code provides single-error correction and double-error detection for each 32-bit memory word.The PROM device type above typically means that parallel NOR Flash, MRAM or EEPROM is connected to the memory controller. A block diagram of how FTMCTRL can be connected toexternal devices and the on-chip system is shown in the figure below.Figure 1: FTMCTRL generic block diagramThe types of devices supported and the signals available on external pins of a device depends on the specific device implementation.Date:2018-04-17Page: 5 of 93.2FTMCTRL PROM EDACThe FTMCTRL is provided with an BCH EDAC that can correct one error and detect two errors in a 32-bit word. For each word, a 7-bit checksum is generated. A correctable error will be handled transparently by the memory controller. If an un-correctable error (double-error) is detected, the current AHB cycle will end with an AMBA ERROR response. The EDAC is enabled for the PROM area by setting the corresponding EDAC enable bit in the MCFG3 register. When working in 32-bit mode, the checksum is present on the CB bus (see figure 1) and will be stored in a memory device present in parallel with the device(s) providing the 32-bit data bus.For 8-bit mode, the EDAC checkbit bus (CB[7:0]) is not used but it is still possible to use EDAC protection. Data is always accessed as words (4 bytes at a time) and the corresponding checkbits are located at the address acquired by inverting the word address (bits 2 to 27) and using it as a byte address. Please refer to the relevant device user's manual or the FTMCTRL IP core documentation for further documentation on the 8-bit mode and EDAC.When using a parallel device to hold the checkbits, the only way to set the data bus of that device to an arbitrary value is to use the write bypass and read bypass functionality provided by FTMCTRL. If the MCFG3.WB (Memory Configuration register 3, WB field - write bypass) bit is set, then the value in the MCFG3.TCB field will replace the normal checkbits during memory write cycles. If the RB (read bypass) is set, the memory checkbits of the loaded data will be stored in the TCB field during memory read cycles. This bypass functionality has some limitations:•When read bypass is activated, then any memory read access will cause MCFG3.TCB to be updated.•The read bypass functionality requires that EDAC is enabled.•When write bypass is activated, then any memory write access will make use of the MCFG3.TCB field for the checksum valueThis means that accesses to the memory controller must be limited in order for the read bypass and write bypass functionality to be reliable. The next section describes sources of memory accesses. 3.3Sources of memory accessesThis document covers parallel checkbits for the PROM area. Since the same memory controller often provides provides access also to RAM memory used as the primary memory for a processor system, unwanted accessed may be caused by:•Processor instruction fetches due to misses in the instruction cache•Processor data fetches due to misses in the data cache•Peripherals that perform direct-memory access (DMA)Date:2018-04-17Page: 6 of 93.4Programming parallel checkbitsProgramming of parallel checkbits is straightforward for memory types that accept write operations performed in the same way as a read operation, with the difference that a write signal is asserted. Other devices, such as NOR Flash devices using the Common Flash Interface (CFI), require that both the address bus and the data bus are controlled when issuing commands to the memory devices and reading the responses to these commands. Controlling the data bus means that the write bypass functionality must be used in FTMCTRL and reading responses from a memory device means that the read bypass functionality needs to be enabled.The read bypass and write bypass functionality of FTMCTRL can be used safely from a debugger such as GRMON by stopping the processor(s) and all on-chip peripherals capable of DMA in the system. If the bypass functionality shall be used from software running on the processor then it is possible to design a program, taking into account the cache structure and replacement policy of the processor implementation, that runs completely from cache. It is not possible to guarantee that the sequence will run from cache in an environment where radiation effects can case single-event upsets in the processor's cache or if interrupts are enabled which can lead to a changed flow of execution and changes in the cache state (and also to unintended write accesses from interrupt handling).It should also be noted that a complicating, but not blocking, factor is that since read-bypass requires EDAC to be enabled, it is necessary to handle the corresponding AMBA ERROR, leading to a processor trap when reading CFI command responses via read-bypass.Because of the limitations described above it is considered infeasible to perform CFI Flash programming with parallel checkbits from a processor that is executing from memory mapped to the same FTMCTRL, when using an operating system or when operating in an environment where L1 cache parity errors may be encountered.3.5AlternativesConfigurations with memory devices with 32-bit data and parallel checkbits may be wanted due to attainable memory size and memory access latency. In case the non-volatile memory devices need to be reprogrammed during operation then use of NOR Flash devices needs to be considered in combination with the limitations described in section 3.4. It can also be noted that if the non-volatile memory needs to be updated at random addresses then Flash devices usually only support erase operations on a page granularity. Alternatives to NOR Flash include MRAM devices and EEPROM devices.A hybrid solution, usable unless the boot software needs to be updated, is to boot from FTMCTRL with EDAC enabled and make use of parallel checkbits. Once the system is up and running from RAM memory then the EDAC functionality for the PROM area can be disabled. EDAC for other parts of the PROM can then be implemented in software by creating a checksum for EDAC pages and storing it as part of the data that is memory-mapped. This way software will calculate andDate:2018-04-17Page:7 of 9validate checksums for the memory blocks that it reads and writes from non-volatile memory. The memory controller will not cause traps due to EDAC errors from the PROM after the EDAC is disabled.4CONTROLLING THE PARALLEL CHECKBIT BUSThe subsections below contain device specific observations and recommendations for CFI Flash programming.4.1UT699, UT699E and UT700To safely read and control the parallel checkbit bus on a UT699 device from the LEON3FT processor, all accesses to the shared FTMCTRL memory controller must be controlled. This means that:•All DMA units must be stopped•Interrupts must be disabled•Flash programming routines and their corresponding data must reside in L1 cache (cannot be guaranteed if L1 cache encounters parity-errors due to single-event upsets)For the UT699 processor, L1 cache coherency through bus snooping cannot be used and this functionality will be disabled by software. For the UT699E and UT700 the cache snooping functionality can optionally be enabled by software. If bus snooping is enabled then snooping will invalidate cache lines due to DMA traffic and this could have effects for software implementations that rely on data being present in cache for PROM programming.4.2GR712RCFor software running out of external memory, the same limitations apply as described for theUT699E and UT700 in section 4.1.Many of the limitations come from the need to execute software from the same memory controller as the one that provides access to the external non-volatile memory. The GR712RC also has an on-chip RAM. If this RAM is utilized to hold the programming application then it is sufficient if the following rules are met:•All DMA units using external memory must be stopped•The full program, including trap table, must reside in the on-chip RAM•An adapted trap handler for handling AMBA ERROR responses caused by reading memory device command responses with read-bypass must be installed.A software example for programming NOR Flashes with parallel checkbits is available [RD2].Date:2018-04-17Page:8 of 94.3GR740The FTMCTRL in GR740 supports 8- and 16-bit interfaces. EDAC check bits are programmed in the memory-mapped area and the special precautions described in this document do not need to be considered for the GR740.4.4LEON3FT-RTAXThe same restrictions as the ones listed in section 4.1 apply.4.5Other designs with FTMCTRLThe same restrictions as the ones listed in section 4.1 apply for devices that has one FTMCTRL that provides access to both RAM and non-volatile memory. For devices that have other RAM or ROM that software can use, the restrictions described in 4.2 apply.5GRMONGRMON versions 1.x.y and 2.x.y do not support programming parallel check bits. Support will be added for GRMON3 and this document will be updated with version information once the feature is available in GRMON3.Date:2018-04-17Page:9 of 9Copyright © 2018 Cobham Gaisler.Information furnished by Cobham Gaisler is believed to be accurate and reliable. However, no responsibility is assumed by Cobham Gaisler for its use, or for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Cobham Gaisler.All information is provided as is. There is no warranty that it is correct or suitable for any purpose, neither implicit nor explicit.。

基于边不相交最小路径法的互联网络可靠性评估与分析(IJCNIS-V10-N10-2)

Copyright © 2018 MECS

I.J. Computer Network and Information Security, 2018, 10, 11-17

12

Reliability Evaluation and Analysis of Interconnection Network using Edge-disjoint Minimal Path Method

I. INTRODUCTION With the recent advances in technology the design of robust interconnection network is always a challenging issue. Interconnection network (IN) plays an important role in the design of large scale and complex real time systems, as it provides the basic mean of data exchange among different components of such networks. Communication networks, multistage interconnection networks, stochastic flow networks, distributed network are some examples of real time systems. The operationability of such systems largely depend on the robustness of their interconnection networks. Thus, in general, it is quite apparent that interconnection network must be operational to ensure a robust system as a whole. Reliability is a parameter that measure successful operation of interconnection network. Out of many reliability measure network reliability is an important measure as it ensures at least one operational path among each node to every other node. The exact evaluation of network reliability of interconnection network is found to be NP-hard [1]. The existing methods to evaluate the network reliability of interconnection network are mainly based on sum of disjoint product method [3, 4, 11], enumeration of path sets/cut sets or spanning trees [5, 10, 11, 14, 15, 16], binary decision diagram(BDD) [7, 8, 12], factoring theorem [6], multiple variable inversion [9], etc. A detail discussion on these methods can be found in [15]. The worked carried out in [15] provides a clear insight into the use of cut-sets to evaluate the different reliability measures. Further, the difficulty in the use of path sets/spanning trees to evaluate the reliability is also discussed in this paper. In order to minimize the number of path sets, edge disjoint minimal path sets can be used as a substitute. Two minimal paths are said to be edge disjoint if they have no edge in common. Thus, k-disjoint minimal path problem can be defined as there must exist disjoint paths among k distinct pair of vertices such that every path connects a source node to a destinationuation and Analysis of Interconnection Network using Edge-disjoint Minimal Path Method

高斯朴素贝叶斯训练集精确度的英语

高斯朴素贝叶斯训练集精确度的英语Gaussian Naive Bayes (GNB) is a popular machine learning algorithm used for classification tasks. It is particularly well-suited for text classification, spam filtering, and recommendation systems. However, like any other machine learning algorithm, GNB's performance heavily relies on the quality of the training data. In this essay, we will delve into the factors that affect the training set accuracy of Gaussian Naive Bayes and explore potential solutions to improve its performance.One of the key factors that influence the training set accuracy of GNB is the quality and quantity of the training data. In order for the algorithm to make accurate predictions, it needs to be trained on a diverse and representative dataset. If the training set is too small or biased, the model may not generalize well to new, unseen data. This can result in low training set accuracy and poor performance in real-world applications. Therefore, it is crucial to ensure that the training data is comprehensive and well-balanced across different classes.Another factor that can impact the training set accuracy of GNB is the presence of irrelevant or noisy features in the dataset. When the input features contain irrelevant information or noise, it can hinder the algorithm's ability to identify meaningful patterns and make accurate predictions. To address this issue, feature selection and feature engineering techniques can be employed to filter out irrelevant features and enhance the discriminative power of the model. Byselecting the most informative features and transforming them appropriately, we can improve the training set accuracy of GNB.Furthermore, the assumption of feature independence in Gaussian Naive Bayes can also affect its training set accuracy. Although the 'naive' assumption of feature independence simplifies the model and makes it computationally efficient, it may not hold true in real-world datasets where features are often correlated. When features are not independent, it can lead to biased probability estimates and suboptimal performance. To mitigate this issue, techniques such as feature extraction and dimensionality reduction can be employed to decorrelate the input features and improve the training set accuracy of GNB.In addition to the aforementioned factors, the choice of hyperparameters and model tuning can also impact the training set accuracy of GNB. Hyperparameters such as the smoothing parameter (alpha) and the covariance type in the Gaussian distribution can significantly influence the model's performance. Therefore, it is important to carefully tune these hyperparameters through cross-validation andgrid search to optimize the training set accuracy of GNB. By selecting the appropriate hyperparameters, we can ensure that the model is well-calibrated and achieves high accuracy on the training set.Despite the challenges and limitations associated with GNB, there are several strategies that can be employed to improve its training set accuracy. By curating a high-quality training dataset, performing feature selection and engineering, addressing feature independence assumptions, and tuning model hyperparameters, we can enhance the performance of GNB and achieve higher training set accuracy. Furthermore, it is important to continuously evaluate and validate the model on unseen data to ensure that it generalizes well and performs robustly in real-world scenarios. By addressing these factors and adopting best practices in model training and evaluation, we can maximize the training set accuracy of Gaussian Naive Bayes and unleash its full potential in various applications.。

黑 ду克软件组合分析产品说明书

Black Duck provides complete control over open source risk, regardless of your organization’s size or budget OverviewBlack Duck® software composition analysis (SCA) can be implemented in two out-of-the-box configurations—Security Edition and Professional Edition. Black Duck Binary Analysis and the cryptography module can be added to either edition to provide greater insight into your application risk posture and enhanced control over your open source and third-party software consumption.Black Duck Security EditionAutomatically identify and remediate open source risks throughout your entire SDLCBlack Duck Security Edition can run either a full dependency scan during a build or a fast scan using the Code Sight™ IDE plugin to provide visibility into the open source security risks in your applications. Black Duck automatically discovers open source components in your applications, and also provides a complete open source Bill of Materials (BOM) for your software projects, giving you critical insight into any known vulnerabilities, as well as the license and code quality risks affecting your applications.• Vulnerability mapping identifies any security risks associated with the open source components in your applications at any point in your software development life cycle (SDLC).• Vulnerability monitoring and alerting automatically monitors for new vulnerabilities against inventoried open source components. It also helps accelerate remediation by instantly alerting security and development teams with detailed and actionable information.• Black Duck Security Advisories (BDSAs) provide notifications of vulnerable open source component versions, including detailed descriptions, exploit profiles, severity scoring, impact analysis, and detailed remediation guidance that security experts and developers alike can understand.• License risk identification safeguards sensitive intellectual property and helps avoid litigation by identifying the open source licenses that apply to the components in your applications. You can view license terms and obligations, automatically generate notice files, and define your own custom policy and let Black Duck handle the enforcement.• Operational risk metrics mitigates the risk of higher support and remediation costs for your development teams by identifying out-of-date component versions or those with limited project activity and community engagement.• Rapid Scan instantly analyzes open source dependencies for vulnerabilities and policy violations before code is built or merged into release branches.• Policy configuration lets you manage and mitigate risk throughout the SDLC. Structure policies for secure and compliant open source consumption and usage, and automate policy violation notifications for faster enforcement and remediation.• DevOps integrations automate open source discovery and provide critical risk insight to the teams who need it, when they needit. Integrations are available for CI/CD tools, package managers, IDEs, container platforms, code repositories, issue trackers, and application security suites.• Black Duck KnowledgeBase is the industry’s largest database of open source project, vulnerability, and license data. Map your BOMto more than 15 years of data, 30% more vulnerabilities than are tracked in the National Vulnerability Database (NVD), and over 2,750 unique licenses.Black Duck Professional EditionCompletely manage open source risk and consumption in your SDLCBlack Duck Professional Edition gives teams the tools they need to fully manage open source risks across their applications and containers. Professional Edition includes all the capabilities of Black Duck Security Edition, plus Black Duck’s advanced security and license compliance capabilities. Regardless of how large your organization or development team is, or what languages and technology you’re employing in your applications, Black Duck scales to meet your unique business needs and provides the most complete risk picture on the market.Multifactor open source discoveryNot all open source is explicitly declared or included in its original form, but it still carries risk. Black Duck identifies all open source components in your applications, modified or unmodified, partial or whole, via a combination of discovery techniques.• Dependency analysis tracks declared components and dependencies• Code print analysis finds undeclared, modified, and partial components, even in languages that don’t use package managers, like C/C++• Snippet matching identifies snippets of open source embedded in your code• Binary analysis detects open source in virtually any compiled software, firmware, or installer format without access to source code or build systems• Custom component detection uses string searching and code printing to find non-open-source, internal, or third-party commercial componentsAdvanced license complianceProtect intellectual property and mitigate the risk of open source license noncompliance with greater insight into license obligations and attribution requirements. Black Duck provides:• Identification and analysis of all applicable licenses beyond those declared• Automated generation of customizable open source software reports at the project/release level• Full texts for the most popular open source licenses• The ability to view license responsibilities and confirm that license commitments have been metSnippet analysis identifies small sections of code originating from open source components that carry the same license obligation as those components. Black Duck enables you to:• View code snippet matches highlighted in the component source, augmenting the accuracy of your open source BOM• Perform a full codebase scan or accelerate your analysis with a delta scan, examining only the files that have changed• Evaluate and triage matches by license risk, matched component version release data, and prevalence• Review key snippet data, including matched component name and version, component license, path, percentage of scanned code matched to component file, and release date• Confirm, flag, or ignore potential matches en masse with bulk edit capabilitiesAdditional Black Duck solutionsBlack Duck is available with additional security enhancements to further your open source risk management capabilities. Both Black Duck Binary Analysis (BDBA) and the cryptography module can be added to Black Duck Security Edition or Professional Edition.Black Duck Binary AnalysisModern software is a patchwork of open source software, commercial code, and internally developed components, and the tendencyto defer accountability throughout today’s complex software supply chain exposes you to significant risk. Vulnerable open source components in your applications are weak links in the supply chain, providing a viable point of entry for attackers. Take steps to identify the risks in the software libraries, executables, and vendor-supplied binaries in your codebase. Black Duck Binary Analysis helps you:• Analyze virtually any compiled software, firmware, mobile application, or installer format without access to source code• Create a detailed BOM of vulnerable open source components, including version, location, license, and known vulnerabilities• Use data from the NVD, including CVSS 2.0 and 3.x metrics, to rank vulnerabilities for remediation• Access detailed vulnerability descriptions, links to vendor advisories, patches, and more• Receive automatic alerts about new vulnerabilities in previously scanned software• Identify declared open source licenses and any potential risk of noncompliance• Use the REST API to accelerate and automate essential risk mitigation and remediation tasks• Identify potential sources of sensitive data leakage that might be in a software package• Gain insight into requested permissions for binary code types where relevant, such as in Android and iOS apps• Identify components that have been compiled without exploit mitigation mechanisms or that contain dangerous execution configurationsCryptography moduleThis module supports data security initiatives and regulations around the legal export of cryptography by tracking the cryptographic algorithms in the open source components in your applications and identifying weak cryptography or obsolete hashing mechanisms. The Black Duck cryptography module provides:• Identification of encryption algorithms found in each open source component version• Detailed cryptography data including key length, originator, licensing, and patent information• Indication of weak encryptionSecurity Edition Professional EditionScanning Dependency, rapid Multifactor scanningVulnerability info BDSA BDSALicense info Basic AdvancedPolicy●●Monitoring●●Reporting●●Integrations All AllAuto-remediation●●Reachability●●Containers●●On-prem options●●ScanningLanguages• C • C++ • C# • Clojure • Erlang • Golang • Groovy • Java• JavaScript • Kotlin • Node.js • Objective-C • Perl • Python • PHP • R • Ruby • Scala •Swift• .NET Cloud technologiesPackage managers• NuGet • Hex • Vndr • Godep • Dep • Maven • Gradle • Npm• CocoaPods • Cpanm • Conda • Pear• Composer • Pip• Packrat • RubyGems • SBT • Bazel • Cargo• C/C++ (Clang)• GoLang • Erlang/Hex • Rebar • Python • Yarn •YoctoBlack Duck | Source and Package Manager ScanningBDBA package manager support• Distro-package-manager: Leverages information from a Linux distribution package manager database to extract component information• The remaining four methods are only applicable to Java bytecode:–pom: Extracts the Java package, group name, and version from the pom.xml or pom.properties files in a JAR file –manifest: extracts the Java package name and version from the entries in the MANIFEST.MF file in a JAR file –jar-filename: Extracts the Javapackage name and version from the jar-filename–hashsum: Uses the sha1 checksum of the JAR file to look it up from known Maven Central registered Java projectsBinary formats• Native binaries • Java binaries • .NET binaries • Go binaries Compression formats• Gzip (.gz) • bzip2 (.bz2) • LZMA (.lz) • LZ4 (.lz4) • Compress (.Z) • XZ (.xz)• Pack200 (.jar) • UPX (.exe) • Snappy • DEFLATE•zStandard (.zst)Archive formats• ZIP (.zip, .jar, .apk, and other derivatives) • XAR (.xar) • 7-Zip (.7z) • ARJ (.arj) • TAR (.tar)• VM TAR (.tar) • cpio (.cpio) • RAR (.rar) • LZH (.lzh)• Electron archive (.asar) •DUMPInstallation formats• Red Hat RPM (.rpm) • Debian package (.deb) • Mac installers (.dmg, .pkg)• Unix shell file installers (.sh, .bin) • Windows installers (.exe, .msi, .cab)• vSphere Installation Bundle (.vib) • Bitrock Installer•Installer generator formats that are supported:–7z, zip, rar self-extracting .exe –MSI Installer –CAB Installer –InstallAnywhere –Install4J –InstallShield –InnoSetup –Wise Installer–Nullsoft Scriptable Install System (NSIS)–WiX InstallerFirmware formats• Intel HEX • SREC • U-Boot• Arris firmware • Juniper firmware • Kosmos firmware•Android sparse file system• Cisco firmwareFile systems / disk images• ISO 9660 / UDF (.iso) • Windows Imaging • ext2/3/4 • JFFS2 • UBIFS • RomFS• Microsoft Disk Image • Macintosh HFS• VMware VMDK (.vmdk, .ova) • QEMU Copy-On-Write (.qcow2) • VirtualBox VDI (.vdi) • QNX—EFS, IFS• NetBoot image (.nbi) •FreeBSD UFSContainer formats• DockerBlack Duck only BDBA onlyCloud technologiesCloud platforms• Amazon Web Services • Google Cloud Platform • Microsoft Azure• Pivotal Cloud FoundryContainer platforms• Docker • OpenShift• Pivotal Cloud Foundry•Kubernetes Package managersDatabases• PostgreSQLBlack Duck | IntegrationsDevOps toolsIDEs• Eclipse• Visual Studio IDE • IntelliJ IDEA • WebStorm • PyCharm • RubyMine • PhpStorm • VS Code• Android StudioContinuous integration• Jenkins • TeamCity • Bamboo• Team Foundation Server • Travis CI • CircleCI • GitLab CI• Visual Studio Team Services • Concourse CI • AWS CodeBuild • Codeship • Azure DevOps • GitHub Actions •OpenShiftWorkflow and notifications• Jira • Slack • Email • SPDX•Azure Boards• Microsoft TeamsBinary and source repositories• Artifactory • NexusApplication security suites• IBM AppScan• Micro Focus Fortify • SonarQube • ThreadFix • Cybric • Code Dx • Fortify •ZeroNorth。

RBS2000基站故障代码

CF I2A:30

Reinstall IDB with OMT and press DXU RBS数据库不好;RBS Database Corrupted reset. If this doesn’t help, change The RBS database (Note 2) in DXU is corrupted or cannot be read DXU. by the SW. 处理方法是重建立IDB,后RESET DXU,若无 IDB有干扰,或者启动用的软件未准备好。 效,换DXU。 CF I1A-15 RU数据库不好;RU Database Corrupted;The RU database (Note 2) in DXU is corrupted or cannot be read by the SW. CF I1A-16 硬件及IDB不好;HW and IDB inconsistent The IDB doesn’t match the HW present in cabinet (e.g. wrong frequency band, cabinet type, transmission type, etc.) CF I1A-17 内部结构不好;Internal Configuration failed One or several subsystems in DXU SW have failed their internal configuration (Note 2). The DXU stays in local mode and cannot be reached by BSC. CF I1A-18 Reset DXU. If this doesn’t help, change DXU.

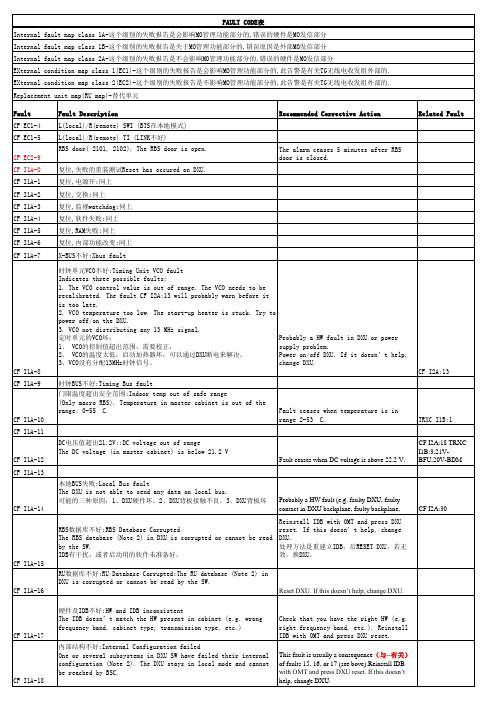

FAULT CODE表 Internal fault map class 1A-这个级别的失败报告是会影响MO管理功能部分的,错误的硬件是MO发信部分 Internal fault map class 1B-这个级别的失败报告是关于MO管理功能部分的,错误原因是外部MO发信部分 Internal fault map class 2A-这个级别的失败报告是不会影响MO管理功能部分的,错误的硬件是MO发信部分 EXternal condition map class 1(EC1)-这个级别的失败报告是会影响MO管理功能部分的,此告警是有关TG无线电收发组外部的. EXternal condition map class 2(EC2)-这个级别的失败报告是不影响MO管理功能部分的,此告警是有关TG无线电收发组外部的. Replacement unit map(RU map)-替代单元 Fault CF EC1-4 CF EC1-5 CF EC2-9 CF I1A-0 CF I1A-1 CF I1A-2 CF I1A-3 CF I1A-4 CF I1A-5 CF I1A-6 CF I1A-7 复位,失败的重装测试Reset has occured on DXU. 复位,电源开;同上 复位,交换;同上 复位,监视watchdog;同上 复位,软件失败;同上 复位,RAM失败;同上 复位,内部功能改变;同上 X-BUS不好;Xbus fault 时钟单元VCO不好;Timing Unit VCO fault Indicates three possible faults: 1. The VCO control value is out of range. The VCO needs to be recalibrated. The fault CF I2A:13 will probably warn before it is too late. 2. VCO temperature too low. The start-up heater is stuck. Try to power off/on the DXU. 3. VCO not distributing any 13 MHz signal. 定时单元的VCO坏: 1、 VCO的控制值超出范围,需要校正, 2、 VCO的温度太低,启动加热器坏,可以通过DXU断电来解决。 3、VCO没有分配13MHz时钟信号。 CF I1A-8 CF I1A-9 时钟BUS不好;Timing Bus fault 门限温度超出安全范围;Indoor temp out of safe range (Only macro RBS). Temperature in master cabinet is out of the range: 0-55C. CF I1A-10 CF I1A-11 DC电压值超出21.2V;;DC voltage out of range The DC voltage (in master cabinet) is below 21.2 V CF I1A-12 CF I1A-13 本地BUS失败;Local Bus fault The DXU is not able to send any data on local bus. 可能的三种原因:1、DXU硬件坏。2、DXU背板接触不良,3、DXU背板坏 CF I1A-14 Fault ceases when DC voltage is above 22.2 V. CF I2A:18 TRXC I1B:3.21VBFU,20V-BDM Fault ceases when temperature is in rangeTRXC I1B:1 2-53C. Fault Description L(local)/R(remote) SWI (BTS在本地模式) L(local)/R(remote) TI (LINK不好) RBS door( 2101, 2102). The RBS door is open. The alarm ceases 5 minutes after RBS door is closed. Recommended Corrective Action Related Fault

X-SEL错误指令大全