数字电路考试A

数字电子技术期末试卷标准答案及评分标准(A卷)

班级:__________ 学号: __________姓名: __________阅卷教师: _____________ 成绩: _______________一、判断题(将答案添入下表,每题1分,共10分。

正确选“√”,错误选“×”) 1 2 3 4 5 6 7 8 9101.在时间和幅度上都断续变化的信号是数字信号,因为说话时语音是断续的,所以是数字信号。

( )2.若两个函数具有不同的逻辑函数式,则两个逻辑函数必然不相等。

( ) 3.N 变量逻辑函数全部2N 个最大项之积恒等于1。

( ) 4.因为逻辑表达式A+B+AB=A+B 成立,所以AB=0成立。

( )。

5.TTL 集电极开路门输出为1时由外接电源和电阻提供输出电流。

( ) 6.异步时序电路是指的各级触发器类型不同的电路。

( )7.D 触发器的特征方程Q n+1=D ,而与Q n 无关,所以,D 触发器不是时序电路。

( ) 8.D/A 转换器的最大输出电压的绝对值可达到基准电压V REF 。

( )9.施密特触发器可用于将正弦波变换成三角波。

( )10.SRAM 是指静态RAM ,DRAM 是指动态RAM ;对相同容量的SRAM 和DRAM 而言,前者造价高,响应速度也快。

( )二、试将下列函数化为最简与或形式(10分,每题5分,要有解题步骤,否则不给分)(1)D C B A D C B A D B A AD Y +++=(2)化简逻辑函数D C B A BCD A D C B A D C B A F ⋅⋅++⋅⋅=),,,(;给定约束条件:0=+++⋅+⋅++⋅D C B A D ABC ABCD D C B A D C AB D C B A CD B A三、已知电路如图所示,写出F1、F2、F3、F 与输入变量A 、B 、C 、D 之间的逻辑表达式。

(本题10分)阅卷教师: _____________ 成绩: _______________四、设计一个能被2 或3 整除的逻辑电路,其中被除数A、B、C、D是8421BCD编码。

大工《数字电路与系统》课程考试模拟试卷A答案

机密★启用前大连理工大学网络教育学院2014年8月份《数字电路与系统》课程考试模拟试卷答案考试形式:闭卷试卷类型:A一、单项选择题(本大题共6小题,每小题3分,共18分)1.B 2.C 3.C 4.B 5.A 6.C二、填空题(本大题共10空,每空2分,共20分)1.(1) 213(2) 12.04(3) 40D(4) 10101001.11002.题号原码反码补码十进制数(1) 10111 01000(2) 1,011100 1,011101(3) 0,10101.01 +21.25三、化简题(本大题共3小题,每小题6分,共18分)=++1.答:F XYZ XY XY ZXY XY=+(3分)=(3分)Y2.答:填卡诺图,圈1,得到最简与或表达式。

CD AB00101101101111001110011100011110(3分)Y B AD A CD ∴=++ (3分)3.证明:0A ⊕00A A =+ (3分) A = (3分)四、简答题(本大题共3小题,第1、2小题各7分,第3小题10分,共24分)1.答:QQ OO ttSR O Ott(错1处扣1分,图都正确7分满分)2.答: ln()DD T T DD T T V V V T RC V V V -++--=- (3分)3812 2.7 6.3201010ln()s 12 6.3 2.7--=⨯⨯⨯⨯- (2分)0.267ms 267μs == (2分)3.答:(1)3ref f 322821016V 210V FSR R R ⨯⨯⨯===⨯ (2分) (2)当123011X X X =时,333166V 28o V FSR=-=-⨯=- (2分) 当123110X X X =时,3661612V 28o V FSR =-=-⨯=- (2分)(3),min 311162V 28o V FSR=-=-⨯= (2分)(4)3,max 32171614V 28o V FSR -=-=-⨯=- (2分)五、计算题(本大题1小题,共20分)1.答:(1)分析。

数字电子技术试卷A及答案

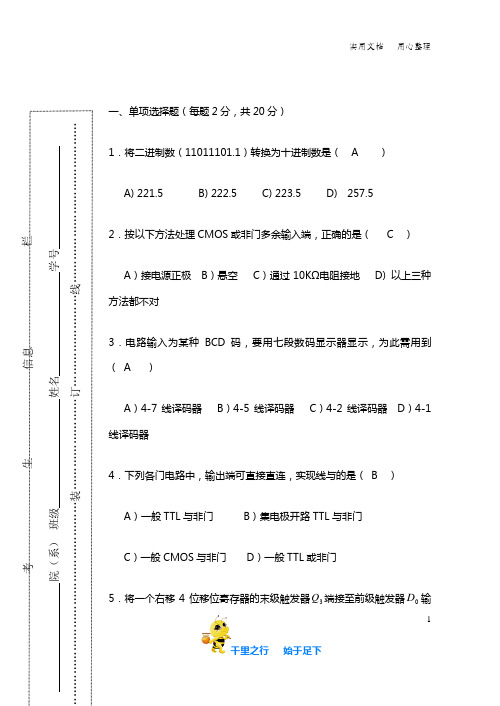

1一、单项选择题(每题2分,共20分)1.将二进制数(11011101.1)转换为十进制数是( A )A) 221.5 B) 222.5 C) 223.5 D) 257.52.按以下方法处理CMOS 或非门多余输入端,正确的是( C )A )接电源正极B )悬空C )通过10K Ω电阻接地 D) 以上三种方法都不对3.电路输入为某种BCD 码,要用七段数码显示器显示,为此需用到( A )A )4-7线译码器B )4-5线译码器C )4-2线译码器D )4-1线译码器4.下列各门电路中,输出端可直接直连,实现线与的是( B )A )一般TTL 与非门B )集电极开路TTL 与非门C )一般CMOS 与非门D )一般TTL 或非门5.将一个右移4位移位寄存器的末级触发器3Q 端接至前级触发器0D 输2入端。

设初态为3210Q Q Q Q =1101,以过5个CP 作用后的状态为( B )A )1101B )1110C )1011D )01116.用256×4位的RAM 扩展成2048×12位RAM ,每一条I/O 总线上并联了几条数据线?( C )A )24B )12C )8D )47.如下图中电路的名称是( D )A )单稳态电路B )JK 触发器C )施密特电路D )多谐振荡器8.已知函数D C B A Y ++=)(,则其反函数为( B )A )D CB DC A + B )D C B A ++ C )AC D AB + D )D B C A +9.可实现逻辑函数A Y =的是( D )A ) A A ⋅B ) A A +C )0⊕AD )1⊕A310.在倒T 形电阻网络D /A 转换器中,n n REFo D V V 2-=,设REF V =10V , D ="1000"0123=d d d d 时,则o V 为( B )伏。

A )3210-B ) 210-C ) 3210D ) 210 二、填空题:(24%)1.与十六进制(2D )16对应的二进制数是(101101)2 。

大工《数字电路与系统》课程考试模拟试卷A

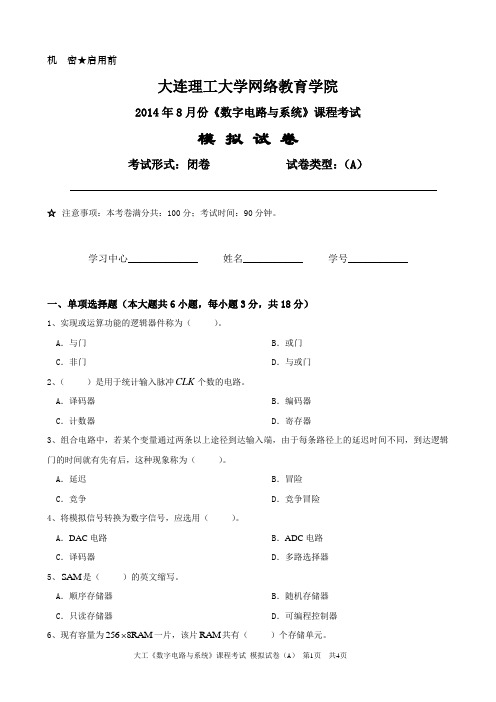

机密★启用前大连理工大学网络教育学院2014年8月份《数字电路与系统》课程考试模拟试卷考试形式:闭卷试卷类型:(A)☆注意事项:本考卷满分共:100分;考试时间:90分钟。

学习中心______________ 姓名____________ 学号____________一、单项选择题(本大题共6小题,每小题3分,共18分)1、实现或运算功能的逻辑器件称为()。

A.与门B.或门C.非门D.与或门2、()是用于统计输入脉冲CLK个数的电路。

A.译码器B.编码器C.计数器D.寄存器3、组合电路中,若某个变量通过两条以上途径到达输入端,由于每条路径上的延迟时间不同,到达逻辑门的时间就有先有后,这种现象称为()。

A.延迟B.冒险C.竞争D.竞争冒险4、将模拟信号转换为数字信号,应选用()。

A.DAC电路B.ADC电路C.译码器D.多路选择器5、SAM是()的英文缩写。

A.顺序存储器B.随机存储器C.只读存储器D.可编程控制器一片,该片RAM共有()个存储单元。

6、现有容量为2568RAMA.512 B.1024C .2048D .4056二、填空题(本大题共10空,每空2分,共20分)1、(1) (11010101)2=( )10(2) (10.0625)10=( )8(保留小数点后2位) (3) (2015)8=( )16 (4) (A9.C)16=( )2 2、题号 原码反码补码 十进制数 (1) 01001 23 (2) 1,100011-35 (3)0,10101.010,10101.01三、化简题(本大题共3小题,每小题6分,共18分)1、请用公式法化简下式:F XYZ XY XY Z =++2、用卡诺图化简法将函数Y AB ACD ABD ACD ABCD =++++化为最简与或表达式。

3、证明异或运算公式0A A ⊕=。

四、简答题(本大题共3小题,第1、2小题各7分,第3小题10分,共24分)1、请在下图()b 中补全基本RS 触发器输出端Q 、Q 的电压波形图,基本RS 触发器如图()a 所示。

数字电子技术考试卷及答案 (5)

七、(本题12分)画出用74161的异步清零功能构成的80进制计数器的连线图。

八、(本题15分)用D触发器设计一个按自然态序进行计数的同步加法计数器。

要求当控制信号M=0时为5进制,M=1时为7进制(要求有设计过程)。

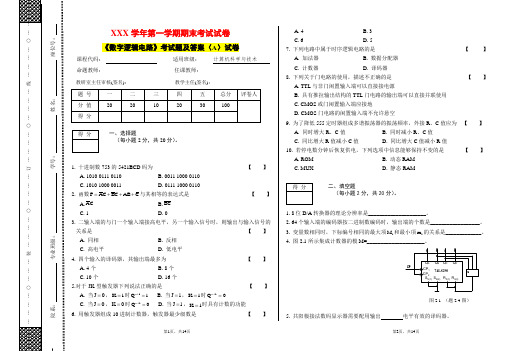

7《数字电子技术基础》期末考试A卷标准答案及评分标准8910北京航空航天大学2004-2005 学年第二学期期末《数字数字电子技术基础》考试A 卷班级______________学号_________姓名______________成绩_________2007年1月18日班号学号姓名成绩《数字电路》期末考试A卷注意事项:1、答案写在每个题目下面的空白处,如地方不够可写在上页背面对应位置;2、本卷共5页考卷纸,7道大题;((a)74LS85四、逻辑电路和各输入信号波形如图所示,画出各触发器Q 端的波形。

各触发器的初始状态为0。

(本题12分)五、由移位寄存器74LS194和3—8译码器组成的时序电路如图所示,分析该电路。

(1)画出74LS194的状态转换图;(2)说出Z 的输出序列。

(本题13分)CP CP六、已知某同步时序电路的状态转换图如图所示。

(1)作出该电路的状态转换表;(2)若用D触发器实现该电路时写出该电路的激励方程;(3)写出输出方程。

(本题15分)七、电路由74LS161和PROM组成。

(1)分析74LS161的计数长度;(2)写出W、X、Y、Z的函数表达式;(3)在CP作用下。

分析W、X、Y、Z端顺序输出的8421BCD码的状态(W为最高位,Z为最低位),说明电路的功能。

(本题16分)《数字电子技术基础》期末考试A卷标准答案及评分标准一、1、按照波形酌情给分。

北京航空航天大学2005-2006 学年第二学期期末《数字电子技术基础》考试A 卷班级______________学号_________姓名______________成绩_________2006年7月12日班号学号姓名成绩N图712Q Q Y(状态转换、设计过程和步骤对得10分,化简有误扣3-5分)七、MN=00时,是5进制,显示最大数字为4;MN=01时,是6进制。

数字电路与系统期末题及答案两套2009-2011年。30P

《考研专业课高分资料》大连理工大学《数字电路与系统》期末题北京总部考研专业课教研中心《考研专业课高分资料》之期末题細:餓+期末试题 (3)大连理工大学2010—2011学年寃1学期期末考试 ................ : . (3)(A) .................................... : (3)数字电路与系_试试题(A)参考答案 (12)人-连理工大学2009—2010学年第1学期期末考试 (17)(A) (17)者萨培避与襄^试试题(A)参考答案 (26)3/29 . . • •• - • -考研专业课研发中心:第四模块期末试题I ■I I I \I i 大连理工大学2010-2011学年第1学期期末考试I 1 I ti 龄猶絲鑛试试题(A )I 1 I:所有答案必须做在答案题纸上,做在试题纸上无效!以下各题,皆只有一个答案是正确的,请选择:(1分*10)1.下图是某一逻辑门的内部结构图,请固答:+5VV(1) .若输入信号X=1且¥=0,则输出信号Z 应为 :A : 1. B: 0C:.不确定 D :皆有可能’(2) .该逻辑门电路的逻辑符号为■:A: - B :CO-D :与)(3) .在正逻辑体制下,孩.逻辑门的等效逻辑符号为::上二ID-c ;-D :-I I■'2.请完成以下计窣制的转换:58in =A : 00101011B ; 01011010C : 00111011D : 0.0111010 3. 请完.成以下分数制的转换:10110010,= ■■ ,/- -'• ■ - -八:By B: A2 C: Al D: Bli- : m负載的CMOS反相器(即非门),若萬输入逻辑值为1,则其输出逻辑值为」A: 1 B:0 C:不确定 D:皆有可能扬出端有电流流入,请问:该电流是::;-■, ■:.B:灌电流i-;l ii:; iii 力 - ________ :...B:负值5 - ■:'■! b门屯路如下所示,则输出信号F= _________________________■;. 4电路和组合逻辑电路在功能上有何区别?1任意吋刻输出状态是否跟输入信号作用前的状态有关仃无输出信号::.勹令’(!分45)1-矿幵关代数(也称为布尔代数)中1 + 1=2.利周反演规则(也称为德•摩根定理),写出逻函数F=Y J- Z+X'' Y的反函数为(无需化简):F, =3:将逻辑函数G=X -Y+Y -Z+X *Z改写为最小项之和的形式:F=S X.Y.Z()和最大项之积的形式:F=JI». t. “ )4.在四变量的卡诺图中,W-X* ^Y*Z的四个相邻项为:5.写出以下电路的输出表达式:Fl= 、F2= 、F3=6.J -K 触发器的特性方程为: D 触发器的特性方程为:若使用D 触发器来设计一个模为十的计数器,请问至少需要几个D 触发器?7.利用卡诺图化简函数的结果是不是唯一的?三.某一逻辑函数 F=2,.I .r.z ( 2, 3,6, 7, 9,-12,13),回答问题(5 分*2): 1.画出该函数的卡诺图,并将菡数值填入该卡诺图:......2. 宣接在上面的卡诺图中,将可以合并的1单元圈起来,并写出该函数的最简与或式:四.集成电'路74X139包含两个二线至四线的译码器,其逻辑符号如下图所示,请回答以下问题(3分*5〉:1,.74X139中的两个二线至'四线译码德若要IE 常译码,其使能控制端EN_L 的有效逻辑值应为什么? ++ . - . 5/2?;' 、‘.• 考研专业澡研发中心F2X O T1 FiEN A BENLL -L -LL-L-L-L74X139刊奶幻妁罚们72736/291ENABCID0IDIID2D3D4D5D6D7考研专业课研发中心所奋输出端的有效电平为高电平还是低电平?JiivoZ间是何种逻辑关系?i:出苏中一个输出端Y3.L的逻辑表达式:也•• •A 74X139组成的电路如图所示,请写出输出端F的表达式:五,集成电路74X151是一个八选一的数椐选择器,其中C、B、A是3位选择变量,DO〜D7是八个数据输入端I £11.是低电平有效的使能控制端,请回答以下问题(共10分):74X151,0 ---------- ----- 9-1.在实噓屮,若使74X151正常工作,实现其数据选择的功能,使能端EN_L应如何连线?请直接在上图 f涵出(2分),2.请根据上图填写下面的数据选择表(8分):六.某一同步时序逻辑电路如下图所示(5分*3〉:1.请写出各触发器的激励方程(也称为存储器的输入方程):- Dl-= •- . • •.,曇“•. L F L•-.考研专业课研发中心《考研专业课高分资料3之期末题谞•^出该电路的次态方程(也称为状态方程):01 =调的输出方程:;)UT:-i::::组方程填写状态转换表:3.请究成该屯路的状态图,并标注状态转换时的输入输出值(X/OUT):《考研专业锞髙分资料》之期末题七.7虹163是集成的四位计数器电路,其组成的不足模计数电路如下图所示(10分h74X163->C3X <2 CLR ■o LD -ENP —ENTQAQB QC QD RCO1. •请画出该计 环图(7分乂2.该计数器电路是模几的计数器?(3分)Vcc=+5Vj — 数电路的状态循《考研专业课高分资料》之期末题A.在举重比赛中,有A、B、C三名裁判,其中A为主裁判,当两名或者两名以上裁判(且必须包括A在上举合格后,才可发出合格信号,请按照以下步骤实现丄述要求的逻辑电路(15分)。

计算机科学与技术专业《数字逻辑电路》考试题及答案(A)试卷

院系: 专业班级: 学号: 姓名: 座位号:A. 4B. 3C. 6D. 57. 下列电路中属于时序逻辑电路的是 【 】A. 加法器B. 数据分配器C. 计数器D. 译码器8. 下列关于门电路的使用,描述不正确的是 【 】A. TTL 与非门闲置输入端可以直接接电源B. 具有推拉输出结构的TTL 门电路的输出端可以直接并联使用C. CMOS 或门闲置输入端应接地D. CMOS 门电路的闲置输入端不允许悬空 9. 为了降低555定时器组成多谐振荡器的振荡频率,外接R 、C 值应为 【 】A. 同时增大R 、C 值B. 同时减小R 、C 值C. 同比增大R 值减小C 值D. 同比增大C 值减小R 值 10. 若停电数分钟后恢复供电,下列选项中信息能够保持不变的是 【 】A. ROMB. 动态RAMC. MUXD. 静态RAM1. 8位D/A 转换器的理论分辨率是_____________________。

2. 64个输入端的编码器按二进制数编码时,输出端的个数是__________________。

3. 变量数相同时,下标编号相同的最大项i M 和最小项i m 的关系是_____________。

4. 图2.1所示集成计数器的模M=_____________________。

图2.1 (题2.4图)5. 共阳极接法数码显示器需要配用输出 电平有效的译码器。

二、填空题(每小题2分,共20分)。

6. 对于T 触发器,当T=______时,触发器处于保持状态。

7. 逻辑函数C B AB F +=的反函数F 为_____________________。

8. 5个变量的逻辑函数全部最大项有_____________________个。

9. 二进制数()20110.101110转换成十进制数是___________________。

10. 同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为_____________________。

2016-2017学年1学期数字逻辑电路期末考试试卷_A卷_

3

vO

6

vI2 555

2

15

0.01µF

5.逻辑函数

P=A

⊕B

⊕C,写成最小项和的形式应为

P(A,B,C)=

∑ m

(

)。

评卷人

得分

三、综合题(8 小题,1-5 题每题 8 分,6 题 10 分, 7-8 题每题 15 分,共 80 分)

4.在 10 位二进制数 D/A 转换器中,已知其最大满刻度输出模拟电压 Vom=5V,求最小分辨

电压 VLSB 和分辨率。

5.图为由中规模 4 位二进制同步加法计数器 74LS161(同步置数,异步清零,QD 最高位)

构成的电路,试画出完整状态转换图,说明它是几进制计数器?

1.化简逻辑函数 P=AB+ A C+ B C+CD,用与非门实现该逻辑函数。 2.分析图逻辑电路,写出输出 Y0、Y1、Y2 和 Y3 的表达式和真值表,说明该电路的逻辑功能。

6. 试分析图所示电路的逻辑功能,列出特性表,写出特性方程。

队别__________

3.图题为一通过可变电阻 RW 实现占空比调节的多谐振荡器,图中 R W = RW1 + RW 2 ,试分

析电路的工作原理,求振荡频率 f 和占空比 q 的表达式。

试卷 第 2 页 (共 3 页)

…………………………密………………………………封………………………………线………………………………………

南京信息工程大学 2015-2016 学年第二学期《数字电子技术基础》期末考试试卷

南京信息工程大学

2016-2017 年 第 1 学期 数字逻辑电路 课程 期末 试卷(A 卷)

本试卷共 3 页;考试时间 120 分钟;出卷时间 2016 年 12 月

2023年扬州大学研究生自主命题 875数字电路、信号与系统A试题考试真题

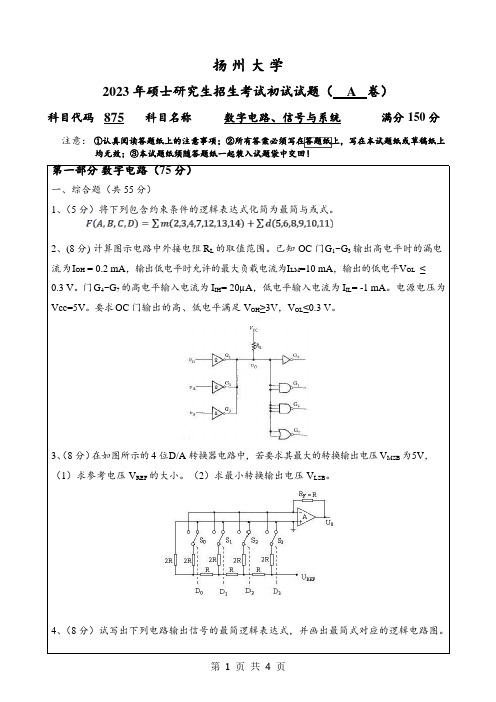

扬州大学2023 年硕士研究生招生考试初试试题( A 卷)科目代码875 科目名称数字电路、信号与系统满分 150 分注意:①认真阅读答题纸上的注意事项;②所有答案必须写在答题纸上,写在本试题纸或草稿纸上均无效;③本试题纸须随答题纸一起装入试题袋中交回!第一部分数字电路(75 分)一、综合题(共 55 分)1、(5 分)将下列包含约束条件的逻辑表达式化简为最简与或式。

2、(8 分) 计算图示电路中外接电阻 R L 的取值范围。

已知 OC 门 G1~G3 输出高电平时的漏电流为I OH= 0.2 mA,输出低电平时允许的最大负载电流为ⅠLM=10 mA,输出的低电平V OL≤0.3 V。

门 G4~G7 的高电平输入电流为 I IH= 20µA,低电平输入电流为 I IL= -1 mA。

电源电压为Vcc=5V。

要求 OC 门输出的高、低电平满足 V OH≥3V,V OL≤0.3 V。

3、(8 分)在如图所示的 4 位D/A 转换器电路中,若要求其最大的转换输出电压 V MSB 为5V,(1)求参考电压 V REF 的大小。

(2)求最小转换输出电压 V LSB。

4、(8 分)试写出下列电路输出信号的最简逻辑表达式,并画出最简式对应的逻辑电路图。

5、(8 分)如图所示电路,已知输入 A、B 的波形,试写出输出 Y 的表达式,并画出波形。

6、(8 分)已知由 555 集成定时器构成的电路如下图所示,(1)试说明该电路的名称。

(2)计算画出在 UI(V)作用下输出电压波形。

7、(10 分)边沿 JK 触发器组成的电路如图所示。

已知触发信号 CLK 和输入信号 A 的波形,(1)试写出电路的驱动方程。

(2)写出电路的状态方程。

(3)画出输出 Q1、Q2 以及 J2(K2)的波形。

(所有触发器的初态为 0)二、设计题(共两小题,每题 10 分,共 20 分)1、(10 分)74LS160 为十进制加法计数器,试用同步级联方式和整体反馈归零法设计一个24 进制计数器,请写出设计过程并画出连线图。

306数字电路结业A答案

四川邮电职业技术学院 2006-2007学年第二学期期末考试306级通信类专业各班《数字电子技术》试卷(A 套)(闭卷)(参考答案及评分标准)1.A 2.A 3.A 4.C 5.C三、(10分)1.反函数Y=AB (A + B),Y=A+B+AB (2分)对偶函数Y =A+B AB '+(2分)2.Y=AB+AB (3分)3.逻辑电路图为:(3分)A B B A四、(10分)1.解:Y的卡诺图为B所以Y (A 、B 、C 、D )=B (6分)评分标准:填卡诺图2分;画圈2分;写表达式2分2.解:Y(A 、B 、C 、D )=C+AB (4分)评分标准:画圈2分;写表达式2分 五、(5分)状态转换图为:(3分)所以该计数器为六进制计数器。

(2分) 六、(6分)解:由图有Q n+1=D=n Q (2分)所以Q的波形为(设初态为0):(4分)CP Q评分说明:可以不写表达式,直接画波形,只要波形正确,给满分。

七、设计题(28分)1.(6分)解:电路图为:(3分)状态转换图为: (3分)2.(22分)(1)解: ① 分析题意列真值表。

(2分)A B C图12-19 例12-2电路图C A② 由真值表写出逻辑函数式。

(2分) Y = A BC + A B C + AB C + ABC ③ 化简(3分)Y = A BC + A B C + AB C + ABC= BC(A + A)+ AC(B +B) + AB C = BC + AC + AB C = AC + B(C + A ) = AC + BC + AB =AC+BC+AB=ACBCAB④ 画逻辑电路图。

(3分)(2)用74LS138和门电路实现(6分) 解:由(1)中真值表可知: Y = A BC + A B C + AB + ABC=m 3+m 5+m 6+m 7 =3567m m m m所以只要令74LS138的输入A 2、A 1、A 0分别代表输入变量A 、B 、C ,那么Y =3567m m m m=3567Y Y Y Y (3分)所以逻辑电路图为:(3分)(3) 用74LS151实现(6分)解:令输入变量A 、B 、C 分别对应74LS151的数据选择端A 2、A 1、A 0,则74LS151的输出Y =0011223344556677D D D D D D D D m m m m m m m m +++++++由(1)中真值表可知: Y = A BC + A B C + AB C + ABC=m 3+m 5+m 6+m 7所以只要令74LS151的数据输入端分别为D 2=D 1=D 0=D 4=0,D 3=D 5=D 6=D 7=1,那么就可以用74LS151实现。

数字电路与逻辑设计试题及答案试卷A

数字集成电路基础试题 A考试时间:120分钟班级: 姓名: 学号: 成绩:一、填空题共20分1. 数字信号的特点是在 上和 上都是断续变化的,其高电平和低电平常用 和 来表示;2. 常用的BCD 码有 、 、 等,常用的可靠性代码有 、 等;3. 将十进制数45转换成8421码可得 ;4. 同步RS 触发器的特性方程为Q n+1=__________;约束方程为 ;5. 数字电路按照是否有记忆功能通常可分为两类: 、 ;6. 当数据选择器的数据输入端的个数为8时,则其地址码选择端应有 位; 7.能将模拟信号转换成数字信号的电路,称为 ;而将能把数字信号转换成模拟信号的电路称为 ;8.时序逻辑电路按照其触发器是否有统一的时钟控制分为 时序电路和 时序电路;9. 两片中规模集成电路10进制计数器串联后,最大计数容量为 位; 二、单项选择题共 20分1. 对于四位二进制译码器,其相应的输出端共有 ;A . 4个 B. 16个 C. 8个 D. 10个2. 要实现n 1n Q Q =+,JK 触发器的J 、K 取值应为 ;A . J=0,K=0 B. J=0,K=1 C. J=1,K=0 D. J=1,K=1 3. 图2.1所示是 触发器的状态图;A. SRB. DC. TD. T ˊ4.在下列逻辑电路中,不是组合逻辑电路的有 ; A.译码器 B.编码器 C.全加器 D.寄存器 5.欲使D 触发器按Q n+1=Q n 工作,应使输入D= ;A. 0B. 1C. QD. Q 6.多谐振荡器可产生 ;A.正弦波B.矩形脉冲C.三角波D.锯齿波 7. N 个触发器可以构成最大计数长度进制数为 的计数器; A.N B.2N C.N 2 D.2N 8.随机存取存储器具有 功能;A.读/写B.无读/写C.只读D.只写9.只读存储器ROM 中的内容,当电源断掉后又接通,存储器中的内容 ; A.全部改变 B.全部为0 C.不可预料 D.保持不变 10. 555定时器构成施密特触发器时,其回差电压为 ; A .VCC B. 1/2VCC C. 2/3VCC D. 1/3VCC 三、设计题 共20分图2.11、有一水箱由大、小两台水泵M L 和M S 供水,如图3.1所示,箱中设置了3个水位检测元件A 、B 、C;水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平;现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作;试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单;四、简答题共10分图3.1v v v I1OOv ,12658437Ov ,v I2v I1v v IC V CC v O555(b)D R555定时器的电气原理图如图4.1所示,当5脚悬空时,比较器C 1和C 2的比较电压分别为cc V 32和cc V 31;问:1当v I1>cc V 32,v I2>cc V 31时,比较器 C 1输出低电平,C 2输出高电平,基本RS 触发器 置0\置1\状态不变,放电三极管T 导通,输出端v O 为低电平;2当v I1<cc V 32,v I2<cc V 31时,比较器 C 1输出高电平,C 2输出低电平,基本RS 触发器 置0\置1\状态不变,放电三极管T 截止,输出端v O 为高电平;3当v I1<cc V 32,v I2>cc V 31时,比较器 C 1输出 ,C 2输出 ,即基本触发器 置0\置1\状态不变,电路亦保持原状态不变; 五、分析作图题共30分1、设主从JK 触发器的初始状态为0,触发器的触发翻转发生在时钟脉冲的下降沿,已知输入J 、K 的波形图如图5.1,1写出JK 触发器的特性方程式;2画出输出Q 的波形图;10%2、74161集成计数器功能真值表如表5.1所示,其惯用符号如图5.2所示,1利用反CP J KQ 123456图5.1馈复位法将其构成十进制计数器;2利用反馈预置法将其构成8进制计数器;20%表5.1图5.2数字集成电路基础试题A 评分标准一、填空题每空1分,共20分1、时间;数值;0;12、8421BCD ;5421BCD ;余3码;格雷码;奇偶校验码3、010001014、n Q R S +;0=•S R5、组合逻辑电路;时序逻辑电路6、3位7、A/D ;D/A 8、同步;异步 9、100二、单项选择题每题2分,共 20分三、设计题 共20分解:一、列出满足逻辑要求的真值表并化简化简方法可多种自选化简得 C B A M S += B M L =二、作出逻辑电路图1置0;2置1;3高电平;高电平;状态不变sL五、分析作图题共30分1、共10分1n n n Q K Q J Q +=+12CP J K Q1234562、共20分解:1错误!写出S 10的二进制代码为 S N =S 10=1010错误!写出反馈归零函数,由于74161的异步置0信号为低电平0,因此 B D r Q Q C •=2错误!N-1 S N =S 8-1=0111错误!写出反馈归零函数,方法一:从0开始计数 B C D D Q Q Q L ••=方法二:从1000开始计数,取状态S 15=1111时,Q C =1,经非门得0==C D Q L 错误!画连线图 方法一方法二:。

数字集成电路期末考试卷A-2012

a b c

F = ac + bc

100·Cin

Cin

图2

图3

4. 根据逻辑表达式 F = ac + bc 设计 CMOS 逻辑门电路的版图并通过逻辑努力优化每级的输 入电容量。 (1)画出用最少的晶体管实现该功能的 CMOS 逻辑门的电路图。 分) (4 (2)利用欧拉路径方法找出具有规则版图的晶体管排列顺序,即使版图具有连续的 pdiff 和 ndiff 扩散区和多晶栅线。 分) (4 (3) 用棍棒图画出该版图的结构,请注明您的表示方法, 如金属 1 MET1) 扩散区 ( , (ndiff 和 pdiff) , n 阱(nWell) ,多晶(Poly),它们之间的连接请用 X 表示。 分) (4 (4)假设 nMOS 管与 pMOS 管的工艺互导的比为 3。在电路原理图中标明该门电路的各晶体管 宽度尺寸,使它的输出驱动能力与单位对称反相器相同,即它的上升和下降时间相等且与单位对 称反相器延迟一致。 分) (4 (5)计算该逻辑门 c 输入端的逻辑努力。 分) (4 (6)如图 3 所示如果一个逻辑链含有该逻辑门(黑实线部分) ,试求每级输入电容的最优值使该 逻辑链的延迟最小,设输入电容 Cin 等于单位对称反相器的输入电容,输出负载电容为 100·Cin。

华

日

侨

大

学

数字集成电路设计

试

卷 A(期末,开卷)

年 月

班 级:

考试日期 2 0 1 1

姓 名:________________________学 所有案按顺序填写在答卷纸上

号__________________________

一、填空题(30%)(计算精确到小数点后 2 位,或者 3 位有效数字;每空 2 分,有单位的请写明 单位,否则扣 1 分) 1.三态门的三个状态分别是:( 1 ), ( 2 )( , 3 ) 。 2.互连线由电阻率为ρ=4µΩ·m, 线的厚度为 0.5µm,宽为 0.8µm,长 100µm 的导线电阻 R= ( 4 ) 。 3.互补 MOS(CMOS)采用两种类型的 MOSFET 构建逻辑电路,一种是( 6 ) MOSFET;另外一种是( 6 )MOSFET。 4.如果一个反相器的输出端连接 4 个同样的反相器,那么它的电气努力是( 7 ) 假设 。 忽略寄生电容的对延迟的影响, 即无负载电容时延迟为 0; 如果它的电气努力是 1 时的延迟是 1ns, 那么以上电路的延迟时间是( 8 ) 。 5.以下 SPICE 语言所描述的 nMOS 晶体管的单位面积栅氧电容 Cox=( 9 ) 其中 , −13 10 ); 等 效 开 关 电 阻 Rn= ε ox = 3.453 × 10 F/cm;源极的零偏置电压的结电容 CSB=( ( 11 ) ; ******************* Spice 网表 ************************ Vdd ndrain 0 5V Vgs ngate 0 5V Mnmos ndrain ngate 0 0 nFET L=0.5U W=4U AD=12P PD=12U AS=12P PS=12U .Model nFET NMOS (KP=150U VTO=1 TOX=1.25e-8 CJ=8.5e-4 CJSW=2.5E-10) ******************* Spice 网表 ************************ 6. 求以下数字的波茨编码(Booth Coding) ,若二进制补码 A=10101011,则它的波茨编码为 B=( 12 )X 26 +( 13 )X 24 +( 14 )X 22 +( 15 ) 。 二、问答题(15%) (1)集成电路中双极器件和单极器件的定义分别是什么? (2)方块电阻的定义是什么?它的单位是什么? (3)有比电路和无比电路的定义分别是什么? 三、综合题(55%) 1. 图1为阻性负载的反相器电路。电源电压VDD为5V,MOS管的工艺互导为20uA/V2,阈值电 压为0.8V,负载电阻RL为200K,W/L=2。计算该反相器的传输特性数值(VIL,VOL,VIH, VOH)及电路的噪声容限,并在此基础上评价该反相器的设计是否最优。 (11分)

《数字集成电路》期末试卷A(含答案)

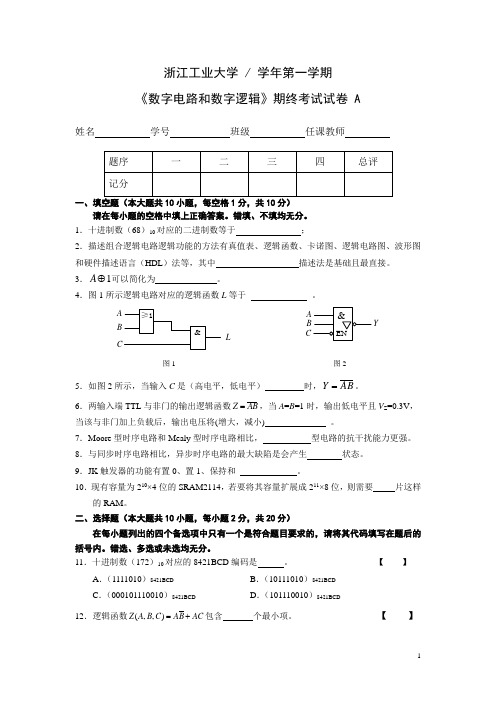

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷 A姓名 学号 班级 任课教师一、填空题(本大题共10小题,每空格1分,共10分)请在每小题的空格中填上正确答案。

错填、不填均无分。

1.十进制数(68)10对应的二进制数等于 ;2.描述组合逻辑电路逻辑功能的方法有真值表、逻辑函数、卡诺图、逻辑电路图、波形图和硬件描述语言(HDL )法等,其中 描述法是基础且最直接。

3.1A⊕可以简化为 。

4.图1所示逻辑电路对应的逻辑函数L 等于 。

A B L≥1&CYC图1 图25.如图2所示,当输入C 是(高电平,低电平) 时,AB Y =。

6.两输入端TTL 与非门的输出逻辑函数AB Z =,当A =B =1时,输出低电平且V Z =0.3V ,当该与非门加上负载后,输出电压将(增大,减小) 。

7.Moore 型时序电路和Mealy 型时序电路相比, 型电路的抗干扰能力更强。

8.与同步时序电路相比,异步时序电路的最大缺陷是会产生 状态。

9.JK 触发器的功能有置0、置1、保持和 。

10.现有容量为210×4位的SRAM2114,若要将其容量扩展成211×8位,则需要 片这样的RAM 。

二、选择题(本大题共10小题,每小题2分,共20分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

11.十进制数(172)10对应的8421BCD 编码是 。

【 】A .(1111010)8421BCDB .(10111010)8421BCDC .(000101110010)8421BCD D .(101110010)8421BCD12.逻辑函数AC B A C B A Z +=),,(包含 个最小项。

【 】A .2B .3C .4D .513.设标准TTL 与非门AB Z =的电源电压是+5V ,不带负载时输出高电平电压值等于+3.6V ,输出低电平电压值等于0.3V 。

数字逻辑电路期末试卷及答案 (3)

第1页,共8页第2页,共8页院系: 专业班级: 学号: 姓名: 座位号:20 -20 学年第 学期期末考试试卷《数字逻辑电路》(A )卷一、选择题(每小题2分,共20分)1、下列数中最大的数是 【D 】 A 、(3C )16 B 、(57)8C 、(70)10D 、(1110010)22、8个输入端的编码器按二进制数编码时,输出端的个数是 【B 】 A 、2个 B 、3个C 、4个D 、8个3、逻辑电路中的晶体管一般工作在【B 】A 、放大区B 、饱和区或截至区C 、截至区D 、饱和区4、同步时序电路和异步时序电路比较,其差异在于后者 【B 】 A 、没有触发器; B 、没有统一的时钟脉冲控制; C 、没有稳定状态; D 、输出只与内部状态有关;5、n 个变量的逻辑函数全部最大项的个数有 【C 】 A 、n B 、2n C 、2nD 、2n -16、555定时器的结构如图1.1所示,如果芯片的5脚悬空;RD =V CC =5V ,6脚输入4V 电压,2脚输入2V 电压,下列关于555电路说法正确的是 【 A 】U CC U CO U 6(TH)(TR)U oR D U 2放电端图1.1(题1.6图)A 、U O 输出低电平,放电开关V 1导通;B 、U O 输出高电平,放电开关V 1截止;C 、U O 输出低电平,放电开关V 1截止;D 、U O 输出高电平,放电开关V 1导通; 7、图1.2所示用74LS161(同步16进制计数器,Cr 异步清零端、LD 同步置数端、OC 进位输出端,P 、T 计数允许端)构成的计数器正确的说法是 【D 】A 、同步置数法组成的9进制计数器;B 、异步置数法组成的8进制计数器;C 、同步置数法组成的10进制计数器;D 、异步复位法组成的9进制计数器; 图1.2( 题1.7图) 8、要使由与非门组成的基本RS 触发器保持原状态不变,D S 、D R 端输入的信号应取 【A 】 A 、1==D D S RB 、10==D D S R 、C 、01==D DS R 、 D 、0==D D S R9、为获得输出频率非常稳定的脉冲信号,应采用 【C 】A 、对称多谐振荡器B 、555定时器组成的对称多谐振荡器第3页,共8页第4页,共8页装订线内不许答题 C 、石英晶体振荡器 D 、单稳态触发器 10、下列关于TTL 与非门闲置输入端的处理不正确的是 【D 】 A 、直接接电源电压VccB 、与有用输入端并联使用C 、外界干扰小时,可以剪断或悬空D 、直接接地1、二进制数-110011的补码是 1001101 。

2007-2008学年第2学期《数字电路》期末考试试卷(闭卷A)

2007-2008学年第2学期《数字电路》期末考试试卷(闭卷A)我以⼀名⼤学⽣的⼈格尊严保证,在本场考试中,⾃觉遵守考试纪律,服从考试管理,决不作弊或帮助别⼈作弊!签名:学院专业学号级班··················密···················封·····················线··················命题⼈签字:系主任签字:审核院长签字:共印份数:第1页共4页聊城⼤学计算机学院07—08学年第2学期期末考试2007级《数字电路》试题(闭卷 A卷)⼀、填空题(每空1分,共20分)8421BCD代码为。

2.Y=A(B+C)+CD的对偶式Y D=。

3.常⽤的逻辑函数表⽰⽅法主要有、、、波形图、卡诺图和硬件描述语⾔等。

4.逻辑函数Y=AB+BC+AC化为与⾮—与⾮形式为。

5.如果以⾼电平表⽰逻辑1,以低电平表⽰逻辑0,则这种表⽰⽅法为。

6.⼏个OD(漏极开路输出)门的输出直接相连,可以实现逻辑。

7.CMOS电路最突出的⼀⼤优点是。

数字电子技术试卷A答案

第1页共8页

姓名:

学号:

得分

二、选择题(共 10 小题,每小题 2 分,共 20 分)

Q2n Q3n

⎪⎩Q3n+1 = Q2nQ1nQ3n + Q1nQ3n

3) 输出方程 Y: (2 分)

Q1n Q2n Q3n

/0

/0

000 001 011

/1

/0

100 110 111

/0

/1

/1

010

/1

101

Y = Q1n

4) 列状态转换表如下:(令 Q1n Q2n Q3n =000)

Q1n Q2n Q3n

解: W = ∑m (5, 11, 12, 14) X = ∑m (2, 4, 7, 8, 10, 13) Y = ∑m (0, 6, 7, 9, 13, 15) Z = ∑m (0, 1, 3, 4, 5, 8, 9, 10, 12, 13, 14, 15)

在 CP 作用下,由 WXYZ 组成的 8421BCD 码依次输出 3.141592653589793….. 即:是一个π常数存储器。

1、下列说法正确的是 C

。

(A)若 X+Y=X+Z,则 Y=Z

(C)若 X+Y=X+Z,且 XY=XZ,则 Y=Z

(B)若 XY=XZ,则 Y=Z (D)以上说法都不对

2、下列各门电路中 D

的输出端不可以并联使用;

(A)CMOS OD 门

[VIP专享]数字电路A卷答案

![[VIP专享]数字电路A卷答案](https://img.taocdn.com/s3/m/064b8690763231126fdb1118.png)

F1 F2

解: F1=AB+A’B’C’+BC’D’ F2=AB+BC’D’ #每个表达式 3 分

三、写出下图所示电路的输出逻辑函数。(6 分)

(第 3 页 共 5 页)

110000 电路为 4 进制计数器。

电压 VO 为( 1.54 )V。 4、一个有 4096 个存储单元的 RAM,每个字是 8 位,此存储器应有( 512

)根地址线。

得

分

二、将下列逻辑函数化为最简“与或”函数式(每小题 5 分,共 10 分)

(1) Y A'(CD'+C'D)+BC'D+AC'D+A'CD 解:原式=A’C+C’D

=((M7)’ (M4)’ (M2)’ (M0)’)’

Z3=(ABC+AB’C’+A’BC’+A’B’C’)’’

=((M7)’ (M3)’ (M1)’ )’

Z2=(ABC+A’BC+A’B’C)’’

& Z4

& Z1

& Z2

A2 Y0 A1 Y1 A0 Y2

Y3

74138

Y4

S1 Y5 S’2 Y6 S’0 Y7

0

=((M6)’ (M5)’ (M4)’ (M3)’)’

0

=((ABC’)’(AB’C)’(AB’C’)’(A’BC)’)’ 1

解:Z1=(ABC’+AB’C+AB’C’+A’BC)’’

C

B

Z3

&

Z4=A’B+AB’C

A

88.8918÷1.2990÷.1=4214÷3922=.0034=1÷15251371=8535.78.208÷023.2173c00÷1*m=29030.3922c=.1÷20m3=2÷120252.=3535=42314c)*523m240341*31.252=31*.1.535.*031342.*9205221.04.455=+213*05*2022.02.854850.3150.*+58c12*5m1*202+.050+0.014*85.20*051000+0+03/8T.+0÷+=55+1*011+010+91÷01454050*0010200+5+0+080+400*+4**1*1510.3910%*C%-*6+÷M(=*M=5÷50)*30*31(÷3110*5+**÷4*1m243.%71e=78%n0)8=8s.5=77.93c.6c0mmc.4*m1*31,0w199o.k2.m4c-cem.5mn2csp26m659*.0.34-50.60c5*pm.3c85m9,c05g.m.05i0rp-l.s.85p6/c50bcm0.om7py.c.6spm5c+mc;0m..7.cmk ; 1+1k+12+1+k2234=1c+m1++4+4+2

数字电路与逻辑设计试卷(有答案)

数字电路与逻辑设计(A 卷)班级 学号 姓名 成绩一.单项选择题(每题1分,共10分)1.表示任意两位无符号十进制数需要( )二进制数。

)二进制数。

)二进制数。

A .6B 6 B..7C 7 C..8D 8 D..92.余3码10001000对应的2421码为(码为( ))。

A .01010101 B.10000101 C.10111011 D.11101011 3.补码1.1000的真值是(的真值是( ))。

A . +1.0111 B. -1.0111 C. -0.1001 D. -0. 1000 4.标准或.标准或--与式是由(与式是由( )构成的逻辑表达式。

)构成的逻辑表达式。

)构成的逻辑表达式。

A .与项相或.与项相或 B. B. B. 最小项相或最小项相或最小项相或 C. C. C. 最大项相与最大项相与最大项相与 D. D. D.或项相与或项相与或项相与 5.5.根据反演规则,根据反演规则,()()E DE C C A F ++×+=的反函数为(的反函数为( ))。

A. E )]E D (C C [A F ×++= B. E )E D (C C A F ×++= C. E )E D C C A (F ×++= D. E )(D A F ×++=E C C6.下列四种类型的逻辑门中,可以用( )实现三种基本运算。

)实现三种基本运算。

)实现三种基本运算。

A. A. 与门与门与门B. B. B. 或门或门或门C. C. 非门非门非门D. D. D. 与非门与非门与非门7. 将D 触发器改造成T 触发器,图1所示电路中的虚线框内应是(所示电路中的虚线框内应是( ))。

图1A. A. 或非门或非门或非门B. B. B. 与非门与非门与非门C. C. C. 异或门异或门异或门D. D. D. 同或门同或门同或门8.实现两个四位二进制数相乘的组合电路,应有( )个输出函数。

数字电路期中考试试卷

数字电路期中考试试卷 A 卷一、填空(每题2分,共16分)1. 如图1所示,A=0时,Y= ;A=1,B=0时,Y= ;2. C A AB Y +=,Y 的最简与或式为 ;3. TTL 门电路输出高电平为 V ,阈值电压为 V ;4. 如图2所示为TTL 的TSL 门电路,EN=0时,Y 为 ,EN=1时,Y= ;5. 触发器按逻辑功能可分为RSF 、JKF 、 、 和DF ;6. 四位二进制减法计数器的初始状态为0011,四个CP 脉冲后它的状态为 ;7. 数字系统按组成方式可分为 、 两种; 8. 组合逻辑电路产生竞争冒险的内因是 ;二、选择题(每题2分,共24分) 1.逻辑函数F=)(B A A ⊕⊕ = 。

A. BB. AC. B A ⊕D. B A ⊕2.一个16选一的数据选择器,其地址输入(选择控制输入)端有 个。

A.1B.2C.4D.163.用三线-八线译码器74LS 138实现原码输出的8路数据分配器,应 。

A.A ST =1,B ST =D ,C ST =0 B. A ST =1,B ST =D ,C ST =D C.A ST =1,BST =0,CST =D D.A ST =D ,BST =0,CST =04.四选一数据选择器的数据输出Y 与数据输入X i 和地址码Ai之间的逻辑表达式为Y= 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 015.在下列触发器中,有约束条件的是 。

A.主从J K F/FB.主从 D F/FC.同步RS F /FD.边沿 D F/F6.对于T 触发器,若原态Q n =1,欲使新态Q n +1=1,应使输入T = 。

A.0B.1C.QD.Q7.为实现将J K 触发器转换为D 触发器,应使 。

A.J=D,K=DB. K =D ,J=DC.J=K=DD.J=K=D8.8位移位寄存器,串行输入时经 个脉冲后,8位数码全部移入寄存器中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程测试试题( A 卷)

----------------------以下为教师填写--------------------

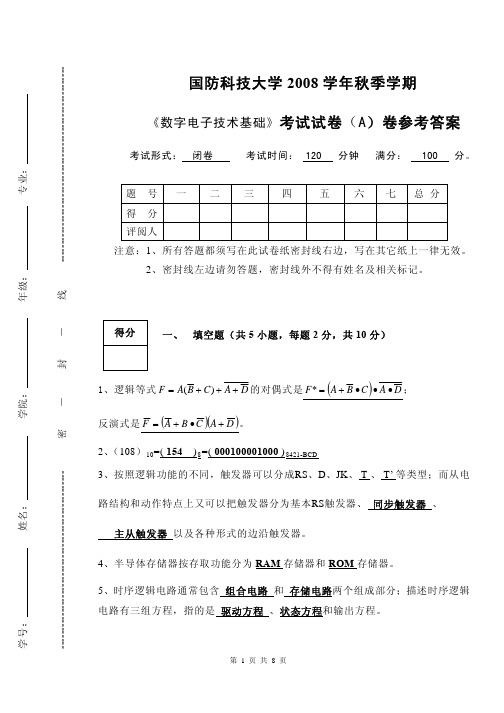

I 、命题院(系):物理科学与信息工程学院 II 、课程名称: 数字电子技术基础 III 、测试学期:2008-2009学年度第2学期 IV 、测试对象: 07电科2班(39人) VV 、问卷页数(A4): 5 页

VI 、考试方式: 闭卷 (开卷或闭卷) Ⅶ、考试时间:120分钟

Ⅷ、问卷内容:(学生将所有内容做在答题纸上的规定位置)

一.填空:(共20分,每空1分) 1.2168(1110.0111)(___________)(__________)==

2.为了将600份文件顺序编码,如果采用二进制代码,最少需要用__________位?如果改用八进制代码,最少需要用__________位?如果改用十六进制代码,最少需要用__________位?

3.2(00101)(____________)(_____________)==原码补码-

4.目前应用最广的__________和__________两类集成门电路

5.对于JK 触发器的两个输入端,当输入信号相反时构成_________触发器,当输入信号相同时构成____________触发器。

触发器的触发方式有____________、____________、____________。

6.半导体存储器从读、写的功能上分成_______________和

___________两大类型。

7. _____________和_____________是较早应用的两种PLD。

电路的基本结构是与-或逻辑陈列型。

8. _____________和_____________是A/D、D/A转换器最重要的两个指标。

二.证明题(共10分)

1.''

++=+

AB B A B A B

2.'()''''

⊕+++=⊕

A C D BC D ACD A

B

C

D C D

三.简答题:(共25分)

1.用卡诺图法将下列逻辑函数化简为最简与或式:

Y ABC ABD C D AB C A CD AC D

=+++++(5分)

''''''

2.试用4位同步二进制加法计数器74LS161设计一个同步7进制加法计数器。

(10分)

3.PROM 实现的组合逻辑函数如下图所示,写出组合逻辑函数F1和F2的最小项之和的形式。

(10分)

三.分析设计题:(共45分)

1.用8选1数据选择器74LS151设计一个组合逻辑电路。

该电路有3个输入逻辑变量A 、B 、C 和1个工作状态控制变量M 。

当0M =时电路实现“意见一致”功能(A 、B 、C 状态一致时输出为1,否则输出为0),而1M =时电路实现“多数表决”功能,即输出与A 、B 、C 中多数的状态一致。

(10分)

2.用全加器74LS283将余3码转换成8421的二十进制代码。

(5分)

3.由两片同步十进制计数器74LS160组成的计数器电路如图所示。

(10分)

(1)第一、二片74LS160各接成多少进制计数器?

(2)整个电路Y输出是多少进制计数器?

4.由二-五-十进制异步计数器74LS290组成的电路如图所示。

(3Q 2Q 1Q 0Q 初态为0000),试求:(10分)

(1)在脉冲信号CP 作用下,画出3Q 2Q 1Q 0Q 状态转换图。

(2)说明该电路是几进制计数器。

5.由555定时器构成的电路如图所示。

试问: (1) 该电路构成什么功能的脉冲电路? (2) 计算振荡器频率及占空比。

(3) 定性画出C V 及O V 的工作波形图。

(10分)

C。