LM2663中文资料

和利时LM可编程控制器硬件手册

第1章从硬件体系结构、编程软件、快速应用等各个方面对LM小型PLC作了概述性介绍。

第2、3章主要针对CPU模块、扩展模块的技术规格、端子定义与接线示意图及等效电路进行 了详细阐述。

目录

第 1 章 概述 .......................................................................................................... 1

1.1 概述................................................................................................................................................... 1 1.2 硬件体系结构................................................................................................................................... 1

本手册仅供商业用户阅读、查询,在未得到北京和利时系统工程股份有限公司特别授权的 情况下,无论出于何种原因和目的,均不得用任何电子或机械方法,以任何形式复制和传递本 手册的内容。否则本公司将依法追究法律责任。

我们已核对本手册中的内容、图表与所述硬件设备相符,但误差难以避免,并不能保证完 全一致,还恳请广大用户批评指正。同时,我们会定期对手册的内容、图表进行检查、修改和 维护,恕不另行通知。

LM883AH中文资料

Parameter

Conditions

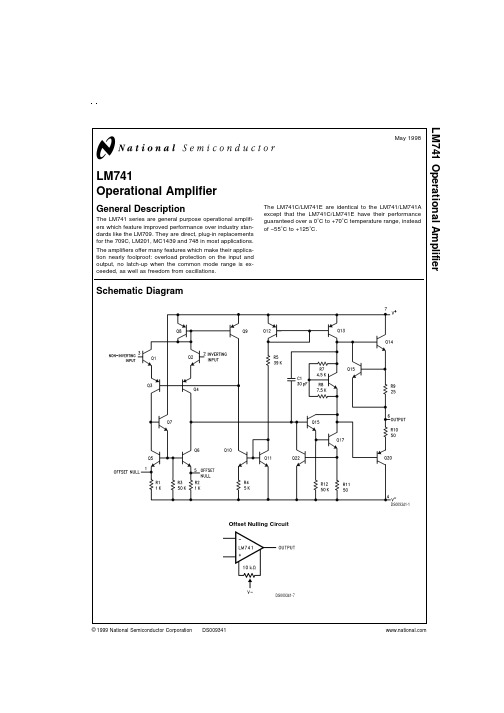

LM741A/LM741E

LM741

LM741C

Units

Min Typ Max Min Typ Max Min Typ Max

Large Signal Voltage Gain TA = 25˚C, RL ≥ 2 kΩ

VS = ±20V, VO = ±15V

50

LM741A/LM741E

LM741

LM741C

Units

Min Typ Max Min Typ Max Min Typ Max

0.8 3.0

1.0 5.0

2.0 6.0 mV mV

4.0

mV

6.0

7.5 mV

15

µV/˚C

±10

±15

±15

mV

3.0 30 70 0.5

20 200 85 500

20 200 nA 300 nA nA/˚C

Input Voltage (Note 3)

±15V

±15V

±15V

±15V

Output Short Circuit Duration

Continuous

Continuous

Continuous

Continuous

Operating Temperature Range

−55˚C to +125˚C

0˚C to +70˚C

(Note 6)

LM741A

LM741E

LM741

LM741C

Supply Voltage

±22V

±22V

±22V

±18V

Power Dissipation (Note 2)

LM2662 data sheet芯片数据表单

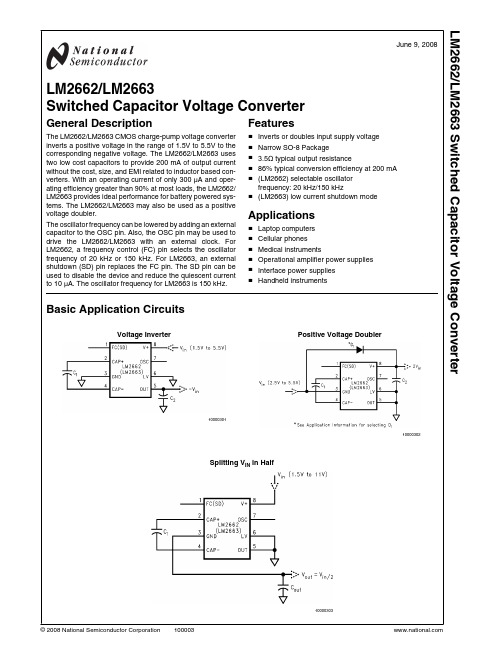

June 9, 2008 LM2662/LM2663Switched Capacitor Voltage ConverterGeneral DescriptionThe LM2662/LM2663 CMOS charge-pump voltage converterinverts a positive voltage in the range of 1.5V to 5.5V to thecorresponding negative voltage. The LM2662/LM2663 usestwo low cost capacitors to provide 200 mA of output currentwithout the cost, size, and EMI related to inductor based con-verters. With an operating current of only 300 μA and oper-ating efficiency greater than 90% at most loads, the LM2662/LM2663 provides ideal performance for battery powered sys-tems. The LM2662/LM2663 may also be used as a positivevoltage doubler.The oscillator frequency can be lowered by adding an externalcapacitor to the OSC pin. Also, the OSC pin may be used todrive the LM2662/LM2663 with an external clock. ForLM2662, a frequency control (FC) pin selects the oscillatorfrequency of 20 kHz or 150 kHz. For LM2663, an externalshutdown (SD) pin replaces the FC pin. The SD pin can beused to disable the device and reduce the quiescent currentto 10 μA. The oscillator frequency for LM2663 is 150 kHz.Features■Inverts or doubles input supply voltage■Narrow SO-8 Package■ 3.5Ω typical output resistance■86% typical conversion efficiency at 200 mA■(LM2662) selectable oscillatorfrequency: 20 kHz/150 kHz■(LM2663) low current shutdown modeApplications■Laptop computers■Cellular phones■Medical instruments■Operational amplifier power supplies■Interface power supplies■Handheld instrumentsBasic Application CircuitsVoltage Inverter10000301Positive Voltage Doubler10000302Splitting VINin Half10000303© 2008 National Semiconductor LM2662/LM2663 Switched Capacitor Voltage ConverterAbsolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V+ to GND, or GND to OUT)6V LV (OUT − 0.3V) to (GND + 3V)FC, OSC, SD The least negative of (OUT − 0.3V)or (V+ − 6V) to (V+ + 0.3V)V+ and OUT Continuous Output Current 250 mA Output Short-Circuit Duration to GND (Note 2) 1 sec.Power Dissipation (T A = 25°C) (Note 3)735 mWT J Max (Note 3)150°CθJA (Note 3)170°C/WOperating Ambient Temperature Range −40°C to +85°C Operating Junction Temperature Range −40°C to +105°C Storage Temperature Range −65°C to +150°C Lead Temperature (Soldering, 10 seconds)300°C ESD Rating 2 kVElectrical CharacteristicsLimits in standard typeface are for T J = 25°C, and limits in boldface type apply over the full Operating Junction TemperatureRange. Unless otherwise specified: V+ = 5V, FC = Open, C 1 = C 2 = 47 μF.(Note 4)Symbol ParameterConditionMin Typ Max Units V+Supply VoltageR L = 1kInverter, LV = Open 3.5 5.5 Inverter, LV = GND 1.5 5.5VDoubler, LV = OUT 2.5 5.5 I Q Supply Current No Load FC = V+ (LM2662)1.34mALV = Open SD = Ground (LM2663)FC = Open0.30.8I SD Shutdown Supply Current10μA (LM2663)V SD Shutdown Pin Input Voltage Shutdown Mode 2.0(Note 5)V (LM2663)Normal Operation0.3I L Output Current200mA R OUT Output Resistance (Note 6)I L = 200 mA 3.57Ωf OSC Oscillator Frequency (Note 7)OSC = Open FC = Open 720kHzFC = V+55150 f SW Switching Frequency (Note 8)OSC = Open FC = Open 3.510 kHzFC = V+27.575 I OSC OSC Input Current FC = Open ±2 μAFC = V+±10 P EFF Power Efficiency R L (500) between V + and OUT 9096 %I L = 200 mA to GND 86 V OEFFVoltage Conversion EfficiencyNo Load9999.96%Note 1:Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical specifications do not apply when operating the device beyond its rated operating conditions.Note 2:OUT may be shorted to GND for one second without damage. However, shorting OUT to V+ may damage the device and should be avoided. Also, for temperatures above 85°C, OUT must not be shorted to GND or V+, or device may be damaged.Note 3:The maximum allowable power dissipation is calculated by using P DMax = (T JMax − T A )/θJA , where T JMax is the maximum junction temperature, T A is the ambient temperature, and θJA is the junction-to-ambient thermal resistance of the specified package.Note 4:In the test circuit, capacitors C 1 and C 2 are 47 μF, 0.2Ω maximum ESR capacitors. Capacitors with higher ESR will increase output resistance, reduce output voltage and efficiency.Note 5:In doubling mode, when V out > 5V, minimum input high for shutdown equals V out − 3V.Note 6:Specified output resistance includes internal switch resistance and capacitor ESR.Note 7:For LM2663, the oscillator frequency is 150 kHz.Note 8:The output switches operate at one half of the oscillator frequency, f OSC = 2f SW . 2L M 2662/L M 2663Test Circuits1000030410000305FIGURE 1. LM2662 and LM2663 Test CircuitsTypical Performance Characteristics(Circuit of Figure 1)Supply Current vsSupply Voltage10000337Supply Current vsOscillator Frequency10000338Output SourceResistance vs SupplyVoltage10000339Output SourceResistance vsTemperature10000340LM2662/LM2663Output Source Resistance vs Temperature10000341Efficiency vs LoadCurrent10000342Output Voltage Drop vs Load Current 10000343Efficiency vs Oscillator Frequency10000344Output Voltage vs Oscillator Frequency10000345Oscillator Frequencyvs External Capacitance10000346 4L M 2662/L M 2663Oscillator Frequencyvs Supply Voltage10000347Oscillator Frequencyvs Supply Voltage10000348Oscillator Frequencyvs Temperature10000349Oscillator Frequencyvs Temperature10000350Shutdown SupplyCurrent vsTemperature(LM2663 Only)10000351 LM2662/LM2663Connection Diagrams8-Lead SO (M)1000032010000321Top ViewOrder Number LM2662M, LM2663M See NS Package Number M08APin DescriptionsPin NameFunctionVoltage InverterVoltage Doubler1FC Frequency control for internal oscillator:Same as inverter.(LM2662)FC = open, f OSC = 20 kHz (typ);FC = V+, f OSC = 150 kHz (typ);FC has no effect when OSC pin is driven externally.1SD (LM2663)Shutdown control pin, tie this pin to the ground in normal operation.Same as inverter.2CAP+Connect this pin to the positive terminal of charge-pump capacitor.Same as inverter.3GND Power supply ground input.Power supply positive voltage input.4CAP−Connect this pin to the negative terminal of charge-pump capacitor.Same as inverter.5OUT Negative voltage output.Power supply ground input.6LVLow-voltage operation input. Tie LV to GND when input voltage is less than 3.5V. Above 3.5V, LV can beconnected to GND or left open. When driving OSC with an external clock, LV must be connected to GND.LV must be tied to OUT.7OSCOscillator control input. OSC is connected to an internal 15 pF capacitor. An external capacitor can be connected to slow the oscillator. Also, an external clock can be used to drive OSC.Same as inverter except that OSC cannot be driven by an external clock.8V+Power supply positive voltage input.Positive voltage output.Circuit DescriptionThe LM2662/LM2663 contains four large CMOS switches which are switched in a sequence to invert the input supply voltage. Energy transfer and storage are provided by external capacitors. Figure 2 illustrates the voltage conversion scheme. When S 1 and S 3 are closed, C 1 charges to the supply voltage V+. During this time interval switches S 2 and S 4 are open. In the second time interval, S 1 and S 3 are open and S 2 and S 4 are closed, C 1 is charging C 2. After a number of cycles, the voltage across C 2 will be pumped to V+. Since the anode of C 2 is connected to ground, the output at the cathode of C 2 equals −(V+) assuming no load on C 2, no loss in the switches, and no ESR in the capacitors. In reality, the chargetransfer efficiency depends on the switching frequency, the on-resistance of the switches, and the ESR of the capacitors. 6L M 2662/L M 266310000322FIGURE 2. Voltage Inverting PrincipleApplication InformationSIMPLE NEGATIVE VOLTAGE CONVERTERThe main application of LM2662/LM2663 is to generate a negative supply voltage. The voltage inverter circuit uses only two external capacitors as shown in the Basic Application Circuits. The range of the input supply voltage is 1.5V to 5.5V.For a supply voltage less than 3.5V, the LV pin must be con-nected to ground to bypass the internal regulator circuitry.This gives the best performance in low voltage applications.If the supply voltage is greater than 3.5V, LV may be con-nected to ground or left open. The choice of leaving LV open simplifies the direct substitution of the LM2662/LM2663 for the LMC7660 Switched Capacitor Voltage Converter.The output characteristics of this circuit can be approximated by an ideal voltage source in series with a resistor. The volt-age source equals −(V+). The output resistance R out is a function of the ON resistance of the internal MOS switches,the oscillator frequency, and the capacitance and ESR of C 1and C 2. Since the switching current charging and discharging C 1 is approximately twice as the output current, the effect of the ESR of the pumping capacitor C 1 is multiplied by four in the output resistance. The output capacitor C 2 is charging and discharging at a current approximately equal to the output current, therefore, its ESR only counts once in the output re-sistance. A good approximation is:where R SW is the sum of the ON resistance of the internal MOS switches shown in Figure 2.High value, low ESR capacitors will reduce the output resis-tance. Instead of increasing the capacitance, the oscillator frequency can be increased to reduce the 2/(f osc × C 1) term.Once this term is trivial compared with R SW and ESRs, further increasing in oscillator frequency and capacitance will be-come ineffective.The peak-to-peak output voltage ripple is determined by the oscillator frequency, and the capacitance and ESR of the out-put capacitor C 2:Again, using a low ESR capacitor will result in lower ripple.POSITIVE VOLTAGE DOUBLERThe LM2662/LM2663 can operate as a positive voltage dou-bler (as shown in the Basic Application Circuits). The doubling function is achieved by reversing some of the connections tothe device. The input voltage is applied to the GND pin with an allowable voltage from 2.5V to 5.5V. The V+ pin is used as the output. The LV pin and OUT pin must be connected to ground. The OSC pin can not be driven by an external clock in this operation mode. The unloaded output voltage is twice of the input voltage and is not reduced by the diode D 1's for-ward drop.The Schottky diode D 1 is only needed for start-up. The internal oscillator circuit uses the V+ pin and the LV pin (connected to ground in the voltage doubler circuit) as its power rails. Volt-age across V+ and LV must be larger than 1.5V to insure the operation of the oscillator. During start-up, D 1 is used to charge up the voltage at V+ pin to start the oscillator; also, it protects the device from turning-on its own parasitic diode and potentially latching-up. Therefore, the Schottky diode D 1should have enough current carrying capability to charge the output capacitor at start-up, as well as a low forward voltage to prevent the internal parasitic diode from turning-on. A Schottky diode like 1N5817 can be used for most applica-tions. If the input voltage ramp is less than 10V/ms, a smaller Schottky diode like MBR0520LT1 can be used to reduce the circuit size.SPLIT V+ IN HALFAnother interesting application shown in the Basic Application Circuits is using the LM2662/LM2663 as a precision voltage divider. Since the off-voltage across each switch equals V IN /2, the input voltage can be raised to +11V.CHANGING OSCILLATOR FREQUENCYFor the LM2662, the internal oscillator frequency can be se-lected using the Frequency Control (FC) pin. When FC is open, the oscillator frequency is 20 kHz; when FC is connect-ed to V+, the frequency increases to 150 kH z. A higher oscillator frequency allows smaller capacitors to be used for equivalent output resistance and ripple, but increases the typ-ical supply current from 0.3 mA to 1.3 mA.The oscillator frequency can be lowered by adding an external capacitor between OSC and GND (See typical performance characteristics). Also, in the inverter mode, an external clock that swings within 100 mV of V+ and GND can be used to drive OSC. Any CMOS logic gate is suitable for driving OSC.LV must be grounded when driving OSC. The maximum ex-ternal clock frequency is limited to 150 kHz.The switching frequency of the converter (also called the charge pump frequency) is half of the oscillator frequency.Note:OSC cannot be driven by an external clock in the voltage-doublingmode.TABLE 1. LM2662 Oscillator Frequency SelectionFC OSCOscillator Open Open 20 kHz V+Open150 kHz Open or V+External CapacitorSee Typical Performance Characteristics N/AExternal ClockExternal Clock(inverter mode only)Frequency7LM2662/LM2663TABLE 2. LM2663 Oscillator Frequency SelectionOSCOscillatorOpen 150 kHzExternal Capacitor See Typical PerformanceCharacteristicsExternal Clock External Clock Frequency (inverter mode only)SHUTDOWN MODEFor the LM2663, a shutdown (SD) pin is available to disable the device and reduce the quiescent current to 10 μA. Apply-ing a voltage greater than 2V to the SD pin will bring the device into shutdown mode. While in normal operating mode, the SD pin is connected to ground.CAPACITOR SELECTIONAs discussed in the Simple Negative Voltage Converter sec-tion, the output resistance and ripple voltage are dependent on the capacitance and ESR values of the external capaci-tors. The output voltage drop is the load current times the output resistance, and the power efficiency isWhere I Q (V+) is the quiescent power loss of the IC device,and I L 2R OUT is the conversion loss associated with the switch on-resistance, the two external capacitors and their ESRs.Low ESR capacitors (Table 3) are recommended for both ca-pacitors to maximize efficiency, reduce the output voltage drop and voltage ripple. For convenience, C 1 and C 2 are usu-ally chosen to be the same.The output resistance varies with the oscillator frequency and the capacitors. In Figure 3, the output resistance vs. oscillator frequency curves are drawn for four difference capacitor val-ues. At very low frequency range, capacitance plays the most important role in determining the output resistance. Once the frequency is increased to some point (such as 100 kHz for the 47 μF capacitors), the output resistance is dominated by the ON resistance of the internal switches and the ESRs of the external capacitors. A low value, smaller size capacitor usu-ally has a higher ESR compared with a bigger size capacitor of the same type. Ceramic capacitors can be chosen for their lower ESR. As shown in Figure 3, in higher frequency range,the output resistance using the 10 μF ceramic capacitors is close to these using higher value tantalum capacitors.10000336FIGURE 3. Output Source Resistance vs Oscillator FrequencyTABLE 3. Low ESR Capacitor ManufacturersManufacturer PhoneCapacitor TypeNichicon Corp.(708)-843-7500PL, PF series, through-hole aluminum electrolytic AVX Corp.(803)-448-9411TPS series, surface-mount tantalumSprague (207)-324-4140593D, 594D, 595D series, surface-mount tantalum Sanyo (619)-661-6835OS-CON series, through-hole aluminum electrolytic Murata (800)-831-9172Ceramic chip capacitors Taiyo Yuden (800)-348-2496Ceramic chip capacitors Tokin(408)-432-8020Ceramic chip capacitors 8L M 2662/L M 2663Other ApplicationsPARALLELING DEVICESAny number of LM2662s (or LM2663s) can be paralleled to reduce the output resistance. Each device must have its own pumping capacitor C 1, while only one output capacitor C out is needed as shown in Figure 4. The composite output resis-tance is:10000324FIGURE 4. Lowering Output Resistance by Paralleling DevicesCASCADING DEVICESCascading the LM2662s (or LM2663s) is an easy way to pro-duce a greater negative voltage (as shown in Figure 5). If n is the integer representing the number of devices cascaded, the unloaded output voltage V out is (−nV in ). The effective output resistance is equal to the weighted sum of each individual device:A three-stage cascade circuit shown in Figure 6 generates −3V in , from V in .Cascading is also possible when devices are operating in doubling mode. In Figure 7, two devices are cascaded to generate 3V in .An example of using the circuit in Figure 6 or Figure 7 is gen-erating +15V or −15V from a +5V input.Note that, the number of n is practically limited since the in-creasing of n significantly reduces the efficiency and increas-es the output resistance and output voltage ripple.10000325FIGURE 5. Increasing Output Voltage by Cascading DevicesLM2662/LM266310000326FIGURE 6. Generating −3Vinfrom +Vin10000327FIGURE 7. Generating +3Vinfrom +VinREGULATING VoutIt is possible to regulate the output of the LM2662/LM2663 byuse of a low dropout regulator (such as LP2986). The wholeconverter is depicted in Figure 8. This converter can give aregulated output from −1.5V to −5.5V by choosing the properresistor ratio:where, Vref= 1.23VThe error flag on pin 7 of the LP2986 goes low when the reg-ulated output at pin 5 drops by about 5% below nominal. TheLP2986 can be shutdown by taking pin 8 low. The less than1 μA quiescent current in the shutdown mode is favorable forbattery powered applications.10LM2662/LM266310000328 FIGURE 8. Combining LM2662/LM2663 with LP2986 to Make a Negative Adjustable RegulatorAlso, as shown in Figure 9 by operating the LM2662/LM2663 in voltage doubling mode and adding a low dropout regulator (such as LP2986) at the output, we can get +5V output from an input as low as +3.3V.10000329FIGURE 9. Generating +5V from +3.3V Input Voltage LM2662/LM2663Physical Dimensions inches (millimeters) unless otherwise noted8-Lead SO (M)Order Number LM2662M or LM2663MNS Package Number M08A 12L M 2662/L M 2663LM2662/LM2663 NotesNotesL M 2662/L M 2663 S w i t c h e d C a p a c i t o r V o l t a g e C o n v e r t e rFor more National Semiconductor product information and proven design tools, visit the following Web sites at:ProductsDesign SupportAmplifiers /amplifiers WEBENCH /webench Audio/audio Analog University /AU Clock Conditioners /timing App Notes /appnotes Data Converters /adc Distributors /contacts Displays /displays Green Compliance /quality/green Ethernet /ethernet Packaging/packaging Interface /interface Quality and Reliability /quality LVDS/lvds Reference Designs /refdesigns Power Management /power Feedback /feedback Switching Regulators /switchers LDOs /ldo LED Lighting /led PowerWise/powerwise Serial Digital Interface (SDI)/sdiTemperature Sensors /tempsensors Wireless (PLL/VCO)/wirelessTHE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION (“NATIONAL”) PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF TH E CONTENTS OF TH IS PUBLICATION AND RESERVES TH E RIGH T TO MAKE CH ANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITH OUT NOTICE. NO LICENSE, WH ETH ER EXPRESS,IMPLIED, ARISING BY ESTOPPEL OR OTH ERWISE, TO ANY INTELLECTUAL PROPERTY RIGH TS IS GRANTED BY TH IS DOCUMENT.TESTING AND OTH ER QUALITY CONTROLS ARE USED TO TH E EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL’S PRODUCT WARRANTY. EXCEPT WH ERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR TH EIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS TH AT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.EXCEPT AS PROVIDED IN NATIONAL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WH ATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO TH E SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCH ANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGH T OR OTH ER INTELLECTUAL PROPERTY RIGHT.LIFE SUPPORT POLICYN ATION AL’S PRODUCTS ARE N OT AUTHORIZED FOR USE AS CRITICAL COMPON EN TS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AN D GEN ERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.Copyright© 2008 National Semiconductor CorporationFor the most current product information visit us at National Semiconductor Americas Technical Support CenterEmail: support@ Tel: 1-800-272-9959National Semiconductor Europe Technical Support CenterEmail: europe.support@ German Tel: +49 (0) 180 5010 771English Tel: +44 (0) 870 850 4288National Semiconductor Asia Pacific Technical Support Center Email: ap.support@National Semiconductor Japan Technical Support Center Email: jpn.feedback@。

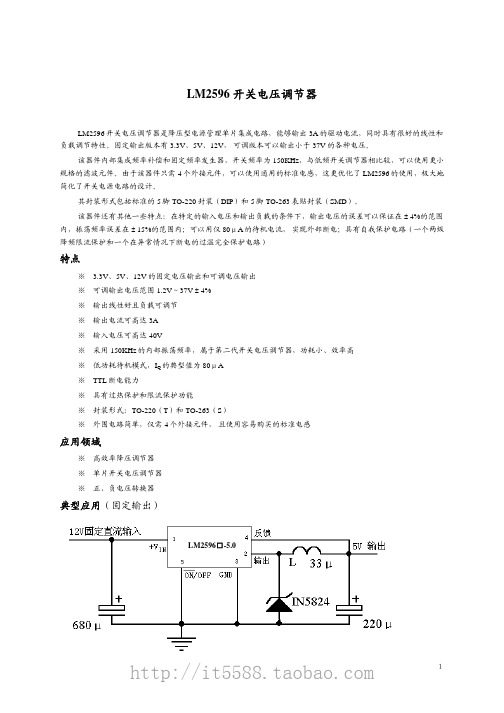

lm2596-3.3 LM2596-ADJ LM2596-12 LV2596-3.3 中文资料

2.0

V(min)

5

μA

15

μA(max)

0.02

μA

5

μA(max)

注 2: 典型值是指在 25℃下的数值,代表最常见的情况。 注 3: 所有的极限参数都必须适合于室温(用正常字体表示)和极限温度(用带下划线的粗斜体字表示),所有室

温下的极限参数都是经过测试得出的,所有的极限温度下的极限参数都可以通过使用相关的标准静态质量控 制方法来加以保证。 注 4:二极管、电感、输入和输出端的电容以及调节输出电压的电阻等外接元件可能会影响开关调节器的系统性 能。当 LM2596 用在如图 1 所示测试电路中时,其系统性能如电气特性中系统参量所示。 注 5:当第二级电流极限功能启动时,开关频率会有所下降, 下降的程度取决于过电流的严重程度。 注 6:输出管脚不连接电感、电容或二极管。 注 7:把反馈管脚和输出管脚断开,把反馈管脚连到 0V,以强制输出开关晶体管导通。 注 8:把反馈管脚和输出管脚断开,把反馈管脚连到 12V(当 VOUT=3.3V、5V 或 ADJ 时)或 15V(当 VOUT=12V 时), 以强制输出开关晶体管截止。 注 9:VIN=40V 注 10:环境热阻(不外加散热片)是指 TO-220 封装的 LM2596 垂直焊接在覆盖有面积约为 1 平方英寸铜箔的 PCB 上所对应的值。 注 11:TO-263 封装的 LM2596 垂直焊接在覆盖有面积约为 0.5 平方英寸铜箔的单面 PCB 上所对应的环境热阻。 注 12:TO-263 封装的 LM2596 垂直焊接在覆盖有面积约为 2.5 平方英寸铜箔的单面 PCB 上所对应的环境热阻。 注 13:TO-263 封装的 LM2596 垂直焊接在覆盖有面积约为 3 平方英寸铜箔的双面 PCB 上所对应的环境热阻,而 PCB 的另一面覆盖有面积约为 16 平方英寸铜箔。 注14: LM2596T-3.3, LM2596T-5.0, LM2596T-12, LM2596T-ADJ为TO-220封装(DIP); LM2596S-3.3, LM2596S-5.0,LM2596S-12, LM2596S-ADJ为TO-263封装(SMT)。

高速光耦6N137HCPL2601,HCPL2611,HCPL2630,HCPL2631中文资料

高速光耦6N137HCPL2601,HCPL2611,HCPL2630,HCPL2631中文资料高速光耦6N137/HCPL2601,HCPL2611,HCPL2630,HCPL2631中文资料常用高速光电耦合器型号:单通道: 6N137 , HCPL2601 , HCPL2611双通道: HCPL2630 , HCPL2631高速10MBit / s的逻辑门光电作用:6N137/HCPL2601,HCPL2611,HCPL2630,HCPL2631是高速光电耦合器内部结构框图6N137/HCPL2601,HCPL2611,HCPL2630,HCPL2631的内部结构原理如下图所示,信号从脚2和脚3输入,发光二极管发光,经片内光通道传到光敏二极管,反向偏置的光敏管光照后导通,经电流-电压转换后送到与门的一个输入端,与门的另一个输入为使能端,当使能端为高时与门输出高电平,经输出三极管反向后光电隔离器输出低电平。

当输入信号电流小于触发阈值或使能端为低时,输出高电平,但这个逻辑高是集电极开路的,可针对接收电路加上拉电阻或电压调整电路。

引脚图原理如上图所示,若以脚2为输入,脚3接地,则真值表如附表所列,这相当于非门的传输,若希望在传输过程中不改变逻辑状态,则从脚3输入,脚2接高电平。

6N137/HCPL2601,HCPL2611,HCPL2630,HCPL2631真值表真值表功能(正逻辑)高速光耦6N137/HCPL2601,HCPL2611,HCPL2630,HCPL2631参数绝对最大额定值(Ta= 25 ℃除非另有说明):建议操作条件:电学特性(Ta=0至70 ,除非另有规定)单独的组件特征:开关特性 (TA= -40℃ to 85℃, VCC= 5V, IF= 7.5mA 除非另有说明):电气特性(续)转移特性(TA = -40 to 85℃ 除非另有说明)隔离特性(Ta= -40 ℃至85 ℃ ,除非另有说明. ):波形图测试电路和波形 tPLH, tPHL, tr and tf测试电路tEHL和tELHTAG标签:HCPL26HCPL2631HCPL2630资料中文顶一下(1)100.00%踩一下(0)0.00%------分隔线----------------------------。

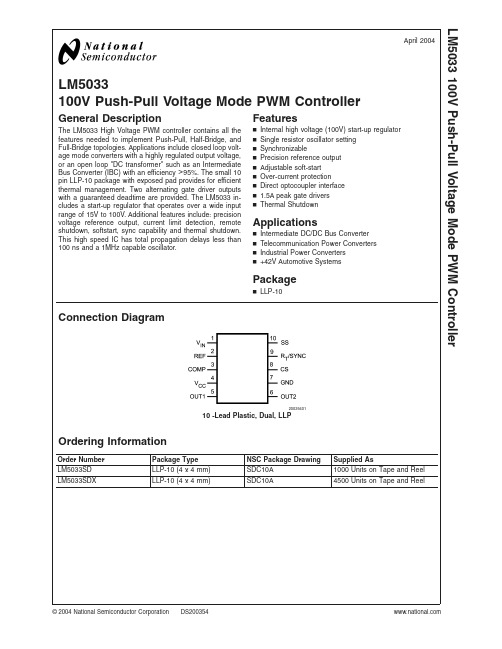

LM5033中文资料

LM5033100V Push-Pull Voltage Mode PWM ControllerGeneral DescriptionThe LM5033High Voltage PWM controller contains all the features needed to implement Push-Pull,Half-Bridge,and Full-Bridge topologies.Applications include closed loop volt-age mode converters with a highly regulated output voltage,or an open loop "DC transformer"such as an Intermediate Bus Converter (IBC)with an efficiency >95%.The small 10pin LLP-10package with exposed pad provides for efficient thermal management.Two alternating gate driver outputs with a guaranteed deadtime are provided.The LM5033in-cludes a start-up regulator that operates over a wide input range of 15V to 100V.Additional features include:precision voltage reference output,current limit detection,remote shutdown,softstart,sync capability and thermal shutdown.This high speed IC has total propagation delays less than 100ns and a 1MHz capable oscillator.Featuresn Internal high voltage (100V)start-up regulator n Single resistor oscillator setting n Synchronizablen Precision reference output n Adjustable soft-start n Over-current protectionn Direct optocoupler interface n 1.5A peak gate drivers nThermal ShutdownApplicationsn Intermediate DC/DC Bus Converter n Telecommunication Power Converters n Industrial Power Converters n+42V Automotive SystemsPackagen LLP-10Connection Diagram2003540110-Lead Plastic,Dual,LLPOrdering InformationOrder Number Package Type NSC Package Drawing Supplied AsLM5033SD LLP-10(4x 4mm)SDC10A 1000Units on Tape and Reel LM5033SDXLLP-10(4x 4mm)SDC10A4500Units on Tape and ReelApril 2004LM5033100V Push-Pull Voltage Mode PWM Controller©2004National Semiconductor Corporation Pin DescriptionPIN NAME DESCRIPTIONAPPLICATION INFORMATION1Vin Input VoltageInput to the start-up regulator.Input range is 15V to 90V,with transient capability to 100V .2REF 2.5V precision reference output Sink only,requires an external pull-up resistor.This can be used as a reference for external circuitry.3COMPPWM InputFeedback to the PWM comparator’s inverting input,through a 3:1divider.The output duty cycle increases as this pin’s voltage increases.Internally there is a 5k Ωpullup to +5.2V.4VCC9.6V output from the internal high voltage series pass regulatorAn external voltage (10V -15V)can be applied to this pin to shutdown the internal regulator,thereby reducing internal dissipation.An internal diode connects Vcc to Vin.5OUT1Gate Driver Output #1Alternating output gate driver,which can source and sink 1.5A.6OUT2Gate Driver Output #2Alternating output gate driver,which can source and sink 1.5A.7GNDGround pin for all internal circuitryConnections to external ground must be done with care for optimum performance.See the Functional Description and Applications Section for more information.8CS Current sense inputCurrent sense input for the current limit detection.If CS exceeds 0.5V the outputs are disabled and the softstart pin is discharged to ground.9R T /SYNCOscillator timing resistor pin and synchronization input An external resistor to ground sets the oscillator frequency.This pin will also accept ac-coupled synchronization pulses from an external source.10SSSoftstart pinAn internal 10µA current source and an external capacitor set the soft-start timing.This pin can be externally pulled to below 0.5V to disable the output drivers.L M 5033 2LM5033 Block DiagramFunctional Block Diagram Array20035402FIGURE1.3Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.V IN to GND -0.3V to 100V V CC to GND -0.3V to 16V Rt/Sync to GND -0.3V to 5.5V Pins 3,8,10to GND -0.3V to 7.0VESD Rating (Note 3)Human Body Model 2kVStorage Temperature Range -65˚C to 150˚C Junction Temperature 150˚CPower Dissipation (Note 2)Internally LimitedOperating Ratings (Note 1)V IN Voltage (Pin1)15to 90V Operating Junction Temperature-40˚C to 125˚CElectrical CharacteristicsSpecifications with standard typeface are for T J =25˚C,and those with boldface type apply over full Operating Junction Temperature range .V IN =48V,V CC =10V applied externally,R T =26.7k Ω,unless otherwise stated.See (Note 4)and (Note 5).Symbol Parameter ConditionsMin Typ Max Units V CC Startup Regulator (Pins 1,4)V CC Reg V CC Voltage Pin 4open9.29.610.0V Icc-outV CC Current LimitOut1,Out2disabled.Ext.supply to Vcc disconnected.2034mAIinStartup Regulator Current into V INNormal Operation V IN =90V150500µA Ext.V CC Supply Disconnected andOutput Load =1800pF 7mASS Pin =0V3mA UVTV CC Undervoltage Threshold (increasing V CC )VccReg -300mV VccReg -100mVVUVT Hysteresis (decreasing V CC )2.3 2.83.3Icc-inSupply Current from external source to V CCSS Pin =0V23mASS Pin =open and Output Load =1800pF 72.5V Reference (Pin 2)VrefOutput voltage Pin 2sink current =5mA2.44 2.50 2.56V Current sink capability5.013mACurrent Sense (Pin 8)CSThreshold voltage 0.450.500.55V CS delay to outputPin 8taken from zero to 0.6V.Time for Out1or Out2to fall to 90%of Vcc.CLoad =0@Out1,Out230nsCurrent sink capability (clocked)Pin 8≤0.3V36mASoftstart (Pin 10)Softstart current source71013µA Softstart to Comp offset0.250.500.75V Open Circuit Voltage5.0VL M 5033 4Electrical Characteristics(Continued)Specifications with standard typeface are for T J=25˚C,and those with boldface type apply over full Operating Junction Temperature range.V IN=48V,V CC=10V applied externally,R T=26.7kΩ,unless otherwise stated.See(Note4)and(Note 5).Symbol Parameter Conditions Min Typ Max Units Oscillator(Pin9)Fs1Internal frequency Rt=26.7kΩ175200225kHz Fs2Internal frequency Rt=8.2kΩ600kHz Vsync Sync threshold 3.2 3.8V R t/Sync DC voltage 2.0V PWM Comparator Input(Pin3)t PWM Gain from pin3toPWM comparator0.34V/VMaximum duty cycle at Out1,Out2See PWM Comparatortext100x(0.5T S-T D)/T S%Minimum duty cycle atOut1,Out2Pin3=0V.0% Open Circuit Voltage 4.2 5.2 6.2VShort circuit current Pin3=0V0.6 1.1 1.5mAOutput Drivers(Pin5,6)Deadtime(T D)CLoad=0@OUT1,OUT2.Time measuredfrom10%of fallingoutput to10%of risingoutput.85135185nsRise Time C Load=1nF16nsFall Time C Load=1nF16nsOutput High Voltage Iout=50mA(source)Vcc-0.75Vcc-0.25VOutput Low Voltage Iout=100mA(sink)0.250.75VMax.source current 1.5AMax.sink current 1.5AThermal ShutdownT SD Shutdown temperature165˚C Shutdown temperaturehysteresis15˚CThermal ResistanceθJA Junction to Ambient SDC10A Package38˚C/WNote1:Absolute Maximum Ratings are limits beyond which damage to the device may occur.Operating Ratings are conditions under which operation of the deviceis intended to be functional.For guaranteed specifications and test conditions,see the Electrical Characteristics.Note2:The maximum allowable power dissipation is a function of the maximum allowed junction temperature(T J(max)),the ambient temperature(T A),and thejunction-to-ambient thermal resistance(θJA).The maximum allowable power dissipation can be calculated from PD=(T J(max)-T A)/θJA.Excessive power dissipationwill cause the thermal shutdown to activate.Note3:The human body model is a100pF capacitor discharged through a1.5kΩresistor into each pin.Note4:Min and Max limits are100%production tested at25˚C.Limits over the operating temperature range are guaranteed through correlation using StatisticalQuality Control(SQC)methods.Limits are used to calculate National’s Average Outgoing Quality Level(AOQL).Note5:Typical specifications represent the most likely parametric norm at25˚C operation.LM50335Typical Performance CharacteristicsV CC vs V INV CC vs I CC (V IN =48V)2003540320035404Oscillator Frequency vs R TOscillator Frequency vs TemperatureR T =26.7k Ω2003540520035406Soft Start Current vs Temperature Dead Time vs Temperature2003540720035408L M 5033 6Typical Performance Characteristics(Continued)Output Duty Cycle vs Comp VoltageR T=16.5kΩV REF vs I REF2003540920035410I CC vs V CC(V CC Powered Externally)I IN vs V IN(V CC Not Powered Externally)2003541120035412LM5033 7Functional DescriptionThe LM5033High Voltage PWM controller contains all of the features needed to implement Push-Pull and Bridge topolo-gies,using voltage-mode control in a small 10pin package.Features included are:startup regulator,precision 2.5V ref-erence output,current limit detection,alternating gate driv-ers,sync capability,thermal shutdown,softstart,and remote shutdown.This high speed IC has total propagation delays <100ns.These features simplify the design of an open loop DC-DC converter,or a voltage controlled closed loop con-verter.The Functional Block Diagram is shown in Figure 1.High Voltage Start-Up Regulator (Pins 1,4)The LM5033contains an internal high voltage startup regu-lator.The input pin (V IN )can be connected directly to line voltages as high as 90V for normal operation,and can withstand transients to 100V.The regulator output at V CC (9.6V)is internally current limited and sources a minimum of 20mA.Upon power up,the capacitor at V CC will charge up,providing a time delay while internal circuits stabilize.When V CC reaches the upper threshold of the under-voltage sen-sor (typically 9.5V),the under-voltage sensor resets,en-abling the output drivers,although the PWM duty cycle will initially be at zero.As the Softstart capacitor then charges up (described below)the output duty cycle will increase until regulated by the PWM control loop.The value of the V CC capacitor which affects the above mentioned delay depends on the total system design and its start-up characteristics.The recommended range of values for the V CC capacitor is 0.1to 50µF.The lower threshold of the under-voltage sensor is typically at 6.8V.If V CC falls below this value the outputs are disabled and the softstart capacitor is discharged.When V CC is again increased above the upper threshold the outputs are en-abled,and the softstart sequence repeats.The LM5033’s internal power dissipation can be reduced by powering V CC from an external supply.Typically this is done by means of an auxiliary transformer winding which is diode connected to the V CC pin to provide 10-15V to V CC as the controller completes the start-up sequence.The externally applied V CC voltage will cause the internal regulator to shut off.The under-voltage sensor circuit will still function in this mode,requiring that the external V CC capacitor be sized so that V CC never falls below 6.8V.The required current into the V CC pin from the external source is shown in Typical Perfor-mance Characteristics (I CC vs.V CC ).If a fault condition occurs such that the external supply to V CC fails,external current draw from the V CC pin must be limited as to not exceed the regulator’s current limit,or the maximum power dissipation of the IC.An external start-up or other bias rail can be used instead of the internal start-up regulator by connecting the V CC and the V IN pins together and feeding the external bias voltage (10-15V)into that node.A thermal shutdown protection will activate if the die tem-perature exceeds 165o C,disabling the outputs (OUT1and OUT2),and shutting down the V CC regulator.When the die temperature has reduced below 150˚C (typical hysteresis =15˚C)the V CC regulator is enabled and a softstart sequence will initiate.Reference (Pin 2)The Ref pin provides a reference voltage of 2.5V,±2.4%.The pin is internally connected to an NMOS FET drain at the buffer amplifier’s output,allowing it to sink,but not source current.An external pullup resistor is required.Current into the pin must be limited to less than 20mA to maintain regulation.See the graph in the Typical Performance Char-acteristics.During start-up if the pullup voltage is present before the reference amplifier establishes regulation,the voltage on pin 2must not exceed 5.5V.If this reference is not used the Ref pin can float or be connected to ground.PWM Comparator (Pin 3),Duty Cycle and DeadtimeThe PWM comparator compares an internal ramp signal (0-0.65V)with the loop error voltage derived from the Comp pin (pin 3).The Comp voltage is typically set by an external error amplifier through an optocoupler for closed loop applica-tions.Internally,the voltage at the Comp pin passes through two level shifting diodes,and a gain reducing 3:1resistor divider.The output of the PWM comparator provides the pulse width information to the output drivers (Out1and Out2).This comparator is optimized for speed in order to achieve minimum discernable duty cycles.The output duty cycle is 0%for V COMP <1.5V,and maximum for V COMP >3.5V.See the Typical Performance Characteristics.The maximum duty cycle for each output is limited to less than 50%due to the forced deadtime.The typical deadtime be-tween the falling edge of one gate driver output and the rising edge of the other gate driver output is 135ns,and does not vary with frequency.The maximum duty cycle for each output can be calculated from:where T S is the period of each output,and T D is the dead-time.For example,if the oscillator frequency is 200kHz,each output will cycle at 100kHz,and T S =10µing the nominal deadtime of 135ns,the maximum duty cycle at this frequency is 48.65%.Using the minimum deadtime of 85ns,the maximum duty cycle increases to 49.15%.When the Softstart pin (pin 10)is pulled down (internally or externally)the Comp pin voltage is pulled down with it,with a difference of 0.5V.When the Softstart pin voltage in-creases the Comp voltage is allowed to increase,pulled up by an internal 5.2V supply through a 5k Ωresistor.In an open loop application,such as an intermediate bus converter,pin 3can be left open resulting in maximum duty cycle at the output drivers .Current Sense (Pin 8)The current sense circuit is intended to protect the power converter when an abnormal primary current is sensed by initiating a low duty cycle hiccup mode.When the threshold (0.5V)at Pin 8is exceeded the outputs are disabled,and the softstart capacitor (at pin 10)is internally discharged.When the softstart capacitor is fully discharged and the voltage at the CS pin is below 0.5V,the outputs are re-enabled allowing the softstart capacitor voltage and the output duty cycle to increase.L M 5033 8Current Sense (Pin 8)(Continued)The external current sensing circuit should include an RC filter located near the IC to prevent false triggering of the Current Sense comparator due to transients or noise.An internal MOSFET discharges the external filter capacitor at the conclusion of each PWM cycle to improve dynamic performance.The discharge time is equal to the deadtime between Out1and Out2at maximum duty cycle.Additionally,pin 8is pulled low when V CC is below the under-voltage threshold or when an over temperature condition occurs.Oscillator,Sync Capability (Pin 9)The LM5033oscillator frequency is set by a single external resistor connected between Rt/Sync and ground.The re-quired Rt resistor is calculated from:The outputs (Out1and Out2)alternate at half the oscillator frequency.The voltage at the Rt/Sync pin is internally regu-lated to a nominal 2.0V.The Rt resistor should be located as close as possible to the IC,and connected directly to the pins (Rt and GND).The LM5033can be synchronized to an external clock by applying a narrow pulse to pin 9.The external clock must be a higher frequency than the free running frequency set by the Rt resistor,and the pulse width must be between 15and 150ns.The clock signal must be coupled into the Rt/Sync pin through a 100pF capacitor.When the synchronizing pulse transitions low-to-high,the voltage at pin 9must ex-ceed 3.8V from its nominal 2.0V dc level.During the clock signal’s low time the voltage at pin 9will be clamped at 2.0V by an internal regulator.The Rt resistor is always required,whether the oscillator is free running or externally synchro-nized.Soft Start (Pin 10)The softstart feature allows the converter to gradually reach a steady state operating point,thereby reducing start-up stresses and current surges.Upon turn-on,after the under-voltage sensor resets at V CC ,an internal 10µA current source charges an external capacitor at pin 10to generate a ramping voltage (0to +5V)which allows the voltage on the Comp pin (pin 3)to increase gradually.As the COMP voltage increases the output duty cycle will increase from zero to the value required for regulation.Internally,the softstart pin is pulled low when a current fault is detected at pin 8,the V CC voltage is below the lower threshold of the under-voltage sensor,or when a thermal shutdown occurs.Additionally,the softstart pin can be pulled low by an external device.In the event of a current fault,(see Current Sense section)the softstart capacitor will be discharged by an internal pull-down device.The falling voltage at pin 10will pull down the COMP pin,thereby ensuring a minimum output duty cycle when the outputs are re-enabled.The softstart capacitor will then begin to ramp up,allowing the COMP voltage to in-crease.As the COMP voltage increases,the output duty cycle increases from zero to the value required for regula-tion.However,if the fault condition is still present the above sequence repeats until the fault is removed.If the V CC voltage falls below the lower under-voltage sensor threshold (typically 6.8V)the outputs are disabled,and thesoftstart capacitor is discharged.The falling voltage at pin 10will pull down the COMP pin,thereby ensuring minimum output duty cycle when the outputs are re-enabled.After the V CC voltage increases above the upper threshold (typically 9.5V),the outputs are enabled,and the softstart capacitor will begin to ramp up,allowing the COMP pin voltage to increase.The output duty cycle will then increase from zero to the value required for regulation.In the event of a fault which results in an excessively high die temperature,an internal Thermal Shutdown circuit is pro-vided to protect the IC.When activated (at 165˚C)the IC is forced into a low power reset state,disabling the output drivers and the V CC regulator.When the die temperature has reduced (typical hysteresis =15˚C),the V CC regulator is enabled and a softstart sequence will initiate.Using an externally controlled switch,the outputs (Pins 5&6)can be disabled at any time by pulling pin 10below 0.5V.This will pull down the COMP pin to near ground,causing the output duty cycle to go to zero.Upon releasing pin 10,the softstart capacitor will ramp up,allowing the COMP pin voltage to increase.The output duty cycle then increases from zero to the value required for regulation.OUT1,OUT2(Pins 5,6)The LM5033provides two alternating outputs,OUT1and OUT2,each capable of sourcing and sinking 1.5A peak.Each will toggle at one-half the internal oscillator frequency.The voltage output levels are nominally ground and V CC ,minus a saturation voltage at each level which depends on the current flow.The outputs can drive power MOSFETs directly in a push-pull application,or they can drive a high voltage gate driver (e.g.,LM5100)in a bridge application.The outputs are disabled when any of the following condi-tions occur:1.An overcurrent condition is detected at pin 8,2.The V CC under-voltage sensor is active,3.An over-temperature condition is detected,or4.The voltage at Pin 10is below 0.5VThermal ProtectionThe system design should limit the LM5033junction tem-perature to not exceed 125˚C during normal operation.How-ever,in the event of a fault which results in a higher die temperature,an internal Thermal Shutdown circuit is pro-vided to protect the IC.When thermal shutdown is activated,typically at 165˚C,the IC is forced into a low power reset state disabling the output drivers and the V CC regulator.This feature helps prevent catastrophic failures from accidental device overheating.When the die temperature has reduced (typical hysteresis =15˚C)the V CC regulator is enabled and a softstart sequence initiates.Application InformationThe following information is intended to provide guidelines for implementing the LM5033.However,final selection of all external components is dependent on the configuration and operating characteristics of the complete power conversion system.LM50339Application Information(Continued)V IN (PIN 1)The voltage applied at pin 1,normally the same as that applied to the main transformer’s primary,can be in the range of 15to 90V,with transient capability to 100V.The current into pin 1depends not only on V IN ,but also on the load on the output driver pins,any load on V CC ,and whether or not an external voltage is applied to V CC .If Vin is close to the absolute maximum rating of the LM5033,it is recom-mended the circuit of Figure 2be used to filter transients which may occur at the input supply.If V CC is not powered externally,requiring all internal bias currents for the LM5033,and output driver currents,to be supplied at Vin and through the internal regulator,the re-quired input current (Iin)is shown in the Typical Performance Characteristics (I IN vs.V IN ).If V CC is powered externally,Iin will increase with V IN as shown in the above mentioned graph until the external volt-age is applied to V CC .In most applications,this occurs once the outputs are enabled and load current begins to flow.The current into Vin will then drop to a nominal 150µA (Pin 10=open or grounded).V CC (PIN 4)The capacitor at the V CC pin provides not only noise filtering and stability,but also a necessary time delay during start-up.The time delay allows the internal circuitry of the LM5033,and associated external circuitry,to stabilize before V CC reaches its final value,at which time the outputs are enabled and the softstart sequence begins.Any external circuitry connected to the REF output (Pin 2)and Softstart (Pin 10)should be designed to stabilize during the time delay.The current limit of the V CC regulator,and the external capacitor,determine the V CC turn-on time delay.Typically,a 1µF capacitor will provide approximately 300µs of delay,with larger capacitors providing proportionately longer de-lays.Experimentation with the final design may be neces-sary to determine the minimum value for the V CC capacitor.SOFTSTART (PIN 10)The capacitor at pin 10determines the time required for the output duty cycle to increase from zero to the final value for regulation.The minimum acceptable time is dependent on the response of the feedback loops to the COMP pin,as well as the characteristics of the magnetic components.If the Softstart time is too quick,the system output could signifi-cantly overshoot its intended voltage before the loop has a chance to establish regulation,possibly adversely affecting the load.Experimentation with the final design is usually necessary to determine the minimum value for the SS ca-pacitor.CURRENT SENSE (PIN 8)This pin typically receives an input representative of the primary current from the current sense elements of the ex-ternal circuitry.The peak amplitude at this pin must be less than 0.5V for normal operation.Filtering at this pin should be sufficient to prevent false triggering of the Current Sense comparator,but not significantly delay detection of an over-current condition.The filter’s capacitor at pin 8should not be larger than 2200pF.OSCILLATOR,SYNC INPUT (PIN 9)The internal oscillator frequency is generally selected in conjunction with the system magnetic components,and any other aspects of the system which may be affected by the frequency.The R t resistor at pin 9sets the frequency accord-ing to the formula in the Functional Description.Each output (OUT1and OUT2)switches at half the oscillator frequency.If the required frequency value is critical in a particular appli-cation,the tolerance of the external resistor,and the fre-quency tolerance indicated in the Electrical Characteristics,must be taken into account when selecting the resistor.If the LM5033is to be synchronized to an external clock,that signal must be coupled into pin 9through a 100pF capacitor.The R t resistor is still required in this case,and it must be selected to set the internal oscillator to a frequency lower than the external synchronizing frequency.The amplitude of the external pulses must take pin 9above 3.8V on the low-to-high transition but no higher than 5.5V.The clock pulse width should be between 15and 150ns.DEADTIME ADJUSTMENTIf the application requires a change in the minimum dead-time between the outputs,the circuits in Figure 3are recom-mended.Suggested values for the resistor and capacitor at each output are 500Ω,and 100pF,respectively for a nomi-nal 50ns change.The diodes can be 1N4148,or similar.20035415FIGURE 2.Input Transient ProtectionL M 5033 10Application Information(Continued)PC BOARD LAYOUTThe LM5033current sense and PWM comparators are very fast,and as such will respond to short duration noise pulses. Layout considerations are critical for the current sense filter. The components at pins3,8,9,and10should be as physically close as possible to the IC,thereby minimizing noise pickup in the PC tracks.If a current sense transformer is used both leads of the transformer secondary should be routed to the sense filter components,and to the IC pins.The ground side of the transformer should be connected via a dedicated PC board track to pin7of the IC rather than through the ground plane. If the current sense circuit employs a sense resistor in the drive transistor sources,a low inductance resistor should be used.In this case all the noise sensitive low power grounds should be connected in common near the IC,and then a single connection made to the power ground(sense resistor ground point).The outputs of the LM5033,or of the high voltage gate driver (if used),should have short direct paths to the power MOS-FETs in order to minimize the effects of inductance in the PC board traces.If the internal dissipation of the LM5033and any of the power devices produces high junction temperatures during normal operation,good use of the PC board’s ground plane can help considerably to dissipate heat.The exposed pad on the bottom of the LLP-10package can be soldered to ground plane on the PC board,and the ground plane should extend out from beneath the IC to help dissipate the heat.The exposed pad is internally connected to the IC substrate.Additionally,the use of wide PC board traces where possible can help conduct heat away from the IC.Judicious position-ing of the PC board within the end product,along with use of any available air flow(forced or natural convection)can help reduce the junction temperatures.APPLICATION CIRCUIT EXAMPLEFigure6shows an example circuit for a half-bridge200W DC/DC converter built in a quarter brick format.The circuit is that of an intermediate bus converter(IBC)which operates open-loop(unregulated output),converting a nominal48V input to a nominal9.0V output with a30mΩoutput imped-ance.The current sense transformer(T2),and the associ-ated filter at the CS pin,provide overcurrent detection at approximately23A.The auxiliary winding on T1powers V CC and the LM5100’s V+pin(once the outputs are enabled)to reduce power dissipation within the LM5033.The LM5100 provides appropriate level shifting for Q1.Synchronous rec-tifiers Q3and Q4minimize conduction losses in the output stage.Dual comparators U2and U3provide under-voltage and over-voltage sensing at Vin.The under-voltage sense levels are37V increasing,and33V decreasing.The over-voltage sense levels are63V increasing,and61.5V decreas-ing.The circuit can be shut down by taking the ON/OFF input below0.8V.An external synchronizing frequency can be applied to the SYNC input.Measured efficiency and output characteristics for this circuit are shown in Figure4and Figure5.20035416FIGURE3.Deadtime AdjustmentLM5033 11。

LM323K中文资料

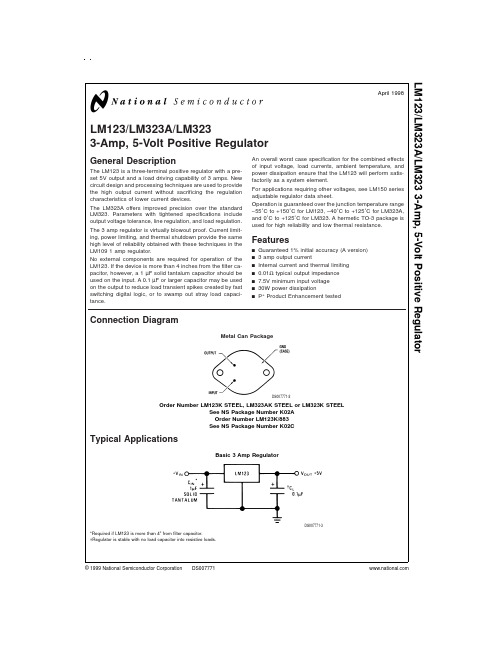

LM123/LM323A/LM3233-Amp,5-Volt Positive RegulatorGeneral DescriptionThe LM123is a three-terminal positive regulator with a pre-set 5V output and a load driving capability of 3amps.New circuit design and processing techniques are used to provide the high output current without sacrificing the regulation characteristics of lower current devices.The LM323A offers improved precision over the standard LM323.Parameters with tightened specifications include output voltage tolerance,line regulation,and load regulation.The 3amp regulator is virtually blowout proof.Current limit-ing,power limiting,and thermal shutdown provide the same high level of reliability obtained with these techniques in the LM1091amp regulator.No external components are required for operation of the LM123.If the device is more than 4inches from the filter ca-pacitor,however,a 1µF solid tantalum capacitor should be used on the input.A 0.1µF or larger capacitor may be used on the output to reduce load transient spikes created by fast switching digital logic,or to swamp out stray load capaci-tance.An overall worst case specification for the combined effects of input voltage,load currents,ambient temperature,and power dissipation ensure that the LM123will perform satis-factorily as a system element.For applications requiring other voltages,see LM150series adjustable regulator data sheet.Operation is guaranteed over the junction temperature range −55˚C to +150˚C for LM123,−40˚C to +125˚C for LM323A,and 0˚C to +125˚C for LM323.A hermetic TO-3package is used for high reliability and low thermal resistance.Featuresn Guaranteed 1%initial accuracy (A version)n 3amp output currentn Internal current and thermal limiting n 0.01Ωtypical output impedance n 7.5V minimum input voltage n 30W power dissipationnP +Product Enhancement testedConnection DiagramTypical ApplicationsMetal Can PackageDS007771-2Order Number LM123K STEEL,LM323AK STEEL or LM323K STEELSee NS Package Number K02A Order Number LM123K/883See NS Package Number K02CBasic 3Amp RegulatorDS007771-3*Required if LM123is more than 4"from filter capacitor.†Regulator is stable with no load capacitor into resistive loads.April 1998LM123/LM323A/LM3233-Amp,5-Volt Positive Regulator©1999National Semiconductor Corporation Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.(Note5)Input Voltage20V Power Dissipation Internally Limited Operating Junction Temperature RangeLM123−55˚C to+150˚C LM323A−40˚C to+125˚C LM3230˚C to+125˚C Storage Temperature Range−65˚C to+150˚C Lead Temperature(Soldering,10sec.)300˚C ESD Tolerance(Note5)2000VLM123Electrical Characteristics(Note2)Parameter Conditions LM123UnitsMin Typ Max Output Voltage T j=25˚C 4.75 5.3VV IN=7.5V,I OUT=0A7.5V≤V IN≤15V 4.6 5.4V0A≤I OUT≤3A,P≤30WLine Regulation(Note4)T j=25˚C525mV7.5V≤V IN≤15VLoad Regulation(Note4)T j=25˚C,V IN=7.5V,25100mV0A≤I OUT≤3AQuiescent Current7.5V≤V IN≤15V,1220mA0A≤I OUT≤3AOutput Noise Voltage T j=25˚C40µVrms10Hz≤f≤100kHzShort Circuit Current Limit T j=25˚CV IN=15V3 4.5AV IN=7.5V45A Long Term Stability35mV Thermal Resistance Junctionto Case(Note3)2˚C/W LM323A/LM323Electrical Characteristics(Note2)Parameter Conditions LM323A LM323UnitsMin Typ Max Min Typ MaxOutput Voltage T j=25˚C 4.955 5.05 4.85 5.2VV IN=7.5V,I OUT=0A7.5V≤V IN≤15V 4.85 5.15 4.75 5.25V0A≤I OUT≤3A,P≤30WLine Regulation(Note4)T j=25˚C510525mV7.5V≤V IN≤15VLoad Regulation(Note4)T j=25˚C,V IN=7.5V,255025100mV0A≤I OUT≤3AQuiescent Current7.5V≤V IN≤15V,12201220mA0A≤I OUT≤3AOutput Noise Voltage T j=25˚C4040µVrms10Hz≤f≤100kHzShort Circuit Current Limit T j=25˚CV IN=15V3 4.53 4.5AV IN=7.5V4645A Long Term Stability3535mV Thermal Resistance Junctionto Case(Note3)22˚C/W 2LM323A/LM323Electrical Characteristics(Note2)(Continued)Note1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note2:Unless otherwise noted,specifications apply for−55˚C≤T j≤+150˚C for the LM123,−40˚C≤T j≤+125˚C for the LM323A,and0˚C≤T j≤+125˚C for the LM323.Although power dissipation is internally limited,specifications apply only for P≤30W.Note3:Without a heat sink,the thermal resistance of the TO-3package is about35˚C/W.With a heat sink,the effective thermal resistance can only approach the specified values of2˚C/W,depending on the efficiency of the heat sink.Note4:Load and line regulation are specified at constant junction temperature.Pulse testing is required with a pulse width≤1ms and a duty cycle≤5%.Note5:Refer to RETS123K drawing for LM123K military specifications.Note6:Human body model,1.5kΩin series with100pF.Typical Performance CharacteristicsMaximum Average Power Dissipation for LM123DS007771-9Maximum Average PowerDissipation for LM323A,LM323DS007771-10Output ImpedanceDS007771-11Peak Available Output CurrentDS007771-12Short Circuit CurrentDS007771-13Ripple RejectionDS007771-14Dropout VoltageDS007771-15Line Transient ResponseDS007771-16Output VoltageDS007771-17 3Typical Performance Characteristics(Continued)Typical ApplicationsQuiescent CurrentDS007771-18Load Transient ResponseDS007771-19Output Noise VoltageDS007771-2010Amp Regulator with Complete Overload ProtectionDS007771-6 *Select for20mA Current from Unregulated Negative Supply4Typical Applications(Continued)Adjustable Regulator0V−10V@3ADS007771-7A1—LM101AC1—2µF Optional—Improves Ripple Rejection,Noise,and Transient ResponseTrimming Output to5VDS007771-8Adjustable Output5V−10V0.1%RegulationDS007771-4*Select to Set Output Voltage**Select to Draw25mA from V−5Schematic DiagramDS007771-1 6Physical Dimensions inches(millimeters)unless otherwise notedMetal Can Package(K)Order Number LM123K STEEL,LM323AK STEEL or LM323K STEELNS Package Number K02A7Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507Metal Can Package (K)Mil-Aero ProductOrder Number LM123K/883NS Package Number K02CL M 123/L M 323A /L M 3233-A m p ,5-V o l t P o s i t i v e R e g u l a t o rNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

LM2661资料