实验二-静态随机存储器-(罗忠霖)

静态随机存储器工作原理

静态随机存储器工作原理

静态随机存储器(Static Random Access Memory,SRAM)是

一种用于计算机内存的存储设备,其工作原理是利用存储电路中的稳定电荷储存信息。

SRAM由一组双稳态触发器构成,每个触发器可以储存一个

二进制位(bit),这些触发器以交叉反馈方式连接,形成稳

定的存储单元。

每个存储单元都有两个稳定的状态,即0和1,分别对应着低电平和高电平的电信号。

SRAM的读写操作是通过控制信号来完成的。

当要读取某个

存储单元的值时,控制电路将相应行线选通,并将其连接到读取电路,读取电路通过放大和判别电路将单元的电平状态转换为相应的输出信号。

当要写入某个存储单元的值时,控制电路将相应行线选通,并将写入数据送入存储单元,存储单元根据输入数据的电平状态来改变其状态。

SRAM相对于动态随机存储器(DRAM)来说,具有读写速

度快、读写可靠性高的特点,但也相应占用较大的面积和功耗较高。

因此,在计算机系统中,SRAM通常用于高速缓存等

需要快速读写的存储器部分。

静态随机存储器实验报告

静态随机存储器实验报告1. 背景静态随机存储器(SRAM)是一种用于存储数据的半导体器件。

与动态随机存储器(DRAM)相比,SRAM速度更快、功耗更低,但成本更高。

SRAM通常用于高速缓存、寄存器文件和数据延迟线等需要快速访问的应用。

本实验旨在通过设计和实现一个简单的SRAM电路来深入了解SRAM的工作原理和性能特点。

2. 设计和分析2.1 SRAM基本结构SRAM由存储单元组成,每个存储单元通常由一个存储电容和一个存储转换器(存储反转MOSFET)组成。

存储电容用于存储数据位,存储转换器用于读取和写入数据。

存储单元按照空间布局进行编址,每个存储单元都有一个唯一的地址。

地址线和控制线用于选择要读取或写入的存储单元。

SRAM还包括写入电路、读取电路和时钟控制电路等。

2.2 SRAM工作原理在SRAM中,数据是以二进制形式存储。

写入操作通过将所需的位值写入存储电容来完成。

读取操作通过将控制信号应用到存储单元和读取电路上来完成。

读取操作的过程如下: 1. 选择要读取的存储单元,将其地址输入到地址线上; 2. 控制信号使存储单元的存储转换器进入放大模式,将存储电容中的电荷放大到可观测的输出电压; 3. 读取电路将放大后的信号恢复到合适的电平,供外部电路使用。

写入操作的过程如下: 1. 选择要写入的存储单元,将其地址输入到地址线上; 2. 控制信号使存储单元的存储转换器进入写入模式; 3. 将数据位的值输入到写入电路; 4. 控制信号触发写入电路将输入的值写入存储电容。

2.3 SRAM性能指标SRAM的性能指标主要包括存储体积、访问速度、功耗和稳定性。

存储体积是指存储单元和控制电路的总体积,通常以平方毫米(㎡)为单位衡量。

访问速度是指读写操作的平均时间。

它受到电路延迟、线材电容和电阻等因素的影响。

功耗是指SRAM在正常操作期间消耗的总功率,通常以毫瓦(mW)为单位衡量。

功耗由静态功耗和动态功耗组成,其中静态功耗是在存储器处于静止状态时消耗的功率,动态功耗是在读取和写入操作期间消耗的功率。

静态随机存储器实验实验报告

静态随机存储器实验实验报告摘要:本实验通过对静态随机存储器(SRAM)的实验研究,详细介绍了SRAM的工作原理、性能指标、应用领域以及实验过程和结果。

实验使用了仿真软件,搭建了SRAM电路,通过对不同读写操作的观察和分析,验证了SRAM的可靠性和高速性。

一、引言静态随机存储器(SRAM)是一种常用的存储器类型,被广泛应用于计算机系统和其他电子设备中。

它具有存储速度快、数据可随机访问、易于控制等优点,适用于高速缓存、寄存器堆以及其他要求高速读写和保持稳定状态的场景。

本实验旨在通过设计和搭建SRAM电路,深入理解SRAM的工作原理和性能指标,并通过实验验证SRAM的可靠性和高速性。

二、实验设备和原理1. 实验设备本实验使用了以下实验设备和工具:- 电脑- 仿真软件- SRAM电路模块2. SRAM原理SRAM是由静态触发器构成的存储器,它的存储单元是由一对交叉耦合的反相放大器构成。

每个存储单元由6个晶体管组成,分别是两个传输门、两个控制门和两个负反馈门。

传输门被用于读写操作,控制门用于对传输门的控制,负反馈门用于保持数据的稳定状态。

SRAM的读操作是通过将存储单元的控制门输入高电平,将读取数据恢复到输出端。

写操作是通过将数据线连接到存储单元的传输门,将写入数据传输到存储单元。

三、实验过程和结果1. 设计电路根据SRAM的原理和电路结构,我们设计了一个8位的SRAM 电路。

电路中包括8个存储单元和相应的读写控制线。

2. 搭建电路通过仿真软件,我们将SRAM电路搭建起来,连接好各个线路和电源。

确保电路连接正确无误。

3. 进行实验使用仿真软件中提供的读写操作指令,分别进行读操作和写操作。

观察每个存储单元的输出情况,并记录数据稳定的时间。

4. 分析实验结果根据实验结果,我们可以得出以下结论:- SRAM的读操作速度较快,可以满足高速读取的需求。

- SRAM的写操作也较快,但需要保证写入数据的稳定性和正确性。

静态随机存取存贮器实验

计算机组成原理实验报告

写数据:

1、传入数据的存储地址:

照连线图连接实验仪

使nWR = 1,nRD = 1,IN单元的nCS=0、nRD=0(即为禁止对存贮器读写),将IN单元中的地址数据输出

MAR单元的nMAROE = 0,允许MAR中锁存的地址数据输出到地址总线上;wMAR = 0,允许写MAR,按CON单元的STEP键一次,依次发出T1、T2、T3信号,在T3的下降沿,IN单元给出的地址数据锁存到MAR中。

2、写数据在存储地址上

禁止对存储器6116的读写(nWR = 1,nRD = 1)、MAR的写(wMAR = 1);

IN单元的拨动开关给出8位数据,IN单元的nCS=0、nRD=0,允许IN单元

输出;

允许对6116写(M_nIO = 1,nRD = 1, nWR = 0),按uSTEP键三次,在T2

的下降沿,数据写入存储器6116中。

3读取数据

通过in单元给出地址,并紧张in单元输出数据

使 M_nIO = 1,nRD = 0, nWR = 1

在T2、T3信号有效时,6116向数据总线输出数据

实验结果

分析。

静态随机存储器实验实验报告

静态随机存储器实验实验报告一、实验目的本次静态随机存储器实验的目的在于深入了解静态随机存储器(SRAM)的工作原理、存储结构和读写操作,通过实际操作和数据观测,掌握 SRAM 的性能特点和应用方法,并培养对数字电路和存储技术的实践能力和问题解决能力。

二、实验原理静态随机存储器(SRAM)是一种随机存取存储器,它使用触发器来存储数据。

每个存储单元由六个晶体管组成,能够保持数据的状态,只要电源不断电,数据就不会丢失。

SRAM 的读写操作是通过地址线选择存储单元,然后通过数据线进行数据的读取或写入。

读操作时,被选中单元的数据通过数据线输出;写操作时,数据通过数据线输入到被选中的单元。

三、实验设备与材料1、数字电路实验箱2、静态随机存储器芯片(如 6116 等)3、示波器4、逻辑分析仪5、导线若干四、实验步骤1、连接实验电路将静态随机存储器芯片插入实验箱的相应插槽。

按照实验原理图,使用导线连接芯片的地址线、数据线、控制线与实验箱上的控制信号源和数据输入输出端口。

2、设置控制信号通过实验箱上的开关或旋钮,设置地址线的输入值,以选择要操作的存储单元。

设置读写控制信号,确定是进行读操作还是写操作。

3、进行写操作当读写控制信号为写时,通过数据输入端口输入要写入的数据。

观察实验箱上的相关指示灯或示波器,确认数据成功写入存储单元。

4、进行读操作将读写控制信号切换为读。

从数据输出端口读取存储单元中的数据,并与之前写入的数据进行对比,验证读取结果的正确性。

5、改变地址,重复读写操作更改地址线的值,选择不同的存储单元进行读写操作。

记录每次读写操作的数据,分析存储单元的地址与数据之间的对应关系。

6、使用逻辑分析仪观测信号将逻辑分析仪连接到实验电路的相关信号线上,如地址线、数据线和控制信号线。

运行逻辑分析仪,捕获读写操作过程中的信号波形,分析信号的时序和逻辑关系。

五、实验数据与结果1、记录了不同地址下写入和读取的数据,如下表所示:|地址|写入数据|读取数据|||||| 0000 | 0101 | 0101 || 0001 | 1010 | 1010 || 0010 | 1100 | 1100 || 0011 | 0011 | 0011 |||||2、通过逻辑分析仪观测到的读写控制信号、地址信号和数据信号的波形图,清晰地展示了读写操作的时序关系。

计算机组成原理 - 实验二存储器实验_

操作步骤

接线图中OO1、OO2、OOE1、OOE2是四个观察记数的 指示灯,其中OO1、OO2是写信号记数,OOE1、OOE2 是读信号记数。FULL及EMPTYy是满和空标志灯。

实验时,先拨动CLR开关使FIFO清空。然后给INPUT DEVICE单元中置一个数,按动START,此时将此数写入 到FIFO中,依次写四次后,FULL满标志置位。此时再也 写不进去,然后连续按动KK2-读信号,将顺序读出所存 的四个数,从总线显示灯检查结果是否与理论值一致。

C3=FIFOWR&O2&!O1; C4=FIFOWR&O2&O1; EMPTY=(OE==O)&!FLAGG; FULL=(OE==O)&FLAGG; END

25

26

3.LS273模块(ls273.abl)

MODULE LS273

"INPUT

CLK

PIN ;

I7,I6,I4,I3,I2,I1,I0 PIN ;

OE.CLK=FIFORD;

O.CLK=!FIFOWR;

24

OE.AR=!RST; O.AR=!RST; FLAGG.CLK=FIFOWR; FLAGG.AR=(!FIFORD)#(!RST); FLAGG:=1; WHEN OE==3 THEN OE:=0 ELSE OE:=OE+1; WHEN O==3 THEN O:=0 ELSE O:=O+1; C1=FIFOWR&!O2&!O1; C2=FIFOWR&!O2&O1;

7

三.实验内容

实验时将T3脉冲接至实验板上时序电路模块的TS3 相应插孔中,其脉冲宽度可调,其它电平控制信号 由“SWITCH UNIT”单元的二进制开关模拟,其中 SW-B为低电平有效,LDAR为高电平有效。

静态随机存储器实验报告

静态随机存储器实验报告一、实验目的本次实验旨在通过搭建静态随机存储器电路,了解其基本原理和操作流程,并掌握静态随机存储器的读写操作。

二、实验原理1. 静态随机存储器(Static Random Access Memory,简称SRAM)是一种使用触发器作为存储单元的半导体存储器。

与动态随机存储器(Dynamic Random Access Memory,简称DRAM)相比,SRAM 具有更快的读写速度和更低的功耗。

2. SRAM通常由若干个存储单元组成,每个存储单元包含一个触发器和一个选择开关。

选择开关用于控制读写操作。

3. 在SRAM中,读操作和写操作都需要先将地址信号送入地址译码器中进行译码,然后将译码结果送入选择开关中。

对于读操作,选择开关将对应地址处的数据输出到数据总线上;对于写操作,则将数据输入到对应地址处。

1. 按照电路图搭建SRAM电路,并连接上电源和示波器。

2. 将地址信号输入到地址译码器中,并将译码结果送入选择开关中。

3. 进行读操作:将读使能信号输入到选择开关中,并观察示波器上的输出波形。

可以看到,对应地址处的数据被输出到了数据总线上。

4. 进行写操作:将写使能信号输入到选择开关中,并将需要写入的数据输入到对应地址处。

再次进行读操作,可以看到读出的数据已经被更新为新写入的数据。

四、实验结果与分析1. 实验中,我们成功搭建了SRAM电路,并进行了读写操作。

2. 通过观察示波器上的波形,可以看到SRAM具有快速响应和稳定性好等特点。

3. 实验结果表明,SRAM在存储器中具有重要作用,在计算机系统中得到广泛应用。

通过本次实验,我们深入了解了SRAM的基本原理和操作流程,并掌握了其读写操作方法。

同时,也加深了对存储器在计算机系统中的重要性认识。

实验二存储器实验

原 ①接通电源,用示波器接入方波信号源的输出插孔H24,调节电位器

理 W1,使H24端输出实验所期望的频率的方波。

实 ②将时序电路模块中的ф和H23排针相连。 验

③在时序电路模块中有两个二进制开关“STOP”和“STEP”,将

“STOP”开关置为“RUN”状态、“STEP”开关置为“EXEC”状

态时,按动微动开关START,则T3输出为连续的方波信号,此时调

节电位器W1,用示波器观察,使TS3端输出实验要求的脉冲信号。

当“STOP”开关置为“RUN”状态、“STEP”开关置为“STEP”

状态时,每按动一次微动开关START,则T3 输出一个单脉冲,其脉

冲宽度与连续方式相同。

④关闭电源。

7

计

算

四、实验步骤

机

组

成 ⑵ 按如下图所示,连接实验线路,仔细查线

理

实

控制信号

写地址

写内容

读内容

验

SW-B

LDAR

CE

WE

14

计

算

机

组 (2)向存储器的00H,01H,02H,03H,04H,05H,06H地址

成

单元分别写入数据

原 理

AAH,55H,33H,44H,66H,08H,F0H(十六进制).

实

验

15

计 算

六、思考题

机

组

成

原 ①存储器在写操作和读操作的过程中

理 实 验

6. 本实验中存储器能够存储的最大容量是多少? PC、AR寄存器的位数是多少?存储器的每个

单元能存放的最大整数和最小整数是多少?

7. 存储器本身是怎样存取数据的?本实验中是 如何控制内存的读和写?

实验二静态随机存贮器实验

实验序号:02实验项目名称:静态随机存贮器实验

学 号

姓 名

专业、班

实验地点

文波332

指导教师

杨光

时间

一、实验目的

掌握静态随机存储器RAM工作特性及数据的读写方法。

二、实验原理

实验所用的半导体静态存储器电路原理如下图 所示,实验中的静态存储器由一片 6116(2K×8)构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。地址 灯 AD0~AD7与地址线相连,显示地址线状况。数据开关经一个三态门(74LS245)连至 数据总线,分时给出地址和数据.

实验时将T3脉冲接至时序电路模块的TS3相应插孔中,其脉冲宽度可调,其他电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B为低电平有效,LDAR为高电平有效。

三、实验内容与步骤

(1)形成时钟脉冲信号T3。具体接线方法和操作步骤如下:

①接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1及W2,使H23端输出实验所期望的频率及占空比的方波。

写存储器流程如下图所示(以向00 号单元写入 11H 为例)。

(4) 读存储器。

依次读出第 00、01、02、03、04 号单元中的内容,观察上述各单元中的内容是否与前面写入的一致。同写操作类似,读每个单元也需要两步,第一步写地址,先关掉存储器的片选(CE=1),打开地址锁存器门控信号(LDAR=1 ),打开数据开关三态门(SW-B=0),由开关给出要写存储单元的地址,按动 START 产生 T3 脉冲将地址输入到地址锁存器;第二步读存储器,关掉地址锁存器门控信号(LDAR=0 ),关掉数据开关三态门(SW-B=1),片选存储器,使它处于读状态(CE=0,WE=0 ),此时数据总线上显示的数据即为从存储器当前地址中读出的数据内容。读其他单元依次循环上述步骤。

数据库原理实验报告-(罗忠霖)-实验三

《数据库原理》实验报告题目:实验二建立数据库及表学号:2010810072 成绩姓名:罗忠霖日期:2012/11/22一、实验使用环境:Window7 、SQL Server 2005二、实验内容与完成情况:1.查询2013年3月10日以前进货且进货价大于500元的商品信息,进货价格按从大到小排序。

程序代码select*fromPurchasewhere(进货时间<'2012-03-10'and进货价>500)order by进货价desc运行结果2.创建一个新表名为:总金额表。

字段包含:商品名称,总金额,返回的结果集行的百分比为程序代码select top 50 percent商品名称,(数量*进货价)as总金额into newtablefrom Purchaseselect*from newtable--查看表信息运行结果3.汇总各部门的员工人数程序代码select部门,count(*)as员工人数from Employeesgroup by部门运行结果4.显示如下结果程序代码select部门,性别,count(*)as员工人数from Employeesgroup by性别,部门运行结果5.显示如下结果程序代码select部门,性别,count(*)as人数from Employeesgroup by部门,性别with cube结果6.分别统计各个员工的销售总数:(使用COMPUTE)程序代码select售货员工编号,商品编号,数量from Sellorder by售货员工编号compute sum(数量)by售货员工编号结果7.查询商品名称,销售编号及销售数量,包括没有销售的商品名称。

程序代码select商品名称,销售编号,Sell.数量from Purchase left join Sellon(Sell.商品编号)=(Purchase.商品编码)运行结果8.使用笛卡尔积连接两张表Purchase和Sell 程序select*代码from Purchase cross join Sell 运行结果9.为新建的表创建唯一性聚集索引:程序代码create table生产厂商表(厂商编号int identity(1,1)not null,厂商名称varchar(30)not null,法人代表varchar(8),厂商地址varchar(50))create unique index weiyi on生产厂商表(厂商编号asc)运行结果10.为Employees表的“姓名”字段创建一个名为“I_姓名”的非聚集索引,使用降序排列,填充因子为:程序代码create index I_姓名on Employees(编号desc)运行结果11.显示Employees表的I_姓名索引的碎片统计信息。

静态存储器-实验报告

静态存储器-实验报告引言静态存储器是计算机中的一种存储器件,广泛应用于微型计算机、工控系统、控制器等领域中。

与动态存储器不同,静态存储器是由一系列逻辑门电路组成的,不需要周期性地进行刷新操作。

本实验主要介绍静态存储器的基本原理以及应用,并通过实验验证静态存储器的功能。

一、实验目的1. 掌握静态存储器的组成原理和基本功能。

2. 熟悉静态存储器的应用场景和使用方法。

3. 通过实验验证静态存储器的功能和性能。

二、实验原理静态存储器是由许多逻辑门组成的,逻辑门分为三种类型:与门、或门、反相器。

其中与门和或门分别用于输入/输出数据的选择和判断,反相器用于数据存储和输出。

将这些逻辑门组合在一起,形成了静态存储器的核心电路结构,如图1所示。

图1 静态存储器电路结构图静态存储器的基本功能是将输入的二进制数据通过逻辑电路存储,以便随时读取。

当CPU需要访问某个存储单元中的数据时,静态存储器将该单元中的数据输出给CPU,完成读取操作。

另外,通过特定的电路设计,静态存储器还可以实现数据的随机访问和写入操作等功能。

三、实验设备2. 电路板3. 电源4. 信号源5. 示波器四、实验步骤1. 将静态存储器模块插入电路板中。

2. 将电路板与电源和信号源连接。

3. 将信号源输出线连接到静态存储器的输入端,将示波器接到静态存储器的输出端。

4. 设置信号源的输出并观察静态存储器的输出波形。

6. 将示波器的观察时间延长,并调整信号源的输出幅度和频率,观察静态存储器在不同输入信号下的工作状态。

五、实验结果分析通过实验可以看出,静态存储器能够很好地记录输入信号的历史,并在需要时将数据输出。

同时,静态存储器对于不同频率和幅度的输入信号均有良好的适应性。

这说明静态存储器具有很好的稳定性和可靠性,并且适用于多种实际应用场景。

六、实验结论通过本次实验,我们成功掌握了静态存储器的组成原理及基本功能,并通过实验验证了其良好的性能和应用效果。

静态存储器作为计算机存储器中的一种重要组成部分,在现代计算机系统中得到广泛使用,在各个领域都有着广泛的应用前景。

静态随机存储器实验报告

静态随机存储器实验报告静态随机存储器实验报告引言:静态随机存储器(Static Random Access Memory, SRAM)是一种常见的存储器类型,广泛应用于计算机系统中。

本实验旨在通过对SRAM的实验研究,深入了解其工作原理、特性以及性能表现。

一、实验目的本实验的目的是通过实践操作,学习SRAM的基本原理和操作方法,掌握其读写操作的过程和时序,并了解SRAM的性能指标。

二、实验器材和方法实验器材:1. SRAM芯片2. 逻辑分析仪3. 示波器4. 示教板实验方法:1. 连接SRAM芯片和逻辑分析仪,建立实验电路。

2. 在示波器上观察SRAM的读写时序,并记录相关数据。

3. 使用示教板进行SRAM的读写操作,观察并记录操作结果。

三、实验结果与分析1. SRAM的读操作通过示波器观察SRAM的读操作时序,可以发现读取数据的过程包括地址输入、读使能信号的激活以及数据输出等步骤。

读操作的时序图显示了这些步骤的顺序和时机。

根据实验数据,我们可以计算出SRAM的读取速度和稳定性。

2. SRAM的写操作写操作是将数据写入SRAM芯片中的过程。

通过示波器观察SRAM的写操作时序,可以发现写操作包括地址输入、写使能信号的激活以及数据输入等步骤。

写操作的时序图显示了这些步骤的顺序和时机。

根据实验数据,我们可以计算出SRAM的写入速度和稳定性。

3. SRAM的性能指标通过对实验数据的分析,我们可以得出SRAM的性能指标,如读写速度、稳定性和可靠性等。

这些指标对于评估SRAM芯片的质量和适用范围非常重要。

四、实验总结通过本次实验,我们深入了解了静态随机存储器的工作原理和操作方法。

通过观察和分析实验数据,我们对SRAM的性能指标有了更清晰的认识。

实验过程中,我们学习了使用逻辑分析仪和示波器等工具,提高了实验操作和数据分析的能力。

通过这次实验,我们不仅对SRAM有了更深入的了解,还培养了实验思维和动手能力。

在今后的学习和研究中,这些能力将对我们的科研工作有着重要的帮助。

储存原理实验报告总结(3篇)

第1篇一、实验背景随着计算机技术的飞速发展,存储器作为计算机系统的重要组成部分,其性能直接影响着计算机系统的整体性能。

为了深入了解存储器的原理及其在实际应用中的表现,我们进行了储存原理实验。

二、实验目的1. 理解存储器的基本概念、分类、组成及工作原理;2. 掌握存储器的读写操作过程;3. 了解不同类型存储器的优缺点;4. 分析存储器性能的影响因素。

三、实验内容1. 静态随机存储器(SRAM)实验(1)实验目的:掌握SRAM的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察SRAM的读写过程,记录读写时序,分析读写速度。

(3)实验结果:SRAM读写速度快,但价格较高,功耗较大。

2. 动态随机存储器(DRAM)实验(1)实验目的:掌握DRAM的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察DRAM的读写过程,记录读写时序,分析读写速度。

(3)实验结果:DRAM读写速度较SRAM慢,但价格低,功耗小。

3. 只读存储器(ROM)实验(1)实验目的:掌握ROM的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察ROM的读写过程,记录读写时序,分析读写速度。

(3)实验结果:ROM只能读,不能写,读写速度较慢。

4. 固态硬盘(SSD)实验(1)实验目的:掌握SSD的读写操作过程,了解其优缺点。

(2)实验内容:通过实验,观察SSD的读写过程,记录读写时序,分析读写速度。

(3)实验结果:SSD读写速度快,功耗低,寿命长。

四、实验分析1. 不同类型存储器的读写速度:SRAM > SSD > DRAM > ROM。

其中,SRAM读写速度最快,但价格高、功耗大;ROM读写速度最慢,但成本较低。

2. 存储器性能的影响因素:存储器容量、读写速度、功耗、成本、可靠性等。

在实际应用中,需要根据具体需求选择合适的存储器。

3. 存储器发展趋势:随着计算机技术的不断发展,存储器性能不断提高,功耗不断降低,成本不断降低。

微机原理答案(集美大学)罗忠霖

的 FFFF0H 单元开始执行指令,使得系统在启动时自动进入系统程序。

题目答案:T

你的答案:T

第2题(1分)

你的得分:1

【2】对存储器进行访问时,地址线有效和数据线有效的时间关系是数据线较先有效。

题目答案:F

你的答案:F

题目分析:

对存储器进行访问时,地址线有效和数据线有效的时间关系是地址线较先有效。

第6题(2分)

你的得分:2

一微机存储器首地址为2000H,若存储器容量为8KB,则存储器的末地址为【7】。

A. 21FFH

B. 23FFH

C. 27FFH

D. 3FFFH

题目答案:D 你的答案:D

第2页

题目分析:

集美大学计算机工程学院 计算 1013 班 罗忠霖

需要13根地址线来区分8K 个存储单元,这些存储单元最低地址为0 0000 0000

第12题(1分)

你的得分:1

构成4KB 的存储系统,需用【13】。

A. 1024×4位的芯片8片

B. 2K×1位的芯片8片

C. 1024×8位的芯片2片

D. 16K×1位的芯片4片

题目答案:A

你的答案:A

题目分析:

A. 1024×4位的芯片8片=4KB

B. 2K×1位的芯片8片=2KB

C. 1024×8位的芯片2片=2KB

(高/低)电平。

2. 当 8086CPU 工作在最小模式下时,如果读 I/O 口,在 T1~T4 期间,数据来自【9】(I/O

口、存储器)。

3. 请问 AD0~AD15 信号由【10】流向【11】。

题目答案:【8】低【9】I/O 口【10】I/O 口【11】CPU

你的答案:【8】低【9】I/O 口【10】I/O 口【11】CPU

主存器原理实验报告

一、实验目的1. 理解主存器的组成和工作原理。

2. 掌握主存器读写操作的基本步骤。

3. 分析主存器性能参数对计算机系统的影响。

二、实验原理主存器(Memory)是计算机系统中用于存储数据和指令的部件,它是计算机运行的基本单元。

主存器分为两种:静态随机存储器(SRAM)和动态随机存储器(DRAM)。

1. 静态随机存储器(SRAM)SRAM由MOS电路构成的双稳触发器保存二进制信息。

其优点是访问速度快,只要不掉电可以永久保存信息。

缺点是集成度低,功耗大,价格高。

2. 动态随机存储器(DRAM)DRAM由MOS电路中的栅极电容保存二进制信息。

其优点是集成度高,功耗约为SRAM的1/6,价格低。

缺点是访问速度慢,电容的放电作用会使信息丢失,要长期保存数据必须定期刷新存储单元。

三、实验内容1. 主存器组成原理分析通过实验,观察主存器的结构,了解其内部组成,包括地址译码器、存储单元、读写控制电路等。

2. 主存器读写操作步骤(1)初始化:将主存器地址译码器、存储单元、读写控制电路等部分连接到实验系统。

(2)写操作:向主存器写入数据,通过地址译码器定位存储单元,控制电路完成写操作。

(3)读操作:从主存器读取数据,通过地址译码器定位存储单元,控制电路完成读操作。

3. 主存器性能参数分析(1)容量:主存器能够存储的数据量,通常以字节为单位。

(2)速度:主存器读写操作所需的时间,通常以纳秒(ns)为单位。

(3)功耗:主存器在运行过程中消耗的电能,通常以瓦特(W)为单位。

四、实验步骤1. 连接实验系统,将主存器各部分连接到实验系统。

2. 初始化主存器,确保各部分正常工作。

3. 编写程序,实现主存器的写操作和读操作。

4. 运行程序,观察主存器读写操作的结果。

5. 分析实验数据,得出结论。

五、实验结果与分析1. 主存器组成原理分析通过实验,观察到主存器由地址译码器、存储单元、读写控制电路等部分组成。

地址译码器负责将地址转换为存储单元的物理位置,存储单元用于存储数据,读写控制电路负责控制读写操作。

操作系统实验报告-罗忠霖--实验一

集美大学计算机工程学院实验报告课程名称:操作系统班级:计算1013指导教师:李传目姓名:罗忠霖实验项目编号:实验一学号:2010810072实验项目名称:进程的创建实验成绩:一、实验目的1、掌握进程的概念,明确进程的含义2、认识并了解并发执行的实质二、实验内容1、编写一段程序,使用系统调用fork( )创建两个子进程。

当此程序运行时,在系统中有一个父进程和两个子进程活动。

让每一个进程在屏幕上显示一个字符:父进程显示'a',子进程分别显示字符'b'和字符'c'。

试观察记录屏幕上的显示结果,并分析原因。

2、修改上述程序,每一个进程循环显示一句话。

子进程显示'daughter …'及'son ……',父进程显示'parent ……',观察结果,分析原因。

三、实验使用环境Red hat linux和visualbox VM四、实验程序及运行结果第一题程序:#include <stdio.h>main( ){int p1,p2;while((p1=fork( ))= = -1); /*创建子进程p1*/if (p1= =0) printf(“child(p1):b\n”);else{while((p2=fork( ))= = -1); /*创建子进程p2*/if(p2= =0) printf(“child(p2):c\n”);else printf(“parent:a\n”);}}运行结果:第二题程序:#include <stdio.h>main( ){int p1,p2,i;while((p1=fork( ))= = -1); /*创建子进程p1*/if (p1= =0)for(i=0;i<5;i++)printf("p1 is daughter %d\n",i);else{while((p2=fork( ))= = -1); /*创建子进程p2*/if(p2= =0)for(i=0;i<5;i++)printf("p2 is son %d\n",i);elsefor(i=0;i<5;i++)printf("then parent %d\n",i);}}运行结果:四、实验小结1.这次的实验主要是熟悉软件的使用,熟悉了对fork()函数的使用。

基本运算器静态随机存储器实验报告

(4)用输入开关向暂存器A置数。

①拨动CON单元的SD27…SD20数据开关,形成二进制数01100101(或其它数值),数据显示亮为‘1’,灭为‘0’。

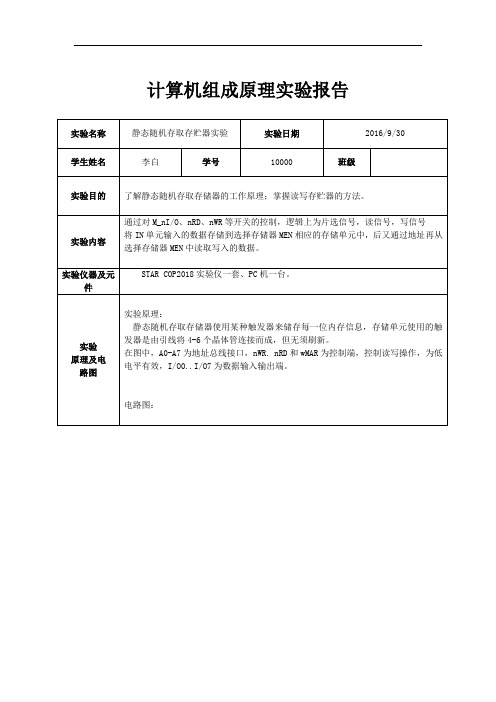

表1-2-1 SRAM 6116功能表

功能

1

0

0

0

X

1

0

0

X

0

1

0

不选择

读

写

写

存储器数据线接至数据总线,数据总线上接有8个LED灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED灯显示A7…A0的内容,

地址由地址锁存器(74LS273,位于PC&AR单元)给出。数据开关(位于IN单元)经一个三

(6)改变运算器的功能设置,观察运算器的输出。置ALU_B=0、LDA=0、LDB=0,然后按表1-1-1置S3、S2、S1、S0和Cn的数值,并观察数据总线LED显示灯显示的结果。如置S3、S2、S1、S0为0010,运算器作逻辑与运算,置S3、S2、S1、S0为1001,运算器作加法运算。如果实验箱和PC联机操作,则可通过软件中的数据通路图来观测实验结果(软件使用说明请看附录一),方法是:打开软件,选择联机软件的“【实验】—【运算器实验】”,打开运算器实验的数据通路图,如图1-1-6所示。进行上面的手动操作,每按动一次TS按钮,数据通路图会有数据的流动,反映当前运算器所做的操作,或在软件中选择“【调试】—【单周期】”,其作用相当于将时序单元的状态开关置为‘单步’档后按动了一次TS按钮,数据通路图也会反映当前运算器所做的操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集美大学计算机工程学院实验报告

课程名称:计算机组成原理指导教师:汪志华实验成绩:实验项目编号: 3.6实验项目名称:静态随机存储器实验

班级:计算1013姓名:何荣贤

罗忠霖学号:2010810071

2010810072

上机实践日期:2012/11/15上机实践时间:2学时

一、实验目的

掌握静态随机存储器RAM工作特性及数据的读/写方法。

二、实验设备

(1)TDN-CM+或TDN-CM++教学实验系统一套;

(2)PC机(或示波器)一台;

三、实验原理

⑴、在此实验中,所用的半导体静态存储器又一片6116(2K×8)构成,其数据线接至

数据总线,地址线又地址锁存器(74LS273)给出。

地址灯AD7-AD0与地址线连,

显示地址线内容。

数据开关经三态门(74LS245)连至数据总线,分时给出地址和

数据。

⑵、6116有三个控制线:CE(片选线)、OE(读线)、WE(写线)。

当片选有效

(CE=0)时,OE=0时进行读操作,WE=0时进行写操作,在本实验中,将OE 常接地,因此6116的引脚信号WE = 1时进行度操作,WE = 0时进行写操作。

⑶、要对存储器进行读(写)操作,必须设置控制端CE=0,WE=0(WE=1),同时有T3

脉冲到来。

⑷、实验时,将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可

调(在本实验中影响不大),其它电平控制信号由“SWITCH UNIT”单元的二进制

开关模拟,其中SW-B(三态门)为低电平有效,LDAR为高电平有效。

四、实验步骤

(1)将时序电路模块中的Φ和H23排针相连。

将时序电路模块中的二进制开关

“STOP”设置为“RUN”状态、将“STEP”设置为"STEP"状态。

注意:关于stop

和step的说明: 将“STOP”开关置为“Run"状态、“STEP”开关置为“EXEC”

状态时,按动微动开关START,则T3输出为连续的方波信号,此时调节电位器

W1,用示波器观察,使T3输出实验要求的脉冲信号。

当“STOP”开关置为

“RUN”状态、“STEP”开关置为"STEP"状态时,每按动一次微动开关START,

则T3输出一个单脉冲,其脉冲宽度与连续方式相同。

(2)按图2连接实验线路,仔细查线无误后接通电源。

(3)

⑴、向存储器指定的地址送入数据,如:向00单元中输入11.步骤如下:

①、向地址寄存器AR中输入地址00的流程如下:

CE=1(存储器无效)

按START发T3脉冲

②、输入要存放的数据11的流程如下:

CE=0 WE=1

发T3脉冲

③、重复1、2操作步骤继续向下面的几个地址中输入下述数据:

⑷、从存储器指定的地址中读出数据,

①.如在00中读出流程如下:

LDAR=1 LDAR=0

发T3脉冲 CE=0

②.同样从其它4个地址: 01 ,02 ,03 , 04中读出数据,观察地址显示灯, 数据显示灯

和数码显示管的变化,并检查是否和输入的数据一致。

五、实验结果

步骤3向存储器指定的地址输入数据结果:

步骤4中,地址显示灯, 数据显示灯和数码显示管的变化,和输入的数据一致。

六、实验小结。