MIC1232中文资料

MIC26603YJL TR,MIC26603YJL TR,MIC26603YJL TR, 规格书,Datasheet 资料

MIC2660328V, 6A Hyper Light Load ™Synchronous DC/DC Buck RegulatorSuperSwitcher IIG ™Hyper Speed Control, Hyper Light Load, SuperSwitcher II, and Any Capacitor are trademarks of Micrel, Inc. MLF and Micro LeadFrame are registered trademarks of Amkor Technology, Inc.General DescriptionThe Micrel MIC26603 is a constant-frequency, synchronous DC/DC buck regulator featuring adaptive on-time control architecture. The MIC26603 operates over a supply range of 4.5V to 28V. It has an internal linear regulator which provides a regulated 5V to power the internal control circuitry. MIC26603 operates at a constant 600kHz switching frequency in continuous-conduction mode and can be used to provide up to 6A of output current. The output voltage is adjustable down to 0.8V.Micrel’s Hyper Light Load ™ architecture provides the samehigh-efficiency and ultra-fast transient response as theHyper Speed Control ™ architecture under medium to heavy loads, but also maintains high efficiency under light load conditions by transitioning to variable-frequency, discontinuous-mode operation. The MIC26603 offers a full suite of protection features to ensure protection of the IC during fault conditions. These include undervoltage lockout to ensure proper operationunder power-sag conditions, thermal shutdown, internalsoft-start to reduce the inrush current, foldback current limit and “hiccup mode” short-circuit protection. TheMIC26603 includes a Power Good (PG) output to allow simple sequencing. All support documentation can be found on Micrel’s web site at: .Features• Hyper Light Load ™ efficiency – up to 80% at 10mA • Hyper Speed Control ™ architecture enables − High Delta V operation (V IN = 28V and V OUT = 0.8V) − Small output capacitance• Input voltage range: 4.5V to 28V • Output current up to 6A • Up to 95% Efficiency• Adjustable output voltage from 0.8V to 5.5V• ±1% FB accuracy• AnyCapacitor TM stable − zero-to-high ESR • 600kHz switching frequency • Power Good (PG) output • Foldback current-limit and “hiccup mode” short-circuit protection• Safe start-up into pre-biased loads • 5mm x 6mm MLF ® package• –40°C to +125°C junction temperature range Applications • Distributed power systems • Telecom/networking infrastructure • Printers, scanners, graphic cards, and video cards___________________________________________________________________________________________________________Typical ApplicationOrdering InformationPart NumberVoltageSwitching FrequencyJunction TemperatureRangePackage Lead FinishMIC26603YJL Adjustable600kHz–40°C to +125°C 28-Pin 5mm × 6mm MLF ®Pb-FreePin Configuration28-Pin 5mm x 6mm MLF ® (YJL)Pin DescriptionPin NumberPin NamePin Function1 PVDD5V Internal Linear Regulator (Output): PVDD supply is the power MOSFET gate drive supply voltage and created by internal LDO from V IN . When V IN < +5.5V, PVDD should be tied to PVIN pins. A 2.2µF ceramic capacitor from the PVDD pin to PGND (pin 2) must be place next to the IC. 3 NC No Connect.4, 9, 10, 11, 12SWSwitch Node (Output): Internal connection for the high-side MOSFET source and low-side MOSFETdrain. Due to the high speed switching on this pin, the SW pin should be routed away from sensitive nodes.2, 5, 6, 7, 8, 21 PGNDPower Ground. PGND is the ground path for the MIC26603 buck converter power stage. The PGND pins connect to the low-side N-Channel internal MOSFET gate drive supply ground, the sources of the MOSFETs, the negative terminals of input capacitors, and the negative terminals of output capacitors. The loop for the power ground should be as small as possible and separate from the Signal ground (SGND) loop.13,14,15, 16,17,18,19PVINHigh-Side N-internal MOSFET Drain Connection (Input): The PV IN operating voltage range is from 4.5V to 26V. Input capacitors between the PVIN pins and the power ground (PGND) are required and keep the connection short.20 BSTBoost (output): Bootstrapped voltage to the high-side N-channel MOSFET driver. A Schottky diode is connected between the PVDD pin and the BST pin. A boost capacitor of 0.1μF is connected betweenthe BST pin and the SW pin. Adding a small resistor at the BST pin can slow down the turn-on time of high-side N-Channel MOSFETs.Pin Description (Continued)Pin NumberPin NamePin Function22 CSCurrent Sense (input): The CS pin senses current by monitoring the voltage across the low-sideMOSFET during the OFF-time. The current sensing is necessary for short circuit protection and zero current cross comparator. In order to sense the current accurately, connect the low-side MOSFET drain to SW using a Kelvin connection. The CS pin is also the high-side MOSFET’s output driver return. 23 SGNDSignal ground. SGND must be connected directly to the ground planes. Do not route the SGND pinto the PGND Pad on the top layer, see PCB layout guidelines for details. 24 FBFeedback (Input): Input to the transconductance amplifier of the control loop. The FB pin is regulated to 0.8V. A resistor divider connecting the feedback to the output is used to adjust the desired output voltage. 25 PGPower Good (Output): Open Drain Output. The PG pin is externally tied with a resistor to VDD. Ahigh output is asserted when V OUT > 92% of nominal. 26 EN Enable (input): A logic level control of the output. The EN pin is CMOS-compatible. Logic high =enable, logic low = shutdown. In the off state, supply current of the device is greatly reduced(typically 5µA). The EN pin should not be left open. 27VINPower Supply Voltage (Input): Requires bypass capacitor to SGND.28 VDD5V Internal Linear Regulator (Output): VDD supply is the supply bus for the IC control circuit. V DD is created by internal LDO from V IN . When V IN < +5.5V, VDD should be tied to PVIN pins. A 1.0µF ceramic capacitor from the VDD pin to SGND pins must be place next to the IC.Absolute Maximum Ratings(1,2)PV IN to PGND................................................−0.3V to +29V V IN to PGND....................................................−0.3V to PV IN PV DD, V DD to PGND.........................................−0.3V to +6V V SW, V CS to PGND..............................−0.3V to (PV IN +0.3V) V BST to V SW........................................................−0.3V to 6V V BST to PGND..................................................−0.3V to 35V V FB, V PG to PGND...............................−0.3V to (V DD + 0.3V) V EN to PGND........................................−0.3V to (V IN +0.3V) PGND to SGND...........................................−0.3V to +0.3V Junction Temperature..............................................+150°C Storage Temperature (T S).........................−65°C to +150°C Lead Temperature (soldering, 10sec)........................260°C Operating Ratings(3)Supply Voltage (PV IN, V IN).................................4.5V to 28V PVDD, VDD Supply Voltage (PV DD, V DD).........4.5V to 5.5V Enable Input (V EN)..................................................0V to V IN Junction Temperature (T J)........................−40°C to +125°C Maximum Power Dissipation......................................Note 4 Package Thermal Resistance(4)5mm x 6mm MLF®-24L (θJA) .............................28°C/WElectrical Characteristics(5)PV IN = V IN = V EN = 12V, V BST – V SW = 5V; T A = 25°C, unless noted. Bold values indicate -40°C ≤ T J ≤ +125°C.Parameter Condition Min.Typ.Max.Units Power Supply InputInput Voltage Range (V IN, PV IN) 4.5 28 VQuiescent Supply Current V FB = 1.5V (non-switching) 450 750 µAShutdown Supply Current V EN = 0V 5 10 µAV DD Supply VoltageV DD Output Voltage V IN = 7V to 28V, I DD = 40mA 4.8 5 5.4 VV DD UVLO Threshold V DD Rising 3.7 4.2 4.5 VV DD UVLO Hysteresis 400 mVDropout Voltage (V IN – V DD) I DD = 25mA 380 600 mVDC/DC ControllerOutput-Voltage Adjust Range (V OUT) 0.85.5 VReference0°C ≤ T J≤ 85°C (±1.0%) 0.792 0.8 0.808−40°C ≤ T J≤ 125°C (±1.5%) 0.788 0.8 0.812V Load Regulation I OUT = 1A to 6A (Continuous Mode) 0.25 % Line Regulation V IN = 4.5V to 28V 0.25 % FB Bias Current V FB = 0.8V 50 500 nA Enable ControlEN Logic Level High 1.8 V EN Logic Level Low 0.6 V EN Bias Current V EN = 12V 6 30 µA OscillatorSwitching Frequency (6)450 600 750 kHz Maximum Duty Cycle (7)V FB = 0V 82 % Minimum Duty Cycle V FB = 1.0V 0 % Minimum Off-Time 300 nsElectrical Characteristics (5) (Continued)PV IN = V IN = V EN = 12V, V BST – V SW = 5V; T A = 25°C, unless noted. Bold values indicate −40°C ≤ T J ≤ +125°C. Parameter Condition Min. Typ. Max. Units Soft-Start Soft-Start time5msShort-Circuit Protection Current-Limit Threshold V FB = 0.8V, TJ = 25°C 7.5 13 17 A Current-Limit Threshold V FB = 0.8V, TJ = 125°C 6.6 13 17 A Short-Circuit Current V FB = 0V 2.7 A Internal FETs Top-MOSFET R DS (ON) I SW = 3A 42 m Ω Bottom-MOSFET R DS (ON) I SW = 3A 12.5 m Ω SW Leakage Current V EN = 0V 60 µA V IN Leakage Current V EN = 0V 25 µA Power GoodPower Good Threshold Voltage Sweep V FB from Low to High 85 92 95 %V OUT Power Good Hysteresis Sweep V FB from High to Low 5.5 %V OUT Power Good Delay Time Sweep V FB from Low to High 100 µs Power Good Low Voltage Sweep V FB < 0.9 × V NOM , I PG = 1mA 70 200 mV Thermal Protection Over-Temperature Shutdown T J Rising 160 °C Over-Temperature Shutdown Hysteresis15°CNotes:1. Exceeding the absolute maximum rating may damage the device.2. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k Ω in series with 100pF.3. The device is not guaranteed to function outside operating range.4. PD (MAX) = (T J(MAX) – T A )/ θJA , where θJA depends upon the printed circuit layout. A 5 square inch 4 layer, 0.62”, FR-4 PCB with 2oz finish copper weightper layer is used for the θJA . 5. Specification for packaged product only. 6. Measured in test mode.7. The maximum duty-cycle is limited by the fixed mandatory off-time t OFF of typically 300ns.Typical CharacteristicsDie Temperature* : The temperature measurement was taken at the hottest point on the MIC26603 case mounted on a 5 square inch 4 layer, 0.62”, FR-4 PCB with 2oz finish copper weight per layer; see Thermal Measurement section. Actual results will depend upon the size of the PCB, ambient temperature and proximity to other heat emitting components.Functional CharacteristicsFunctional DiagramFigure 1. MIC26603 Block DiagramFunctional DescriptionThe MIC26603 is an adaptive, ON-time, synchronous step-down, DC/DC regulator with an internal 5V linear regulator and a Power Good (PG) output. It is designed to operate over a wide input voltage range from 4.5V to 28V and provides a regulated output voltage at up to 7A of output current. An adaptive ON-time control scheme is employed in to obtain a constant switching frequency and to simplify the control compensation. Over-current protection is implemented without the use of an external sense resistor. The device includes an internal soft-start function which reduces the power supply input surge current at start-up by controlling the output voltage rise time.Theory of OperationThe MIC26603 is able to operate in either continuous mode or discontinuous mode. The operating mode isdetermined by the output of the Zero Cross comparator(ZC) as shown in Figure 1.Continuous ModeIn continuous mode, the output voltage is sensed by theMIC26603 feedback pin FB via the voltage divider R1and R2, and compared to a 0.8V reference voltage V REF at the error comparator through a low gaintransconductance (g m ) amplifier. If the feedback voltagedecreases and the output of the g m amplifier is below0.8V, then the error comparator will trigger the controllogic and generate an ON-time period. The ON-timeperiod length is predetermined by the “FIXED t ONESTIMATION” circuitry:600kHz ×V V =t IN OUTed)ON(estimat Eq. 1where V OUT is the output voltage and V IN is the power stage input voltage. At the end of the ON-time period, the internal high-side driver turns off the high-side MOSFET and the low-sidedriver turns on the low-side MOSFET. The OFF-timeperiod length depends upon the feedback voltage inmost cases. When the feedback voltage decreases and the output of the g m amplifier is below 0.8V, the ON-time period is triggered and the OFF-time period ends. If the OFF-time period determined by the feedback voltage is less than the minimum OFF-time t OFF(min), which is about 300ns, the MIC26603 control logic will apply the t OFF(min) instead. t OFF(min) is required to maintain enough energy in the boost capacitor (C BST ) to drive the high-side MOSFET.The maximum duty cycle is obtained from the 300ns t OFF(min):SSOFF(min)S max t 300ns1t t t D --==Eq. 2where t S = 1/600kHz = 1.66μs.It is not recommended to use MIC26603 with a OFF-time close to t OFF(min) during steady-state operation. Also, as V OUT increases, the internal ripple injection will increase and reduce the line regulation performance. Therefore, the maximum output voltage of the MIC26603 should be limited to 5.5V and the maximum external ripple injection should be limited to 200mV.Please refer to “SettingOutput Voltage” subsection in Application Information formore details. The actual ON-time and resulting switching frequencywill vary with the part-to-part variation in the rise and falltimes of the internal MOSFETs, the output load current, and variations in the V DD voltage. Also, the minimum t ON results in a lower switching frequency in high V IN to V OUTapplications, such as 24V to 1.0V. The minimum t ONmeasured on the MIC26603 evaluation board is about100ns. During load transients, the switching frequency is changed due to the varying OFF-time.To illustrate the control loop operation, we will analyze both the steady-state and load transient scenarios. Figure 2 shows the MIC26603 control loop timing during steady-state operation. During steady-state, the g m amplifier senses the feedback voltage ripple, which is proportional to the output voltage ripple and the inductor current ripple, to trigger the ON-time period. The ON-time is predetermined by the t ON estimator. The termination of the OFF-time is controlled by the feedbackvoltage. At the valley of the feedback voltage ripple, which occurs when V FB falls below V REF , the OFF periodends and the next ON-time period is triggered through the control logic circuitry.Figure 2. MIC26603 Control Loop TimingFigure 3 shows the operation of the MIC26603 during a load transient. The output voltage drops due to the sudden load increase, which causes the V FB to be less than V REF. This will cause the error comparator to trigger an ON-time period. At the end of the ON-time period, a minimum OFF-time t OFF(min) is generated to charge C BST since the feedback voltage is still below V REF. Then, the next ON-time period is triggered due to the low feedback voltage. Therefore, the switching frequency changes during the load transient, but returns to the nominal fixed frequency once the output has stabilized at the new load current level. With the varying duty cycle and switching frequency, the output recovery time is fast and the output voltage deviation is small in MIC26603 converter.Figure 3. MIC26603 Load Transient Response Unlike true current-mode control, the MIC26603 uses the output voltage ripple to trigger an ON-time period. The output voltage ripple is proportional to the inductor current ripple if the ESR of the output capacitor is large enough. The MIC26603 control loop has the advantage of eliminating the need for slope compensation.In order to meet the stability requirements, the MIC26603 feedback voltage ripple should be in phase with the inductor current ripple and large enough to be sensed by the g m amplifier and the error comparator. The recommended feedback voltage ripple is 20mV~100mV. If a low-ESR output capacitor is selected, then the feedback voltage ripple may be too small to be sensed by the g m amplifier and the error comparator. Also, the output voltage ripple and the feedback voltage ripple are not necessarily in phase with the inductor current ripple if the ESR of the output capacitor is very low. In these cases, ripple injection is required to ensure proper operation. Please refer to “Ripple Injection” subsection in Application Information for more details about the ripple injection technique.Discontinuous ModeIn continuous mode, the inductor current is always greater than zero; however, at light loads the MIC26603 is able to force the inductor current to operate in discontinuous mode. Discontinuous mode is where the inductor current falls to zero, as indicated by trace (I L) shown in Figure 4. During this period, the efficiency is optimized by shutting down all the non-essential circuits and minimizing the supply current. The MIC26603 wakes up and turns on the high-side MOSFET when the feedback voltage V FB drops below 0.8V.The MIC26603 has a zero crossing comparator that monitors the inductor current by sensing the voltage drop across the low-side MOSFET during its ON-time. If the V FB > 0.8V and the inductor current goes slightly negative, then the MIC26603 automatically powers down most of the IC circuitry and goes into a low-power mode. Once the MIC26603 goes into discontinuous mode, both LSD and HSD are low, which turns off the high-side and low-side MOSFETs. The load current is supplied by the output capacitors and V OUT drops. If the drop of V OUT causes V FB to go below V REF, then all the circuits will wake up into normal continuous mode. First, the bias currents of most circuits reduced during the discontinuous mode are restored, then a t ON pulse is triggered before the drivers are turned on to avoid any possible glitches. Finally, the high-side driver is turned on. Figure 4 shows the control loop timing in discontinuous mode.Figure 4. MIC26603 Control Loop Timing(Discontinuous Mode)During discontinuous mode, the zero crossing comparator and the current-limit comparator are turned off. The bias current of most circuits are reduced. As a result, the total power supply current during discontinuous mode is only about 450μA, allowing the MIC26603 to achieve high efficiency in light load applications.V DD RegulatorThe MIC26603 provides a 5V regulated output for input voltage V IN ranging from 5.5V to 28V. When V IN < 5.5V, V DD should be tied to PVIN pins to bypass the internal linear regulator.Soft-StartSoft-start reduces the power supply input surge current at startup by controlling the output voltage rise time. The input surge appears while the output capacitor is charged up. A slower output rise time will draw a lower input surge current.The MIC26603 implements an internal digital soft-start by making the 0.8V reference voltage V REF ramp from 0 to 100% in about 5ms with 9.7mV steps. Therefore, the output voltage is controlled to increase slowly by a stair-case V FB ramp. Once the soft-start cycle ends, the related circuitry is disabled to reduce current consumption. V DD must be powered up at the same time or after V IN to make the soft-start function correctly. Current LimitThe MIC26603 uses the R DS(ON) of the internal low-side power MOSFET to sense over-current conditions. This method will avoid adding cost, board space and power losses taken by a discrete current sense resistor. The low-side MOSFET is used because it displays much lower parasitic oscillations during switching than the high-side MOSFET.In each switching cycle of the MIC26603 converter, the inductor current is sensed by monitoring the low-side MOSFET in the OFF period. If the inductor current is greater than 13A, then the MIC26603 turns off the high-side MOSFET and a soft-start sequence is triggered. This mode of operation is called “hiccup mode” and its purpose is to protect the downstream load in case of a hard short. The load current-limit threshold has a fold back characteristic related to the feedback voltage as shown in Figure 5.Figure 5. MIC26603 Current LimitFoldback CharacteristicPower Good (PG)The Power Good (PG) pin is an open drain output which indicates logic high when the output is nominally 92% of its steady state voltage. A pull-up resistor of more than 10kΩ should be connected from PG to VDD.MOSFET Gate DriveThe Block Diagram (Figure 1) shows a bootstrap circuit, consisting of D1 (a Schottky diode is recommended) and C BST. This circuit supplies energy to the high-side drive circuit. Capacitor C BST is charged, while the low-side MOSFET is on, and the voltage on the SW pin is approximately 0V. When the high-side MOSFET driver is turned on, energy from C BST is used to turn the MOSFET on. As the high-side MOSFET turns on, the voltage on the SW pin increases to approximately V IN. Diode D1 is reverse biased and C BST floats high while continuing to keep the high-side MOSFET on. The bias current of the high-side driver is less than 10mA so a 0.1μF to 1μF is sufficient to hold the gate voltage with minimal droop for the power stroke (high-side switching) cycle, i.e. ΔBST = 10mA × 1.67μs/0.1μF = 167mV. When the low-side MOSFET is turned back on, C BST is recharged through D1. A small resistor R G, which is in series with C BST, can be used to slow down the turn-on time of the high-side N-channel MOSFET.The drive voltage is derived from the V DD supply voltage. The nominal low-side gate drive voltage is V DD and the nominal high-side gate drive voltage is approximately V DD – V DIODE, where V DIODE is the voltage drop across D1. An approximate 30ns delay between the high-side and low-side driver transitions is used to prevent current from simultaneously flowing unimpeded through both MOSFETs.Application InformationInductor SelectionValues for inductance, peak, and RMS currents are required to select the output inductor. The input and output voltages and the inductance value determine the peak-to-peak inductor ripple current. Generally, higher inductance values are used with higher input voltages. Larger peak-to-peak ripple currents will increase the power dissipation in the inductor and MOSFETs. Larger output ripple currents will also require more output capacitance to smooth out the larger ripple current. Smaller peak-to-peak ripple currents require a larger inductance value and therefore a larger and more expensive inductor. A good compromise between size, loss and cost is to set the inductor ripple current to be equal to 20% of the maximum output current. The inductance value is calculated in Equation 3:OUT(max)sw IN(max)OUT IN(max)OUT I 20% f V )V (V V L ×××−×=Eq. 3where:f SW = switching frequency, 600kHz20% = ratio of AC ripple current to DC output current V IN(max) = maximum power stage input voltage The peak-to-peak inductor current ripple is:Lf V )V (V V I sw IN(max)OUT IN(max)OUT L(pp)××−×=Δ Eq. 4The peak inductor current is equal to the average output current plus one half of the peak-to-peak inductor current ripple.I L(pk) =I OUT(max) + 0.5 × ΔI L(pp) Eq. 5The RMS inductor current is used to calculate the I 2R losses in the inductor.12ΔI I I 2L(PP)2OUT(max)L(RMS)+= Eq. 6Maximizing efficiency requires the proper selection of core material and minimizing the winding resistance. The high-frequency operation of the MIC26603 requires the use of ferrite materials for all but the most cost sensitive applications. Lower cost iron powder cores may be used but the increase in core loss will reduce the efficiency of the power supply. This is especially noticeable at low output power. The winding resistance decreases efficiency at the higher output current levels. The winding resistance must be minimized although this usually comes at the expense of a larger inductor. The power dissipated in the inductor is equal to the sum of the core and copper losses. At higher output loads, the core losses are usually insignificant and can be ignored. At lower output currents, the core losses can be a significant contributor. Core loss information is usually available from the magnetics vendor. Copper loss in the inductor is calculated by Equation 7:P INDUCTOR(Cu) = I L(RMS)2 × R WINDING Eq. 7The resistance of the copper wire, R WINDING , increases with the temperature. The value of the winding resistance used should be at the operating temperature.P WINDING(Ht) = R WINDING(20°C) × (1 + 0.0042 × (T H – T 20°C ))Eq. 8where:T H = temperature of wire under full load T 20°C = ambient temperatureR WINDING(20°C) = room temperature winding resistance (usually specified by the manufacturer)Output Capacitor SelectionThe type of the output capacitor is usually determined by its equivalent series resistance (ESR). Voltage and RMS current capability are two other important factors for selecting the output capacitor. Recommended capacitor types are tantalum, low-ESR aluminum electrolytic, OS-CON and POSCAP. The output capacitor’s ESR is usually the main cause of the output ripple. The output capacitor ESR also affects the control loop from a stability point of view.The maximum value of ESR is calculated:L(PP)OUT(pp)C ΔI ΔV ESR OUT ≤Eq. 9where:ΔV OUT(pp) = peak-to-peak output voltage ripple ΔI L(PP) = peak-to-peak inductor current rippleThe total output ripple is a combination of the ESR and output capacitance. The total ripple is calculated in Equation 10:()2C L(PP)2SW OUT L(PP)OUT(pp)OUT ESR ΔI 8f CΔI ΔV ×+⎟⎟⎠⎞⎜⎜⎝⎛××= Eq. 10where:D = duty cycleC OUT = output capacitance value f SW = switching frequencyAs described in the “Theory of Operation” subsection in Functional Description , the MIC26603 requires at least20mV peak-to-peak ripple at the FB pin to make the g mamplifier and the error comparator behave properly. Also, the output voltage ripple should be in phase with theinductor current. Therefore, the output voltage ripplecaused by the output capacitors value should be muchsmaller than the ripple caused by the output capacitor ESR. If low-ESR capacitors, such as ceramic capacitors, are selected as the output capacitors, a ripple injection method should be applied to provide the enoughfeedback voltage ripple. Please refer to the “RippleInjection” subsection for more details. The voltage rating of the capacitor should be twice theoutput voltage for a tantalum and 20% greater foraluminum electrolytic or OS-CON. The output capacitorRMS current is calculated in Equation 11:12ΔI I L(PP)(RMS)C OUT =Eq. 11 The power dissipated in the output capacitor is:OUT OUT OUT C 2(RMS)C )DISS(C ESR I P ×= Eq. 12Input Capacitor SelectionThe input capacitor for the power stage input V IN should be selected for ripple current rating and voltage rating. Tantalum input capacitors may fail when subjected to high inrush currents, caused by turning the input supply on. A tantalum input capacitor’s voltage rating should be at least two times the maximum input voltage to maximize reliability. Aluminum electrolytic, OS-CON, and multilayer polymer film capacitors can handle the higher inrush currents without voltage de-rating. The input voltage ripple will primarily depend on the input capacitor’s ESR. The peak input current is equal to the peak inductor current, so:ΔV IN = I L(pk) × ESR CIN Eq. 13The input capacitor must be rated for the input current ripple. The RMS value of input capacitor current is determined at the maximum output current. Assuming the peak-to-peak inductor current ripple is low:D)(1D I I OUT(max)CIN(RMS)−××≈ Eq. 14 The power dissipated in the input capacitor is: P DISS(CIN) = I CIN(RMS)2 × ESR CIN Eq. 15 Ripple Injection The V FB ripple required for proper operation of theMIC26603 g m amplifier and error comparator is 20mV to 100mV. However, the output voltage ripple is generally designed as 1% to 2% of the output voltage. For a low output voltage, such as a 1V, the output voltage ripple is only 10mV to 20mV, and the feedback voltage ripple isless than 20mV. If the feedback voltage ripple is so smallthat the g m amplifier and error comparator can’t sense it,then the MIC26603 will lose control and the output voltage is not regulated. In order to have some amountof V FB ripple, a ripple injection method is applied for lowoutput voltage ripple applications.。

MAX1232

④ 选择看门狗定时器时间必须充分考虑到程序设计中的中断嵌套、多重调用、查询等待、与外部低速器件(如液晶显示屏)接口等影响程序完成一个循环所需时间的各种因素并适当留有余量,否则容易产生意外的看门狗复位。具体时间应由试验决定。在设计初始阶段最稳妥的办法,是在监控芯片的时间选择端设置拨位开关,以便根据实际情况进行选择。

因此,从程序运行产生错误到DSP芯片完成复位,将有共计1.8 s的非受控时间,这对于对实时性要求很高的电力故障录波器来说是不能忍受的。如果在此期间电网发生故障,录波器将无法作出正确的反应。很显然,必须寻找一种具有适合看门狗定时器时间和复位脉冲宽度的硬件监控芯片。

在这里,必须明确对看门狗定时器时间的选择条件。在程序设计中,为了保证硬件监控效果,不宜过多地设置对看门狗芯片的操作,一般应在程序循环的关键部位设置1~2处对看门狗芯片的触发操作。所以,看门狗定时器的时间只要大于一个需时最长的程序循环即可。在基于F206的故障录波器中,需时最长的程序循环包含1个16点的FFT运算,整个程序循环的总时间小于2 ms。

由此看来,硬件监控电路的看门狗时间只要大于2 ms即可满足要求,过长的看门狗时间是不必要的,对保证装置的实时性也是十分不利的。

2 MAX6369~MAX6374监控芯片的原理及应用

根据以上标准,我们选用了MAXIM公司出品的MAX6374监控芯片。MAX6374是MAX6369~ MAX6374系列监控芯片中的一员。该系列芯片的看门狗定时器时间可以通过外部引脚SET2、SET1、SET0的逻辑电平进行精确调节,其引脚电平与看门狗定时器时间的关系如表1所列。

但是,根据我们的设计经验和对系统运行的仔细分析,使用MAX706等类似的许多硬件监控芯片存在2个需要注意的问题:第一,看门狗定时器的时间过长,MAX706的典型时间为1.6 s,也就是说,当DSP中的程序运行产生错误时,MAX706要在 1.6 s(相当于80个工频周期)后才能发出复位信号。第二,监控芯片输出的复位信号脉冲宽度过大,MAX706的典型值为200 ms(相当于10个工频周期),这主要是为了兼顾上电复位时对晶振100~300 ms稳定期的要求。

mic29302中文资料_数据手册_参数

May 2010

M9999-050510-B

电子元器件现货商城上万联芯城,专业一站式报价服务, 万联芯城-以良心做好良芯,专为终端工厂企业客户提供电子元器件一站式 配套报价服务,BOM表整单采购有优惠,只需联系客服提交清单,即可获 得优势报价,为客户节省采购成本,满足客户物料需求,点击进入万联芯城。

MIC29300-5.0WT(2)

MIC29300-5.0BU

MIC29300-5.0WU(2)

MIC29300-12BT

MIC29300-12WT(2)

MIC29300-12BU

MIC29300-12WU(2)

MIC29301-3.3BT

MIC29301-3.3WT(2)

MIC29301-3.3BU

MIC29151-5.0BT

MIC29151-5.0WT(2)

MIC29151-5.0BU

MIC29151-5.0WU(2)

MIC29151-12BT

MIC29151-12WT(2)

MIC29151-12BU

MIC29151-12WU(2)

MIC29152BT

MIC29152WT(2)

MIC29152BU

Junction Temp. Range(1)

–40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C

MEMORY存储芯片MAX1232CSA+T中文规格书

o Hot-Swap Input Structures on DE and RE

o Enhanced Slew-Rate Limiting Facilitates ErrorFree Data Transmission (MAX13080E–MAX13084E/MAX13089E)

UCSP is Taetrleadceommark of Maxim Integrated Products, Inc.

Security Systems

Instrumentation

Profibus

Features

o +5.0V Operation

o Extended ESD Protection for RS-485/RS-422 I/O Pins ±15kV Human Body Model

o Low-Current Shutdown Mode (Except MAX13081E/MAX13084E/MAX13087E)

o Pin-Selectable Full-/Half-Duplex Operation (MAX13089E)

o Phase Controls to Correct for Twisted-Pair Reversal (MAX13089E)

MAX13080ECPD+

0°C to +70°C 14 PDIP

MAX13080ECSD+

0°C to +70°C 14 SO

MAX13080EEPD+ -40°C to +85°C 14 PDIP

DS1232PDF芯片资料

RST

050798 3/7

DS1232/DS1232S

TIMING DIAGRAM: PUSHBUTTON RESET Figure 4

tPB tPDLY VIH VIL

temperature –40°C to +85°C available, designated N

DS1232 8–PIN DIP (300 MIL) See Mech. Drawings Section

DS1232S 16–PIN SOIC (300 MIL) See Mech. Drawings Section

OPERATION – WATCHDOG TIMER

A watchdog timer function forces RST and RST signals to the active state when the ST input is not stimulated for a predetermined time period. The time period is set by the TD input to be typically 150 ms with TD connected to ground, 600 ms with TD left unconnected, and 1.2 seconds with TD connected to VCC. The watchdog timer starts timing out from the set time period as soon as RST and RST are inactive. If a high–to–low transition occurs on the ST input pin prior to time–out, the watchdog timer is reset and begins to time–out again. If the watchdog timer is allowed to time-out, then the RST and RST signals are driven to the active state for 250 ms minimum. The ST input can be derived from microprocessor address signals, data signals, and/or control signals. When the microprocessor is functioning normally, these signals would, as a matter of routine, cause the watchdog to be reset prior to time–out. To guarantee that the watchdog timer does not time–out, a high–to–low transition must occur at or less than the minimum shown in Table 1. A typical circuit example is shown in Figure 3.

MIC4102中文资料

MIC4102100V Half Bridge MOSFET Driver with Anti-Shoot Through Protection PRELIMINARY SPECIFICATIONSMicrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • General Description The MIC4102 is a high frequency, 100V Half Bridge MOSFET driver IC featuring internal anti-shoot-through protection. The low-side and high-side gate drivers are controlled by a single input signal to the PWM pin. The MIC4102 implements adaptive anti-shoot-through circuitry to optimize the switching transitions for maximum efficiency. The single input control also reduces system complexity and greatly simplifies the overall design.The MIC4102 also features a low-side drive disable pin. This gives the MIC4102 the capability to operate in a non-synchronous buck mode. This feature allows the MIC4102 to start up into applications where a bias voltage may already be present without pulling the output voltage down. Under-voltage protection on both the low-side and high-side supplies forces the outputs low. An on-chip boot-strap diode eliminates the discrete diode required with other driver ICs.The MIC4102 is available in the SOIC-8L package with a junction operating range from –40°C to +125°C.Data sheets and support documentation can be found on Micrel’s web site at .Features• Drives high- and low-side N-Channel MOSFETs with single input • Adaptive anti-shoot-through protection • Low side drive disable pin• Bootstrap supply voltage to 118V DC • Supply voltage up to 16V • TTL input thresholds • On-chip bootstrap diode• Fast 30ns propagation times• Drives 1000pF load with 10ns rise and 6ns fall times • Low power consumption• Supply under-voltage protection• 2.5Ω pull up , 1.5Ω pull down output resistance • Space saving SOIC-8L package• –40°C to +125°C junction temperature rangeApplications• High voltage buck converters• Networking / Telecom power supplies • Automotive power supplies• Current Fed Push-Pull Topologies • Ultrasonic drivers• Avionic power supplies___________________________________________________________________________________________________________Typical Application100V Buck Regulator SolutionOrdering InformationPart NumberStandard Pb-Free Input JunctionTemp.Range PackageMIC4102BM MIC4102YM TTL –40° to +125°CSOIC-8LPin ConfigurationVDD HB HO HSLOVSSLSPWM SOIC-8L (M)Pin DescriptionPin Number Pin Name Pin Function1 VDD Positive Supply to lower gate drivers. Decouple this pin to VSS (Pin 7). Bootstrapdiode connected to HB (pin 2).2 HB High-Side Bootstrap supply. External bootstrap capacitor is required. Connectpositive side of bootstrap capacitor to this pin. Bootstrap diode is on-chip.3 HO High-Side Output. Connect to gate of High-Side power MOSFET.4 HS High-Side Source connection. Connect to source of High-Side power MOSFET.Connect negative side of bootstrap capacitor to this pin.5 PWM Control Input. PWM high signal makes high-side HO output high, and low-sideLO output low. PWM low signal makes high-side HO output low, and low-sideLO output high.6 LS Low-Side Disable. When pulled low, this control signal immediately terminatesthe low-side LO output drive. The low-side LO output drive will remain low untilthis signal is removed. HS drive is not affected by the LS signal. Here is thelogic table:LS PWM LO HO0 0 0 00 1 0 11 0 1 01 1 0 17 VSS Chip negative supply, generally will be grounded.8 LO Low-Side Output. Connect to gate of Low-Side power MOSFET.Absolute Maximum Ratings(1)Supply Voltage (V DD, V HB – V HS)......................-0.3V to 18V Input Voltages (V PWM, V LS).....................-0.3V to V DD + 0.3V Voltage on LO (V LO)..............................-0.3V to V DD + 0.3V Voltage on HO (V HO)......................V HS - 0.3V to V HB + 0.3V Voltage on HS (continuous)..............................-1V to 110V Voltage on HB.. (118V)Average Current in VDD to HB Diode.......................100mA Junction Temperature (T J)........................–55°C to +150°C Storage Temperature (T s)..........................-60°C to +150°C EDS Rating(3)..............................................................Note 3 Operating Ratings(2)Supply Voltage (V DD)........................................+9V to +16V Voltage on HS...................................................-1V to 100V Voltage on HS (repetitive transient)..................-5V to 105V HS Slew Rate............................................................50V/ns Voltage on HB...................................V HS + 8V to V HS + 16V and............................................V DD - 1V to V DD + 100V Junction Temperature (T J)........................–40°C to +125°C Junction Thermal ResistanceSOIC-8L(θJA)...................................................140°C/WElectrical Characteristics(4)V DD = V HB = 12V; V SS = V HS = 0V; No load on LO or HO; T A = 25°C; unless noted. Bold values indicate –40°C< T J < +125°C.Symbol Parameter Condition MinTypMaxUnits Supply CurrentI DD V DD Quiescent Current PWM = 0V 150 450600µAI DDO V DD Operating Current f = 500kHz 3 3.54.0mAI HB Total HB Quiescent Current PWM = 0V 25 150200µAI HBO Total HB Operating Current f = 500kHz 1.5 2.53mAI HBS HB to VSS Current, Quiescent V HS = V HB = 110V 0.05 130µAInput Pins (TTL)V IL Low Level Input VoltageThreshold0.8 1.5 VV IH High Level Input VoltageThreshold1.52.2 VR I Input Pull-down Resistance 100 200 500 kΩUnder Voltage ProtectionV DDR V DD Rising Threshold 6.5 7.3 8.0 VV DDH V DD ThresholdHysteresis 0.5 V V HBR HB Rising Threshold 6.0 7.0 8.0 VV HBH HBThresholdHysteresis 0.4 V Boost Strap DiodeV DL Low-Current Forward Voltage I VDD-HB = 100µA 0.4 0.550.70VV DH Low-Current Forward Voltage I VDD-HB = 100mA 0.7 0.81.0VR D Dynamic Resistance I VDD-HB = 100mA 1.0 1.52.0ΩElectrical CharacteristicsSymbol Parameter Condition MinTypMaxUnits LO Gate DriverV OLL Low Level Output Voltage I LO = 160mA 0.18 0.30.4VV OHL High Level Output Voltage I LO = -100mA, V OHL = V DD - V LO 0.25 0.30.45VI OHL Peak Sink Current V LO = 0V 3 AI OLL Peak Source Current V LO = 12V 2 A HO Gate DriverV OLH Low Level Output Voltage I HO = 160mA 0.22 0.30.4VV OHH High Level Output Voltage I HO = -100mA, V OHH = V HB – V HO 0.25 0.30.45VI OHH Peak Sink Current V HO = 0V 3 AI OLH Peak Source Current V HO = 12V 2 A Switching Specifications (Anti-Shoot-Through Circuitry)t LOOFF Delay between PWM going highto LO going low30 4560nsV LOOFF Voltage threshold for LOMOSFET to be considered OFF1.7Vt HOON Delay between LO OFF to HOgoing High30 5060nst HOOFF Delay between PWM going Lowto HO going low45 6570nsV SWth Switch Node Voltage Thresholdwhen HO turns off1 2.5 4Vt LOON Delay between HO MOSFETbeing considered off to LOturning ON30 6070nst LSOFF Delay between LS going lowand LO turning OFFC L = 1000pF36 4570nst SWTO Forced LO ON, if VLOTH is notdetected120 250 450 nsSwitching Specificationst R Either Output Rise Time (3V to9V)C L = 1000pF 10 nst F Either Output Fall Time (3V to9V)C L = 1000pF 6 nst R Either Output Rise Time (3V to9V)CL = 0.1µF0.33 0.60.8µst F Either Output Fall Time (3V to9V)CL = 0.1µF0.2 0.30.4µsElectrical Characteristics (cont.)Symbol Parameter Condition MinTypMaxUnits Switching Specifications (cont.)t PW Minimum Input Pulse Width thatchanges the output with LS=5VC L=0Note 640 60 nst PW Minimum Output Pulse Widthon HO with min pulse width onPWM with LS=5VC L=0Note 615 nst PW Minimum Input Pulse Width thatchanges the output with LS=0VC L=0Note 613 20 nsMinimum Output Pulse Widthon HO with min pulse width onPWM with LS=0VC L=0Note 620t BS Bootstrap Diode Turn-On orTurn-Off Time10 nsNotes:1. Exceeding the absolute maximum rating may damage the device.2. The device is not guaranteed to function outside its operating rating.3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5kΩ in series with 100pF.4. Specification for packaged product only.5. All voltages relative to pin7, V SS unless otherwise specified.6. Guaranteed by design. Not production tested.Typical CharacteristicsTypical Characteristics (cont.)Timing DiagramstLSSw itch LOHOTime Point Action1-2PWM signal goes high. This initiates the LO signal to go low. The delay between PWM high to (V LO –10%) is typically 30ns (t LOOFF )2-4 LO goes low. When LO reaches 1.7V (V LOOFF ) thelow side MOSFET is deemed to be off. The high side output HO then goes high. The delay between 3 and 4 is typically 30ns (T HOON ); this allows for large turn off delay times of MOSFETs.5-7 PWM goes low; HO goes low, typically within45ns, t HOOFF . The switch node (HS pin) is then monitored; when the switch node is VDD-2.5V (V SWTH ) the high side MOSFET is deemed to be off and the LO output goes high within typically 30ns (t LOON ). This is controlled by a one shot and remains high until PWM goes high. This isbecause it is possible to have the SW node oscillate, and could easily bounce through 10V level. If the LO high transition has not happened within 250ns, it is forced to happen, unless the LS input is low.8-10 If at any time after 7 has occurred and LS pingoes low, the LO output will turn off within 36ns (V LSOFF ). HO will remain off. The LS pin overrides all shoot through control logic. If LS is low at the start of the next cycle when PWM signal goes high then HO shall switch transition 1-4 as normal. I.e. PWM signal equals HO output, LO = 0V.Functional Diagram156V V 7Figure 1. MIC4102 Functional Block DiagramFunctional DescriptionThe MIC4102 is a high voltage, non-inverting, synchronous MOSFET driver that uses a single PWM input signal to alternately drive both high-side and low-side N-Channel MOSFETs. The block diagram of the MIC4102 is shown in Figure 1.The MIC4102 input is TTL compatible. The high-side output buffer includes a high speed level-shifting circuit that is referenced to the HS pin. An internal diode is used as part of a bootstrap circuit to provide the drive voltage for the high-side output.Startup and UVLOThe UVLO circuit forces both driver outputs low until the supply voltage exceeds the UVLO threshold. The low-side UVLO circuit monitors the voltage between the VDD and VSS pins. The high-side UVLO circuit monitors the voltage between the HB and HS pins. Hysteresis in the UVLO circuit prevents noise and finite circuit impedance from causing chatter during turn-on.The VDD pin voltage is supplied to the HS pin through the internal bootstrap diode. The HB pin voltage will always be a diode drop less than VDD.Input StageThe MIC4102 utilizes a TTL compatible input stage. ThePWM input pin is referenced to the VSS pin. The voltage state of the input signal does not change the quiescent current draw of the driver. The threshold level is independent of the VDD supply voltage and there is no dependence between I VDD and the input signal amplitude. This feature makes the MIC4102 an excellent level translator that will drive high threshold MOSFETs from a low voltage PWM IC.Low-Side DriverA block diagram of the low-side driver is shown in Figure 2. The low-side driver is designed to drive a ground (Vss pin) referenced N-channel MOSFET. Low driver impedances allow the external MOSFET to be turned on and off quickly. The rail-to-rail drive capability of the output ensures a low Rdson from the external MOSFET. A low level applied to PWM pin will cause the HO output to go low and the LO output to go high. The upper driver FET turns on and Vdd is applied to the gate of the external MOSFET. A high level on the PWM pin forces the LO output low by turning off the upper driver and turning on the lower driver which ground the gate of the external MOSFET.Pulling the LS pin low disables the LO pin.VddExternal FETFigure 2. Low-Side Driver Block DiagramHigh-Side Driver and Bootstrap CircuitA block diagram of the high-side driver and bootstrap circuit is shown in Figure 3. This driver is designed to drive a floating N-channel MOSFET, whose source terminal is referenced to the HS pin.External FETC BFigure 3. High-Side Driver Block DiagramA low power, high speed, level shifting circuit isolates the low side (VSS pin) referenced circuitry from the high-side (HS pin) referenced driver. Power to the high-side driver and UVLO circuit is supplied by the bootstrap circuit while the voltage level of the HS pin is shifted high.The bootstrap circuit consists of an internal diode and external capacitor, C B . In a typical application, such as the synchronous buck converter shown in Figure 4, the HS pin is at ground potential while the low-side MOSFET is on. The internal diode allows capacitor C B to charge up to V DD -V D during this time (where V D is the forward voltage drop of the internal diode). After the low-side MOSFET is turned off and the HO pin turns on, the voltage across capacitor C B is applied to the gate of the upper external MOSFET. As the upper MOSFET turns on, voltage on the HS pin rises with the source of the high-side MOSFET until it reaches V IN . As the HS and HB pin rise, the internal diode is reverse biased preventing capacitor C B from discharging.VoutFigure 4. High-Side Driver and Bootstrap CircuitApplications InformationPower Dissipation ConsiderationsPower dissipation in the driver can be separated into three areas: • Internal diode dissipation in the bootstrap circuit •Internal driver dissipation• Quiescent current dissipation used to supply theinternal logic and control functions. Bootstrap Circuit Power DissipationPower dissipation of the internal bootstrap diode primarily comes from the average charging current of the C B capacitor times the forward voltage drop of the diode. Secondary sources of diode power dissipation are the reverse leakage current and reverse recovery effects of the diode.The average current drawn by repeated charging of the high-side MOSFET is calculated by:frequencyswitching drive gate V at Charge Gate Total Q :where HB gate )(==×=S Sgate AVE F f f Q I The average power dissipated by the forward voltage drop of the diode equals:dropvoltage forward Diode V :where F )(=×=FAVE F fwd V I PdiodeThe value of V F should be taken at the peak current through the diode, however, this current is difficult to calculate because of differences in source impedances. The peak current can either be measured or the value of V F at the average current can be used and will yield a good approximation of diode power dissipation.The reverse leakage current of the internal bootstrap diode is typically 11uA at a reverse voltage of 100V and 125C. Power dissipation due to reverse leakage is typically much less than 1mW and can be ignored.Reverse recovery time is the time required for the injected minority carriers to be swept away from the depletion region during turn-off of the diode. Power dissipation due to reverse recovery can be calculated by computing the average reverse current due to reverse recovery charge times the reverse voltage across the diode. The average reverse current and power dissipation due to reverse recovery can be estimated by:Time Recovery Reverse t Current Recovery Reverse Peak I :where 2rr RRM )()(==×=×××=REVAVE RR RR S rr RRM AVE RR V I Pdiode f t I IThe total diode power dissipation is:RR fwd total Pdiode Pdiode Pdiode +=An optional external bootstrap diode may be used instead of the internal diode (Figure 5). An external diode may be useful if high gate charge MOSFETs are being driven and the power dissipation of the internal diode is contributing to excessive die temperatures. The voltage drop of the external diode must be less than the internal diode for this option to work. The reverse voltage across the diode will be equal to the input voltage minus the Vdd supply voltage. A 100V Schottky diode will work for most 72V input telecom applications. The above equations can be used to calculate power dissipation in the external diode, however, if the external diode has significant reverse leakage current, the power dissipated in that diode due to reverse leakage can be calculated as:supply power the of frequency switching fs /t Cycle Duty D Voltage Reverse Diode V T and V at flow current Reverse I :where )1(ON REV J REV R =====−××=SREV R REV f D V I PdiodeThe on-time is the time the high-side switch is conducting. In most power supply topologies, the diode is reverse biased during the switching cycle off-time.Figure 5. Optional Bootstrap DiodeGate Drive Power DissipationPower dissipation in the output driver stage is mainly caused by charging and discharging the gate to source and gate to drain capacitance of the external MOSFET.Figure 6 shows a simplified equivalent circuit of the MIC4102 driving an external MOSFET.C BFigure 6. MIC4103 Driving an External MOSFETDissipation during the external MOSFET Turn-On Energy from capacitor C B is used to charge up the input capacitance of the MOSFET (Cgd and Cgs). The energy delivered to the MOSFET is dissipated in the three resistive components, Ron, Rg and Rg_fet. Ron is the on resistance of the upper driver MOSFET in the MIC4102. Rg is the series resistor (if any) between the driver IC and the MOSFET. Rg_fet is the gate resistance of the MOSFET. Rg_fet is usually listed in the power MOSFET’s specifications. The ESR of capacitor C B and the resistance of the connecting etch can be ignored since they are much less than Ron and Rg_fet.The effective capacitance of Cgd and Cgs is difficult to calculate since they vary non-linearly with Id, Vgs, and Vds. Fortunately, most power MOSFET specifications include a typical graph of total gate charge vs. Vgs. Figure 7 shows a typical gate charge curve for an arbitrary power MOSFET. This chart shows that for a gate voltage of 10V, the MOSFET requires about 23.5nC of charge. The energy dissipated by the resistive components of the gate drive circuit during turn-on is calculated as:MOSFETthe of e capacitancgate total the is Ciss Qg 1/2E soV C Q but221whereV V Ciss E gsgs ××=×=××=Figure 7. Typical Gate Charge vs. V GSThe same energy is dissipated by Roff, Rg and Rg_fet when the driver IC turns the MOSFET off.circuit drive gate the of frequency switching the is fs MOSFETthe on voltage source to gate the is Vgs Vgsat charge gate total the is Qg off -turn or on -turn during dissipated power the is P off -turn or on -turn during dissipated energy the is E Qg 21Qg 21E driver driver driver gs driver gs wherefs V P and V ×××=××=The power dissipated inside the MIC4102 equals the ratio of Ron & Roff to the external resistive losses in Rg and Rg_fet. The power dissipated in the MIC4102 due to driving the external MOSFET is:fetRg Rg Roff RoffP fet Rg Rg Ron Ron P Pdiss driver driver drive __++×+++×=Supply Current Power DissipationPower is dissipated in the MIC4102 even if is there is nothing being driven. The supply current is drawn by the bias for the internal circuitry, the level shifting circuitry and shoot-through current in the output drivers. The supply current is proportional to operating frequency and the Vdd and Vhb voltages. The typical characteristic graphs show how supply current varies with switching frequency and supply voltage.The power dissipated by the MIC4102 due to supply current isIhb Vhb Idd Vdd Pdiss ply ×+×=supTotal power dissipation and Thermal Considerations Total power dissipation in the MIC41032 equals the power dissipation caused by driving the external MOSFETs, the supply current and the internal bootstrap diode .total drive ply total Pdiode Pdiss Pdiss Pdiss ++=supThe die temperature may be calculated once the total power dissipation is known.JA total A J Pdiss T T θ×+=C/W)( air ambient to junction from resistance thermal the is θMIC4102the of n dissipatio power the is Pdiss C)( e temperatur junction the is T e temperatur ambient maximum the is T :JC total J A °°whereAnti Shoot-Through, Propagation Delay and other Timing ConsiderationsThe block diagram in Figure 1 illustrates how the MIC4102 drives the power stage of a synchronous buck converter. It is important that only one of the two MOSFETs is on at any given time. If both MOSFETs are simultaneously on they will short Vin to ground, causing high current from the Vin supply to “shoot through” the MOSFETs into ground. Excessive shoot-through causes higher power dissipation in the MOSFETs, voltage spikes and ringing in the circuit. The high current and voltage ringing generate conducted and radiated EMI.Minimizing shoot-through can be done passively, actively or though a combination of both. Passive shoot-through protection uses delays between the high and low gate drivers to prevent both MOSFETs from being on at the same time. These delays can be adjusted for different applications. Although simple, the disadvantage of this approach is the long delays required to account for process and temperature variations in the MOSFET and MOSFET driver.Active shoot-though monitors voltages on the gate drive outputs and switch node to determine when to switch the MOSFETs on and off. This active approach adjusts the delays to account for some of the variations, but it too has its disadvantages. High currents and fast switching voltages in the gate drive and return paths can cause parasitic ringing that may turn the MOSFETs back on even though the gate driver output is low. Another disadvantage is the driver cannot monitor the gate voltage inside the MOSFET. Figure 8 shows an equivalent circuit, including parasitics, of the gate driver section. The internal gate resistance (Rg_gate) and any external damping resistor (Rg) isolate the MOSFET’s gate from the driver output. There is a delay between when the driver output goes low and the MOSFET turns off. This turn-off delay is usually specified in the MOSFET data sheet. This delay increases when an external damping resistor is used.Switching NodeFigure 8. Gate Drive Circuit with ParasiticsThe MIC4102 uses a combination of active sensing and passive delay to insure that both MOSFETs are not on at the same time and to minimize shoot-through current. The timing diagram helps illustrate how the anti-shoot-through circuitry works. A high level on the PWM pin causes the LO pin to go low. The MIC4102 monitors the LO pin voltage and prevents the HO pin from turning on until the voltage on the LO pin reaches the V LOOFF threshold. After a short delay, the MIC4102 drives the HO pin high. Monitoring the LO voltage eliminates any excessive delay due to the MOSFET drivers turn-off time and the short delay accounts for the MOSFET turn-off delay as well as letting the LO pin voltage settle out. An external resistor between the LO output and the MOSFET may affect the performance of the LO pin monitoring circuit and is not recommended.A low on the PWM pin causes the HO pin to go low after a short delay (T HOOFF ). Before the LO pin can go high,the voltage on the switching node (HS pin) must have dropped to 2.5V below the Vdd voltage. Monitoring the switch voltage instead of the HO pin voltage eliminates timing variations and excessive delays due to the high side MOSFET turn-off. The LO driver turns on after a short delay (T LOON). Once the LO driver is turn on, it is latched on until the PWM signal goes high. This prevents any ringing or oscillations on the switch node or HS pin from turning off the LO driver. If the PWM pin goes low and the voltage on the HS pin does not cross the V SWth threshold, the LO pin will be forced high after a short delay (T SWTO), insuring proper operation.Fast propagation delay between the input and output drive waveform is desirable. It improves overcurrent protection by decreasing the response time between the control signal and the MOSFET gate drive. Minimizing propagation delay also minimizes phase shift errors in power supplies with wide bandwidth control loops.Care must be taken to insure the input signal pulse width is greater than the minimum specified pulse width. An input signal that is less than the minimum pulse width may result in no output pulse or an output pulse whose width is significantly less than the input.The maximum duty cycle (ratio of high side on-time to switching period) is determined by the time required for the C B capacitor to charge during the off-time. Adequate time must be allowed for the C B capacitor to charge up before the high-side driver is turned back on.The anti-shoot-through circuit in the MIC4102 prevents the driver from turning both MOSFETs on at the same time, however, other factors outside of the anti-shoot-through circuit’s control can cause shoot-through. Some of these are ringing on the gate drive node and capacitive coupling of the switching node voltage on the gate of the low-side MOSFET.Decoupling and Bootstrap Capacitor Selection Decoupling capacitors are required for both the low side (Vdd) and high side (HB) supply pins. These capacitors supply the charge necessary to drive the external MOSFETs as well as minimize the voltage ripple on these pins. The capacitor from HB to HS serves double duty by providing decoupling for the high-side circuitry as well as providing current to the high-side circuit while the high-side external MOSFET is on. Ceramic capacitors are recommended because of their low impedance and small size. Z5U type ceramic capacitor dielectrics are not recommended due to the large change in capacitance over temperature and voltage. A minimum value of 0.1uf is required for each of the capacitors, regardless of the MOSFETs being driven. Larger MOSFETs may require larger capacitance values for proper operation. The voltage rating of the capacitors depends on the supply voltage, ambient temperature and the voltage derating used for reliability. 25V rated X5R or X7R ceramic capacitors are recommended for most applications. The minimum capacitance value should be increased if low voltage capacitors are use since even good quality dielectric capacitors, such as X5R, will lose 40% to 70% of their capacitance value at the rated voltage.Placement of the decoupling capacitors is critical. The bypass capacitor for Vdd should be placed as close as possible between the Vdd and Vss pins. The bypass capacitor (C B) for the HB supply pin must be located as close as possible between the HB and HS pins. The etch connections must be short, wide and direct. The use of a ground plane to minimize connection impedance is recommended. Refer to the section on layout and component placement for more information. The voltage on the bootstrap capacitor drops each time it delivers charge to turn on the MOSFET. The voltage drop depends on the gate charge required by the MOSFET. Most MOSFET specifications specify gate charge vs. Vgs voltage. Based on this information and a recommended ∆V HB of less than 0.1V, the minimum value of bootstrap capacitance is calculated as:pinHBtheatdropVoltage∆VatChargeGateTotalQ:whereHBHBgate==∆≥HBgateB VQCThe decoupling capacitor for the Vdd input may be calculated in with the same formula, however, the two capacitors are usually equal in value.Grounding, Component Placement and CircuitLayoutNanosecond switching speeds and ampere peak currents in and around the MIC4102 driver require proper placement and trace routing of all components. Improper placement may cause degraded noise immunity, false switching, excessive ringing or circuit latch-up.Figure 9 shows the critical current paths when the driver outputs go high and turn on the external MOSFETs. It also shown the need for a low impedance ground plane. Charge needed to turn-on the MOSFET gates comes from the decoupling capacitors C VDD and C B. Current in the low-side gate driver flows from C VDD through the internal driver, into the MOSFET gate and out the Source. The return connection back to the decoupling capacitor is made through the ground plane. Any inductance or resistance in the ground return path causes a voltage spike or ringing to appear on the source of the MOSFET. This voltage works against the gate voltage and can either slow down or turn off the MOSFET during the period where it should be turned on.。

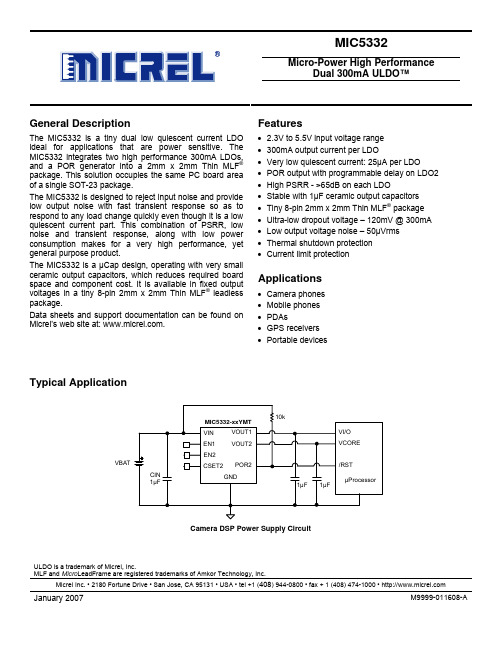

MIC5332中文资料

MIC5332

Micro-Power High Performance Dual 300mA ULDO™

General Description

The MIC5332 is a tiny dual low quiescent current LDO ideal for applications that are power sensitive. The MIC5332 integrates two high performance 300mA LDOs, and a POR generator into a 2mm x 2mm Thin MLF® package. This solution occupies the same PC board area of a single SOT-23 package.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 •

January 2007

M9999-011608-A

Pin Configuration

VIN 1 GND 2 POR2 3 EN2 4

8 VOUT1 7 VOUT2 6 CSET2 5 EN1

8-Pin 2mm x 2mm Thin MLF® (MT) (Top View)

Pin Description

Pin Number 1 2 3

4

5

6

7 8

Pin Name VIN GND

Regulator Output – LDO2.

Regulator Output – LDO1.

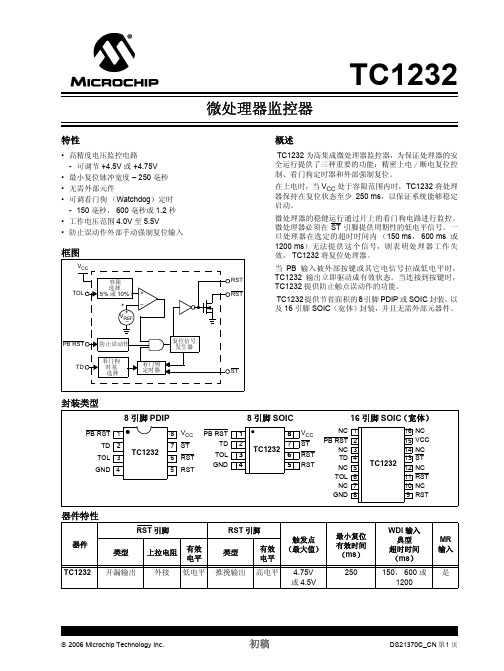

TC1232中文资料

2006 Microchip Technology Inc.

初稿

DS21370C_CN 第3 页

TC1232

tPB

ST

tST

tTD

PB RST

tPBD

VIL

RST RST

VIH tRST

防误动作 PB RST 输入引脚忽略长度小于 1 毫秒的输入脉冲 , 设计成只识别长度大于等于 20 毫秒的脉冲。

4: 由设计保证。

DS21370C_CN 第2 页

初稿

2006 Microchip Technology Inc.

TC1232

VCC

tF

+4.75V +4.25V

tR +4.75V

+4.25V

VCC = 5V

VCC

+4.5V(5% 触发点) +4.25V(10% 触发点) VCC

4.6V(5% 触发点) 4.5V(10% 触发点)

器件参考地。

复位输出 (高电平有效) 以下任一条件发生时,输出变成有效 (高电平):

1. 如果 VCC 电压跌落至选定的复位电压门限值以下; 2. 如果 PB RST 引脚被强制为低电平;

3. 如果 ST 引脚在选定的最小超时周期内没有被锁存; (参考 TD 引脚)

4. 初始上电时。

复位输出 (低电平有效) 以下任一条件发生时,输出变成有效 (低电平):

TC1232

微处理器监控器

特性

• 高精度电压监控电路 - 可调节 +4.5V 或 +4.75V

• 最小复位脉冲宽度 – 250 毫秒 • 无需外部元件 • 可调看门狗 (Watchdog)定时

KK1232中文资料

TECHNICAL DATAPOWER SUPPLY CONTROLWITH BUILT-IN WATCHDOG TIMERKK 1232 is designed to monitor power supply within the system ofreset signal generation formicroprocessors. It is used in monitor systems for controlling various processes and entities. Packaged in 8-pin SOP or DIP.Features:• Rated supply voltage 5.0 V • Accurate 5% or 10% microprocessor power supply monitoring • Programming of watchdog timer overflow time• Generation of reset signals at power on for correct microprocessor start.KK 1232The chip contains reference voltage source, analog comparator,Watchdog timer, circuit for monitoring power supply deviation accuracy. .Functions:• Reset signal generation after power failure/ error • Reset signal generation from external “RESET” pushbutton• Reset signal generation from watchdog timerFig 1 – PIN ASSIGNMENT06 RST 05 RST GND 04 PBRST 01 TD 02TOL 03 07 ST 08 Vcc Table 1 – Absolute maximum ratingsTypicalSymbol ParameterMin Max Units V ССSupply voltage- 7.0 V V IH Input voltage, high level - 7.0 V V IL Input voltage, low level -1.0 - V ТA Operating temperature range -40 +85 °С T stgStorage temperature-60+125°СTable 2 – Recommended operating conditionsTypicalUnits Symbol ParameterMin MaxVССSupply voltage 4.5 5.5 VV IH Input voltage, high level 2.0 UСС+0.3 V V IL Input voltage, low level -0.3 0.8 VТA Operating temperature range -20 +70 °СTable 3 DC electrical characteristics (T Amb = -40° to +85°С)Table 4 – AC electrical characteristics (Тamb = from -40 to +85 °С)Table 5 – Pin description______PBRST____ RST RSTFig. 2 – Timing diagram of forming reset signal from external PBRST control button___ ST Indeterminate strob Valid strob Invalid strobt ST ≥20 нс 62.5 ms ≤ t TD1 ≤250 ms 250 ms ≤ t TD2 ≤1000 ms 500 ms ≤ t TD3 ≤2000 msFig. 3 – Timing diagram : Strobe inputFig. 5 – Timing diagram: Power-Up/ StableFig.6 Block diagramGNDKK 1232Fig.7 Application Circuit : Watchdog Timer。

MEMORY存储芯片DS1232LPS-2中文规格书

Maxim > Design Support > Technical Documents > Application Notes > Microprocessor Supervisor Circuits > APP 581 Keywords: power on reset, por, push-button reset, manual reset, debounced, power fail, watchdog timer, strobe timer, selectable reset timeout, reset threshold, programming 8051, microprocessor supervisorAPPLICATION NOTE 581Advantages of Using a MicroMonitor and a Simple Application Demonstrating the Use of a DS1232May 17, 2001Abstract: Discusses how the DS1232 can be used to MicroMonitor an 8051-based system. This supervisor circuit provides power-on-reset (POR), manual reset (push-button) input, a watchdog timer (strobe timer), and an early power-fail comparator. The reset threshold tolerance can set selected to monitor both 5% and 10% supply tolerance systems. In addition, a pin-selectable reset time-out delay is available.To simplify the use of the device, a software execution program is included to show how the 8051 processor can be used in conjunction with the DS1232.IntroductionMaxim's DS1232 MicroMonitor chip is a highly integrated solution to add power-on reset delay, a pushbutton reset controller, robust power failure monitoring, and watchdog timer functionality to your microprocessor system with the addition of a single chip. The chip also offers both active and low reset signals, and selectivity of the watchdog time out period and the voltage monitoring level. The high level of integration reduces both the cost of implementation and the board space required. The chips are available in several packages including 8-pin mSOP, SOIC, and DIP.Advantages of Using a Dallas Semiconductor DS1232 MicroMonitorPower-on Reset Delay Allows Board Resources to Stabilize Before Execution Begins Precise control of a microcontroller's reset pin is important at all times during the operation of a circuit. Thus, it is imperative that the reset pin is controlled during both normal operation and during the power-up time of the circuit. One common problem with many microprocessor circuits is that the microcontroller begins execution before the memory and I/O resources available to it have a stable power supply. Some chips require hundreds of milliseconds to reset themselves and ready for operation. If a microprocessor begins execution within microseconds of a reset, it could be executing based on invalid input from the system resources. This can be resolved by adding a power-on reset (POR) circuit that holds the microprocessor in reset during the power-up sequence for 100s of milliseconds after a reset occurs. The DS1232 will hold a microcontroller's reset pin active for a minimum time of 250ms (typically 610 ms.) Additionally, it can provide either an active high or active low reset, which makes it compatible with any microprocessor.Pushbutton Reset Circuit Debounces a Momentary Switch and Provides a Solid Reset PulseAnother common problem in microprocessor circuits is that a less than perfect reset signal causes the microprocessor to reset several times, possibly executing some fragment of the initialization routine several times before the reset finally stabilizes. In some circuits, this is trivial. However, in other circuits this could cause major system problems. The DS1232 has internal circuitry that debounces a pushbutton and provides the system a clean reset signal. This eliminates the need to have both a separate power-on reset circuit and pushbutton circuitry attached separately to the reset pin. Plus, the DS1232 will hold the reset pin low for at least 250 ms to guarantee that the manual reset is received correctly by the microprocessor every time.The DS1232 Provides Power Failure MonitoringBrownouts and power failures are a reality for most microprocessor systems. Since there is no way to avoid the occasional power cycle, a robust microprocessor solution must account for the various power failure modes. The DS1232 monitors the power supply to a microprocessor and forces the microprocessor into its reset state if there is a brownout or if the power fails altogether. This guarantees that the system will not try to operate during irregular supply voltage conditions, and it can prevent the microprocessor from executing code when it should really be waiting for the supply voltage to return to a valid state.An Internal Watchdog Timer MAY Reset a Microprocessor, but an External Watchdog WILL Reset ItWatchdog timers are used to ensure that if the code operating on a microprocessor enters into an unanticipated state, then the processor will reset after some minimal amount of time elapses. Many microprocessors have an internal watchdog timer that handles this function without an external component. However, the internal watchdog timer can be disabled by the pseudo-random code that is executing on the microprocessor. The external watchdog timer on the DS1232 cannot be disabled. This gives you peace of mind, knowing that if the MicroMonitor is not strobed, then the microcontroller will be reset. Another nice feature of the DS1232 is that the strobe period can be varied to one of three different values. The device thus works well with faster and slower microprocessors because you can program the watchdog timer to an appropriate rate for any microcontroller. Another advantage of the external watchdog timer is that the strobe signal is visible to the external world because it is on an I/O pin. This allows easier debugging of watchdog-related problems.Hardware Required for Using a DS1232 with a MicrocontrollerThe greatest asset of the DS1232 is that all of the functions listed above are implemented in a single package. This functionality does not require a complex chipset. The schematic below shows how theDS1232 is used with a Dallas Semiconductor DS87C520 Microcontroller. Since most systems incorporate a pushbutton reset, the only things added are the DS1232, a pull-up resistor for the active low output, and a decoupling capacitor to reduce the possibility of noise on the power supply causing a reset. The pull-up resistor is added here because it is used to generate the oscilloscope plots shown on the following pages. The active-low RST output of the DS1232 is not required by the DS87C520. The LEDs on the diagram are used to signal when ISRs (Interrupt Service Requests) are being serviced.Figure 3. Typical active-low RST signal during power-up sequence: 1) V CC 2) active-low RST.After the reset signal becomes inactive, the microcontroller must strobe the ST signal low before the watchdog timer elapses. The DS1232's watchdog timer cannot be disabled, so this must occur within n ms of the reset signals becoming inactive, or the microprocessor will be reset. The watchdog time-out values for the DS1232 are programmable and specified with somewhat wide ranges. However, it is best to strobe the ST pin faster than the minimum watchdog time-out specification, because it eliminates the chance that a fast watchdog will cause the system to erroneously reset. The watchdog time-out can be set to one of three values by adjusting the value of the TD pin according to Table 1.Table 1. Watchdog Time-Out Values for Each TD Pin StateTD Pin State Minimum Time-Out Typical Time-Out Maximum Time-OutGround62.5 ms150 ms250 msFloating250 ms600 ms1000 msV CC500 ms1200 ms2000 msFigure 1 shows the TD pin grounded, and hence ST must see a negative edge every 62.5ms to guarantee that the microprocessor will not be reset. If it is strobed at the typical rate of 150 ms, there is a chance that it would work with one MicroMonitor but not another. The inclusion of the minimum, typical and maximum values informs the end user of the behavior of the watchdog. Program the TD such that the microprocessor can strobe the ST pin before it reaches the minimum time-out and plan on it taking as long as the maximum time-out to reset the microcontroller. The typical value does not apply to any specific MicroMonitor; it simply shows that the critical time is between the minimum and maximum time-out value. Thus, the typical value for any given MicroMonitor could range anywhere between the minimum and maximum time-out values.Figure 4 (below) shows the strobe signal that was used for the same hardware setup. Trace # 1 shows V CC and #2 shows ST. As the same hardware was used with the reset signals shown in Figures 2 and 3, the reset was de-asserted at ~460ms. The first negative edge of the strobe signal occurs at 496 ms, or 36 ms after reset becomes inactive. This is sufficiently early to guarantee that the watchdog will not reset the system unless the microcontroller enters an unanticipated state.Figure 4. Watchdog strobe signal (ST) at the beginning of execution: 1)V CC 2) ST.As you can see from Figure 5 (below), the ST signal receives a negative-edge approximately every 20 ms. With a faster microprocessor, there is no reason not to strobe more often than required. Also, on this graph it is easy to see that the strobes start to occur at 496 ms after the voltage is applied.Figure 5. Zoom showing frequence of the ST signal: 1)V CC 2) ST.The DS1232 will also debounce a momentary switch without additional hardware, making it easy to add a pushbutton reset to over-ride the system. The pushbutton is shown in Figure 1, and the RST and active-low RST signals it causes are shown in Figures 6 and 7. Note that the pushbutton does not bounce when connected to the DS1232 and that the reset is held for approximately the same period of time as a reset during power-up (610 ms typically). Also note that a pull-up resistor is not required for the pushbutton, because an internal pull-up resistor is available within the DS1232.。

MICRF211AYQS中文资料

Ordering Information

Part Number

Temperature Range

Package

MICRF211AYQS

–40° to +105°C

16-Pin QSOP

_______________________________________________________________________________________________

Not Connected (Connect to Ground)

Reference resonator input connection to Colpitts oscillator stage, 7pF, in parallel with low resistance MOS switch-to-GND, during normal operation. Driven by startup excitation circuit during the internal startup control sequence.

元器件交易网

CRF211

3V, QwikRadio® 433.92 MHz Receiver

General Description

Features

ADS1232中文资料

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

MIC5233中文资料

MIC5233

2

August 2003

MIC5233

Micrபைடு நூலகம்l

Absolute Maximum Ratings (Note 1)

Input Supply Voltage ....................................... –20V to 38V Enable Input Voltage ...................................... –0.3V to 38V Power Dissipation .................................... Internally Limited Junction Temperature .............................. –40°C to +125°C Storage Temperature ............................... –65°C to +150°C ESD Rating, Note 3

Typical Application

GROUND CURRENT (µA)

40 35 30 25 20 15 10 4 IOUT = 10µA 8 12 16 20 24 28 32 36 40 INPUT VOLTAGE (V) IOUT = 1mA

VIN CIN=1.0µF

OFF ON

MIC5233BM5

Applications

Ordering Information

Part Number MIC5233-1.8BM5 MIC5233-2.5BM5 MIC5233-3.0BM5 MIC5233-3.3BM5 MIC5233-5.0BM5 MIC5233BM5 Marking L318 L325 L330 L333 L350 L3AA Voltage 1.8V 2.5V 3.0V 3.3V 5.0V ADJ. Junction Temp. Range –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C –40°C to +125°C Package SOT-23-5 SOT-23-5 SOT-23-5 SOT-23-5 SOT-23-5 SOT-23-5

枫笛Saramonic一拖二无线话筒中文使用说明书

UwMic9UHF无线麦克风系统使用手册声明请在使用前仔细阅读使用手册,并按照手册严格操作。

请妥善保存本手册以供将来参考。

如果使用手册不能解决您的问题,请向您的零售商寻求帮助,或发送电子邮件给我们:***********************@注意事项1. 请不要在水下或雨中使用,并将产品储存在阴凉,干燥的地方。

2. 请在常温下保存. 请不要在极端条件下使用,请远离热源,如加热器和烤箱。

3. 在使用和存储过程中,请注意避免灰尘和湿气。

4. 为了获得最佳拾音效果,请不要遮盖咪头。

5. 如果长时间不使用,请将电池移除。

目录概述 (4)便携式接收机 UwMic9-RX9 (4)简介 (4)产品结构 (4)安装配件 (5)LCD 显示屏操作指南 (6)腰包式发射机UwMic9-TX9 (10)简介 (10)产品结构 (10)安装配件 (12)LCD 显示屏操作指南 (13)手持式麦克风 UwMic9-HU9 (16)简介 (16)产品结构 (16)设置向导 (17)手雷发射机UwMic9-TX-XLR9 (18)简介 (18)产品结构 (18)安装配件 (20)LCD显示屏操作指南 (21)操作指南 (25)规格 (30)接收机 RX9 (30)发射机 TX9,HU9和TX-XLR9 (31)包装清单 (32)概述Saramonic UwMic9 UHF 无线麦克风套装适用于便携式无线操作,可在多种环境中使用,例如数码单反相机的视频录制,实地录音,广播电视,电子新闻采集,现场采访等。

便携式接收机 UwMic9-RX9介绍枫笛 UwMic9-RX9 便携式接收机可提供数字音频处理级音质和稳定的模拟 FM 调制。

它可提供宽频率范围并覆盖多个通道,易于使用的高清显示屏和小尺寸接收机可完美连接在DSLR摄像机上。

UwMic9-RX9 具有自动扫描功能,可以自动搜索可用传输频率通道设置,同时也可选择输出信号是单声道/立体声。

MIC923资料

Micrel

Min 65 Typ 76 86 7 7.5 –7.5 410 2200 70 40 84 50 2.5 9 1.1 3 –7 Max Units dB dB V V MHz V/µs mA mA mA nV/√Hz pA/√Hz

Micrel, Inc. • 1849 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 944-0970 •

March 2002

1பைடு நூலகம்

MIC923

MIC923

2

March 2002

元器件交易网 MIC923

Symbol AVOL VOUT GBW SR ISC IS Parameter Large-Signal Voltage Gain Condition RL = 2kΩ, VOUT = ±3V RL = 100Ω, VOUT = ±1V Maximum Output Voltage Swing positive, RL = 2kΩ negative, RL = 2kΩ Gain-Bandwidth Product Slew Rate Short-Circuit Output Current CL = 1.7pF, RL = 100Ω C=1.7pF, Av =2, RL = 1MΩ, RF = 2kΩ positive SR = 2100V/µs source sink Supply Current Input Voltage Noise Input Current Noise

No Load f = 10kHz f = 10kHz

MIC2130资料