MC74LVX8053MELG中文资料

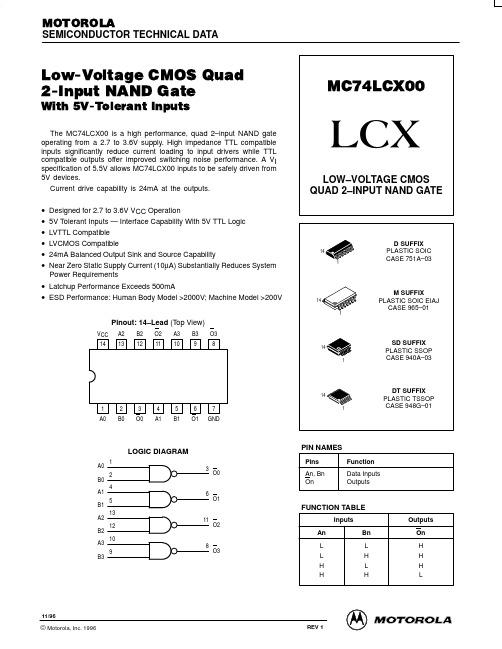

MC74LCX00中文资料

CAPACITIVE CHARACTERISTICS

Symbol CIN COUT CPD Parameter Input Capacitance Output Capacitance Power Dissipation Capacitance Condition VCC = 3.3V, VI = 0V or VCC VCC = 3.3V, VI = 0V or VCC 10MHz, VCC = 3.3V, VI = 0V or VCC Typical 7 8 25 Unit pF pF pF

MC74LCX00

ABSOLUTE MAXIMUM RATINGS*

Symbol VCC VI VO IIK IOK Parameter DC Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current Value –0.5 to +7.0 –0.5 ≤ VI ≤ +7.0 –0.5 ≤ VO ≤ VCC + 0.5 –50 –50 +50 IO ICC IGND TSTG DC Output Source/Sink Current DC Supply Current Per Supply Pin DC Ground Current Per Ground Pin Storage Temperature Range ±50 ±100 ±100 –65 to +150 Note 1. VI < GND VO < GND VO > VCC Condition Unit V V V mA mA mA mA mA mA °C

14 1

MCX7系列金属通讯接线器产品说明书

MCX7–J–P–H–RA–TH1

MCX7–J–P–H–ST–TH1

MCX7–P–C–H–RA–CA3

MCX7–P–C–H–ST–C7–P–P–H–ST–SM1

MCX7 SERIES

75 Ω OPTIMIZED MCX JACKS & PLUGS

contact

– ST

= Straight

– RA

= Right-angle (–J–TH1 only)

(6.00) .236 SQ

(0.50) .020

(5.08) .200 DIA

(0.71) .028 DIA

(10.44) .411

(3.94) .155

–J–ST–TH1

(6.00) .236 SQ

PROCESSING

Lead–Free Solderable: Yes

MCX7

GENDER

TYPE

–P

= Plug

–J

= Jack

–P

= PCB Mount

(6.00) .236 SQ

(0.76) .030

(5.08) .200 DIA

(6.76) .266

–J–ST–SM1

(0.71) .028 DIA

(1.65) .065

(6.00) .236 SQ

(8.20) .323

(4.00) .158

(0.20) .008 (1.00) .039

–P–ST–SM1

(0.90) .035 DIA

(3.00) .118

PLATING

ORIENTATION

TERMINATION

–H

= 30 µ" (0.76 µm) Gold center contact, 3 µ" (0.08 µm) Gold outer

74系列芯片数据手册大全

74系列芯片数据手册大全本文将为大家介绍74系列芯片数据手册的大全,主要是介绍各种74系列芯片的应用以及参数等相关信息。

一、常用的74系列芯片有哪些?74系列芯片是最常用的数字集成电路之一,主要包括以下几种芯片:1. 74LS00:四个二输入与门。

6. 74LS74:双D触发器。

8. 74LS138:三线八选一译码器。

9. 74LS151:八路数据选择器/复用器。

10. 74LS161:四位二进制同步计数器。

11. 74LS240:三态缓冲器。

13. 74LS373:透明锁存器。

16. 74LS595:8位移位寄存器。

二、74LS00芯片的应用及参数74LS00芯片是一种四个二输入与门的数字集成电路,通常用于逻辑门的实现和数字电路的设计。

该芯片可以从以下几方面进行分析:1. 参数描述该芯片内部具有四个与门,每个与门都有两个输入端和一个输出端。

输入端的输入电压范围通常为0V-5V,输出电平为低电平(0V)或高电平(5V),输出电流为16mA。

该芯片的工作电压范围为4.75V-5.25V,工作温度范围为0°C-70°C或-40°C-85°C。

2. 应用领域74LS00芯片通常用于逻辑门的实现和数字电路的设计,例如计数器、锁存器、转换器、寄存器等电路。

由于其适用于逻辑运算,因此在数字电路的开发中已经成为一种非常重要的芯片。

3. 管脚说明该芯片的14个管脚可以分为四类:电源引脚(VCC和GND)、输入引脚(A1、A2、B1、B2、C1、C2、D1和D2)、输出引脚(Y1、Y2、Y3和Y4)和负载引脚。

其中,电源引脚VCC 和GND是给电源提供电的,输入引脚是二进制的输入信号,输出引脚是二进制的输出信号,负载引脚是与其它数字电路相连的终端。

4. 使用方法在使用74LS00芯片时,需要将芯片的电源引脚接到适当的电源上,然后将输入引脚所接收到的二进制值输入到芯片中,芯片会处理这些二进制数值并输出相应结果。

74LVC1G53资料

74LVC1G53

2-channel analog multiplexer/demultiplexer

Rev. 03 — 29 August 2007

Product data sheet

1. General description

The 74LVC1G53 is a low-power, low-voltage, high-speed, Si-gate CMOS device.

Rev. 03 — 29 August 2007

© NXP B.V. 2007. All rights reserved.

2 of 22

元器件交易网

NXP Semiconductors

6. Pinning information

6.1 Pinning

74LVC1G53

Z1 E2 GND 3 GND 4

The 74LVC1G53 provides one analog multiplexer/demultiplexer with a digital select input (S), two independent inputs/outputs (Y0 and Y1), a common input/output (Z) and an active LOW enable input (E). When pin E is HIGH, the switch is turned off.

For XSON8 and XQFN8 packages: above 45 °C the value of Ptot derates linearly with 2.4 mW/K.

74LVC1G53_3

Product data sheet

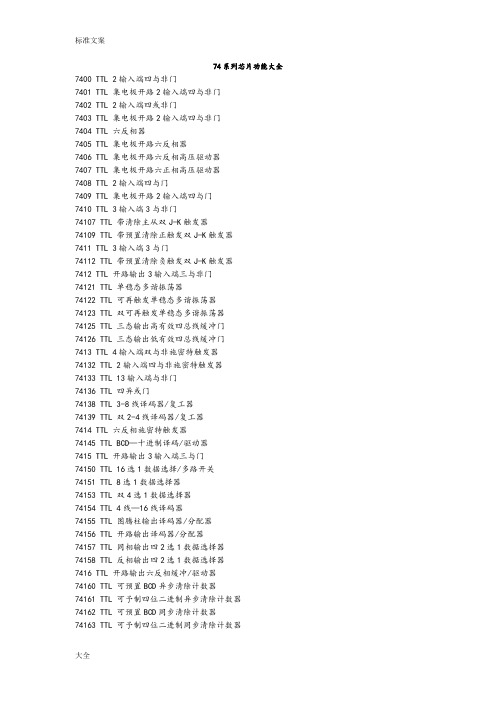

74系列芯片功能大全

74系列芯片功能大全7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称 74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门 (OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√。

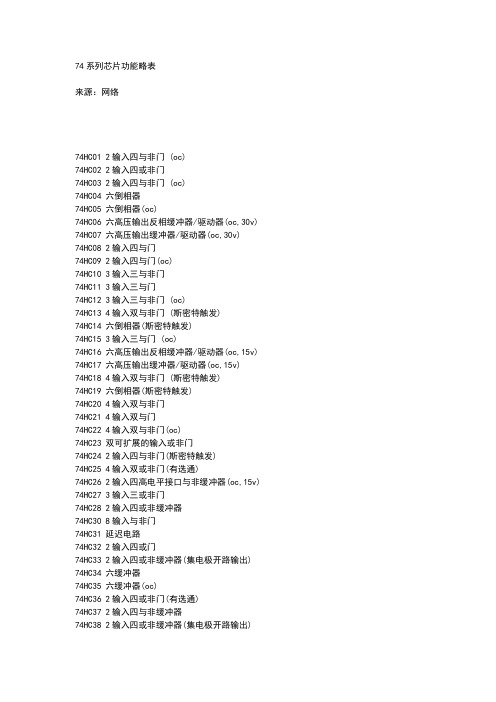

74系列芯片简单说明

74系列芯片功能略表来源:网络74HC01 2输入四与非门 (oc)74HC02 2输入四或非门74HC03 2输入四与非门 (oc)74HC04 六倒相器74HC05 六倒相器(oc)74HC06 六高压输出反相缓冲器/驱动器(oc,30v) 74HC07 六高压输出缓冲器/驱动器(oc,30v)74HC08 2输入四与门74HC09 2输入四与门(oc)74HC10 3输入三与非门74HC11 3输入三与门74HC12 3输入三与非门 (oc)74HC13 4输入双与非门 (斯密特触发)74HC14 六倒相器(斯密特触发)74HC15 3输入三与门 (oc)74HC16 六高压输出反相缓冲器/驱动器(oc,15v) 74HC17 六高压输出缓冲器/驱动器(oc,15v)74HC18 4输入双与非门 (斯密特触发)74HC19 六倒相器(斯密特触发)74HC20 4输入双与非门74HC21 4输入双与门74HC22 4输入双与非门(oc)74HC23 双可扩展的输入或非门74HC24 2输入四与非门(斯密特触发)74HC25 4输入双或非门(有选通)74HC26 2输入四高电平接口与非缓冲器(oc,15v) 74HC27 3输入三或非门74HC28 2输入四或非缓冲器74HC30 8输入与非门74HC31 延迟电路74HC32 2输入四或门74HC33 2输入四或非缓冲器(集电极开路输出) 74HC34 六缓冲器74HC35 六缓冲器(oc)74HC36 2输入四或非门(有选通)74HC37 2输入四与非缓冲器74HC38 2输入四或非缓冲器(集电极开路输出)74HC39 2输入四或非缓冲器(集电极开路输出)74HC40 4输入双与非缓冲器74HC41 bcd-十进制计数器74HC42 4线-10线译码器(bcd输入)74HC43 4线-10线译码器(余3码输入)74HC44 4线-10线译码器(余3葛莱码输入)74HC45 bcd-十进制译码器/驱动器74HC46 bcd-七段译码器/驱动器74HC47 bcd-七段译码器/驱动器74HC48 bcd-七段译码器/驱动器74HC49 bcd-七段译码器/驱动器(oc)74HC50 双二路2-2输入与或非门(一门可扩展)74HC51 双二路2-2输入与或非门74HC51 二路3-3输入,二路2-2输入与或非门74HC52 四路2-3-2-2输入与或门(可扩展)74HC53 四路2-2-2-2输入与或非门(可扩展)74HC53 四路2-2-3-2输入与或非门(可扩展)74HC54 四路2-2-2-2输入与或非门74HC54 四路2-3-3-2输入与或非门74HC54 四路2-2-3-2输入与或非门74HC55 二路4-4输入与或非门(可扩展)74HC60 双四输入与扩展74HC61 三3输入与扩展74HC62 四路2-3-3-2输入与或扩展器74HC63 六电流读出接口门74HC64 四路4-2-3-2输入与或非门74HC65 四路4-2-3-2输入与或非门(oc)74HC70 与门输入上升沿jk触发器74HC71 与输入r-s主从触发器74HC72 与门输入主从jk触发器74HC73 双j-k触发器(带清除端)74HC74 正沿触发双d型触发器(带预置端和清除端)74HC75 4位双稳锁存器74HC76 双j-k触发器(带预置端和清除端)74HC77 4位双稳态锁存器74HC78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74HC80 门控全加器74HC81 16位随机存取存储器74HC82 2位二进制全加器(快速进位)74HC83 4位二进制全加器(快速进位)74HC84 16位随机存取存储器74HC85 4位数字比较器74HC86 2输入四异或门74HC87 四位二进制原码/反码/oi单元74HC89 64位读/写存储器74HC90 十进制计数器74HC91 八位移位寄存器74HC92 12分频计数器(2分频和6分频)74HC93 4位二进制计数器74HC94 4位移位寄存器(异步)74HC95 4位移位寄存器(并行io)74HC96 5位移位寄存器74HC97 六位同步二进制比率乘法器74HC100 八位双稳锁存器74HC103 负沿触发双j-k主从触发器(带清除端)74HC106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74HC107 双j-k主从触发器(带清除端)74HC108 双j-k主从触发器(带预置,清除,时钟)74HC109 双j-k触发器(带置位,清除,正触发)74HC110 与门输入j-k主从触发器(带锁定)74HC111 双j-k主从触发器(带数据锁定)74HC112 负沿触发双j-k触发器(带预置端和清除端)74HC113 负沿触发双j-k触发器(带预置端)74HC114 双j-k触发器(带预置端,共清除端和时钟端)74HC116 双四位锁存器74HC120 双脉冲同步器/驱动器74HC121 单稳态触发器(施密特触发)74HC122 可再触发单稳态多谐振荡器(带清除端)74HC123 可再触发双单稳多谐振荡器74HC125 四总线缓冲门(三态输出)74HC126 四总线缓冲门(三态输出)74HC128 2输入四或非线驱动器74HC131 3-8译码器74HC132 2输入四与非门(斯密特触发)74HC133 13输入端与非门74HC134 12输入端与门(三态输出)74HC135 四异或/异或非门74HC136 2输入四异或门(oc)74HC137 八选1锁存译码器/多路转换器74HC138 3-8线译码器/多路转换器74HC139 双2-4线译码器/多路转换器74HC140 双4输入与非线驱动器74HC141 bcd-十进制译码器/驱动器74HC142 计数器/锁存器/译码器/驱动器74HC145 4-10译码器/驱动器74HC147 10线-4线优先编码器74HC148 8线-3线八进制优先编码器74HC150 16选1数据选择器(反补输出)74HC151 8选1数据选择器(互补输出)74HC152 8选1数据选择器多路开关74HC153 双4选1数据选择器/多路选择器74HC154 4线-16线译码器74HC155 双2-4译码器/分配器(图腾柱输出)74HC156 双2-4译码器/分配器(集电极开路输出) 74HC157 四2选1数据选择器/多路选择器74HC158 四2选1数据选择器(反相输出)74HC160 可预置bcd计数器(异步清除)74HC161 可预置四位二进制计数器(并清除异步) 74HC162 可预置bcd计数器(异步清除)74HC163 可预置四位二进制计数器(并清除异步) 74HC164 8位并行输出串行移位寄存器74HC165 并行输入8位移位寄存器(补码输出)74HC166 8位移位寄存器74HC167 同步十进制比率乘法器74HC168 4位加/减同步计数器(十进制)74HC169 同步二进制可逆计数器74HC170 4*4寄存器堆74HC171 四d触发器(带清除端)74HC172 16位寄存器堆74HC173 4位d型寄存器(带清除端)74HC174 六d触发器74HC175 四d触发器74HC176 十进制可预置计数器74HC177 2-8-16进制可预置计数器74HC178 四位通用移位寄存器74HC179 四位通用移位寄存器74HC180 九位奇偶产生/校验器74HC181 算术逻辑单元/功能发生器74HC182 先行进位发生器74HC183 双保留进位全加器74HC184 bcd-二进制转换器74HC185 二进制-bcd转换器74HC190 同步可逆计数器(bcd,二进制)74HC191 同步可逆计数器(bcd,二进制)74HC192 同步可逆计数器(bcd,二进制)74HC193 同步可逆计数器(bcd,二进制)74HC199 八位移位寄存器74HC210 2-5-10进制计数器74HC213 2-n-10可变进制计数器74HC221 双单稳触发器74HC230 八3态总线驱动器74HC231 八3态总线反向驱动器74HC240 八缓冲器/线驱动器/线接收器(反码三态输出)74HC241 八缓冲器/线驱动器/线接收器(原码三态输出)74HC242 八缓冲器/线驱动器/线接收器74HC243 4同相三态总线收发器74HC244 八缓冲器/线驱动器/线接收器74HC245 八双向总线收发器74HC246 4线-七段译码/驱动器(30v)74HC247 4线-七段译码/驱动器(15v)74HC248 4线-七段译码/驱动器74HC249 4线-七段译码/驱动器74HC251 8选1数据选择器(三态输出)74HC253 双四选1数据选择器(三态输出)74HC256 双四位可寻址锁存器74HC257 四2选1数据选择器(三态输出)74HC258 四2选1数据选择器(反码三态输出)74HC259 8为可寻址锁存器74HC260 双5输入或非门74HC261 4*2并行二进制乘法器74HC265 四互补输出元件74HC266 2输入四异或非门(oc)74HC270 2048位rom (512位四字节,oc)74HC271 2048位rom (256位八字节,oc)74HC273 八d触发器74HC274 4*4并行二进制乘法器74HC275 七位片式华莱士树乘法器74HC276 四jk触发器74HC278 四位可级联优先寄存器74HC279 四s-r锁存器74HC280 9位奇数/偶数奇偶发生器/较验器74HC28174HC283 4位二进制全加器74HC290 十进制计数器74HC291 32位可编程模74HC293 4位二进制计数器74HC294 16位可编程模74HC295 四位双向通用移位寄存器74HC298 四-2输入多路转换器(带选通)74HC299 八位通用移位寄存器(三态输出)74HC348 8-3线优先编码器(三态输出)74HC352 双四选1数据选择器/多路转换器74HC353 双4-1线数据选择器(三态输出)74HC354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74HC365 6总线驱动器74HC366 六反向三态缓冲器/线驱动器74HC367 六同向三态缓冲器/线驱动器74HC368 六反向三态缓冲器/线驱动器74HC373 八d锁存器74HC374 八d触发器(三态同相)74HC375 4位双稳态锁存器74HC377 带使能的八d触发器74HC378 六d触发器74HC379 四d触发器74HC381 算术逻辑单元/函数发生器74HC382 算术逻辑单元/函数发生器74HC384 8位*1位补码乘法器74HC385 四串行加法器/乘法器74HC386 2输入四异或门74HC390 双十进制计数器74HC391 双四位二进制计数器74HC395 4位通用移位寄存器74HC396 八位存储寄存器74HC398 四2输入端多路开关(双路输出)74HC399 四-2输入多路转换器(带选通)74HC422 单稳态触发器74HC423 双单稳态触发器74HC440 四3方向总线收发器,集电极开路74HC441 四3方向总线收发器,集电极开路74HC442 四3方向总线收发器,三态输出74HC443 四3方向总线收发器,三态输出74HC444 四3方向总线收发器,三态输出74HC445 bcd-十进制译码器/驱动器,三态输出74HC446 有方向控制的双总线收发器74HC448 四3方向总线收发器,三态输出74HC449 有方向控制的双总线收发器74HC465 八三态线缓冲器74HC466 八三态线反向缓冲器74HC467 八三态线缓冲器74HC468 八三态线反向缓冲器74HC490 双十进制计数器74HC540 八位三态总线缓冲器(反向)74HC541 八位三态总线缓冲器74HC589 有输入锁存的并入串出移位寄存器74HC590 带输出寄存器的8位二进制计数器74HC591 带输出寄存器的8位二进制计数器74HC592 带输出寄存器的8位二进制计数器74HC593 带输出寄存器的8位二进制计数器74HC594 带输出锁存的8位串入并出移位寄存器74HC595 8位输出锁存移位寄存器74HC596 带输出锁存的8位串入并出移位寄存器74HC597 8位输出锁存移位寄存器74HC598 带输入锁存的并入串出移位寄存器74HC599 带输出锁存的8位串入并出移位寄存器74HC604 双8位锁存器74HC605 双8位锁存器74HC606 双8位锁存器74HC607 双8位锁存器74HC620 8位三态总线发送接收器(反相)74HC621 8位总线收发器74HC622 8位总线收发器74HC623 8位总线收发器74HC640 反相总线收发器(三态输出)74HC641 同相8总线收发器,集电极开路74HC642 同相8总线收发器,集电极开路74HC643 8位三态总线发送接收器74HC644 真值反相8总线收发器,集电极开路74HC645 三态同相8总线收发器74HC646 八位总线收发器,寄存器74HC647 八位总线收发器,寄存器74HC648 八位总线收发器,寄存器74HC649 八位总线收发器,寄存器74HC651 三态反相8总线收发器74HC652 三态反相8总线收发器74HC653 反相8总线收发器,集电极开路74HC654 同相8总线收发器,集电极开路74HC668 4位同步加/减十进制计数器74HC669 带先行进位的4位同步二进制可逆计数器74HC670 4*4寄存器堆(三态)74HC671 带输出寄存的四位并入并出移位寄存器74HC672 带输出寄存的四位并入并出移位寄存器74HC673 16位并行输出存储器,16位串入串出移位寄存器74HC674 16位并行输入串行输出移位寄存器74HC681 4位并行二进制累加器74HC682 8位数值比较器(图腾柱输出)74HC683 8位数值比较器(集电极开路)74HC684 8位数值比较器(图腾柱输出)74HC685 8位数值比较器(集电极开路)74HC686 8位数值比较器(图腾柱输出)74HC687 8位数值比较器(集电极开路)74HC688 8位数字比较器(oc输出)74HC689 8位数字比较器74HC690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74HC691 计数器/寄存器(带多转换,三态输出)74HC692 同步十进制计数器(带预置输入,同步清除)74HC693 计数器/寄存器(带多转换,三态输出)74HC696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74HC697 计数器/寄存器(带多转换,三态输出)74HC698 计数器/寄存器(带多转换,三态输出)74HC699 计数器/寄存器(带多转换,三态输出)74HC716 可编程模n十进制计数器74HC718 可编程模n十进制计数器。

MC74LVX50 CMOS 六路高速缓冲器说明书

MC74LVX50Hex BufferThe MC74LVX50 is an advanced high speed CMOS buffer fabricated with silicon gate CMOS technology.The internal circuit is composed of three stages, including a buffered output which provides high noise immunity and stable output. The inputs tolerate voltages up to 7.0 V , allowing the interface of 5.0 V systems to 3.0 V systems.Features•High Speed: t PD = 4.1 ns (Typ) at V CC = 3.3 V•Low Power Dissipation: I CC = 2 m A (Max) at T A = 25°C •High Noise Immunity: V NIH = V NIL = 28% V CC •Power Down Protection Provided on Inputs •Balanced Propagation Delays•Designed for 2.0 V to 3.6 V Operating Range •Low Noise: V OLP = 0.5 V (Max)•These Devices are Pb−Free and are RoHS CompliantY1A1A2A3A4A5A6Y2Y3Y4Y5Y6A1Y11A2Y21A3Y31A4Y41A5Y51A6Y61Figure 1. Logic Diagram Figure 2. Logic SymbolY = AFUNCTION TABLEL HA Input Y OutputL HSee detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.ORDERING INFORMATIONMARKING DIAGRAMSTSSOP−14DT SUFFIXCASE 948GSOIC−14 NB D SUFFIXCASE 751ALVX 50ALYW G G 114LVX50= Specific Device Code A = Assembly Location WL, L = Wafer Lot Y= YearWW, W = Work WeekG or G= Pb−Free Package (Note: Microdot may be in either location)TSSOP−14SOIC−14 NBPIN ASSIGNMENT14−Lead (Top View)1314121110982134567V CC A6Y6A5Y5A4Y4A1Y1A2Y2A3Y3GNDMAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage*0.5 to )7.0V V IN DC Input Voltage*0.5 to )7.0V V OUT DC Output Voltage*0.5 to V CC)0.5VI IK DC Input Diode Current V I < GND*20mAI OK DC Output Diode Current V O < GND±20mAI OUT DC Output Sink Current±25mAI CC DC Supply Current per Supply Pin±50mAT STG Storage Temperature Range*65 to )150_C T L Lead Temperature, 1 mm from Case for 10 Seconds260_C T J Junction Temperature under Bias)150_C q JA Thermal Resistance(Note 1)SOIC TSSOP 125170_C/WMSL Moisture Sensitivity Level 1F R Flammability Rating Oxygen Index: 30% − 35%UL94−**********V ESD ESD Withstand Voltage Human Body Model (Note 2)Machine Model (Note 3)Charged Device Model (Note 4)> 2000> 2002000VI Latchup Latchup Performance Above V CC and Below GND at 85_C (Note 5)±300mA Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.Measured with minimum pad spacing on an FR4 board, using 10 mm−by−1 inch, 2−ounce copper trace with no air flow.2.Tested to EIA/JESD22−A114−A.3.Tested to EIA/JESD22−A115−A.4.Tested to JESD22−C101−A.5.Tested to EIA/JESD78.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC Supply Voltage 2.0 3.6V V I Input Voltage(Note 6)0 5.5V V O Output Voltage(HIGH or LOW State)0V CC V T A Operating Free−Air Temperature*40)85_CD t/D V Input Transition Rise or Fall Rate V CC = 3.0 V ±0.3 V0100ns/V Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.6.Unused inputs may not be left open. All inputs must be tied to a high− or low−logic input voltage level.NOTE:The q JA of the package is equal to 1/Derating. Higher junction temperatures may affect the expected lifetime of the device per the table and figure below.DC ELECTRICAL CHARACTERISTICSSymbol Parameter Test Conditions V CC(V)T A = 25°C T A≤ 85°CUnit Min Typ Max Min MaxV IH High−Level Input Voltage 2.03.03.61.52.02.41.52.02.4VV IL Low−Level Input Voltage 2.03.03.60.50.80.80.50.80.8VV OH High−Level Output Voltage (V IN= V IH or V IL)I OH = −50 m AI OH = −50 m AI OH = −4 mA2.03.03.01.92.92.582.03.01.92.92.48VV OL Low−Level Output Voltage (V IN= V IH or V IL)I OL = 50 m AI OL = 50 m AI OL = 4 mA2.03.03.00.00.00.10.10.360.10.10.44VI IN Input Leakage Current V IN = 5.5 V or GND0 to3.6±0.1±1.0m AI CC Quiescent Supply Current V IN = V CC or GND 3.6 2.020.0m A Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.AC ELECTRICAL CHARACTERISTICS Input t r = t f= 3.0 nsSymbol Parameter Test ConditionsT A = 25°C T A≤ 85°CUnit Min Typ Max Min Maxt PLH, t PHL Propagation Delay,Input A to YV CC = 2.7 V C L = 15 pFC L = 50 pF5.47.910.113.61.01.012.516.0nsV CC = 3.3 V ± 0.3 V C L = 15 pFC L = 50 pF4.16.66.29.71.01.07.511.5t OSHL t OSLH Output−to−Output Skew(Note 7)V CC = 2.7 V C L = 50 pF 1.5 1.5nsV CC = 3.3 V ±0.3V C L = 50 pF 1.5 1.5C IN Input Capacitance41010pFC PD Power Dissipation Capacitance (Note 8)Typical @ 25°C, V CC = 3.3 VpF157.Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device.The specification applies to any outputs switching in the same direction, either HIGH−to−LOW (t OSHL) or LOW−to−HIGH (t OSLH); parameter guaranteed by design.8.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC. C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.NOISE CHARACTERISTICS Input t r = t f = 3.0ns, C L = 50pF, V CC = 3.3 VSymbol CharacteristicT A = 25°CUnit Typ MaxV OLP Quiet Output Maximum Dynamic V OL0.30.5V V OLV Quiet Output Minimum Dynamic V OL−0.3−0.5V V IHD Minimum High Level Dynamic Input Voltage 2.0V V ILD Maximum Low Level Dynamic Input Voltage0.8VFigure 3. Switching Waveforms V CCGNDAY*Includes all probe and jig capacitanceFigure 4. Test CircuitC L *Figure 5. Input Equivalent CircuitINPUTEMBOSSED CARRIER DIMENSIONS (See Notes 9 and 10)Tape SizeB 1MaxDD 1EFKPP 0P 2RTW8 mm4.35 mm (0.179”)1.5 mm + 0.1−0.0(0.059” +0.004−0.0)1.0 mm Min (0.179”) 1.75 mm ±0.1 (0.069±0.004”)3.5 mm ±0.5(1.38±0.002”) 2.4 mm Max (0.094”)4.0 mm ±0.10(0.157±0.004”) 4.0 mm ±0.1(0.157±0.004”)2.0 mm ±0.1(0.079±0.004”)25 mm (0.98”)0.6 mm (0.024)8.3 mm (0.327)12 mm8.2 mm (0.323”) 1.5 mm Min (0.060)5.5 mm ±0.5(0.217±0.002”)6.4 mm Max (0.252”)4.0 mm ±0.10(0.157±0.004”)8.0 mm ±0.10(0.315±0.004”)30 mm (1.18”)12.0 mm ±0.3(0.470±0.012”)16 mm12.1 mm (0.476”)7.5 mm ±0.10(0.295±0.004”)7.9 mm Max (0.311”)4.0 mm ±0.10(0.157±0.004”)8.0 mm ±0.10(0.315±0.004”)12.0 mm ±0.10(0.472±0.004”)16.3 mm (0.642)24 mm20.1 mm (0.791”)11.5 mm ±0.10(0.453±0.004”)11.9 mm Max (0.468”)16.0 mm ±0.10(0.63±0.004”)24.3 mm (0.957)9.Metric Dimensions Govern−English are in parentheses for reference only.10.A 0, B 0, and K 0 are determined by component size. The clearance between the components and the cavity must be within 0.05 mm min to 0.50 mm max. The component cannot rotate more than 10° within the determined cavityD 1FOR COMPONENTS2.0 mm × 1.2 mm AND LARGEROF CAVITYUSER DIRECTION OF FEEDFOR MACHINE REFERENCEONLYINCLUDING DRAFT AND RADII CONCENTRIC AROUND B 0R MIN.TAPE AND COMPONENTSSHALL PASS AROUND RADIUS “R”WITHOUT DAMAGE1)EMBOSSMENTTYPICALCOMPONENT CAVITY CENTER LINETYPICALCOMPONENT CENTER LINECAMBER (TOP VIEW)ALLOWABLE CAMBER TO BE 1 mm/100 mm NONACCUMULATIVE OVER 250 mm11.A 0000.50 mm max. The component cannot rotate more than 10° within the determined cavityFigure 6. Carrier Tape SpecificationsFigure 7. Reel DimensionsREEL DIMENSIONSTape Size T&R Suffix A Max Gt Max 8 mm T1, T2178 mm (7”)8.4 mm, +1.5 mm, −0.0(0.33” + 0.059”, −0.00)14.4 mm (0.56”)8 mm T3, T4330 mm (13”)8.4 mm, +1.5 mm, −0.0(0.33” + 0.059”, −0.00)14.4 mm (0.56”)12 mm R2330 mm (13”)12.4 mm, +2.0 mm, −0.0(0.49” + 0.079”, −0.00)18.4 mm (0.72”)16 mm R2360 mm (14.173”)16.4 mm, +2.0 mm, −0.0(0.646” + 0.078”, −0.00)22.4 mm (0.882”)24 mmR2360 mm (14.173”)24.4 mm, +2.0 mm, −0.0(0.961” + 0.078”, −0.00)30.4 mm (1.197”)HOLEFigure 8. Reel Winding Direction160 mm MINDIRECTION OF FEEDTAPEFigure 9. Tape Ends for Finished GoodsFigure 10. TSSOP and SOIC R2 Reel Configuration/OrientationUser Direction of FeedTAPE UTILIZATION BY PACKAGETape Size SOICTSSOPQFNSC88A / SOT−353SC88/SOT−3638 mm 5−, 6−Lead12 mm 8−Lead 8−, 14−, 16−Lead 8−, 14−, 16−Lead 16 mm 14−, 16−Lead 20−, 24−Lead 20−, 24−Lead 24 mm18−, 20−, 24−, 28−Lead48−, 56−Lead48−, 56−LeadORDERING INFORMATIONDevicePackage Shipping †MC74LVX50DG SOIC−14 NB (Pb−Free)55 Units / Rail MC74LVX50DR2G SOIC−14 NB (Pb−Free)2500 Tape & Reel MC74LVX50DTG TSSOP−14(Pb−Free)96 Units / Rail MC74LVX50DTR2GTSSOP−14(Pb−Free)2500 Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.CASE 948G ISSUE BDIM MIN MAX MIN MAX INCHES MILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W−.____14X REF 14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.CASE 751A−03ISSUE KNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.5.MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.DETAIL ADIM MIN MAX MIN MAX INCHESMILLIMETERS D 8.558.750.3370.344E 3.80 4.000.1500.157A 1.35 1.750.0540.068b 0.350.490.0140.019L 0.40 1.250.0160.049e 1.27 BSC 0.050 BSC A30.190.250.0080.010A10.100.250.0040.010M0 7 0 7 H 5.80 6.200.2280.244h 0.250.500.0100.019____14X0.581.27PITCH*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at /site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended,or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONMouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:O N Semiconductor:MC74LVX50DG MC74LVX50DR2G MC74LVX50DTG MC74LVX50DTR2G。

MC74VHCT50A中文资料

ICC

Maximum Quiescent

VIN = VCC or GND

5.5

Supply Current

2.0

20

40 µA

ICCT

Quiescent Supply

Current

Input: VIN = 3.4 V

5.5

1.35

1.50

1.65 mA

IOFF

Output Leakage

VOUT = 5.5 V

The MC74VHCT50A input structure provides protection when voltages up to 7 V are applied, regardless of the supply voltage. This allows the MC74VHCT50A to be used to interface 5 V circuits to 3 V circuits. The output structures also provide protection when VCC = 0 V. These input and output structures help prevent device destruction caused by supply voltage – input/output voltage mismatch, battery backup, hot insertion, etc.

125 170

Unit V V V mA mA mA mA mA _C _C _C

_C/W

PD

Power Dissipation in Still Air

mW

SOIC

500

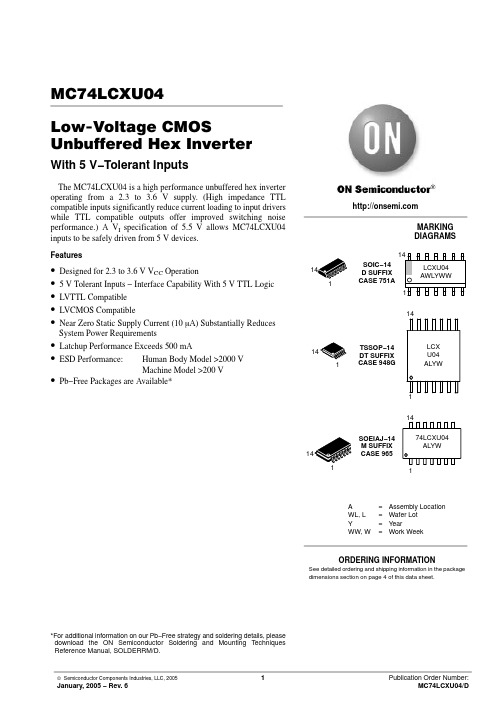

MC74LCXU04中文资料

MC74LCXU04Low−Voltage CMOS Unbuffered Hex InverterWith 5 V−Tolerant InputsThe MC74LCXU04 is a high performance unbuffered hex inverter operating from a 2.3 to 3.6 V supply. (High impedance TTL compatible inputs significantly reduce current loading to input driverswhile TTL compatible outputs offer improved switching noise performance.) A V I specification of 5.5 V allows MC74LCXU04 inputs to be safely driven from 5 V devices.Features•Designed for 2.3 to 3.6 V V CC Operation•5 V Tolerant Inputs − Interface Capability With 5 V TTL Logic •LVTTL Compatible•LVCMOS Compatible•Near Zero Static Supply Current (10 m A) Substantially Reduces System Power Requirements•Latchup Performance Exceeds 500 mA•ESD Performance:Human Body Model >2000 VMachine Model >200 V•Pb−Free Packages are Available**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATIONV A3O3A4O4A5O5Figure 2. Logic DiagramMAXIMUM RATINGSvalues (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.I O absolute maximum rating must be observed.RECOMMENDED OPERATING CONDITIONSDC ELECTRICAL CHARACTERISTICSIAC CHARACTERISTICS t R = t F = 2.5ns; R L = 500 W (Note 3)4.Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device.The specification applies to any outputs switching in the same direction, either HIGH−to−LOW (t OSHL) or LOW−to−HIGH (t OSLH); parameter guaranteed by design.DYNAMIC SWITCHING CHARACTERISTICSmeasured in the LOW state.CAPACITIVE CHARACTERISTICSORDERING INFORMATIONSpecifications Brochure, BRD8011/D.*This package is inherently Pb−Free.PROPAGATION DELAYSt R = t F = 2.5 ns, 10% to 90%; f = 1 MHz; t W = 500 nsV CC0 VV OHV OLAnOnFigure 3. AC WaveformsV R LC L = 50 pF at V CC = 3.3 0.3 V or equivalent (includes jig and probe capacitance)C L = 30 pF at V CC = 2.5 0.2 V or equivalent (includes jig and probe capacitance)R L = R 1 = 500 W or equivalentR T = Z OUT of pulse generator (typically 50 W )Figure 4. Test CircuitPACKAGE DIMENSIONSSOIC−14D SUFFIX CASE 751A−03ISSUE GTSSOP−14DT SUFFIX CASE 948G−01ISSUE ODIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH,PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15(0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W−.____14X REF K1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____PACKAGE DIMENSIONSSOEIAJ−14M SUFFIXCASE 965−01ISSUE OON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

MC74VHC244DWR2G,MC74VHC244DT,MC74VHC244DTR2,MC74VHC244DWR2,MC74VHC244MELG, 规格书,Datasheet 资料

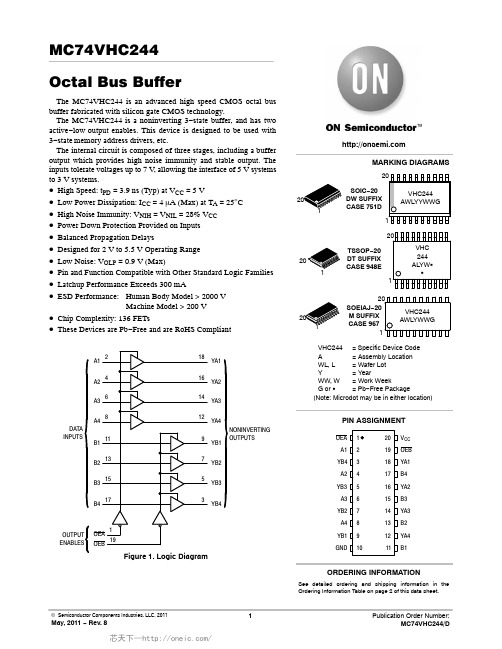

MC74VHC244Octal Bus BufferThe MC74VHC244 is an advanced high speed CMOS octal bus buffer fabricated with silicon gate CMOS technology.The MC74VHC244 is a noninverting 3−state buffer, and has two active −low output enables. This device is designed to be used with 3−state memory address drivers, etc.The internal circuit is composed of three stages, including a buffer output which provides high noise immunity and stable output. The inputs tolerate voltages up to 7 V , allowing the interface of 5 V systems to 3 V systems.•High Speed: t PD = 3.9 ns (Typ) at V CC = 5 V•Low Power Dissipation: I CC = 4 m A (Max) at T A = 25°C •High Noise Immunity: V NIH = V NIL = 28% V CC •Power Down Protection Provided on Inputs •Balanced Propagation Delays•Designed for 2 V to 5.5 V Operating Range •Low Noise: V OLP = 0.9 V (Max)•Pin and Function Compatible with Other Standard Logic Families •Latchup Performance Exceeds 300 mA•ESD Performance:Human Body Model > 2000 VMachine Model > 200 V•Chip Complexity: 136 FETs•These Devices are Pb −Free and are RoHS CompliantDATA INPUTSYB4YB3YB2YB1YA4YA3YA2YA1NONINVERTING OUTPUTSFigure 1. Logic Diagram201120MARKING DIAGRAMSSOIC −20DW SUFFIX CASE 751DTSSOP −20DT SUFFIX CASE 948ESOEIAJ −20M SUFFIX CASE 967VHC244AWLYWWGVHC244= Specific Device Code A = Assembly Location WL, L = Wafer Lot Y= Year WW, W = Work Week G or G = Pb −Free Package(Note: Microdot may be in either location)VHC 244ALYW G G A3A2YB4A1OEA GNDYB1A4YB2YB3YA2B4YA1OEB V CC B1YA4B2YA3B3PIN ASSIGNMENTORDERING INFORMATIONSee detailed ordering and shipping information in the Ordering Information Table on page 2 of this data sheet.FUNCTION TABLEINPUTS OUTPUTSOEA, OEB A, B YA, YBL L LL H HH X ZORDERING INFORMATIONDevice Package Shipping†MC74VHC244DW − OBSOLETE*SOIC−20 WB38 Units/RailMC74VHC244DWR2G SOIC−20 WB(Pb−Free)1000/T ape & ReelMC74VHC244DTG TSSOP−20(Pb−Free)75 Units/RailMC74VHC244DTR2G TSSOP−20(Pb−Free)2500/T ape & ReelMC74VHC244M − OBSOLETE*SOIC EIAJ−20(Pb−Free)1600 Units/BoxMC74VHC244MELG SOIC EIAJ−20(Pb−Free)2000/T ape & Reel*This device is obsolete, information available for reference.†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.MAXIMUM RATINGS (Note 1)Symbol Parameter Value UnitV CC Positive DC Supply Voltage−0.5 to +7.0VV IN Digital Input Voltage−0.5 to +7.0VV OUT DC Output Voltage−0.5 to V CC +0.5VI IK Input Diode Current−20mAI OK Output Diode Current$20mAI OUT DC Output Current, per Pin$25mAI CC DC Supply Current, V CC and GND Pins$75mAP D Power Dissipation in Still Air SOICTSSOP 500450mWT STG Storage Temperature Range−65 to +150°CV ESD ESD Withstand Voltage Human Body Model (Note 2)Machine Model (Note 3)Charged Device Model (Note 4)>2000>200>2000VI LATCHUP Latchup Performance Above V CC and Below GND at 125°C (Note 5)$300mAq JA Thermal Resistance, Junction−to−Ambient SOICTSSOP 96128°C/WStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.V in and V out should be constrained to the range GND v (V in or V out) v V CC. Unused inputs must always be tied to an appropriate logic voltagelevel (e.g., either GND or V CC). Unused outputs must be left open.2.Tested to EIA/JESD22−A114−A3.Tested to EIA/JESD22−A115−A4.Tested to JESD22−C101−A5.Tested to EIA/JESD78RECOMMENDED OPERATING CONDITIONSSymbol Characteristics Min Max Unit V CC DC Supply Voltage 2.0 5.5V V IN DC Input Voltage0 5.5V V OUT DC Output Voltage0V CC V T A Operating Temperature Range, all Package Types−55125°Ct r, t f Input Rise or Fall Time V CC = 3.3 V + 0.3 VV CC = 5.0 V + 0.5 V 010020ns/VDEVICE JUNCTION TEMPERATURE VERSUS TIME TO 0.1% BOND FAILURESJunctionTemperature °C Time, Hours Time, Years 801,032,200117.890419,30047.9100178,70020.411079,6009.4 12037,000 4.2 13017,800 2.0 1408,900 1.011101001000TIME, YEARSNORMALIZEDFAILURERATEFigure 2. Failure Rate vs. Time Junction TemperatureDC CHARACTERISTICS (Voltages Referenced to GND)V CC T A = 25°C T A≤ 85°C−55°C ≤ T A≤ 125°C Symbol Parameter Condition(V)Min Typ Max Min Max Min Max UnitV IH Minimum High−LevelInput Voltage2.03.0 to5.51.5V CCX0.71.5V CCX0.71.5V CCX0.71.5V CCX0.7VV IL Maximum Low−LevelInput Voltage2.03.0 to5.50.5V CCX0.30.5V CCX0.30.5V CCX0.3VV OH Maximum High−LevelOutput Voltage V IN = V IH or V ILI OH = −50 m A2.03.04.51.92.94.42.03.04.51.92.94.41.92.94.4VV IN = V IH or V ILI OH = −4 mAI OH = −8 mA3.04.52.583.942.483.82.343.66V OL Maximum Low−LevelOutput Voltage V IN = V IH or V ILI OL = 50 m A2.03.04.50.00.00.00.10.10.10.10.10.10.10.10.1VV IN = V IH or V ILI OH = 4 mAI OH = 8 mA3.04.50.360.360.440.440.520.52I IN Input Leakage Current V IN = 5.5 V or GND0 to5.5±0.1±1.0±1.0m AI OZ Maximum 3−StateLeakage Current V IN = V IH or V ILV OUT = V CC or GND5.5±0.25±2.5±2.5m AI CC Maximum QuiescentSupply Current(per package)V IN = V CC or GND 5.5 4.040.040.0m AAC ELECTRICAL CHARACTERISTICS (Input t r = t f= 3.0 ns)Symbol Parameter Test ConditionsT A = 25°C T A3 85°C−55°C 3 T A3 125°CUnit Min Typ Max Min Max Min Maxt PLH, t PHL Maximum PropagationDelay, A to YA orB to YBV CC = 3.3 ± 0.3 V C L = 15 pFC L = 50 pF5.88.38.411.91.01.010.013.51.01.011.014.5nsV CC = 5.0 ± 0.5 V C L = 15 pFC L = 50 pF3.95.45.57.51.01.06.58.51.01.07.59.5t PZL, t PZH Output Enable TimeOEA to YA orOEB to YBV CC = 3.3 ± 0.3 V C L = 15 pFR L = 1 k W C L = 50 pF6.69.110.614.11.01.012.516.01.01.013.517.0nsV CC = 5.0 ± 0.5 V C L = 15 pFR L = 1 k W C L = 50 pF4.76.27.39.31.01.08.510.51.01.09.511.5t PLZ, t PHZ Output Disable TimeOEA to YA orOEB to YBV CC = 3.3 ± 0.3 V C L = 50 pFR L = 1 k W10.314.0 1.016.0 1.017.0nsV CC = 5.0 ± 0.5 V C L = 50 pFR L = 1 k W6.79.2 1.010.5 1.011.5t OSLH, t OSHL Output to Output Skew V CC = 3.3 ± 0.3 V C L = 50 pF(Note 6)1.5 1.5 1.5nsV CC = 5.0 ± 0.5 V C L = 50 pF(Note 6)1.0 1.0 1.5C in Maximum InputCapacitance4101010pFC out Maximum Three−StateOutput Capacitance(Output in High−ImpedanceState)6pFC PD Power Dissipation Capacitance (Note 7)Typical @ 25°C, V CC = 5.0VpF196.Parameter guaranteed by design. t OSLH = |t PLHm− t PLHn|, t OSHL = |t PHLm− t PHLn|.7.C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.Average operating current can be obtained by the equation: I CC(OPR) = C PD V CC f in + I CC/8 (per bit). C PD is used to determine the no−load dynamic power consumption; P D = C PD V CC2 f in + I CC V CC.NOISE CHARACTERISTICS (Input t r = t f = 3.0 ns, C L = 50 pF, V CC = 5.0 V)Symbol ParameterT A = 25°CUnit Typ MaxV OLP Quiet Output Maximum Dynamic V OL0.60.9V V OLV Quiet Output Minimum Dynamic V OL−0.6−0.9V V IHD Minimum High Level Dynamic Input Voltage 3.5V V ILD Maximum Low Level Dynamic Input Voltage 1.5VFigure 3. Switching Waveform Figure 4. Switching WaveformV CCGNDOEA or OEBYA or YBYA or YBV CCGNDHIGHIMPEDANCEHIGHIMPEDANCE*Includes all probe and jig capacitance C L *TEST POINTFigure 5. Test Circuit *Includes all probe and jig capacitanceTEST POINTFigure 6. Test CircuitCONNECT TO V CC WHEN TESTING t PLZ AND t PZL .CONNECT TO GND WHEN TESTING t PHZ AND t PZH .TEST CIRCUITSSWITCHING WAVEFORMSFigure 7. Input Equivalent CircuitINPUTSOIC−20 WB DW SUFFIX CASE 751D−05 ISSUE GM0.25SA SBTDIM MIN MAXMILLIMETERSA 2.35 2.65A10.100.25B0.350.49C0.230.32D12.6512.95E7.407.60e 1.27 BSCH10.0510.55h0.250.75L0.500.90q0 7NOTES:1.DIMENSIONS ARE IN MILLIMETERS.2.INTERPRET DIMENSIONS AND TOLERANCESPER ASME Y14.5M, 1994.3.DIMENSIONS D AND E DO NOT INCLUDE MOLDPROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.5.DIMENSION B DOES NOT INCLUDE DAMBARPROTRUSION. ALLOWABLE PROTRUSIONSHALL BE 0.13 TOTAL IN EXCESS OF BDIMENSION AT MAXIMUM MATERIALCONDITION.__TSSOP −20CASE 948E −02ISSUE CDIM A MIN MAX MIN MAX INCHES 6.600.260MILLIMETERS B 4.30 4.500.1690.177C 1.200.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSCH 0.270.370.0110.015J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M 0 8 0 8 ____NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION:MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSIONSHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.DETAIL E6.400.252------16X0.360.65PITCHSOLDERING FOOTPRINTSOEIAJ −20CASE 967−01ISSUE ADIM MIN MAX MIN MAX INCHES --- 2.05---0.081MILLIMETERS 0.050.200.0020.0080.350.500.0140.0200.150.250.0060.01012.3512.800.4860.5045.10 5.450.2010.2151.27 BSC 0.050 BSC 7.408.200.2910.3230.500.850.0200.0331.10 1.500.0430.0590 0.700.900.0280.035---0.81---0.032A 1H E Q 1L E _10 _0 _10 _NOTES: 1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982. 2.CONTROLLING DIMENSION: MILLIMETER. 3.DIMENSIONS D AND E DO NOT INCLUDEMOLD FLASH OR PROTRUSIONS AND AREMEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15(0.006) PER SIDE. 4.TERMINAL NUMBERS ARE SHOWN FORREFERENCE ONLY. 5.THE LEAD WIDTH DIMENSION (b) DOES NOTINCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003)TOTAL IN EXCESS OF THE LEAD WIDTHDIMENSION AT MAXIMUM MATERIAL CONDITION.DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACEBETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 ( 0.018).DETAIL PA b c D E e L M ZON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

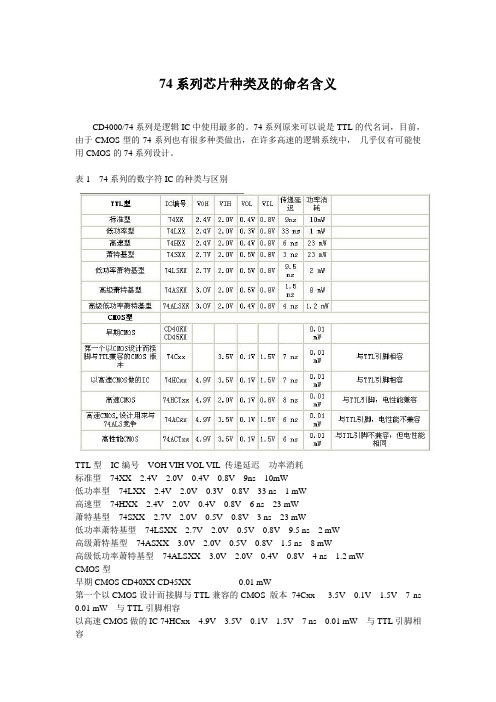

74系列芯片种类及的命名含义

74系列芯片种类及的命名含义CD4000/74系列是逻辑IC中使用最多的。

74系列原来可以说是TTL的代名词,目前,由于CMOS型的74系列也有很多种类做出,在许多高速的逻辑系统中,几乎仅有可能使用CMOS的74系列设计。

表1 74系列的数字符IC的种类与区别TTL型IC编号VOH VIH VOL VIL 传递延迟功率消耗标准型74XX 2.4V 2.0V 0.4V 0.8V 9ns 10mW低功率型74LXX 2.4V 2.0V 0.3V 0.8V 33 ns 1 mW高速型74HXX 2.4V 2.0V 0.4V 0.8V 6 ns 23 mW萧特基型74SXX 2.7V 2.0V 0.5V 0.8V 3 ns 23 mW低功率萧特基型74LSXX 2.7V 2.0V 0.5V 0.8V 9.5 ns 2 mW高级萧特基型74ASXX 3.0V 2.0V 0.5V 0.8V 1.5 ns 8 mW高级低功率萧特基型74ALSXX 3.0V 2.0V 0.4V 0.8V 4 ns 1.2 mWCMOS型早期CMOS CD40XX CD45XX 0.01 mW第一个以CMOS设计而接脚与TTL兼容的CMOS 版本74Cxx 3.5V 0.1V 1.5V 7 ns 0.01 mW 与TTL引脚相容以高速CMOS做的IC 74HCxx 4.9V 3.5V 0.1V 1.5V 7 ns 0.01 mW 与TTL引脚相容高速CMOS 74HCTxx 4.9V 2.0V 0.1V 0.8V 8 ns 0.01 mW 与TTL引脚,电性能兼容高速CMOS,设计用來与74ALS竞争74ACxx 4.9V 3.5V 0.1V 1.5V 6 ns 0.01 mW 与TTL引脚,电性能不兼容高性能CMOS 74ACTxx 4.9V 3.5V 0.1V 1.5V 6 ns 0.01 mW 与TTL引脚不兼容,但电性能相同注:XX处一般为2~3位数的数字,各代表同一功能。

摩菲控制器MC系列说明书

说明MC 系列 Millennium 控制器是一种以微机为基础的监视、控制和数据采集系统。

MC 系列适用于机动压缩机及其它多种工业设备控制。

MC 系列作为成套控制设备的核心,可无间断地监视输入信号和设置点,并相应控制输出,以保持设备正常运行。

如果输入发生超限,控制器会显示关键的设备运行参数或停机故障信息。

除监视,停机和控制功能外,MC 系列控制器还可进行重要的设备及操作数据的本地以及远程通信。

此高级系统提供了多种远程通信选择。

对于可编程逻辑控制器、PC 和 SCADA 系统均提供了一个串行链接。

无线电和卫星通信通过 MODBUS RTU 协议提供。

设备运行时间和历史数据趋势记录为运行分析和保养提供了有效的工具。

此外,停机快照功能能让操作人员全面了解系统停机时的完整状况。

摩菲公司 (Murphy) 可为您定制设计成套控制设备,以满足您的具体规格要求。

此外,还可提供多种非常经济实惠的预设计系统。

基本组件MC 系列由一个显示模块、一个带有连接电缆的电源,以及各种扩展模块和相应电缆组成。

控制器显示 PC 模块MCH-V-M :586 兼容处理器、100 MHz ;8MB RAM ;VFD 显示屏电源MCPS-A2:带两路模拟输出。

I/O 扩展模块C267:8 路数字输入、7 路模拟输入、电源监视、8 路数字输出。

9 – 28 伏直流,2.25 – 11.2 瓦,不包括最大 18 安的额外输出。

C277:18 路热电偶或 4 – 20 毫安电流输入。

9 至 28 伏直流,0.6 瓦C287:9 至 28 伏直流,3 – 5 瓦,包括4 – 20 毫安输出。

电缆部件MCCA72:电源线部件。

MC 系列通用规格电源输入:10 – 32 伏直流,最大 26 瓦。

操作温度:-40 至 85°C (-40 至 185°F )底座装置及VFD 显示 -40 至 85°C (-40 到185°F )。

74LVX08MTC中文资料

Parameter Min

Pb-Free 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide Package Number M14D

5

元器件交易网

74LVX08 Low Voltage Quad 2-Input AND Gate

50 PA 50 PA 4 mA

50 PA 50 PA 4 mA

r0.1

2.0

r1.0

20.0

PA PA

Noise Characteristics (Note 4)

Symbol VOLP VOLV VIHD VILD Parameter Quiet Output Maximum Dynamic VOL Quiet Output Minimum Dynamic VOL Minimum HIGH Level Dynamic Input Voltage Maximum LOW Level Dynamic Input Voltage

The LVX08 contains four 2-input AND gates. The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems.

Features

s Input voltage level translation from 5V to 3V s Ideal for low power/low noise 3.3V applications s Guaranteed simultaneous switching noise level and dynamic threshold performance

MC74LCX16373中文资料

nLE

Inputs LE1 X H H L OE1 H L L L D0:7 X L H X

Outputs O0:7 Z L H O0 LE2 X H H L

Inputs OE2 H L L L D8:15 X L H X

Outputs O8:15 Z L H O0

H = High Voltage Level; L = Low Voltage Level; Z = High Impedance State; X = High or Low Voltage Level and Transitions Are Acceptable, for ICC reasons, DO NOT FLOAT Inputsபைடு நூலகம்

MOTOROLA

2

LCX DATA BR1339 — REV 3

元器件交易网

MC74LCX16373

ABSOLUTE MAXIMUM RATINGS*

Symbol VCC VI VO Parameter DC Supply Voltage DC Input Voltage DC Output Voltage Value –0.5 to +7.0 –0.5 ≤ VI ≤ +7.0 –0.5 ≤ VO ≤ +7.0 –0.5 ≤ VO ≤ VCC + 0.5 IIK IOK DC Input Diode Current DC Output Diode Current –50 –50 +50 IO ICC IGND TSTG DC Output Source/Sink Current DC Supply Current Per Supply Pin DC Ground Current Per Ground Pin Storage Temperature Range ±50 ±100 ±100 –65 to +150 Output in 3–State Note 1. VI < GND VO < GND VO > VCC Condition Unit V V V V mA mA mA mA mA mA °C

74系列各个芯片详细介绍

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04 ┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │1413 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 7 4LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │1413 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位总线驱动器 74LS245│2019 18 17 16 15 14 13 12 11│)│DIR =1 A=>B│ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│Y = AB )│2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │1413 12 11 10 9 8│Y = AB )│2输入四正与非门 74LS 00│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │1413 12 11 10 9 8│Y = ABC )│3输入三正与非门 74LS 10│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│)│8输入与非门 74LS30│ 1 2 3 4 5 6 7│________└┬─┬─┬─┬─┬─┬─┬┘Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐2输入四或门 74LS32│1413 12 11 10 9 8│)│Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐2输入四或非门 74LS02│1413 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│1413 12 11 10 9 8│ _____)│2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐4-2-3-2与或非门 74S64 74S65(OC门)│1413 12 11 10 9 8│______________)│Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│)│_ _│ 1 2 3 4 5 6 7│Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器 74LS688│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=A B C Y1=A B B Y2=A B C Y3=A B C│1615 14 13 12 11 10 9 │)│__ _ _ ___ __ _ __│ 1 2 3 4 5 6 7 8│Y4=A B C Y5=A B C Y6=A B C Y 7=A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│1615 14 13 12 11 10 9 │)│__ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│Y0=1A 1B Y1=1A 1B Y2=1A 1B Y 3=1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器 74LS688│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│1413 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位锁存器 74LS373│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(O C)TI[DATA]SN7406六高压输出反相器(OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

HD74LV1G04AVSE中文资料

HD74LV1G04AInverterREJ03D0064-0800Rev.8.00 Mar 21, 2008DescriptionThe HD74LV1G04A has an inverter in a 5 pin package. Low voltage and high-speed operation is suitable for the battery powered products (e.g., notebook computers), and the low power consumption extends the battery life.Features• The basic gate function is lined up as Renesas uni logic series. • Supplied on emboss taping for high-speed automatic mounting. • Electrical characteristics equivalent to the HD74LV04A Supply voltage range : 1.65 to 5.5 VOperating temperature range : –40 to +85°C• All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V) All outputs V O (Max.) = 5.5 V (@V CC = 0 V)• Output current ±6 mA (@V CC = 3.0 V to 3.6 V), ±12 mA (@V CC = 4.5 V to 5.5 V) • All the logical input has hysteresis voltage for the slow transition. • Ordering InformationPart NamePackage TypePackage Code (Previous Code) Package AbbreviationTaping Abbreviation(Quantity) HD74LV1G04ACME CMPAK–5 pinPTSP0005ZC-A(CMPAK-5V) CM E (3000 pcs/reel) HD74LV1G04AVSE VSON–5 pinPUSN0005KA-A(TNP-5DV)VSE (3000 pcs/reel)Note: Please consult the sales office for the above package availability.Outline and Article IndicationOutline and Article IndicationFunction TableInput A Output YH LL H H : High levelL : Low levelPin ArrangementAbsolute Maximum RatingsItem Symbol Ratings Unit Test ConditionsSupply voltage range V CC –0.5 to 7.0 VInput voltage range *1V I –0.5 to 7.0 V–0.5 to V CC + 0.5 Output : H or LOutput voltage range *1, 2 V O –0.5 to 7.0 VV CC : OFFInput clamp current I IK –20 mA V I < 0 Output clamp current I OK ±50 mA V O < 0 or V O > V CC Continuous output current I O ±25 mA V O = 0 to V CC Continuous current through V CC or GNDI CC or I GND ±50 mAMaximum power dissipationat Ta = 25°C (in still air) *3P T 200 mW Storage temperature Tstg–65 to 150°CNotes: The absolute maximum ratings are values, which must not individually be exceeded, and furthermore no twoof which may be realized at the same time.1. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings areobserved.2. This value is limited to 5.5 V maximum.3. The maximum package power dissipation was calculated using a junction temperature of 150°C.Recommended Operating ConditionsItem Symbol Min Max Unit ConditionsSupply voltage range V CC 1.65 5.5 V Input voltage range V I 0 5.5 V Output voltage range V O 0 V CC V— 1 V CC = 1.65 to 1.95 V — 2 V CC = 2.3 to 2.7 V— 6 V CC = 3.0 to 3.6 V I OL— 12 V CC = 4.5 to 5.5 V— –1 V CC = 1.65 to 1.95 V — –2 V CC = 2.3 to 2.7 V— –6 V CC = 3.0 to 3.6 V Output current I OH— –12 mAV CC = 4.5 to 5.5 V 0 300 V CC = 1.65 to 1.95 V 0 200 V CC = 2.3 to 2.7 V0 100 V CC = 3.0 to 3.6 V Input transition rise or fall rate ∆t / ∆v 0 20 ns / VV CC = 4.5 to 5.5 V Operating free-air temperatureT a –40 85 °CNote: Unused or floating inputs must be held high or low.• Ta = –40 to 85°CItem Symbol V CC (V) * Min Typ Max Unit Test condition1.65 to 1.95 V CC ×0.75 — —2.3 to 2.7 V CC ×0.7 — —3.0 to 3.6 V CC ×0.7 — — V IH4.5 to5.5 V CC ×0.7 — —1.65 to 1.95 — — V CC ×0.252.3 to 2.7 — — V CC ×0.33.0 to 3.6 — — V CC ×0.3 Input voltage V IL4.5 to5.5 — — V CC ×0.3 V1.8 — 0.25 —2.5 — 0.30 —3.3 — 0.35 —Hysteresis voltage V H 5.0 — 0.45 — V V T + – V T –Min to Max V CC –0.1 — — I OH = –50 µA1.65 1.4 — — I OH = –1 mA2.3 2.0 — —I OH = –2 mA 3.0 2.48 — —I OH = –6 mA V OH4.5 3.8 — —I OH = –12 mAMin to Max — — 0.1I OL = 50 µA 1.65 — — 0.3 I OL = 1 mA 2.3 — — 0.4 I OL = 2 mA 3.0 — — 0.44I OL = 6 mAOutput voltageV OL4.5 — — 0.55 VI OL = 12 mA Input current I IN0 to 5.5 — — ±1 µA V IN = 5.5 V or GNDQuiescent supply current I CC 5.5 — — 10 µAV IN = V CC or GND,I O = 0Output leakage currentI OFF 0 — — 5 µA V IN or V O = 0 to 5.5 V Input capacitanceC IN 3.3 — 3.0 — pF V IN = V CC or GNDNote: For conditions shown as Min or Max, use the appropriate values under recommended operating conditions.• V CC = 1.8 ± 0.15 VTa = 25°C Ta = –40 to 85°CItem Symbol Min Typ Max Min Max UnitTestConditions FROM (Input) TO (Output)— 12.6 22.0 1.0 24.0 C L = 15 pF Propagation delay time t PLHt PHL — 19.7 33.0 1.0 36.0 nsC L = 50 pFAY• V CC = 2.5 ± 0.2 VTa = 25°C Ta = –40 to 85°CItem Symbol Min Typ Max Min Max UnitTestConditions FROM (Input) TO (Output)— 7.0 11.7 1.0 14.0 C L = 15 pF Propagation delay time t PLHt PHL — 10.5 15.5 1.0 18.0 nsC L = 50 pFAY• V CC = 3.3 ± 0.3 VTa = 25°C Ta = –40 to 85°CItem Symbol Min Typ Max Min Max UnitTestConditions FROM (Input) TO (Output)— 5.0 7.1 1.0 8.5 C L = 15 pF Propagation delay time t PLHt PHL — 7.5 10.6 1.0 12.0 nsC L = 50 pFAY• V CC = 5.0 ± 0.5 VTa = 25°C Ta = –40 to 85°CItem Symbol Min Typ Max Min Max UnitTestConditions FROM (Input) TO (Output)— 3.8 5.5 1.0 6.5C L = 15 pF Propagation delay time t PLH t PHL— 5.3 7.5 1.0 8.5nsC L = 50 pFAYOperating Characteristics• C L = 50 pFTa = 25°CItem Symbol V CC (V)Min Typ MaxUnit Test Conditions3.3 — 8.5 —Power dissipationcapacitanceC PD5.0 — 10.0 —pFf = 10 MHzTest CircuitWaveformsPackage DimensionsRefer to "/en/network " for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology (Shanghai) Co., Ltd.Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145Renesas Technology Malaysia Sdn. BhdUnit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510RENESAS SALES OFFICES。

MC74ACT74MELG资料

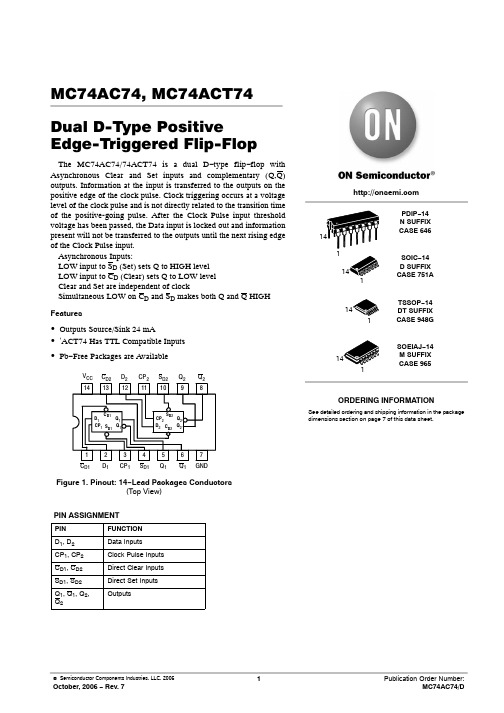

MC74AC74, MC74ACT74 Dual D−Type PositiveEdge−Triggered Flip−FlopThe MC74AC74/74ACT74 is a dual D−type flip−flop with Asynchronous Clear and Set inputs and complementary (Q,Q) outputs. Information at the input is transferred to the outputs on the positive edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive-going pulse. After the Clock Pulse input threshold voltage has been passed, the Data input is locked out and information present will not be transferred to the outputs until the next rising edge of the Clock Pulse input.Asynchronous Inputs:LOW input to S D (Set) sets Q to HIGH levelLOW input to C D (Clear) sets Q to LOW levelClear and Set are independent of clockSimultaneous LOW on C D and S D makes both Q and Q HIGH Features•Outputs Source/Sink 24 mA•′ACT74 Has TTL Compatible Inputs•Pb−Free Packages are AvailableV C S QFigure 1. Pinout: 14−Lead Packages Conductors(Top View)PIN ASSIGNMENTPIN FUNCTIOND1, D2Data InputsCP1, CP2Clock Pulse InputsC D1, C D2Direct Clear InputsS D1, S D2Direct Set InputsQ1, Q1, Q2, Q2OutputsSee detailed ordering and shipping information in the packagedimensions section on page 7 of this data sheet.ORDERING INFORMATIONNOTE:H = HIGH Voltage LevelL = LOW Voltage LevelX = Immaterial;= LOW-to-HIGH Clock TransitionQ0(Q0) = Previous Q(Q) before LOW-to-HIGHTransition of Clock Figure 2. Logic SymbolS D D CPC DQQ Figure 3. Logic DiagramNOTE:This diagram is provided only for the understanding oflogic operations and should not be used to estimatepropagation delays.MAXIMUM RATINGSSymbol Parameter Value UnitV CC DC Supply Voltage (Referenced to GND)−0.5 to +7.0VV in DC Input Voltage (Referenced to GND)−0.5 to V CC +0.5VV out DC Output Voltage (Referenced to GND)−0.5 to V CC +0.5VI in DC Input Current, per Pin±20mAI out DC Output Sink/Source Current, per Pin±50mAI CC DC V CC or GND Current per Output Pin±50mAT stg Storage Temperature−65 to +150°C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above theRecommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max UnitV CC Supply Voltage′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5V in, V out DC Input Voltage, Output Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note )′AC Devices except Schmitt Inputs V CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/V V CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note )′ACT Devices except Schmitt Inputs V CC @ 4.5 V−10−ns/V V CC @ 5.5 V−8.0−T J Junction Temperature (PDIP)−−140°C T A Operating Ambient Temperature Range−402585°C I OH Output Current − High−−−24mAI OL Output Current − Low−−24mA1.V in from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V in from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 3.0 1.5 2.1 2.1V OUT = 0.1 V4.5 2.25 3.15 3.15V or V CC− 0.1 V5.5 2.75 3.85 3.85V IL Maximum Low LevelInput Voltage 3.0 1.50.90.9V OUT = 0.1 V4.5 2.25 1.35 1.35V or V CC− 0.1 V5.5 2.75 1.65 1.65V OH Minimum High LevelOutput Voltage 3.0 2.99 2.9 2.9I OUT = −50 m A4.5 4.49 4.4 4.4V5.5 5.49 5.4 5.4V*V IN = V IL or V IH3.0− 2.56 2.46−12 mA4.5− 3.86 3.76I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 3.00.0020.10.1I OUT = 50 m A4.50.0010.10.1V5.50.0010.10.1V*V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0m A V I = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CC.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74AC74ACUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxf max Maximum ClockFrequency3.3100125−95−MHz3−35.0140160−125−t PLH Propagation DelayC Dn or S Dn to Q n or Q n3.3 5.08.012.54.013.0ns3−65.0 3.56.09.0 3.010.0t PHL Propagation DelayC Dn or S Dn to Q n or Q n3.34.010.512.0 3.513.5ns3−65.0 3.08.09.5 2.510.5t PLH Propagation DelayC Pn to Q n or Q n3.34.58.013.5 4.016.0ns3−65.0 3.56.010.0 3.010.5t PHL Propagation DelayC Pn to Q n or Q n3.3 3.58.014.0 3.514.5ns3−65.0 2.56.010.0 2.510.5*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V.AC OPERATING REQUIREMENTSSymbol Parameter V CC*(V)74AC74ACUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFTyp Guaranteed Minimumt s Set-up Time, HIGH or LOW 3.3 1.5 4.0 4.5ns3−9 D n to CP n 5.0 1.0 3.0 3.0t h Hold Time, HIGH or LOW 3.3−2.00.50.5ns3−9 D n to CP n 5.0−1.50.50.5t w C Pn or C Dn or S Dn 3.3 3.0 5.57.0ns3−6 Pulse Width 5.0 2.5 4.5 5.0t rec Recovery TIme 3.3−2.500ns3−9 C Dn or S Dn to CP 5.0−2.000*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V.DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 4.5 1.5 2.0 2.0VV OUT = 0.1 V 5.5 1.5 2.0 2.0or V CC− 0.1 VV IL Maximum Low LevelInput Voltage 4.5 1.50.80.8VV OUT = 0.1 V 5.5 1.50.80.8or V CC− 0.1 VV OH Minimum High LevelOutput Voltage 4.5 4.49 4.4 4.4VI OUT = −50 m A5.5 5.49 5.4 5.4*V IN = V IL or V IH4.5− 3.86 3.76VI OH−24 mA 5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 4.50.0010.10.1VI OUT = 50 m A5.50.0010.10.1*V IN = V IL or V IH4.5−0.360.44VI OL24 mA 5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0m A V I = V CC, GND D I CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC−2.1 VI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74ACT74ACTUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxf max Maximum ClockFrequency5.0145210−125−MHz3−3t PLH Propagation DelayC Dn or S Dn to Q n or Q n5.0 3.0 5.59.5 2.510.5ns3−6t PHL Propagation DelayC Dn or S Dn to Q n or Q n5.0 3.06.010.0 3.011.5ns3−6t PLH Propagation DelayC Pn to Q n or Q n5.0 4.07.511.0 4.013.0ns3−6t PHL Propagation DelayC Pn to Q n or Q n5.0 3.56.010.0 3.011.5ns3−6 *Voltage Range 5.0 V is 5.0 V ±0.5 V.AC OPERATING REQUIREMENTSSymbol Parameter V CC*(V)74ACT74ACTUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFTyp Guaranteed Minimumt s Set-up Time, HIGH or LOW5.0 1.0 3.0 3.5ns3−9D n to CP nt h Hold Time, HIGH or LOW5.0−0.5 1.0 1.0ns3−9D n to CP nt w C Pn or C Dn or S Dn5.0 3.0 5.06.0ns3−6 Pulse Widtht rec Recovery TIme5.0−2.500ns3−9C Dn or S Dn to CP*Voltage Range 5.0 V is 5.0 V ±0.5 V. CAPACITANCESymbol Parameter ValueTyp Unit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 V C PD Power Dissipation Capacitance35pF V CC = 5.0 VORDERING INFORMATIONDevicePackage Shipping †MC74AC74N PDIP −1425 Units/RailMC74AC74NG PDIP −14(Pb −Free)MC74ACT74N PDIP −14MC74ACT74NG PDIP −14(Pb −Free)MC74AC74D SOIC −1455 Units/Rail MC74AC74DG SOIC −14(Pb −Free)MC74AC74DR2SOIC −142500/Tape & Reel MC74AC74DR2G SOIC −14(Pb −Free)MC74ACT74D SOIC −1455 Units/Rail MC74ACT74DG SOIC −14(Pb −Free)MC74ACT74DR2SOIC −142500/Tape & Reel MC74ACT74DR2G SOIC −14(Pb −Free)MC74AC74DT TSSOP −14*96 Units/Rail MC74AC74DTR2TSSOP −14*2500/Tape & Reel MC74AC74DTR2G TSSOP −14*MC74ACT74DT TSSOP −14*96 Units/Rail MC74ACT74DTR2TSSOP −14*2500/Tape & Reel MC74ACT74DTR2G TSSOP −14*MC74AC74MEL SOEIAJ −142000/Tape & ReelMC74AC74MELG SOEIAJ −14(Pb −Free)MC74ACT74MEL SOEIAJ −14MC74ACT74MELGSOEIAJ −14(Pb −Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MARKING DIAGRAMSA = Assembly Location WL, L = Wafer Lot YY, Y = YearWW, W = Work WeekG or G = Pb −Free PackagePDIP −14SOIC −14TSSOP −14MC74AC74N AWLYYWWGAC 74ALYW G GMC74ACT74N AWLYYWWG74AC74ALYWGSOEIAJ −1474ACT74ALYWGACT 74ALYW G G (Note: Microdot may be in either location)PACKAGE DIMENSIONSPDIP−14CASE 646−06ISSUE PSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.11PACKAGE DIMENSIONSTSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BEDETERMINED AT DATUM PLANE −W −.____14X REF K14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOEIAJ −14CASE 965−01ISSUE ANOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74系列功能大全(中文)

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。