OPA742W23;中文规格书,Datasheet资料

PTH08T230WAZ;PTH08T230WAD;PTH08T231WAD;PTH08T231WAZ;PTH08T230WAS;中文规格书,Datasheet资料

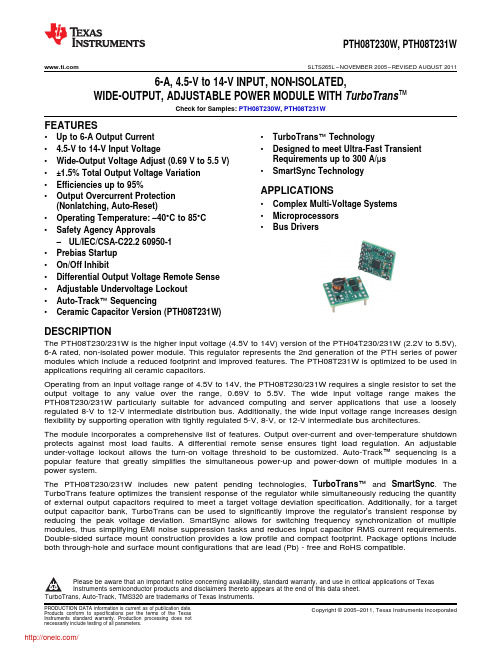

PTH08T230W,PTH08T231W SLTS265L–NOVEMBER2005–REVISED AUGUST20116-A,4.5-V to14-V INPUT,NON-ISOLATED,WIDE-OUTPUT,ADJUSTABLE POWER MODULE WITH TurboTrans™Check for Samples:PTH08T230W,PTH08T231WFEATURES•Up to6-A Output Current•TurboTrans™Technology• 4.5-V to14-V Input Voltage•Designed to meet Ultra-Fast TransientRequirements up to300A/µs•Wide-Output Voltage Adjust(0.69V to5.5V)•SmartSync Technology•±1.5%Total Output Voltage Variation•Efficiencies up to95%APPLICATIONS•Output Overcurrent Protection•Complex Multi-Voltage Systems (Nonlatching,Auto-Reset)•Microprocessors•Operating Temperature:–40°C to85°C•Bus Drivers•Safety Agency Approvals–UL/IEC/CSA-C22.260950-1•Prebias Startup•On/Off Inhibit•Differential Output Voltage Remote Sense•Adjustable Undervoltage Lockout•Auto-Track™Sequencing•Ceramic Capacitor Version(PTH08T231W)DESCRIPTIONThe PTH08T230/231W is the higher input voltage(4.5V to14V)version of the PTH04T230/231W(2.2V to5.5V), 6-A rated,non-isolated power module.This regulator represents the2nd generation of the PTH series of power modules which include a reduced footprint and improved features.The PTH08T231W is optimized to be used in applications requiring all ceramic capacitors.Operating from an input voltage range of4.5V to14V,the PTH08T230/231W requires a single resistor to set the output voltage to any value over the range,0.69V to 5.5V.The wide input voltage range makes the PTH08T230/231W particularly suitable for advanced computing and server applications that use a loosely regulated8-V to12-V intermediate distribution bus.Additionally,the wide input voltage range increases design flexibility by supporting operation with tightly regulated5-V,8-V,or12-V intermediate bus architectures.The module incorporates a comprehensive list of features.Output over-current and over-temperature shutdown protects against most load faults.A differential remote sense ensures tight load regulation.An adjustable under-voltage lockout allows the turn-on voltage threshold to be customized.Auto-Track™sequencing is a popular feature that greatly simplifies the simultaneous power-up and power-down of multiple modules in a power system.The PTH08T230/231W includes new patent pending technologies,TurboTrans™and SmartSync.The TurboTrans feature optimizes the transient response of the regulator while simultaneously reducing the quantity of external output capacitors required to meet a target voltage deviation specification.Additionally,for a target output capacitor bank,TurboTrans can be used to significantly improve the regulator's transient response by reducing the peak voltage deviation.SmartSync allows for switching frequency synchronization of multiple modules,thus simplifying EMI noise suppression tasks and reduces input capacitor RMS current requirements. Double-sided surface mount construction provides a low profile and compact footprint.Package options include both through-hole and surface mount configurations that are lead(Pb)-free and RoHS compatible.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.TurboTrans,Auto-Track,TMS320are trademarks of Texas Instruments.PTH08T230W,PTH08T231WSLTS265L –NOVEMBER 2005–REVISED AUGUST 2011This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PTH08T230WA.R SET required to set the output voltage to a value higher than 0.69V.See the Electrical Characteristics table.B.An additional 22-μF ceramic input capacitor is recommended to reduce RMS ripple current.C.For V I greater than 8V,the minimum required C I may be reduced to 220μF plus a 22-μF ceramic capacitor.D.200μF of output capacitance can be achieved by using two 100-μF ceramic capacitors or four 47-μF ceramic capacitors.PTH08T230W,PTH08T231W SLTS265L–NOVEMBER2005–REVISED AUGUST2011PTH08T231W-Ceramic Capacitor VersionA.R SET required to set the output voltage to a value higher than0.69V.See the Electrical Characteristics table.B.200μF of output capacitance can be achieved by using two100-μF ceramic capacitors or four47-μF ceramiccapacitors.C.300µF of ceramic or330µF of electrolytic input capacitance is required for proper operation.D.For V I greater than8V,the minimum required C I may be reduced to200µF ceramic or220μF electrolytic plus a22-μF ceramic capacitor.PTH08T230W,PTH08T231WSLTS265L–NOVEMBER2005–REVISED ORDERING INFORMATIONFor the most current package and ordering information,see the Package Option Addendum at the end of this data sheet,or see the TI website at .DATASHEET TABLE OF CONTENTSDATASHEET SECTION PAGE NUMBER ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS3ELECTRICAL CHARACTERISTICS TABLE(PTH08T230W)4ELECTRICAL CHARACTERISTICS TABLE(PTH08T231W)6PIN-OUT AND TERMINAL FUNCTIONS8TYPICAL CHARACTERISTICS(V I=12V)9TYPICAL CHARACTERISTICS(V I=5V)10ADJUSTING THE OUTPUT VOLTAGE11CAPACITOR RECOMMENDATIONS13TURBOTRANS™INFORMATION17 UNDERVOLTAGE LOCKOUT(UVLO)22SOFT-START POWER-UP23OVER-CURRENT PROTECTION23OVER-TEMPERATURE PROTECTION23OUTPUT ON/OFF INHIBIT24REMOTE SENSE24 SYCHRONIZATION(SMARTSYNC)25AUTO-TRACK SEQUENCING26PREBIAS START-UP29TAPE&REEL AND TRAY DRAWINGS31ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS(Voltages are with respect to GND)UNIT V Track Track pin voltage–0.3to V I+0.3VV SYNC SYNC pin voltage–0.3to6.0VT A Operating temperature range Over V I range–40to85Surface temperature of module body or pinsT wave Wave soldering temperature AD suffix260(5seconds maximum)AS suffix235(1)°CT reflow Solder reflow temperature Surface temperature of module body or pinsAZ suffix260(1)T stg Storage temperature Storage temperature of module removed from shipping package–55to125T pkg Packaging temperature Shipping Tray or Tape and Reel storage or bake temperature45 Mechanical shock Per Mil-STD-883D,Method2002.3,1msec,1/2sine,mounted500Suffix AD20G Mechanical vibration Mil-STD-883D,Method2007.2,20-2000HzSuffix AS and AZ15 Weight 2.5grams Flammability Meets UL94V-O(1)During reflow of surface mount package version do not elevate peak temperature of the module,pins or internal components above thestated maximum.PTH08T230W,PTH08T231W SLTS265L–NOVEMBER2005–REVISED AUGUST2011ELECTRICAL CHARACTERISTICST A=25°C,V I=5V,V O=3.3V,C I=330µF,C O1=200µF ceramic,C O2=100µF,I O=I O max(unless otherwise stated) PARAMETER TEST CONDITIONS PTH08T230WMIN TYP MAX UNITI O Output current Over V O range25°C,natural convection06A0.69≤V O≤1.2 4.514(1)V I Input voltage range Over I O range 1.2<V O≤3.6 4.514V3.6<V O≤5.5V O+1(2)14Output adjust range Over I O range0.69 5.5VSet-point voltage tolerance±1.0(3)%V o Temperature variation–40°C<T A<85°C±0.25%V oV OLine regulaltion Over V I range±3mVLoad regulation Over I O range±2mVTotal output variation Includes set-point,line,load,–40°C≤T A≤85°C±1.5(3)%V OR SET=169Ω,V I=8.0V,V O=5.0V95%R SET=1.21kΩ,V O=3.3V92%R SET=2.37kΩ,V O=2.5V90%R SET=4.75kΩ,V O=1.8V88%ηEfficiency I O=6AR SET=6.98kΩ,V O=1.5V87%R SET=12.1kΩ,V O=1.2V85%R SET=20.5kΩ,V O=1.0V83%R SET=681kΩ,V O=0.7V79% V O Ripple(peak-to-peak)20-MHz bandwidth1(1)%V OI LIM Overcurrent threshold Reset,followed by auto-recovery10ARecovery Time70µSecw/o TurboTransC O1=200μF,ceramic VOOvershoot150mVw/o TurboTrans(4)Recovery Time100µSec2.5A/µs load step CO 1=200μF,ceramicTransient response50%to100%I O max V O Overshoot100mVC O2=330μF,Type BV O=2.5Vwith TurboTrans Recovery Time150µSecC O1=200μF,ceramicC O2=330μF,Type B VO Overshoot60mVR TT=11.3kΩI IL Track input current(pin9)Pin to GND-130(5)µA dV track/dt Track slew rate capability C O≤C O(max)1V/msV I increasing,R UVLO=OPEN 4.3 4.45Adjustable Under-voltage lockoutUVLO ADJ V I decreasing,R UVLO=OPEN 3.7 4.2V (pin10)Hysteresis,R UVLO≤52.3kΩ0.5Input high voltage(V IH)Open(6)V Inhibit control(pin10)Input low voltage(V IL)-0.20.6Input low current(I IL),Pin10to GND235µAI in Input standby current Inhibit(pin10)to GND,Track(pin9)open5mAf s Switching frequency Over V I and I O ranges,SmartSync(pin1)to GND300kHz(1)For output voltages≤1.2V,at nominal operating frequency,the output ripple may increase(typically2×)when operating at inputvoltages greater than(V O×11).When using the SmartSync feature to adjust the switching frequency,see the SmartSyncConsiderations section of the datasheet for further guidance.(2)The minimum input voltage is4.5V or(V O+1)V,whichever is greater.Additional input capacitance may be required when V I<(V O+2)V.(3)The set-point voltage tolerance is affected by the tolerance and stability of R SET.The stated limit is unconditionally met if R SET has atolerance of1%with100ppm/°C or better temperature stability.(4)Without TurboTrans,the minimum ESR limit of7mΩmust not be violated.(5)A low-leakage(<100nA),open-drain device,such as MOSFET or voltage supervisor device,is recommended to control pin9.Theopen-circuit voltage is less than6.5Vdc.(6)This control pin has an internal pull-up.Do not place an external pull-up on this pin.If it is left open-circuit,the module operates wheninput power is applied.A small,low-leakage(<100nA)MOSFET is recommended for control.For additional information,see the related application information section.PTH08T230W,PTH08T231WSLTS265L–NOVEMBER2005–REVISED ELECTRICAL CHARACTERISTICS(continued)T A=25°C,V I=5V,V O=3.3V,C I=330µF,C O1=200µF ceramic,C O2=100µF,I O=I O max(unless otherwise stated) PARAMETER TEST CONDITIONS PTH08T230WMIN TYP MAX UNITf SYNC Synchronization(SYNC)frequency240400kHzV SYNCH SYNC High-Level Input Voltage2 5.5VSmartSync ControlV SYNCL SYNC Low-Level Input Voltage0.8Vt SYNC SYNC Minimum Pulse Width200nSecC I External input capacitance330(7)µFNonceramic0(8)1005000(9)Capacitance valueµFwithoutCeramic200(8)500TurboTransEquivalent series resistance(non-ceramic)7mΩC O External output capacitancesee table10,000Capacitance valueμFwith(10)(11)TurbotransCapacitance×ESR product(C O×ESR)100010,000μF×mΩPer Telcordia SR-332,50%stress,MTBF Reliability 6.7106HrT A=40°C,ground benign(7)A330µF electrolytic input capacitor is required for proper operation.The capacitor must be rated for a minimum of450mA rms of ripplecurrent.An additional22-μF ceramic input capacitor is recommended to reduce rms ripple current.When operating at V I>8V,the minimum required C I may be reduced to a220-μF electrolytic plus a22-μF ceramic.(8)200µF ceramic external output capacitance is required for basic operation.The required ceramic output capacitance can be made up of2×100µF or4×47µF.The minimum output capacitance requirement increases when TurboTrans™(TT)technology is used.See the Application Information for more guidance.(9)This is the calculated maximum disregarding TurboTrans™technology.When the TurboTrans feature is used,the minimum outputcapacitance must be increased.See the TurboTrans application notes for further guidance.(10)When using TurboTrans™technology,a minimum value of output capacitance is required for proper operation.Additionally,low ESRcapacitors are required for proper operation.See the TurboTrans application notes for further guidance.(11)This is the calaculated maximum when using the TurboTrans feature.Additionally,low ESR capacitors are required for proper operation.See the TurboTrans application notes for further guidance.PTH08T230W,PTH08T231W SLTS265L–NOVEMBER2005–REVISED AUGUST2011ELECTRICAL CHARACTERISTICST A=25°C,V I=5V,V O=3.3V,C I=330µF,C O1=200µF ceramic,and I O=I O max(unless otherwise stated) PARAMETER TEST CONDITIONS PTH08T231WMIN TYP MAX UNITI O Output current Over V O range25°C,natural convection06A0.69≤V O≤1.2 4.514(1)V I Input voltage range Over I O range 1.2<V O≤3.6 4.514V3.6<V O≤5.5V O+1(2)14Output adjust range Over I O range0.69 5.5VSet-point voltage tolerance±1.0(3)%V o Temperature variation–40°C<T A<85°C±0.25%V oV OLine regulaltion Over V I range±3mVLoad regulation Over I O range±2mVTotal output variation Includes set-point,line,load,–40°C≤T A≤85°C±1.5(3)%V OR SET=169Ω,V I=8.0V,V O=5.0V95%R SET=1.21kΩ,V O=3.3V92%R SET=2.37kΩ,V O=2.5V90%R SET=4.75kΩ,V O=1.8V88%ηEfficiency I O=6AR SET=6.98kΩ,V O=1.5V87%R SET=12.1kΩ,V O=1.2V85%R SET=20.5kΩ,V O=1.0V83%R SET=681kΩ,V O=0.7V79% V O Ripple(peak-to-peak)20-MHz bandwidth1(1)%V OI LIM Overcurrent threshold Reset,followed by auto-recovery10ARecovery Time80µSecw/o TurboTransC O1=200μF,ceramic VO Overshoot85mV2.5A/µs load stepRecovery Time120µSec w/o TurboTrans(4)50%to100%I O max Transient response CO 1=400μF,ceramicV I=12V V O Overshoot75mVV O=3.3Vwith TurboTrans Recovery Time220µSecC O1=400μF,ceramicV O Overshoot45mVR TT=8.06kΩI IL Track input current(pin9)Pin to GND-130(5)µA dV track/dt Track slew rate capability C O≤C O(max)1V/msV I increasing,R UVLO=OPEN 4.3 4.45Adjustable Under-voltage lockoutUVLO ADJ V I decreasing,R UVLO=OPEN 3.7 4.2V (pin10)Hysteresis,R UVLO≤52.3kΩ0.5Input high voltage(V IH)Open(6)V Inhibit control(pin10)Input low voltage(V IL)-0.20.6Input low current(I IL),Pin10to GND235µAI in Input standby current Inhibit(pin10)to GND,Track(pin9)open5mAf s Switching frequency Over V I and I O ranges,SmartSync(pin1)to GND300kHzf SYNC Synchronization(SYNC)frequency240400kHzV SYNCH SYNC High-Level Input Voltage2 5.5VSmartSync ControlV SYNCL SYNC Low-Level Input Voltage0.8Vt SYNC SYNC Minimum Pulse Width200nSec(1)For output voltages≤1.2V,at nominal operating frequency,the output ripple may increase(typically2×)when operating at inputvoltages greater than(V O×11).When using the SmartSync feature to adjust the switching frequency,see the SmartSyncConsiderations section of the datasheet for further guidance.(2)The minimum input voltage is4.5V or(V O+1)V,whichever is greater.Additional input capacitance may be required when V I<(V O+2)V.(3)The set-point voltage tolerance is affected by the tolerance and stability of R SET.The stated limit is unconditionally met if R SET has atolerance of1%with100ppm/°C or better temperature stability.(4)Without TurboTrans,the minimum ESR limit of7mΩmust not be violated.(5)A low-leakage(<100nA),open-drain device,such as MOSFET or voltage supervisor device,is recommended to control pin9.Theopen-circuit voltage is less than6.5Vdc.(6)This control pin has an internal pull-up.Do not place an external pull-up on this pin.If it is left open-circuit,the module operates wheninput power is applied.A small,low-leakage(<100nA)MOSFET is recommended for control.For additional information,see the related application information section.PTH08T230W,PTH08T231WSLTS265L–NOVEMBER2005–REVISED ELECTRICAL CHARACTERISTICS(continued)T A=25°C,V I=5V,V O=3.3V,C I=330µF,C O1=200µF ceramic,and I O=I O max(unless otherwise stated) PARAMETER TEST CONDITIONS PTH08T231WMIN TYP MAX UNITC I External input capacitance300(7)µFwithoutCapacitance value Ceramic200(8)5000µFTurboTransC O External output capacitance see tableCapacitance value Ceramic5000(10)μFwith(9)TurbotransCapacitance×ESR product(C O×ESR)1001000μF×mΩPer Telcordia SR-332,50%stress,MTBF Reliability 6.7106HrT A=40°C,ground benign(7)300µF of ceramic or330µF of electrolytic input capacitance is required for proper operation.Electrolytic capacitance must be rated fora minimum of450mA rms of ripple current.An additional22-μF ceramic input capacitor is recommended to reduce rms ripple current.(8)200µF ceramic external output capacitance is required for basic operation.The required ceramic output capacitance can be made up of2×100µF or4×47µF.The minimum output capacitance requirement increases when TurboTrans™(TT)technology is used.See the Application Information for more guidance.(9)When using TurboTrans™technology,a minimum value of output capacitance is required for proper operation.Additionally,low ESRcapacitors are required for proper operation.See the TurboTrans application notes for further guidance.(10)This is the calaculated maximum when using the TurboTrans feature.Additionally,low ESR capacitors are required for proper operation.See the TurboTrans application notes for further guidance.11097654382PTH08T230W,PTH08T231WSLTS265L –NOVEMBER 2005–REVISED AUGUST 2011PTH08T230/231W (TOP VIEW)TERMINAL FUNCTIONSTERMINALDESCRIPTIONNAME NO.V I 2The positive input voltage power node to the module,which is referenced to common GND.V O 4The regulated positive power output with respect to the GND.This is the common ground connection for the V I and V O power connections.It is also the 0Vdc reference for GND3the control inputs.The Inhibit pin is an open-collector/drain,negative logic input that is referenced to GND.Applying a low level ground signal to this input disables the module ’s output and turns off the output voltage.When the Inhibit control is active,the input current drawn by the regulator is significantly reduced.If the Inhibit pin is left open-circuit,the Inhibit and module produces an output whenever a valid input source is applied.10UVLO (1)This pin is also used for input undervoltage lockout (UVLO)programming.Connecting a resistor from this pin to GND (pin 3)allows the ON threshold of the UVLO to be adjusted higher than the default value.For more information,see the Application Information section.A 0.05W 1%resistor must be directly connected between this pin and pin 6(–Sense)to set the output voltage to a value higher than 0.69V.The temperature stability of the resistor should be 100ppm/°C (or better).The setpoint range for the output voltage is from 0.69V to 5.5V.If left open circuit,the output voltage will default to V O Adjust7its lowest value.For further information,on output voltage adjustment see the related application note.The specification table gives the preferred resistor values for a number of standard output voltages.The sense input allows the regulation circuit to compensate for voltage drop between the module and the load.+Sense 5For optimal voltage accuracy,+Sense must be connected to V O ,close to the load.The sense input allows the regulation circuit to compensate for voltage drop between the module and the load.–Sense6For optimal voltage accuracy,–Sense must be connected to GND (pin 3),very close to the module (within 10cm).This is an analog control input that enables the output voltage to follow an external voltage.This pin becomes active typically 20ms after the input voltage has been applied,and allows direct control of the output voltage from 0V up to the nominal set-point voltage.Within this range the module 's output voltage follows the voltage at Track 9the Track pin on a volt-for-volt basis.When the control voltage is raised above this range,the module regulates at its set-point voltage.The feature allows the output voltage to rise simultaneously with other modules powered from the same input bus.If unused,this input should be connected to V I .NOTE:Due to the undervoltage lockout feature,the output of the module cannot follow its own input voltage during power up.For more information,see the related application note.This input pin adjusts the transient response of the regulator.To activate the TurboTrans feature,a 1%,0.05W resistor must be connected between this pin and pin 5(+Sense)very close to the module.For a given value of output capacitance,a reduction in peak output voltage deviation is achieved by using this feature.If unused,this TurboTrans ™8pin must be left open-circuit.The resistance requirement can be selected from the TurboTrans resistor table in the Application Information section.External capacitance must never be connected to this pin unless the TurboTrans resistor is a short,0Ω.This input pin sychronizes the switching frequency of the module to an external clock frequency.The SmartSync feature can be used to sychronize the switching fequency of multiple PTH08T230/231W modules,aiding EMI SmartSync 1noise suppression efforts.If unused,this pin should be connected to GND (pin 3).For more information,please review the Application Information section.(1)Denotes negative logic:Open =Normal operation,Ground =Function activeI O −Output Current −A0.51.512.5−P o w e r D i s s i p a t i o n −WP D 2E f f i c i e n c y −%I O −Output Current −AI −Output Current −AO V O u t p u t V o l t a g e R i p p l e −V (m V )O P P −T A −A m b i e n t T e m p e r a t u r e −Co I O −Output Current −AT A −A m b i e n t T e m p e r a t u r e −Co I O −Output Current −AT A −A m b i e n t T e m p e r a t u r e −Co I O −Output Current −APTH08T230W,PTH08T231WSLTS265L –NOVEMBER 2005–REVISED AUGUST 2011TYPICAL CHARACTERISTICS (1)(2)CHARACTERISTIC DATA (V I =12V)EFFICIENCYOUTPUT RIPPLEPOWER DISSIPATIONvsvsvsOUTPUT CURRENTOUTPUT CURRENTOUTPUT CURRENTFigure 1.Figure 2.Figure 3.AMBIENT TEMPERATUREAMBIENT TEMPERATUREAMBIENT TEMPERATUREvsvsvsOUTPUT CURRENTOUTPUT CURRENTOUTPUT CURRENTFigure 4.Figure 5.Figure 6.(1)The electrical characteristic data has been developed from actual products tested at 25°C.This data is considered typical for the converter.Applies to Figure 1,Figure 2,and Figure 3.(2)The temperature derating curves represent the conditions at which internal components are at or below the manufacturer 's maximum operating temperatures.Derating limits apply to modules soldered directly to a 100mm x 100mm double-sided PCB with 2oz.copper.Applies to Figure 4,Figure 5and Figure 6.分销商库存信息:TIPTH08T230WAZ PTH08T230WAD PTH08T231WAD PTH08T231WAZ PTH08T230WAS PTH08T230WAST PTH08T230WAZT PTH08T231WAS。

AZ742中文资料

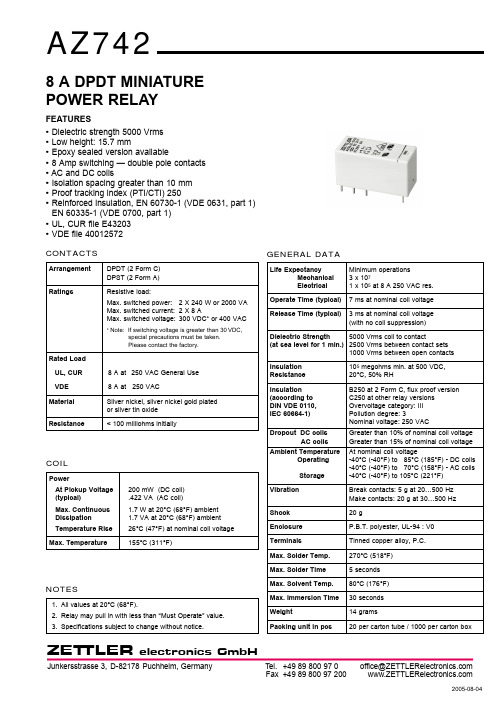

GENERAL DATALife ExpectancyMinimum operations Mechanical 3 x 107Electrical 1 x 105at 8 A 250 VAC res.Operate Time (typical)7 ms at nominal coil voltage Release Time (typical)3 ms at nominal coil voltage (with no coil suppression)Dielectric Strength 5000 Vrms coil to contact(at sea level for 1 min.)2500 Vrms between contact sets1000 Vrms between open contacts Insulation 105megohms min. at 500 VDC,Resistance 20°C, 50% RHInsulation B250 at 2 Form C, flux proof version (according to C250 at other relay versions DIN VDE 0110, Overvoltage category: III IEC 60664-1)Pollution degree: 3Nominal voltage: 250 VACDropout DC coilsGreater than 10% of nominal coil voltage AC coilsGreater than 15% of nominal coil voltage Ambient TemperatureAt nominal coil voltageOperating-40°C (-40°F) to 85°C (185°F) - DC coils -40°C (-40°F) to 70°C (158°F) - AC coils Storage-40°C (-40°F) to 105°C (221°F)Vibration Break contacts: 5 g at 20…500 Hz Make contacts: 20 g at 30…500 Hz Shock 20 gEnclosure P.B.T. polyester, UL-94 : V0TerminalsTinned copper alloy, P.C.Max. Solder Temp.270°C (518°F)Max. Solder Time5 seconds Max. Solvent Temp.80°C (176°F)Max. Immersion Time 30 seconds Weight14 gramsPacking unit in pcs20 per carton tube / 1000 per carton boxZET TLER8 A DPDT MINIATURE POWER RELAYFEATURES •Dielectric strength 5000 Vrms •Low height: 15.7 mm•Epoxy sealed version available•8 Amp switching — double pole contacts •AC and DC coils•Isolation spacing greater than 10 mm •Proof tracking index (PTI/CTI) 250•Reinforced insulation, EN 60730-1 (VDE 0631, part 1)EN 60335-1 (VDE 0700, part 1)•UL, CUR file E43203 •VDE file 40012572CONTACTSArrangement DPDT (2 Form C)DPST (2 Form A)RatingsResistive load:Max. switched power: 2 X 240 W or 2000 VA Max. switched current: 2 X 8 AMax. switched voltage:300 VDC* or 400 VAC* Note: If switching voltage is greater than 30VDC,special precautions must be taken.Please contact the factory.Rated Load UL, CUR 8 A at 250VAC General Use VDE 8 A at 250 VACMaterial Silver nickel, silver nickel gold plated or silver tin oxide Resistance< 100 milliohms initiallyCOILPowerAt Pickup Voltage 200 mW (DC coil)(typical).422 VA (AC coil)Max. Continuous 1.7 W at 20°C (68°F) ambient Dissipation 1.7 VA at 20°C (68°F) ambient Temperature Rise 26°C (47°F) at nominal coil voltage Max. Temperature155°C (311°F)NOTES1.All values at 20°C (68°F).2.Relay may pull in with less than “Must Operate” value.3.Specifications subject to change without notice.ZET TLER* “2A” or “2C” denote silver nickel contacts.Add suffix “G” at “2A” or “2C” for gold plated silver nickel contacts. Add suffix “E” at “2A” or “2C” for silver tin oxide contacts.Add suffix “E” at the end of order number for sealed version.COIL SPECIFICATIONS - AC COILORDER NUMBER*Nominal CoilMust OperateMax. ContinuousNominal CurrentCoil Resistance 2 Form A 2 Form C VACVACVACmA ± 10%Ohm ± 10%129.018.063.0100AZ742–2A–12A AZ742–2C–12A 2418.036.031.3400AZ742–2A–24A AZ742–2C–24A 4836.072.015.61,550AZ742–2A–48A AZ742–2C–48A 6045.090.012.52,600AZ742–2A–60A AZ742–2C–60A 11082.5165.0 6.88,900AZ742–2A–110A AZ742–2C–110A 11586.3172.5 6.59,600AZ742–2A–115A AZ742–2C–115A 12090.0180.0 6.310,200AZ742–2A–120A AZ742–2C–120A 220165.0330.0 3.435,500AZ742–2A–220A AZ742–2C–220A 230172.5345.0 3.338,500AZ742–2A–230AAZ742–2C–230A 240180.0360.03.142,500AZ742–2A–240AAZ742–2C–240ARELAY ORDERING DATACOIL SPECIFICATIONS - DC COILORDER NUMBER*Nominal CoilMust OperateMax. ContinuousCoil Resistance 2 Form A 2 Form C VDCVDCVDCOhm ± 10%3 2.17.622AZ742–2A–3D AZ742–2C–3D 5 3.512.760 AZ742–2A–5DAZ742–2C–5D 6 4.215.390AZ742–2A–6D AZ742–2C–6D 9 6.322.9200AZ742–2A–9D AZ742–2C–9D 128.430.6360 AZ742–2A–12D AZ742–2C–12D1812.645.9710AZ742–2A–18D AZ742–2C–18D 2416.861.21,440 AZ742–2A–24DAZ742–2C–24D 3625.292.03,140AZ742–2A–36D AZ742–2C–36D 4833.6122.05,700AZ742–2A–48D AZ742–2C–48D 6042.0153.07,500AZ742–2A–60D AZ742–2C–60D 11077.0280.025,200AZ742–2A–110DAZ742–2C–110DACCESSORIESMECHANICAL DATAZETTLERh = 15 ... 16.5 mm h = 15 ... 16.5 mmFor P.C.B. mount: Socket EC 50Retaining Clip MP 16 / MH 16For DIN rail mount: Socket ES 50Retaining Clip MS 16ZET TLER。

OPA741W23;中文规格书,Datasheet资料

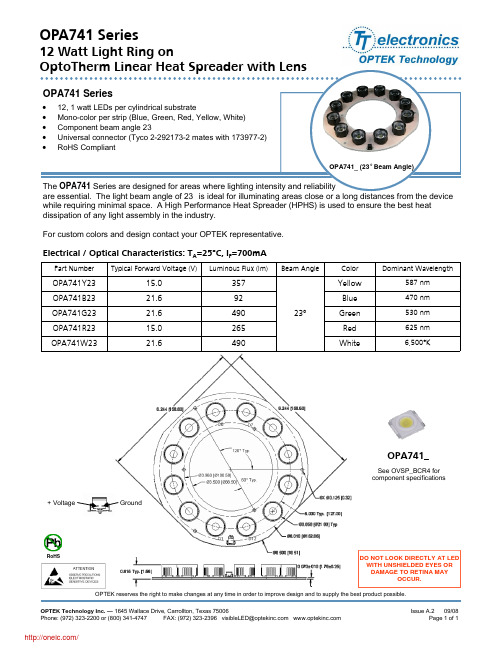

12 Watt Light Ring on OptoTherm Linear Heat Spreader with Lens

OPA741 Series

• • • • •

12, 1 watt LEDs per cylindrical substrate Mono-color per strip (Blue, Green, Red, Yellow, White) Component beam angle 23° Universal connector (Tyco 2-292173-2 mates with 173977-2) RoHS Compliant

+ Voltຫໍສະໝຸດ geGroundRoHS

DO NOT LOOK DIRECTLY AT LED WITH UNSHIELDED EYES OR DAMAGE TO RETINA MAY OCCUR.

OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Issue A.2 09/08 Page 1 of 1

/

分销商库存信息:

OPTEK-TECHNOLOGY OPA741W23

Product Photo Here

OPA741_ (23° Beam Angle)

The OPA741 Series are designed for areas where lighting intensity and reliability are essential. The light beam angle of 23° is ideal for illuminating areas close or a long distances from the device while requiring minimal space. A High Performance Heat Spreader (HPHS) is used to ensure the best heat dissipation of any light assembly in the industry. For custom colors and design contact your OPTEK representative.

音频处理芯片AIC23完整中文资料

⾳频处理芯⽚AIC23完整中⽂资料TLV320AIC23中⽂资料管脚图及其应⽤TLV320AIC23(以下简称AIC23)是TI推出的⼀款⾼性能的⽴体声⾳频Codec芯⽚,内置⽿机输出放⼤器,⽀持MIC和LINE IN两种输⼊⽅式(⼆选⼀),且对输⼊和输出都具有可编程增益调节。

AIC23的模数转换(ADCs)和数模转换(DACs)部件⾼度集成在芯⽚内部,采⽤了先进的Sigma-delta过采样技术,可以在8K到96K的频率范围内提供16bit、20bit、24bit和32bit的采样,ADC和DAC的输出信噪⽐分别可以达到90dB 和100dB。

与此同时,AIC23还具有很低的能耗,回放模式下功率仅为23mW,省电模式下更是⼩于15uW。

由于具有上述优点,使得AIC23是⼀款⾮常理想的⾳频模拟I/O器件,可以很好的应⽤在随声听(如CD,MP3……)、录⾳机等数字⾳频领域。

AIC23的管脚和内部结构框图如下:从上图可以看出,AIC23主要的外围接⼝分为以下⼏个部分:⼀.数字⾳频接⼝:主要管脚为BCLK-数字⾳频接⼝时钟信号(bit时钟),当AIC23为从模式时(通常情况),该时钟由DSP产⽣;AIC23为主模式时,该时钟由AIC23产⽣;LRCIN-数字⾳频接⼝DAC⽅向的帧信号(I2S模式下word时钟)LRCOUT-数字⾳频接⼝ADC⽅向的帧信号DIN-数字⾳频接⼝DAC⽅向的数据输⼊DOUT-数字⾳频接⼝ADC⽅向的数据输出这部分可以和DSP的McBSP(Multi-channel buffered serial port,多通道缓存串⼝)⽆缝连接,唯⼀要注意的地⽅是McBSP 的接收时钟和AIC23的BCLK都由McBSP的发送时钟提供,连接⽰意图如下:⼆.麦克风输⼊接⼝:主要管脚为MICBIAS-提供麦克风偏压,通常是3/4 AVDDMICIN-麦克风输⼊,由AIC结构框图可以看出放⼤器默认是5倍增益连接⽰意图如下:三.LINE IN输⼊接⼝:主要管脚为LLINEIN-左声道LINE IN输⼊RLINEIN-右声道LINE IN输⼊连接⽰意图如下:四.⽿机输出接⼝:主要管脚为LHPOUT-左声道⽿机放⼤输出RHPOUT-右声道⽿机放⼤输出LOUT-左声道输出ROUT-右声道输出从框图可以看出,LOUT和ROUT没有经过内部放⼤器,所以设计中常⽤LHPOUT和RHPOUT,连接⽰意图如下:五.配置接⼝:主要管脚为SDIN-配置数据输⼊SCLK-配置时钟DSP通过该部分配置AIC23的内部寄存器,每个word的前7bit为寄存器地址,后9bit 为寄存器内容。

IC datasheet pdf-OPA743,OPA2743,OPA4743,pdf(CMOS, Rail-to-Rail, I_O Operational Amplifiers)

ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

OPA2743EA

MSOP-8

337

E43

OPA2743EA/250

Tape and Reel

"

"

"

"

OPA2743EA/2K5

Tape and Reel

OPA2743UA

"

SO-8

"

182

OPA2743UA

OPA2743UA

Rails

"

"

OPA2743UA/2K5

Tape and Reel

OPA2743PA

OPA743

Out 1 V– 2 +In 3

OPA743

5 V+ 4 –In

SOT23-5

Out A 1 –In A 2 +In A 3

V– 4

OPA2743

A B

NC 1 –In 2 +In 3 V– 4

SO-8, DIP-8 8 V+ 7 Out B 6 –In B 5 +In B

8 NC 7 V+ 6 Out 5 NC Out A 1

MAX742中文资料

MAX742

CC-

+5V INPUT

+2.0V VREF

R -SENSE

PWM

S -DRIVE

P

-VO

OSC +VO

S +DRIVE

N

PWM

R +SENSE

CC+

________________________________________________________________ Maxim Integrated Products 1

Operating Temperature Ranges MAX742C_ _ .......................................................0°C to +70°C MAX742E_ _ ....................................................-40°C to +85°C MAX742MJP ..................................................-55°C to +125°C

W741E203资料

4-BIT FLASH MICROCONTROLLERPublication Release Date: March 1998Table of Contents--GENERAL DESCRIPTION.........................................................................................................................2 FEATURES.................................................................................................................................................2 PIN CONFIGURATIONS............................................................................................................................3 PIN DESCRIPTION....................................................................................................................................4 BLOCK DIAGRAM......................................................................................................................................5 FUNCTIONAL DESCRIPTION...................................................................................................................6 ABSOLUTE MAXIMUM RATINGS .............................................................................................................28 DC CHARACTERISTICS............................................................................................................................29 AC CHARACTERISTICS............................................................................................................................30 PAD ASSIGNMENT & POSITIONS............................................................................................................31 TYPICAL APPLICATION CIRCUIT.............................................................................................................32 INSTRUCTION SET TABLE.......................................................................................................................33 PACKAGE DIAMENSIONS (79)GENERAL DESCRIPTIONThe W741E20X is a high-performance 4-bit microcontroller (µC) that provides an flash EEPROM for the program memory. The device contains a 4-bit ALU, two 8-bit timers, a divider, a serial port, and five 4-bit I/O ports (including 3 output port for LED driving). There are also seven interrupt sources and 8-level subroutine nesting for interrupt applications. The W741E20X has two power reduction modes, hold mode and stop mode, which help to minimize power dissipation.The W741E20X is suitable for end product manufacturer engineering testing and earlier samples before mass production.FEATURES•Operating voltage: 2.4V−5.5V•Crystal or RC oscillation circuit can be selected by the code option− Crystal/Ceramic oscillator: up to 4 MHz− RC oscillator: up to 4 MHz• Both in crystal or RC oscillator operation mode, high-frequency (400 KHz to 4 MHz) or low-frequency (32.768 KHz) oscillation must be determined by the code option• Memory− 2048 × 16 bit program flash EEPROM (including 2K × 4 bit look-up table)− 128 × 4 bit data RAM (including 16 working registers)•21 input/output pins− Input/output ports: 4 ports/16 pins− Serial input/output port: 1 port /4 pins (high sink current for LED driving)− MFP output pin: 1 pin (MFP)• Power-down mode− Hold function: no operation (except for oscillator)− Stop function: no operation (including oscillator)•Seven types of interrupts− Five internal interrupts (Divider 0, Timer 0, Timer 1, and Serial I/O)− Two external interrupts (Port RC and INT pin)•MFP output pin− Output is software selectable as modulating or nonmodulating frequency− Works as frequency output specified by Timer 1•Built-in 14-bit clock frequency divider circuit•Two built-in 8-bit programmable countdown timers− Timer 0: One of two internal clock frequencies (F OSC/4 or F OSC/1024) can be selected− Timer 1: Offers auto-reload function and one of two internal clock frequencies (F OSC or F OSC/64) can be selected or falling edge of pin RC.0 can be selected (output through MFP pin)•Built-in 18/14-bit watchdog timer selectable for system reset•Powerful instruction set: 118 instructions•8-level subroutine (include interrupt) nestingPublication Release Date: March 1998 • One serial transmission/receiver port specified by software • Up to 1 µS instruction cycle (with 4 MHz operating frequency) • Packaged in 18-pin, 20-pin, 28-pin PDIP and 20-pin, 28-pin SOPPIN CONFIGURATIONSPIN DESCRIPTIONNote: There are internal pull-high resistors in these pins of W741C20X.Publication Release Date: March 1998 BLOCK DIAGRAMFUNCTIONAL DESCRIPTIONProgram Counter (PC)Organized as an 11-bit binary counter (PC0 to PC10), the program counter generates the addresses of the 2048 × 16 on-chip flash EEPROM containing the program instruction. When the jump or subroutine call instructions or the interrupt or initial reset conditions are to be executed, the address corresponding to the instruction will be loaded into the program counter. The format used is shownStack Register (STACK)The stack register is organized as 11 bits × 8 levels (first-in, last-out). When either a call subroutine or an interrupt is executed, the program counter will be pushed onto the stack register automatically. At the end of a call subroutine or an interrupt service subroutine, the RTN instruction must be executed to pop the contents of the stack register into the program counter. When the stack register is pushed over the eighth level, the contents of the first level will be lost. In other words, the stack register is always eight levels deep.Program Memory (flash EEPROM)The flash EEPROM is used to store program codes; the look-up table is arranged as 2048 × 4 bits. The first three quarters of flash EEPROM (000H to 5FFH) are used to store instruction codes only, but the last quarter (600H to 7FFH) can store both instruction codes and the look-up table. Each look-up table element is composed of 4 bits, so the look-up table can be addressed up to 2048 elements. There are two registers (TABL and TABH) to be used in look-up table addressing and they are controlled by MOV TABH, R and MOV TABL, R instructions. When the instruction MOVC R is executed, the contents of the look-up table location address specified by TABH, TABL and ACC will be read and transferred to the data RAM. Refer to the instruction table for more details. The organization of the program memory is shown in Figure 1.Publication Release Date: March 1998Figure 1. Program Memory OrganizationData Memory (RAM)1. ArchitectureThe static data memory (RAM) used to store data is arranged as 128 × 4 bits. The data memory can be addressed directly or indirectly. The organization of the data memory is shown in Figure 2.Figure 2. Data Memory OrganizationThe first sixteen addresses (00H to 0FH) in the data memory are known as the working registers (WR). The other data memory is used as general memory and cannot operate directly with immediate data. The relationship between data memory locations and the page register (PAGE) in indirect addressing mode is described in the next section.2. Page Register (PAGE)The page register is organized as a 4-bit binary register. The bit descriptions are as follows:PAGENote: R/W means read/write available.Bit 3 is reserved.Bit 2, Bit 1, Bit 0 Indirect addressing mode preselect bits:000 = Page 0 (00H - 0FH)001 = Page 1 (10H - 1FH)010 = Page 2 (20H - 2FH)011 = Page 3 (30H - 3FH)100 = Page 4 (40H - 4FH)101 = Page 5 (50H - 5FH)110 = Page 6 (60H - 6FH)111 = Page 7 (70H - 7FH)Accumulator (ACC)The accumulator (ACC) is a 4-bit register used to hold results from the ALU and transfer data between the memory, I/O ports, and registers.Arithmetic and Logic Unit (ALU)This is a circuit which performs arithmetic and logic operations. The ALU provides the following functions:•Logic operations: ANL, XRL, ORL•Branch decisions: JB0, JB1, JB2, JB3, JNZ, JZ, JC, JNC, DSKZ, DSKNZ, SKB0, SKB1, SKB2, SKB3 •Shift operations: SHRC, RRC, SHLC, RLC•Binary additions/subtractions: ADC, SBC, ADD, SUB, ADU, DEC, INCAfter any of the above instructions are executed, the status of the carry flag (CF) and zero flag (ZF) is stored in the internal registers. CF can be read out by executing MOVA R, CF.Publication Release Date: March 1998 Clock GeneratorThe W741E20X provides a crystal or RC oscillation circuit selected by option codes to generate the system clock through external connections. If a crystal oscillator is used, a crystal or a ceramic resonator must be connected to XIN and XOUT, and the capacitor must be connected if an accurate frequency is needed. When a crystal oscillator is used, a high-frequency clock (400 KHz to 4 MHz) or low-frequency clock (32 KHz) can be selected for the system clock by means of option codes. If the RC oscillator is used, a resistor in the range of 20 K Ω to 1.6 M Ω must be connected to XIN and XOUT, as shown in Figure 3. The system clock frequency range is from 32 KHz to 4 MHz. One machine cycle consists of a four-phase system clock sequence and can run up to 1 µS with a 4 MHz system clock.Figure 3. Oscillator ConfigurationDivider 0Divider 0 is organized as a 14-bit binary up-counter designed to generate periodic interrupts, as shown in Figure 4. When the system starts, the divider is incremented by each system clock (Fosc). When an overflow occurs, the divider event flag is set to 1 (EVF.0 = 1). Then, if the divider interrupt enable flag has been set (IEF.0 = 1), the interrupt is executed, while if the hold release enable flag has been set (HEF.0 = 1), the hold state is terminated. The last 4-stage of the Divider 0 can be reset by executing CLR DIVR0 instruction. If the oscillator is connected to the 32768 Hz crystal, the EVF.0 will be set to 1 periodically at each 500 mS interval.Watchdog Timer (WDT)The watchdog timer (WDT) is organized as a 4-bit up counter and is designed to protect the program from unknown errors. The WDT is enable when the corresponding option code bit of the WDT is set to 1. If the WDT overflows, the chip will be reset. At initial reset, the input clock of the WDT is F OSC /1024. The input clock of the WDT can be switched to F OSC /16384 (or F OSC /1024) by executing the SET PMF, #08H (or CLR PMF, #08H) instruction. The contents of the WDT can be reset by the instruction CLR WDT. In normal operation, the application program must reset WDT before it overflows. A WDT overflow indicates that the operation is not under control and the chip will be reset. The WDT minimun overflow period is 468.75 mS when the system clock (F OSC ) is 32 KHz and WDT clock input is F OSC /1024. When the corresponding option code bit of the WDT is set to 0, the WDT function is disabled. The organization of the Divider0 and watchdog timer is shown in Figure 4.Figure 4. Organization of Divider and Watchdog TimerParameter Flag (PMF)The parameter flag is organized as a 4-bit binary register (PMF.0 to PMF.3). The PMF is controlled by the SET PMF, #I or CLR PMF, #I instruction. The bit descriptions are as follows:123PMFNote: W means write only.Bit 0, Bit 1 & Bit 2 are reserved.Bit 3 = 0 The fundamental frequency of the watch dog timer is Fosc/1024.= 1 The fundamental frequency of the watch dog timer is Fosc/16384.At initial reset, bit 3 of PMF is set to "0".Publication Release Date: March 1998 Timer/CounterTimer 0 (TM0)Timer 0 (TM0) is a programmable 8-bit binary down-counter. The specified value can be loaded into TM0 by executing the MOV TM0L(TM0H), R or MOV TM0, #I instruction. When the MOV TM0L (TM0H), R instructions are executed, the TM0 will stop down-counting (if the TM0 is down-counting), the MR0.3 will be reset to 0, and the specified value is loaded into TM0. If MR0.3 is set to 1, the event flag 1 (EVF.1) is reset and the TM0 starts to count. When it decrements to FFH, Timer 0 stops operating and generates an underflow (EVF.1 = 1). The interrupt is executed if the Timer 0 interrupt enable flag has been set (IEF.1 = 1); and the hold state is terminated if the hold release enable flag 1 has been set (HEF.1 = 1). The Timer 0 clock input can be set as F OSC /1024 or F OSC /4 by setting MR0.0 to 1 or by resetting MR0.0 to 0. The default timer value is F OSC /4. The organization of Timer 0 is shown in Figure 5.If the Timer 0 clock input is Fosc/4, then: Desired time 0 interval = (preset value +1) × 4 × 1/Fosc If the Timer 0 clock input is Fosc/1024, then:Desired time 0 interval = (preset value +1) × 1024 × 1/Fosc Preset value: Decimal number of Timer 0 preset value Fosc: Clock oscillation frequencyFigure 5. Organization of Timer 0Timer 1 (TM1)Timer 1 (TM1) is also a programmable 8-bit binary down counter, as shown in Figure 6. Timer 1 can be used as a counter to count external events or to output an arbitrary frequency to the MFP pin. The input clock of Timer 1 can be one of three sources: Fosc/64, Fosc, or an external clock from the RC.0input pin. The source can be selected by setting bit 0 and bit 1 of mode register 1 (MR1). At initial reset, the Timer 1 clock input is Fosc. If an external clock is selected as the clock source of Timer 1, the content of Timer 1 is decreased by 1 at the falling edge of RC.0. When the MOV TM1L, R or MOV TM1H,R instruction is executed, the specified data are loaded into the auto-reload buffer and the TM1 down-counting will be disabled (i.e. MR1.3 is reset to 0). If the bit 3 of MR1 is set (MR1.3 = 1), the contents of the auto-reload buffer will be loaded into the TM1 down counter, Timer 1 starts to down count, and the event flag 7 is reset (EVF.7 = 0). When the MOV TM1, #I instruction is executed, the event flag 7 (EVF.7) and MR1.3 are reset and the specified value is loaded into auto-reload buffer and TM1 by the internal hardware, then the MR1.3 is set, that is the TM1 starts to count by the hardware. When the timer decrements to FFH, it will generate an underflow (EVF.7 = 1) and be auto-reloaded with the specified data, after which it will continue to count down. An interrupt is executed if the interrupt enable flag 7 has been set to 1 (IEF.7 = 1), and the hold state is terminated if the hold mode release enable flag 7 is set to 1 (HEF.7 = 1). The specified frequency of Timer 1 can be delivered to the MFP output pin by programming bit 2 of MR1. Bit 3 of MR1 can be used to make Timer 1 stop or start counting.If the Timer 1 clock input is F T, then :Desired Timer 1 interval = (preset value +1) / F TDesired frequency for MFP output pin = F T ÷ (preset value + 1) ÷ 2 (Hz) Preset value: Decimal number of Timer 1 preset value, and Fosc: Clock oscillation frequencyFigure 6. Organization of Timer 1Publication Release Date: March 1998 For example, when F T equals 32768 Hz, depending on the preset value of TM1, the MFP pin will output a single tone signal in the tone frequency range from 64 Hz to 16384 Hz. The relation between the tone frequency and the preset value of TM1 is shown in the table below.3 45Tone frequency TM1 preset value &MFP frequency Tonefrequency TM1 preset value & MFP frequency Tone frequency TM1 preset value & MFP frequencyC 130.81 7CH 131.07 261.63 3EH 260.06 523.25 1EH 528.51C#138.59 75H 138.84 277.18 3AH 277.69 554.37 1CH 564.96 T D 146.83 6FH 146.28 293.66 37H 292.57 587.33 1BH 585.14 D# 155.56 68H 156.03 311.13 34H 309.13 622.25 19H 630.15 O E 164.81 62H 165.49 329.63 31H 327.68 659.26 18H 655.36 F 174.61 5DH 174.30 349.23 2EH 372.36 698.46 16H 712.34 N F# 185.00 58H 184.09 369.99 2BH 390.09 739.99 15H 744.72 G 196.00 53H 195.04 392.00 29H 420.10 783.99 14H 780.19 E G#207.65 4EH 207.39 415.30 26H 443.81 830.61 13H 819.20 A 220.00 49H 221.40 440.00 24H 442.81 880.00 12H 862.84 A# 233.08 45H 234.05 466.16 22H 468.11 932.23 11H 910.22B246.94 41H 248.24 493.88 20H 496.48 987.77 10H 963.76Note: Central tone is A4 (440 Hz).Mode Register 0 (MR0)Mode Register 0 is organized as a 4-bit binary register (MR0.0 to MR0.3). MR0 can be used to controlthe operation of Timer 0. The bit descriptions are as follows:0123MR0Note: W means write only.Bit 0 = 0 The fundamental frequency of Timer 0 is F OSC /4. = 1 The fundamental frequency of Timer 0 is F OSC /1024. Bit 1 & Bit 2 are reservedBit 3 = 0 Timer 0 stops down-counting. = 1 Timer 0 starts down-counting.Mode Register 1 (MR1)Mode Register 1 is organized as a 4-bit binary register (MR1.0 to MR1.3). MR1 can be used to control the operation of Timer 1. The bit descriptions are as follows:0123MR1Note: W means write only.Bit 0 = 0 The internal fundamental frequency of Timer 1 is Fosc. = 1 The internal fundamental frequency of Timer 1 is Fosc/64.Bit 1 = 0 The fundamental frequency source of Timer 1 is the internal clock.= 1 The fundamental frequency source of Timer 1 is the external clock from RC.0 input pin.Bit 2 = 0 The specified waveform of the MFP generator is delivered at the MFP output pin. = 1 The specified frequency of Timer 1 is delivered at the MFP output pin.Bit 3 = 0 Timer 1 stops down-counting. = 1 Timer 1 starts down-counting.Input/Output Ports RA, RBPort RA consists of pins RA.0 to RA.3 and Port RB consists of pins RB.0 to RB.3. At initial reset, input/output ports RA and RB are both in input mode. When RA and RB are used as output ports, CMOS or NMOS open drain output type can be selected by the PM0 register. Each pin of port RA or RB can be specified as input or output mode independently by the PM1 and PM2 registers. The MOVA R, RA or MOVA R, RB instructions operate the input functions and the MOV RA, R or MOV RB, R operate the output functions. For more details, refer to the instruction table and Figure 7.Figure 7. Architecture of RA & RB Input/Output PinsPublication Release Date: March 1998 Port Mode 0 Register (PM0)The port mode 0 register is organized as 4-bit binary register (PM0.0 to PM0.3). PM0 can be used to determine the structure of the input/output ports; it is controlled by the MOV PM0, #I instruction. The bit descriptions are as follows:PM00123Note: W means write only.Bit 0 = 0 RA port is CMOS output type. Bit 0 = 1 RA port is NMOS open drain output type. Bit 1 = 0 RB port is CMOS output type. Bit 0 = 1 RB port is NMOS open drain output type. Bit 2 & Bit 3 are reserved.Port Mode 1 Register (PM1)The port mode 1 register is organized as 4-bit binary register (PM1.0 to PM1.3). PM1 can be used to control the input/output mode of port RA. PM1 is controlled by the MOV PM1, #I instruction. The bit descriptions are as follows:PM10123Note: W means write only.Bit 0 = 0 RA.0 works as output pin; Bit 0 = 1 RA.0 works as input pin Bit 1 = 0 RA.1 works as output pin; Bit 1 = 1 RA.1 works as input pin Bit 2 = 0 RA.2 works as output pin; Bit 2 = 1 RA.2 works as input pin Bit 3 = 0 RA.3 works as output pin; Bit 3 = 1 RA.3 works as input pin At initial reset, port RA is input mode (PM1 = 1111B).Port Mode 2 Register (PM2)The port mode 2 register is organized as 4-bit binary register (PM2.0 to PM2.3). PM2 can be used to control the input/output mode of port RB. PM2 is controlled by the MOV PM2, #I instruction. The bit descriptions are as follows:PM20123Note: W means write only.Bit 0 = 0 RB.0 works as output pin; Bit 0 = 1 RB.0 works as input pin Bit 1 = 0 RB.1 works as output pin; Bit 1 = 1 RB.1 works as input pin Bit 2 = 0 RB.2 works as output pin; Bit 2 = 1 RB.2 works as input pin Bit 3 = 0 RB.3 works as output pin; Bit 3 = 1 RB.3 works as input pin At initial reset, the port RB is input mode (PM2 = 1111B).Port Mode 3 Register (PM3)Port Mode 3 Register is organized as a 4-bit binary register (PM3.0 to PM3.3). PM3 can be used to determine the operating mode of the output port RE and the clock rate of the serial I/O function. The PM3 control diagram is shown in Figure 8. The bit descriptions are as follows:123PM3Note: W means write only.Bit 0 is reserved.Bit 1 = 0 The output of the port RE is the output of the internal parallel port RT.= 1 The port RE works as the serial input/output port. Bit 2 is reserved.Bit 3 = 0 Serial Tx rate = Fosc/2= 1 Serial Tx rate = Fosc/256Figure 8. PM3 Control DiagramPort Mode 4 Register (PM4)The port mode 4 register is organized as 4-bit binary register (PM4.0 to PM4.3). PM4 can be used to control the input/output mode of port RC. PM4 is controlled by the MOV PM4, #I instruction. The bit descriptions are as follows:PM40123Note: W means write only.Publication Release Date: March 1998 Bit 0 = 0 RC.0 works as output pin; Bit 0 = 1 RC.0 works as input pin Bit 1 = 0 RC.1 works as output pin; Bit 1 = 1 RC.1 works as input pin Bit 2 = 0 RC.2 works as output pin; Bit 2 = 1 RC.2 works as input pin Bit 3 = 0 RC.3 works as output pin; Bit 3 = 1 RC.3 works as input pin At initial reset, port RC is input mode (PM4 = 1111B).Port Mode 5 Register (PM5)The port mode 5 register is organized as 4-bit binary register (PM5.0 to PM5.3). PM5 can be used to control the input/output mode of port RD. PM5 is controlled by the MOV PM5, #I instruction. The bit descriptions are as follows:PM50123Note: W means write only.Bit 0 = 0 RD.0 works as output pin; Bit 0 = 1 RD.0 works as input pin Bit 1 = 0 RD.1 works as output pin; Bit 1 = 1 RD.1 works as input pin Bit 2 = 0 RD.2 works as output pin; Bit 2 = 1 RD.2 works as input pin Bit 3 = 0 RD.3 works as output pin; Bit 3 = 1 RD.3 works as input pinAt initial reset, the port RB is input mode (PM2 = 1111B). Input/Output Ports RC, RDPort RC consists of pins RC.0 to RC.3, and port RD consists of pins RD.0 to RD.3. At initial reset, input/output ports RC and RD are both in input mode. When RC and RD are used as output ports, the CMOS type is the only ouput driving type. Each pin of port RC or RD can be specified as input or output mode independently by the PM4 and PM5 registers. The MOVA R, RC or MOVA R, RD instructions operate the input functions and the MOV RC, R or MOV RD, R operate the output functions. When the PEF, HEF, and IEF corresponding to the RC port are set, a signal change at the specified pins of port RC will execute the hold mode release or interrupt subroutine. Port status register 0 (PSR0) records the status of port RC, and that can be read out and cleared by the MOV R, PSR0, and CLR PSR0 instructions. Before the port mode of the RC port is changed from output mode to input mode in the hold mode release and interrupt application, the output value must be preset to the same as the system status to prevent the undesired signal change being accepted. When the interrupt of RC port is accepted, the corresponding event flag (EVF.2) will be reset, but the content of PSR0 should not be changed except the CLR PSR0 or MOV PEF,#I instruction being executed or performing the reset function. In addition, the falling edge signal on the pin of port RC specified by the instruction MOV SEF, #I will cause the device to exit the stop mode. The RD port is used as the I/O port only. Refer to Figure 9, Figure 10 and the instruction table for more details.Figure 9. Architecture of RC & RD Input/Output PinsPort Enable Flag (PEF)The port enable flag is organized as 4-bit binary register (PEF.0 to PEF.3). Before port RC may be used to release the hold mode or preform interrupt function, the content of the PEF must be set first. The PEF is controlled by the MOV PEF, #I instruction. The bit descriptions are as follows:PEF 0123Note: W means write only.PEF.0: Enable/disable the signal change at pin RC.0 to release hold mode or perform interrupt. PEF.1: Enable/disable the signal change at pin RC.1 to release hold mode or perform interrupt. PEF.2: Enable/disable the signal change at pin RC.2 to release hold mode or perform interrupt. PEF.3: Enable/disable the signal change at pin RC.3 to release hold mode or perform interrupt.Port Status Register 0 (PSR0)Port status register 0 is organized as 4-bit binary register (PSR0.0 to PSR0.3). PSR0 can be read orcleared by the MOVA R, PSR0, and CLR PSR0 instructions. The bit descriptions are as follows:0123PSR0Note: R means read only.Publication Release Date: March 1998 Bit 0 = 1 Signal change at RC.0 Bit 1 = 1 Signal change at RC.1 Bit 2 = 1 Signal change at RC.2 Bit 3 = 1 Signal change at RC.3Figure 10. Input Architecture of Ports RCOutput Port REOutput port RE can be used as an output of the internal RT port, or as a serial input/output port. The control flow is shown in Figure 8. When bit 1 of port mode 3 register (PM3) equals to 0, port RE works as an output of internal port RT. When the MOV RE, R instruction is executed, the data in the RAM will be output to port RT through port RE. When RE works as a parallel output port, it provides a high sink current to drive LEDs. When bit 1 of MR0 equals to 1, the RE port works as a serial input/output port, and RE.0 to RE.3 are used as DOUT, CLKO, DIN, and CLKI, respectively. In this case, the DIN pin will has a built-in pull-high resistor. The serial I/O functions are controlled by the instructions SOP R and SIP R. The functions of the two instructions are described below:(1) When the SIP R instruction is executed, the data will be loaded from the serial input buffer to the ACC and RAM first, and bit 1 of port status register 2 will automatically be set to "1" (BUSYI = 1). Then the CLKI pin will send out 8 clocks and the data from the DIN pin will be loaded to SIB at the rising edge of the CLKI pin. After the 8 clocks have been sent, BUSYI will be reset to "0" and EVF.5 will be set to "1." At this time, if IEF.5 has been set (IEF.5 = 1), an interrupt is executed; if HEF.5 has been set (HEF.5 = 1), the hold state is terminated. Users can check the status of PSR2.1 (BUSYI) to know whether the serial input process is completed or not. If a serial input process is not completed, and the SIP R instruction is executed again, the data will be lost. The timing is shown in Figure 11.Figure 11. Timing of the Serial Input Function (SIP R)Publication Release Date: March 1998 (2) When the SOP R instruction is executed, the data will be loaded to the serial output buffer (SOB) and bit 3 of port status register 2 will be set to "1" (BUSYO = 1). Then the CLKO pin will send out 8 clocks and the data in SOB will be sent out at the falling edge of the CLKO pin. After the 8 clocks have been sent, BUSYO will be reset to "0" and EVF.6 will be set to "1." At this time, if IEF.6 has been set (IEF.6 = 1), an interrupt is executed; if HEF.6 has been set (HEF.6 = 1), the hold state is terminated. Users can check the status of PSR2.3 (BUSYO) to know whether the serial output process is completed or not. If a serial output process is not completed, and the SOP R instruction is executed again, the data will be lost. The timing is shown in Figure 12.Figure 12. Timing of the Serial Output Function (SOP R)In the above description, the low nibble location of the serial input/output register is contributed to the ACC, and the high nibble is to R. The port status register 2 (PSR2) including BUSYI, and BUSYO can be read out or cleared by the MOVA R, PSR2, or CLR PSR2 instruction.Port Status Register 2 (PSR2)Port status register 2 is organized as 4-bit binary register (PSR2.0 to PSR2.3). PSR2 is controlled by the MOVA R, PSR2, and CLR PSR2 instructions. The bit descriptions are as follows:123PSR2Note: R means read only.Bit 0 is reserved.Bit 1 (BUSYI):Serial port input busy flag.Bit 2 is reserved.Bit 3 (BUSYO):Serial port output busy flag.MFP Output Pin (MFP)The MFP output pin can output the Timer 1 clock or the modulation frequency; the output of the pin is determined by mode register 1 (MR1). The organization of MR1 is shown in Figure 6. When bit 2 of MR1 is reset to "0," the MFP output can deliver a modulation output in any combination of one signal from among DC, 4096Hz, 2048Hz, and one or more signals from among 128 Hz, 64 Hz, 8 Hz, 4 Hz, 2 Hz, or 1 Hz (when using a 32.768 KHz crystal). The MOV MFP, #I instruction is used to specify the modulation output combination. The data specified by the 8-bit operand and the MFP output pin are shown as below.(Fosc = 32.768 KHz)R6 R5 R4 R3 R2 R1 R0 FUNCTION R7levelLow0 0 0 0 0 0Hz1280 0 0 0 0 1Hz640 0 0 0 1 0Hz80 0 0 0 1 0 04Hz0 0 1 0 0 00 1 0 0 0 0 2 HzHz1 0 0 0 0 01level0 0 0 0 0 0HighHz1280 0 0 0 0 1Hz0 0 0 0 1 0648Hz1 0 0 0 1 0 0Hz0 0 1 0 0 04Hz20 1 0 0 0 0Hz11 0 0 0 0 0Hz0 0 0 0 0 020480 0 0 0 0 1 2048 Hz * 128 Hz64Hz*0 0 0 0 1 02048Hz1 0 0 0 0 1 0 0 2048 Hz * 8 Hz4Hz*Hz20480 0 1 0 0 02Hz*0 1 0 0 0 0Hz20481Hz*20481 0 0 0 0 0Hz。

OPA2343UA中文资料

®

For most current data sheet and other product information, visit

OPA4343 ®

OPA2343

OPA4343

OPA343 OPA2343 OPA4343

SINGLE-SUPPLY, RAIL-TO-RAIL OPERATIONAL AMPLIFIERS MicroAmplifier ™ Series

OPA343 series rail-to-rail CMOS operational amplifiers are designed for low cost, miniature applications. They are optimized for low voltage, single supply operation. Rail-to-rail input/output and high speed operation make them ideal for driving sampling analog-to-digital converters. They are also well suited for general purpose and audio applications as well as providing I/V conversion at the output of D/A converters. Single, dual, and quad versions have identical specifications for design flexibility.

–In B 6

14 Out D

13 –In D D

12 +In D

PS2502-2规格书,PS2502-1技术资料,PS2502-4,datasheet,PDF,NEC光耦代理商

Document No. P11303EJ4V0DS00 (4th edition)

The mark shows major revised points.

Date Published September 1997 NS

Printed in Japan

©

1988

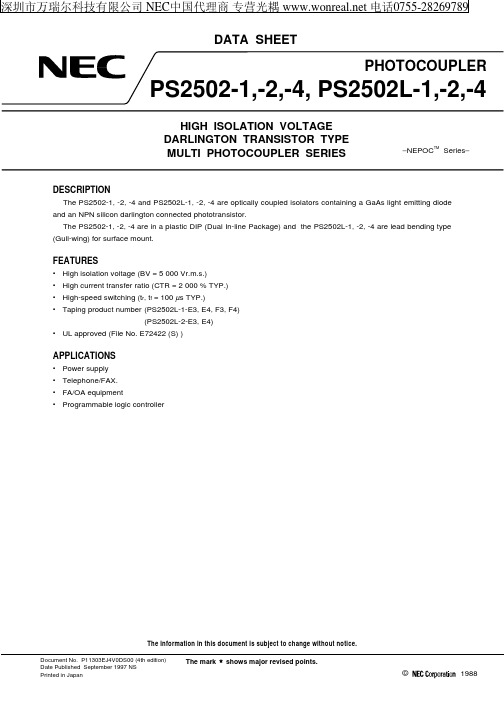

深圳市万瑞尔科技有限公司 NEC中国代理商 专营光耦 电话0755-28269789 PS2502-1,-2,-4,PS2502L-1,-2,-4

FORWARD CURRENT vs. FORWARD VOLTAGE

100

50 TA = +100 ˚C +60 ˚C +25 ˚C

10

5

0 ˚C

–25 ˚C

1

–55 ˚C

0.5

0.1 0.7 0.8 0.9 1.0 1.1 1.2 1.3 1.4 1.5 Forward Voltage VF (V)

0.65

0.65

1.25±0.15 2.54

0.50 ± 0.10 0.25 M

0 to 15˚ 1.25±0.15 2.54

0.50 ± 0.10 0.25 M

Caution New package 1-ch only 2

0 to 15˚

深圳市万瑞尔科技有限公司 NEC中国代理商 专营光耦 电话0755-28269789 PS2502-1,-2,-4,PS2502L-1,-2,-4

深圳市万瑞尔科技有限公司nec中国代理商专营光耦wwwwonrealnet电话07552826978911ps2502124ps2502l124memo深圳市万瑞尔科技有限公司nec中国代理商专营光耦wwwwonrealnet电话075528269789ps2502124ps2502l124cautionwithinexistsgaasgalliumarsenidematerialwhichharmfulsubstanceingestedpleasedounderanycircumstancesbreakhermeticseal

运算放大器datasheet参数详细中文解析

运算放大器datasheet参数详细中文解析

前言输入失调电压V os:输入失调电压的温度漂移(简称输入失调电压温漂)ΔV os/ΔT:输入偏置电流输入失调电流的温度漂移(简称输入失调电流温漂)Δios/ΔT:最大共模输入电压Vcm:共模抑制比CMRR:电源电压抑制比PSRR:输出峰-峰值电压V out:输入阻抗Rin:输出阻抗Rout:开环增益Av:开环带宽:压摆率(转换速率)SR:全功率带宽:

在额定的负载时,运放的闭环增益为1倍条件下,将一个恒幅正弦大信号输入到运放的输入端,使运放输出幅度达到最大(允许一定失真)的信号频率。

这个频率受到运放转换速率的限制。

近似地,全功率带宽=转换速率/2πV op(V op是运放的峰值输出幅度)。

全功率带宽是一个很重要的指标,用于大信号处理中运放选型。

常用运费选型表

下面为从其它地方转载过来的常用运放选型表:

器件名称制造商简介

μA741 TI 单路通用运放

μA747 TI 双路通用运放

AD515A ADI 低功耗FET输入运放

AD605 ADI 低噪声,单电源,可变增益双运放

AD644 ADI 高速,注入BiFET双运放

AD648 ADI 精密的,低功耗BiFET双运放

AD704 ADI 输入微微安培电流双极性四运放

AD705 ADI 输入微微安培电流双极性运放

AD706 ADI 输入微微安培电流双极性双运放

AD707 ADI 超低漂移运放

AD708 ADI 超低偏移电压双运放

AD711 ADI 精密,低成本,高速BiFET运放。

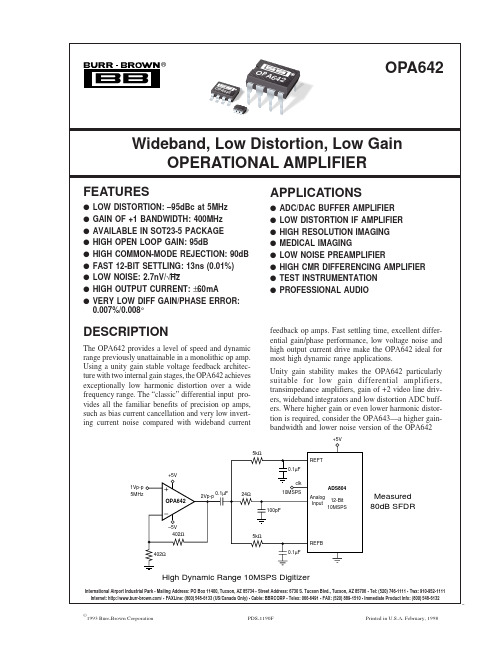

OPA642 资料

+5V 1Vp-p 5MHz clk 2Vp-p 0.1µF 24Ω 100pF –5V 402Ω 10MSPS Analog Input 12-Bit 10MSPS ADS804

OPA642

Measured 80dB SFDR

5kΩ REFB 0.1µF

402Ω

High Dynamic Range 10MSPS Digitizer

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: / • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

VS = ±4.5 to ±5.5V VCM = 0V VCM = 0V

65

T T T T

2.7 27 2.8 ±3.0 90 11 || 1 650 || 1 95 85 T T T 80

T T T T T T T 98

nV/√Hz µVrms pA/√Hz V V dB kΩ || pF kΩ || pF dB dB MHz MHz MHz MHz MHz V/µs V/µs ns ns ns dBc % degrees V V V V mA mA Ω V V mA mA °C °C/W °C/W °C/W °C/W

OPA2337UA资料

Out A 1 –In A 2 +In A 3

V– 4

A B

8 V+ 7 Out B 6 –In B 5 +In B

8-Pin DIP(1), SO-8, SOT23-8

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

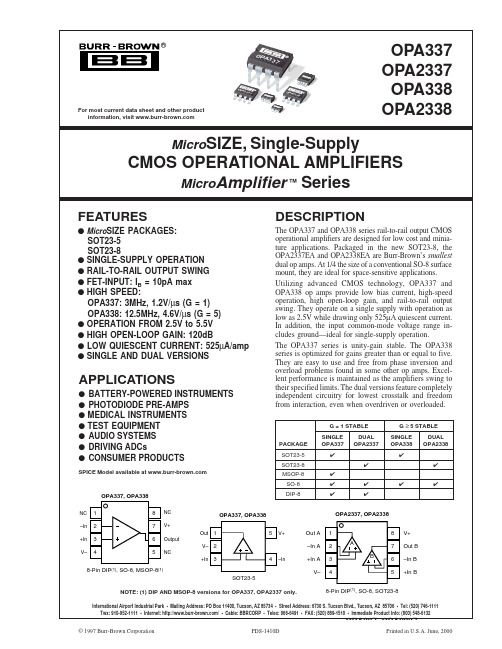

Utilizing advanced CMOS technology, OPA337 and OPA338 op amps provide low bias current, high-speed operation, high open-loop gain, and rail-to-rail output swing. They operate on a single supply with operation as low as 2.5V while drawing only 525µA quiescent current. In addition, the input common-mode voltage range includes ground—ideal for single-supply operation.

PARAMETER

OFFSET VOLTAGE

Input Offset Voltage TA = –40°C to +85°C vs Temperature

vs Power Supply Rejection Ratio TA = –40°C to +85°C Channel Separation (dual versions)

OPA2234中文资料

✻

±250

µV

✻

±350

µV

✻

✻

µV/°C

✻

20

µV/V

✻

µV/mo

✻

µV/V

INPUT BIAS CURRENT Input Bias Current(2) Input Offset Current

IB

VCM = 2.5V

IOS

VCM = 2.5V

–15

–30

±1

±5

✻

–50

nA

✻

✻

nA

NOISE

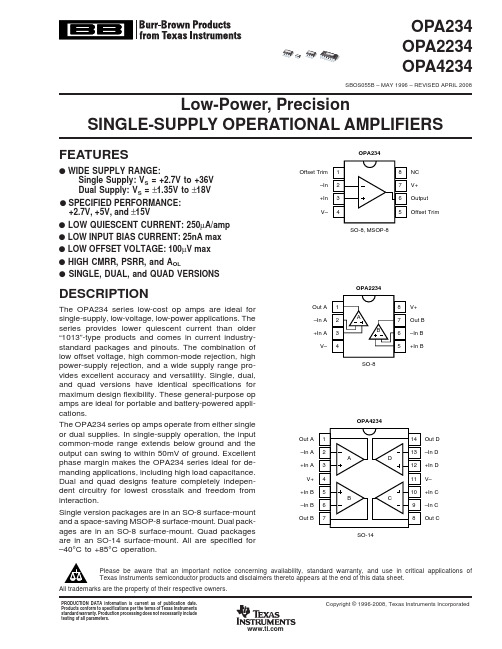

Single version packages are in an SO-8 surface-mount and a space-saving MSOP-8 surface-mount. Dual packages are in an SO-8 surface-mount. Quad packages are in an SO-14 surface-mount. All are specified for –40°C to +85°C operation.

OPA234

Offset Trim 1 –In 2 +In 3 V– 4

8 NC 7 V+ 6 Output 5 Offset Trim

SO-8, MSOP-8

Out A 1 –In A 2 +In A 3

V– 4

OPA2234 A

B

SO-8

8 V+ 7 Out B 6 –In B 5 +In B

Out A 1 –In A 2 +In A 3

G = 1, 3V Step, CL = 100pF

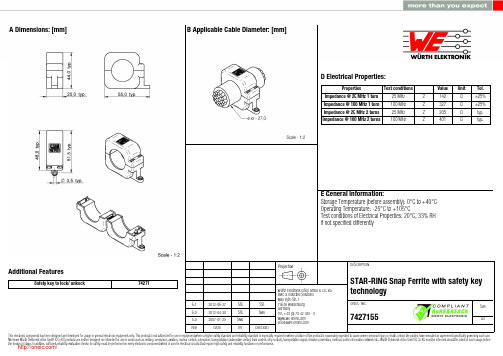

7427155;中文规格书,Datasheet资料

6.1 6.0 5.02012-06-272012-04-302007-01-25SStSStSMuSStSMu-Würth Elektronik eiSos GmbH & Co. KGEMC & Inductive SolutionsMax-Eyth-Str. 174638 WaldenburgGermanyTel. +49 (0) 79 42 945 - 0A Dimensions: [mm]Additional FeaturesSafety key to lock/ unkock74271D2 General Properties:Ferrite core Ferrite core Ferrite core Plastic housing Plastic housing Test cable Test cablePropertiesMaterial Initial permeability Curie temperatureColourFlammability ClassificationApplicable cable Applicable cable lengthµi T CValue 4 W 620620150Grey UL94-V0AWG26120Unit°Cmm Tol.typ.typ.F Typical Impedance Characteristics:I Cautions and Warnings:The following conditions apply to all goods within the product series of WE-STAR RINGof Würth Elektronik eiSos GmbH & Co. KG:General:All recommendations according to the general technical specifications of the data sheet have to be complied with.The disposal and operation of the product within ambient conditions which probably alloy or harm the component surface has to be avoided.The packaging of the product is to encase the needed humidity of the plastic housing. To ensure the humidity level, the products have to be stored in this delivered packaging. If not, the products are losing their humidity. In this case you can re-condition the components according to the internal standard WE1883 to ensure the necessary humidity in the plastic.To ensure the operating mode of the product, the ambient temperature at processing (when the part will be mounted on the cable) has to be in the range of 15 to 25 °C.Before mounting, the part should be stored for one hour in this condition.The responsibility for the applicability of customer specific products and the use in a particular customer design is always within the authority of the customer. All technical specifications for standard products do also apply for customer specific products.Direct mechanical impact to the product and the forcible closing of this shall be prevented as the ferrite material of the ferrite body or the pla-stic housing could flake or in the worst case it could break.Product specific:Follow all instructions mentioned in the datasheet, especially:•The cable diameter must be pointed out, otherwise no warranty will be sustained.•Violation of the technical product specifications such as exceeding the nominal rated current will result in the loss of warranty.1. General Customer ResponsibilitySome goods within the product range of Würth Elektronik eiSos GmbH & Co. KG contain statements regarding general suitability for certain application areas. These statements about suitability are based on our knowledge and experience of typical requirements concerning the are-as, serve as general guidance and cannot be estimated as binding statements about the suitability for a customer application. The responsibi-lity for the applicability and use in a particular customer design is always solely within the authority of the customer. Due to this fact it is up to the customer to evaluate, where appropriate to investigate and decide whether the device with the specific product characteristics described in the product specification is valid and suitable for the respective customer application or not.2. Customer Responsibility related to Specific, in particular Safety-Relevant ApplicationsIt has to be clearly pointed out that the possibility of a malfunction of electronic components or failure before the end of the usual lifetime can-not be completely eliminated in the current state of the art, even if the products are operated within the range of the specifications.In certain customer applications requiring a very high level of safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health it must be ensured by most advanced technological aid of suitable design of the customer application that no injury or damage is caused to third parties in the event of malfunction or failure of an electronic component.3. Best Care and AttentionAny product-specific notes, warnings and cautions must be strictly observed.4. Customer Support for Product SpecificationsSome products within the product range may contain substances which are subject to restrictions in certain jurisdictions in order to serve spe-cific technical requirements. Necessary information is available on request. In this case the field sales engineer or the internal sales person in charge should be contacted who will be happy to support in this matter.5. Product R&DDue to constant product improvement product specifications may change from time to time. As a standard reporting procedure of the Product Change Notification (PCN) according to the JEDEC-Standard inform about minor and major changes. In case of further queries regarding the PCN, the field sales engineer or the internal sales person in charge should be contacted. The basic responsibility of the customer as per Secti-on 1 and 2 remains unaffected.6. Product Life CycleDue to technical progress and economical evaluation we also reserve the right to discontinue production and delivery of products. As a stan-dard reporting procedure of the Product Termination Notification (PTN) according to the JEDEC-Standard we will inform at an early stage about inevitable product discontinuance. According to this we cannot guarantee that all products within our product range will always be available. Therefore it needs to be verified with the field sales engineer or the internal sales person in charge about the current product availability ex-pectancy before or when the product for application design-in disposal is considered.The approach named above does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.7. Property RightsAll the rights for contractual products produced by Würth Elektronik eiSos GmbH & Co. KG on the basis of ideas, development contracts as well as models or templates that are subject to copyright, patent or commercial protection supplied to the customer will remain with Würth Elektronik eiSos GmbH & Co. KG.8. General Terms and ConditionsUnless otherwise agreed in individual contracts, all orders are subject to the current version of the “General Terms and Conditions of Würth Elektronik eiSos Group”, last version available at .J Important Notes:The following conditions apply to all goods within the product range of Würth Elektronik eiSos GmbH & Co. KG:分销商库存信息: WURTH-ELECTRONICS 7427155。

OPA2353UA中文资料

元器件交易网

®

For most current data sheet and other product information, visit

OPA2353

OPA4353

OPA4353

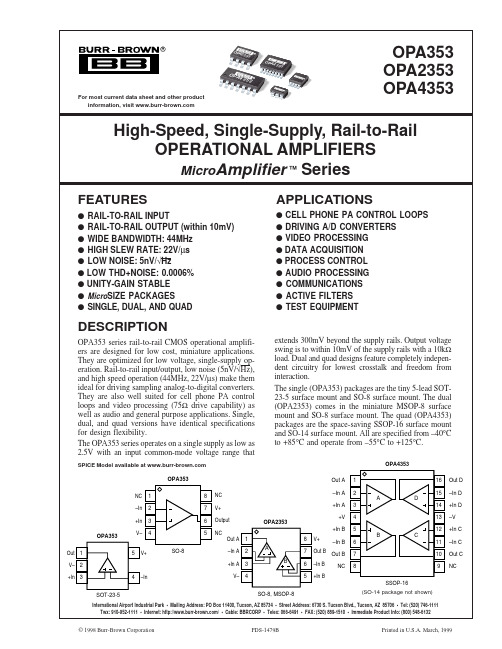

OPA353 OPA2353 OPA4353

High-Speed, Single-Supply, Rail-to-Rail OPERATIONAL AMPLIFIERS MicroAmplifier ™ Series

TA = –40°C to +85°C

TEMPERATURE RANGE Specified Range Operating Range Storage Range Thermal Resistance

SOT-23-5 MSOP-8 Surface Mount SO-8 Surface Mount SSOP-16 Surface Mount SO-14 Surface Mount

DESCRIPTION

OPA353 series rail-to-rail CMOS operational amplifiers are designed for low cost, miniature applications. They are optimized for low voltage, single-supply operation. Rail-to-rail input/output, low noise (5nV/√Hz), and high speed operation (44MHz, 22V/µs) make them ideal for driving sampling analog-to-digital converters. They are also well suited for cell phone PA control loops and video processing (75Ω drive capability) as well as audio and general purpose applications. Single, dual, and quad versions have identical specifications for design flexibility.

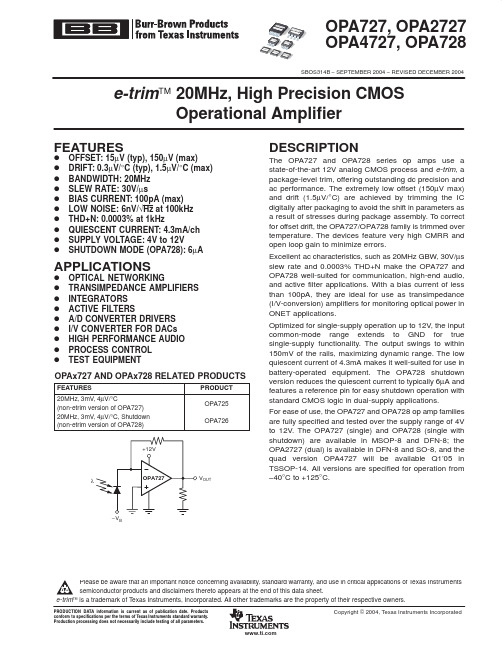

OPA2727资料

APPLICATIONS

OPAx727 AND OPAx728 RELATED PRODUCTS

FEATURES 20MHz, 3mV, 4µV/°C (non-etrim version of OPA727) 20MHz, 3mV, 4µV/°C, Shutdown (non-etrim version of OPA728) PRODUCT OPA725 OPA726

DESCRIPTION

The OPA727 and OPA728 series op amps use a state-of-the-art 12V analog CMOS process and e-trim, a package-level trim, offering outstanding dc precision and ac performance. The extremely low offset (150µV max) and drift (1.5µV/°C) are achieved by trimming the IC digitally after packaging to avoid the shift in parameters as a result of stresses during package assembly. To correct for offset drift, the OPA727/OPA728 family is trimmed over temperature. The devices feature very high CMRR and open loop gain to minimize errors. Excellent ac characteristics, such as 20MHz GBW, 30V/µs slew rate and 0.0003% THD+N make the OPA727 and OPA728 well-suited for communication, high-end audio, and active filter applications. With a bias current of less than 100pA, they are ideal for use as transimpedance (I/V-conversion) amplifiers for monitoring optical power in ONET applications. Optimized for single-supply operation up to 12V, the input common-mode range extends to GND for true single-supply functionality. The output swings to within 150mV of the rails, maximizing dynamic range. The low quiescent current of 4.3mA makes it well-suited for use in battery-operated equipment. The OPA728 shutdown version reduces the quiescent current to typically 6µA and features a reference pin for easy shutdown operation with standard CMOS logic in dual-supply applications. For ease of use, the OPA727 and OPA728 op amp families are fully specified and tested over the supply range of 4V to 12V. The OPA727 (single) and OPA728 (single with shutdown) are available in MSOP-8 and DFN-8; the OPA2727 (dual) is available in DFN-8 and SO-8, and the quad version OPA4727 will be available Q1’05 in TSSOP-14. All versions are specified for operation from −40°C to +125°C.

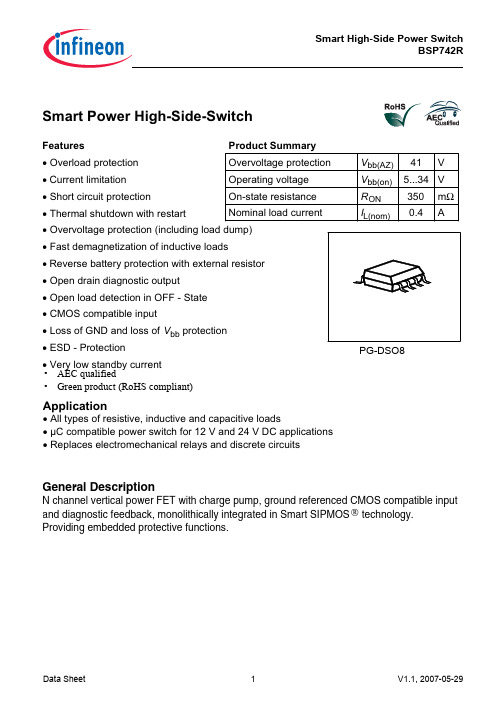

BSP742R中文资料

2QVWDWH UHVLVWDQFH

521

Tj & ,/ $ 9EE 9

Tj &

1RPLQDO ORDG FXUUHQW 'HYLFH RQ 3&%

,/ QRP

TC & 7M ≤ &

7XUQRQ WLPH

WR 9287

元器件交易网

Smart High-Side Power Switch BSP742R

6PDUW 3RZHU +LJK6LGH6ZLWFK

)HDWXUHV

3URGXFW 6XPPDU\

• 2YHUORDG SURWHFWLRQ

2YHUYROWDJH SURWHFWLRQ

Data Sheet

1

V1.1, 2007-05-29

元器件交易网

Smart High-Side Power Switch BSP742R

%ORFN 'LDJUDP

9ROWDJH VRXUFH

9 /RJLF

,1

67 (6'

/RJLF

2YHUYROWDJH &XUUHQW

6\PERO

9DOXHV

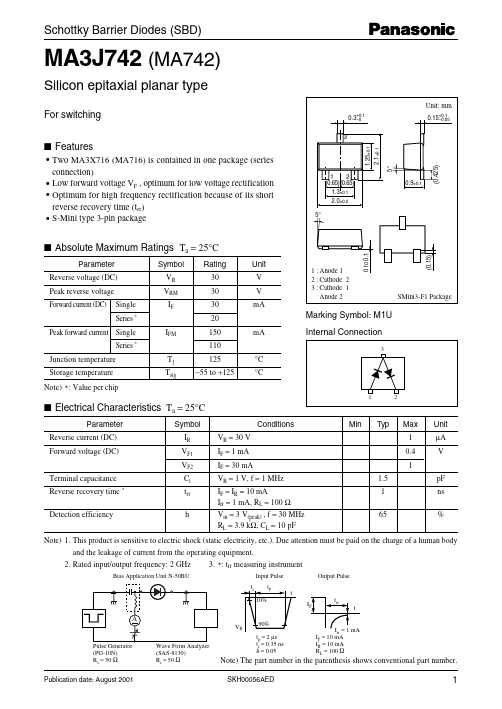

MA3J742资料

Ta = 125°C

0.8 IF = 30 mA 0.6

10

10

75°C

1

1 25°C 10−1

0.4 3 mA 0.2 1 mA

10−1

10−2

0

0.2

0.4

0.6

0.8

1.0

1.2

10−2

0

5

10

15

20

25

30

0 −40

0

40

80

120

160

Forward voltage VF (V)RevBiblioteka rse voltage VR (V)

1

元器件交易网

MA3J742

IF V F

103 103

IR V R

1.0

VF Ta

102

75°C 25°C Ta = 125°C −20°C

102

Forward current IF (mA)

Reverse current IR (µA)

Forward voltage VF (V)

元器件交易网

Schottky Barrier Diodes (SBD)

MA3J742 (MA742)

Silicon epitaxial planar type

Unit: mm

For switching

3

0.3+0.1 –0

0.15+0.1 –0.05

• Two MA3X716 (MA716) is contained in one package (series connection) • Low forward voltage VF , optimum for low voltage rectification • Optimum for high frequency rectification because of its short reverse recovery time (trr) • S-Mini type 3-pin package

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

RoHS

DO NOT LOOK DIRECTLY AT LED WITH UNSHIELDED EYES OR DAMAGE TO RETINA MAY OCCUR.

OPTEK reserves the right to make changes at any time in order to improve design and to supply the best product possible. OPTEK Technology Inc. — 1645 Wallace Drive, Carrollton, Texas 75006 Phone: (972) 323-2200 or (800) 341-4747 FAX: (972) 323-2396 visibleLED@ Issue A.2 09/08 Page 1 of 1

Product Photo Here

OPA742_ (23° Beam Angle)

The OPA742 Series are designed for areas where lighting intensity and reliability are essential. The light beam angle of 23° is ideal for illuminating areas close or a long distances from the device while requiring minimal space. A High Performance Heat Spreader (HPHS) is used to ensure the best heat dissipation of any light assembly in the industry. For custom colors and design contact your OPTEK representative.

/

分销商库存信息:

OPTEK-TECHNOLOGY OPA742W23

OPA742 Series

1 Watt Light Spot on OptoTherm Linear Heat Spreader with Lens

OPA742 Series

• • • • •

1 watt LED on round substrate Mono-color per strip (Blue, Green, Red, Yellow, White) Component beam angle option 23° Universal connector (Tyco 2-292173-2 mates with 173977-2) RoHS Compliant

Electrical / Optical Characteristics: TA=25°C, IF=350mA

Part Number Typical Forward Voltage (V) Luminous Flux (lm) Beam Angle Color Dominant Wavelength 587 nm 470 nm 530 nm 625 nm 6,500°K

OPA742Y23 OPA742B23 OPA742G23 OPA742R23 OPA742W23

2.5 3.6 3.6 2.5 3.6

22 8 41 30 41 23°

Yellow Blue Green Red White

+ Volt-

GroundБайду номын сангаас

OPA742_

See OVSP_BCR4 for component specifications