第9章 单片机串行扩展

合集下载

轻轻巧巧第9章

方法2:软件模拟开发系统 基于Proteus(Keil)仿真软件的设计与开发工具

第9章单片机应用系统的设计与开发

9.1单片机系统的设计开发过程 9.2单片机系统的可靠性技术 9.3单片机系统设计开发应用举例 9.4单片机串行扩展单元介绍

第9章单片机应用系统的设计与开发

智能仪器是一种依靠嵌入式计算机技术发展的新型电子测控 单元,其基本功能是根据传感器的实时信号和仪器设定的目 标参数进行测量与控制。

第9章单片机应用系统的设计与开发

一个完整的单片机应用系统由单片机最小应用系统、前向 通道、后向通道、人机交互通道与计算机相互通道组成。

第9章单片机应用系统的设计与开发

单片机最小系统 最小应用系统——具有最简单配置的单片机系统

P2.7 P2.0 CE A15

~ ~

~

A8 A7

803 1

地址 锁存器 P0.7 P0.0 PSEN

S0 S1 S2 S3 S4 S5 S6 S7

U4 C1

3 Q0 30pF

RP1 C2

30pF

1

C1/->

VCC

&

1D 4 5 6 Q1 Q2 Q3 Q4 Q5 Q6 Q7 VCC

X1

19 CRYSTAL

U1

XTAL1 P0.0/AD0 P0.1/AD1 P0.2/AD2 P0.3/AD3 P0.4/AD4 P0.5/AD5 P0.6/AD6 P0.7/AD7 P2.0/A8 P2.1/A9 P2.2/A10 P2.3/A11 P2.4/A12 P2.5/A13 P2.6/A14 P2.7/A15 P3.0/RXD P3.1/TXD P3.2/INT0 P3.3/INT1 P3.4/T0 P3.5/T1 P3.6/WR P3.7/RD 39 38 37 36 35 34 33 32 21 22 23 24 25 26 27 28 10 11 12 13 14 15 16 17 P20 P21 P22 P23 P24 P25 P26 P27 P30 P31 P32 2 P20 PNP P21 P36 P22 P23 P37 2 3 4 5 6 7 8 9 19 1

单片机原理与接口技术课件 单片机系统常用串行扩展技术

I2C总线的外围扩展器件大都是CMOS器件,总 线有足够的电流驱动能力,因此总线扩展的节点数 由负载电容特性决定,I2C总线的驱动能力为400 pF。 可根据器件的I2C总线接口的等效电容确定可扩展的 器件数目和总线的长度,以减小总线传输的延迟和 出错。

*

单片机原理与接口技术(第2版).李晓林.电子工业出版社

----总线信号,时钟

(4)数据信号:地址和数据均以字节为单位,且高位在前,低位在 后。数据接收方每接收一字节数据都产生一个应答信号。发送 器必须在接收器发送应答信号前,预先释放对SDA线的控制 (SDA=1),以便主控器件对SDA线上应答信号的检测。

返回目录

10

9.1.1 I2C串行总线

----总线器件寻址方式

器件的地址由4位固定位和3位可编程位组成。固定位由生产

厂家给出,用户不能改变。可编程位与器件的地址管脚的连接相 对应,当系统中使用了多个相同芯片时可以进行正确的访问。

不同的器件有时会有 相同的固定地址编码,例 如静态RAM器件PCF8570 和EEPROM器件PCF8582 的固定位均为1010,此时 通过可编程位进行区分, 如图所示。

数据接收方可以接收数据时, 产生应答信号(ACK) 。当主器 件接收从器件送来的最后一个数据后, 必须给从器件发一个非 应答信号(NACK), 令从器件释放SDA信号线, 这样主器件可 以发送终止信号来结束数据的传输。

*

单片机原理与接口技术(第2版).李晓林.电子工业出版社

返回目录

13

9.1.1 I2C串行总线

返回目录

9.1.1 I2C串行总线

----特性

由于I2C总线的双向特性,总线上的主器件和从器件都可能 成为发送器和接收器。

第9章 串行总线接口技术

addata = addata <<1; /*左移一位,先读取为高位,后读为低位*/

CLK=0;

/*令CLK恢复为0*/

_nop_( );

_nop_( );

}

return addata; /*返回A/D转换值*/

}

void delay ( ) { unsigned char i;

for(i=0;i<20;i++) }

2020/3/2

图9-7 TLC561519的时序

16位数据的高4位和低2位不会被转换,待转换数据输入的格式 见表9-1:

表9-1 D/A转换数据输入格式

输入序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 输入数据 × × × × D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 0 0

2020/3/2

图9-3 TLC549与单片9 机的硬件连接

A/D转换的汇编语言程序:

DO BIT P1.2

CLK BIT P1.1

CS BIT P1.0

… TLC549_AD: CLR A

; TLC549 A/D转换子程序,转换结果在A中

CLR CLK

MOV R5,#08H

CLR CS LOOP: SETB CLK

2020/3/2

图9-6 TLC56151的8 引脚

2、TLC5615的时序

TLC5615的时序如图9-7所示。/CS当为低电平时,在每一个 SCLK时钟的上升沿从DIN 引脚移入一位数据,高位在前,低位 在后。经16个时钟后,/CS的上升沿将16 位移位寄存器的10 位 有效数据锁存到10位DAC寄存器, 供DAC电路进行转换。

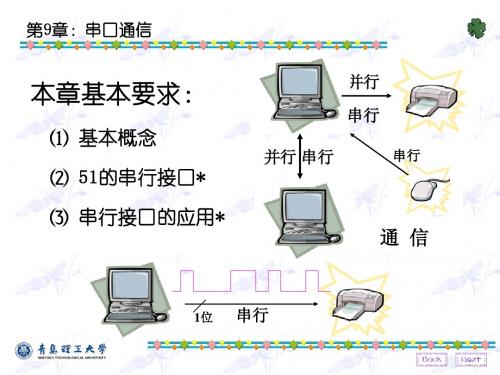

单片机教程 第9章-串口通信

9.2

MCS-51单片机串行接口

方式1所传送的波特率取决于定时器T1的溢出 率和特殊功能寄存器PCON中SMOD的值,即方式1的

波特率=(2SMOD/32)×定时器T1的溢出率。

②方式1接收:当串行口置为方式1,且REN=1 时,串行口处于方式1输入状态。它以所选波特率 的16倍的速率采样RXD引脚状态。

示字符的结束。异步传送的字符格式如图所示。 ①字符帧:也叫数据帧,由起始位、数据位、奇 偶校验位和停止位4个部分组成。

9.1

串行通信基础

9.1

串行通信基础

②波特率:就是数据的传送速率,即每秒钟传送的 二进制位数,单位:位/秒。 说明:要求发送端与接收端的波特率必须一 致。波特率越高,传送速度越快。

9.1

串行通信基础

下图为以上两种通信方式的示意图。由图可知, 假设并行传送N位数据所需时间为T,那么串行传送 的时间至少为NT,实际上总是大于NT的。

9.1

串行通信基础

9.1.1

串行通信的分类

1、异步通信

异步传送的特点是数据在线路上的传送不连

续。在传送时,数据是以一个字符为单位进行传送

的。它用一个起始位表示字符的开始,用停止位表

;清0接收中断标志 ;接收数据 ;取奇偶校验位 ;偶校验时转L1 ;奇校验时RB8为0转出错处理

;偶校验时RB8为1转出错处理 ;奇偶校验对时存入数据 ;修改指针 ;恢复现场 ;中断返回 ;出错处理 ;中断返回

L1: L2:

ERR:

9.2

MCS-51单片机串行接口

4、方式3 方式3为波特率可变的9位异步通信方式,除了

fOSC 2 SMOD 64

T 1溢出率2 SMOD 32

单片机串行扩展

图9.18 通过UART的串行存储器扩展连接

9.5.2 串行接口的软件模拟

图9.19 80C51与PCF8582的模拟I2C总线连接

9.5.3 I2C总线接口芯片PCF8584 1. PCF8584的逻辑结构

图9.20

PCF8584芯片的逻辑结构图

2. 通过PCF8584将80C51接入I2C总线

图9.14 SAA1064的引脚排列

2. SAA1064的接口连接和操作

图9.15 SAA1064静态显示方式接口连接

图9.16

SAA1064动态显示方式接口连接

3. SAA1064的特点 9.5 单片机80C51的串行扩展 9.5.1 通过UART进行串行程序存储器扩展

图9.17 93C46芯片引脚排列

(1)总线空闲 (2)占有总线和释放总线 (3)时钟信号和数据信号

图9.3 I2C总线的时钟信号和数据信号

(4)启动信号和停止信号

图9.4 I2C总线的启动信号和停止信号

(5)应答信号和非应答信号

图9.5 I2C总线的应答信号和非应答信号

(6)等待状态 9.2.2 I2C总线数据传输方式 1. 基本数据传输格式

控、E2PROM等功能的X5045等。

I2C总线

I2C(Inter Integrated Circuit )常译为 内部集成电路总线,或集成电路间总线,它是 由Philips公司推出的芯片间串行传输总线。 9.2.1 I2C总线结构和信号 1. I2C总线结构

2. I2C总线器件接入

3. I2C总线的状态和信号

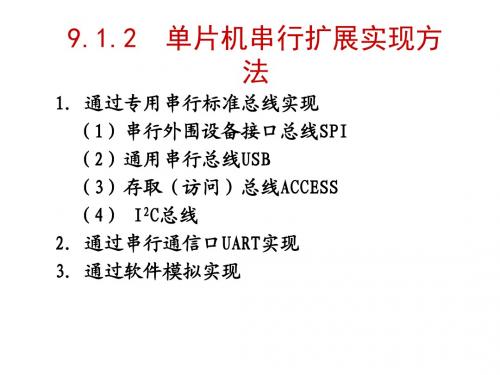

9.1.2 单片机串行扩展实现方 法

1. 通过专用串行标准总线实现 (1)串行外围设备接口总线SPI (2)通用串行总线USB (3)存取(访问)总线ACCESS (4) I2C总线 2. 通过串行通信口UART实现 3. 通过软件模拟实现

单片机原理与接口技术》第9章MCS51单片机的IO扩展ppt课件

图9-4 合并输入输出口

• 正如前面所提到的,扩展I/O口和扩展外部RAM一样,因此访 问外部I/O口就像访问外部 RAM一样,用的是 MOVX类指令。

• 对于图9-4,如果需要实现的功能是按下任意一个按键,对应的 LED发光,则程序如下:

• LOOP: MOV DPTR,#0FEFFH ;数据指针指向扩展I/O 地址

个输出端口、1个时钟输入端 CLK(上升沿有效)和1个允许控制 端OE,其功能见表9-1。(见教材P190页) • 如图9-1所示,OE与P2.7相连,74LS377的地址为7FFFH; • 若与P2.0相连,则地址相应为0EFFH。

图9-1 MCS-51扩展输出口74LS377

• 【例9.1】 若以图9-1为接口电路,将片内RAM地址为50H单元 的数据通过该电路输出。程序清单如下:

• 输入控制信号由P2.0和RD合成,当二者同时为低电平时,或门

• 与74HC244相连的按键开关没有按下时,输入全为1;若按下某 键则所在的线输入为0。

• 可见,输入输出都是在P2.0为0时有效,因此它们的口地址为 0FEFFH,即占用相同的地址空间。但是由于分别用RD和WR信号 控制,因此不会发FFFH ;数据指针指向74LS377

•

MOV A,50H

;输出的50H单元数据送累加器A

•

MOVX @DPTR,A

;P0口将数据通过74LS377输出

• (2)用74LS374扩展并行输出口

• 74LS374是具有三态输出的8D边沿触发器,其功能与 74LS377相似,见表9-2。(见教材P190页)

用相同的指令。

• (2)扩展多片I/O芯片或多个I/O设备时,注意总线的驱动能 力问题;

• (3)扩展I/O口的目的是为了单片机与外部设备进行信息交换 而设置的一个输入输出通道,I/O口最终与外设相连。

• 正如前面所提到的,扩展I/O口和扩展外部RAM一样,因此访 问外部I/O口就像访问外部 RAM一样,用的是 MOVX类指令。

• 对于图9-4,如果需要实现的功能是按下任意一个按键,对应的 LED发光,则程序如下:

• LOOP: MOV DPTR,#0FEFFH ;数据指针指向扩展I/O 地址

个输出端口、1个时钟输入端 CLK(上升沿有效)和1个允许控制 端OE,其功能见表9-1。(见教材P190页) • 如图9-1所示,OE与P2.7相连,74LS377的地址为7FFFH; • 若与P2.0相连,则地址相应为0EFFH。

图9-1 MCS-51扩展输出口74LS377

• 【例9.1】 若以图9-1为接口电路,将片内RAM地址为50H单元 的数据通过该电路输出。程序清单如下:

• 输入控制信号由P2.0和RD合成,当二者同时为低电平时,或门

• 与74HC244相连的按键开关没有按下时,输入全为1;若按下某 键则所在的线输入为0。

• 可见,输入输出都是在P2.0为0时有效,因此它们的口地址为 0FEFFH,即占用相同的地址空间。但是由于分别用RD和WR信号 控制,因此不会发FFFH ;数据指针指向74LS377

•

MOV A,50H

;输出的50H单元数据送累加器A

•

MOVX @DPTR,A

;P0口将数据通过74LS377输出

• (2)用74LS374扩展并行输出口

• 74LS374是具有三态输出的8D边沿触发器,其功能与 74LS377相似,见表9-2。(见教材P190页)

用相同的指令。

• (2)扩展多片I/O芯片或多个I/O设备时,注意总线的驱动能 力问题;

• (3)扩展I/O口的目的是为了单片机与外部设备进行信息交换 而设置的一个输入输出通道,I/O口最终与外设相连。

单片机串行口IO端口扩展介绍

是否兼容

08

检查串行口IO端 口的电源供应是

否正常

09

检查串行口IO端 口的接地是否正

确

10

检查串行口IO端 口的抗干扰措施

是否正确

串行口IO端口扩展应 用案例

实际应用场景

智能家居:通过串行口IO端口扩展,实现对家电 设备的远程控制和监测。

工业自动化:通过串行口IO端口扩展,实现对工 业设备的远程监控和操作。

单片机与网络设备通信:通过串行口扩展IO端口,实现 单片机与网络设备的通信,实现网络控制和数据传输。

串行口IO端口扩展硬 件设计

硬件结构设计

单片机串行口IO端口 扩展硬件主要包括单 片机、串行口、IO端 口扩展芯片等部分。

IO端口扩展芯片负责 将单片机的IO端口进 行扩展,增加硬件的

IO端口数量。

利用单片机的IO 端口进行扩展

使用串行口扩展 板进行扩展

扩展应用实例

单片机与传感器通信:通过串行口扩展IO端口,实现单 片机与各种传感器的通信。

单片机与显示屏通信:通过串行口扩展IO端口,实现单 片机与显示屏的通信,显示各种信息。

单片机与无线模块通信:通过串行口扩展IO端口,实现 单片机与无线模块的通信,实现无线数据传输。

端口扩展程序

1 端口扫描:检测可用端口并进行编号 2 端口配置:设置端口参数,如波特率、数据位、停止位等 3 数据收发:实现数据的接收和发送 4 错误处理:检测并处理通信错误,如超时、数据丢失等 5 端口管理:实现端口的添加、删除、修改等操作 6 用户界面:提供友好的用户界面,方便用户操作和查看端口状态

校验方式等

串行通信接口:用于连 接串行设备的物理接口

串行通信波特率:数据 传输的速率,单位为bps

08

检查串行口IO端 口的电源供应是

否正常

09

检查串行口IO端 口的接地是否正

确

10

检查串行口IO端 口的抗干扰措施

是否正确

串行口IO端口扩展应 用案例

实际应用场景

智能家居:通过串行口IO端口扩展,实现对家电 设备的远程控制和监测。

工业自动化:通过串行口IO端口扩展,实现对工 业设备的远程监控和操作。

单片机与网络设备通信:通过串行口扩展IO端口,实现 单片机与网络设备的通信,实现网络控制和数据传输。

串行口IO端口扩展硬 件设计

硬件结构设计

单片机串行口IO端口 扩展硬件主要包括单 片机、串行口、IO端 口扩展芯片等部分。

IO端口扩展芯片负责 将单片机的IO端口进 行扩展,增加硬件的

IO端口数量。

利用单片机的IO 端口进行扩展

使用串行口扩展 板进行扩展

扩展应用实例

单片机与传感器通信:通过串行口扩展IO端口,实现单 片机与各种传感器的通信。

单片机与显示屏通信:通过串行口扩展IO端口,实现单 片机与显示屏的通信,显示各种信息。

单片机与无线模块通信:通过串行口扩展IO端口,实现 单片机与无线模块的通信,实现无线数据传输。

端口扩展程序

1 端口扫描:检测可用端口并进行编号 2 端口配置:设置端口参数,如波特率、数据位、停止位等 3 数据收发:实现数据的接收和发送 4 错误处理:检测并处理通信错误,如超时、数据丢失等 5 端口管理:实现端口的添加、删除、修改等操作 6 用户界面:提供友好的用户界面,方便用户操作和查看端口状态

校验方式等

串行通信接口:用于连 接串行设备的物理接口

串行通信波特率:数据 传输的速率,单位为bps

第9章 单片机系统常用串行扩展技术

3.I C总线的器件寻址方式

2

I2C 总线上连接的器件都是总线上的节点,每个时刻只 有一个主控器件操控总线。每个器件都有一个唯一确定的地 址,主控器件通过这个地址实现对从器件的点对点数据传输。 器件的地址由7位组成,其后附加了1位方向位,确定数据的 传输方向。这8位构

成了传输起始状态S后的

第一个字节,如图所示。

3

9.1.1 I2C串行总线

----特性

由于I2C总线的双向特性,总线上的主器件和从器件都可能 成为发送器和接收器。

在主器件发送数据或命令时,主器件是发送器(主发送 器); 在主器件接收从器件的数据时,主器件为接收器(主接收 器); 从器件在接收主器件命令或数据时,从器件是接收器(从 接收器); 从器件向主器件返回数据时则是发送器(从发送器)。

2

9.1 常用串行总线协议

9.1.1 I C串行总线

2

----术语

为了简化集成电路之间的互连,Philips公司开发出一种 标准外围总线互连接口,称为“集成电路间总线”或“内部 2 2 集成电路总线” I C( Inter-IC)。 I C 总线是一个两线双向 串行总线接口标准,采用这种接口标准的器件只需要使用两 条信号线与单片机进行连接,就可以完成单片机与接口器件 之间的信息交互。 其相关的术语有: 发送器(Transmitter):发送数据到总线的器件; 接收器(Receiver):从总线接收数据的器件; 主器件(Master):即主控器件,初始化发送、产 生时钟信号和终止发送的器件; 从器件(Slave):被主控器件寻址的器件。

15

9.1.1 I2C串行总线

----数据传输方式

(3) 复合模式。主器件向从器件发送命令或数据后,再次向

单片机原理及应用第9章 系统扩展技术PPT课件

存储单元数决定,对于8K×8 容量的芯 片需要13 根地址线A12~A0。

然后将余下的高位地址线分别接到

个存储芯片的片选端CS,称为线选。

下图是利用线选法,用3 片2746A 扩展24K×8 位 EPROM 的电路图:

用线选法实现片选

各芯片的地址范围如下:

2.

译码法寻址就是利用地址译码器对系统的片外高位地址 进行译码, 以其译码输出作为存储器芯片的片选信号, 将地址 划分为连续的地址空间块, 避免了地址的间断。

接口的含义: 接口是连接单片机与外围电路、芯片、设

备(如I/O设备、A/D、D/A设备)的中间环节。 接口牵涉到包括外围电路、设备、芯片的结构、 使用方法、时序要求;单片机本身的硬件、软 件资源等很多问题。

接口技术要解决系统扩展时单片机与相应 芯片的接口(如地址总线、数据总线、控制总 线的连接)与编程问题。

在单片机应用系统中, 扩展的三总线上挂接很多负载, 如存 储器、并行接口、A/D接口、显示接口等, 但总线接口的负载 能力有限, 因此常常需要通过连接总线驱动器进行总线驱动。

总线驱动器对于单片机的I/O口只相当于增加了一个TTL 负载, 因此驱动器除了对后级电路驱动外,还能对负载的波动变 化起隔离作用。

在对TTL 负载驱动时, 只需考虑驱动电流的大小; 在 对MOS负载驱动时, MOS负载的输入电流很小, 更多地 要考虑电平的兼容和分布电容的电流。

一般TTL 电平和CMOS 电平是不兼容的,CMOS 电路能驱 动 TTL 电路 ,而 TTL 电路一般 不能驱动 CMOS 电路,在TTL 电路和CMOS 电路混用的系统中, 应特别注意。

2. 静态RAM芯片

I/O 0~7:数据线 A0~A12:地址线 CE、CE:片选线 OE:输出使能 WE:写入使能 VCC、GND:电源 NC:未使用

然后将余下的高位地址线分别接到

个存储芯片的片选端CS,称为线选。

下图是利用线选法,用3 片2746A 扩展24K×8 位 EPROM 的电路图:

用线选法实现片选

各芯片的地址范围如下:

2.

译码法寻址就是利用地址译码器对系统的片外高位地址 进行译码, 以其译码输出作为存储器芯片的片选信号, 将地址 划分为连续的地址空间块, 避免了地址的间断。

接口的含义: 接口是连接单片机与外围电路、芯片、设

备(如I/O设备、A/D、D/A设备)的中间环节。 接口牵涉到包括外围电路、设备、芯片的结构、 使用方法、时序要求;单片机本身的硬件、软 件资源等很多问题。

接口技术要解决系统扩展时单片机与相应 芯片的接口(如地址总线、数据总线、控制总 线的连接)与编程问题。

在单片机应用系统中, 扩展的三总线上挂接很多负载, 如存 储器、并行接口、A/D接口、显示接口等, 但总线接口的负载 能力有限, 因此常常需要通过连接总线驱动器进行总线驱动。

总线驱动器对于单片机的I/O口只相当于增加了一个TTL 负载, 因此驱动器除了对后级电路驱动外,还能对负载的波动变 化起隔离作用。

在对TTL 负载驱动时, 只需考虑驱动电流的大小; 在 对MOS负载驱动时, MOS负载的输入电流很小, 更多地 要考虑电平的兼容和分布电容的电流。

一般TTL 电平和CMOS 电平是不兼容的,CMOS 电路能驱 动 TTL 电路 ,而 TTL 电路一般 不能驱动 CMOS 电路,在TTL 电路和CMOS 电路混用的系统中, 应特别注意。

2. 静态RAM芯片

I/O 0~7:数据线 A0~A12:地址线 CE、CE:片选线 OE:输出使能 WE:写入使能 VCC、GND:电源 NC:未使用

第九章单片机系统扩展

ALE PSEN P2口 P0口

输出PCH

输出PCH

输出PCH

输出PCH

PCL

指令 PCL

指令

PCL

指令

PCL

指令

PCL

80C51系列单片机的CPU在访问片外ROM的一个机器周期内, 信号ALE出现两次(正脉冲),ROM选通信号也两次有效, 这说明在一个机器周期内,CPU两次访问片外ROM,也即在 一个机器周期内可以处理两个字节的指令代码,所以在

P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7 EA ALE

D0 D1

QQO1

D2 Q2

74HC373

D3 Q3

D4 Q4 D5 Q5

D6 Q6

D7 Q7

G OE

OE A8 A9 A10 A11 A12

A0

A1

A2

A3

A4

A5 A6

27C64

A7

D0

D1

D2

D3

D4

D5

OE

外部ROM的状态与地址线A15的关系表

ROM引脚 /CE 单片机引脚 A15

0 0 1 1

A14~A8 P2口

00000000 11111111 00000000 11111111

A7~A0 P0口

00000000 11111111 00000000 11111111

地址范围

0000H~ 07FFH 8000H FFFFH

8051 8751

EA

9.1 并行扩展概述

并行扩展器件寻址分两步: 1)器件芯片的寻址 -> 片选 2)芯片内部存储单元的寻址

并行扩展器件寻址主要是研究芯片的寻址 问题,目前常用的有两种方法:线选法和译码 法。

单片机的串行扩展技术

Loop:

CLR MOVC CJNE AJMP

A A, @A+DPTR A, #0x55, Loop1 Start

; 清0累加器A ; 查表,取待传送的数据 ; 是否“结束码”?否,则跳转到Loop1

输入数据为0

传送前8位数据,即段选位 ACALL HC164_Serial_Change_Parallel ; 先传数段选位 MOV A, #0x00 理想的实验效果: 位选位全部置“0” 将选通所有数码管 ACALL HC164_Serial_Change_Parallel ; 后传送位选位,全部置“0” Loop1: ACALL Delay ; 增加延时时间,动态显示效果更明显 输入数据 ACALL Delay INC 0x6F, DPTR0x5B, 0x4F, 0x66, 0x6D, 0x7D, 0x07, 0x7F, 0x6F ; 0~9字符表 ; 数据指针加1,取下一个码 .DB 0x06, 列 AJMP Loop .DB 0x55 表 ……

HC164_Serial_Change_Parallel: MOV Send_1_bit_Data: RLC MOV R6, #0x08

A中存储8位数据D7~D0 带进位左移,依次将D7~D0 ; 传送1位数据 中的数据移入进位C A ; 将A中的最高位左移到进位位C ; 将进位位C的内容送到P1.0口AB端

R5, A 将A中的数据传送到U1 ; 保存待传送的数据 HC164_Serial_Change_Parallel ; 调用8位串入并出送数子程序 A, R5 ; 取待传送的数据 HC164_Serial_Change_Parallel ; 调用8位串入并出送数子程序 Delay 将A中的数据传送到U1, DPTR U1中的数据传送到U2 ; 数据指针加1,取下一个码 Loop

第9章 串行总线接口技术PPT课件

Microwire总线及单总线(1-Wire BUS)。

串行扩展总线的应用是单片机目前发展的一种趋势。AT89系列

单片机利用自身的通用并行线可以模拟多种串行总线时序信号,

因此可以充分利用各种串行接口芯片资源。本章主要介绍I2C总线、

SPI总线及单总线(1-Wire BUS)的基本知识、常用的串行总线接

口器件及和单片机的接口应用。

2020/7/17

4

4

9.1 SPI串行总线接口技术

9.1.1 SPI串行总线简介

SPI接口的全称是“Serial Peripheral Interface”,意为串行外

围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外

2020/7/17

图9-2 TLC5499的时序

9

TLC549没有启动控制端,只要读走前一次数据后马上就进行 新的转换,转换完成后就进入保持状态,转换时间为36个系统时 钟周期,最大为17uS。没有转换完成标志信号,只要采用延时 操作即可控制每次读取数据的操作。

3.TLC549与单片机的接口

TLC549与单片机的连接如图9-3所示。采用P1.0~P1.2连接 TLC549的串行接口。

2020/7/17

3

第9章 串行总线接口技术

由于数据的串行传输连线少,因而采用串行总线扩展技术可以

使系统的硬件设计简化,系统的体积减小,同时,系统的更改和

扩充更为容易。

目前,单片机应用系统中常用的串行扩展总线有:I2C(Inter

IC BUS)总线、SPI(Serial Peripheral Interface)总线、

单片机原理及接口技术(C51编程)第9章 系统并行扩展

供低8位地址和8位双向数据总线。片外数据存储器RAM的读和写由 AT89S51的 RD*(P3.7)和WR*(P3.6)信号控制,而片外程序存储器 EPROM的输出端允许(OE*)由AT89S51单片机的读选通信号PSEN*控制 。尽管与EPROM地址空间范围都相同,但由于是两个不同空间,控制信号 不同,故不会发生数据冲突。

14

由表9-2可见,当译码器输入为某一固定编码时,其8个输出引脚Y0*~ Y7*中仅有1个引脚输出为低,其余全为高。而输出低电平的引脚恰好作为 片选信号。

(2)74LS139 双2-4译码器。两个译码器完全独立,分别有各自的 数据输入端、译码状态输出端以及数据输入允许端,其引脚如图9-4所示 ,其中1组的真值表见表9-3。

32

9.2.2 读写片外RAM的操作时序 AT89S51单片机对片外RAM的读和写两种操作时序的基本过程是相同的。 1.读片外RAM的时序 AT89S51单片机若外扩一片RAM,应将其引脚与RAM芯片的引脚连接,引

脚与芯片引脚连接。ALE信号的作用是锁存低8位地址。 AT89S51单片机读片外RAM的时序如图9-11所示。

第9章 单片机系统的并行 扩展

1

AT89S51单片机片内存储器和I/O资源还不能满足需要,需外扩存储器芯 片和I/O接口芯片,即单片机的系统扩展。

系统扩展分为并行扩展和串行扩展,本章介绍应用系统的并行扩展,第12 章介绍串行扩展。

首先介绍AT89S51片外两个存储器空间地址分配,然后介绍如何扩展外部 数据存储器和外部程序存储器以及扩展I/O接口芯片具体设计。

图9-11 AT89S51单片机读片外RAM的操作时序图

在第一个机器周期的S1状态,ALE信号由低变高(见①处),读RAM周 期开始。在S2状态,CPU把低8位地址送到P0口总线上,把高8位地 址送上P2口。ALE的下降沿(见②处),把低8位地址信息锁存到外 部锁存器74LS373内。而高8位地址信息一直锁存在P2口锁存器中( 见③处)。

14

由表9-2可见,当译码器输入为某一固定编码时,其8个输出引脚Y0*~ Y7*中仅有1个引脚输出为低,其余全为高。而输出低电平的引脚恰好作为 片选信号。

(2)74LS139 双2-4译码器。两个译码器完全独立,分别有各自的 数据输入端、译码状态输出端以及数据输入允许端,其引脚如图9-4所示 ,其中1组的真值表见表9-3。

32

9.2.2 读写片外RAM的操作时序 AT89S51单片机对片外RAM的读和写两种操作时序的基本过程是相同的。 1.读片外RAM的时序 AT89S51单片机若外扩一片RAM,应将其引脚与RAM芯片的引脚连接,引

脚与芯片引脚连接。ALE信号的作用是锁存低8位地址。 AT89S51单片机读片外RAM的时序如图9-11所示。

第9章 单片机系统的并行 扩展

1

AT89S51单片机片内存储器和I/O资源还不能满足需要,需外扩存储器芯 片和I/O接口芯片,即单片机的系统扩展。

系统扩展分为并行扩展和串行扩展,本章介绍应用系统的并行扩展,第12 章介绍串行扩展。

首先介绍AT89S51片外两个存储器空间地址分配,然后介绍如何扩展外部 数据存储器和外部程序存储器以及扩展I/O接口芯片具体设计。

图9-11 AT89S51单片机读片外RAM的操作时序图

在第一个机器周期的S1状态,ALE信号由低变高(见①处),读RAM周 期开始。在S2状态,CPU把低8位地址送到P0口总线上,把高8位地 址送上P2口。ALE的下降沿(见②处),把低8位地址信息锁存到外 部锁存器74LS373内。而高8位地址信息一直锁存在P2口锁存器中( 见③处)。

单片机系统的扩展

9

数据存储器扩展电路

P2.7 P2.0-P2.4

ALE P0

89C51 +5V

EA WR RD

74LS573

G OE D7 Q7 :: :: D0 Q0

CE A8-A12

CS

A7

: :

6264

A0

D0~D7 WE OE

10

存储器片选信号的连接

• 线选法:地址信号直接连接片选。地址不连续。 • 译码法:地址组合译码后连接片选。增加芯片。 • 编址:地址的确定。

P2.6

D7-0 /CE /CE AD7-0 A10 A9 A8

Q7-0

RAM (2K)

锁存器

/CE D7-0

缓冲器

P2.7 做输出锁存器的片选线

地址范围:011X XXXX XXXX P2X.6XX做X输入缓冲器的片选线

(例:6000H)

地址范围:101X XXXX XXXX XXX(例X:A000H)

2 3 4 5 6 7 8 9

1D 2D 3D 4D 5D 6D 7D 8D

1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q

19 18 17 16 15 14 13 12

P3.6/WR P2.7/A15 P3.7/RD

16 28 17

74HCT245

9 8 7 6 5 4 3 2

A8 A7 A6 A5 A4 A3 A2 A1

74LS138

74HCT573

VCC 1 19 18 17 16 15 14 13 12 11

VCC 1 19 18 17 16 15 14 13 12 11

U4 74LS245-1

DIR

G

A1

B1 A2

数据存储器扩展电路

P2.7 P2.0-P2.4

ALE P0

89C51 +5V

EA WR RD

74LS573

G OE D7 Q7 :: :: D0 Q0

CE A8-A12

CS

A7

: :

6264

A0

D0~D7 WE OE

10

存储器片选信号的连接

• 线选法:地址信号直接连接片选。地址不连续。 • 译码法:地址组合译码后连接片选。增加芯片。 • 编址:地址的确定。

P2.6

D7-0 /CE /CE AD7-0 A10 A9 A8

Q7-0

RAM (2K)

锁存器

/CE D7-0

缓冲器

P2.7 做输出锁存器的片选线

地址范围:011X XXXX XXXX P2X.6XX做X输入缓冲器的片选线

(例:6000H)

地址范围:101X XXXX XXXX XXX(例X:A000H)

2 3 4 5 6 7 8 9

1D 2D 3D 4D 5D 6D 7D 8D

1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q

19 18 17 16 15 14 13 12

P3.6/WR P2.7/A15 P3.7/RD

16 28 17

74HCT245

9 8 7 6 5 4 3 2

A8 A7 A6 A5 A4 A3 A2 A1

74LS138

74HCT573

VCC 1 19 18 17 16 15 14 13 12 11

VCC 1 19 18 17 16 15 14 13 12 11

U4 74LS245-1

DIR

G

A1

B1 A2

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图9.21 80C51与PCF8584接口连接

9.1.2 单片机串行扩展实现方 法

1. 通过专用串行标准总线实现 串行外围设备接口总线SPI (1)串行外围设备接口总线SPI 通用串行总线USB (2)通用串行总线USB 存取(访问)总线ACCESS (3)存取(访问)总线ACCESS (4) I2C总线 通过串行通信口UART UART实现 2. 通过串行通信口UART实现 3. 通过软件模拟实现

图9.18 通过UART的串行存储器扩展连接

9.5.2 串行接口的软件模拟

图9.19 80C51与PCF8582的模拟I2C总线连接

9.5.3 I2C总线接口芯片PCF8584 1. PCF8584的逻辑结构

图9.20

PCF8584芯片的逻辑结构图

2. 通过PCF8584将80C51接入I2C总线

9.2 I2C总线

I2C(Inter Integrated Circuit)常译为 Circuit) 内部集成电路总线,或集成电路间总线, 内部集成电路总线,或集成电路间总线,它是 Philips公司推出的芯片间串行传输总线 公司推出的芯片间串行传输总线。 由Philips公司推出的芯片间串行传输总线。 9.2.1 I2C总线结构和信号 总线结构和信号 1. I2C总线结构

图9.14 SAA1064的引脚排列

2. SAA1064的接口连接和操作

图9.15 SAA1064静态显示方式接口连接

图9.16

SAA1064动态显示方式接口连接

3. SAA1064的特点 9.5 单片机80C51的串行扩展 9.5.1 通过UART进行串行程序存储器扩展

图9.17 93C46芯片引脚排列

(2)引脚地址 9.3 单片机8×C552的I2C总线 9.3.1 8×C552的I2C总线接口电路 1. I2C总线接口的结构

图9.9 8×C552芯片的I2C总线接口框图

2. I2C总线专用寄存器 3. I2C总线中断 9.3.2 8×C552的I2C总线控制机制 1. I2C总线状态码 2. I2C总线协议驱动程序 9.3.3 由8×C552构成的单主I2C总线系统 1. 单主系统应用举例 (1)传输程序设计

P1.0 P1.1 P1.2 P1.3

SS SCK

MCS-51 单片机系统

SPI 从设备 MOSI MISO

图2 MCS-51单片机I/O口模拟SPI总线接口原理图

4.常用SPI串行总线接口的器件 4.常用SPI串行总线接口的器件 常用SPI

• 单片机,如Motorola公司的M68HC08系列、Cygnal公司的C8051F0XX系列、 单片机, Motorola公司的M68HC08系列、Cygnal公司的C8051F0XX系列、 公司的M68HC08系列 公司的C8051F0XX系列 Philips公司的P89LPC93X系列。 Philips公司的P89LPC93X系列。 公司的P89LPC93X系列 • A/D和D/A转换器,如:AD公司的AD7811/12、TI公司的TLC1543、 A/D和D/A转换器, 转换器 AD公司的AD7811/12、TI公司的TLC1543、 公司的AD7811/12 公司的TLC1543 TLC2543、TLC5615等 TLC2543、TLC5615等。 • 实时时钟RTC,如Dallas公司的DS1302/05/06等。 实时时钟RTC, Dallas公司的DS1302/05/06等 RTC 公司的DS1302/05/06 • 温度传感器,如AD公司的AD7816/17/18;NS公司的LM74等。 温度传感器, AD公司的AD7816/17/18;NS公司的LM74等 公司的AD7816/17/18 公司的LM74 • 其他设备,如LED控制驱动器MAX7219、HD7279等,集成看门狗、电压监 其他设备, LED控制驱动器MAX7219、HD7279等 集成看门狗、 控制驱动器MAX7219 PROM等功能的X5045等 等功能的X5045 控、E2PROM等功能的X5045等。

图9.10 单主I2C总线系统的操作流程

(2)中断处理程序 2. 数据传送过程说明 (1)SI08(启动信号正常发出,准备发送SLA+R/w 和接收应答信号) (2)SI18(发出SLA+W后收到应答信号,准备发 第一个数据字节) (3)SI28(发送一个数据字节后收到应答信号,准 备继续发送数据字节或停止信号) 9.4 单片机8×C552的串行扩展 9.4.1 通过I2C总线扩展串行数据存储器 1. PCF8571/8570/8570C芯片概述

图1 单片机与多个SPI串行接口设备典型连接

3.SPI串行总线在MCS-51系列单片机中的实 3.SPI串行总线在MCS-51系列单片机中的实 串行总线在MCS 现

• MCS-51单片机I/O口模拟SPI总线接口原理图如图2所示。 MCS-51单片机I/O口模拟SPI总线接口原理图如图2所示。 单片机I/O口模拟SPI总线接口原理图如图

2. I2C总线器件接入

3. I2C总线的状态和信号

(1)总线空闲 (2)占有总线和释放总线 (3)时钟信号和数据信号

图9.3 I2C总线的时钟信号和数据信号

(4)启动信号和停止信号 )

图9.4 I2C总线的启动信号和停止信号 总线的启动信号和停止信号

(5)应答信号和非应答信号 )

图9.5 I2C总线的应答信号和非应答信号 总线的应答信号和非应答信号

SPI总线技术是 总线技术是Motorola公司推出的一种同步串行接口 总线技术是 公司推出的一种同步串行接口

2.SPI总线系统的构成 2.SPI总线系统的构成

• 单片机与多个SPI串行接口设备典型结构如图1所示。 单片机与多个SPI串行接口设备典型结构如图1所示。 SPI串行接口设备典型结构如图

ห้องสมุดไป่ตู้第9 章

单片机串行扩展

9.1 单片机串行扩展概述

9.1.1 单片机需要串行扩展的原因 1、远距离大范围多目标的单片机控制应用只能 以串行方式进行。 以串行方式进行。 手持无线化单片机控制系统只能用串行方式。 2、手持无线化单片机控制系统只能用串行方式。 3、单片机接入internet只能用串行方式。 单片机接入internet只能用串行方式。 internet只能用串行方式 串行系统的缺点: 串行系统的缺点:速度慢 优点:连线简单,结构简化,成本低。 优点:连线简单,结构简化,成本低。

图9.11 PCF8571/8570/8570C引脚图

图9.12

PCF8571/8570/8570C硬件结构图

2. 数据读/写操作 (1)指定地址写 (2)指定地址读 (3)现行地址读 3. 串行数据存储器扩展连接

图9.13

I2C总线系统中的多片数据存储器扩展

9.4.2 I2C总线的发展 1. 页地址 2. 10位地址方式 (1)10位地址方式的寻址过程 (2)10位地址方式的数据传送格式 9.4.3 通过I2C总线扩展LED显示器 1. LED驱动芯片SAA1064

(6)等待状态 9.2.2 I2C总线数据传输方式 1. 基本数据传输格式

图9.6 I2C总线数据传输格式

2. 主发送方式

图9.7 主发送方式的数据传输格式

3. 主接收方式

图9.8 主接收方式的数据传输格式

9.2.3 器件与器件寻址 1. 器件分类 2. 器件工作方式 3. 器件寻址 (1)器件编址

SPI串行总线 SPI串行总线

1.SPI总线的特点 1.SPI总线的特点 串行外围设备接口:serial peripheral (串行外围设备接口 interface) ) 一般使用4条线 一般使用 条线 串行时钟线( 串行时钟线(SCK) ) 主机输入/从机输出数据线 从机输出数据线MISO 主机输入 从机输出数据线 主机输出/从机输入数据线 从机输入数据线MOSI 主机输出 从机输入数据线 低电平有效的从机选择线SS 低电平有效的从机选择线

9.1.2 单片机串行扩展实现方 法

1. 通过专用串行标准总线实现 串行外围设备接口总线SPI (1)串行外围设备接口总线SPI 通用串行总线USB (2)通用串行总线USB 存取(访问)总线ACCESS (3)存取(访问)总线ACCESS (4) I2C总线 通过串行通信口UART UART实现 2. 通过串行通信口UART实现 3. 通过软件模拟实现

图9.18 通过UART的串行存储器扩展连接

9.5.2 串行接口的软件模拟

图9.19 80C51与PCF8582的模拟I2C总线连接

9.5.3 I2C总线接口芯片PCF8584 1. PCF8584的逻辑结构

图9.20

PCF8584芯片的逻辑结构图

2. 通过PCF8584将80C51接入I2C总线

9.2 I2C总线

I2C(Inter Integrated Circuit)常译为 Circuit) 内部集成电路总线,或集成电路间总线, 内部集成电路总线,或集成电路间总线,它是 Philips公司推出的芯片间串行传输总线 公司推出的芯片间串行传输总线。 由Philips公司推出的芯片间串行传输总线。 9.2.1 I2C总线结构和信号 总线结构和信号 1. I2C总线结构

图9.14 SAA1064的引脚排列

2. SAA1064的接口连接和操作

图9.15 SAA1064静态显示方式接口连接

图9.16

SAA1064动态显示方式接口连接

3. SAA1064的特点 9.5 单片机80C51的串行扩展 9.5.1 通过UART进行串行程序存储器扩展

图9.17 93C46芯片引脚排列

(2)引脚地址 9.3 单片机8×C552的I2C总线 9.3.1 8×C552的I2C总线接口电路 1. I2C总线接口的结构

图9.9 8×C552芯片的I2C总线接口框图

2. I2C总线专用寄存器 3. I2C总线中断 9.3.2 8×C552的I2C总线控制机制 1. I2C总线状态码 2. I2C总线协议驱动程序 9.3.3 由8×C552构成的单主I2C总线系统 1. 单主系统应用举例 (1)传输程序设计

P1.0 P1.1 P1.2 P1.3

SS SCK

MCS-51 单片机系统

SPI 从设备 MOSI MISO

图2 MCS-51单片机I/O口模拟SPI总线接口原理图

4.常用SPI串行总线接口的器件 4.常用SPI串行总线接口的器件 常用SPI

• 单片机,如Motorola公司的M68HC08系列、Cygnal公司的C8051F0XX系列、 单片机, Motorola公司的M68HC08系列、Cygnal公司的C8051F0XX系列、 公司的M68HC08系列 公司的C8051F0XX系列 Philips公司的P89LPC93X系列。 Philips公司的P89LPC93X系列。 公司的P89LPC93X系列 • A/D和D/A转换器,如:AD公司的AD7811/12、TI公司的TLC1543、 A/D和D/A转换器, 转换器 AD公司的AD7811/12、TI公司的TLC1543、 公司的AD7811/12 公司的TLC1543 TLC2543、TLC5615等 TLC2543、TLC5615等。 • 实时时钟RTC,如Dallas公司的DS1302/05/06等。 实时时钟RTC, Dallas公司的DS1302/05/06等 RTC 公司的DS1302/05/06 • 温度传感器,如AD公司的AD7816/17/18;NS公司的LM74等。 温度传感器, AD公司的AD7816/17/18;NS公司的LM74等 公司的AD7816/17/18 公司的LM74 • 其他设备,如LED控制驱动器MAX7219、HD7279等,集成看门狗、电压监 其他设备, LED控制驱动器MAX7219、HD7279等 集成看门狗、 控制驱动器MAX7219 PROM等功能的X5045等 等功能的X5045 控、E2PROM等功能的X5045等。

图9.10 单主I2C总线系统的操作流程

(2)中断处理程序 2. 数据传送过程说明 (1)SI08(启动信号正常发出,准备发送SLA+R/w 和接收应答信号) (2)SI18(发出SLA+W后收到应答信号,准备发 第一个数据字节) (3)SI28(发送一个数据字节后收到应答信号,准 备继续发送数据字节或停止信号) 9.4 单片机8×C552的串行扩展 9.4.1 通过I2C总线扩展串行数据存储器 1. PCF8571/8570/8570C芯片概述

图1 单片机与多个SPI串行接口设备典型连接

3.SPI串行总线在MCS-51系列单片机中的实 3.SPI串行总线在MCS-51系列单片机中的实 串行总线在MCS 现

• MCS-51单片机I/O口模拟SPI总线接口原理图如图2所示。 MCS-51单片机I/O口模拟SPI总线接口原理图如图2所示。 单片机I/O口模拟SPI总线接口原理图如图

2. I2C总线器件接入

3. I2C总线的状态和信号

(1)总线空闲 (2)占有总线和释放总线 (3)时钟信号和数据信号

图9.3 I2C总线的时钟信号和数据信号

(4)启动信号和停止信号 )

图9.4 I2C总线的启动信号和停止信号 总线的启动信号和停止信号

(5)应答信号和非应答信号 )

图9.5 I2C总线的应答信号和非应答信号 总线的应答信号和非应答信号

SPI总线技术是 总线技术是Motorola公司推出的一种同步串行接口 总线技术是 公司推出的一种同步串行接口

2.SPI总线系统的构成 2.SPI总线系统的构成

• 单片机与多个SPI串行接口设备典型结构如图1所示。 单片机与多个SPI串行接口设备典型结构如图1所示。 SPI串行接口设备典型结构如图

ห้องสมุดไป่ตู้第9 章

单片机串行扩展

9.1 单片机串行扩展概述

9.1.1 单片机需要串行扩展的原因 1、远距离大范围多目标的单片机控制应用只能 以串行方式进行。 以串行方式进行。 手持无线化单片机控制系统只能用串行方式。 2、手持无线化单片机控制系统只能用串行方式。 3、单片机接入internet只能用串行方式。 单片机接入internet只能用串行方式。 internet只能用串行方式 串行系统的缺点: 串行系统的缺点:速度慢 优点:连线简单,结构简化,成本低。 优点:连线简单,结构简化,成本低。

图9.11 PCF8571/8570/8570C引脚图

图9.12

PCF8571/8570/8570C硬件结构图

2. 数据读/写操作 (1)指定地址写 (2)指定地址读 (3)现行地址读 3. 串行数据存储器扩展连接

图9.13

I2C总线系统中的多片数据存储器扩展

9.4.2 I2C总线的发展 1. 页地址 2. 10位地址方式 (1)10位地址方式的寻址过程 (2)10位地址方式的数据传送格式 9.4.3 通过I2C总线扩展LED显示器 1. LED驱动芯片SAA1064

(6)等待状态 9.2.2 I2C总线数据传输方式 1. 基本数据传输格式

图9.6 I2C总线数据传输格式

2. 主发送方式

图9.7 主发送方式的数据传输格式

3. 主接收方式

图9.8 主接收方式的数据传输格式

9.2.3 器件与器件寻址 1. 器件分类 2. 器件工作方式 3. 器件寻址 (1)器件编址

SPI串行总线 SPI串行总线

1.SPI总线的特点 1.SPI总线的特点 串行外围设备接口:serial peripheral (串行外围设备接口 interface) ) 一般使用4条线 一般使用 条线 串行时钟线( 串行时钟线(SCK) ) 主机输入/从机输出数据线 从机输出数据线MISO 主机输入 从机输出数据线 主机输出/从机输入数据线 从机输入数据线MOSI 主机输出 从机输入数据线 低电平有效的从机选择线SS 低电平有效的从机选择线