根据NiosII的流水灯设计

基于Nios II的LED显示屏控制器设计

基于Nios II的LED显示屏控制器设计LED显示屏作为最大的广告屏运用解决方案,LED显示屏的设计与生产,让我们更加的关注LED显示屏可用性的过程。

目前的LED显示屏按火枪手据传输的方式分为两类,一是同步实时显示,二是异步通信更新数据。

目前是以同步传输的方式更为常见。

通常,异步通信控制方式只能将屏幕作为一个完整的区域显示,对于较大屏幕的显示系统,有时需要将整屏分为若干个窗口分别显示不同的内容,且内容的更新只是某一个或几个窗口。

针对这种情况,本文提出了一种基于Nios II 32位处理器的设计方案,能有效地实现单屏幕多窗口的任意位置显示,使得显示方式更加灵活方便。

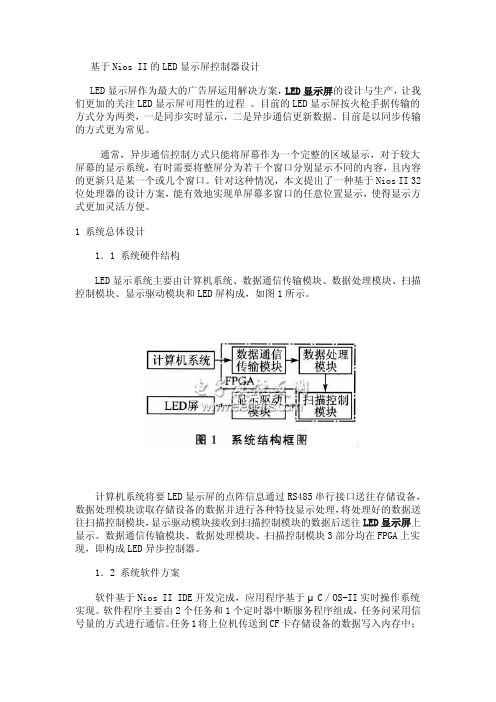

1 系统总体设计1.1 系统硬件结构LED显示系统主要由计算机系统、数据通信传输模块、数据处理模块、扫描控制模块、显示驱动模块和LED屏构成,如图1所示。

计算机系统将要LED显示屏的点阵信息通过RS485串行接口送往存储设备,数据处理模块读取存储设备的数据并进行各种特技显示处理,将处理好的数据送往扫描控制模块,显示驱动模块接收到扫描控制模块的数据后送往LED显示屏上显示。

数据通信传输模块、数据处理模块、扫描控制模块3部分均在FPGA上实现,即构成LED异步控制器。

1.2 系统软件方案软件基于Nios II IDE开发完成,应用程序基于μC/OS-II实时操作系统实现。

软件程序主要由2个任务和1个定时器中断服务程序组成,任务问采用信号量的方式进行通信。

任务1将上位机传送到CF卡存储设备的数据写入内存中;任务2从内存中读取数据并进行分析处理,把分析处理完的数据送往扫描控制模块。

为了充分利用μC/OS-II的实时性和多任务的特点,采用嵌入式文件系统进行数据管理。

2 控制系统硬件部分设计数据处理模块由Nios II软核CPU、1片SDRAM和1片Flash存储器组成。

Nios II软核CPU是整个控制器的核心,负责数据的处理;sDRAM作为CPU处理数据时的缓存使用;Flash存储器用于存储点阵信息数据和LED屏显示控制参数。

实验三基于QuartusII的流水灯设计仿真

实验收获与体会

理论与实践相结合

通过本次实验,我们将数字电路设计与FPGA应用开发的理论知识与实践相结合,加深了对理论知识的理解,提高了 实际操作能力。

团队合作的重要性

在实验过程中,我们小组成员之间进行了充分的讨论和交流,共同解决问题。这使我们深刻体会到团队合作在解决问 题中的重要性。

不断探索与创新

03 通过设计实现流水灯,培养数字电路设计能力。

实验背景

FPGA(现场可编程门阵列)是一种可编artus II是Altera公司推出的一款FPGA开发软件,提供了完整的FPGA设计流程, 包括设计输入、综合、布局布线、仿真和下载等。

Verilog是一种硬件描述语言,用于描述数字电路的行为和结构,广泛应用于FPGA 设计和ASIC设计领域。

高度集成

Quartus II软件集成了设计、编译、仿真和编程等所有必要 的工具,方便用户进行FPGA开发。

高效编译

Quartus II软件采用了高效的编译算法,能够快速将设计转 换为FPGA可执行的配置文件。

灵活设计

Quartus II软件支持多种硬件描述语言,如VHDL和Verilog, 以及多种设计约束格式,方便用户进行灵活的设计。

03 流水灯设计原理

流水灯简介

01

流水灯是一种常见的LED显示设 备,通过控制LED灯的亮灭顺序 和时间间隔,实现动态的视觉效 果。

02

流水灯通常由多个LED灯珠组成 ,按照一定的顺序排列在一条线 上,通过控制每个LED灯的亮灭 状态,形成连续的视觉效果。

流水灯工作原理

流水灯的工作原理主要是通过控 制每个LED灯的亮灭状态和时间 间隔,实现动态的视觉效果。

控制每个LED灯的亮灭状态通常 是通过微控制器或数字逻辑电路 实现的,时间间隔则通过程序控

SOPC技术LED流水灯设计

Sopc_LED实验指导一.实验目的:1.掌握NIOS II软核的定制流程。

2.掌握NIOS II的开发流程。

3.熟识NIOS II IDE 开发环境的使用。

4.掌握基本的软件的调试方法。

5.掌握通过寄存器形式对硬件进行控制,可以更透彻地看清NIOS II 开发过程。

二.实验内容:1.PIO 模块的构建。

2.软件编程,通过寄存器形式对硬件进行控制。

3.下载程序并硬件调试。

4. 扩展实验:程序功能通过SOPC建立的软核来运行程序功能:LED 显示控制。

通过PIO 直接控制8 个LED 产生流水灯效果三.实验简介:这一节,我将给大家了解第一个与硬件有关的程序,虽然内容简单,却极具代表性。

我将采用一种寄存器的操作方案,让大家感受到开发NIOS跟单片机一样的简单,看透NIOS II开发的本质,尽量避免使用NIOS II IDE提供的API,这样做有很多好处。

首先,有单片机开发经验的人应熟悉这种操作方案,其次,它是硬件试验部分的第一课,通过这个简单的实验,可以让你对单片机的操作有一个感官上的了解,可以说意义不同寻常。

这一节,我也通过LED 实验来带大家进入NIOS II 的开发世界,感受NIOS 的魅力所在,下面我们开始吧。

四.实验内容:1.硬件开发第一步,我们要在软核中加入PIO 模块。

打开我们上一次建的Quartus 工程,如下图红圈所示(如果你没保留上次的工程,需要按照上次指导书重新再做一个下面的。

)双击上图的hello_word后进入了SOPC BUILDER界面,如下图所示点击下图所示红圈处PIO(Parallel I/O)点击后,如下图所示,红圈1处是你需要的PIO口的宽度,即你需要几个IO口,这里面我设置为8,即我要控制8个LED,红圈2是选择输出方式,我选择为输出(Output)。

接下来,点击Finish,完成PIO模块的构建,然后将其改名为LED,如下图所示接下来,需要自动分配一下基地址,上一次已经讲过,如下图所示接下来,双击cpu,看下图红圈的地址为下图的。

实验四 Nios II 嵌入式处理器关浩亮2012029180002

实验四 Nios II 嵌入式处理器一、实验要求:1、实现一个由Nios II控制的由18个发光二级管组成的流水灯效果;2、为了点亮LED灯,程序运行速度不要太快,需要进行适当延时。

二、实验目的:1,掌握基于SOPC Builder和Nios SBT实现嵌入式系统的硬件、软件设计过程;2,学会根据需求定制一个Nios II硬件系统,并在此基础上编写应用程序。

三、实验原理和实验内容:1、SOPC技术SOPC(System On a Programmable Chip)是指用可编程逻辑技术把整个系统放到一块硅片上。

它是一种特殊的嵌入式系统。

一方面,它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;另一方面,它是可编程系统,具有灵活的设计方式,可裁减、扩充、升级,并具备软硬件在系统可编程的功能。

这项技术将EDA、计算机设计、嵌入式系统、DSP等技术融为一体。

SOPC 结合了SOC 和PLD、FPGA 各自的优点,一般具备以下基本特征:至少包含一个嵌入式处理器内核;具有小容量片内高速RAM 资源;丰富的IP Core资源可供选择;足够的片上可编程逻辑资源;处理器调试接口和FPGA 编程接口;可包含部分可编程模拟电路;单芯片,低功耗,微封装。

随着EDA 技术的发展和大规模可编程器件性能的不断提高,SOPC 技术已被广泛应用于许多领域。

首先,SOPC 在极大提高了许多电子系统性能价格比的同时,还开辟了许多新的应用领域,如高端的数字信号处理、通信系统、软件无线电系统的设计、微处理器及大型计算机处理器的设计等等;同时,由于SOPC 具有基于EDA 技术标准的设计语言与系统测试手段、规范的设计流程与多层次的仿真功能以及高效率的软硬件开发与实现技术,使得SOPC 及其实现技术无可争议地成为现代电子技术最具时代特征的典型代表。

与基于ASIC 的SOC 相比,SOPC 具有更多的特点与吸引力:开发软件成本低,硬件实现风险低,产品上市效率高,系统结构可重构及硬件可升级等,它还具有设计者易学易用、高附加值、产品设计成本低等优势。

根据NiosII的流水灯设计

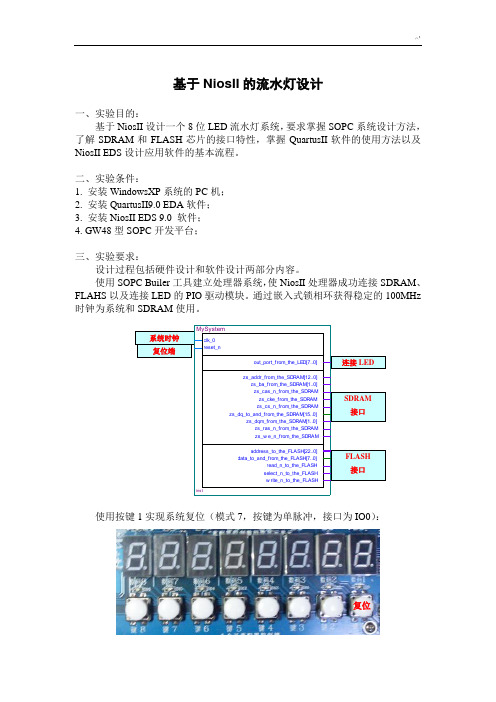

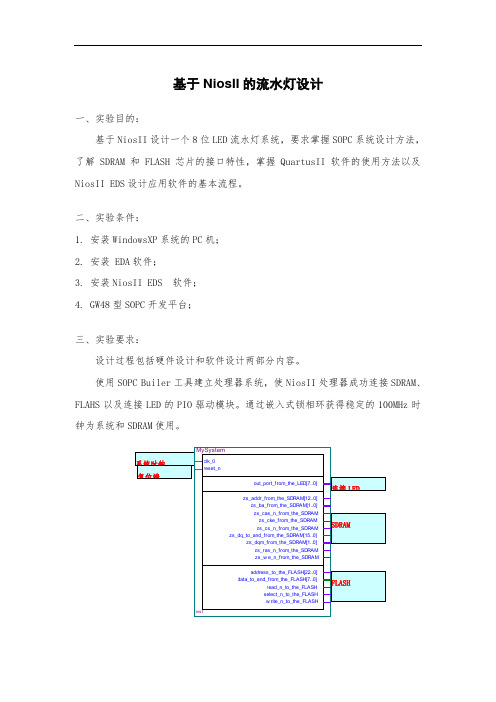

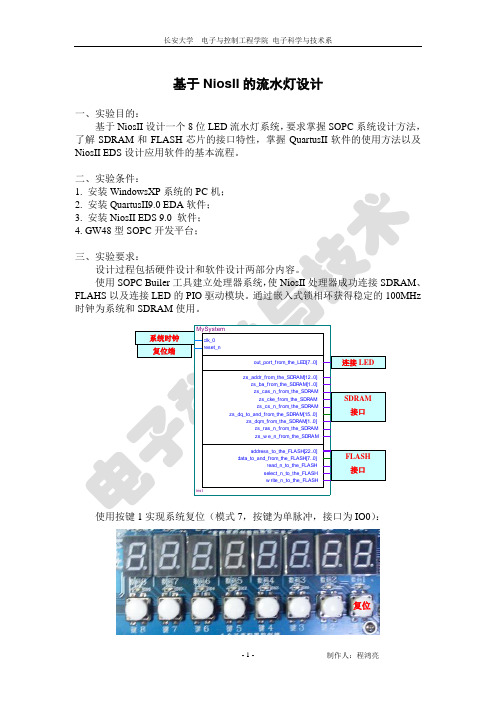

基于NiosII 的流水灯设计一、实验目的:基于NiosII 设计一个8位LED 流水灯系统,要求掌握SOPC 系统设计方法,了解SDRAM 和FLASH 芯片的接口特性,掌握QuartusII 软件的使用方法以及NiosII EDS 设计应用软件的基本流程。

二、实验条件:1. 安装WindowsXP 系统的PC 机;2. 安装QuartusII9.0 EDA 软件;3. 安装NiosII EDS 9.0 软件;4. GW48型SOPC 开发平台;三、实验要求:设计过程包括硬件设计和软件设计两部分内容。

使用SOPC Builer 工具建立处理器系统,使NiosII 处理器成功连接SDRAM 、FLAHS 以及连接LED 的PIO 驱动模块。

通过嵌入式锁相环获得稳定的100MHz 时钟为系统和SDRAM 使用。

使用按键1实现系统复位(模式7,按键为单脉冲,接口为IO0):系统时钟 复位端连接LEDSDRAM 接口 FLASH 接口 clk_0reset_n out_port_from_the_LE D[7..0] zs_addr_from_the_SDRAM[12..0]zs_ba_from_the_SDRAM[1..0]zs_cas_n_from_the_SDRAMzs_cke_from_the_SDRAM zs_cs_n_from_the_SDRAMzs_dqm_from_the_SDRAM[1..0]zs_ras_n_from_the_SDRAMzs_w e_n_from_the_SDRAMaddress_to_the_FLASH[22..0]read_n_to_the_FLASH select_n_to_the_FLASHw rite_n_to_the_FLASHzs_dq_to_and_from_the_SDRAM[15..0] data_to_and_from_the_FLASH[7..0]MySysteminst复位用LED阵列显示流水灯效果:注:要求使用LED1~LED8。

NiosⅡ的LED显示屏控制器设计

D3 - / 0_ D3 J 0 O

D3 . D3 一 0_ 6 O7

匝圆 计 算 串 口 十—1 争 — —= —= 斗 一 = 一 争 一 通 机 信 匝 圃 { ! 叵圃 叵麴 … 匪 i 系

…

一 。

匝垂圈匦 圃 匝鲴 —[——[——[—]

=;

j

31 9 D 11 3_

w ihi t n FPG A s s v d. Alo, r a on bl g nia i f d t t r g r duc s t o plxiy ofbo h a a pr c s i g a he o r l i ole s e s a e or a z ton o a a s o a e e e he c m e t t d t o e sn nd t c nt o

进行扫描。

所 谓 位 分 离 , 是 把 数 据 的 高 低 位 按 权 重 分 开 , 后 重 新 就 然

组 织 。位 分 离 在 可 编 程逻 辑 器件 巾 比较 容 易 实 现 , 以 划 可

串 口控 制 器 、 时 器 、 储 器 控 制 器 、 定 存 CF卡 控 制 器 通 过 S C B i e 软 件定 制集 成 I OP ul r d P核 自动 生 成 。本 控 制 器 的 硬件 结 构 如 图 2所 示 。

核 心 , 制 单 屏 幕 多窗 口任 意 显 示 。整 个控 制 系统 在 一 片 F GA 上 实 现 , 用 S ) C B i e 控 P 使 (P ul r软 件 定 制 集 成 I d P核 , 过 通 外 扩 存储 设 备 实现 数 据 的 海 量 存 储 , 决 了 FP 解 GA 内部 资 源 相 对 不 足 的 问题 。 同 时 , 理 组 织 数 据 存 储 方 式 , 合 降低 了数

根据NiosII的流水灯设计

基于NiosII的流水灯设计一、实验目的:基于NiosII设计一个8位LED流水灯系统,要求掌握SOPC系统设计方法,了解SDRAM和FLASH芯片的接口特性,掌握QuartusII软件的使用方法以及NiosII EDS设计应用软件的基本流程。

二、实验条件:1. 安装WindowsXP系统的PC机;2. 安装 EDA软件;3. 安装NiosII EDS 软件;4. GW48型SOPC开发平台;三、实验要求:设计过程包括硬件设计和软件设计两部分内容。

使用SOPC Builer工具建立处理器系统,使NiosII处理器成功连接SDRAM、FLAHS以及连接LED的PIO驱动模块。

通过嵌入式锁相环获得稳定的100MHz时钟为系统和SDRAM使用。

使用按键1实现系统复位(模式7,按键为单脉冲,接口为IO0):用LED阵列显示流水灯效果:注:要求使用LED1~LED8。

对应的IO编号分别为(IO60、IO67、IO65、IO63、IO70、IO73、IO75、IO79)。

四、实验步骤:1. 打开QuartusII软件,建立一个新的工程:单击菜单File\New Project Wizard…输入工程的路径、工程名以及顶层实体名。

单击Next>按钮,出现以下窗口⒈⒉⒊⒋⒌⒍⒎⒏⒐⒑⒒⒓⒔⒕⒖⒗复位由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。

设置器件信息:单击Next>,指定第三方工具:这里我们不指定第三方EDA工具,单击Next>后结束工程建立。

2. 建立SOPC系统单击Tool\SOPC Builder菜单项,启动SOPC Builder配置工具。

在弹出的系统命名对话框中为系统名称命名“MySystem”,并选择目标描述语言为“VHDL”,点击OK保存。

建立并配置处理器IP核。

双击或选择IP核库列表中的NiosII Processor 为系统添加NiosII处理器。

实验一:基于Nios II系统的LED实验

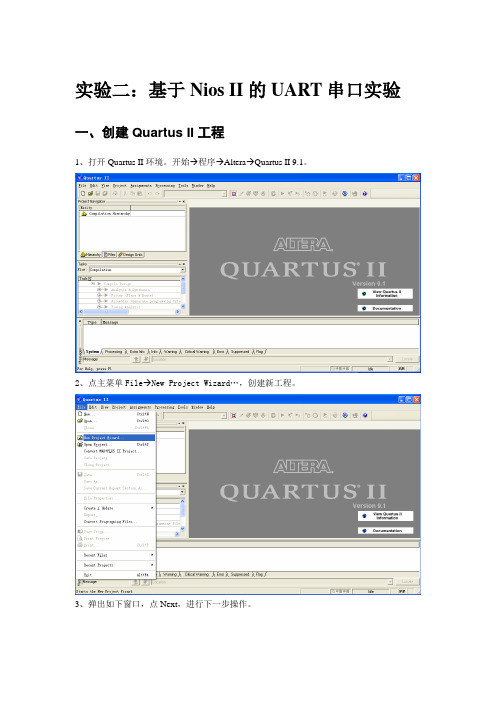

实验二:基于Nios II的UART串口实验一、创建Quartus II工程1、打开Quartus II环境。

开始→程序→Altera→Quartus II 9.1。

2、点主菜单File→New Project Wizard…,创建新工程。

3、弹出如下窗口,点Next,进行下一步操作。

4、输入新建工程路径,工程名及工程顶层实体,点Next,下一步。

如所输入工程路径文件夹不存在,则会弹如下窗口,点“是”,创建工程文件夹。

5、弹出如下窗口,按默认,点Next,下一步操作。

6、选择目标板上对应的正确芯片型号,点Next,下一步操作。

7、设置仿真格式,选择V erilog HDL,点Next,下一步操作。

8、点Finish,完成工程结构创建。

9、点击Assignment-Device。

10、选择Device & Pin Option,进行器件及管脚选项设置。

11、选择Dual-Purpose Pins,在弹出的如下对话框中双击Use as programming pin,然后在下拉框中选择Use as regular I/O,点确定,点OK。

12、选择Unused Pins选项,把没用到管脚设为三态输入“As input tri-stated”,其它选项按默认,点确定,完成设置。

13、附:由于芯片变更,将需要做如下调整以适应新的芯片核心电压,步骤如下:1.选择file-open并将工程所在路径打开如图:2.选择File菜单下的open,在文件类型下拉框中选All files,在所在工程文件夹下找到.qsf文件打开。

3.将set_global_assignment-name NOMINAL_CORE_SUPPL Y_VOLTAGE 1.0V后面的1.0V改为1.2V。

然后保存。

二、SOPC Builder创建系统模块1、在Quartus II环境中选择菜单Tools SOPC Builder…,打开SOPC Builder向导。

基于NIOS技术的流水灯LED显示系统的设计

基于NIOS技术的流水灯LED显示系统的设计内容提要:随着电子技术的不断发展,电子产品向体积越来越小、设计时间越来越短、集成度越来越精密、产品周期越来越短、成本越来越低、功能越来越强大等方向发展。

使用NIOSⅡ处理器的用户可以根据他们的需要调嵌入式系统的特性、性能以及成本,快速使得产品推向市场,扩展产品的生命周期,并且避免处理器的更新换代。

本论文结合EDA技术、C语言、NIOSⅡ技术、计算机技术等多种技术实现基于NiosⅡ的系统设计。

并用LED流水灯显示来检验我设计的NIOSⅡ技术的系统功能。

同时也为其他相关项目的设计提供了参考。

关键词:E DA技术SOPC技术 NIOSⅡ处理器嵌入式技术LED显示NIOS Ⅱ technology-based systems design andimplementation of- LED light water showAbstract:With the continuo us development of electronic technolo gy, electronic products to the size is getting smaller and smaller, shorter and shorter design time, more and more sophisticated integration, product life cycle is becoming shorter and shorter, more and more low-cost, more and more powerful features, such as Direction. The use of NIOS Ⅱprocessor users based on their need to transfer the characteristics of embedded systems, performance and cost of making products to market quickly, expand the product's life cycle and to avoid the replacement of the processor.This thesis EDA combination of technology, C language, NIOS Ⅱ technology, computer technology and other technology-based Nios Ⅱ system design. And the LED light water show designed to test my NIOS Ⅱ technology system. At the same time as other related projects designed to provide a referenceKey words:EDA Technology SOPC technology NIOS Ⅱ processor technology embedded LED display目录一、前言…………………………………………………………………………………二、总体方案……………………………………………………………………………(一)方案比较………………………………………………………………………(二)方案论证与选择……………………………………………………………三、所用技术和器件的介绍……………………………………………………………(一)基本器件的介绍…………………………………………………………………1、EDA的介绍…………………………………………………………………………2、CPLD和FPGA的介绍…………………………………………………………………3、QuartusⅡ的介绍……………………………………………………………………(二)特殊器件介绍……………………………………………………………………1、SOPC Builder开发工具介绍………………………………………………………2、NIOSⅡ的使用说明…………………………………………………………………3、Cyclone EP1C12Q240C8开发板的介绍……………………………………………四、系统设计……………………………………………………………………………(一)、硬件设计………………………………………………………………………1.新建工程……………………………………………………………………………2.用SOPC Builder 定制NiosⅡ处理器及其外设……………………………………3.在Quartus Ⅱ工程中添加上述niosⅡ系统………………………………………4.添加其他元件模块…………………………………………………………………5.定义管脚……………………………………………………………………………6.编译工程……………………………………………………………………………7.下载编辑代码到FPGA………………………………………………………………(二)、软件设计………………………………………………………………………1.设计该工程软件……………………………………………………………………2.编译设置……………………………………………………………………………3.编译…………………………………………………………………………………五、系统调试…………………………………………………………………………1.调试…………………………………………………………………………………2.编译并下载到实验板上面…………………………………………………………六、系统功能、指标参数………………………………………………………………七、总结与体会…………………………………………………………………………八、辞谢…………………………………………………………………………………附录……………………………………………………………………………………参考文献………………………………………………………………………………基于NIOS Ⅱ技术的系统设计与实现一、前言(绪论)随着微电子技术的发展,促使集成电路向高速、高集成度、低工耗的系统集成方向发展,SOP C(Sy ste m On a Pro gra mma ble Ch ip、片上可编程系统)是现代电子技术和电子系统设计的汇聚点和发展方向。

niosii开发纪录之总结niosii开发注意点(一)

NIOS II开发纪录之总结NIOS II 开发注意点(一)从开始接触Altera(现在应该叫intel PSG了)的NIOS II 处理器,到现在,已经有6个年头了。

从开始的C语言都不懂,到现在能使用NIOS II开发一些实用的东西,中间的过程也是非常的曲折。

最开始的时候,完全是炼狱一般,走一步,十个坑,没人指导,填几天,再走一步,再填一个坑。

到了后来对这个东西开始心生敬畏,敬畏不是因为它有多么多么强大,而是在学习和使用它的过程中,让我对CPU架构,单片机系统实现思路和编程方法有了较为底层的认识,也算是一个升华吧,虽然在这个过程中还是常常掉入坑里好久才能爬出来。

到了现在,能够指导大家学习和使用NIOS II处理器结合FPGA RTL逻辑实现一些功能,自己也能做一些不大的小东西。

这6年,感觉就像是按照指数函数的曲线进步的,最开始很慢,后面越来越快。

想想自己能坚持到现在,可真不容易(/偷笑)。

深知大家在自学这门技术的开始半年时间内有多么痛苦。

我一早就想出一点NIOS II方面开发的实用性书籍文档,可一直一个人打理着各种事情,实在没有精力。

我也深知当下讲解和使用NIOS II的开发已经有些不那么前沿了,毕竟现在嵌入硬核的FPGA应用已经较为成熟了,NIOS II这个处理器处于中间这样一个尴尬的位置,实用性和性价比值得思量。

但是,毕竟NIOS II和Xilinx的MicroBlaze处理器设计和开发思路异曲同工,MicroBlaze和Xilinx当前非常受欢迎的Zynq硬核FPGA开发思路和过程很像,NIOS II和Intel (Altera)的SOC FPGA开发过程和思路很像,因此,学习NIOS II处理器,是一条经济轻巧的道路。

真正掌握了NIOS II处理器的应用和开发,迁移到Intel SOC FPGA上,也就需要3~5周的时间,换到Xilinx的MicroBlaze或者Zynq平台上也只需要5~8周。

NIOS教程2---点亮你的LED灯

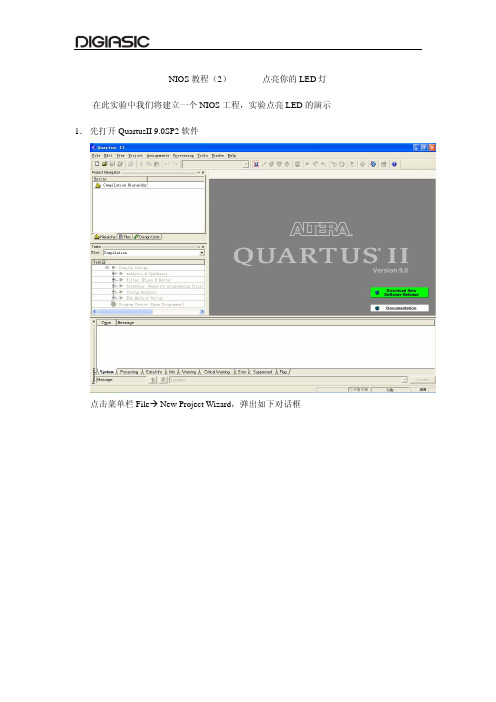

NIOS教程(2) --------点亮你的LED灯在此实验中我们将建立一个NIOS工程,实验点亮LED的演示1.先打开QuartusII 9.0SP2软件点击菜单栏FileÆ New Project Wizard,弹出如下对话框点击Next>按钮继续,在此步中,What is the working directory for this project? 是询问你的这个项目工程打算放在哪里?我们改为d:\ask2cb_nios\nios2 (表示整个工程建立在D盘的ask2cb_nios目录下面的nios2目录中)What is the name of this project? 是询问你这个工程项目名是什么?我们改为nios2(表示这是第二个nios示例工程)What is the name of the top-level design entity for this project? 是询问这个工程项目的顶层设计入门名我们改为nios2,表示顶层模块名为nios2改成如下图所示:点击Next>继续提示D盘ask2cb_nios目录下面没有nios2这个目录,询问是否要创建它,选择是(y),让QuartusII创建这个目录。

向导开始询问是否有现成的文件需要加到当前新建的工程中?这步不用管它,点击Next>继续,在此步中,向导询问你使用的是何种器件,我们在Device family组合框中,Family下拉列表中选择CycloneII,在Available devices:下面的列表框中选择EP2C5Q208C8,这是我们ASK2CB-5开发板所使用的FPGA主芯片(EP2C5Q208C8),如果您购买的是ASK2CB-8开发板,请选择EP2C8Q208C8。

在本教程中,默认采用的是EP2C5Q208C8,如果你的开发板上的FPGA主芯片为EP2C8Q208,请修改相应的器件为EP2C8Q208C8点击Next按钮继续在此步中询问你要使用何种综合工具,仿真工作,时序分析工具,不用管它,点Next>继续,最后显示一个整个新建的Project的摘要。

虚拟仪器课程设计-流水灯

电控学院课程设计(论文)课程名称:虚拟仪器题目:数字流水灯的设计院(系):专业班级:姓名:学号:指导教师:年月日基于LabVIEW的流水灯设计摘要虚拟仪器(virtual instrumention)是基于计算机的仪器。

计算机和仪器的密切结合是目前仪器发展的一个重要方向。

LabVIEW是一种程序开发环境,由美国国家仪器(NI)公司研制开发的,类似于C和BASIC开发环境,但是LabVIEW与其他计算机语言的显著区别是:其他计算机语言都是采用基于文本的语言产生代码,而LabVIEW使用的是图形化编辑语言G编写程序,产生的程序是框图的形式。

流水灯是一种生活中比较常见的装饰,本文主要通过labview来设计了一个流水灯系统的上位机界面,通过串口通信实现了其有规律的亮灭,带来一定的观赏效果。

关键词:虚拟仪器、上位机、串口通信、流水灯IAbstractVirtual Instrument (virtual instrumention) is a computer-based instruments. Close combination of computer and instruments is an important development direction of the current instrument. LabVIEW is a program development environment from National Instruments (NI) developed by the company, similar to C and BASIC development environment, but LabVIEW significantly different from other computer languages are: the use of other computer languages are generated text-based language code, and the use of LabVIEW graphical programming G editing language program is produced in block diagram form.Light water is a relatively common life decorative paper labview mainly through the PC interface to design a light water system through serial communication achieved its regular light off, bring some viewing.Keywords:Virtual Instrument, PC, serial communications, water lightsII目录1 设计任务 (1)2系统方案选择 (1)2.1整体设计 (1)2.2通信协议 (1)2.3下位机设计方案 (2)2.4上位机设计方案 (2)3下位机设计 (3)3.1硬件设计 (3)3.1.1单片机串口发送数据单元 (4)3.2软件设计 (4)3.2.1跑马灯程序设计 (5)3.2.2串口发送数据程序设计 (5)4上位机设计 (6)4.1前面板设计 (6)4.2后面板设计 (7)5系统调试 (8)6结论 (9)7总结 (10)参考文献 (11)附录 (12)III1 设计任务1.通过RS232接口进行数据采集。

基于NiosII的流水灯设计解读

基于NiosII的流水灯设计一、实验目的:基于NiosII设计一个8位LED流水灯系统,要求掌握SOPC系统设计方法,了解SDRAM和FLASH芯片的接口特性,掌握QuartusII软件的使用方法以及NiosII EDS设计应用软件的基本流程。

二、实验条件:、使用按键1实现系统复位(模式7,按键为单脉冲,接口为IO0):复位用LED 阵列显示流水灯效果:注:要求使用LED1~LED8。

对应的IO 编号分别为(IO60、IO67、IO65、IO63、IO70、IO73、IO75、IO79)。

四、实验步骤:1. 打开QuartusII 软件,建立一个新的工程:单击菜单File\New Project Wizard …输入工程的路径、工程名以及顶层实体名。

单击Next>按钮,出现以下窗口⒈ ⒉ ⒊ ⒋ ⒌ ⒍ ⒎ ⒏ ⒐⒑⒒⒓⒔⒕⒖⒗由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。

设置器件信息:单击Next>,指定第三方工具:这里我们不指定第三方EDA工具,单击Next>后结束工程建立。

2. 建立SOPC系统单击Tool\SOPC Builder菜单项,启动SOPC Builder配置工具。

在弹出的系统命名对话框中为系统名称命名“MySystem”,并选择目标描述语言为“VHDL”,点击OK保存。

统添加NiosII处理器。

Finish默认系统的配置。

右键处理器更改其名称为“MyCPU”。

本设计所使用的存储器是核心板载的SDRAM(K4S561632)和FLASH (AM29VL065D),所以需要通过为系统添加相关的IP核来驱动。

双击IP核列表中的Memories and Memory Controllers/SDRAM/SDRAM Controller将弹出以下的SDRAM控制器配置窗口,根据板载的SDRAM外围参数,按以下数据填入。

点击Next填写SDRAM的延时参数(默认参数),点击Finish完成。

NIOSⅡ经典教程

NIOS Ⅱ简明教程Nios II是一个用户可配置的通用RISC的嵌入式处理器,Altera推出的Nios II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获得超过200 DMIPS的性能,用户可以从三种处理器以及超过60个的IP核中选择所需要的,Nios II系统为用户提供了最基本的多功能性,设计师可以以此来创建一个最适合他们需求的嵌入式系统。

Nios II处理器的优点和特性,使用Nios II处理器的用户可以根据他们的需要来调整嵌入式系统的特性、性能以及成本,快速使得产品推向市场,扩展产品的生命周期,并且避免处理器的更新换代。

(1) 提高系统性能* 一系列的处理器核可供选择,其中包括了超过200 DMIPS性能的核* 实现任何数量的处理器或将不同的处理器核组和在一起* 增加了已有的处理器,在FPGA中添加一个或更多的Nios II软核处理器(2) 更低的系统成本* 通过将处理器、外设、存储器和I/O接口集成到一个单一的FPGA中,从而降低了系统成本、复杂性和功耗* 通过将Nios II处理器嵌入到低成本的FPGA中只需花费35美分或者更低(编者:对大多数用户而言,NiosII所占逻辑资源的成本大约是10-20元人民币,具体取决于所选FPGA的类型和NiosII的配置)(3) 应对产品的生命周期* 提供易用的设计工具从而快速将产品推向市场。

* 提供永久的,免费的许可从而使基于Nios II处理器的产品避免了处理器的更新换代而带来的损失。

(4) 功能强大、易用的开发工具* 通过使用Nios II集成开发环境(IDE),从而加速了软件的开发* 利用Altera的强大的SOPC Builder系统开发工具和Quartus II设计软件可以在几分钟内设计一个系统(5) 使用完全功能的开发包* 使用易用的Nios II 开发包开始一个设计* 使用易用的Nios II开发包开始设计* 可以选择具有低成本特性的Cyclone FPGA开发套件,或高性能的Stratix FPGA 开发套件下图是一个简化的基于Quartus 6.0和Nios II的SOPC开发流程。

LabVIEW课程设计基于LabVIEW软件平台的流水灯的设计原理及过程

在硬件设计中主要为下位机的AT89C52所设计的流水灯,其中包括基本的时钟晶振模块,复位电路模块,8位LED灯模块和最重要的串口通讯模块。

3.1 时钟晶振模块

外接晶振给单片机提供一个时钟信号(一个非常稳定的频率信号),使单片机各内部组件同步工作,并且在和外部设备通信时是也能达到同步。

RS232-C是美国电子工业协会EIA(Electronic Industry Association)制定的一种串行物理接口标准。RS是英文“推荐标准”的缩写,232为标识号,C表示修改次数。RS232-C标准设有25条信号线,包括一个主通道和一个辅助通道。在多数情况下主要使用主通道,对于一般双工通信,仅需几条信号线就可实现,如一条发送线、一条接收线及一条地线。

LabVIEW(Laboratory Virtual Instrument Engineering Workbench)是一种用图标代替文本行创建应用程序的图形化编程语言。传统文本编程语言根据语句和指令的先后顺序决定程序执行顺序,而 LabVIEW 则采用数据流编程方式,程序框图中节点之间的数据流向决定了VI及函数的执行顺序。VI指虚拟仪器,是 LabVIEW 的程序模块。

图形化的程序语言,又称为 “G” 语言。使用这种语言编程时,基本上不写程序代码,取而代之的是流程图或框图。它尽可能利用了技术人员、科学家、工程师所熟悉的术语、图标和概念,因此,LabVIEW是一个面向最终用户的工具。它可以增强你构建自己的科学和工程系统的能力,提供了实现仪器编程和数据采集系统的便捷途径。使用它进行原理研究、设计、测试并实现仪器系统时,可以大大提高工作效率。

图4.1 主流程图

4.1.1串口工作原理部分

系统的串口部分十分重要,主要是初始化部分对相应的寄存器进行设置,发送数据的时候只需要将数据写入SBUF里面即可,由发送中断标志位TI检测其数据发送结束。而接收则有中断方式和等待方式两种,本系统因为单片机所要完成的简单,所以采用等待的方式。串口的初始化程序流程图如图4.4所示。

sopc 流水灯实验

实验3、流水灯实验一、实验目的熟悉并行输入、输出内核提供从NiOSII软核处理器到通用输入/输出端口之间的寄存器映射接口。

二、实验环境PC机、Quartus II 13.0、Nios II三、实验内容按照书上介绍的方法和流程,完成H ello World 实验,包括N ios II 软核处理器系统的产生、编译、综合、Nios II EDS 工程创建、C 语言源文件的编辑及编译、配置目标F PGA 器件、下载观察实验结果四、实验步骤1、启动Quartus II 13.0,新建工程将其命名为l edsk,选择好目标芯片,然后设置没有用的引脚。

2、进入Tool-Qsys,进行如下图所示的硬件构架(1)从左侧组件库输入p io,双击添加组件并进行如下设置,并改名为l ed18_pio。

(2)双击led18_pio 组件中export 栏输入led18_pio,这是设置该组件外部硬件连接端口(注意点击自动分配地址和自动连接复位端口选项)。

(3)将文件保存命名为l ed18.qsys,点击g enerate 生成硬件。

3、添加q ip 文件,新建如图所示的b df(Block Schematic File)文件,编译分配引脚,再编译。

4、由Nios II C/C++菜单File-New- Nios II Application and BSP from Template 打开新工程设置窗口如下图所示。

找到led18.sopcinfo 文件,将软件工程命名为LED,并选择空白模板blank project.5、在L ED 文件夹下新建l ed.c 文件。

输入代码,Ctrl+s 保存。

Ctrl+b 进行全编译,编译完成进行,进行板上运行,观察结果。

五、实验心得与体会在这次实验中,主要是在NiosII上做出流水灯的实验,实验步骤大都与以往相同,在Quartus II上操作比较熟练。

但也有很多不足,下一次会注意本次试验中的问题。

实验3基于QuartusII的流水灯设计仿真综述

(devices)EP1C3T144C8 3. 新建图形设计文件,调用相关元件,设计总体电路原理 图,并编译通过; 4. 新建波形矢量文件,添加引脚端口并编辑激励波形,保 存该文件并执行时序仿真,观察并分析仿真结果。

15

QuartusII软件操作流程

请同学们参照后面的步骤,提前做好预习,熟悉

1

Q0 Q1 Q2 Q3 M1 CR 74 LS 194 M0 DSR DSL D0 D1 D2 D3

CP 0 0 0 0

1

Q0 Q1 Q2 Q3 M1 CR 74 LS 194 M0 DSR DSL D0 D1 D2 D3

CP 0 0 0 1 1 K

0 1

顺序脉冲发生器启动时需要通过置数功能先预置状态初值, 然后再切换回移位状态,这需要对74LS194的M1、M0 模式控制端使用开关进行模式切换

保存文件并关闭,重启Quartus,注册请求界面已消失。

18

若注册请求界

面还未消失 请按左图选择

在下图中重设

文件指向路径

2、Quartus II 6.0主界面操作环境

1、Project Navigator(工程管理器)

2、Status window(状态窗口)

2、Message window(信息窗口)

2.设计一个移存型流水灯的逻辑电路并完成仿真测试,电路

采用8灯结构,8个灯按1亮7暗的规律循环流动。

设计的步骤要求同上。

7

实验操作成绩评分标准

A:内容1、内容2 原理图、波形均正确

B:完成内容1、内容2 其中一个

C:内容1、内容2 均未完成

QuartusII使用注意事项

新建文件夹,如test3

SOPC流水灯实验

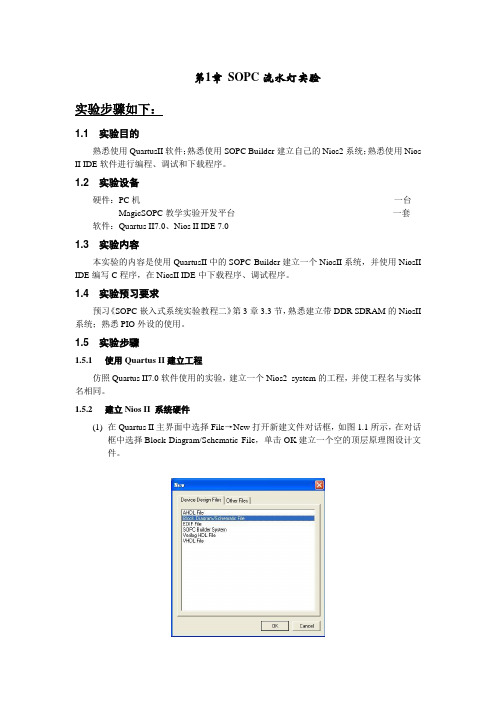

第1章SOPC流水灯实验实验步骤如下:1.1 实验目的熟悉使用QuartusII软件;熟悉使用SOPC Builder建立自己的Nios2系统;熟悉使用Nios II IDE软件进行编程、调试和下载程序。

1.2 实验设备硬件:PC机一台MagicSOPC教学实验开发平台一套软件:Quartus II7.0、Nios II IDE 7.01.3 实验内容本实验的内容是使用QuartusII中的SOPC Builder建立一个NiosII系统,并使用NiosII IDE编写C程序,在NiosII IDE中下载程序、调试程序。

1.4 实验预习要求预习《SOPC嵌入式系统实验教程二》第3章3.3节,熟悉建立带DDR SDRAM的NiosII 系统;熟悉PIO外设的使用。

1.5 实验步骤1.5.1使用Quartus II建立工程仿照Quartus II7.0软件使用的实验,建立一个Nios2_system的工程,并使工程名与实体名相同。

1.5.2建立Nios II 系统硬件(1)在Quartus II主界面中选择File→New打开新建文件对话框,如图1.1所示,在对话框中选择Block Diagram/Schematic File,单击OK建立一个空的顶层原理图设计文件。

图1.1 新建文件对话框(2)在Quartus II主界面中选择Tools→SOPC Builder打开如图1.2所示的对话框,在System Name一栏中填入Nios II 系统的名称nios2_ep2c35,然后单击OK进入到如图1.3所示的SOPC Builder的主界面。

图1.2 Create New System对话框图1.3 SOPC Builder的主界面(3)双击SOPC Builder主界面左侧中的“Nios II Processor-Altera Corporation”,出现Nios II CPU的配置向导对话框,如图1.4所示,在这果可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,然后单击Next进入下一步配置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

%基于NiosII的流水灯设计一、实验目的:基于NiosII设计一个8位LED流水灯系统,要求掌握SOPC系统设计方法,了解SDRAM和FLASH芯片的接口特性,掌握QuartusII软件的使用方法以及NiosII EDS设计应用软件的基本流程。

二、实验条件:1. 安装WindowsXP系统的PC机;2. 安装 EDA软件;3. 安装NiosII EDS 软件;【4. GW48型SOPC开发平台;三、实验要求:设计过程包括硬件设计和软件设计两部分内容。

使用SOPC Builer工具建立处理器系统,使NiosII处理器成功连接SDRAM、FLAHS以及连接LED的PIO驱动模块。

通过嵌入式锁相环获得稳定的100MHz时钟为系统和SDRAM使用。

,|使用按键1实现系统复位(模式7,按键为单脉冲,接口为IO0):用LED 阵列显示流水灯效果:,注:要求使用LED1~LED8。

对应的IO 编号分别为(IO60、IO67、IO65、IO63、IO70、IO73、IO75、IO79)。

四、实验步骤:1. 打开QuartusII 软件,建立一个新的工程:单击菜单File\New Project Wizard …输入工程的路径、工程名以及顶层实体名。

单击Next>按钮,出现以下窗口)?⒉ ⒊ ⒋ ⒌ ⒍ ⒎ ⒏ [⒑⒒⒓⒔⒕⒖⒗复位由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。

设置器件信息:单击Next>,指定第三方工具:这里我们不指定第三方EDA工具,单击Next>后结束工程建立。

<2. 建立SOPC系统单击Tool\SOPC Builder菜单项,启动SOPC Builder配置工具。

在弹出的系统命名对话框中为系统名称命名“MySystem”,并选择目标描述语言为“VHDL”,点击OK保存。

建立并配置处理器IP核。

双击或选择IP核库列表中的NiosII Processor 为系统添加NiosII处理器。

系统将弹出如下对话框要求用户对处理器情况进行配置,此时我们先选择Finish默认系统的配置。

右键处理器更改其名称为“MyCPU”。

/本设计所使用的存储器是核心板载的SDRAM(K4S561632)和FLASH (AM29VL065D),所以需要通过为系统添加相关的IP核来驱动。

双击IP核列表中的Memories and Memory Controllers/SDRAM/SDRAM Controller将弹出以下的SDRAM控制器配置窗口,根据板载的SDRAM外围参数,按以下数据填入。

点击Next填写SDRAM的延时参数(默认参数),点击Finish完成。

右键修改SDRAM 的名称“SDRAM”。

如下图双击IP核列表中的Library/Bridges and Adapters/Avalon-MM Tristate Bridge为系统添加链接FLASH的三态桥IP核。

在弹出的对话中中直接点击Finish。

双击IP核列表中的Library/Memories and Memory Controllers/Flash/Flash MemoryInterface(CFI)为系统添加FLASH界面IP 核,并按照下图填入描述参数。

-点击Next填入时序参数,并点击Finish完成参数配置。

修改此IP核实例名称为“FLASH”,如下图。

配置IP核之间的连接关系点击菜单System/Auto-Assign Base Addresses完成存储器地址分配。

在此双击处理器IP核实例“MyCPU”配置复位地址和异常中断地址,并点击Finish完成配置,如下图。

…更改处理器的工作时钟频率为100MHz,如下图。

双击IP核列表中的Library/PIO,添加PIO模块,按照下图配置(默认配置)并更名为“LED”。

建议再次点击菜单System/Auto-Assign Base Addresses重新对地址分配。

?到此,SOPC系统的配置工作已经完成,点击Generate按钮生成SOPC系统,系统生成完毕并成功后点击Exit推出SOPC Builder环境。

3. 建立系统电路图单击File\New菜单项,选择弹出窗口中的Block Diagram/Schematic File,单击OK按钮以建立打开空的图形输入文件,注意此文件并没有在硬盘中保存。

双击图形输入区域的空白处,选择弹出窗口中的SOPC系统模块,点击OK 按钮添加到图形输入区域。

添加锁相环。

点击菜单Tools/MegaWizard Plug-In Manager…并在弹出的对话框中选择“Create a new custom megafunction variation”点击Next继续。

[如下图选择锁相环IP核,并对其命名“MyPLL”,点击Next进入锁相环的设定环节。

按照下图设定锁相环的输入频率为20MHz,点击Next继续。

清除弹出对话框的所有选项,以此简化对锁相环的控制,点击Next。

对弹出的对话框做如下设置,点击Next继续。

"对弹出的对话框,配置c0时钟频率为输入时钟的5倍(100MHz),如下图,点击Next继续。

出现c1时钟配置页面后,不选择此时钟输出,直接点击Next继续。

弹出c2时钟配置页面后,对其做如下配置,用于SDRAM的时钟(频率为100MHz,移相为-63°),点击Next继续。

:到此配置过程完成,点击Finish 生成锁相环。

连接锁相环到电路中。

双击图形输入区域,选择生成的锁相环,添加到电路中。

再次双击图形输入空白区域,如下图输入引脚类型“input”添加输入和输出引脚,按照图示连接并对引脚命名。

(添加输出引脚时输入“output”,双向引脚“bidir”)连接其他引脚。

根据SOPC系统端口的方向依次添加各引脚并按照下图命名(复位端用到了一个反相器,键入名称“NOT”即可获得)。

端口连接和命名完成之后点击保存按钮。

*引脚锁定。

点击Processing/Start Compilation编译当前工程,以获得电路的引脚信息。

编译完成之后,点击菜单Assignments/Assignment Editor对引脚进行锁定。

引脚名称锁定位置FLASH_DATA[4]PIN_T3FLASH_DATA[5]PIN_T5FLASH_DATA[6]、PIN_T6FLASH_DATA[7]PIN_U1FLASH_RDn PIN_W9FLASH_RSTn PIN_Y6FLASH_WRn,PIN_Y5CLK PIN_L1RST PIN_AB15LED[0]PIN_AB16LED[1];PIN_AB11LED[2]PIN_AB7LED[3]PIN_AB19LED[4]PIN_A8LED[5]?PIN_A5LED[6]PIN_A3LED[7]PIN_Y10点击菜单Assignments/Device将弹出以下对话框,点击其中的“Device and Options”按钮,在弹出对话框的“Unused Pins”选项卡中设定未使用的引脚为“As input tri-stated with weak pull-up”。

$编译工程。

单击Processing\Start Compilation开始编译,编译过程中如果有出错消息,请参考提示对工程进行修改直到编译完全成功为止。

4. 软件设计启动NiosII EDS软件,选择File/New/NiosII Application and BSP from Template新建一个应用工程和板级描述包。

在弹出的对话框中填入SOPC描述信息和工程名。

在模板窗口中选择“Blank Project”点击Finish完成一个空应用工程的建立。

{在工程管理窗口中右键点击“Led_Flow_Soft”,从弹出菜单中选择新建源文件,如下图。

为源文件起名“”已建立一个C++文件,点击Finish确定。

编写源文件:保存工程后点击Project/Build All编译工程。

\点击菜单项NiosII/QuartusII Programmer,打开QuartusII编程下载对话框,将QuartusII工程生成的SOF文件下载到FPGA芯片中。

下载成功后,开发板就构造成功了一个NiosII系统,我们需要把流水灯程序下载到其中的Flash 中实现流水灯效果。

注意下载后不要断电,后续的Flash下载过程需要保证NiosII系统常驻在FPGA中。

点击菜单项NiosII/Flash Programmer,打开Flash编程下载对话框。

点击新建菜单,指定板级描述文件的位置(默认位置在工程目录的software文件夹中)。

添加程序下载文件到对话框中,下载文件后缀名为.elf。

点击Start即进行下载。

程序下载无误即可看到LED的流水灯效果。

五、实验结果)附:1. 参考代码:--------------------------------制作人:程鸿亮--------------------------------------------#include""#include""#include""|#include""int main(){alt_u8 iData(1);alt_u8 i(0);while(1){if(i<7)】iData=iData<<1;elseiData=iData>>1;IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE,iData);i=(++i)%14;usleep(100000);}return 0;-}--------------------------------------------------------------------------------------------------。