基于SKILL语言的原理图检查系统实现

cadence简介和使用基础

CMOS电路原理图设计

或者CIW窗口→File→Open(打开已有的 Cellview)。

CMOS电路原理图设计

也可以在Library Manager中直接打开。

Cadence的使用基础

双击Schematics,出现原理图编辑器

Cadence的使用基础

之后出现Symbol Generation Options窗口。

Cadence的使用基础

出现界面:

Cadence的使用基础

可将上图修改为惯用图形,以CMOS反相器为例。

CMOS电路原理图设计

电路仿真 仿真环境简介

Schematic图形窗口→Tools→Analog Environment。

Cadence的使用基础

Cadence的使用基础

基本工作环境

局域网资源

Cadence的使用基础

用户登陆 微机登陆后,点击桌面X-manager 图标,

Cadence的使用基础

打开X-manager图标后,点击xstart 图标,出现对话 框,进行如下设置:

Cadence的使用基础

登录时出现Linux-CDE (Common Desktop Environment) 界面

一、 cadence简介和使用

集成电路设计软件技术介绍

EDA技术的概念

EDA技术是在电子CAD技术基础上发展起来 的计算机软件系统,是指以计算机为工作平台, 融合了应用电子技术、计算机技术、信息处理 及智能化技术的最新成果,进行电子产品的自 动设计

EDA工具的功能

利用EDA工具,电子设计师可以从概念、算法、 协议等开始设计电子系统,大量工作可以通过 计算机完成,并可以将电子产品从电路设计、

2、Cacence原理图编辑的操作

② 点击Browse按钮=>Library Browser

在Sample库和AnalogLib库中包含MOS管和PMOS管符号。

PMOS管

NMOS管

2) 连线。命令Add →Wire(narrow);或快捷键<w>;或点击图标。 3)加电源和地符号。在AnalogLib库中选调。 4)加终端(或管脚)。命令Add→ Pin...或快捷键<p> => Add Pin对话 框,输入管脚名(注意选择方向)。

第1章 Cacence软件

CELL 设计流程

创建工艺文件 符号生成 模拟 版图单元 验证版图 反标注 打印输出 生成抽象 单元转换 生成参数化单元 生成复杂阵列

系统组织结构

大多数 Cadence 工具使用同样的库模型,库 结构按目录结构组织数据,这利于不同工具之 间的数据交互和一致操作。 物理组织 逻辑组织

目录 子目录 子目录

库 单元 视图

系统组织结构

Example

vendlib dff

/usr/proj/vendlib

mux2

/usr/proj/vendlib/dff /usr/proj/vendlib/mux2

gates

Vhdl.vhd

body

/usr/proj/vendlib/mux2/gates /usr/proj/vendlib/mux2/body

一个cshrc文件的sample

setenv setenv setenv setenv setenv setenv setenv setenv setenv setenv setenv setenv setenv LANG en_US CIC1 /home/user1/IC50 PATH {$PATH}:$CIC1/tools/bin PATH {$PATH}:$CIC1/tools/dfII/bin PATH {$PATH}:$CIC1/tools/plot/bin CDSHOME $CIC1 CDSDIR $CIC1/tools CDS_ROOT $CIC1/tools CDS_INST_DIR $CIC1/tools CDS_INSTALL_DIR $CIC1/tools/dfII CDS_LIC_FILE 5280@localhost.localdomain CDS_Netlisting_Mode Analog CDS_INST_DIR $CIC1

Allegro16.x导入网表介绍

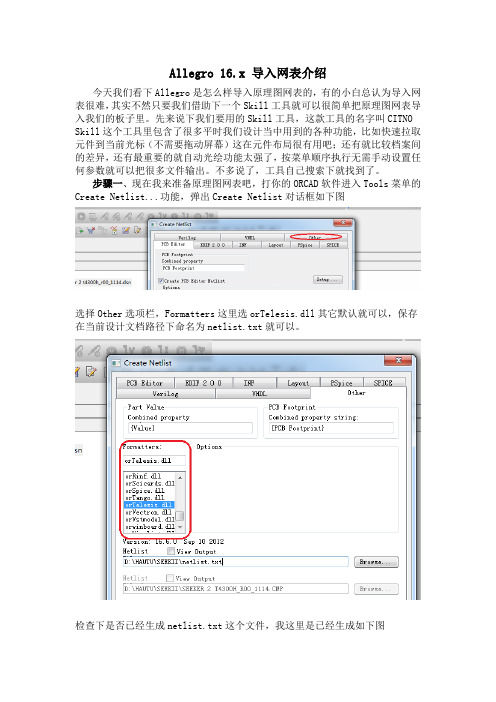

Allegro 16.x 导入网表介绍

今天我们看下Allegro是怎么样导入原理图网表的,有的小白总认为导入网表很难,其实不然只要我们借助下一个Skill工具就可以很简单把原理图网表导入我们的板子里。

先来说下我们要用的Skill工具,这款工具的名字叫CITNO Skill这个工具里包含了很多平时我们设计当中用到的各种功能,比如快速拉取元件到当前光标(不需要拖动屏幕)这在元件布局很有用吧;还有就比较档案间的差异,还有最重要的就自动光绘功能太强了,按菜单顺序执行无需手动设置任何参数就可以把很多文件输出。

不多说了,工具自己搜索下就找到了。

步骤一、现在我来准备原理图网表吧,打你的ORCAD软件进入Tools菜单的Create Netlist...功能,弹出Create Netlist对话框如下图

选择Other选项栏,Formatters这里选orTelesis.dll其它默认就可以,保存在当前设计文档路径下命名为netlist.txt就可以。

检查下是否已经生成netlist.txt这个文件,我这里是已经生成如下图

步骤二,准备已经导入Outline 的PCB档案,下面是我的板子已经有Outline

现在我们的板子是有零件库的,所以必须设置库路径。

现在把CITNO Skill菜单调出来,运行命令:CTRL+z

CITNO Skilll菜单界面图如下

其中Netin,3rd Party这是导入网表功能,即第三方网表导入现在我们开始执行此命令

过几秒钟之后,导入成功

现在我们把器件放置进来,下图我已经成功放置器件。

到这里我们的导入原理图网表教程已经结束,谢谢!。

cad skill

• 画宽度线(W); • 画箭头(W); • 画弧、画圆、画矩形(A);

常用编辑命令

复制(带基点):co或ctrl+c、 移动:m 镜像:mi 旋转:ro 偏移:o 重复上次命令:空格或回车 返回至上次命令:ctrl+z或u 删除:e

——其他实用编辑命令——

文字:dt、mt 标注:dli、dal、le、mls 查询:di、aa 块与编辑:b、battman、

Eg----应用实例:调机电建筑底图。

“实用”命令

快速选择:右键Q 查找替换:find 过滤计算:fi 重新生成:re 清理:pu

五、图形输出

1、布局、视口、比例、图纸大小(小模 型、分块、搭边问题) 2、打印样式(与图层管理控制的区别)

Eg:做布局,调打印样式。

中国.中学政治教学网崇尚互联共享

2、命令的取消 按ESC键可以中断正在执行的命令 输入U或点取 可以撤消前面执行的命令,要恢 复撤消的最后一个命令,可以键入REDO

三、CAD绘图命令

1、“画”命令 2、“编辑”命令 3、“管理”命令 4、“实用”命令 5、“图形输出”命令

你画的最多的是:

线

中国.中学政治教学网崇尚互联共享

计算改变扬程、转速等参数。

7 考虑施工及经济,优化管材

•必须考虑施工的可行性,足够的实际尺寸余地利于施工进行 管线排布,将大管道改为小管道,增加数量,利于施工。

二、深化设计的要点

8 机房等详图设计

•为了对施工提供详尽的图纸,必须进行机房、处理构筑物、管井、 卫生间的详图设计,同时考虑各专业的协调。

2、熟悉原招标图纸设计理念

机房及处理构筑物位置【给水泵房、中水处理机房、中水泵房、热水泵房、 集水井、化粪池、隔油池等】;

CHECKLIST EE原理图设计检查

有支持I2C的设计需求,要事先规划好系统I2C拓扑,在芯片选型 19 时要考虑预留逻辑空间。(BMC如果I2C资源够用,CPLD单独占用

一组I2C总线)

三、USB

Item Number

检查项目

Designer Check OK NG

关于RJ45接头中的LED,建议Symbol中能体现出二极管的极 8 性,注意State和ACT两个信号的接法

9

注意不同颜色LED指示内容(Active/Link/Speed)是否和产品需求 、机构丝印一致

在使用多Port RJ45/SFP/SFP+时,注意LED和端口的对应关系。 10 Layout过程中调线时,尤其注意不仅要调整总线,对应的LED也

10 单板上同一电源和地名称要统一

单相PWM driver 的BOOT Pin与phase端接0.1uF电容.核对BOOT电 11 容,是否耐压值为50V 12 H-side Gate上预留0ohm电阻. 13 Feedback电路设置是否准确

GND和AGND电路要分开,但最后要通过一点进行连接。如果是 14 chipset的 AGND电流很大,可直接与GND相连,不需要连接0OHM,

否则通流不够。 15 PWROK的Pull high要用本身的power去做。

第一次画power原理图要加上GAP,方便调试。(所有Power的 16 Enable信号可以预留一个Gap,方便Power调试)

有些模块线路copy过来后,需要注意AGND属性要更改,最好能赋 17 予net名字,比如经常会遇到两个P1V1的AGND起的名字一样。

EE原理图设计 Check List -J

PDK

PDK introductionPDK(process design kit)是沟通IC设计公司、代工厂与EDA厂商的桥梁。

当我们需要开始采用一个新的半导体工艺时,第一件事就是需要开发一套PDK,PDK用代工厂的语言定义了一套反映foundary工艺的文档资料,是设计公司用来做物理验证的基石,也是流片成败关键的因素。

PDK包含了反映制造工艺基本的“积木块”:晶体管、接触孔,互连线等,除PDK的参考手册(Documentation)外,PDK的内容还包括:器件模型(Device Model):由Foundry提供的仿真模型文件Symbols & View:用于原理图设计的符号,参数化的设计单元都通过了SPICE 仿真的验证CDF(Component Description Format,组件描述格式) & Callback:器件的属性描述文件,定义了器件类型、器件名称、器件参数及参数调用关系函数集Callback、器件模型、器件的各种视图格式等Pcell(Parameterized Cell,参数化单元):它由Cadence的SKILL语言编写,其对应的版图通过了DRC和LVS验证,方便设计人员进行Schematic Driven Layout(原理图驱动的版图)设计流程技术文件(Technology File):用于版图设计和验证的工艺文件,包含GDSII的设计数据层和工艺层的映射关系定义、设计数据层的属性定义、在线设计规则、电气规则、显示色彩定义和图形格式定义等;PV Rule(物理验证规则)文件:包含版图验证文件DRC/LVS/RC提取,支持Cadence的Diva、Dracula、Assura等。

在开发PDK的演进中,有些事情在慢慢变化着:一是Virtuoso 不再是这个领域唯一的玩家,所有主要的EDA厂商都纷纷给出了自己的解决方案,但没有一家EDA工具能读写Virtuoso的PDK。

“汽车电动后视镜系统检修”混合式教学案例设计

◆文/江苏 耿彪“汽车电动后视镜系统检修”混合式教学案例设计为适应“互联网+职业教育”发展需求,学习并执行《国家职业教育改革实施方案》(职教20条)和最新版《中华人民共和国职业教育法》中的有关精神。

本文以《汽车辅助电气系统构造与检修》课程中的“汽车电动后视镜系统检修”教案设计为例,在原教学模式的基础上,融入“互联网+”、虚拟仿真等技术,深挖课程思政元素,将原教案设计成符合新时代职业院校专业课程的混合式教案,让教师更便于教,使学生更乐于学。

一、《汽车辅助电气系统构造与检修》课程简介《汽车辅助电气系统构造与检修》课程是汽车检测与维修技术专业五年制高职学生必修的一门专业核心课程,课程总课时为108学时,占6学分。

本课程的课程目标是让学生能够掌握车载网络系统、风窗刮水洗涤系统、电动后视镜系统、电动车窗系统、中控门锁系统、电动座椅系统、安全气囊系统等汽车辅助电气系统的结构组成、工作原理、元件检查和更换方法等。

希望通过本课程的学习后,使学生具有汽车维修行业相关工作和参加等级工或“1+X ”认证所必需知识及技能;培养学生遵守国家法律法规、规范标准的意识和爱国、敬业、诚信、友善的职业道德;提高学生自主学习、综合分析、团队协作、沟通交流、创新意识等能力。

教学内容分为电动后视镜认知与检查、零部件拆装与更换、电路分析与测量、故障诊断与排除,共4个任务,计12课时,培养“会检查、能更换、知原理、懂排故”的汽车机电维修人才,如图1所示。

3.课程思政融入课程以“德技并修”为主线构建课程思政育人体系,完全契合新版职教法对职业教育人才培养提出的目标要求。

从我国古代匠人采用抛光雕刻法制造出独具风格的青铜镜,使得我国成为世界上最早使用铜镜的国家之一,以此培养学生的文化自信;再到激发学生学习“执着专注、精益求精、一丝不苟、追求卓越”工匠精神的热情;最后在课程学习过程中强调操作团队合作、实训操作和小组评价等注意事项,真正地把社会主义核心价值观、工匠耿彪(本刊编委会委员)汽车职业院校讲师,国家职业技能大赛裁判员,汽车维修工高级技师,汽车维修电工技师。

cadence简介

EDA概述

• EDA技术特征:

(1)硬件采用工作站和PC机。 (2)具有IP模块化芯核的设计和可重复利用功能。 (3)EDA技术采用高级硬件描述语言描述硬件结构、参 数和功能,具有系统级仿真和综合能力。

EDA概述

• EDA工具一般由两部分组成:

逻辑工具 物理工具

物理工具主要实现物理布局布线。 逻辑工具基于网表、布尔逻辑、传输时序等概念。 该两部分由不同工具承担,利用标准化的网表文件进行 数据交换。

• Synopsys公司简介:

是为全球集成电路设计提供电子设计自动化(EDA) 软件工具的主导企业。为全球电子市场提供技术先进的 IC设计与验证平台,致力于复杂的芯片上系统(SoCs)的 开发。总部设在美国加利福尼亚州Mountain View,有 超过60家分公司分布在北美、欧洲、日本与亚洲。 提供前后端完整IC设计方案的领先EDA工具供应商。 是EDA历史上第一次由一家EDA公司集成了业界最好的 前端和后端设计工具。

第二章 EDA概述

• 电子设计自动化(EDA:Electronic Design Automation)就是利用计算机作为工作平台进 行电子自动化设计的一项技术。 • 涵盖内容:系统设计与仿真,电路设计与

仿真,印制电路板设计与校正,集成电 路版图设计数模混合设计,嵌入式系统 设计,软硬件系统协同设计,系统芯片 设计,可编程逻辑器件和可编程系统芯 片设计,专用集成电路设计等

EDA概述

• 软核IP(soft IP)是用可综合的硬件描述语言描述的 RTL级电路功能块,不涉及用与什么工艺相关的电路 和电路元件实现这些描述。 • 优点:设计周期短,设计投入少,不涉及物理实现, 为后续设计留有很大发挥空间,增大了IP的灵活性和 适应性。 • 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

allegro skill 干货1-制作焊接丝印图

allegro skill 干货1-制作焊接丝印图1.Allegro skill 提供了PCB editor 二次开发的可能,它可以使某些繁琐的操作自动化,简单化,例如,在某些情况下我们需要手工焊接时,需要对照原理图,丝印图一一去找器件,这样既浪费了很多时间,同时还导致手工焊接出错。

2.本文讲到方法是,通过写一个skill 脚本的方法,可以使电阻或者电容的值直接标注在相应器件的丝印上,这样可以非常直观的进行焊接。

类似下面这张图一样,是不是非常容易查找到对应的阻容进行焊接。

3.开始讲解实现的过程。

贴上一段代码。

首先注册一个函数,就是allegro加载skill脚本时的名称,脚本可以设置打开allegro时加载,也可以设置成手工加载,后面会详细说明。

下文中黄色高亮的事注释部分,commen Lisp中注释使用;开头。

;申请一个函数axlCmdRegister("AutoHandSilk",'AutoHandSilk);实现这个函数;定义函数为AutoHandSilk,与上文申请的函数名称一致defun(AutoHandSilk ();关闭所有class和subclassaxlVisibleDesign(nil);打开BOARD GEOMETRY/OUTLINE层等等,为后面选中做准备,这里为什么打开; DEVICE TYPE/ASSEMBLY_TOP层呢,是因为只有这个层会有阻容值得信息,例如这;样R_R0603_2.2KaxlVisibleLayer("BOARD GEOMETRY/OUTLINE" t);axlVisibleLayer("PIN/TOP" t)axlVisibleLayer("DEVICE TYPE/ASSEMBLY_TOP" t)axlVisibleLayer("PACKAGE GEOMETRY/PLACE_BOUND_TOP" t);过滤选中的关键字,这里过滤的是textaxlSetFindFilter(?enabled list("noall" "text")?onButtons list("noall" "text"));选中页面上以上显示层的text,这个和实际在allegro环境中框选一样axlAddSelectAll();将选中的text信息赋值给对象allall = axlGetSelSet();去除显示,相当于去除高亮axlClearSelSet();这里是打印一条logaxlMsgPut("DEVICE TYPE/Assy place started.");这里是skill语言也就是commen Lisp语言的for循环foreach(i all;将text值取出来赋值给变量texttext = i ->text;下面这句相当于split字符串的功能,就是把类似R_R0603_2.2K的字符串;中有用的信息2.2K取出来text_list = parseString(text,"_")text=car(last(text_list));去阻容丝印等的原点坐标,注意丝印的原点坐标不是字的正中心,是字底;部的中心xy = i ->xy;取当前丝印的旋转角度txt_rot = round(i ->rotation);将180度都统一用0度表示,90度的统一用270表示cond((txt_rot == 180, txt_rot = 0)(txt_rot == 90, txt_rot = 270));这里是对每个丝印进行具体处理了,下面就是把丝印放在什么位置呢,;这里的方法是取place_bound_top层的长方形算中心foreach(childid, i ->parent ->childrenwhen(childid ->layer == "PACKAGE GEOMETRY/PLACE_BOUND_TOP" || childid ->layer == "PACKAGE GEOMETRY/PLACE_BOUND_BOTTOM"sym_x = (xCoord(car(childid ->bBox)) + xCoord(cadr(childid ->bBox))) / 2.0sym_y = (yCoord(car(childid ->bBox)) + yCoord(cadr(childid ->bBox))) / 2.0));前面说过丝印的xy并不是字的正中心,所以这里算出偏移量并根据具体;情况加或者减halfT extHeight = axlGetParam(sprintf(nil, "paramTextBlock:%d", 1)) ->height / 2.0case(txt_rot( 0, sym_y = sym_y - halfT extHeight)( 90, sym_x = sym_x + halfT extHeight)(180, sym_y = sym_y + halfTextHeight)(270, sym_x = sym_x - halfTextHeight));这里的xy才是要把丝印最终放置的位置xy = list(sym_x, sym_y);定义要创建文字的属性,字体默认使用1号了,使用者可以根据实际情况修;改合适的字体,然后再使用此脚本textOrientation = make_axlT extOrientation( ?textBlock "1", ?rotation txt_rot, ?mirrored i ->isMirrored, ?justify "CENTER");下面是注释掉的语句,实现的是直接在assemble_top上创建丝印,并删除;掉旧的丝印,实际上就是相当于移动丝印。

Virtuoso cadence 教程轻松学

IC设计基础

CADENCE

• 典型的实际分层次设计流程:

11

IC设计基础

CADENCE

• 分层次设计流程主要适用于数字系统设 计,模拟IC设计基本上是手工设计。

• 即便是数字IC设计,也需要较多的人工 干预。

12

IC设计基础

CADENCE

• IC设计方法

(1)全定制设计 (2)半定制设计

通道门阵列法 门海法

• 缺点:会有一定比例的后续工序无法适应软核IP设计, 从而造成一定程度的软核IP修正,在性能上有较大的 不可预知性。

16

EDA概述

CADENCE

• 硬核IP(Hard IP)是经过布局、布线并针对某 一特定工艺库优化过的网表或物理级版图,通 常是GDSⅡ-Stream的文件形式。

• 优点:在功耗、尺寸方面都作了充分的优化, 有很好的预知性。

2

IC设计基础

CADENCE

• 集成电路制造过程示意图:

3

IC设计基础

CADENCE

• 集成电路设计域主要包括三个方面: 行为设计(集成电路的功能设计) 结构设计(逻辑和电路设计) 物理设计(光刻掩模版的几何特性和物 理特性的具体实现)

4

IC设计基础

CADENCE

• 集成电路设计层次主要包括五个层次:

• IP分三类: 软核IP 固核IP 硬核IP

15

EDA概述

CADENCE

• 软核IP(soft IP)是用可综合的硬件描述语言描述的 RTL级电路功能块,不涉及用与什么工艺相关的电路 和电路元件实现这些描述。

• 优点:设计周期短,设计投入少,不涉及物理实现, 为后续设计留有很大发挥空间,增大了IP的灵活性和 适应性。

BODAS-skill

4

输入和输出

电位计输入通道状态监测函数

in_getPotiStatus(ANA_A1); 只有该通道由函数 in_getPoti() 或 in_getPotiDir() 或 in_configPoti() 标定后,该监测函数才有效。

Datum, Abteilung und Vermerke geben Sie über <Ansicht><Kopf- und Fußzeiel> im Feld <Fußzeile> ein © Alle Rechte bei Bosch Rexroth AG, auch für den Fall von Schutzrechtsanmeldungen. Jede Verfügungsbefugnis, wie Kopier- und Weitergaberecht, bei uns.

Datum, Abteilung und Vermerke geben Sie über <Ansicht><Kopf- und Fußzeiel> im Feld <Fußzeile> ein © Alle Rechte bei Bosch Rexroth AG, auch für den Fall von Schutzrechtsanmeldungen. Jede Verfügungsbefugnis, wie Kopier- und Weitergaberecht, bei uns.

Datum, Abteilung und Vermerke geben Sie über <Ansicht><Kopf- und Fußzeiel> im Feld <Fußzeile> ein © Alle Rechte bei Bosch Rexroth AG, auch für den Fall von Schutzrechtsanmeldungen. Jede Verfügungsbefugnis, wie Kopier- und Weitergaberecht, bei uns.

学会skill语言(1)——学习前的准备

学会skill语言(1)——学习前的准备在介绍「ocean脚本仿真」内容的时候已经对skill语言有了初步的了解,后台也有同学询问关于skill 语言的内容,接下来的一段时间小目同学就和大家一起学习关于skill语言的基础内容,希望通过学习,大家可以逐渐掌握skill语言并在工作和学习中灵活使用。

skill语言介绍skill语言是Cadence软件平台使用的一种语言,由Lisp﴾List Processing language﴿发展而来,对于有编程基础的同学来说很容易掌握。

在Cadence软件平台中无论用户在图形界面做的任何操作,在底层都是通过调用相应的skill函数或者程序实现功能的,可以认为Cadence软件平台上凡是可以通过图形界面实现的功能都可以使用相应的skill代码实现,对于图形界面不方便完成的操作也可以通过编写skill脚本完成。

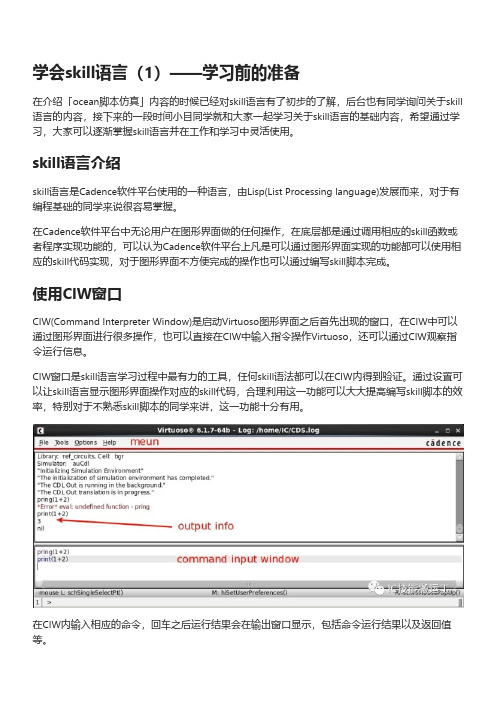

使用CIW窗口CIW﴾Command Interpreter Window﴿是启动Virtuoso图形界面之后首先出现的窗口,在CIW中可以通过图形界面进行很多操作,也可以直接在CIW中输入指令操作Virtuoso,还可以通过CIW观察指令运行信息。

CIW窗口是skill语言学习过程中最有力的工具,任何skill语法都可以在CIW内得到验证。

通过设置可以让skill语言显示图形界面操作对应的skill代码,合理利用这一功能可以大大提高编写skill脚本的效率,特别对于不熟悉skill脚本的同学来讲,这一功能十分有用。

在CIW内输入相应的命令,回车之后运行结果会在输出窗口显示,包括命令运行结果以及返回值等。

在CIW内的菜单栏,通过选择:Options‐>Log Filter,打开Log文件设置窗口,通过勾选相应的选项,设置Log文件的输出内容,方便用户回顾软件运行情况,所有在CIW输出窗口显示的内容都会保存在该CIW相应的CDS.log文件内。

至于Log文件设置窗口中每个符号代表的意义可以通过符号后面的解释知晓,CDS.log文件中的每一行信息也都通过相应的符号进行注释。

allegro特色功能

特色功能

1.class/subclass:使各子件属性分得准确细致,更利于深入了解相关概念、设计过程及工

艺,更规范设计和较小错误;

2.鼠标手势:Stroke Editor

3.Z-copy:

4.place:灵活的元件place功能,区域摆放、根据属性值摆放;

5.布线:实时推挤以及贴线布线功能方便布线修线;

6.铺铜:强大的内层分割及检查功能,动静态铜等;

7.同步:与orCAD紧密结合,方便SCH与PCB的双向同步以及交互设计;

allegro 其中有很多专家级的技术

1。

高速原理图&PCB同时高亮查找。

(当然也可以在原理图中选择网络)

2。

高速的对象查找,小到焊盘。

3。

强大的规则设计就不用说了。

4。

高精度的尺寸单位。

最小到微米,强大的尺寸标注和显示。

5。

基于lisp语言基础的skill开发。

基本上allegro中的操作就是skill功能展示。

6。

最热衷的就是和dxf输入和输出了。

能用autocad进行精确的元件封装设计及pcb外形规划。

Zkh

2010-06。

原理图的电气检查功能

电气规则检的注意事项

报告的生成 报告的内容(包含警告,不包含警告) 报告的作用域(本图、本项目,此时需

注意层次图的端口与网络标号作用范围) 自已编辑的元件的引脚属性是否正确

(如全为Passive,则电气规则检查不报告 错误)

练习4 由555构成锯齿波发生器

原理图图号重叠Duplicate sheet number(指在层次电路图中)

在层次电路中,每 张图纸的图号应该 是不同的,并且需 要手工修改。

Design设计/Option 选项

原理图元件序号重叠

Duplicate sheet number

元件序号重复, 如果生成网络表, 就会少一些元件, 就会造成元件找 不到的情况。

本次教学主要目标:

掌握进行原理图电气规则检查的方法 了解原理图电气规则检查各项的意义 了解原理图电气规则检的基本规则和

注意事项 掌握常见电气规则错误的改正方法

原理图电气规则检查的意义

原理图中的 ERC (电气法则检查)工具能帮助设 计者更快地查出和改正错误.

在完成原理图的绘制后,要对原理图进行检查, 防止由于自己的疏忽,造成原理图中存在的一 些错误,使后面的工作无法正常进行。检查的 方法通常是设计者自己通过观察或是采用电气 规则检查。电气规则检测的速度比较快,可以 输出相关的物理逻辑冲突报告。

总线名称格式错误

总线名称格式

D[0..7] A[0..15] 等

D[0 .. 7 ]Fra bibliotek输入引脚悬空

在一些电路中,输 入引脚必须接一个 确定的电平,漏接 有可能造成电路功 能错误或不稳定。 如,在CMOS电路 中输入引脚是不允 许悬空的。

电气规则检查出错处理方法

生成错误报告(*.ERC) 添加错误标记到原理图

skill语法用户手册

skill语法用户手册一、概述Skill语法是一种基于自然语言处理技术的语法分析器,它可以将自然语言文本转化为结构化的数据,从而方便计算机对文本进行处理和分析。

本用户手册将详细介绍如何使用Skill语法进行文本分析。

二、安装与配置1.安装:请根据您的操作系统和编程环境,按照官方网站的安装指南进行安装。

2.配置:在安装完成后,您需要创建一个新的项目,并选择适合您需求的语法文件。

您可以在官方网站上下载所需的语法文件,或者根据您的需求自行编写。

三、使用方法1.文本输入:将需要分析的文本输入到指定的输入框中。

2.语法分析:点击“开始分析”按钮,系统将自动对输入的文本进行分析。

分析结果将以结构化的形式展示在界面上。

3.数据导出:您可以将分析结果导出为多种格式,如CSV、JSON等,以便在其他应用程序中使用。

四、语法规则Skill语法采用基于规则的自然语言处理技术,通过定义不同的语法规则来解析不同的文本。

以下是常见的一些语法规则:1.名词短语:用于识别句子中的名词或名词短语,如“苹果”、“红色的苹果”。

2.动词短语:用于识别句子中的动词或动词短语,如“吃”、“吃苹果”。

3.形容词短语:用于识别句子中的形容词或形容词短语,如“甜的”、“非常甜的苹果”。

4.时间表达式:用于识别句子中的时间表达式,如“今天”、“明天”、“去年”。

5.数字表达式:用于识别句子中的数字表达式,如“3个”、“50%”、“2023年”。

6.标点符号:用于识别句子中的标点符号,如“、”、“;”、“!”等。

7.停用词:用于识别句子中常见的无意义词汇,如“的”、“了”等。

8.短语类型:用于识别短语类型,如“动词短语+名词短语”、“形容词短语+名词短语”等。

9.语义角色标注:用于识别句子中不同成分之间的语义关系,如“施事”、“受事”、“时间”等。

五、常见问题与解决方法1.问题:无法正常安装和运行。

解决方法:请检查您的操作系统和编程环境是否符合要求,并确保已按照安装指南进行操作。

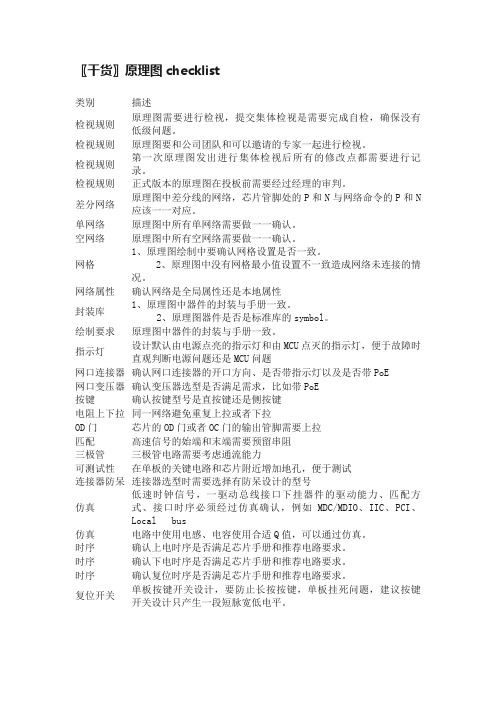

〖干货〗原理图checklist

〖干货〗原理图checklist 类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P和N与网络命令的P和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

网格1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性封装库1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU点灭的指示灯,便于故障时直观判断电源问题还是MCU问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD门芯片的OD门或者OC门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO、IIC、PCI、Local bus仿真电路中使用电感、电容使用合适Q值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

Cadence-skill语言简介

Cadence-skill语⾔简介Cadence skill语⾔简介Cadence提供⼆次开发的SKILL语⾔,它是⼀种基于通⽤⼈⼯智能语⾔—Lisp的交互式⾼级编程语⾔(LISP即List Processing-表处理,是最早和最重要的符号处理编程语⾔之⼀,它于1958年由美国的J. McCarthy提出,LISP在⼈⼯智能AI⽅⾯获得⼴泛应⽤)。

SKILL语⾔⽀持⼀套类似C语⾔的语法,⼤⼤降低了初学者学习的难度,同时⾼⽔平的编程者可以选择使⽤类似Lisp语⾔的全部功能。

所以SKILL语⾔既可以⽤作最简单的⼯具语⾔,也可以作为开发任何应⽤的、强⼤的编程语⾔。

SKILL可以与底层系统交互,也提供了访问Cadence各个⼯具的丰富接⼝。

⽤户可以通过Skill语⾔来访问,并且可以开发⾃⼰的基于Cadence平台的⼯具。

1. Skill语⾔和Lisp语⾔的关系Skill函数提供两种表⽰法,⼀种是代数表⽰法,现在⼤多数语⾔采取这种⽅式,即func( arg1 arg2 ...),另⼀种是前缀表⽰法,类似于Lisp语⾔,即(func arg1 arg2 ...)。

这⾥举个例⼦作为对⽐:1.代数表⽰法procedure( fibonacci(n)if( (n == 1 || n == 2) then1else fibonacci(n-1) + fibonacci(n-2)))2.前缀表⽰法(defun fibonacci (n)(cond((or (equal n 1) (equal n 2)) 1)(t (plus (fibonacci (difference n 1))(fibonacci (difference n 2))))))这⾥可以看到类似Lisp语⾔的表⽰法后⾯有很多右括号,⽽且函数和参数容易混淆,所以⼀般推荐还是⽤常⽤的类C语⾔代数表⽰法Skill程序就像⼀个list表,类似Lisp语⾔,程序的操作就像操作数据(list)⼀样,可以⽣成,修改,求值等2. 关于Skill函数SKILL语⾔⽀持⼀套类似C语⾔的语法,初学者有了⼀定的C语⾔基础,⼊门是很容易的。

Cadence实验教程

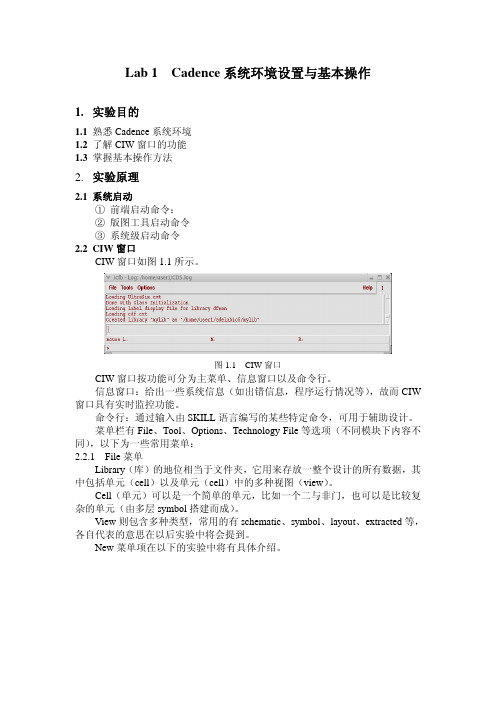

Lab 1 Cadence系统环境设置与基本操作1.实验目的1.1熟悉Cadence系统环境1.2了解CIW窗口的功能1.3掌握基本操作方法2.实验原理2.1系统启动① 前端启动命令:② 版图工具启动命令③ 系统级启动命令2.2CIW窗口CIW窗口如图1.1所示。

图1.1 CIW窗口CIW窗口按功能可分为主菜单、信息窗口以及命令行。

信息窗口:给出一些系统信息(如出错信息,程序运行情况等),故而CIW 窗口具有实时监控功能。

命令行:通过输入由SKILL语言编写的某些特定命令,可用于辅助设计。

菜单栏有File、Tool、Options、Technology File等选项(不同模块下内容不同),以下为一些常用菜单:2.2.1File菜单Library(库)的地位相当于文件夹,它用来存放一整个设计的所有数据,其中包括单元(cell)以及单元(cell)中的多种视图(view)。

Cell(单元)可以是一个简单的单元,比如一个二与非门,也可以是比较复杂的单元(由多层symbol搭建而成)。

View则包含多种类型,常用的有schematic、symbol、layout、extracted等,各自代表的意思在以后实验中将会提到。

New菜单项在以下的实验中将有具体介绍。

图1.2 New Library窗口图1.3 Create New File Library窗口分为Library和Technology File两部分。

Library部分有Name和Directory两项,分别对应要建立的Library名称和路径,Library名称可以自定义。

一般Technology部分选择Don’t need a techfile选项。

如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的工艺文件)或Attach to an existing techfile(使用原有的工艺文件)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于SKILL语言的原理图检查系统实现

摘要:利用VSE提供的二次开发接口,基于SKILL语言编程实现了一个集规则配置、规则集成和规则检查于一体的原理图检查系统。

将该原理图查询系统与VSE无缝集成,能够提供更多的设计规则。

关键词:SKILL;原理图;设计规则

0引言

当IC(Integrated Circuit)工程师进行原理图设计时,要遵循一些基本的电气规则,例如器件输入或输出管脚的连接限制。

一般的原理图设计输入工具都会提供一些基本的原理图检查功能,以保证设计出的原理图满足一定的设计规则,但是不同的IC设计公司往往有不同的需求。

根据调查,目前EDA(Electronic Design Automation)公司很难完美预测IC工程师对原理图检查功能的需求,所以这些预置的设计规则往往比较简单,不能满足IC设计公司的全部需求。

IC工程师不得不花费大量的时间进行人工检查,以保证设计出的原理图符合公司的设计要求,浪费了相当的人力资源,使其不能得到充分的利用。

Cadence公司的Virtuoso Schematic Editor(VSE)是一款使用非常广泛的原理图设计输入工具,它帮助IC设计工程师成功地实现了一个又一个完美的产品设计。

尤其是,它完美集成了Cadence公司自己的SKILL编程语言,提供了完善的二次开发接口。

本文实现的原理图检查系统(Schematic Check System,SCS)

就是基于VSE,充分利用VSE固有的开发接口,用SKILL语言编程实现。

该系统集成于VSE之中,根据IC设计公司的需求,提供了更多的设计检查规则以满足IC工程师的需要,极大地提高了工作效率。

1原理图检查系统

本文充分利用VSE的二次开发接口,实现了一个集规则配置、规则集成和规则检查于一体的软件系统,并且把它和VSE无缝集成在一起,可以方便地在原理图上进行检查结果反标。

系统结构如图1所示。

1.1设计规则

在本系统中,每一条设计规则由四部分组成:

规则标识——例如ID1。

规则描述——例如Naming conventions(Terminal in uppercase and net in lowercase)。

规则作用域——可以应用一条规则对原理图中的所有设计元素进行检查,也可以指定一条规则仅仅对某一个设计元素进行检查。

规则检查函数——每一条规则都有一个相应的SKILL函数去执行规则检查。

到目前为止,本系统实现了13条设计规则,如图2所示。

用户将通过上图的“Schematic Rules Setting”窗口进行规则配置:(1)选择一条规则,例如ID1:Naming conventions(Terminal in uppercase and net in lowercase)。

(2)指定规则作用域。

如果想用这条规则对当前原理图中所有设计元素进行检查,在“Rule Scope”中选择“All”;

如果想用这条规则对当前原理图中的某种器件进行检查,在“RuleScope”中选择“Cell”;

如果想用这条规则对当前原理图中的某种器件的某个管脚进行检查,在“Rule Scope”中选择“Cell Terminal”;

如果想用这条规则对当前原理图中的某个器件的例示进行检查,在“Rule Scope”中选择“Instance”;

如果想用这条规则对当前原理图中的某个网络进行检查,在“RuleScope”中选择“Net”。

对“Cell”、“Cell Terminal”、“Instance”、“Net”,IC工程师可以点击“Select”按钮在当前原理图中进行选择。

(3)使能规则。

对一个规则进行配置后,点击“Add”按钮将把配置完成的规则加入到“Schematic Rules Summary”表格中,然后进行下一个规则的配置。

完成配置的“Schematic Rules Setting”窗口如图3所示。

1.2规则集成

完成需要的规则配置后,点击“Schematic Rules Setting”窗口中的“OK”按钮。

系统将调用SKILL函数,利用VSE提供的接口把这些规则和VSE预置的设计规则集成在一起。

(1)调用SKILL函数创建一个规则组。

如下所示:

schRegisterCheckGroup(

?name concat("Schematic Check System")

?description strcat("the rules of Schematic Check System")

)

(2)对每一个配置好的规则调用SKILL函数,将它注册到上面创建的规则组中。

如下所示:

schRegisterCheckRule(

?title "ID1:Naming conventions"

?name 'namingConventions

?groupName concat("Schematic Check System")

?severity 'error

?checkCB '_scsCheckNamingConventions

)

(3)注册之后,这些规则就和VSE预置的设计规则一样。

在VSE中点击Check->Rules Setup菜单打开“Schematic Rules Checks Setup”窗口,如图4所示,被注册到同一个规则组中的所有规则被显示在同一个页面中。

每一条规则都有相应的出错等级,IC 工程师可以通过该窗口进行配置。