IRLML2244TRPBF;中文规格书,Datasheet资料

IRFTS9342TRPBF;中文规格书,Datasheet资料

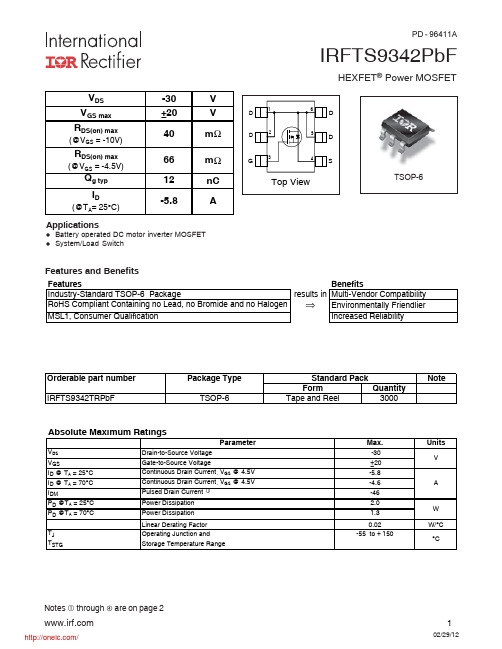

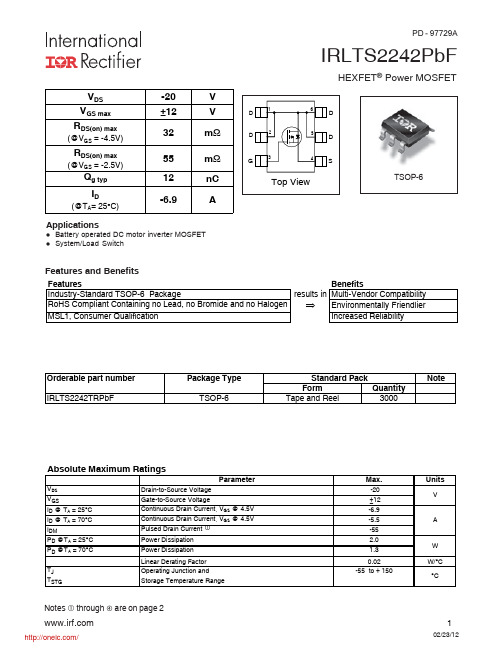

IRFTS9342PbFHEXFET ® Power MOSFETNotes through are on page 2Applicationsl Battery operated DC motor inverter MOSFET lSystem/Load SwitchFeatures and Benefitsresults in ⇒PD - 96411AIRFTS9342PbFNotes:Repetitive rating; pulse width limited by max. junction temperature. Pulse width ≤ 400μs; duty cycle ≤ 2%.When mounted on 1 inch square copper board.Static @ T = 25°C (unless otherwise specified)IRFTS9342PbFFig 4. Normalized On-Resistance vs. TemperatureFig 2. Typical Output CharacteristicsFig 1. Typical Output CharacteristicsFig 6. Typical Gate Charge vs.Gate-to-Source VoltageFig 5. Typical Capacitance vs.Drain-to-Source Voltage T J , Junction Temperature (°C)R D S (o n ) , D r a i n -t o -S o u r c e O n R e s i s t a n c e 110100-V DS , Drain-to-Source Voltage (V)10100100010000C , C a p a c i t a n c e (p F )0246810121416Q G Total Gate Charge (nC)0.02.04.06.08.010.012.014.0-V G S , G a t e -t o -S o u r c e V o l t a g e (V )DS -V DS , Drain-to-Source Voltage (V)0.1110100-I D , D r a i n -t o -S o u r c e C u r r e n t (A )IRFTS9342PbFFig 11. Maximum Effective Transient Thermal Impedance, Junction-to-CaseFig 8. Maximum Safe Operating AreaFig 9. Maximum Drain Current vs.Case TemperatureFig 7. Typical Source-Drain Diode Forward VoltageFig 10. Threshold Voltage vs. Temperature255075100125150T A , Ambient Temperature (°C)0123456-I D , D r a i n C u r r e n t (A)0.010.1110100V DS , Drain-to-Source Voltage (V)0.010.11101001000I D , D r a i n -t o -S o u r c e C u r r e n t (A)0.1110100-I S D , R e v e r s e D r a i n C u r r e n t (A )T J , Temperature ( °C )-V G S (t h ), G a t e t h r e s h o l d V o l t a g e (V )IRFTS9342PbFFig 12. On-Resistance vs. Gate VoltageFig 14. Maximum Avalanche Energy vs. Drain Current Fig 15. Typical Power vs. Time* Reverse Polarity of D.U.T for P-Channel* V GS = 5V for Logic Level Devices®2468101214161820-V GS, Gate -to -Source Voltage (V)255075100125150Starting T J , Junction Temperature (°C)020406080100120E A S , S i n g l e P u l s e A v a l a n c h e E n e r g y (m J )Time (sec)P o w e r (W )IRFTS9342PbFFig 17a. Gate Charge Test CircuitFig 17b. Gate Charge WaveformFig 18b. Unclamped Inductive WaveformsFig 18a. Unclamped Inductive Test CircuitFig 19b. Switching Time WaveformsFig 19a. Switching Time Test CircuitIdQgs1Qgs2Qgd QgodrV DDR DV DDI ASV DSV GSt t t tNote: For the most current drawing please refer to IR website at: /package/WW = (27-52) IF PRECEDED BY A LETTERYEA R Y Z52W WORK WEEK 26ZF = IRF5801(a s show n here) indica tes Lead-F ree.Note: A line above the w ork w eek G = IRF5803D = IRF5851E = IRF5852I = IRF 5805C = IRF5850N = IRF 5802K = IRF5810J = IRF5806H = IRF 5804S = Not a pplicable R = IRFTS 9342TRPBF T = IRLT S2242TRPBFIRFTS9342PbFTSOP-6 Tape and Reel Information† Qualification standards can be found at International Rectifier’s web site /product-info/reliability†† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information: /whoto-call/salesrep/†††Applicable version of JEDEC standard at the time of product release.IR WORLD HEADQUARTERS: 101 N. Sepulveda Blvd., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903Visit us at for sales contact information . 02/2012Data and specifications subject to change without notice.8mmFEED DIRECTION4mmNOTES :1. OUTLINE CONFORMS TO EIA-481 & EIA-541.9.90 ( .390 )8.40 ( .331 )178.00( 7.008 ) MAX.NOTES:1. CONTROLLING DIMENSION : MILLIMETER.2. OUTLINE CONFORMS TO EIA-481 & EIA-541.Qualification information †分销商库存信息: IRIRFTS9342TRPBF。

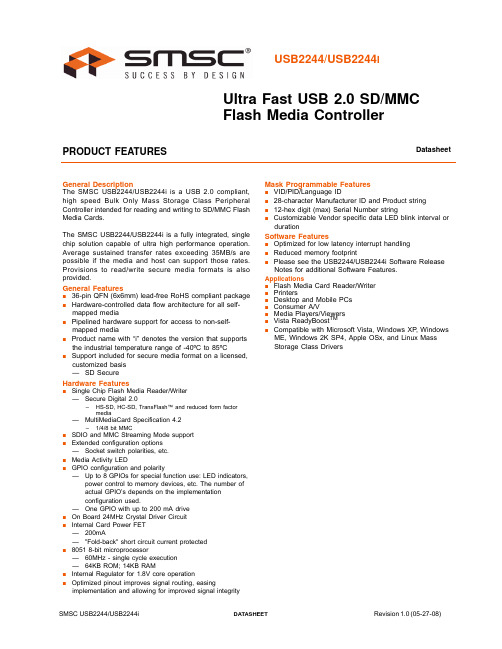

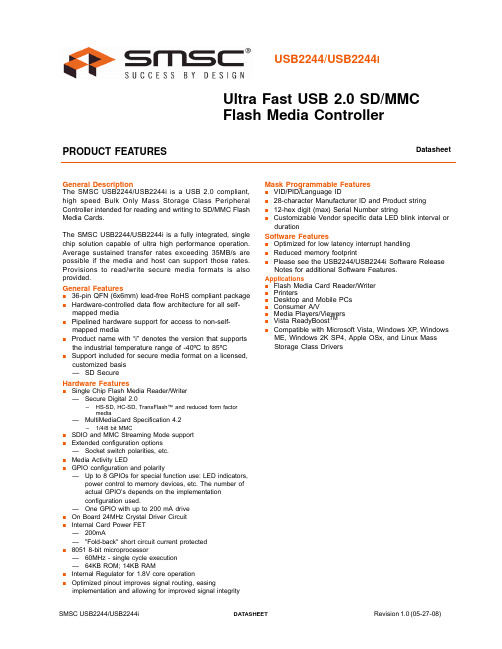

USB2244中文资料

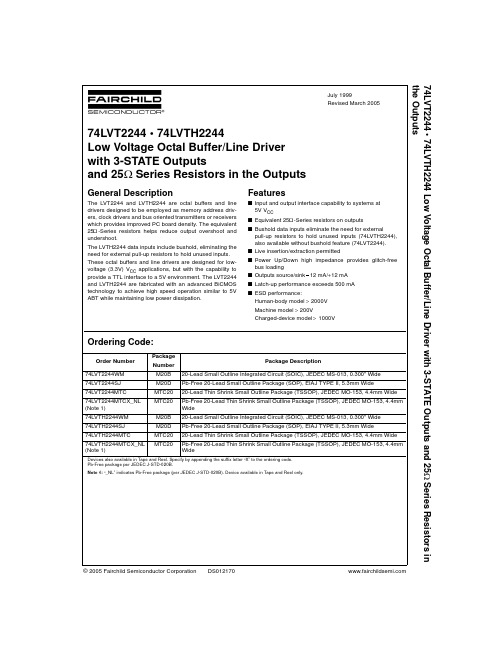

DatasheetPRODUCT FEATURESUSB2244/USB2244IUltra Fast USB 2.0 SD/MMC Flash Media ControllerGeneral DescriptionThe SMSC USB2244/USB2244i is a USB 2.0 compliant,high speed Bulk Only Mass Storage Class Peripheral Controller intended for reading and writing to SD/MMC Flash Media Cards.The SMSC USB2244/USB2244i is a fully integrated, single chip solution capable of ultra high performance operation.Average sustained transfer rates exceeding 35MB/s are possible if the media and host can support those rates.Provisions to read/write secure media formats is also provided.General Features36-pin QFN (6x6mm) lead-free RoHS compliant package Hardware-controlled data flow architecture for all self-mapped mediaPipelined hardware support for access to non-self-mapped mediaProduct name with “i” denotes the version that supports the industrial temperature range of -40ºC to 85ºCSupport included for secure media format on a licensed, customized basis —SDSecureHardware FeaturesSingle Chip Flash Media Reader/Writer —Secure Digital 2.0–HS-SD, HC-SD, TransFlash™ and reduced form factor media —MultiMediaCard Specification 4.2–1/4/8 bit MMCSDIO and MMC Streaming Mode support Extended configuration options —Socket switch polarities, etc. Media Activity LEDGPIO configuration and polarity—Up to 8 GPIOs for special function use: LED indicators,power control to memory devices, etc. The number of actual GPIO’s depends on the implementation configuration used.—One GPIO with up to 200 mA drive On Board 24MHz Crystal Driver CircuitInternal Card Power FET —200mA—"Fold-back" short circuit current protected8051 8-bit microprocessor—60MHz - single cycle execution —64KB ROM; 14KB RAMInternal Regulator for 1.8V core operationOptimized pinout improves signal routing, easingimplementation and allowing for improved signal integrityMask Programmable FeaturesVID/PID/Language ID28-character Manufacturer ID and Product string 12-hex digit (max) Serial Number stringCustomizable Vendor specific data LED blink interval or durationSoftware FeaturesOptimized for low latency interrupt handling Reduced memory footprintPlease see the USB2244/USB2244i Software Release Notes for additional Software Features.ApplicationsFlash Media Card Reader/Writer PrintersDesktop and Mobile PCs Consumer A/VMedia Players/Viewers Vista ReadyBoost TMCompatible with Microsoft Vista, Windows XP , Windows ME, Windows 2K SP4, Apple OSx, and Linux Mass Storage Class DriversORDER NUMBER:USB2244/USB2244i-AEZG-XX for 36 pin, QFN Lead-Free RoHS Compliant Package “XX” in the order number indicates the internal ROM firmware revision level.Please contact your SMSC sales representative for more information.80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123Copyright © 2008 SMSC or its subsidiaries. All rights reserved.Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC’s website at . SMSC is a registered trademark of Standard Microsystems Corporation (“SMSC”). Product names and company names are the trademarks of their respective holders.SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.Ultra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheetUltra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheetTable of ContentsChapter1Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Chapter2Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Chapter3Pin Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 3.136-Pin Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Chapter4Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Chapter5Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 5.1Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 5.2Buffer Type Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Chapter6Pin Reset State Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 6.136-Pin Reset States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14Chapter7DC Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 7.1Maximum Guaranteed Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 7.2Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 7.3DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 7.4Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Chapter8AC Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 8.1Oscillator/Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Chapter9Package Outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Chapter10GPIO Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22Ultra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheet List of FiguresFigure2.1USB2244/USB2244i Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure4.1USB2244/USB2244i 36 Pin QFN Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure6.1Pin Reset States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure6.2Legend for Pin Reset States Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure7.1Supply Rise Time Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure8.1Typical Crystal Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure8.2Formula to Find Value of C1 and C2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure9.1USB2244/USB2244i 36-QFN, 6x6mm Body, 0.5mm Pitch . . . . . . . . . . . . . . . . . . . . . . . . . . 21Ultra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheetList of TablesTable3.1USB2244/2244i 36-Pin QFN Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Table5.2USB2244/2244i 36-Pin QFN Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table5.3USB2244/USB2244i Buffer Type Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Table6.1USB2244/USB2244i Pin Reset States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table7.1Pin Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Table10.1USB2244/USB2244i GPIO Usage(ROM Rev 0x00). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22Ultra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheetRevision 1.0 (05-27-08)6SMSC USB2244/USB2244iChapter 1 AcronymsMMC: MultiMediaCard PLL: Phase-Locked Loop QFN: Quad Flat no LeadsRoHS: Restriction of Hazardous Substances Directive SD: Secure DigitalSDIO: Secure Digital Input/Output SDC: Secure Digital Controllerl SIE: Serial Interface Engine*Note: In order to develop, make, use, or sell readers and/or other products using or incorporating any of the SMSC devices made the subject of this document or to use related SMSC software programs, technical information and licenses under patent and other intellectual property rights from or through various persons or entities, including without limitation media standard companies,forums, and associations, and other patent holders may be required. These media standard companies, forums, and associations include without limitation the following: Sony Corporation (Memory Stick, Memory Stick Pro); SD3 LLC (Secure Digital); MultiMedia Card Association (MultiMediaCard); the SSFDC Forum (SmartMedia); the Compact Flash Association (Compact Flash); and Fuji Photo Film Co., Ltd., Olympus Optical Co., Ltd., and Toshiba Corporation (xD-Picture Card). SMSC does not make such licenses or technical information available; does not promise or represent that any such licenses or technical information will actually be obtainable from or through the various persons or entities (including the media standard companies, forums, and associations), or with respect to the terms under which they may be made available; and is not responsible for the accuracy or sufficiency of, or otherwise with respect to, any such technical information.SMSC's obligations (if any) under the Terms of Sale Agreement, or any other agreement with any customer, or otherwise, with respect to infringement, including without limitation any obligations to defend or settle claims, to reimburse for costs, or to pay damages, shall not apply to any of the devices made the subject of this document or any software programs related to any of such devices, or to any combinations involving any of them, with respect to infringement or claimed infringement of any existing or future patents related to solid state disk or other flash memory technology or applications ("Solid State Disk Patents"). By making any purchase of any of the devices made the subject of this document, the customer represents, warrants, and agrees that it has obtained all necessary licenses under then-existing Solid State Disk Patents for the manufacture, use and sale of solid state disk and other flash memory products and that the customer will timely obtain at no cost or expense to SMSC all necessary licenses under Solid State Disk Patents; that the manufacture and testing by or for SMSC of the units of any of the devices made the subject of this document which may be sold to the customer, and any sale by SMSC of such units to the customer, are valid exercises of the customer's rights and licenses under such Solid State Disk Patents; that SMSC shall have no obligation for royalties or otherwise under any Solid State Disk Patents by reason of any such manufacture, use, or sale of such units; and that SMSC shall have no obligation for any costs or expenses related to the customer's obtaining or having obtained rights or licenses under any Solid State Disk Patents.SMSC MAKES NO WARRANTIES, EXPRESS, IMPLIED, OR STATUTORY, IN REGARD TO INFRINGEMENT OR OTHER VIOLATION OF INTELLECTUAL PROPERTY RIGHTS. SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES AGAINST INFRINGEMENT AND THE LIKE.No license is granted by SMSC expressly, by implication, by estoppel or otherwise, under any patent, trademark, copyright, mask work right, trade secret, or other intellectual property right.**To obtain this software program the appropriate SMSC Software License Agreement must be executed and in effect. Forms of these Software License Agreements may be obtained by contacting SMSC.Ultra Fast USB 2.0 SD/MMC Flash Media Controller DatasheetSMSC USB2244/USB2244i 7Revision 1.0 (05-27-08)Chapter 2 Block DiagramFigure 2.1 USB2244/USB2244i Block DiagramUltra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheetRevision 1.0 (05-27-08)8SMSC USB2244/USB2244iChapter 3 Pin Table3.136-Pin PackageTable 3.1 USB2244/2244i 36-Pin QFN PackageSD/MMC INTERFACE (12 Pins)SD_D0SD_D1SD_D2SD_D3SD_D4SD_D5SD_D6SD_D7SD_CLK SD_CMD SD_WP GPIO15 (SD_nCD)USB INTERFACE (7 PINS)USB+USB-RBIASXTAL1 (CLKIN)XTAL2VDDA33VDD18PLLMISC (13 PINS)GPIO1 (LED1)GPIO2 / RXD / SDA GPIO4GPIO7 / TXD / SCKGPIO10 (CRD_PWR)GPIO12GPIO14(4) NCTEST nRESETDIGITAL, POWER (4 PINS)(3)VDD33VDD18TOTAL 36Ultra Fast USB 2.0 SD/MMC Flash Media Controller DatasheetSMSC USB2244/USB2244i 9Revision 1.0 (05-27-08)Chapter 4 Pin ConfigurationFigure 4.1 USB2244/USB2244i 36 Pin QFN DiagramUltra Fast USB 2.0 SD/MMC Flash Media ControllerDatasheetRevision 1.0 (05-27-08)10SMSC USB2244/USB2244iChapter 5 Pin DescriptionsThis section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.The “n” symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. When “n” is not present before the signal name, the signal is asserted at the high voltage level.The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of “active low” and “active high” signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.5.1 Pin DescriptionsTable 5.2 USB2244/2244i 36-Pin QFN Pin DescriptionsNAMESYMBOL36-PIN QFNBUFFER TYPEDESCRIPTIONSECURE DIGITAL INTERFACESD DataSD_D[7:0]781020232545I/O12PUThe bi-directional signals should have weak pull-up resistors. The register can be controlled by: SD_MMC_INTF_EN bit of SDC_MODE_CTLSD Clock SD_CLK 9O12This is an output clock signal to SD/MMC device.The clock frequency is software configurable.SD Command SD_CMD 11I/O12PUThis is a bi-directional signal that connects to the CMD signal of SD/MMC device. The bi-directional signal should have an internal weak pull-up resistor.The pull-up register can be controlled by:SD_MMC_INTF_EN bit of SDC_MODE CTLSD Write Protect SD_nWP 30I/O12This pin is designated as the Secure Digital card mechanical write detect pin.SD Card Detect GPIOGPIO15 (SD_nCD)26I/O12This is a GPIO designated as the Secure Digital card detection pin.USB INTERFACEUSB Bus Data USB+USB-23I/O-U These pins connect to the USB bus data signals.USB Transceiver BiasRBIAS35I-RA 12.0k , 1.0% resistor is attached from VSSA to this pin in order to set the transceiver's internal bias currents.24MHz Crystal or external clock inputXTAL1 (CLKIN)33ICLKxThis pin can be connected to one terminal of the crystal or it can be connected to an external 24 clock when a crystal is not used.24MHz CrystalXTAL232OCLKxThis is the other terminal of the crystal, or it can be left open when an external clock source is used to drive XTAL1(CLKIN). It may not be used to drive any external circuitry other than the crystal circuit.3.3V Analog PowerVDDA3336 3.3V Analog Power1.8V PLL PowerVDD18PLL34This pin is the 1.8V Power for the PLL.+1.8V Filtered analog power for internal PLL. This pin must have a 1.0μF(or greater) ±20% (ESR <0.1Ω) capacitor to VSS.MISCGeneral Purpose I/OGPIO1 (LED1)1I/O12This pin may be used either as input, edge sensitive interrupt input, or output.In addition, as an output, the GPIO1 can use output controlled by the LED1_GPIO1 register.General Purpose I/OGPIO2 / RXD / SDA27I/O12GPIO: This pin may be used either as input, edge sensitive interrupt input, or output.IRXD: In addition to the above, the signal can be used as input to the RXD of UART in the device, when the TXD_RXD_SEL bit in UTIL_CONFIG1 register is cleared to "0".I/O12SDA: This is the data pin when used with an external serial EEPROM.General Purpose I/OGPIO429I/O12This pin may be used either as input, edge sensitive interrupt input, or output.General Purpose I/OGPIO7 / TXD / SCK31I/O12GPIO: This pin may be used either as input, edge sensitive interrupt input, or output.O12TXD: In addition, as an output, the GPIO7 can be used as an output TXD of UART in the device, when the GPIO2/TXD bit in UTL_CONFIG register is set to "1"O12SCK: This is the clock output when used with an external EEPROM.General Purpose I/OGPIO10 (CRD_PWR)21I/O200GPIO: This pin may be used either as input, edge sensitive interrupt input, or output. CRD_PWR: Card Power drive of 3.3V @ either 100mA or 200mA.General Purpose I/OGPIO1419I/O12This pin may be used either as input, edge sensitive interrupt input, or output.RESET InputnRESET18ISThis active low signal is used by the system to reset the chip. The active low pulse should be at least 1μs wide.NAME SYMBOL 36-PIN QFN BUFFER TYPE DESCRIPTION5.2 Buffer Type DescriptionsTEST InputTEST28IThis signal is used for testing the chip. User should normally tie this pin low externally if the test function is not used.No Connects NCNo Connect. No trace or signal should be routed/attached to these pins.DIGITAL / POWER+1.8V Core powerVDD1813All VDD18 pins must be connected together on the circuit board.+1.8V core power. This pin must have a 1.0μF (or greater) ±20% (ESR <0.1Ω) capacitor to VSS.3.3V Power & Regulator Input.VDD3361422 3.3V Power & Regulator Input.GroundVSS SLUGGround ReferenceTable 5.3 USB2244/USB2244i Buffer Type DescriptionsBUFFERDESCRIPTIONI Input.IS Input with Schmitt trigger.I/O12Input/Output buffer with 12mA sink and 12mA source.I/O200Input/Output buffer 12mA with FET disabled, 100/200mA source only when the FET is enabled.I/O12PU Input/Output buffer with 12mA sink and 12mA source with a pull-up resistor.O12Output buffer with 12mA source.ICLKx XTAL clock input.OCLKx XTAL clock output.I/O-U Analog Input/Output Defined in USB specification.I-RRBIAS.NAME SYMBOL 36-PIN QFN BUFFER TYPE DESCRIPTIONChapter6 Pin Reset State TableFigure6.1 Pin Reset StatesLEGENDyes hardware enables function--hardware disables functionz hardware disables output driverpu hardware enables pulluppd hardware enables pulldownhw hardware controls function, but state is protocol dependent(fw)firmware controls function through registersVDD hardware supplies power through pin, applicable only to CARD_PWR pinsnone hardware disables padFigure6.2 Legend for Pin Reset States Table6.1 36-Pin Reset StatesTable6.1 USB2244/USB2244i Pin Reset StatesRESET STATE Post-Reset State SD ModePIN PIN NAME FUNCTION OUT-PUT PU/PDIN-PUT FUNCTIONOUT-PUTPU/PDIN-PUT8SD_D6none z----SD_D6hw pu yes 7SD_D7none z----SD_D7hw pu yes 5SD_D0none z----SD_D0hw pu yes 4SD_D1none z----SD_D1hw pu yes 30SD_WP SD_WP0----SD_WP(fw)(fw)(fw) 25SD_D2none z----SD_D2hw pu yes 23SD_D3none z----SD_D3hw pu yes 20SD_D4none z----SD_D4hw pu yes 9SD_CLK none z----SD_CLK hw--yes 10SD_D5none z----SD_D5hw pu yes 11SD_CMD none z----SD_CMD hw pu yes 19GPIO14GPIO z pu yes26GPIO15 (SD_nCD)GPIO z pu yes24GPIO12GPIO z pu yes27GPIO2 / RXD / SDA GPIO0----RXD z pu yes 29GPIO4GPIO0----31GPIO7 / TXD / SCK GPIO0----TXD hw----21GPIO10(CARD_PWR)GPIO z----PWR VDD----28TEST TEST z--yes18nRESET nRESET z--yes1GPIO1 (LED1)GPIO10----17:15NC none z----none z----12NC none z----none z----2USB+USB+z----3USB-USB-z----35RBIAS33XTAL1 (CLKIN)32XTAL2Chapter 7 DC Parameters7.1Maximum Guaranteed RatingsNote 7.1Stresses above the specified parameters may cause permanent damage to the device.This is a stress rating only and functional operation of the device at any condition above those indicated in the operation sections of this specification is not implied.Note 7.2When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off.In addition, voltage transients on the AC power line may appear on the DC output. When this possibility exists, it is suggested that a clamp circuit be used.PARAMETER SYMBOL MIN MAXUNITS COMMENTSStorage Temperature T A-55150°C LeadTemperature 325°C Soldering < 10 seconds3.3V supply voltage V DD33, V DDA33-0.5 4.0V Voltage on USB+ and USB- pins -0.5(3.3V supply voltage + 2) ≤ 6VVoltage on GPIO10-0.5V DD33 + 0.3VWhen internal power FET operation of this pin is enabled, this pin may be simultaneously shorted to ground or anyvoltage up to 3.63V indefinitely, without damage to the device as long as V DD33 and V DDA33 are less than 3.63V and T A is less than 70o C.Voltage on any signal pin -0.5V DD33 + 0.3V Voltage on XTAL1 -0.5 4.0V Voltage on XTAL2-0.5V DD18 + 0.3VFigure 7.1 Supply Rise Time Model7.2 Recommended Operating ConditionsNote 7.3A 3.3V regulator with an output tolerance of 1% must be used if the output of the internal power FET’s must support a 5% tolerance.PARAMETERSYMBOLMINMAXUNITSCOMMENTSOperating Temperature Commercial Part Industrial Part T A T A 0-407085°C °C 3.3V supply voltage V DD33, V DDA33 3.0 3.6V (Note 7.3)3.3V supply rise time tRT0400μs Voltage onUSB+ and USB- pins-0.35.5VIf any 3.3V supply voltage drops below 3.0V, then the MAX becomes:(3.3V supply voltage) + 0.5 ≤ 5.5Voltage on any signal pin-0.3V DD33V Voltage on XTAL1 -0.3V DDA33V Voltage on XTAL2-0.3V DD18V7.3 DC Electrical CharacteristicsPARAMETER SYMBOL MIN TYP MAX UNITS COMMENTS I, IPU, IPD Type Input BufferLow Input Level High Input Level Pull DownPull Up V ILIV IHIPDPU2.072580.8VVμAμATTL LevelsIS Type Input BufferLow Input Level High Input Level HysteresisV ILIV IHIV HYSI2.04200.8VVmVTTL LevelsICLK Input BufferLow Input Level High Input Level Input Leakage V ILCKV IHCKI IL1.4-100.5+10VVμA VIN = 0 to V DD33Input Leakage (All I and IS buffers)Low Input Leakage High Input Leakage I ILI IH-10-10+10+10μAμAV IN = 0V IN = V DD33O12 Type BufferLow Output Level High Output Level Output Leakage V OLV OHI OLV DD33- 0.4-100.4+10VVμAI OL = 12mA @V DD33= 3.3VI OH = -12mA @V DD33= 3.3VV IN = 0 to V DD33(Note7.4)Note 7.4Output leakage is measured with the current pins in high impedance.Note 7.5See The USB 2.0 Specification, Chapter 7, for USB DC electrical characteristics Note 7.6RBIAS is a 3.3V tolerant analog pin.Note 7.7Output current range is controlled by program software, software disables FET during short circuit condition.Note 7.8The assignment of each Integrated Card Power FET to a designated Card Connector is controlled by both firmware and the specific board implementation. Firmware will default toI/O12, I/O12PU & I/O12PD Type BufferLow Output LevelHigh Output LevelOutput LeakagePull Down Pull Up V OLV OHI OL PD PUV DD33 - 0.4-1072580.4+10VVµAμA μAI OL = 12mA @ V DD33= 3.3V I OH = -12mA @ V DD33= 3.3V V IN = 0 to V DD33(Note 7.4)IO-U(Note 7.5)I-R(Note 7.6)I/O200Integrated Power FET for GPIO10High Output Current Mode Low Output Current Mode (Note 7.7)On Resistance (Note 7.7)Output Voltage Rise Time I OUT I OUT R DSON t DSON 2001002.1800mA mAΩμs Vdrop FET = 0.46V Vdrop FET = 0.23V I FET = 70mA C LOAD = 10μFSupply Current Unconfigured I CCINIT 8090mA Supply Current Active Full Speed High SpeedI CC I CC 110135140165mA mA Supply Current Suspend I CSBY 350700µA Industrial Temperature SuspendI CSBYI350900µAPARAMETERSYMBOL MIN TYP MAX UNITS COMMENTSthe settings listed in Table10.1, “USB2244/USB2244i GPIO Usage(ROM Rev 0x00),” onpage22.Note7.9The 3.3V supply should be at least at 75% of its operating condition before the 1.8V supply is allowed to ramp up.7.4 CapacitanceT A = 25°C; fc = 1MHz; V DD, V DDP = 1.8VTable7.1 Pin CapacitancePARAMETER SYMBOLLIMITSUNIT TEST CONDITION MIN TYP MAXClock Input Capacitance C XTAL2pF All pins (except USB pinsand pins under test) are tiedto AC ground.Input Capacitance C IN10pFOutput Capacitance C OUT20pFChapter8 AC Specifications8.1 Oscillator/ClockCrystal:Parallel Resonant, Fundamental Mode, 24 MHz ± 100ppm.External Clock: 50% Duty cycle ± 10%, 24 MHz ± 100ppm, Jitter < 100ps rms.Figure8.1 Typical Crystal CircuitNote:C B equals total board/trace capacitance.Figure8.2 Formula to Find Value of C1 and C2。

IRF8852TRPBF;中文规格书,Datasheet资料

VGS, Gate-to-Source Voltage (V)

Fig 3. Typical Transfer Characteristics

Fig 4. Normalized On-Resistance vs. Temperature

3

/

IRF8852PbF

PD - 96246

IRF8852PbF

l l l l l l

Ultra Low On-Resistance Dual N-Channel MOSFET Very Small SOIC Package Low Profile (< 1.1mm) Available in Tape & Reel Lead-Free

Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage

100

1000 OPERATION IN THIS AREA LIMITED BY R DS(on)

10

TJ = 150°C

ID, Drain-to-Source Current (A)

ISD, Reverse Drain Current (A)

Conditions

VGS = 0V, ID = 250µA

V/°C Reference to 25°C, ID = 1mA VGS = 10V, ID = 7.8A mΩ VGS = 4.5V, ID = 6.2A V VDS = VGS, ID = 25µA

e e

µA nA S nC nC Ω

VDS = 20V, VGS = 0V VDS = 20V, VGS = 0V, TJ = 70°C VGS = 20V VGS = -20V VDS = 10V, ID = 7.8A ID = 7.8A,VDS= 13V, VGS = 4.5V ID = 7.8A VDS = 13V VGS = 10V VDD = 13V, VGS = 10V ID = 1.0A RD =13 Ω RG =30 Ω VGS = 0V VDS = 20V ƒ = 1.0MHz Max. 6.5 7.8 Units mJ A

IR2156STRPBF;IR2156PBF;IR2156SPBF;IR2156S;IR2156;中文规格书,Datasheet资料

Features•Ballast control and half-bridge driver in one IC •Programmable preheat frequency •Programmable preheat time •I nternal ignition ramp•Programmable over-current threshold •Programmable run frequencyData Sheet No. PD60182-IBALLAST CONTROL ICCFL Application Diagram•Programmable dead time •DC bus under-voltage reset •Shutdown pin with hysteresis•Internal 15.6V zener clamp diode on Vcc •Micropower startup (150µA)•Latch immunity and ESD protection •Also available LEAD-FREE (PbF)Descriptionboth 14 lead PDIP and 14 lead SOIC packages. 1IR2156(S ) & (PbF)IR2156(S) & (PbF) 2Absolute Maximum RatingsAbsolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.Note 1:This IC contains a zener clamp structure between the chip V CC and COM which has a nominal breakdown voltage of 15.6V. Please note that this supply pin should not be driven by a DC, low impedance power sourcegreater than the V CLAMP specified in the Electrical Characteristics section.IR2156(S ) & (PbF)3Recommended Operating ConditionsFor proper operation the device should be used within the recommended conditions.Note 2:Enough current should be supplied into the V CC lead to keep the internal 15.6V zener clamp diode on this lead regulating its voltage, V CLAMP .Electrical CharacteristicsV CC = V BS = V BIAS = 14V +/- 0.25V, V VDC = Open, R T = 39.0k Ω, R PH = 100.0k Ω, C T = 470 pF, V CPH = 0.0V, V CS = 0.0V,V SD = 0.0V, C LO, HO = 1000pF , T = 25o C unless otherwise specified.IR2156(S) & (PbF) 4Electrical CharacteristicsV CC = V BS = V BIAS = 14V +/- 0.25V, V VDC = Open, R T = 39.0kΩ, R PH= 100.0kΩ, C T = 470 pF, V CPH = 0.0V, V CS = 0.0V, V SD = 0.0V, C LO, HO = 1000pF, T A = 25o C unless otherwise specified.IR2156(S ) & (PbF)5Block DiagramIR2156(S) & (PbF) 6State DiagramVCC < 9.5V(VCC Fault or Power Down)orSD > 5.1V(Lamp Fault or Lamp Removal)IR2156(S ) & (PbF)7Timing DiagramsNormal operationIR2156(S) & (PbF) 8Timing Diagrams Fault conditionIR2156(S ) & (PbF)9IR2156(S) & (PbF) 10( A分销商库存信息:IRIR2156STRPBF IR2156PBF IR2156SPBF IR2156S IR2156IR2156STR。

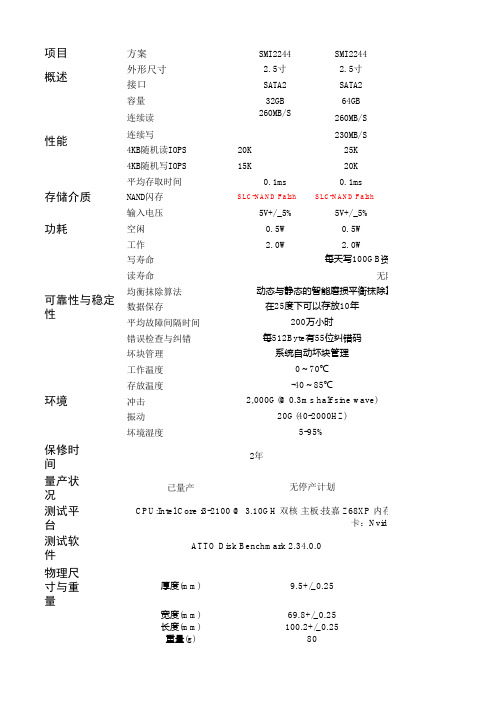

SMI2244参数规格表

方案SMI2244SMI2244外形尺寸 2.5寸 2.5寸接口SATA2SATA2容量32GB 64GB 连续读260MB/S 260MB/S 连续写220MB/S 230MB/S 4KB随机读IOPS 20K 25K 4KB随机写IOPS 15K20K 平均存取时间0.1ms0.1msNAND闪存SLC-NAND FalshSLC-NAND Falsh输入电压5V+/_5%5V+/_5%空闲0.5W 0.5W 工作 2.0W2.0W写寿命读寿命均衡抹除算法数据保存平均故障间隔时间错误检查与纠错坏块管理工作温度存放温度冲击振动坏境湿度保修时间量产状况已量产测试平台测试软件物理尺寸与重量厚度(mm)宽度(mm)长度(mm)重量(g)动态与静态的智能磨损平衡抹除算法9.5+/_0.2569.8+/_0.25100.2+/_0.25805-95%Core i3-2100 @ 3.10GH 双核 主板:技嘉 Z68XP 内存:DDR3 2GB(1333MHZ) Windows7 旗舰版ATTO Disk Benchmark 2.34.0.0-40~85℃2,000G(@0.3ms half sine wave)20G(40-2000HZ)每天写100GB 资料可以用16年无限无停产计划2年在25度下可以存放10年200万小时每512Byte 有55位纠错码系统自动坏块管理0~70℃可靠性与稳定性环境功耗性能存储介质项目概述SMI2244SMI2244SMI22441.8寸 1.8寸2.5寸M-SATA M-SATA SATA232GB64GB128GB260MB/S260MB/S270MB/S50MB/S90MB/S190MB/S20K25K25K12K15K15K0.1ms0.1ms0.1ms MLC-NAND Falsh MLC-NAND Falsh MLC-NAND Falsh 5V+/_5%5V+/_5%5V+/_5%0.5W0.5W0.5W2.0W 2.0W 2.0W除算法,压缩和重复的数据算法。

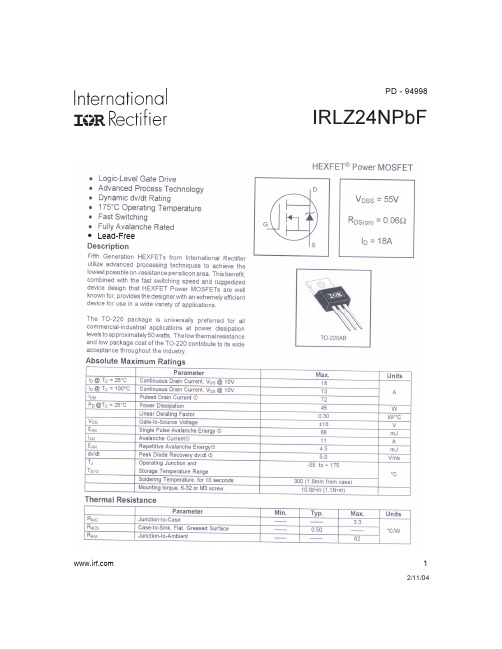

IRLZ24NPBF中文资料

PD - 94998

IRLZ24NPbF

•

Lead-Free

1

2/11/04

元器件交易网

IRLZ24NPbF

2

元器件交易网

IRLZ24NPbF

Dimensions are shown in millimeters (inches)

-B4.69 (.185) 4.20 (.165) 1.32 (.052) 1.22 (.048)

பைடு நூலகம்

4 15.24 (.600) 14.84 (.584)

1.15 (.045) MIN 1 2 3

LEAD ASSIGNMENTS IGBTs, CoPACK 1 - GATE 21- GATE DRAIN 1- GATE 32- DRAINSOURCE 2- COLLECTOR 3- SOURCE 3- EMITTER 4 - DRAIN

3 OUTLINE CONFORMS TO JEDEC OUTLINE TO-220AB. 4 HEATSINK & LEAD MEASUREMENTS DO NOT INCLUDE BURRS.

TO-220AB Part Marking Information

E XAMPL E : T HIS IS AN IR F 1010 LOT CODE 1789 AS S E MB L E D ON WW 19, 1997 IN T H E AS S E MB L Y LINE "C" INT E R NAT IONAL R E CT IF IE R L OGO AS S E MB L Y L OT CODE PAR T NU MB E R

Note: "P" in assembly line position indicates "Lead-Free"

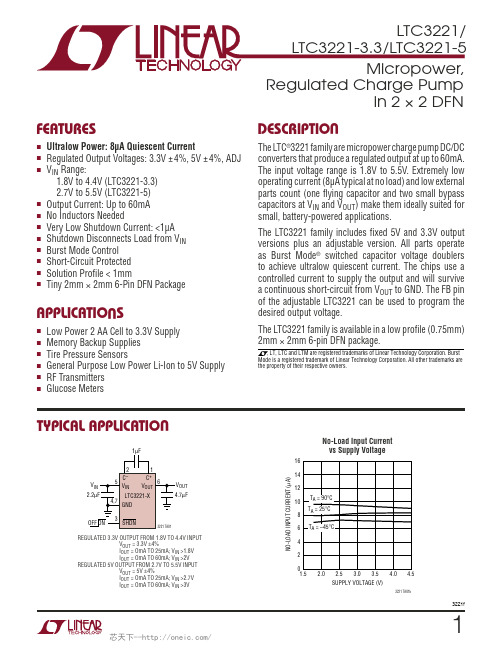

LTC3221EDC 规格书,Datasheet 资料

芯天下--/芯天下--/芯天下--/V IN = 2VI LOAD = 60mAC OUT = 4.7µF, 6.3V, SIZE 06033221 G141µs/DIVV OUT 20mV/DIV (AC-COUPLED)60mA I OUT0mA芯天下--/V IN = 3VI LOAD = 60mAC OUT = 4.7µF, 6.3V, SIZE 06033221 G231µs/DIVV OUT 50mV/DIV (AC-COUPLED)60mA I OUT0mA芯天下--/芯天下--/芯天下--/芯天下--/芯天下--/芯天下--/LTC3221/Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However,no responsibility is assumed for its use. Linear Technology Corporation makes no representation thatthe interconnection of its circuits as described herein will not infringe on existing patent rights.芯天下--/LTC3221/123221fLinear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2006LT 1006 • PRINTED IN USAPART NUMBER DESCRIPTIONCOMMENTSLTC126212V, 30mA Flash Memory Program Supply Regulated 12V ±5% Output, I Q = 500µA LTC1514/LTC1515Buck/Boost Charge Pumps with I Q = 60µA 50mA Output at 3.3V or 5V; 2V to 10V Input LTC1516Micropower 5V Charge PumpI Q = 12µA, Up to 50mA Output, V IN = 2V to 5V LTC1517-5/LTC1517-3.3Micropower 5V/3.3V Doubler Charge Pumps I Q = 6µA, Up to 20mA Output LTC1522Micropower 5V Doubler Charge Pump I Q = 6µA, Up to 20mA OutputLTC1555/LTC1556SIM Card InterfaceStep-Up/Step-Down Charge Pump, V IN = 2.7V to 10V LTC1682Low Noise Doubler Charge PumpOutput Noise = 60µV RMS , 2.5V to 5.5V Output LTC1751-3.3/LTC1751-5Micropower 5V/3.3V Doubler Charge Pumps I Q = 20µA, Up to 100mA Output, SOT-23 Package LTC1754-3.3/LTC1754-5Micropower 5V/3.3V Doubler Charge Pumps I Q = 13µA, Up to 50mA Output, SOT-23 Package LTC1755Smart Card InterfaceBuck/Boost Charge Pump, I Q = 60µA, V IN = 2.7V to 6V LTC3200Constant Frequency Doubler Charge Pump Low Noise, 5V Output or AdjustableLTC3203/LTC3203B/LTC3203B-1/LTC3203-1500mA Low Noise High Effi ciency Dual Mode Step Up Charge PumpsV IN : 2.7V to 5.5V, 3mm × 3mm DFN-10 Package LTC3204/LTC3204B-3.3/LTC3204-5Low Noise Regulated Charge Pumps Up to 150mA (LTC3204-5), Up to 50mA (LTC3204-3.3)LTC3240-3.3/LTC3240-2.5Step-Up/Step-Down Regulated Charge PumpsUp to 150mA OutputRELATED PARTS芯天下--/。

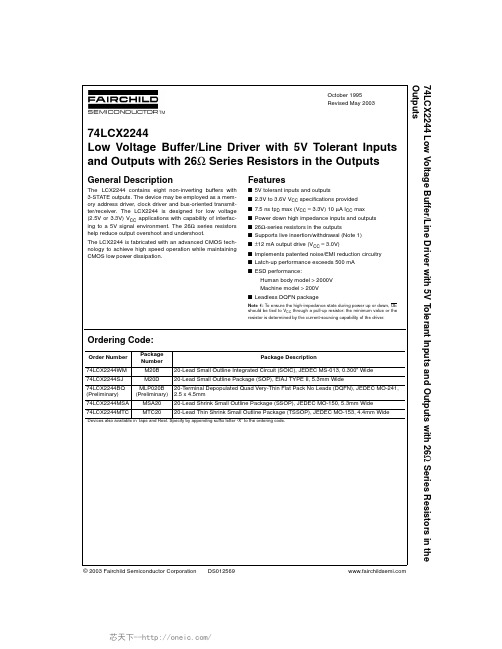

74LCX2244SJ,74LCX2244SJX,74LCX2244WM,74LCX2244WMX,74LCX2244MSA,74LCX2244MSAX, 规格书,Datasheet 资料

© 2003 Fairchild Semiconductor Corporation DS012569October 1995Revised May 200374LCX2244 Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Outputs with 26Ω Series Resistors in the Outputs74LCX2244Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Outputs with 26Ω Series Resistors in the OutputsGeneral DescriptionThe LCX2244 contains eight non-inverting buffers with 3-STATE outputs. The device may be employed as a mem-ory address driver, clock driver and bus-oriented transmit-ter/receiver. The LCX2244 is designed for low voltage (2.5V or 3.3V) V CC applications with capability of interfac-ing to a 5V signal environment. The 26Ω series resistors help reduce output overshoot and undershoot.The LCX2244 is fabricated with an advanced CMOS tech-nology to achieve high speed operation while maintaining CMOS low power dissipation.Featuress 5V tolerant inputs and outputss 2.3V to 3.6V V CC specifications provided s 7.5 ns t PD max (V CC = 3.3V) 10 µA I CC max s Power down high impedance inputs and outputs s 26Ω-series resistors in the outputs s Supports live insertion/withdrawal (Note 1)s ±12 mA output drive (V CC = 3.0V)s Implements patented noise/EMI reduction circuitry s Latch-up performance exceeds 500 mA s ESD performance:Human body model > 2000V Machine model > 200V s Leadless DQFN packageNote 1: To ensure the high-impedance state during power up or down, OE should be tied to V CC through a pull-up resistor: the minimum value or the resistor is determined by the current-sourcing capability of the driver.Ordering Code:Devices also available in T ape and Reel. Specify by appending suffix letter “X” to the ordering code.Order Number Package Number Package Description74LCX2244WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74LCX2244SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74LCX2244BQ (Preliminary)MLP020B (Preliminary)20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mm74LCX2244MSA MSA2020-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide 74LCX2244MTCMTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 274L C X 2244Logic SymbolIEEE/IECConnection DiagramsPin Assignments forSOIC, SOP, SSOP, and TSSOPPad Assignment for DQFN(Top Through View)Pin DescriptionsTruth TablesH = HIGH Voltage Level X = ImmaterialL = LOW Voltage LevelZ = High ImpedancePin Names DescriptionOE 1, OE 23-STATE Output Enable Inputs I 0–I 7Inputs O 0–O 7OutputsInputs Outputs OE 1I n (Pins 12, 14, 16, 18)L LL LH H HXZInputs Outputs OE 2I n (Pins 3, 5, 7, 9)L H L LHHH XZ74LCX2244Absolute Maximum Ratings (Note 2)Recommended Operating Conditions (Note 4)Note 2: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The “Recom-mended Operating Conditions ” table will define the conditions for actual device operation.Note 3: I O Absolute Maximum Rating must be observed.Note 4: Unused inputs must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsSymbol ParameterValueConditionsUnits V CC Supply Voltage −0.5 to +7.0V V I DC Input Voltage −0.5 to +7.0VV O DC Output Voltage −0.5 to +7.0Output in 3-STATEV −0.5 to V CC + 0.5Output in HIGH or LOW State (Note 3)I IK DC Input Diode Current −50V I < GND mA I OK DC Output Diode Current −50V O < GND mA +50V O > V CCI O DC Output Source/Sink Current ±50mA I CC DC Supply Current per Supply Pin ±100mA I GND DC Ground Current per Ground Pin ±100mAT STGStorage Temperature−65 to +150°CSymbol ParameterMin Max Units V CC Supply Voltage Operating 2.0 3.6V Data Retention1.5 3.6V I Input Voltage 0.0 5.5V V O Output Voltage HIGH or LOW State0.0V CC V3-STATE0.05.5I OH /I OLOutput CurrentV CC = 3.0V − 3.6V ±12.0mAV CC = 2.7V − 3.0V ±8.0V CC = 2.3V − 2.7V±4.0T AFree-Air Operating Temperature−40.085.0°C ∆t/∆VInput Edge Rate, V IN = 0.8V − 2.0V, V CC = 3.0V0.010.0ns/VSymbol ParameterConditionsV CC T A = −40°C to +85°C Units (V)Min MaxV IH HIGH Level Input Voltage 2.3 − 2.7 1.7V 2.7 − 3.6 2.0V IL LOW Level Input Voltage 2.3 − 2.70.7V2.7 −3.60.8V OHHIGH Level Output VoltageI OH = −100 µA 2.3 − 3.6V CC − 0.2VI OH = −4 mA 2.3 1.8I OH = −4 mA 2.7 2.2I OH = −6 mA 3.0 2.4I OH = − 8mA 2.7 2.0I OH = −12 mA3.0 2.0V OLLOW Level Output VoltageI OL = 100 µA 2.3 − 3.60.2V I OL = 4 mA 2.30.6I OL = 4 mA 2.70.4I OL = 6 mA 3.00.55I OL = 8 mA 2.70.6I OL = 12 mA3.00.8I I Input Leakage Current 0 ≤ V I ≤ 5.5V 2.3 − 3.6±5.0µA I OZ3-STATE Output Leakage0 ≤ V O ≤ 5.5V 2.3 − 3.6±5.0µA V I = V IH or V IL 474L C X 2244DC Electrical Characteristics (Continued)Note 5: Outputs disabled or 3-STATE only.AC Electrical CharacteristicsNote 6: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ).Dynamic Switching CharacteristicsCapacitanceSymbol ParameterConditionsV CC T A = −40°C to +85°C Units (V)MinMax I OFF Power-Off Leakage Current V I or V O = 5.5V 0.010.0µA I CC Quiescent Supply Current V I = V CC or GND2.3 −3.610.0µA 3.6V ≤ V I , V O ≤ 5.5V (Note 5) 2.3 − 3.6±10.0∆I CCIncrease in I CC per InputV IH = V CC − 0.6V2.3 −3.6500µASymbolParameterT A = −40°C to +85°C, R L = 500ΩUnitsV CC = 3.3V ± 0.3VV CC = 2.7V V CC = 2.5 ± 0.2V C L = 50pF C L = 50pF C L = 30pF MinMax Min Max Min Max t PHL Propagation Delay 1.57.5 1.58.5 1.59.0ns t PLH Data to Output 1.57.5 1.58.5 1.59.0t PZL Output Enable Time1.59.0 1.510.0 1.510.5ns t PZH 1.59.0 1.510.0 1.510.5t PLZ Output Disable Time 1.57.0 1.58.0 1.58.4ns t PHZ 1.57.0 1.58.01.58.4t OSHL Output to Output Skew (Note 6) 1.0ns t OSLH1.0Symbol ParameterConditionsV CC T A = 25°C Units (V)Typical V OLP Quiet Output Dynamic Peak V OL C L = 50 pF, V IH = 3.3V, V IL = 0V 3.30.35V C L = 30 pF, V IH = 2.5V, V IL = 0V 2.50.25V OLVQuiet Output Dynamic Valley V OLC L = 50 pF, V IH = 3.3V, V IL = 0V 3.3−0.35VC L = 30 pF, V IH = 2.5V, V IL = 0V2.5−0.25Symbol ParameterConditionsTypical Units C IN Input Capacitance V CC = Open, V I = 0V or V CC 7.0pF C OUT Output CapacitanceV CC = 3.3V, V I = 0V or V CC8.0pF C PDPower Dissipation CapacitanceV CC = 3.3V, V I = 0V or V CC , f = 10 MHz25.0pF74LCX2244AC LOADING and WAVEFORMS Generic for LCX FamilyFIGURE 1. AC Test Circuit (C L includes probe and jig capacitance)Waveform for Inverting and Non-Inverting FunctionsPropagation Delay. Pulse Width and t rec Waveforms3-STATE Output Low Enable andDisable Times for Logic3-STATE Output High Enable andDisable Times for LogicSetup Time, Hold Time and Recovery Time for Logict rise and t fallFIGURE 2. Waveforms(Input Characteristics; f =1MHz, t r = t f = 3ns)Test Switch t PLH , t PHL Opent PZL , t PLZ 6V at V CC = 3.3 ± 0.3V V CC x 2 at V CC = 2.5 ± 0.2Vt PZH ,t PHZGNDSymbol V CC3.3V ± 0.3V2.7V 2.5V ± 0.2V V mi 1.5V 1.5V V CC /2V mo 1.5V 1.5V V CC /2V x V OL + 0.3V V OL + 0.3V V OL + 0.15V V yV OH − 0.3VV OH − 0.3VV OH − 0.15V 674L C X 2244Schematic DiagramGeneric for LCX Family 74LCX2244Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M20B 874L C X 2244Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M20D74LCX2244 Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mmPackage Number MLP020B(Preliminary) 1074L C X 2244Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm WidePackage Number MSA2074LCX2244 Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Outputs with 26Ω Series Resistors in the OutputsPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC20Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to theuser. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or 芯天下--/。

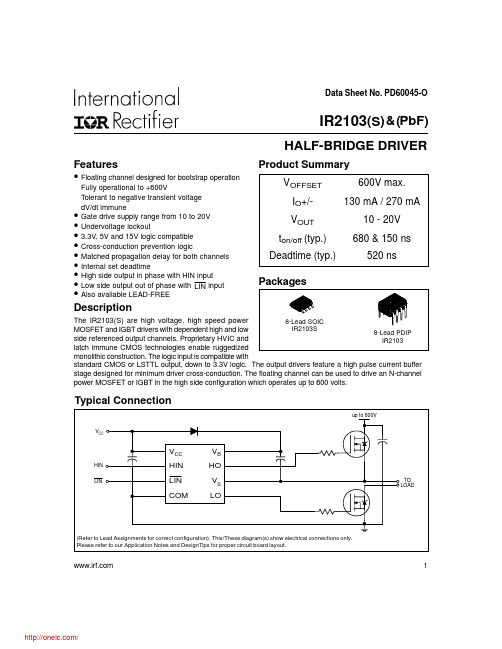

IR2103SPBF;IR2103PBF;IR2103STRPBF;IR2103;IR2103S;中文规格书,Datasheet资料

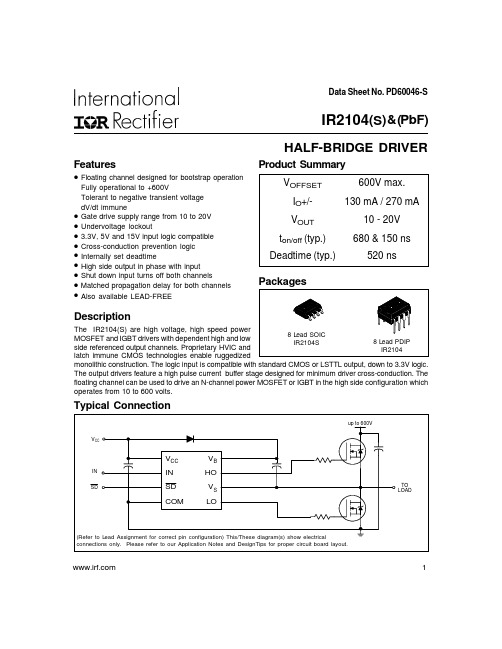

Data Sheet No. PD60045-OTypical ConnectionProduct SummaryHALF-BRIDGE DRIVERFeatures•Fully operational to +600VdV/dt immune••Undervoltage lockout••Cross-conduction prevention logic••Internal set deadtime•••Also available LEAD-FREEDescriptionpower MOSFET or IGBT in the high side configuration which operates up to 600 volts. 1IR2103(S ) & (PbF)IR2103(S) & (PbF)Absolute Maximum RatingsAbsolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage param-eters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.Note 1: Logic operational for V S of -5 to +600V. Logic state held for V S of -5V to -V BS . (Please refer to the Design Tip DT97-3 for more details).IR2103(S) & (PbF) 3Static Electrical CharacteristicsV BIAS (V CC , V BS ) = 15V and T A = 25°C unless otherwise specified. The V IN , V TH and I IN parameters are referenced to COM. The V O and I O parameters are referenced to COM and are applicable to the respective output leads: HO or LO.Dynamic Electrical CharacteristicsV BIAS (V CC , V BS ) = 15V, C L = 1000 pF and T A = 25°C unless otherwise specified.IR2103(S) & (PbF)4Functional Block DiagramLead DefinitionsSymbol DescriptionHIN Logic input for high side gate driver output (HO), in phase Logic input for low side gate driver output (LO), out of phase VB High side floating supply HO High side gate drive output V S High side floating supply return V CC Low side and logic fixed supply LO Low side gate drive output COMLow side returnLINLead Assignments8 Lead PDIP 8 Lead SOICIR2103IR2103S12348765V CC HIN LIN COMV B HO V S LO12348765V CC HIN LIN COMV B HO V S LOIR2103(S) & (PbF) 5Figure 1. Input/Output Timing DiagramLINHOLOHINFigure 4. Deadtime Waveform DefinitionsFigure 2. Switching Time Waveform DefinitionsLOIR2103(S) & (PbF)6IR2103(S) & (PbF) 7IR2103(S) & (PbF)8IR2103(S) & (PbF)9IR2103(S) & (PbF)10vs Temperaturevs Voltage分销商库存信息:IRIR2103SPBF IR2103PBF IR2103STRPBF IR2103IR2103S IR2103STR。

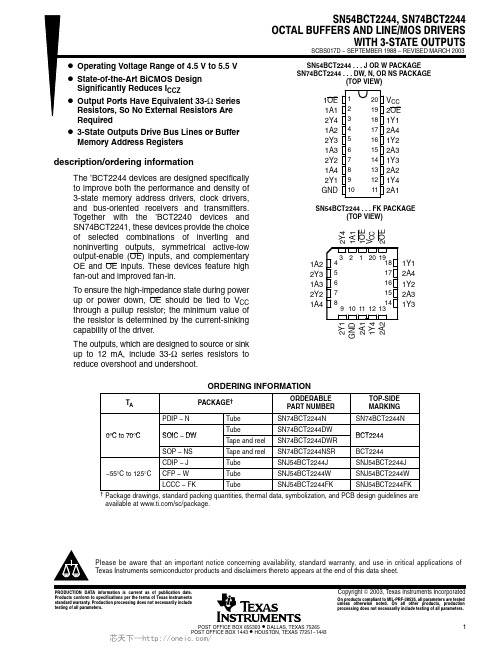

SN74BCT2244NSR,SN74BCT2244NSRE4,SN74BCT2244NSRG4,SN74BCT2244N,SN74BCT2244NE4, 规格书,Datasheet 资料

and bus-oriented receivers and transmitters.Together with the ’BCT2240 devices and SN74BCT2241, these devices provide the choice of selected combinations of inverting and noninverting outputs, symmetrical active-low output-enable (OE) inputs, and complementary OE and OE inputs. These devices feature high fan-out and improved fan-in.To ensure the high-impedance state during power up or power down, OE should be tied to V CC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.The outputs, which are designed to source or sink up to 12 mA, include 33-Ω series resistors to reduce overshoot and undershoot.ORDERING INFORMATIONT APACKAGE †ORDERABLE PART NUMBER TOP-SIDE MARKING PDIP − NTube SN74BCT2244N SN74BCT2244N C to 70SOIC DW Tube SN74BCT2244DW 0°C to 70°CSOIC − DW Tape and reel SN74BCT2244DWR BCT2244SOP − NS Tape and reel SN74BCT2244NSR BCT2244CDIP − JTube SNJ54BCT2244J SNJ54BCT2244J −55°C to 125°CCFP − W Tube SNJ54BCT2244W SNJ54BCT2244W LCCC − FKTubeSNJ54BCT2244FKSNJ54BCT2244FK†Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at /sc/package.32120199101112134567818171615141Y12A41Y22A31Y31A22Y31A32Y21A4SN54BCT2244...FK PACKAGE(TOP VIEW)2Y 41A 11O E 1Y 42A 2O E2Y 1G N D 2A 1V C CCopyright © 2003, Texas Instruments IncorporatedPlease be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of pub lication date.SN54BCT2244, SN74BCT2244OCTAL BUFFERS AND LINE/MOS DRIVERS WITH 3-STATE OUTPUTSSCBS017D − SEPTEMBER 1988 − REVISED MARCH 2003FUNCTION TABLE (each buffer)INPUTS OUTPUTOE A YL H H L L L HXZlogic diagram (positive logic)1A11A21A31A41Y12A12A22A32A42Y11Y21Y31Y42Y22Y32Y41OE2OESN54BCT2244, SN74BCT2244OCTAL BUFFERS AND LINE/MOS DRIVERSWITH 3-STATE OUTPUTSSCBS017D − SEPTEMBER 1988 − REVISED MARCH 2003schematic of Y outputsOutputV CCGNDabsolute maximum ratings over operating free-air temperature range (unless otherwise noted)†Supply voltage range, V CC −0.5 V to 7 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input voltage range, V I (see Note 1) −0.5 V to 7 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Voltage range applied to any output in the disabled or power-off state, V O −0.5 V to 5.5 V . . . . . . . . . . . . . . . . Voltage range applied to any output in the high state, V O −0.5 V to V CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Input clamp current, I IK −30 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Current into any output in the low state, I O 24 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Package thermal impedance, θJA (see Note 2):DW package 58°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . N package 69°C/W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . NS package 60°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Storage temperature range, T stg −65°C to 150°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . †Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, andfunctional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.NOTES: 1.The input and output voltage ratings may be exceeded if the input and output current ratings are observed.2.The package thermal impedance is calculated in accordance with JESD 51-7.recommended operating conditions(see Note 3)SN54BCT2244SN74BCT2244MINNOMMAX MIN NOMMAX UNIT V CC Supply voltage 4.555.54.555.5V V IH High-level input voltage 22V V IL Low-level input voltage 0.80.8V I IK Input clamp current −18−18mA I OH High-level output current −12−12mA I OL Low-level output current 1212mA T AOperating free-air temperature−5512570°CNOTE 3:All unused inputs of the device must be held at V CC or GND to ensure proper device operation. Refer to the TI application report,Implications of Slow or Floating CMOS Inputs , literature number SCBA004.SN54BCT2244, SN74BCT2244OCTAL BUFFERS AND LINE/MOS DRIVERS WITH 3-STATE OUTPUTSSCBS017D − SEPTEMBER 1988 − REVISED MARCH 2003electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)TEST CONDITIONS SN54BCT2244SN74BCT2244PARAMETERTEST CONDITIONSMIN TYP †MAX MIN TYP †MAX UNIT V IK V CC = 4.5 V,I I = −18 mA −1.2−1.2V 45V I OH = −1 mA 2.4 2.4V OH V CC = 4.5 V I OH = −12 mA 22V 45V I OL = 1 mA 0.150.50.150.5V OL V CC = 4.5 V I OL = 12 mA 0.350.80.350.8V I I V CC = 5.5 V,V I = 7 V 0.10.1mA I IH V CC = 5.5 V,V I = 2.7 V 2020μA I IL V CC = 5.5 V,V I = 0.5 V −1−1mA I OZH V CC = 5.5 V,V O = 2.7 V 5050μA I OZL V CC = 5.5 V,V O = 0.5 V −50−50μA I OS ‡V CC = 5.5 V,V O = 0−100−225−100−225mA I CCH V CC = 5.5 V,Outputs open 23372337mA I CCL V CC = 5.5 V,Outputs open 53775377mA I CCZ V CC = 5.5 V,Outputs open 6.5106.510mA C i V CC = 5 V,V I = 2.5 V or 0.5 V 66pF C oV CC = 5 V,V O = 2.5 V or 0.5 V1111pF†All typical values are at V CC = 5 V, T A = 25°C.‡Not more than one output should be tested at a time, and the duration of the test should not exceed one second.switching characteristics over recommended ranges of supply voltage and operating free-air temperature, C L = 50 pF (unless otherwise noted) (see Figure 1)FROM TO V CC = 5 V,T A = 25°C SN54BCT2244SN74BCT2244PARAMETER(INPUT)(OUTPUT)MIN TYP MAX MIN MAX MIN MAX UNITt PLH 0.53 4.40.5 5.20.5 4.9t PHL A Y 1.6 4.6 6.3 1.67.1 1.6 6.7ns t PZH 2.4 6.17.7 2.49.1 2.48.7t PZL OE Y 3.97.69.4 3.910.8 3.910.4ns t PHZ 1.7 5.2 6.9 1.78.1 1.77.8t PLZOEY2.86.58.32.810.92.89.8ns PARAMETER MEASUREMENT INFORMATIONSN54BCT2244, SN74BCT2244OCTAL BUFFERS AND LINE/MOS DRIVERSWITH 3-STATE OUTPUTSSCBS017D − SEPTEMBER 1988 − REVISED MARCH 2003NOTES: A.C L includes probe and jig capacitance.B.All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, t r = t f ≤ 2.5 ns, duty cycle = 50%.C.Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.D.The outputs are measured one at a time with one transition per measurement.E.When measuring propagation delay times of 3-state outputs, switch S1 is open.F.All parameters and waveforms are not applicable to all devices.From Output Under TestTest PointLOAD CIRCUIT FOR TOTEM-POLE OUTPUTSLOAD CIRCUIT FOR3-STATE AND OPEN-COLLECTOR OUTPUTS7 V (t PZL , t PLZ , O.C.)From Output Under TestTest PointL = R1 = R21.5 V1.5 V1.5 V3 V3 V0 V0 Vt ht suVOLTAGE WAVEFORMS SETUP AND HOLD TIMESTiming Input (see Note B)Data Input(see Note B)3 V3 V0 V0 VHigh-LevelPulse(see Note B)Low-LevelPulseVOLTAGE WAVEFORMS PULSE DURATIONt PHLt PLHt PLHt PHLInput(see Note B)Out-of-PhaseOutput (see Note D)1.5 V1.5 V1.5 V1.5 V1.5 V1.5 V3 V0 V V OLV OHV OHV OLIn-Phase Output (see Note D)VOLTAGE WAVEFORMSPROPAGATION DELAY TIMES (see Note D)t PHZt PLZ0.3 V t PZLt PZH1.5 V1.5 V1.5 V 1.5 V3 V0 VOutput Control(low-level enable)Waveform 1(see Notes C and D)Waveform 2(see Notes C and D)0 VV OHV OL 3.5 V 0.3 VVOLTAGE WAVEFORMSENABLE AND DISABLE TIMES, 3-STATE OUTPUTSFigure 1. Load Circuit and Voltage WaveformsAddendum-Page 1PACKAGING INFORMATIONOrderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)5962-9074101M2A ACTIVE LCCC FK 201TBD Call TI Call TI 5962-9074101MRA ACTIVE CDIP J 201TBD Call TI Call TI 5962-9074101MSA ACTIVE CFP W 201TBDCall TICall TISN74BCT2244DW ACTIVE SOIC DW 2025Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244DWE4ACTIVE SOIC DW 2025Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244DWG4ACTIVE SOIC DW 2025Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244DWR ACTIVE SOIC DW 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244DWRE4ACTIVE SOIC DW 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244DWRG4ACTIVE SOIC DW 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244N ACTIVE PDIP N 2020Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type SN74BCT2244NE4ACTIVE PDIP N 2020Pb-Free (RoHS)CU NIPDAU N / A for Pkg Type SN74BCT2244NSR ACTIVE SO NS 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244NSRE4ACTIVE SO NS 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74BCT2244NSRG4ACTIVE SO NS 202000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54BCT2244FK ACTIVE LCCC FK 201TBD POST-PLATE N / A for Pkg TypeSNJ54BCT2244J ACTIVE CDIP J 201TBD A42N / A for Pkg Type SNJ54BCT2244WACTIVECFPW201TBDCall TIN / A for Pkg Type(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.芯天下--/(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN54BCT2244, SN74BCT2244 :•Catalog: SN74BCT2244•Military: SN54BCT2244NOTE: Qualified Version Definitions:•Catalog - TI's standard catalog product•Military - QML certified for Military and Defense ApplicationsAddendum-Page 2芯天下--/TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74BCT2244DWR SOIC DW 202000330.024.410.813.0 2.712.024.0Q1SN74BCT2244NSRSONS202000330.024.48.213.02.512.024.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74BCT2244DWR SOIC DW202000367.0367.045.0SN74BCT2244NSR SO NS202000367.0367.045.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

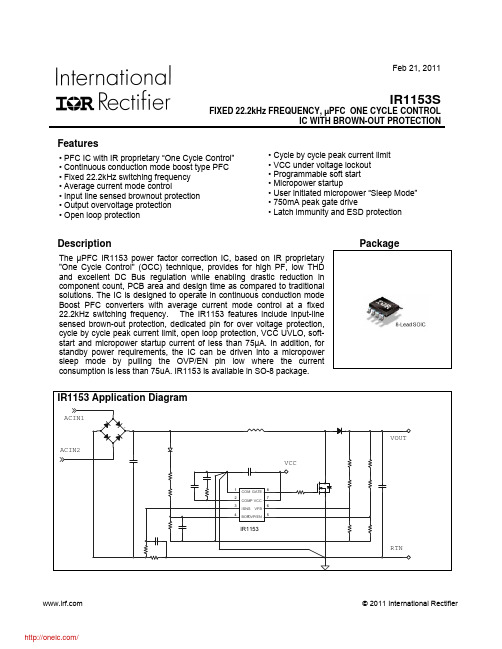

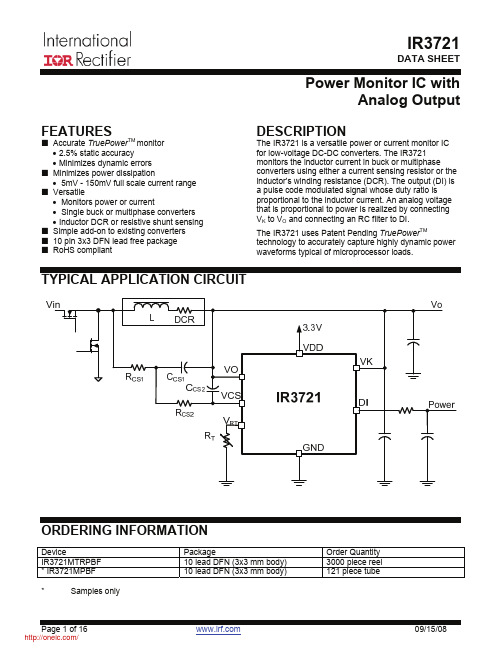

IR1153STRPBF;IR1153SPBF;中文规格书,Datasheet资料