FP812中文资料

EP1C12F144C7中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

EP1C6

5,980 20

92,160 2

185

EP1C12

12,060 52

239,616 2

249

EP1C20 20,060

64 294,912

2 301

1

芯片中文手册,看全文,戳

气旋 FPGA系列数据手册

初稿信息

Cyclone器件在四方扁平封装(QFP),并提供节省空间

FineLine BGA 包(见

Cyclone器件提供一个全局时钟网络和多达两个PLL.全局时钟网络由八 个全局时钟线驱动整个器件.全局时钟网络可以为设备内所有资源 ,如IOEs,LE和存储器块提供时钟.

全局时钟线也可用于控制信号.旋风PLL提供通用与时钟倍频和移相,以 及外部输出高速差分I / O支持时钟.

图1

示出旋风EP1C12装置图.

M4K RAM块与4K位内存加上平价(4,608位)真正双端口存储器 块.这些块宽高达200 MHz提供专用真正双端口,简单双端口或单端 口内存最高可达36位.这些块加在器件分成列在一定LAB之间. Cyclone器件提供嵌入式RAM 60至288千位之间.

每个Cyclone器件I / O引脚由I / O单元(IOE)位于输送 围绕装置外周端部LAB行和列. I / O 引脚支持各种单端和差分I / O标准,如 66 MHz32位PCI标准,并在到LVDS I / O标准 311 Mbps.每个IOE包含一个双向I / O缓冲区和三个寄存器 用于登记输入,输出和输出使能信号.两用 DQS,DQ和DM引脚以及延时链(用于相位对齐DDR 信号)提供与外部存储器设备,诸如接口支持 DDR SDRAM和高达133兆赫(266 Mbps)FCRAM器件.

配置设备配置Cyclone器件.

H3CR-F8-DC12中文资料

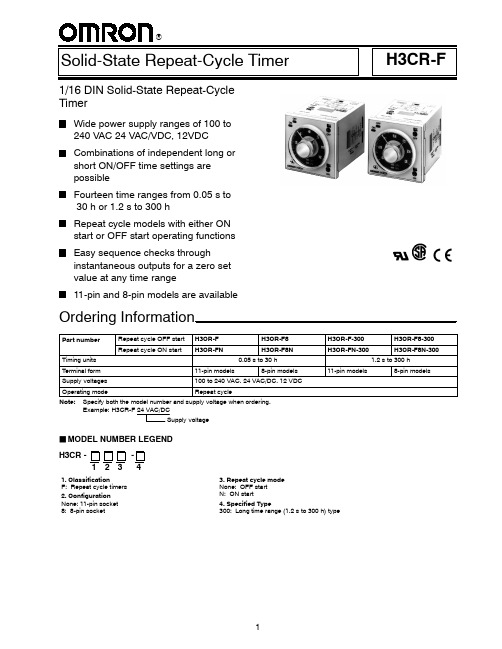

R1Solid-State Repeat-Cycle TimerH3CR-F1/16DIN Solid-State Repeat-CycleTimerWide power supply ranges of 100to 240VAC 24VAC/VDC,12VDC Combinations of independent long or short ON/OFF time settings arepossibleFourteen time ranges from 0.05s to 30h or 1.2s to 300hRepeat cycle models with either ON start or OFF start operatingfunctions Easy sequence checks throughinstantaneous outputs for a zero set value at any timerange11-pin and 8-pin models areavailableOrdering InformationPart number Repeat cycle OFF start H3CR-F H3CR-F8H3CR-F-300H3CR-F8-300Repeat cycle ON startH3CR-FNH3CR-F8NH3CR-FN-300H3CR-F8N-300Timing units 0.05s to 30h1.2s to 300hT erminal form 11-pin models 8-pin models11-pin models8-pin modelsSupply voltages 100to 240VAC,24VAC/DC,12VDCOperating mode Repeat cycleNote:Specify both the model number and supply voltage when ordering.Example:H3CR-F 24VAC/DCSupply voltageJ MODEL NUMBER LEGEND H3CR --12341.ClassificationF:Repeat cycle timers 2.Configuration None:11-pin socket 8:8-pin socket3.Repeat cycle mode None:OFF start N:ON start4.Specified Type300:Long time range (1.2s to 300h)type元器件交易网H3CR-FH3CR-F2J ACCESSORIESDescription Part number Sockets11-pin Bottom surface or track mounting,top screw terminalsP2CF-11pBottom surface or track mounting,top screw terminals,finger-safe terminal conforms toVDE0106/P100P2CF-11-E Back mounting,for use with Y92F-30mounting adapter,bottom screw terminalsP3GA-118-pin Bottom surface or track mounting,top screw terminalsP2CF-08pBottom surface or track mounting,top screw terminals,finger-safe terminal conforms toVDE0106/P100P2CF-08-E Back mounting,for use with Y92F-30mounting adapter,bottom screw terminals P3G-08T erminal cover for P3G sockets,conforms toVDE0106/P100Y92A-486Panel mounting adapter Fits behind panel,ideal for side-by-side e P3G_-_sockets Y92F-30g pPanel-mounting adapter (88mm x 58mm x 66mm)Y92F-73Panel-mounting adapter (58mm x 50mm x 66mm)Y92F-74Protective cover Hard plastic cover protects against dust,dirt and water;not for use with panel covers Y92A-48B NEMA 4cover Waterproof front coverY92A-48N Colored panel coversLight gray (Munsell No.5Y7/1)to match case Y92P-48GL p Medium gray (Munsell No.5Y5/1)Y92P-48GM Black (Munsell No.N1.5)Y92P-48GB Mounting trackDIN rail,50cm (1.64ft)length;7.3mm thick PFP-50N g DIN rail,1m (3.28ft)length;7.3mm thick PFP-100N DIN rail,1m (3.28ft)length;16mm thickPFP-100N2End plate PFP-M SpacerPFP-SJ RANGE SELECTIONON indicator (orange)Lit when the output is OFF indicator (green)Lit when the output is Scale range display windowsTime range selector from 1.2,3,12,and 30)For both ON-time and unit display windowunit selector (select one from sec.s,min.,and hrs,or from 10s,10min,hrs,10h)setting knob (with orange pointer)ON-time settingsetting knob (with green pointer)OFF-time settingunit display window unit selector (select one from sec.10s,min.,and hrs,or from 10s,10min,hrs,and 10h)0.05s to 30h ModelsTime Time units range s (sec)x 10s (10s)min h (hrs)1.20.05to 1.2 1.2to 120.12to 1.230.3to 33to 300.3to 312 1.2to 1212to 120 1.2to 12303to 3030to 3003to 30Note:Instantaneous output is available at any time range.T o obtain instantaneous output,set to below 0. 1.2s to 300h ModelsTime Time units range x 10s (10s)x 10min (10min)h (hrs)x 10h (10h)1.2 1.2to 12 1.2to 120.12to 1.2 1.2to 1233to 303to 300.3to 33to 301212to 12012to 120 1.2to 1212to 1203030to 30030to 3003to 3030to 300Note:Instantaneous output is available at any time range.T o obtain instantaneous output,set to below 0.元器件交易网H3CR-FH3CR-F3SpecificationsPart number H3CR-F/-F-300H3CR-F8/-F8-300H3CR-FN/-FN-300H3CR-F8N/-F8N-300Operating mode OFF startON startSupply lAC 100to 240VAC (50/60Hz)pp y voltage AC/DC 24VAC/DC (50/60Hz)(see note)DC 12VDCOperating voltage range 85%to 110%of rated supply voltage,90%to 110%with 12-VDC models PoweriAC 100to 240VAC:10VA (100VAC applied)consumption AC/DC 24VAC/DC:2VA (24VAC applied)/1W (24VDC applied)DC12VDC:1WStart,Reset,Gate inputsON-impedance:1k Ωmax.ON residual voltage:1V max OFF impedance:500k Ωmin.Control Type DPDT relayoutputsMax.load 5A at 250VAC,p.f.=1Min.load10mA at 5VDCRepeat accuracy ±0.3%full scale max.(±0.3%full scale max.±10ms in ranges of 1.2and 3s)Setting error ±5%full scale max ±0.05s max.Resetting system Time-limit operation/time-limit reset or self-reset Resetting time Minimum power-opening time:0.1secIndicators Output ON indicator (orange LED),output OFF indicator (green LED)Materials Plastic case (light gray Munsell 5Y7/1)Mounting Panel,DIN track,or surface depending on socket selected Connections 11-pin round socket 8-pin round socket11-pin round socket8-pin round socketWeight Approx.100g (4.23oz.)Approvals UL,CSA,CEAmbient Operating --10°to 55°C (14°to 131°F)with no icing temperature Storage--25°to 65°C (--13°to 149°F)with no icing Humidity 35%to 85%VibrationMechanical durability 10to 55Hz with 0.75-mm single amplitude each in three directions Malfunction durability10to 55Hz with 0.5-mm single amplitude each in three directions ShockMechanical durability 980m/s 2(100G)each in three directions Malfunction durability98m/s 2(10G)each in three directionsVariation due to voltage change ±0.5%full scale max.(±0.5%full scale max.±10ms in ranges of 1.2and 3s)Variation due to temperature change ±2%full scale max.(±2%full scale max.±l0ms in ranges of 1.2and 3s)Service lifeMechanical 20million operations min.(under no load at 1,800operations/h)Electrical100,000operations min.(5A at 250VAC,resistive load at 1,800operations/h)Insulation resistance100M Ωmin.(at 500VDC)Note:A power supply with a ripple of 20%max.(single-phase power supply with full-wave rectification)can be used with eachDC model.元器件交易网H3CR-FH3CR-F4Engineering DataNote:A maximum current of 0.15A can be switched at 125VDC (cos f =1)anda maximum current of 0.1A can be switched if L/R is 7ms.In both cases,a life of 100,000operations can be expected.The minimum applicable load is 10mA at 5VDC (failure level:P).Load current (A)30VDC L/R =7ms250VAC/30VDC (cos f =1)250VAC (cos f =0.4)10,0005,0001,000500100S w i t c h i n g o p e r a t i o n s (x 10)3OperationJ BLOCKDIAGRAMS元器件交易网H3CR-FH3CR-F5Timing ChartsH3CR-F H3CR-FN H3CR-F-300H3CR-FN-300H3CR-F8H3CR-F8N H3CR-F8-300H3CR-F8N-300Do not use them as relay terminals.Note:Part numbers with an “N”included are Repeat cycle ON start timers.All others are Repeat cycle OFF start timers.元器件交易网H3CR-FH3CR-F6DimensionsJ TIMERSUnit:mm (inch)H3CR-F H3CR-FN H3CR-F-300H3CR-FN-300H3CR-F8H3CR-F8N H3CR-F8-300H3CR-F8N-3000.717.465.714dia.0.717.465.714dia.66.6(2.62)37dia (1.46)52.366.6(2.62)37dia (1.46)52.3J TRACK MOUNTING 100.7*98.42.3*111.7*109.42.3*11-Pin Models8-Pin ModelsP2CF-11/P2CF-11-EP2CF-08/P2CF-08-EH3CR-F H3CR-FN H3CR-F-300H3CR-FN-300H3CR-F8H3CR-F8N H3CR-F8-300H3CR-F8N-300*These dimensions vary with the kind of DIN track (reference value).J PANEL MOUNTING Y92F-30P3GA-11Y92F-30P3G-0875H3CR-FN-30011-Pin Models8-Pin ModelsH3CR-F8H3CR-F8N H3CR-F8N-300元器件交易网H3CR-FH3CR-F7J PANEL-MOUNTING ADAPTERSUnit:mm (inch)Y92F-30Panel CutoutNote:Adapter installs behind the panel.It is ideal for side by sidee P3G-11or P3G-08sockets.Panel52(2.05)58(2.28)42(1.65)Note:Recommended panel thickness is 1to 3.2mm.48(1.89)Y92F-73Y92F-74PanelPanel43+0.20.2Panel CutoutNote:Note:The mounting panel thickness should be 1to 3.2mm.56(2.2)J SOCKETSTrack-Mounting/Front-Connecting Socket Terminal Arrangement/Internal Connections (Top View)Surface Mounting Holesor two,M4EightM3.5x 7.5semsTwo 4.5dia.holes70max.50max.20.3max.7.834.535.4(1.39)4P2CF-08元器件交易网H3CR-FH3CR-F8P2CF-08-E (Finger-Safe TerminalType)Conforming to VDE0106/P1004.535.421.5max.57.870max.50max.400.2Two,4.5dia.holes31.320.319EightM3.5X 7.5semsP2CF-11holesTwo 4.5dia.holesElevenM3.5x 7.5sems70max.50max.31.2max.7.83 4.5435.4(1.39)P2CF-08-E (Finger-Safe Terminal Type)Conforming to VDE0106/P1004.535.421.5max.57.870max.50max.400.2Two,4.5dia.holesEightM3.5X 7.5sems31.320.319Back-Mounting Socket P3GA-11Terminal Arrangement/Internal Connections (Bottom View)27dia.4.927dia.25.64.516.3(0.64)6.217P3G-08(0.67)45(1.77)45(1.77)45(1.77)45(1.77)元器件交易网H3CR-FH3CR-F9Finger-Safe Terminal Cover for P3G(A)Y92A-48G3427.616.547.448x 4847.7x 4.47Twelve,6.4dia.holesConforming to VDE0106/P100J PROTECTIVE COVER Y92A-48B50.5(1.99)50.5(1.99)16(0.63)overall depthThe hard plastic protective cover prevents accidental resetting.It also shields the front panel from dirt and water.The cover is intended for use in areas where unusual service conditions do not exist.The Y92A-48B cover cannot be used with the Y92P Panel Covers below.J MOUNTING TRACK AND ACCESSORIES PFP-100N/PFP-50NPFP-100N24.51525252525*10107.3+0.1535+0.327+0.1514.51525252525151010L35+0.327241629.211.51,000(500)(see note)Note:The values shown in parentheses are for the PFP-50N.15(5)(see note)PFP-M End PlatePFP-S Spacer5011.5M4x 8pan head screw106.21.8135.535.31.81.34.85161244.334.816.510元器件交易网H3CR-FH3CR-F10ConnectionsPart number Input terminal number Power supply terminal numbers Output terminal numbersCOMReset AC (common),DC −AC (hot),DC+COM NC NO H3CR-F8H3CR-F8N H3CR-F8-300H3CR-F8N-300——27184536H3CR-F H3CR-FN H3CR-F-300H3CR-FN-300——2101114839InstallationJ INPUT CONNECTIONSThe neutral or common of the power supply is connected to terminal 2.T erminal 7of H3CR-F 8-pin terminals andterminal 10of H3CR-F 11-pin terminals should be connected to the “hot”or positive of the power supply.J OUTPUT CONNECTIONSDesign your control circuit using the relay contacts to switch the load.Note:Never switch a load with the contact that is beingused as an input signal.The timer’s circuitry may be damaged.J SELECTING TIME RANGESA time range (0to 1.2,0to 3,0to 12,or 0to 30)is selected for ON-and OFF-time using the time range selector at the lower left corner of the front panel,and the selected time range appears within the plastic frame of the time setting knob (=scale range display windows).For ON-time,the desired time unit (sec,10s,min,and hrs,or 10s,10min,hrs,and 10h)is indicated in the ON-time unit display window at the lower right corner of the front panel and can be changed by turning the ON-time unit selector located below the ON-time unit display window.For OFF-time,the desired time unit (sec,10s,min,and hrs,or 10s,10min,hrs,and 10h)is indicated in the OFF-time unit display window at the upper right corner of the front panel and can be changed by turning the OFF-time unit selector located below the OFF-time unit display window.Time range selectorON time unit selectorOFF time unit selectorJ TRACK MOUNTING Using P2CF-j j SocketMountingThe P2CF-VV socket has two hooks that secure the time to the socket.Be sure to allow at least 20mm (0.79in)clearance above and below the socket to gain access to release the hooks for servicing and maintenance.Then clip rear of the socket to the track.Push the bottom onto the track until the latch hooks securely.RemovalPull the latch on the socket with a flat-blade screwdriver and remove the timer and socket as one unit.Hook20mm (0.79in)P2CF-11or P2CF-08socketUsing Y92F-73and Y92F-74AdaptersInstall the H3CR-H timer,face first,into the back side of the Y92F-73or Y92F-74adapter so the bezel fits snuggly.Be sure the retaining clips at the back of the adapter fit into the slots on either side of the press the top and bottom tabs of the adapter then push the adapter through the front side of the panel cutout.Be sure the tabs extend after the installation for a secure fit.T o remove the timer from the adapter,unclip the two retaining clips at the back of the adapter.T o remove the adapter and timer from the panel as a unit,compress the tabs behind the panel and push the unit out the front of the panel.InstallationPanelRetaining clips for timerMounting tabsRemovalMounting tabs元器件交易网H3CR-FH3CR-FPrecautionsT o avoid malfunction or damage,do not change the time unit or time range while the timer is in operation.Be sure to turn off the power supply to the timer before changing any of the selections.Operating EnvironmentDo not use the Timer in the following locations.•Locations with radical temperature changes.•Locations with high humidity that may result in condensation.•Locations with excessive vibration or shock.•Locations with corrosive gas or dust.•Locations where the Timer is exposed to sprayed water,oil,or chemicals.Organic solvents (such as paint thinner)as well as strong acid or alkali solutions will damage the outer casing of the Timer.If the Timer is used in an area with excessive electrical noise,be sure to separate the Timer,wires,and input device as far aspossible from the noise sources.Furthermore,it is recommended that the input signal wiring be shielded to prevent electrical interference.J PRECAUTIONS FOR EN (VDE)CONFORMANCEThe H3CR-A Series,installed as a built-in timer,conforms to EN61812-1(VDE0435/P2021)provided that the following conditions are satisfied.Make sure that no voltage is applied to any terminals before removing the Timer from the Socket.The output section of the H3CR-A is provided only with basic isolation.Provide supplementary basic isolation on the load side connected to the output so that reinforced isolation required by the EN (VDE)standards will be ensured.The H3CR-A Was Designed to Meet the Following Conditions•Overvoltage category III •Pollution degree 2•IsolationOperation parts:Reinforced isolation--With clearance of 5.5mm and creepage distance of 5.5mm at 230VACOutput:Basic isolation (See Note.)--With clearance of 3mm and creepage distance of 3mm at 230VACNote:The 11-pin model ensures basic isolation by itself and alsoensures basic isolation with the 11-pin model mounted to the OMRON P2CF-11or P3GA-11Socket.Connect the two output contacts different in polarity to the loads,so that they will be the same in potential.J VOLTAGE WITHSTAND TESTIf the Timer is mounted to a control board,remove the Timer from the control board or short-circuit the control board circuitry before carrying out a voltage withstand test between the electric circuitry and non-charged metal part of the Timer.This protects the internal circuitry of the Timer from damage.C a t . N o . G C T M C N 1 3/02 S p ec i f i c a t i ons s u bjec t t o c h ange w i t h out not i c e . P r i nt e d in U .S .A .OMRON ELECTRONICS LLCOne East Commerce Drive Schaumburg,IL 60173NOTE:DIMENSIONS SHOWN ARE IN MILLIMETERS.To convert millimeters to inches divide by 25.4.1-800-55-OMRONOMRON CANADA,INC.885Milner AvenueScarborough,Ontario M1B 5V8416-286-6465ROMRON ON--LINEGlobal --USA --/oei Canada --/oci元器件交易网。

FP75R12KE3中文资料

typ.

1,7 2 5,8 5,3 -

max.

2,2 6,5 5 400 V V V nF mA nA

f = 1MHz, Tvj = 25°C VCE = 25 V, VGE = 0 V VGE = 0V, Tvj = 25°C, VCE =

VCE = 0V, VGE =20V, Tvj =25°C I C = INenn, VCC = VGE = ±15V, Tvj = 25°C, RG = VGE = ±15V, Tvj = 125°C, RG = I C = INenn, VCC = VGE = ±15V, Tvj = 25°C, RG = VGE = ±15V, Tvj = 125°C, RG = I C = INenn, VCC = VGE = ±15V, Tvj = 25°C, VGE = ±15V, Tvj = 125°C, I C = INenn, VGE = ±15V, Tvj = 25°C, VGE = ±15V, Tvj = 125°C, I C = INenn, VGE = ±15V, Tvj = 125°C, RG = RG = VCC = RG = RG = VCC = RG = LS = I C = INenn, VCC = VGE = ±15V, Tvj = 125°C, RG = LS = RG = VCC =

V A A A A As 2 As

2

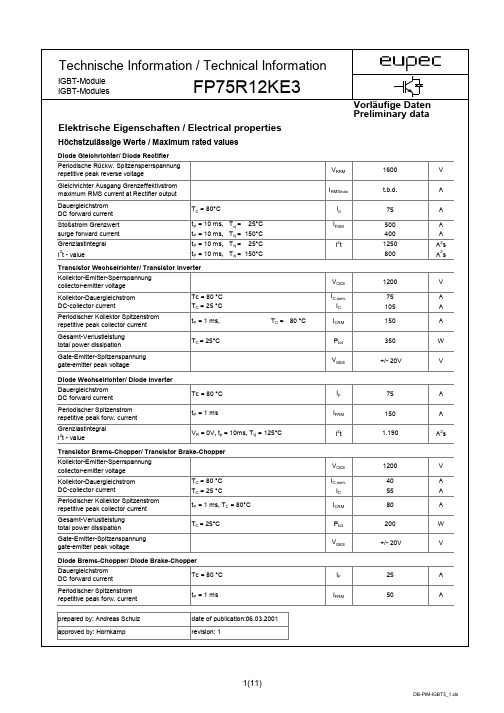

Transistor Wechselrichter/ Transistor Inverter Kollektor-Emitter-Sperrspannung collector-emitter voltage Kollektor-Dauergleichstrom DC-collector current Periodischer Kollektor Spitzenstrom repetitive peak collector current Gesamt-Verlustleistung total power dissipation Gate-Emitter-Spitzenspannung gate-emitter peak voltage Diode Wechselrichter/ Diode Inverter Dauergleichstrom DC forward current Periodischer Spitzenstrom repetitive peak forw. current Grenzlastintegral I 2t - value Tc = 80 °C TC = 25 °C tP = 1 ms, TC = 25°C TC = 80 °C VCES I C,nom. IC I CRM Ptot VGES 1200 75 105 150 350 +/- 20V V A A A W V

atmega128芯片资料(英文)

1Features•High-performance, Low-power AVR ® 8-bit Microcontroller •Advanced RISC Architecture–133 Powerful Instructions – Most Single Clock Cycle Execution–32 x 8 General Purpose Working Registers + Peripheral Control Registers –Fully Static Operation–Up to 16 MIPS Throughput at 16 MHz –On-chip 2-cycle Multiplier•Nonvolatile Program and Data Memories–128K Bytes of In-System Reprogrammable FlashEndurance: 1,000 Write/Erase Cycles–Optional Boot Code Section with Independent Lock BitsIn-System Programming by On-chip Boot Program True Read-While-Write Operation –4K Bytes EEPROMEndurance: 100,000 Write/Erase Cycles –4K Bytes Internal SRAM–Up to 64K Bytes Optional External Memory Space –Programming Lock for Software Security –SPI Interface for In-System Programming •JTAG (IEEE std. 1149.1 Compliant) Interface–Boundary-scan Capabilities According to the JTAG Standard –Extensive On-chip Debug Support–Programming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface •Peripheral Features–Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes–Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode and Capture Mode–Real Time Counter with Separate Oscillator –Two 8-bit PWM Channels–6 PWM Channels with Programmable Resolution from 1 to 16 Bits –8-channel, 10-bit ADC8 Single-ended Channels 7 Differential Channels2 Differential Channels with Programmable Gain (1x, 10x, 200x)–Byte-oriented 2-wire Serial Interface –Dual Programmable Serial USARTs –Master/Slave SPI Serial Interface–Programmable Watchdog Timer with On-chip Oscillator –On-chip Analog Comparator •Special Microcontroller Features–Power-on Reset and Programmable Brown-out Detection –Internal Calibrated RC Oscillator–External and Internal Interrupt Sources–Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby–Software Selectable Clock Frequency–ATmega103 Compatibility Mode Selected by a Fuse –Global Pull-up Disable •I/O and Packages–53 Programmable I/O Lines –64-lead TQFP •Operating Voltages–2.7 - 5.5V (ATmega128L)–4.5 - 5.5V (ATmega128)•Speed Grades–0 - 8 MHz (ATmega128L)–0 - 16 MHz (ATmega128)Rev. 2467AS-08/01Microcontroller with 128K Bytes In-SystemProgrammable ATmega128ATmega128L Preliminary SummaryNote: This is a summary document. A complete document is available on our web site at .2ATmega128(L)2467AS –08/01Pin ConfigurationsFigure 1. Pinout ATmega128OverviewThe ATmega128 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle,the ATmega128 achieves throughputs approaching 1 MIPS per MHz allowing the sys-tem designer to optimize power consumption versus processing speed.3ATmega128(L)2467AS –08/01Block DiagramFigure 2. Block Diagram4ATmega128(L)2467AS –08/01The AVR core combines a rich instruction set with 32 general purpose working registers.All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.The ATmega128 provides the following features: 128K bytes of In-System Programma-ble Flash with Read-While-Write capabilities, 4K bytes EEPROM, 4K bytes SRAM, 53general-purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), four flexible timer/counters with compare modes and PWM, 2 USARTs, a byte oriented 2-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with internal oscillator,an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM,timer/counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip func-tions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction Mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conver-sions. In Standby mode, the crystal/resonator oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.In Extended Standby mode, both the main oscillator and the asynchronous timer con-tinue to run.The device is manufactured using Atmel ’s high-density nonvolatile memory technology.The on-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an on-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Soft-ware in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega128 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.The ATmega128 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.ATmega103 and ATmega128 CompatibilityThe ATmega128 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O location reserved in the AVR instruction set. To ensure backward compatibility with the ATmega103, all I/O locations present in ATmega103 have the same location in ATmega128. Most additional I/O locations are added in an Extended I/O space starting from $60 to $FF, (i.e., in the ATmega103 internal RAM space). These location can be reached by using LD/LDS/LDD and ST/STS/STD instruction only, not by using IN and OUT instruction. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the increased number of interrupt vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega103 compatibility mode can be selected by programming the fuse M103C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega103. Also, the extended interrupt vectors are removed.5ATmega128(L)2467AS –08/01The ATmega128 is 100% pin compatible with ATmega103, and can replace the ATmega103 on current Printed Circuit Boards. The application note “Replacing ATmega103 by ATmega128” describes what the user should be aware of replacing the ATmega103 by an ATmega128.ATmega103 Compatibility ModeBy programming the M103C fuse, the ATmega128 will be compatible with the ATmega103 regards to RAM, I/O pins and interrupt vectors as described above. How-ever, some new features in ATmega128 are not available in this compatibility mode,these features are listed below:•One USART instead of two, asynchronous mode only. Only the 8 least significant bits of the Baud Rate Register is available.•One 16 bits Timer/Counter with 2 compare registers instead of two 16-bit Timer/Counters with 3 compare registers.•2-wire serial interface is not supported.•Port G serves alternate functions only (not a general I/O port).•Port F serves as digital input only in addition to analog input to the ADC.•Boot Loader capabilities is not supported.•It is not possible to adjust the frequency of the internal calibrated RC oscillator.•The External Memory Interface can not release any Address pins for general I/O, neither configure different wait-states to different External Memory Address sections.Pin DescriptionsVCC Digital supply voltage.GNDGround.Port A (PA7..PA0)Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port A also serves the functions of various special features of the ATmega128 as listed on page 68.Port B (PB7..PB0)Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port B also serves the functions of various special features of the ATmega128 as listed on page 69.Port C (PC7..PC0)Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.6ATmega128(L)2467AS –08/01Port C also serves the functions of special features of the ATmega128 as listed on page 72. In ATmega103 compatibility mode, Port C is output only, and the port C pins are not tri-stated when a reset condition becomes active.Port D (PD7..PD0)Port D is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port D also serves the functions of various special features of the ATmega128 as listed on page 73.Port E (PE7..PE0)Port E is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port E also serves the functions of various special features of the ATmega128 as listed on page 76.Port F (PF7..PF0)Port F serves as the analog inputs to the A/D Converter.Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability.As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resis-tors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even if a reset occurs.Port F also serves the functions of the JTAG interface.In ATmega103 compatibility mode, Port F is an input Port only.Port G (PG4..PG0)Port G is a 5-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port G also serves the functions of various special features.The port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.In ATmega103 compatibility mode, these pins only serves as strobes signals to the external memory as well as input to the 32 kHz oscillator, and the pins are initialized to PG0 = 1, PG1 = 1, and PG2 = 0 asynchronously when a reset condition becomes active,even if the clock is not running. PG3 and PG4 are oscillator pins.RESETReset input. A low level on this pin for longer than the minimum pulse length will gener-ate a reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page 46. Shorter pulses are not guaranteed to generate a reset.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.7ATmega128(L)2467AS –08/01XTAL2Output from the inverting oscillator amplifier.AVCCThis is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to VCC, even if the ADC is not used. If the ADC is used, it should be con-nected to VCC through a low-pass filter.AREF This is the analog reference pin for the A/D Converter.PENThis is a programming enable pin for the serial programming mode. By holding this pin low during a power-on reset, the device will enter the serial programming mode. PEN has no function during normal operation.8ATmega128(L)2467AS –08/01Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page($FF)Reserved --------..Reserved --------($9E)Reserved --------($9D)UCSR1C -UMSEL1UPM11UPM10USBS1UCSZ11UCSZ10UCPOL1185($9C)UDR1USART1 I/O Data Register182($9B)UCSR1A RXC1TXC1UDRE1FE1DOR1UPE1U2X1MPCM1183($9A)UCSR1B RXCIE1TXCIE1UDRIE1RXEN1TXEN1UCSZ12RXB81TXB81184($99)UBRR1L USART1 Baud Rate Register Low186($98)UBRR1H ----USART1 Baud Rate Register High186($97)Reserved --------($96)Reserved --------($95)UCSR0C -UMSEL0UPM01UPM00USBS0UCSZ01UCSZ00UCPOL0185($94)Reserved --------($93)Reserved --------($92)Reserved --------($91)Reserved --------($90)UBRR0H ----USART0 Baud Rate Register High186($8F)Reserved --------($8E)Reserved --------($8D)Reserved --------($8C)TCCR3C FOC3A FOC3B FOC3C -----132($8B)TCCR3A COM3A1COM3A0COM3B1COM3B0COM3C1COM3C0WGM31WGM30127 ($8A)TCCR3B ICNC3ICES3-WGM33WGM32CS32CS31CS30130($89)TCNT3H Timer/Counter3 - Counter Register High Byte 132 ($88)TCNT3L Timer/Counter3 - Counter Register Low Byte132 ($87)OCR3AH Timer/Counter3 - Output Compare Register A High Byte 133($86)OCR3AL Timer/Counter3 - Output Compare Register A Low Byte 133($85)OCR3BH Timer/Counter3 - Output Compare Register B High Byte 133($84)OCR3BL Timer/Counter3 - Output Compare Register B Low Byte 133($83)OCR3CH Timer/Counter3 - Output Compare Register C High Byte 133($82)OCR3CL Timer/Counter3 - Output Compare Register C Low Byte 133($81)ICR3H Timer/Counter3 - Input Capture Register High Byte 134($80)ICR3L Timer/Counter3 - Input Capture Register Low Byte134($7F)Reserved --------($7E)Reserved --------($7D)ETIMSK --TICIE3OCIE3A OCIE3B TOIE3OCIE3C OCIE1C 135 ($7C)ETIFR --ICF3OCF3A OCF3B TOV3OCF3COCF1C136($7B)Reserved --------($7A)TCCR1C FOC1AFOC1BFOC1C-----131($79)OCR1CH Timer/Counter1 - Output Compare Register C High Byte 133($78)OCR1CL Timer/Counter1 - Output Compare Register C Low Byte133($77)Reserved --------($76)Reserved --------($75)Reserved --------($74)TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN -TWIE 198($73)TWDR 2-wire Serial Interface Data Register199($72)TWAR TWA6TWA5TWA4TWA3TWA2TWA1TWA0TWGCE 200($671TWSR TWS7TWS6TWS5TWS4TWS3-TWPS1TWPS0199($70)TWBR 2-wire Serial Interface Bit Rate Register 197($6F)OSCCAL Oscillator Calibration Register38($6E)Reserved --------($6D)XMCRA -SRL2SRL1SRL0SRW01SRW00SRW1129($6C)XMCRB XMBK ----XMM2XMM1XMM031($6B)Reserved --------($6A)EICRA ISC31ISC30ISC21ISC20ISC11ISC10ISC01ISC0084($69)Reserved --------($68)SPMCSR SPMIE RWWSB-RWWSREBLBSETPGWRTPGERSSPMEN270($67)Reserved --------($66)Reserved --------($65)PORTG ---PORTG4PORTG3PORTG2PORTG1PORTG083($64)DDRG ---DDG4DDG3DDG2DDG1DDG083($63)PING ---PING4PING3PING2PING1PING083($62)PORTFPORTF7PORTF6PORTF5PORTF4PORTF3PORTF2PORTF1PORTF0839ATmega128(L)2467AS –08/01($61)DDRF DDF7DDF6DDF5DDF4DDF3DDF2DDF1DDF083($60)Reserved --------$3F ($5F)SREG I T H S V N Z C 9$3E ($5E)SPH SP15SP14SP13SP12SP11SP10SP9SP812$3D ($5D)SPL SP7SP6SP5SP4SP3SP2SP1SP012$3C ($5C)XDIV XDIVENXDIV6XDIV5XDIV4XDIV3XDIV2XDIV1XDIV039$3B ($5B)RAMPZ -------RAMPZ012$3A ($5A)EICRB ISC71ISC70ISC61ISC60ISC51ISC50ISC41ISC4085$39 ($59)EIMSK INT7INT6INT5INT4INT3INT2INT1INT086$38 ($58)EIFR INTF7INTF6INTF5INTF4INTF3INTF INTF1INTF086$37 ($57)TIMSK OCIE2TOIE2TICIE1OCIE1A OCIE1B TOIE1OCIE0TOIE0103, 134, 153$36 ($56)TIFR OCF2TOV2ICF1OCF1A OCF1B TOV1OCF0TOV0103, 136, 154$35 ($55)MCUCR SRE SRW10SE SM1SM0SM2IVSEL IVCE 29, 41, 58 $34 ($54)MCUCSR JTD --JTRF WDRF BORF EXTRF PORF 49, 246$33 ($53)TCCR0FOC0WGM00COM01COM00WGM01CS02CS01CS0098$32 ($52)TCNT0 Timer/Counter0 (8 Bit)100$31 ($51)OCR0 Timer/Counter0 Output Compare Register100$30 ($50)ASSR ----AS0TCN0UB OCR0UB TCR0UB 101$2F ($4F)TCCR1A COM1A1COM1A0COM1B1COM1B0COM1C1COM1C0WGM11WGM10127$2E ($4E)TCCR1B ICNC1ICES1-WGM13WGM12CS12CS11CS10130$2D ($4D)TCNT1H Timer/Counter1 - Counter Register High Byte 132$2C ($4C)TCNT1L Timer/Counter1 - Counter Register Low Byte132$2B ($4B)OCR1AH Timer/Counter1 - Output Compare Register A High Byte 133$2A ($4A)OCR1AL Timer/Counter1 - Output Compare Register A Low Byte 133$29 ($49)OCR1BH Timer/Counter1 - Output Compare Register B High Byte 133$28 ($48)OCR1BL Timer/Counter1 - Output Compare Register B Low Byte 133$27 ($47)ICR1H Timer/Counter1 - Input Capture Register High Byte 134$26 ($46)ICR1L Timer/Counter1 - Input Capture Register Low Byte 134$25 ($45)TCCR2FOC2WGM20COM21COM20WGM21CS22CS21CS20151$24 ($44)TCNT2Timer/Counter2 (8 Bit)153$23 ($43)OCR2Timer/Counter2 Output Compare Register 153$22 ($42)OCDR IDRD/OCDR7OCDR6OCDR5OCDR4OCDR3OCDR2OCDR1OCDR0242$21 ($41)WDTCR ---WDCE WDE WDP2WDP1WDP051$20 ($40)SFIOR TSM --ADHSMACMEPUDPSR0PSR32167, 104, 139, 237$1F ($3F)EEARH ----EEPROM Address Register High19$1E ($3E)EEARL EEPROM Address Register Low Byte 19$1D ($3D)EEDR EEPROM Data Register20$1C ($3C)EECR ----EERIE EEMWE EEWE EERE 20$1B ($3B)PORTA PORTA7PORTA6PORTA5PORTA4PORTA3PORTA2PORTA1PORTA081$1A ($3A)DDRA DDA7DDA6DDA5DDA4DDA3DDA2DDA1DDA081$19 ($39)PINA PINA7PINA6PINA5PINA4PINA3PINA2PINA1PINA081$18 ($38)PORTB PORTB7PORTB6PORTB5PORTB4PORTB3PORTB2PORTB1PORTB081$17 ($37)DDRB DDB7DDB6DDB5DDB4DDB3DDB2DDB1DDB081$16 ($36)PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB082$15 ($35)PORTC PORTC7PORTC6PORTC5PORTC4PORTC3PORTC2PORTC1PORTC082$14 ($34)DDRC DDC7DDC6DDC5DDC4DDC3DDC2DDC1DDC082$13 ($33)PINC PINC7PINC6PINC5PINC4PINC3PINC2PINC1PINC082$12 ($32)PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD082$11 ($31)DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD082$10 ($30)PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND082$0F ($2F)SPDR SPI Data Register163$0E ($2E)SPSR SPIF WCOL -----SPI2X 162$0D ($2D)SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1SPR0161$0C ($2C)UDR0 USART0 I/O Data Register182$0B ($2B)UCSR0A RXC0TXC0UDRE0FE0DOR0UPE0U2X0MPCM0183$0A ($2A)UCSR0B RXCIE0TXCIE0UDRIE0RXEN0TXEN0UCSZ02RXB80TXB80184$09 ($29)UBRR0L USART0 Baud Rate Register Low186$08 ($28)ACSR ACD ACBG ACO ACI ACIE ACIC ACIS1ACIS0218$07 ($27)ADMUX REFS1REFS0ADLAR MUX4MUX3MUX2MUX1MUX0233$06 ($26)ADCSRA ADENADSCADRFADIFADIEADPS2ADPS1ADPS0235$05 ($25)ADCH ADC Data Register High Byte 236$04 ($24)ADCL ADC Data Register Low byte 236$03 ($23)PORTE PORTE7PORTE6PORTE5PORTE4PORTE3PORTE2PORTE1PORTE082$02 ($22)DDREDDE7DDE6DDE5DDE4DDE3DDE2DDE1DDE083Register Summary (Continued)AddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page10ATmega128(L)2467AS –08/01Notes:1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.2.Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate onall bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.$01 ($21)PINE PINE7PINE6PINE5PINE4PINE3PINE2PINE1PINE083$00 ($20)PINFPINF7PINF6PINF5PINF4PINF3PINF2PINF1PINF083Register Summary (Continued)AddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page11ATmega128(L)2467AS –08/01Instruction Set SummaryMnemonicsOperandsDescriptionOperationFlags#ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two RegistersRd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2SUB Rd, Rr Subtract two RegistersRd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One ’s Complement Rd ← $FF − Rd Z,C,N,V 1NEG Rd Two ’s Complement Rd ← $00 − Rd Z,C,N,V,H 1SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1CBR Rd,K Clear Bit(s) in Register Rd ← Rd • ($FF - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd − 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V 1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← $FF None 1MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr Z,C 2MULS Rd, Rr Multiply SignedR1:R0 ← Rd x Rr Z,C 2MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 ← Rd x Rr Z,C 2FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 ← (Rd x Rr) << 1Z,C 2FMULS Rd, Rr Fractional Multiply SignedR1:R0 ← (Rd x Rr) << 1Z,C 2FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 ← (Rd x Rr) << 1Z,C 2BRANCH INSTRUCTIONSRJMP kRelative Jump PC ← PC + k + 1None 2IJMP Indirect Jump to (Z)PC ← Z None 2JMP k Direct JumpPC ← kNone 3RCALL kRelative Subroutine Call PC ← PC + k + 1None 3ICALL Indirect Call to (Z)PC ← Z None 3CALL k Direct Subroutine Call PC ← k None 4RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1 / 2 / 3CP Rd,Rr CompareRd − Rr Z, N,V,C,H 1 CPC Rd,Rr Compare with CarryRd − Rr − C Z, N,V,C,H 1CPI Rd,K Compare Register with Immediate Rd − KZ, N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ←PC+k + 1None 1 / 2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ←PC+k + 1None 1 / 2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1 / 2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1 / 2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1 / 2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1 / 2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1 / 2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1 / 2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1 / 2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1 / 2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None 1 / 2BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None 1 / 2BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None 1 / 2BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1 / 2BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None 1 / 2BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None 1 / 2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1 / 2BRVCk Branch if Overflow Flag is Clearedif (V = 0) then PC ← PC + k + 1None1 / 212ATmega128(L)2467AS –08/01MnemonicsOperandsDescriptionOperationFlags#ClocksBRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1None 1 / 2BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1None 1 / 2DATA TRANSFER INSTRUCTIONSMOV Rd, Rr Move Between Registers Rd ← RrNone 1MOVW Rd, Rr Copy Register Word Rd+1:Rd ← Rr+1:Rr None 1LDI Rd, K Load Immediate Rd ← K None 1LD Rd, X Load IndirectRd ← (X)None 2LD Rd, X+Load Indirect and Post-Inc.Rd ← (X), X ← X + 1None 2LD Rd, - X Load Indirect and Pre-Dec.X ← X - 1, Rd ← (X)None 2LD Rd, Y Load IndirectRd ← (Y)None 2LD Rd, Y+Load Indirect and Post-Inc.Rd ← (Y), Y ← Y + 1None 2LD Rd, - Y Load Indirect and Pre-Dec.Y ← Y - 1, Rd ← (Y)None 2LDD Rd,Y+q Load Indirect with Displacement Rd ← (Y + q)None 2LD Rd, Z Load IndirectRd ← (Z)None 2LD Rd, Z+Load Indirect and Post-Inc.Rd ← (Z), Z ← Z+1None 2LD Rd, -Z Load Indirect and Pre-Dec.Z ← Z - 1, Rd ← (Z)None 2LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q)None 2LDS Rd, k Load Direct from SRAM Rd ← (k)None 2ST X, Rr Store Indirect(X) ← RrNone 2ST X+, Rr Store Indirect and Post-Inc.(X) ← Rr, X ← X + 1None 2ST - X, Rr Store Indirect and Pre-Dec.X ← X - 1, (X) ← Rr None 2ST Y, Rr Store Indirect(Y) ← RrNone 2ST Y+, Rr Store Indirect and Post-Inc.(Y) ← Rr, Y ← Y + 1None 2ST - Y, Rr Store Indirect and Pre-Dec.Y ← Y - 1, (Y) ← Rr None 2STD Y+q,Rr Store Indirect with Displacement (Y + q) ← Rr None 2ST Z, Rr Store Indirect(Z) ← RrNone 2ST Z+, Rr Store Indirect and Post-Inc.(Z) ← Rr, Z ← Z + 1None 2ST -Z, Rr Store Indirect and Pre-Dec.Z ← Z - 1, (Z) ← Rr None 2STD Z+q,Rr Store Indirect with Displacement (Z + q) ← Rr None 2STS k, RrStore Direct to SRAM (k) ← Rr None 2LPM Load Program Memory R0 ← (Z)None 3LPM Rd, Z Load Program MemoryRd ← (Z)None 3LPM Rd, Z+Load Program Memory and Post-Inc Rd ← (Z), Z ← Z+1None 3ELPM Extended Load Program Memory R0 ← (RAMPZ:Z)None 3ELPM Rd, Z Extended Load Program MemoryRd ← (RAMPZ:Z)None 3ELPM Rd, Z+Extended Load Program Memory and Post-Inc Rd ← (RAMPZ:Z), RAMPZ:Z ← RAMPZ:Z+1None 3SPM Store Program Memory (Z) ← R1:R0None -IN Rd, P In Port Rd ← P None 1OUT P, Rr Out PortP ← Rr None 1PUSH Rr Push Register on Stack STACK ← Rr None 2POP Rd Pop Register from Stack Rd ← STACK None 2BIT AND BIT-TEST INSTRUCTIONSSBI P,b Set Bit in I/O Register I/O(P,b) ← 1None 2CBI P,b Clear Bit in I/O Register I/O(P,b) ← 0None 2LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROL Rd Rotate Left Through Carry Rd(0)←C,Rd(n+1)← Rd(n),C ←Rd(7)Z,C,N,V 1ROR Rd Rotate Right Through Carry Rd(7)←C,Rd(n)← Rd(n+1),C ←Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag ClearSREG(s) ← 0 SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, b Bit load from T to Register Rd(b) ← T None 1SEC Set Carry C ←1C 1CLC Clear Carry C ← 0 C 1SEN Set Negative Flag N ← 1N 1CLN Clear Negative Flag N ← 0 N 1SEZ Set Zero Flag Z ←1Z 1CLZ Clear Zero Flag Z ← 0 Z 1SEI Global Interrupt Enable I ←1I 1CLI Global Interrupt Disable I ← 0 I 1SES Set Signed Test Flag S ←1S 1CLSClear Signed Test FlagS ← 0S1Instruction Set Summary (Continued)。

EM6322FP8CT-85S中文资料(Emerging Memory)中文数据手册「EasyDatasheet - 矽搜」

推荐直流工作条件

1)

参数 电源电压 地面 输入高电压

输入低电压

符号

VCC VSS VIH VIL

Min 2.7 0 2.2 -0.2 3)

Typ

Max

Unit

3.3

3.6

V

0

0

V

-

VCC + 0.2 2)

V

-

0.6

V

1. TA = -40到85 oC,另有说明

2. 过冲:V

符号

VIN , V OUT VCC PD TA

* 强调超过"绝对最大额定值"可能会造成永久性损坏设备.功能 操作应仅限于推荐工作条件.暴露在绝对最大额定值条件下长时间可能会影响其可靠性.

EM641FV8FS系列

低功耗,512Kx8 SRAM

额定值

-0.2 to Vcc+0.3(Max.4.0V) -0.2 to 4.0V 1.0 -40到85

芯片中文手册,看全文,戳

合并存储器与逻辑解决方案公司

文档标题

512K×8位 超 低 功 耗 和 低 电 压 全 CMOS静 态 RAM

修订记录 版本号 0.0 0.1

历史

初稿草案

第2'草案

加入无铅部件号

EM641FV8FS系列 低功耗,512Kx8 SRAM

草案日期 5月25日,2003 2004年2月13日,

Unit

V V W oC

功能说明

CS

OE

WE

H

X

X

L

H

H

L

L

H

L

X

L

注:X表示不关心. (必须是高或低状态)

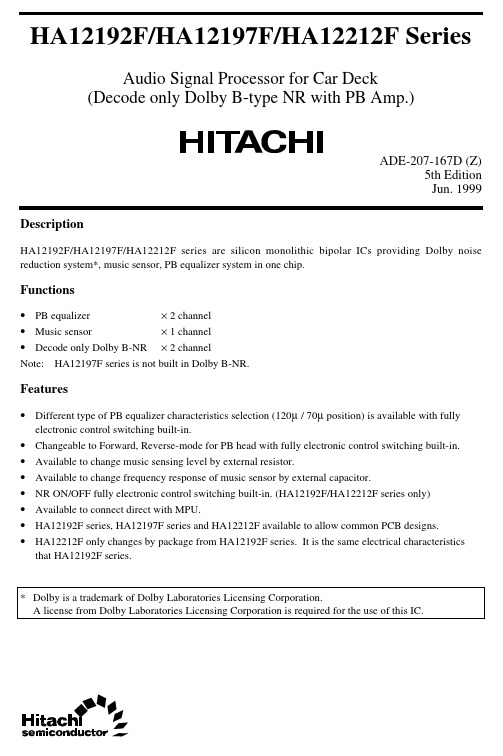

HA12192F中文资料

RIP

RIN (L)

NFI (L)

M-OUT EQOUT (L) (L)

DIN (L)

PBOUT (L)

DET (L)

34 70µ ON I.A. Decode only Dolby B-NR

− + − +

33

32

31

30

29

28

23

22

21

20

19

18

F

R

35 LPF

+ −

DET MA

36 Decode only Dolby B-NR I.A. 1 2 3 8 9 10

MS

F

R

70µ ON 39 40

37

I

Equivalent Circuit

MS VCC

Description MS output (to MPU) *1

200

100k GND

15

21

MSGV

V = VCC / 2

MS gain terminal * 1

V 90k

Note:

1. MS : Music Sensor

6

Block Diagram

HA12192F/HA12197F/HA12212F Series

Audio Signal Processor for Car Deck (Decode only Dolby B-type NR with PB Amp.)

ADE-207-167D (Z) 5th Edition Jun. 1999 Description

18

28

DIN (L)

V = VCC / 2

Deck input

FP40R12KT3中文资料

"43

7

"4ZZ 2/>Gb-

1

元器件交易网

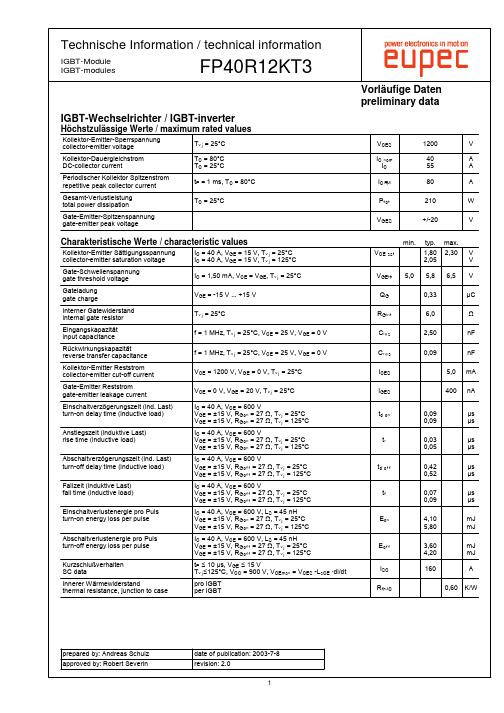

Technische Information / technical information

IGBT-Module IGBT-modules

FP40R12KT3

Vorläufige Daten preliminary data

元器件交易网

Technische Information / technical information

IGBT-Module IGBT-modules

FP40R12KT3

Vorläufige Daten preliminary data

IGBT-Wechselrichter / IGBT-inverter

Charakteristische Werte / characteristic values

! < $ < $ 2 " $ "# # = $ $ $ < $ $ ! $ ! "# # # ! $ T$ $ # U $ # U U ! V W U U V W W W = D D # D $ $ $ $ $ 2- ( 6 2- ( 6 9 ,@. ( 0) ,9 %&' ( )*+ 9 ,@. ( 0) ,9 %&' ( 0 )*+

Charakteristische Werte / characteristic values

! < $ < $ 2 " $ "# # = $ $ $ < $ $ ! = D $ $ $ $ $ 2- ( 0) 9 ,@. ( 0) ,9 %&' ( )*+ 2- ( 0) 9 ,@. ( 0) ,9 %&' ( 0 )*+ 2- ( 9) # 9 ,-. ( ,@.9 %&' ( )*+ ,@. ( 0) , A0) ,

UCN5812EPFTR中文资料

U E D P R O D U C T E F E R E N C E O N L Y d e d r e p l a c e m e n t — A 6812BiMOS II 20-BIT SERIAL-INPUT, LATCHEDSOURCE DRIVERS FOR -40°C TO +85°C OPERATIONThe UCQ5812AF/EPF combine a 20-bit CMOS shift register, data latches, and control circuitry with high-voltage bipolar source drivers and active DMOS pull-downs for reduced supply current requirements. Although designed primarily for vacuum-fluorescent displays, the high-voltage, high-current outputs also allow them to be used in other peripheral power driver applications.The CMOS shift register and latches allow direct interfacing with microprocessor-based systems. With a 5 V supply, they will operate to at least 3.3 MHz. At 12 V, higher speeds are possible. Especially useful for inter-digit blanking, the BLANKING input disables the output source drives and turns on the DMOS sink drivers. Use with TTL may require the use of appropriate pull-up resistors to ensure an input logic high.A CMOS serial data output enables cascade connections in applications requiring additional drive lines. Similar devices are available as theUCQ5810AF/LWF (10 bits), UCQ5811A (12 bits), and UCQ5818AF/EPF (32 bits).The output source drivers are high-voltage PNP-NPN Darlingtons with aminimum breakdown of 60 V and are capable of sourcing up to 40 mA. The DMOS active pull-downs are capable of sinking up to 15 mA.The UCQ5812AF is supplied in a 28-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. For surface mounting, the UCQ5812EPF is furnished in 28-lead plastic chip carrier (quad pack) with 0.050"(1.22 mm)centers. Copper lead-frames, reduced supply current requirements and lower output saturation voltages, allow continuous operation, with all outputs sourcing 25 mA, of the UCQ5812AF over the operating temperature range,and the UCQ5812EPF up to +75°C.Always order by complete part number, e.g.,UCQ5812AF .FEATURESs High-Speed Source Drivers s 60 V Source Outputss To 3.3 MHz Data Input Rate s Low-Output Saturation VoltagessLow-Power CMOS Logic and Latches s Active DMOS Pull-Downs s Reduced Supply Current Requirementss Improved Replacement for TL5812Data Sheet26182.27B5812-F5812-F20-BIT SERIAL-INPUT,LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATION115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TYPICAL OUTPUT DRIVERNDwg. No. A-14,219Copyright © 1995, 2002 Allegro MicroSystems, Inc.MOS SERIAL-PARALLEL SHIFT REGISTERLATCHES5812-F20-BIT SERIAL-INPUT,LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATIONELECTRICAL CHARACTERISTICS over operating temperature range, at V BB = 60 V (unless otherwise noted).Limits @ V DD = 5 V Limits @ V DD = 12 V CharacteristicSymbol Test Conditions Mln.Typ.Max.Min.Typ.Max.Units Output Leakage Current I CEX V OUT = 0 V, T A = +70°C —-5.0-15—-5.0-15µA Output VoltageV OUT(1)I OUT = -25 mA, V BB = 60 V 5858.5—5858.5—V V OUT(0)I OUT = 1 mA — 2.0 3.0———V I OUT = 2 mA ———— 2.0 3.5V Output Pull-Down CurrentI OUT(0)V OUT = 5 V to V BB 2.0 3.5————mA V OUT = 20 V to V BB———8.013—mA Input VoltageV IN(1) 3.5— 5.310.5—12.3V V IN(0)-0.3—+0.8-0.3—+0.8V Input CurrentI IN(1)V IN = V DD —0.050.5—0.1 1.0µA I IN(0)V IN = 0.8 V —-0.05-0.5—-0.1-1.0µA Serial DataV OUT(1)I OUT = -200 µA 4.5 4.7—11.711.8—V V OUT(0)I OUT = 200 µA—200250—100200mV Maximum Clock Frequency f clk 3.3*—————MHz Supply CurrentI DD(1)All Outputs High —100300—200500µA I DD(0)All Outputs Low —100300—200500µA I BB(1)Outputs High, No Load — 1.5 4.0— 1.5 4.0mA I BB(0)Outputs Low—10100—10100µA Blanking to Output Delayt PHL C L = 30 pF, 50% to 50%—2000——1000—ns t PLHC L = 30 pF, 50% to 50%—1000——850—ns Output Fall Time t f C L = 30 pF, 90% to 10%—1450——650—ns Output Rise Timet rC L = 30 pF, 10% to 90%—650——700—nsNegative current is defined as coming out of (sourcing) the specified device pin.* Operation at a clock frequency greater than the specified minimum value is possible but not warranteed.5812-F20-BIT SERIAL-INPUT,LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATION115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TRUTH TABLEL = Low Logic LevelH = High Logic Level X = IrrelevantP = Present State R = Previous StateDwg. No. 12,649ATIMING REQUIREMENTS(T A = +25°C,V DD = 5 V, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75 ns C.Minimum Data Pulse Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150 ns D.Minimum Clock Pulse Width. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150 ns E.Minimum Time Between Clock Activation and Strobe. . . . . . . . . . . 300 ns F.Minimum Strobe Pulse Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100 ns G.Typical Time Between Strobe Activation andOutput Transistion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500 ns Timing is representative of a 3.3 MHz clock. Higher speeds may be attainable with increased supply voltage; operation at high temperatures will reduce the specified maximum clock frequency.Serial Data present at the input is transferred to the shift register on the logic “0” to logic “1”transition of the CLOCK input pulse. On succeed-ing CLOCK pulses, the registers shift datainformation towards the SERIAL DATA OUT-PUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is trans-ferred to the respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to acceptnew data as long as the STROBE is held high.Applications where the latches are bypassed (STROBE tied high) will require that the BLANKING input be high during serial data entry.When the BLANKING input is high, the output source drivers are disabled (OFF); the DMOS sink drivers are ON, the information stored in the latches is not affected by theBLANKING input. With the BLANKING input low, the outputs are controlled by the state of their respective latches.CLOCK DATA IN STROBE BLANKINGOUT5812-F20-BIT SERIAL-INPUT,LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATIONNOTES:1.Exact body and lead configuration at vendor ’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.4.Supplied in standard sticks/tubes of 12 devices.5812-F20-BIT SERIAL-INPUT,LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATION115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000NOTES:1.Exact body and lead configuration at vendor ’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Supplied in standard sticks/tubes of 38 devices or add “TR ” to part number for tape and reel.5812-F20-BIT SERIAL-INPUT, LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATIONThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.5812-F20-BIT SERIAL-INPUT,LATCHED SOURCE DRIVERS FOR -40°C TO +85°C OPERATION115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number †SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V‡58958-Bit 350 mA 50 V 58218-Bit 350 mA 80 V 58228-Bit 350 mA 50 V‡58418-Bit350 mA 80 V‡58428-Bit (constant-current LED driver)75 mA 17 V 62758-Bit (constant-current LED driver)120 mA 24 V 62778-Bit (DMOS drivers)250 mA 50 V 65958-Bit (DMOS drivers)350 mA 50 V‡6A5958-Bit (DMOS drivers)100 mA 50 V 6B59510-Bit (active pull-downs)-25 mA 60 V 5810-F and 681012-Bit (active pull-downs)-25 mA 60 V 581116-Bit (constant-current LED driver)75 mA 17 V 627620-Bit (active pull-downs)-25 mA 60 V 5812-F and 681232-Bit (active pull-downs)-25 mA 60 V 5818-F and 681832-Bit100 mA 30 V 583332-Bit (saturated drivers)100 mA 40 V 5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V‡58008-Bit -25 mA 60 V 58158-Bit350 mA 50 V‡58018-Bit (DMOS drivers)100 mA 50 V 6B2738-Bit (DMOS drivers)250 mA 50 V 6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V‡5804Addressable 8-Bit Decoder/DMOS Driver 250 mA 50 V 6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V‡6A259Addressable 8-Bit Decoder/DMOS Driver 100 mA 50 V 6B259Addressable 28-Line Decoder/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits.Negative current is defined as coming out of (sourcing) the output.†Complete part number includes additional characters to indicate operating temperature range and package style.‡Internal transient-suppression diodes included for inductive-load protection.。

FQPF12N60C中文资料

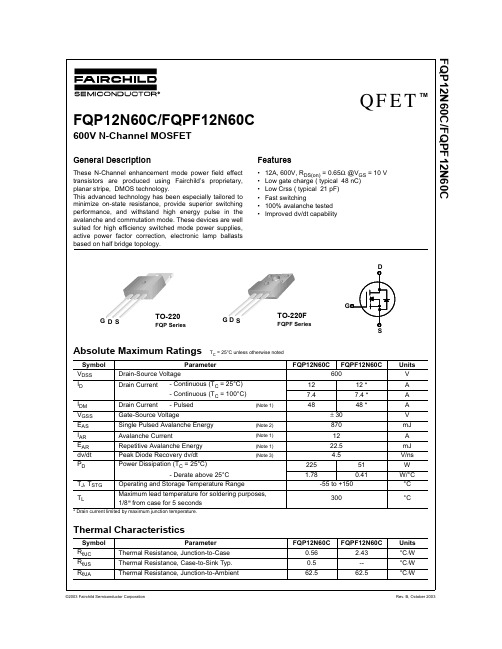

FQP12N60C/FQPF12N60C

FQP12N60C/FQPF12N60C

600V N-Channel MOSFET

QFET TM

General Description

These N-Channel enhancement mode power field effect transistors are produced using Fairchild’s proprietary, planar stripe, DMOS technology. This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode. These devices are well suited for high efficiency switched mode power supplies, active power factor correction, electronic lamp ballasts based on half bridge topology.

D

!

GDS

TO-220

FQP Series

GD S

TO-220F

FQPF Series

G!

●

◀▲

● ●

!

S

Absolute Maximum Ratings TC = 25°C unless otherwise noted

RT812多功能电表校验仪V1_5

第六章

RT812 相关概念说明 ............................................... 33

刻度值 ............................................................................................ 33 分度 .............................................................................................. 33 检表和计算误差 .................................................................................... 34

第三章

基本操作 .......................................................................................................................................................................................................... 6 3.2 在检表菜单中显示接线图..................................................................................................................................... 6 3.3 分度的设置 ........................................................................................................................................................... 6 3.4 记录清空............................................................................................................................................................... 6 3.5 检表数据的保存.................................................................................................................................................... 6 3.6 检表和计算误差.................................................................................................................................................... 6

伺服驱动器12A8中文资料说明书

-

外部的

-

电流模式、IR 补偿模式、测速发电机模式、电压模式

-

有刷直流电机、音圈

-

过流、过温、过压、短路(相间和相地)

机械规格

单位

值

mm(in) 129.3×75.8×2280(9.9)

℃(℉) ℃(℉)

-

0-65 (32-149) -40-85(-40-185) 独立式

路、过压和过温,关掉所有功率开关器件并输出高电平。

无连接(保留)

-

无连接(保留)

-

引脚 1 2 3 4 5

名称 -MOT +MOT POWER GND POWER GND HIGH VOLTAGE

负电机输出 正电机输出

功率接口 P2 描述/注意点

功率地(与信号地相连)

直流电源输入

I/O O O GND GND I

限制电流的最大值,但不影响最大峰值限制电流值。

TTL 电平(+5V)禁止或使能输入。悬空时使能驱动器,接地时禁止驱动器。 I

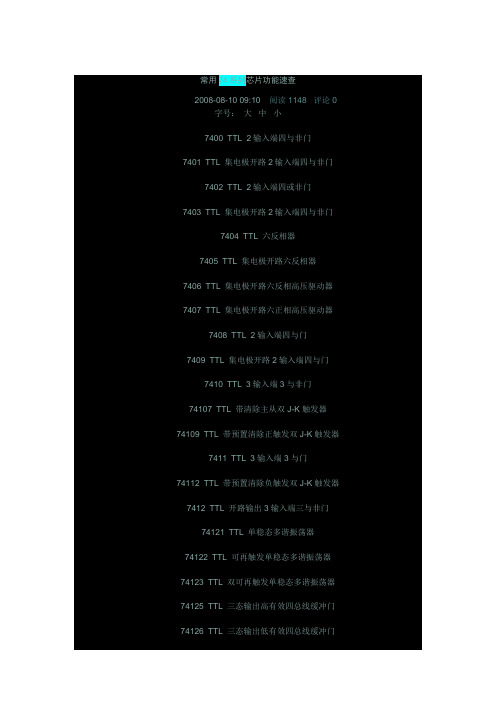

常用74系列芯片功能速查

常用74系列芯片功能速查技术天地 2008-08-10 09:10 阅读1148 评论0字号:大中小7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√ √ √01 四2输入端与非门(OC) √ √02 四2输入端或非门√ √ √03 四2输入端与非门(OC) √ √04 六反相器√ √ √05 六反相器(OC) √ √06 六高压输出反相器(OC,30V) √ √07 六高压输出缓冲,驱动器(OC,30V) √ √ √08 四2输入端与门√ √ √09 四2输入端与门(OC) √√ √10 三3输入端与非门√ √ √11 三3输入端与门√ √12 三3输入端与非门(OC) √ √ √13 双4输入端与非门√ √ √14 六反相器√ √ √15 三3输入端与门(OC) √ √16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√ √ √21 双4输入端与门√ √ √22 双4输入端与非门(OC) √ √25 双4输入端或非门(有选通端) √ √ √26 四2输入端高压输出与非缓冲器√ √ √27 三3输入端或非门√ √ √28 四2输入端或非缓冲器√ √ √30 8输入端与非门√ √ √32 四2输入端或门√ √ √33 四2输入端或非缓冲器(OC) √ √37 四2输入端与非缓冲器√ √38 四2输入端与非缓冲器(OC) √ √40 双4输入端与非缓冲器√ √ √42 4线-10线译码器(BCD输入) √ √43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√ √ √51 2路3-3输入,2路2-2输入与或非门√ √ √52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√ √55 2路4-4输入与或非门√60 双4输入与扩展器√ √61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√ √78 双D型触发器√ √85 四位数值比较器√86 四2输入端异或门√ √ √87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√ √112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√ √ √122 可重触发单稳态触发器√ √ √123 可重触发双稳态触发器√ √ √125 四总线缓冲器√ √ √126 四总线缓冲器√ √ √128 四2输入端或非线驱动器√ √ √132 四2输入端与非门√ √ √。

F81216AD中文资料

F81216AD

F81216AD

LPC to 4 UART + 9-bit Protocol

Release Date: July, 2008 Version: V0.20P

F81216AD.

July, 2008 V0.20P

元器件交易网

F81216AD.

July, 2008 பைடு நூலகம்0.20P

元器件交易网

F81216AD

Table of Content

1. General Description.................................................................................................................................1 2. Feature List..............................................................................................................................................1 3. Pin Configuration ....................................................................................................................................2 4. Pin Description........................................................................................................................................3 4.1 ISA/LPC Interface ................................................................................................................................. 3 4.2 UART Interface...................................................................................................................................... 4 4.3 Power ..................................................................................................................................................... 7 5. Functional Description ............................................................................................................................8 5.1 LPC Interface ...................................................................................................................................... 8 5.2 UART.................................................................................................................................................. 8 5.3 IR Function ....................................................................................................................................... 13 5.4 Watch Dog Timer Function............................................................................................................... 13 5.5 Serial IRQ ......................................................................................................................................... 14 6. Register Description......................................................................................................................17 6.1. Global Control Registers............................................................................................................... 19 6.2. UART1 Registers (CR00) ............................................................................................................. 21 6.3. UART2 Registers (CR01) ............................................................................................................. 25 6.4. UART3 Registers (CR02) ............................................................................................................. 28 6.5. UART4 Registers (CR03) ............................................................................................................. 31 6.6. Watchdog Timer Registers (CR08) ............................................................................................... 34 7. Electron Characteristic .......................................................................................................................36 7.1 Absolute Maximum Ratings ............................................................................................................. 36 7.2 DC Characteristics ............................................................................................................................... 36 8. Ordering Information .........................................................................................................................37 9. Package Dimensions ..........................................................................................................................38 10. Application Circuit ...........................................................................................................................39

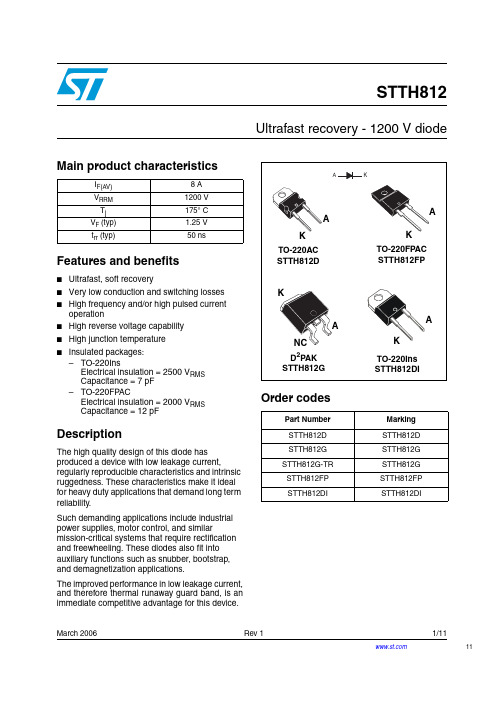

STTH812资料

March 2006 Rev 11/1111STTH812Ultrafast recovery - 1200 V diodeMain product characteristicsFeatures and benefits■Ultrafast, soft recovery■Very low conduction and switching losses ■High frequency and/or high pulsed current operation■High reverse voltage capability ■High junction temperature■Insulated packages: –TO-220InsElectrical insulation = 2500 V RMS Capacitance = 7 pF –TO-220FPACElectrical insulation = 2000 V RMS Capacitance = 12 pFDescriptionThe high quality design of this diode has produced a device with low leakage current,regularly reproducible characteristics and intrinsic ruggedness. These characteristics make it ideal for heavy duty applications that demand long term reliability.Such demanding applications include industrial power supplies, motor control, and similarmission-critical systems that require rectification and freewheeling. These diodes also fit into auxiliary functions such as snubber, bootstrap, and demagnetization applications.The improved performance in low leakage current,and therefore thermal runaway guard band, is an immediate competitive advantage for this device.Order codesI F(AV)8 A V RRM 1200 V T j 175° C V F (typ) 1.25 V t rr (typ)50 nsPart Number Marking STTH812D STTH812D STTH812G STTH812G STTH812G-TR STTH812G STTH812FP STTH812FP STTH812DISTTH812DICharacteristics STTH8122/111 CharacteristicsTo evaluate the conduction losses use the following equation: P = 1.5 x I F(AV) + 0.05 I F 2(RMS)Table 1.Absolute ratings (limiting values at 25° C, unless otherwise specified)Symbol ParameterValue Unit V RRM Repetitive peak reverse voltage 1200V I F(RMS)RMS forward currentTO-220AC / D 2P AK / TO-220FP AC 30ATO-220AC Ins 20I F(AV)Average forward current, δ = 0.5TO-220AC / D 2P AKT c = 140° C 8ATO-220FP AC T c = 75° C TO-220AC InsT c = 115° CI FRM Repetitive peak forward current t p = 5 µs, F = 5 kHz square 100A I FSM Surge non repetitive forward current t p = 10 ms Sinusoidal80A T stg Storage temperature range-65 to + 175°C T jMaximum operating junction temperature175°CTable 2.Thermal parametersSymbolParameterValue UnitR th(j-c)Junction to case TO-220AC / D 2P AK1.9°C/W TO-220FP AC 5.4TO-220AC Ins3.1Table 3.Static electrical characteristicsSymbol ParameterTest conditionsMin.TypMax.Unit I R (1)Reverse leakage currentT j = 25° C V R = V RRM8µAT j = 125° C 550V F (2)Forward voltage dropT j = 25° CI F = 8 A2.2V T j = 125° C 1.30 2.0T j = 150° C1.251.91.Pulse test: t p = 5 ms, δ < 2 %2.Pulse test: t p = 380 µs, δ < 2 %STTH812Characteristics3/11Table 4.Dynamic characteristicsSymbolParameterTest conditionsMin.TypMax.Unitt rrReverse recovery timeI F = 1 A, dI F /dt = -50 A/µs, V R = 30 V , T j = 25° C 100nsI F = 1 A, dI F /dt = -100 A/µs,V R = 30 V , T j = 25° C 5070I RM Reverse recovery current I F = 8 A, dI F /dt = -200 A/µs,V R = 600 V , T j = 125° C 1421A S Softness factor I F = 8 A, dI F /dt = -200 A/µs,V R = 600 V , T j = 125° C 2t fr Forward recovery time I F = 8 A dI F /dt = 50 A/µs V FR = 1.5 x V Fmax , T j = 25° C 400ns V FPForward recovery voltageI F = 8 A, dI F /dt = 50 A/µs,T j = 25° C7VFigure 1.Conduction losses versusFigure 2.Forward voltage drop versusFigure 3.Relative variation of thermal impedance junction to case Figure 4.Relative variation of thermalimpedance junction to case versusCharacteristicsSTTH8124/11Figure 5.Peak reverse recovery currentFigure 6.Reverse recovery time versus dI F /dtFigure 7.Reverse recovery charges versus Figure 8.Softness factor versus dI F /dtFigure 9.Relative variations of dynamic parameters versus junction Figure 10.Transient peak forward voltageversus dI F /dt (typical values)STTH812Characteristics5/11Figure 11.Forward recovery time versus dI F /dt (typical values)Figure 12.Junction capacitance versusreverse voltage applied (typicalFigure 13.Thermal resistance junction toambient versus copper surface under tab (Epoxy printed circuitPackage mechanical data STTH812 2 Package mechanical dataEpoxy meets UL94, V0Cooling method: by conduction (C)Recommended torque value: 0.55 Nm (TO-220AC)Maximum torque value: 0.7 Nm (TO-220AC)6/11STTH812Package mechanical data7/11Package mechanical data STTH8128/11STTH812Package mechanical data22In order to meet environmental requirements, ST offers these devices in ECOP ACK®packages. These packages have a Lead-free second level interconnect . The category ofsecond level interconnect is marked on the package and on the inner box label, incompliance with JEDEC Standard JESD97. The maximum ratings related to solderingconditions are also marked on the inner box label. ECOP ACK is an ST trademark.ECOP ACK specifications are available at: .9/11Ordering information STTH81210/113 Ordering information4 Revision historyPart Number Marking Package Weight Base qtyDelivery modeSTTH812D STTH812D TO-220AC 1.86 g 50Tube STTH812DI STTH812DI TO-220Ins 1.86 g 50Tube STTH812FP STTH812FP TO-220FP AC 2.2 g 50Tube STTH812G STTH812G D 2P AK 1.48 g 50Tube STTH812G-TRSTTH812GD 2P AK1.48 g1000Tape & reelDate RevisionDescription of Changes02-Mar-20061First issue.元器件交易网STTH812Please Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve theright to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at anytime, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of thisdocument refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party productsor services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of suchthird party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIEDWARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZE REPRESENTATIVE OF ST, ST PRODUCTS ARE NOT DESIGNED,AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS, WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, ORSEVERE PROPERTY OR ENVIRONMENTAL DAMAGE.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately voidany warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, anyliability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2006 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America11/11。

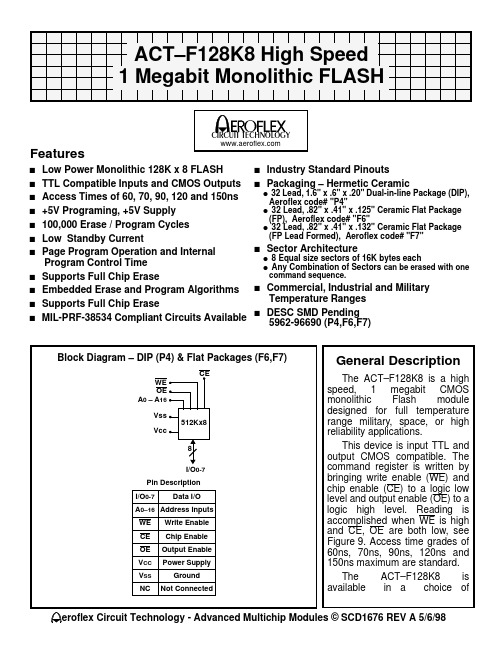

ACT-F1288N-150P4I中文资料

second. Erase is accomplished by executing the erase command sequence. This will invoke the Embedded Erase Algorithm which is an internal algorithm that automatically preprograms the array, (if it is not already programmed before) executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.

The standard ACT–F128K8 offers access times between 60ns and 150ns, allowing operation of high-speed microprocessors without wait states. To eliminate bus contention, the device has separate chip enable (CE), write enable (WE) and output enable (OE) controls. The ACT–F128K8 is command set compatible with JEDEC standard 1 Mbit EEPROMs. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state-machine which controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations.

MEMORY存储芯片MAX813LESA+中文规格书