PowerPC单片机资料 、应用、价格、参数

PowerPC405开发板简要介绍

一、硬件方面:1、CPU介绍:PowerPC® 405 32-bit RISC processor,最高主频333MHz ,带一级数据和指令cache各16KB;PC-133 规范SDRAM 接口;PCI 2.2 规范接口(32-bit, 最高66MHz) ;两个片内以太网10/100Mbps 自适应MAC 提供MII接口;独立的Local BUS 两个串口,一个IIC接口。

2、开发板硬件配置:NOR FLASH:4MBit(512Kx8Bit);NAND FLASH: 64MB ;SDRAM 64MBLocal BUS总线提供外部接口;2个PCI接口;2个串口;2个10/100Mbps以太网接口;外接AC/DC电源适配器(5V输出),调试方便,并具有灵活的启动配置方式。

3、开发板PCB布局在EMC、系统的稳定性方面都做了全面的考虑。

附:开发板正面图:开发板反面图:1 :5V电源输入接口2:5V输入指示灯3:板上电源开关4:板上电源指示灯5:系统复位按钮6:JTAG接口7:PCI SLOT1 8:PCI SLOT2 9:GPIO扩展插座10:LOCAL BUS插座11:8bit NOR FLASH 12:串口013:串口1 14:ETH0-1 15:NAND FLASH16:启动模式配置17:CPU (PPC405EP)18:CPU部分3.3V电源跳线、指示灯19:CPU 部分1.8V电源跳线20-21:GND(方便测试用)此板在设计上具有以下优点:1):指示灯丰富:能直观的看到外接电源开关、板上电源是否工作正常。

尤其是将CPU部分的电源用跳线连接,防止意外烧坏CPU,用户在设计产品时可参考此方法。

2)、走线布局都非常讲究,对SDARM部分还做了走线的等长处理,以保证系统的可靠性和稳定性。

二、软件方面:提供eldk、uboot、linux2.4和linux2.6的BSP包。

三、特别提示:购买开发板后:我们会提供硬件原理图,芯片资料等;并提供较为全面的技术支持。

嵌入式CPU分类

嵌入式CPU分类马秉镇10021170杨张先河10021173薛祎凡10021174徐鑫10021176按功能分类:一、嵌入式微处理器嵌入式微处理器(Micro Processor Unit,MPU)是由通用计算机中的CPU演变而来的。

它的特征是具有32位以上的处理器,具有较高的性能,当然其价格也相应较高。

但与计算机处理器不同的是,在实际嵌入式应用中,只保留和嵌入式应用紧密相关的功能硬件,去除其他的冗余功能部分,这样就以最低的功耗和资源实现嵌入式应用的特殊要求。

和工业控制计算机相比,嵌入式微处理器具有体积小、重量轻、成本低、可靠性高的优点。

目前主要的嵌入式处理器类型有Am186/88、386EX、SC-400、Power PC、68000、MIPS、ARM/ StrongARM系列等。

二、嵌入式微控制器嵌入式微控制器(Microcontroller Unit, MCU)的典型代表是单片机,从70年代末单片机出现到今天,虽然已经经过了20多年的历史,但这种8位的电子器件目前在嵌入式设备中仍然有着极其广泛的应用。

单片机芯片内部集成ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串行口、脉宽调制输出、A/D、D/A、Flash RAM、EEPROM等各种必要功能和外设。

和嵌入式微处理器相比,微控制器的最大特点是单片化,体积大大减小,从而使功耗和成本下降、可靠性提高。

微控制器是目前嵌入式系统工业的主流。

微控制器的片上外设资源一般比较丰富,适合于控制,因此称微控制器。

由于MCU低廉的价格,优良的功能,所以拥有的品种和数量最多,比较有代表性的包括8051、MCS-251、MCS-96/196/296、P51XA、C166/167、68K系列以及MCU 8XC930/931、C540、C541,并且有支持I2C、CAN-Bus、LCD及众多专用MCU和兼容系列。

目前MCU占嵌入式系统约70%的市场份额。

PowerPC处理器原理介绍

PowerPC处理器结构 PowerPC处理器体系结构概述

6、调试 PowerPC405处理器调试资源包括特殊调试模型,在 硬件和软件开发过程中,支持各种类型调试。这些调试包 括: 1)内部调试模式:ROM监控程序和软件调试器 2)外部调试模式:JTAG调试器 3)调试等待模式:处理器停下来允许服务中断 4)实时跟踪模式:事件触发用于实时跟踪

PowerPC处理器结构 PowerPC处理器体系结构概述

缓存控制器采用了最近使用的LRU的缓存行替换策略 。即缓存行被填充时,最近经常访问的缓存行被保留,而 其它均被替换。

指令缓存的功能包括:16KB,双向级关联(2-way set associative);奇偶检测和报告(只有Virtex-4);每缓存 行8字(32字节);提取行缓冲区;提供了来自提取行缓 冲区的取指命中;下一个顺序行的可编程预取到提取行缓 冲区;非缓存指令的可编程预取:全行(8字)/半行(4 字);提取行满时,非阻塞访问。

容。

PowerPC处理器结构 PowerPC处理器体系结构概述

PowerPC处理器是定点处理器,它与PowerPC UISA兼 容。PowerPC405 VEA和OEA支持大部分都可以用来实现 PowerPC405 Book-E的结构。图3.1给出了PowerPC处理器 的结构图。

PowerPC处理器结构 PowerPC处理器体系结构概述

PowerPC处理器结构 PowerPC处理器体系结构概述

4、指令和数据缓存 PowerPC处理器通过指令缓存单元ICU和数据缓存单 元DCU访问存储器。每个缓存单元包括: 1)PLB主接口 2)缓存阵列 3)缓存控制器; 对于CPU来说,对指令和数据缓存的命中是单周期的 存储器访问。处理缓存缺失,就是通过PLB向其它PLB设 备发出请求,比如外部存储器控制器。

PowerPC价格数据大全

PowerPCFreescale(飞思卡尔)Freescale前身为摩托罗拉半导体,2004年分拆后成为独立公司,2006年底被私募基金以176亿美金收购并私有化, 是全球前20大半导体公司之一,高峰时年销售额超过60亿美金。

公司总部位于美国德州,全球员工超过两万名。

Freescale产品在汽车电子、通信网络等领域有很强的优势。

PowerPC介绍PowerPC 处理器有广泛的实现范围,包括从诸如 Power4 那样的高端服务器CPU 到嵌入式 CPU 市场( PowerPC任天堂 Gamecube 使PowerPC)。

PowerPC 处理器有非常强的嵌入式表现,因为它具有优异的性能、较低的能量损耗以及较低的散热量。

除了象串行和以太网控制器那样的集成I/O,该嵌入式处理器与台式机CPU 存在非常显著的区别。

例如,4xx 系列 PowerPC 处理器缺乏浮点运算,并且还使用一个受软件控制的 TLB 进行内存管理,而不是象台式机芯片中那样采用反转页表。

PowerPC 处理器有 32 个(32 位或 64 位)GPR(通用寄存器)以及诸如 PC(程序计数器,也称为 IAR/指令地址寄存器或 NIP/下一指令指针)、LR(链接寄存器)、CR(条件寄存器)等各种其它寄存器。

有些 PowerPC CPU 还有 32 个 64 位 FPR(浮点寄存器)。

PowerPC系列单片机价格产品型号产品描述价格$ MPC5200VR400B IC MPU PROCESSOR 32BIT 272-PBGA 27.218MPC5200CVR400B IC MPU 32BIT 400MHZ 272-PBGA 31.979MPC7410VS400LE IC MPU 32BIT 400MHZ 360-FCCLGA 65.987MPC755BPX300LE IC MPU 300MHZ PPC 360-FCPBGA 72.157MC7447AVS733NB IC MPU RISC 733MHZ 360-FCCLGA 81.735MC7447AVS1000LB IC MPU RISC 1000MHZ 360-FCCLGA 102.866MPC755CRX400LE IC MPU 32BIT 400MHZ PPC 360-CBGA 115.064MC7447AVS1000NB IC MPU RISC 1000MHZ 360-FCCLGA 119.369MPC7410VS500LE IC MPU PPC 500MHZ 360-FCCLGA 143.68MC7447AHX1000NB IC MPU RISC 1000MHZ 360-FCCBGA 155.596MC7447ATHX1000NB IC MPU RISC 1000MHZ 360-FCCBGA 284.995MC7447AVS1333LB IC MPU RISC 1333MHZ 360-FCCLGA 310.334MC7448HX1400ND IC MPU RISC 32BIT 360-FCCBGA 451.04SPC5200CVR400 IC MPU 32BIT 400MHZ 272-PBGA 32.967MPC5200VR400 IC MPU 32BIT 400MHZ PPC 272-PBGA 37.429MC7447AHX600NB IC MPU RISC 600MHZ 360-FCCBGA 59.496MC7447AVU1000NB IC MPU RISC 32BIT 360-BGA 180.047MC7447AHX1420LB IC MPU RISC 1420MHZ 360-FCCBGA 266.336MPC184VMB IC SECURITY PROCESSOR252-MAPBGA 18.076MPC184VFB ICSECURITYPROCESSOR 252-PBGA 18.885 SPC5200CBV400BR2 IC MPU 32BIT 400MHZ 272-PBGA 21.929 SPC5200CVR400BR2 IC MPU 32BIT 400MHZ 272-PBGA 20.558 SPC5200CVR400B IC MPU 32BIT 400MHZ 272-PBGA 23.072 SPC5200CBV400B IC MPU 32BIT 500MHZ 272PBGA 21.447 SPC5200CBV400R2 IC MPU 32BIT 400MHZ 272-PBGA 33.724 MPC5200CBV266 IC MPU 32BIT 266MHZ 272-PBGA 30.793 MPC5200BV400 IC MPU 32BIT 400MHZ 272-PBGA 36.773 MPC5200CBV400 IC MPU 32BIT 400MHZ PPC 272-PBGA 34.733 SPC5200CBV400 IC MPU 32BIT 400MHZ 272-PBGA 36.464 MPC603RZT200LC IC MPU 32BIT 200MHZ PPC 255-PBGA 37.646 MPC5200CVR400 IC MPU 32BIT 400MHZ PPC 272-PBGA 43.189 MPC603RRX200LC IC MPU POWERPC 200MHZ 255-CBGA 46.972 MPC603RRX200TC IC MPU 32BIT 200MHZ 255-CBGA 55.96 MPC603RRX266LC IC MPU 32BIT 266MHZ 255-CBGA 62.125 MPC603RVG200LC MPU RISC PID7V-603E 255FCCBGA 53.339 MPC745BPX300LE MCU HIP4DP 300MHZ 255-PBGA 58.038 MPC745BVT300LE MCU HIP4DP 300MHZ 255-PBGA 52.692 MC7447AVU600NB IC MPU RISC 32BIT 360-BGA 60.897MC7448VU600ND IC MPU RISC 32BIT 360-FCCBGA 64.337 MC7448HX600ND IC MPU RISC 32BIT 360-FCCBGA 62.708 MC7410VU400LE IC MPU RISC 32BIT 360-FCCBGA 62.084 MPC7410HX400LE IC MPU 32BIT LP HP 360-CBGA 61.256 MPC755BVT300LE MCU HIP4DP 300MHZ 360-PBGA 64.266 MPC603RRX300LC IC MPU POWERPC 300MHZ 255-CBGA 63.518 MPC745CPX350LE MCU HIP4DP 350MHZ 255-PBGA 61.17 MPC745CVT350LE MCU HIP4DP 350MHZ 255-PBGA 62.097 MPC603RRX266TC IC MPU 32BIT 266MHZ 255-CBGA 80.546 MPC745BVT350LE IC MPU PPC 350MHZ 255-FCPBGA 64.39 MPC7410HX450LE IC MPU 32BIT 450MHZ 360-CBGA 65.619 MPC755BPX350LE MCU HIP4DP 350MHZ 360-PBGA 67.291HIP4DP 350MHZ 360-CBGA 78.339 MPC755BRX350LE MCUMPC755BVT350LE MCU HIP4DP 350MHZ 360-PBGA 67.291 MPC755CPX350LE MCU HIP4DP 350MHZ 360-PBGA 70.304HIP4DP 350MHZ 360-CBGA 83.36 MPC755CRX350LE MCUMPC755CVT350LE MCU HIP4DP 350MHZ 360-PBGA 68.295 MC7447AHX733NB IC MPU RISC 32BIT 360-FCCBGA 68.507 MC7447AVU733NB IC MPU RISC 32BIT 360-BGA 76.811 MPC603RVG300LC MPU RISC PID7V-603E 255FCCBGA 73.968 MPC755BRX350TE MCU HIP4DP 350MHZ 360-CBGA 100.612 MPC755CRX350TE MCU HIP4DP 350MHZ 360-CBGA 87.437 MC7447AHX867NB IC MPU RISC 32BIT 360-FCCBGA 102.499 MC7447AVU867NB IC MPU RISC 32BIT 360-BGA 86.929 MC7448VU867ND IC MPU RISC 32BIT 360-FCCBGA 96.388 MC7448HX867ND IC MPU RISC 32BIT 360-FCCBGA 109.413 MPC755CPX400LER2 MCU HIP4DP 400MHZ 360-PBGA 109.691 MPC755CVT400LE MCU HIP4DP 400MHZ 360-PBGA 108.215 MPC7410HX500LE IC MPU 32BIT 500MHZ 360-CBGA 90.963 MC7447AHX1000LB IC MPU RISC 32BIT 360-FCCBGA 87.332 MC7447AVU1000LB IC MPU RISC 32BIT 360-BGA 90.019 MC8610VT800GB MPU E600 CORE 800MHZ 783-PBGA 106.659 MC7448VU1000LD IC MPU RISC 32BIT 360-FCCBGA 112.877 MC7410TVU400LE MPU RISC 32BIT 360-CBGA 105.831 MPC7410THX400LE IC MPU 32BIT 400MHZ 360-CBGA 108.782 MPC755CPX400LE IC MPU PPC 400MHZ 360-FCPBGA 119.433 MC7448VU1000ND IC MPU RISC 32BIT 360-FCCBGA 106.477 MC7448HX1000ND IC MPU RISC 32BIT 360-FCCBGA 104.864 MC7410VU500LE IC MPU RISC 32BIT 360-FCCBGA 133.434 MC7457VG867NC IC MPU RISC 867MHZ 483FCCBGA 127.151 MPC755CRX400TE MCU HIP4DP 400MHZ 360-CBGA 117.282 KMC7447AVU1000NB IC MPU RISC 32BIT 1000MHZ 360BGA 127.658MC8610PX1066JB MPU E600 CORE 1066MHZ 783-PBGA 138.583 MC8610VT1066JB MPU E600 CORE 1066MHZ 783-PBGA 135.202 MC7457VG1000LC IC MPU RISC 1000MHZ 483FCCBGA 115.572KMC8610VT1066JB IC HOST PROCESS 1066MHZ783-PBGA 147.4MC7457RX867NC IC MPU RISC 32BIT 483FCCBGA 157.264 MC8610TPX800GB MPU E600 CORE 800MHZ 783-PBGA 139.086 MC8610TVT800GB MPU E600 CORE 800MHZ 783-PBGA 127.332 MC7457RX1000LC IC MPU RISC 32BIT 483FCCBGA 158.121MC8640HX1067NE IC DUAL CORE PROCESSOR994-CBGA 158.814MC8640VU1067NE IC MPU SGL CORE E600 1023FCCBGA 148.762 MC8640VU1000HE IC MPU SGL CORE E600 1023FCCBGA 146.455 MC7447AVS1267LB IC MPU RISC 1267MHZ 360-FCCLGA 160.372 MC7447AVU1267LB IC MPU RISC 32BIT 360-BGA 139.811 MPC7410THX450NE MCURISC1.8V 450MHZ 360-CBGA 172.341 MC7447AVS1167NB IC MPU RISC 1167MHZ 360-FCCLGA 179.704 MC7447AHX1167NB IC MPU RISC 1167MHZ 360-FCCBGA 206.783 MC7457RX1000NC IC MPU RISC 32BIT 483FCCBGA 192.185 MC8610TPX1066JB MPU E600 CORE 1066MHZ 783-PBGA 207.879 MC8610TVT1066JB MPU E600 CORE 1066MHZ 783-PBGA 190.134 MC7448THX1000ND IC MPU RISC 32BIT 360-FCCBGA 196.136 MC7448TVU1000ND MPU 128BIT 1000MHZ 360-CBGA 206.324 MC7457VG1000NC IC MPU RISC 1000MHZ 483FCCBGA 206.189MC8640DHX1000HE IC DUAL CORE PROCESSOR1023-CBGA 185.023MC8640DVU1000HE IC MPU DUAL CORE E6001023FCCBGA 219.883KMC7447AHX1167NB IC MPU RISC 32BIT 1167MHZ 360BGA 182.498 KMC7447AVS1167NB IC MPU RISC 1167MHZ 360-LGA 217.388MC8640DHX1067NE IC DUAL CORE PROCESSOR1023-CBGA 224.216MC8640DVU1067NE IC MPU DUAL CORE E6001023FCCBGA 226.984MC8640DHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 197.849MPC7410THX500LE IC MPU 32BIT 500MHZ 360-CBGA 194.278 MC7448VS1250ND IC MPU RISC 1250MHZ 360-FCCLGA 210.471 MC7448VU1250ND IC MPU RISC 32BIT 360-FCCBGA 222.164 MC7448HX1250ND IC MPU RISC 32BIT 360-FCCBGA 228.01 MC8640DTHX1000HC MPUDUALE600 1023-FCCBGA 224.553 MC8640DTHX1000HE ICDUAL CORE PROCESSOR 227.5871023-CBGAMC8610PX1333JB MPU E600 CORE 1333MHZ 783-PBGA 255.537 MC8610VT1333JB MPU E600 CORE 1333MHZ 783-PBGA 200.779MC8641DHX1000GE IC DUAL CORE PROCESSOR1023-CBGA 229.448MC7448HX1420LD IC MPU RISC 32BIT 360-FCCBGA 235.256 KMC7457RX1000NC IC MPU RISC 32BIT 1000MHZ 483BGA 221.639KMC8610VT1333JB IC HOST PROCESS 1333MHZ783-PBGA 218.896MC7457VG1267LC IC MPU RISC 1267MHZ 483FCCBGA 283.013MC8640DVU1250HE IC MPU DUAL CORE E6001023FCCBGA 246.083MC8640THX1067NE IC DUAL CORE PROCESSOR994-CBGA 260.891MC8640TVU1067NE IC MPU SGL CORE E600 1023FCCBGA 260.891MC8641DVU1250HC IC MPU DUAL E600 CORE1023FCCBGA 248.855MC8641DHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 245.35MC8641HX1000GE IC DUAL CORE PROCESSOR994-CBGA 236.369MC7448VU1600LD IC MPU RISC 32BIT 360-FCCBGA 292.719 MC7447AVU1420LB IC MPU RISC 32BIT 360-BGA 283.883MC8641HX1333JE IC DUAL CORE PROCESSOR994-CBGA 249.663MC8641VU1333JE IC MPU SGL CORE E600 1023FCCBGA 260.518MC8641DHX1000NE IC DUAL CORE PROCESSOR1023-CBGA 294.56MC7448VU1400ND IC MPU RISC 32BIT 360-FCCBGA 310.611 MC7448VS1400ND IC MPU RISC 1400MHZ 360-FCCLGA 281.029MC8640DTVU1000HE IC MPU DUAL CORE E6001023FCCBGA 299.655MC7457RX1267LC IC MPU RISC 32BIT 483FCCBGA 300.594MC8641DVU1000GE IC MPU DUAL CORE E6001023FCCBGA 263.863MC7448VU1700LD IC MPU RISC 32BIT 360-FCCBGA 258.65 MC7448VU1267ND IC MPU RISC 32BIT 360-FCCBGA 277.952 MC7448HX1700LD IC MPU RISC 32BIT 360-FCCBGA 270.231 MC7448VS1267ND IC MPU RISC 1267MHZ 360-FCCLGA 254.789 MC7448VS1700LD IC MPU RISC 1700MHZ 360-FCCLGA 270.231 MC7448HX1267ND IC MPU RISC 32BIT 360-FCCBGA 258.65 MC7447ATHX1167NB IC MPU RISC 1167MHZ 360-FCCBGA 312.568KMC7448HX1400ND IC MPU 128BIT 1400MHZ 360-FCCBGA 266.237 KMC7448VU1400ND IC MPU 128BIT 1400MHZ 360-FCCBGA 266.237 KMC7448HX1267ND IC MPU 128BIT 1267MHZ 360-FCCBGA 259.785MC8641DHX1333JE IC DUAL CORE PROCESSOR1023-CBGA 304.096MC8641DVU1333JE IC MPU DUAL CORE E6001023FCCBGA 284.35KMC7457RX1267LC IC MPU RISC 32BIT 1267MHZ 483BGA 277.987MC8641HX1000NE IC DUAL CORE PROCESSOR994-CBGA 268.363MC8641VU1000NE IC MPU SGL CORE E600 1023FCCBGA 292.759 KMC7448HX1700LD IC MPU 128BIT 1700MHZ 360-FCCBGA 343.35 KMC7448VU1267ND IC MPU RISC 32BIT 360-FCCBGA 314.738 KMC7448VU1700LD IC MPU 128BIT 1700MHZ 360-FCCBGA 314.741 MC8641DTHX1000GC MPU E600 DUAL CORE 1023-FCCBGA 331.136 MC8640DTVU1000NC MPU DUAL E600 994-FCCBGA 323.354MC8640DTHX1067NE IC MPU DUAL CORE E6001023FCCBGA 352.75MC8640DTVU1067NE IC MPU DUAL CORE E6001023FCCBGA 310.756KMC7457VG1267LC IC MPU RISC 32BIT 1267MHZ 483BGA 290.593MC8641DHX1500KE IC DUAL CORE PROCESSOR1023-CBGA 311.456MC8641DVU1500KE IC MPU DUAL CORE E6001023FCCBGA 302.682MC8641DVU1000NE IC MPU DUAL CORE E6001023FCCBGA 349.798MC8640TVU1250HE IC MPU SGL CORE E600 1023FCCBGA 414.226MC8641DTVU1000GE IC MPU DUAL CORE E6001023FCCBGA 382.876MC7448THX1400ND IC MPU RISC 32BIT 360-FCCBGA 340.119MC8641DTHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 444.578MC8641DTVU1250HE IC MPU DUAL CORE E6001023FCCBGA 391.652MC8640DTHX1250HE IC DUAL CORE PROCESSOR1023-CBGA 398.016MC8640DTVU1250HE IC MPU DUAL CORE E6001023FCCBGA 453.296KMC7448THX1400ND IC MPU 128BIT 1400MHZ 360-FCCBGA 387.828 MC8641DTHX1000NC MPU E600 DUAL CORE 1023-FCCBGA 416.985 MC8641DTVU1000NC MPU E600 DUAL CORE 1023-FCCBGA 411.425MC7448TVU1267ND IC MPU SGL E600 CORE 360-FCCBGA 426.459 MC7457TRX1000NC IC MPU RISC 32BIT 483FCCBGA 450.005MC8641DTHX1333JE IC DUAL CORE PROCESSOR1023-CBGA 429.372MC8641DTVU1333JE IC MPU DUAL CORE E6001023FCCBGA 483.044MC7448THX1267ND IC MPU RISC 32BIT 360-FCCBGA 572.2 MPC750ARX266LH IC MPU POWERPC 266MHZ 361-CBGAMPC740ARX233LH IC MPU POWERPC 233MHZ 255-CBGAMPC740ARX266LH IC MPU POWERPC 266MHZ 255-CBGAMPC106ARX83DG IC MPU PCI CONTROLLER 304CBGAMPC106ARX66CG IC MPU PCI CONTROLLER 304CBGAMPC7410RX500LE IC MPU 32BIT 500MHZ PPC 360-CBGA 115.102 MPC745BPX350LE IC MPU PPC 350MHZ 255-FCPBGAMPC755BRX300LE IC MPU 32BIT 300MHZ PPC 360-CBGAMC7447AVS1420LB IC MPU RISC 1420MHZ 360-FCCLGA 223.217 MC7447AVS600NB IC MPU RISC 600MHZ 360-FCCLGA 47.546 MC7447AVS867NB IC MPU RISC 867MHZ 360-FCCLGA 86.517MPC190VMB IC SECURITY PROCESSOR 252-MAPBGAMPC5200CVR266 IC MPU 32BIT 266MHZ PPC 272-PBGA 35.202 MPC7410VS400NE IC MPU 32BIT 400MHZ 360-FCCLGA 101.049 MPC7410VS450LE IC MPU 32BIT 450MHZ 360-FCCLGA 72.734 MPC7410VS450NE IC MPU 32BIT 450MHZ 360-FCCLGA 132.523 SPC5200CVR400R2 IC MPU 32BIT 400MHZ 272-PBGAKMC7410VS500LE IC MPU RISC 32BIT 500MHZ 360-LGA 139.893 KMC7447AHX1420LB IC MPU RISC 32BIT 1420MHZ 360BGA 270.904 KMC7447AVS1420LB IC MPU RISC 32BIT 1420MHZ 360LGA 308.529 KMC7447AVU1420LB IC MPU RISC 32BIT 1420MHZ 360BGA 314.588 KMC7448HX1400NC IC MPU 128BIT 1400MHZ 360-FCCBGA 340.751 KMC7448HX1700LC IC MPU 128BIT 1700MHZ 360-FCCBGA 368.928 KMC7448VS1400NC IC MPU 128BIT 1400MHZ 360-FCCLGAKMC7448VS1700LC IC MPU 128BIT 1700MHZ 360-FCCLGAKMC7448VU1400NC IC MPU 128BIT 1400MHZ 360-FCCBGAKMC7448VU1700LC IC MPU 128BIT 1700MHZ 360-FCCBGA 364.536 KMC7457VG1000NC IC MPU RISC 32BIT 1000MHZ 483BGA 255.456 MC7410VU400NE IC MPU RISC 32BIT 360-FCCBGA 99.683 MC7410VU450NE IC MPU RISC 32BIT 360-FCCBGA 144.047 MC7447AHX1267LB IC MPU RISC 32BIT 360-FCCBGA 159.333 MC7447AVU1167NB IC MPU RISC 32BIT 360-BGAMC7447AVU1333LB IC MPU RISC 32BIT 360-BGA 188.79 MC7448HX1000LC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1000NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1250NC IC MPU RISC 32BIT 360-FCCBGA 216.553 MC7448HX1267NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1400NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1420LC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1600LC IC MPU RISC 32BIT 360-FCCBGAMC7448HX1700LC IC MPU RISC 32BIT 360-FCCBGA 248.602 MC7448HX600NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX667NC IC MPU RISC 32BIT 360-FCCBGAMC7448HX867NC IC MPU RISC 32BIT 360-FCCBGAMC7448VS1000LC IC MPU RISC 1000MHZ 360-FCCLGAMC7448VS1000NC IC MPU RISC 1000MHZ 360-FCCLGAMC7448VS1250NC IC MPU RISC 1250MHZ 360-FCCLGA 208.224 MC7448VS1267NC IC MPU RISC 1267MHZ 360-FCCLGA 294.264 MC7448VS1400NC IC MPU RISC 1400MHZ 360-FCCLGA 274.752 MC7448VS1420LC IC MPU RISC 1420MHZ 360-FCCLGA 223.361 MC7448VS1600LC IC MPU RISC 1600MHZ 360-FCCLGA 268.785 MC7448VS1700LC IC MPU RISC 1700MHZ 360-FCCLGA 313.621 MC7448VS600NC IC MPU RISC 600MHZ 360-FCCLGAMC7448VS667NC IC MPU RISC 667MHZ 360-FCCLGAMC7448VS867NC IC MPU RISC 867MHZ 360-FCCLGAMC7448VU1000LC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1000NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1250NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1267NC IC MPU RISC 32BIT 360-FCCBGA 303.048 MC7448VU1400NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1420LC IC MPU RISC 32BIT 360-FCCBGAMC7448VU1600LC IC MPU RISC 32BIT 360-FCCBGA 293.541 MC7448VU1700LC IC MPU RISC 32BIT 360-FCCBGAMC7448VU600NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU667NC IC MPU RISC 32BIT 360-FCCBGAMC7448VU867NC IC MPU RISC 32BIT 360-FCCBGAMC7457RX733NC IC MPU RISC 32BIT 483FCCBGAMC7457VG733NC IC MPU RISC 733MHZ 483FCCBGAKMC755CVT400LE IC MPU 32BIT 400MHZ 360-FCPBGA 109.087 KMC7448VS1400ND IC MPU 128BIT 1400MHZ 360-FCCLGA 319.72 MC7448VU667ND IC MPU RISC 32BIT 360-FCCBGA 62.161 MC7448VU1600PD IC MPU RISC 32BIT 360-FCCBGA 165.017 MC7448VU1420LD IC MPU RISC 32BIT 360-FCCBGA 218.342 MC7448VS1000LD IC MPU RISC 1000MHZ 360-FCCLGA 91.754 MC7448HX667ND IC MPU RISC 32BIT 360-FCCBGA 61.321 MC7448VS1000ND IC MPU RISC 1000MHZ 360-FCCLGA 96.743MC7448VS667ND IC MPU RISC 667MHZ 360-FCCLGA 64.681 MC7448VS867ND IC MPU RISC 867MHZ 360-FCCLGA 78.527 MC7448VS600ND IC MPU RISC 600MHZ 360-FCCLGA 56.707 MC7448VS1600LD IC MPU RISC 1600MHZ 360-FCCLGA 272.14 MC7448VS1420LD IC MPU RISC 1420MHZ 360-FCCLGA 249.095 MC7448HX1600LD IC MPU RISC 32BIT 360-FCCBGA 278.86 MC7448HX1000LD IC MPU RISC 32BIT 360-FCCBGA 91.754 MPC5200VR400BR2 IC MPU 32BIT 400MHZ 272-PBGAKMC7448VS1267ND IC MPU 128BIT 1267MHZ 360-FCCLGA 304.578 KMC7448VS1700LD IC MPU 128BIT 1700MHZ 360-FCCLGA 283.716。

PowerPC

IBM推出可升级的POWER并行系统,这是第一款采用RS/6000技术,基于微处理器的超级计算机。

谢谢观看

系统接口单元SIU的功能是提供内部总线和外部总线的接口,该接口单元具有32位微处理器的几乎所有的通 用接口特性,尽管Power PC核内部总线为32位,但通过SIU可以将外部总线宽度动态地配置成8、16或32位,以 兼容数据总线宽度为8、 16或32位的外设或存储器。

SIU单元中的存储器控制器支持最多与高达8组存储器的无缝连接,每组的容量从32K字节到256M字节可变, 数据总线宽度可由4个独立的使能信号控制为8bits,16bits或32bits。支持的存储器类型包括SRAM、SSRAM、 EPOM、Flash ROM、DRAM,SDRAM等。存储器控制器为每一组存储器分别提供了可选的0到15个的等待状态以适应 不同速度的存储器。SIU也支持其它需要双时钟访问的外部SRAM和用突发方式访问的外部设备。

PowerPC处理器有 32个(32位或 64位)GPR(通用寄存器)以及诸如 PC(程序计数器,也称为 IAR/指令 寄存器或 NIP/下一指令指针)、LR(链接寄存器)、CR(条件寄存器)等各种其它寄存器。有些 PowerPC CPU 还有 32个 64位 FPR(浮点寄存器)。

PowerPC体系结构是 RISC(精简指令集计算)体系结构的一个示例。因此:

联盟运作

联盟运作

联盟三巨头,个个有来头,因此联盟采行的是松散制联盟。也就是说,联盟的目标一致,但彼此并没有隶属 关系,运作时也难以强制成员遵行。不过联盟负责制定规格、进行授权与认证等相关工作。

分工方面,摩托罗拉主司芯片设计、制造。苹果电脑则是负责操作系统,还有组装及销售。IBM不愧是信息 界的全能选手,他从上游的芯片设计、制造,到中游的系统整合、测试、操作系统,及下游的组装、销售,不但 能全面参与,向来亦是个中好手。

PowerPC 750中文资料

IBM

IBM Logo

PowerPC

AIX

PowerPC 750

Preliminary Edition (Version 2.0, 09/30/1999) This document is the preliminary edition of PowerPC 750TM SCM RISC Microprocessor for the PID8p750.

元器件交易网

PowerPC 750TM SCM RISC Microprocessor for the PID8p-750

Version 2.0 09/30/1999 IBM Microelectronics Division

元器件交易网

Notices

Processor Version Register (PVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9/30/99

Version 2.0

Datasheet

Page iii

元器件交易网

PowerPC 750 SCM RISC Microprocessor PID8p-750

Preface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Figure 1 shows a block diagram of the PID8p-750.

PowerPC简介及编程要点

PowerPC简介及编程一,PowerPC芯片PowerPC是早期Motorola和IBM联合为Apple的MAC机开发的CPU芯片,商标权同时属于IBM和Motorola,并成为他们的主导成品.IBM主要的PowerPC产品有PowerPC604s(深蓝内部的CPU),PowerPC750,PowerPCG3(1.1GHz).Motorola主要有MC和MPC系列.尽管他们产品不一样,但都采用PowerPC的内核.这些产品大都用在嵌入式系统中.Motorola的MPC860简介MPC860 PowerQUICC (Quad Integrated Communications Controller) 内部集成了微处理器和一些控制领域的常用外围组件, 特别适用于通信产品. 包括器件的适应性, 扩展能力和集成度等. MPC860 PowerQUICC集成了两个处理块.一个处理块是嵌入的PowerPC核, 另一个是通信处理模块( CPM, Communications Processor Module), 通信处理模块支持四个串行通信控制器(SCC, Serial Communication Controller), 实际上它有八个串行通道: 四个SCC,两个串行管理控制器(SMC, Serial Management Channels), 一个串行外围接口电路( SPI, Serial Peripheral Interface ) 和一个I2C( Inter-Integrated Circuit ) 接口. 由于CPM分担了嵌入式PowerPC核的外围工作任务, 这种双处理器体系结构功耗要低于传统的体系结构的处理器.单出口, 嵌入式PowerPC核32比特版本(与PowerPC结构定义完全兼容)32x32位通用寄存器(GPRs, General Purpose Registers)o4K数据Cache和4K指令Cache, 分别带有一个MMU.o存储管理单元(MMU)32-输入翻译后备缓冲器( TLBs )o32位数据,地址线∙存储控制器(八个存储体)o单线存储模块无逢接口,静态随即存取存储器(RAM), EPROM, FLASH MEMORY或DRAM等。

powerPC架构及编程

优势三:稳定性,可靠行 Powerpc架构具有很强稳定性能,高可靠性 更长的产品寿命周期(通常 10到 15年以上) 苛刻条件下,芯片具有很强健壮性,适合工业级应用 优势四:软件兼容性 软件可移植,从低端到高端器件,软件代码具有再使用能力 完整功能的组合:Ethernet, USB, PCI

优势五:芯片性能可选范围大 从低端到高端都有芯片可以选择 最低主频率50MHZ,133MHZ,266MHZ,最高可以达到几GHZ

CPM的模块结构 MPC8260高性能通信处理模块(CPM)运行频率133MHz或166MHz,包括了 MPC8260中的所有通信组件,提供3个FCC,2个MCC,4个SCC,2个SMC,1个SPI和 一个I2C,其主要特点有: (1) PowerPC和CPM可以工作在不同频率; (2) 支持串行比特率710Mbit/s @ 133MHz; (3) 并行I/O寄存器; (4) 片内24KB双口RAM; (5) 两个多通道控制器(MCC),每个支持128条全双工的64kbit/s HDLC线; (6) 虚拟DMA功能; (7) 双总线结构:1个64位PowerPC和1个32位本地总线; (8) 2个UTOPIA二级主/从端口,均支持多PHY; (9) 3个MII接口; (10) 8个TDM接口(T1/E1),2个TDM口可以无缝链接到T3/E3; (11) 内部电压2.0V,I/O电平3.3V; (12) 133MHz 功耗位2.5W.

PowerMac G5

PowerPC的特点(优势)

PowerPC 处理器是RISC嵌入式应用的理想基础平台。从一开始,革命性的可扩展 PowerPC 体系结构就是为满足解决方案(从台式机CPU,到高性能、高度集成的嵌入式 MPU)的不同需求设计的。PowerPC 处理器提供极具吸引力的性价比、扩大的运行温度 范围、多处理功能、高集成度,它的指令在整个产品线中兼容,并提供最广泛的开发 工具选择。 PowerPC处理器优势 优势一:MIPS/MHz 性能 选择Power架构的原因是因为它每兆赫兹的MIPS 比Renesas SH 和 ARM高. ARM 大概是 1.1 MIPS/MHz SH4A 大概是 1.8MIPS/MHz Power Architecture 是大于2.0MIPS/MHz MPC8349E : 1260 MIPS @ 667 MHz MPC8548E:3065 MIPS at 1333 MHz 优势二:功耗 PowerQUICC最大功耗范围:2 –8瓦 设备能可靠稳定运行在: -40℃-105℃ 随着温度的升高,性能不会改变

单片机种类比较

引言概述:单片机是一种集成电路,可以用来控制其他电子设备的微型计算机。

在现代电子设备中,单片机广泛应用于各个领域,如汽车、家电、通信、医疗等。

对于单片机的选择,不同的种类有不同的特点和适用范围。

本文将对几种常见的单片机进行比较,帮助读者了解每种单片机的优劣势,以便在实际应用中做出明智的选择。

正文内容:1.8位单片机1.1.8051系列单片机1.1.1.架构简介1.1.2.特点与应用范围1.1.3.优势1.1.4.劣势1.1.5.相关开发工具和资源1.2.AVR单片机1.2.1.架构简介1.2.2.特点与应用范围1.2.3.优势1.2.4.劣势1.3.PIC单片机1.3.1.架构简介1.3.2.特点与应用范围1.3.3.优势1.3.4.劣势1.3.5.相关开发工具和资源2.16位单片机2.1.PIC24单片机2.1.1.架构简介2.1.2.特点与应用范围2.1.3.优势2.1.4.劣势2.1.5.相关开发工具和资源2.2.MSP430单片机2.2.1.架构简介2.2.2.特点与应用范围2.2.3.优势2.2.4.劣势2.3.其他16位单片机2.3.1.架构简介2.3.2.特点与应用范围2.3.3.优势2.3.4.劣势2.3.5.相关开发工具和资源3.32位单片机3.1.ARM系列单片机3.1.1.架构简介3.1.2.特点与应用范围3.1.3.优势3.1.4.劣势3.1.5.相关开发工具和资源3.2.PowerPC系列单片机3.2.1.架构简介3.2.2.特点与应用范围3.2.3.优势3.2.4.劣势3.3.其他32位单片机3.3.1.架构简介3.3.2.特点与应用范围3.3.3.优势3.3.4.劣势3.3.5.相关开发工具和资源4.特殊用途单片机4.1.FPGA单片机4.1.1.架构简介4.1.2.特点与应用范围4.1.3.优势4.1.4.劣势4.1.5.相关开发工具和资源4.2.DSP单片机4.2.1.架构简介4.2.2.特点与应用范围4.2.3.优势4.2.4.劣势4.3.其他特殊用途单片机4.3.1.架构简介4.3.2.特点与应用范围4.3.3.优势4.3.4.劣势4.3.5.相关开发工具和资源5.单片机选择的考虑因素5.1.项目需求5.2.性能要求5.3.软硬件开发成本5.4.技术支持与社区资源5.5.市场可用性与供应链稳定性总结:本文对多种常见的单片机进行了比较,包括8位、16位、32位和特殊用途单片机。

PowerPC 440中文资料

The PowerPC® 440 Core A high-performance, superscalar processor core for embedded applicationsIBM Microelectronics DivisionResearch Triangle Park, NC09/21/1999OverviewThe PowerPC 440 CPU core is the latest addition to IBM’s family of 32-bit RISC PowerPC embedded processor cores. The PPC440’s high-speed, superscalar design and Book E Enhanced PowerPC Architecture™ put it at the leading edge for high performance system-on-a-chip (SOC) designs. The PPC440 core marries the performance and features of standalone microprocessors with the flexibility, low power, and modularity of embedded CPU cores.Target ApplicationsThe PPC440 Core is primarily designed for applications in which maximum performance and extensive peripheral integration are the critical selection criteria.Target market segments for the PPC440 core include:•Consumer applications including digital cameras, video games, set-top boxes, and internet appliances •Office automation products such as laser printers, thin-client systems, and sub-notebooks •Storage and networking products such as RAID controllers, routers, ATM switches, cellular basestations, and network cardsFeatures•2-way superscalar design•Out-of-order issue, execution, and completion•Dynamic branch prediction•Single-cycle branch latency•Three execution pipelines•Single-cycle throughput on 32x32 multiply•24 DSP operations (16x16+32->32, MAC with single-cycle throughput)•Real-time non-invasive instruction traceTypical ApplicationA typical system on a chip design with the PPC440 Core uses the CoreConnect TM bus structure for system level communication. High bandwidth peripherals and the PPC440 core communicate with one another over the processor local bus (PLB). Less demanding peripherals share the on-chip peripheral bus (OPB) and communicate to the PLB through the OPB Bridge. The PLB and OPB provide common interfaces for peripherals and enable quick turnaround, custom solutions for high volume applications.F igure 1 shows an example PPC440 Core-based system on a chip, illustrating the two-level bus structure and modular core-based design.Figure 1. Example PPC440 Core + ASIC SpecificationsPerformance (Dhrystone 2.1)1000 MIPS @ 555MHz (est.), Nominal silicon, 1.8V, 55°C 720 MIPS @ 400MHz (est.), Slow silicon, 1.65V, 85°CFrequency0 – 400MHz , Slow silicon, 1.65V, 85°C555MHz nominalPower Dissipation 2.5mW / MHz @ 1.8V (est.), hard core with 32KI / 32KD cachesArchitecture32-bit PowerPC Book E compliant, application code compatible withall PowerPC processorsDie Size 4.0 mm2 for CPU only (est.)Caches0-64KB, 32-way to 128-way associativeTechnology0.18 µm CMOS copper technology0.12 µm L eff , 4 levels of metalPower Supply 1.8 VoltsTransistors 5.5M, hard core with 32KI / 32KD cachesOperating Range-40°C to 125°C, 1.6V to 1.9VData Bandwidth Up to 6.4 GB/sec via three 128-bit, 200MHz CoreConnect businterfacesTable 1- 440 CPU Core SpecificationsEmbedded Design SupportThe PPC440 Core, as a member of the PowerPC 400 Family, is supported by the IBM PowerPC Embedded Tools TM program, in which over 80 third party vendors have combined with IBM to provide a complete tools solution. Development tools for the PPC440 include C/C++ compilers, debuggers, bus functional models, hardware/software co-simulation environments, and real-time operating systems. As part of the tools program, IBM maintains a complete set of development tools by offering the High C/C++ Compiler, RISCWatch TM debugger with RISCTrace TM trace interface, VHDL and Verilog simulation models and a PPC440 Core Superstructure development kit.PPC440 CPU Core OrganizationPPC440 CPUThe PPC440 CPU operates on instructions in a dual issue, seven stage pipeline, capable of dispatching two instructions per clock to multiple execution units and to optional Auxiliary Processor Units (APUs). The PPC440 core is shown in Figure 2.Figure 2 - PPC440 Core Block DiagramThe pipeline contains the following stages, as shown in Figure 3:1.IFTH – Fetch instructions from instruction cache2.PDCD – Pre-decode; partial instruction decode3.DISS – Decode/Issue; final decode and issue to units4.RACC – Register Access; read from multi-ported General Purpose Register (GPR) file5.EXE1/AGEN – Execute stage 1; complete simple arithmetics, generate load/store address6.EXE2/CRD – Execute stage 2; multiplex in results from units in preparation for writing into GPRfile, Data Cache access7.WB – Writeback; write results into GPR file from integer operation or load operationFigure 3 - PPC440 CPU PipelineInstruction Fetch and Pre-decodeDuring the Instruction Fetch stage (IFTH), an entire cache line (eight words) is read into the instruction cache line read buffer. From there, the next two instructions in the pre-decode buffers PDCD0 and PDCD1 during the PDCD stage. The instruction cache is virtually indexed and tagged, and translation is performed in parallel with the cache access.Branch UnitThe PPC440 uses a Branch History Table (BHT) to maintain dynamic branch prediction of conditional branches. To perform dynamic branch prediction, a 2-bit counter in the BHT is used to decide whether prediction should agree or disagree with the normal PowerPC static branch prediction. The counter counts up if branch determination agrees, and down if it disagrees. Once the counter saturates, it can only count away from saturation. Therefore, four valid states exist: “Strongly agree”, “Agree”, “Disagree”, and “Strongly disagree”. By agreeing or disagreeing with static branch prediction, different branches can use the same counter in the BHT and have opposite static predictions, without the machine necessarily mispredicting a branch.The Branch Target Address Cache (BTAC) is used to predict branches and deliver their target addresses before the instruction cache can deliver the same data. It is accessed during IFTH, whereas normal branch prediction would not occur until PDCD, and therefore avoids a one cycle penalty. The BTAC is made up of an odd and even BTAC containing eight entries each. Only unconditional branches and bdnzinstructions are stored, which gives a significant performance boost while keeping the design straightforward.Decode and IssueThe four-entry decode queue accepts up to two instructions per clock submitted from the pre-decode buffers. Instructions always enter the lowest empty or emptying queue position, behind any instructions already in the queue. Therefore, the queue fills from the bottom up, instructions stay in order, and no bubbles exist in the queue. A significant portion of decode is performed in the lowest two positions (DISS0 and DISS1). Up to two instructions exit the queue based on the instructions’ decode and pipeline availability, and are issued to the RACC stage. DISS1 can issue out of order with respect to DISS0. Register AccessConceptually, the GPR file consists of thirty-two, 32-bit general purpose registers. It is implemented as two 6-port arrays, (one array for LRACC, one for IRACC) each with thirty-two, 32-bit registers containing three write ports and three read ports. On all GPR updating instructions, the appropriate GPR write ports will be written in order to keep the contents of the files the same. On GPR reads, however, the GPR read ports are dedicated to instructions that are dispatched to a RACC’s associated pipe(s). Execution PipelinesThe PPC440 contains three execution pipes: a load/store pipe (“L-pipe”), a simple integer pipe (“J-pipe”), and a complex integer pipe (“I-pipe”). The L-pipe and J-pipe instructions are dispatched from the LRACC; I-pipe instructions are dispatched from IRACC. The three pipes together perform all 32-bit PowerPC integer instructions in hardware compliant with the PowerPC Book E specification. Table 2 lists the rules for dispatching to each of the three execution pipes.L-pipe only Loads/stores1, cache instructions, mbar, msyncI-pipe or J-pipe2Add, addi, addis, and, andc, cntlzw, eqv, extsb, extsh, nand, neg, nor, or, orc, ori, oris, xori, xoris, rlwimi, rlwinm, rlwnm, slw, srw, subfI-pipe only Branches, multiplies, divides, move to/from DCR/SPR, indirect XER updates,indirect LR/CTR updates, indirect CR updates, CR-logicals, MAC instructions,mcrf, mcrxr, mtcrf, mfcr, compares, dlmzb, isync, rfi, rfci, sc, wrtee, wrteei,mtmsr, mfmsr, trapsTable 2 – Rules for Instruction IssueThe MAC unit is an auxiliary processor unit (APU) which adds 24 operations to the PPC440 instruction set. MAC instructions operate on either signed or unsigned 16 bit operands and accumulate the results in a 32-bit GPR. All MAC unit instructions have single cycle throughput. The MAC unit is contained within the I-pipe.1 The stwcx. instruction goes down both the L-pipe as well as the I-pipe, in order to update the CR.2 Instructions which update the CR or XER are not issued to the J-pipe.Instruction and Data CachesProcessor Local Bus (PLB) Memory AccessThe PPC440 has three independent 128-bit Processor Local Bus (PLB) master interfaces, one for instruction fetches, one for data reads, and a third for data writes. Memory accesses are performed through the PLB interfaces to/from the instruction cache (I-Cache) or data cache (D-Cache) units. Having three independent bus interfaces for the cache units provides maximum flexibility for designs to optimize system throughput. Memory accesses (loads/stores) which hit in the cache achieve single-cycle throughput.Cache ConfigurationThe PPC440 has separate instruction and data caches with 8 word (32 byte) cache lines. Instruction and data cache sizes are factory-configurable to any combination of 0KB, 8KB, 16KB, 32KB, or 64KB cache sizes. Configurable cache sizes provide designers with a parameter for optimizing the PPC440 to a desired price-performance for a particular application. The caches are highly associative, with associativity varying with cache size as shown in Table 3. High associativity enables advanced cache functions such as locking and transient memory regions (see “Cache Partitioning” below).Cache Size Ways8 KB3216KB6432KB6464KB128Table 3 – Number of Ways for Different PPC440 Cache SizesThe cache arrays are non-blocking. Non-blocking caches allow the PPC440 to overlap execution ofload/store instructions while instruction fetches take place over the PLB. The caches, therefore, continue supplying data and instructions without interruption to the pipeline. The PPC440 replaces cache lines according to a round-robin replacement policy.The initial PPC440A4 core offering will include a 32KB instruction cache and 32KB data cache. These caches are physically constructed using two, 16KB CAMRAM macros, each consisting of 8, 2KB sub-banks (or “sets”). This organization facilities low-power operation and fast hit/miss determination. Cache PartitioningThe PPC440 caches have the ability to be separated into “normal”, “transient”, and “locked” regions. Normal regions are what is traditionally thought of regarding cache replacement. Transient regions are used for data that is used temporarily and then not needed again, such as the data in a particular JPEG image. A separate transient region avoids castouts of more commonly accessed code in the normal region. The locked region is for code that is not to be cast out of the cache, and is the resulting region not included in the normal and transient regions. The regions are set via “victim” ceiling and floor pointers, as shown in Figure 4. Figure 4 shows two examples of cache partitioning, the left side shows separate transient and normal regions, and the right side shows part of the normal region overlapping with the transient region. The normal ceiling is defined as the top of the cache.Figure 4 – Two Examples of Cache PartitioningI-Cache Speculative Pre-fetchingThe I-Cache utilizes a programmable speculative pre-fetch mechanism to enhance performance. Software can enable up to three additional lines to be speculatively pre-fetched, using a burst protocol, upon any instruction cache miss. When this mode is enabled, the I-Cache controller will automatically inspect the I-Cache on a miss to see if any of up to the next three lines are also misses. If so, the hardware will present a burst request to the PLB immediately after the original line fill request. This speculative burst request takes advantage of the throughput capability of standard memory architectures such as SDRAM and brings in anticipated subsequent instructions after a miss. Furthermore, if the instruction stream branches away from the lines which are being speculatively filled, the burst request which is filling the speculative lines can be abandoned in the middle, and a new fill request at the branch target location immediately initiated. There is a programmable "threshold" to determine when to abandon a speculative line fill that may have been in progress at the time of a branch redirection. This threshold designates how many doublewords of the speculative cache line must be received to not abandon a current line fill. In this fashion, the speculative pre-fetch mechanism can be carefully tailored to provide optimum performance for specific applications and memory subsystems.D-Cache Line FillsThe D-Cache contains three line fill buffers and can queue up to four load misses to three separate cache lines. The PPC440 will then execute past these load misses, until the queue is full or the pipes are held waiting for a load value. The D-Cache controller places the target word on the bypass path as the fill buffer captures data words off the PLB. Additional requests of the cache line held in the fill buffer are also forwarded directly to the operand registers in the execute unit.D-Cache Non-cacheable Store GatheringThe D-Cache “gathers” up to 16 bytes for non-cacheable, write-through, and w/o allocate stores, and will burst the quadword to the PLB for fast writes to non-cacheable memory.D-Cache Write-Back and Write-Through ModesThe D-Cache supports write-back or write-through mode. In write-back mode, store hits are written to the cache and not to main memory. Main memory is later modified if and when the line is flushed from the cache. In write-through mode, the data cache controller writes main memory for store misses as well asstore hits; every store operation generates a PLB write request. (Although write-through requests to non-cacheable memory can be gathered as previously mentioned).D-Cache Store AllocationThe D-Cache can be programmed whether or not to allocate a line on a D-Cache store miss. Write-on-allocate is enabled by default. In this mode, a store miss to cacheable memory forces the data cache controller to allocate a line in the data cache and generate a line fill. In contrast, when “without allocate”is enabled, a store miss to cacheable memory will not allocate a line data cache and will simply write the data to memory.Big Endian and Little Endian SupportThe PPC440 supports big endian or little endian byte ordering for instructions and data stored in external memory. The PowerPC Book E architecture is endian neutral; each page in memory can be configured for big or little endian byte ordering via a storage attribute contained in the TLB entry for that region. Strapping signals on the PPC440 core initialize the beginning TLB entry’s endian attribute, so thePPC440 can boot from little or big endian memory.Memory Management Unit (MMU)The MMU supports multiple page sizes as well as a variety of storage protection attributes and access control options. Multiple page sizes improve TLB efficiency and minimize the number of TLB misses. The PPC440 gives programmers the flexibility to have any combination of the following eight possible page sizes in the translation look-aside buffer (TLB) simultaneously: 1KB, 4KB, 16KB, 64KB, 256KB,1MB, 16MB and 256MB. Having an extremely large page size allows users to define system memory with a minimal number of TLB entries, thereby simplifying TLB allocation and replacement. Small page sizes prevent the wasting of memory when allocating small areas of data.Each page of memory is accompanied by a set of storage attributes. These attributes include cacheability, write through/write back mode, big/little endian, guarded and four user-defined attributes. The user-defined attributes can be used to mark a memory page with an application-specific meaning. The guarded attribute controls speculative accesses. The big/little endian attribute marks a memory page as having big or little endian byte ordering. Write through/write back specifies whether memory is updated in addition to the cache during store operations.Two of the user-defined storage attributes can be programmed for special functions inside the core. One can be enabled to designate normal or transient cache regions. Another can be enabled to control whether or not store misses allocate a line in the D-Cache.Access control bits in the TLB entries enable system software to control read, write, and execute access for programs in both user and supervisor states.The MMU includes a 64-entry fully-associative unified TLB to reduce the overhead of address translation. Contention for the main TLB between data address and instruction address translation is minimized through the use of a four-entry instruction shadow TLB (ITLB) and an eight-entry data shadow TLB (DTLB). The ITLB and DTLB shadow the most recently used entries in the unified TLB. The MMU manages the replacement strategy of the ITLB and DTLB leaving the unified TLB to software control. Real-time operating systems are free to implement their own replacement algorithm for the unified TLB.Interrupt Handling LogicThe PPC440 services exceptions generated by error conditions, the internal timer facilities, debug events, and the external interrupt controller (EIC) interface. Altogether, there are sixteen different interrupt types supported.Interrupts are divided into two classes, critical and non-critical. Each class of interrupt has its own pair of save/restore registers for holding the program counter and machine state. Separate save/restore registers allow the PPC440 to quickly handle critical interrupts even within a non-critical interrupt handler. When an interrupt is taken, the PPC440 automatically writes the program counter and machine state to save/restore register SRR0 and SRR1 respectively for non-critical interrupts, or CSRR0 and CSRR1 respectively for critical interrupts. The machine status and program counter are automatically restored at the end of an exception handler when the return from interrupt (rfi) or return from critical interrupt (rfci) instruction is executed.TimersThe PPC440 contains a 64-bit time base and three timers: the Decrementer (DEC), the Fixed Interval Timer (FIT), and the WatchDog Timer (WDT). The time base counter increments synchronously with the CPU clock or an external clock source. The three timers are synchronous with the time base.The DEC is a 32-bit register that decrements at the time base increment rate. The user loads the DEC register with a value to create the desired delay. When the register reaches zero, the timer stops decrementing and generates a decrementer interrupt. Optionally, the DEC can be programmed to auto-reload the value last written to the DEC auto-reload register, after which the DEC continues to decrement.The FIT generates periodic interrupts based on one of four selectable bits in the time base. When the selected bit changes from 0 to 1, the PPC440 generates a FIT exception.The watchdog timer provides a periodic critical-class interrupt based on a selected bit in the time base. This interrupt can be used for system error recovery in the event of software or system lockups. Users may select one of four time periods for the interval and the type of reset generated if the watchdog timer expires twice without an intervening clear from software. If enabled, the watchdog timer generates a reset unless an exception handler updates the watchdog timer status bit before the timer has completed two of the selected timer intervals.Debug LogicAll architected resources on the PPC440 can be accessed through the debug logic. Upon a debug event, the PPC440 provides debug information to an external debug tool. Three different types of tools are supported depending on the debug mode: ROM Monitors, JTAG debuggers and instruction trace tools. Internal Debug ModeIn internal debug mode, a debug event enables exception-handling software at a dedicated interrupt vector to take over the PPC440 and communicate with a debug tool. Exception-handling software has read-write access to all registers and can set hardware or software breakpoints. ROM monitors typically use the internal debug mode.External Debug ModeIn external debug mode, the PPC440 enters stop state (i.e., stops instruction execution) when a debug event occurs. This mode offers a debug tool non-invasive read-write access to all registers in the PPC440 via the JTAG interface. Once the PPC440 is in stop state, the debug tool can start the PPC440, step an instruction, freeze the timers or set hardware or software break points. In addition to PPC440 control, the debug logic is capable of writing instructions into the instruction cache, eliminating the need for external memory during initial board bring up.Debug Wait ModeDebug wait mode offers the same functionality as external debug mode with one difference; in debug wait mode, the PPC440 will respond to interrupts and temporarily leave stop state to service them before returning to debug wait mode. In external debug mode, by contrast, interrupts are disabled while in stop state. Debug wait mode is particularly useful when debugging real-time control systems.Real-Time Trace Debug ModeIn real-time trace debug mode, instruction trace information is continuously broadcast to the trace port. When a debug event occurs, an external debug tool saves instruction trace information before and after the event. The number of traced instructions depends only on the memory buffer depth of the trace tool. Debug EventsDebug events signal the debug logic to either stop the PPC440, put the PPC440 in debug wait state, cause a debug exception, or save instruction trace information, depending on the debug mode. Table 4 on the following page lists the possible debug events and their description.Debug Event DescriptionBranch Taken A Branch Taken debug event occurs prior to the execution ofa taken branch instruction.Instruction Completion The Instruction Completion debug event occurs after thecompletion of any instruction.Return from Interrupt The Return From Interrupt debug event occurs after thecompletion of an rfi or rfci instruction.Interrupt The Interrupt debug event occurs after an interrupt is taken. Trap The Trap debug event occurs prior to the execution of a trapinstruction, where the trap condition is met.Instruction Address Compare (IAC)The IAC debug event occurs prior to the execution of aninstruction at an address that matches the contents of one offour IAC registers (IAC1, IAC2, IAC3, and IAC4).Alternatively, the registers can be combined to cause an IACdebug event prior to the execution of an instruction at anaddress contained in one of the following ranges as specifiedby the four IAC registers:IAC1 <= range < IAC2 (inclusive),IAC3 <= range < IAC4 (inclusive),range low < IAC1 < IAC2 <= range high (exclusive), orrange low < IAC3 < IAC4 <= range high (exclusive).Data Address Compare (DAC)The DAC debug event occurs prior to the execution of aninstruction that accesses a data address matching the contentsof one of the two DAC registers (DAC1 and DAC2).Alternatively, the registers can be combined to cause a DACdebug event occurs prior to the execution of an instructionthat accesses a data address within one of the followingranges specified by the two DAC registers:DAC1 <= range < DAC2 (inclusive), orrange low < DAC1 < DAC2 <= range high (exclusive). Data Value Compare (DVC)The Data Value Compare debug event occurs prior to theexecution of an instruction that accesses a data addressmatching one of the two DAC registers (or within a DACrange) and containing a particular data value as specified byone of the two DVC registers. The DVC debug event mayoccur when a selected data byte, half-word or word matchesthe corresponding element in DVC1 or DVC2. Unconditional Event An unconditional debug event is set by a debug tool throughthe JTAG port or by ASIC logic external to the PPC440.Table 4 - Debug EventsPower ManagementThe PPC440 core, in keeping with the IBM PowerPC 400 family tradition, utilizes aggressive power management techniques for minimizing power. The PPC440 utilizes three key techniques: redundant operand registers, half-cycle latch stabilization, and dynamic clock gating.Redundant Operand RegistersRedundant operand registers are used at various pipeline stages for feeding operands to each of the execution units. This saves power by preventing unused units from seeing the operand values being used by other units and improves performance by reducing loading and wire length in critical stages.Half-Cycle Latch StabilizationHalf-cycle stabilization latches minimize the propagation of glitches to downstream logic. This is easily employed since the PPC440 core contains a master/slave latch arrangement for scan-test purposes. Therefore, a master-only latch is simply needed in the logic path that is switching in the first half of a cycle. For example, if the select lines for a mux are being determined in the first half of a cycle, then by putting a master-only latch on these select lines before delivering them to the mux, the mux outputs are prevented from glitching while the select lines are being determined. Conversely, if the data lines are unstable in the first half of a cycle, a stabilization latch may be used on the data inputs, while leaving the select lines alone.Dynamic Clock GatingThe most important feature of the PPC440’s dynamic power management is the extensive use of clock gating. Given the PPC440’s master/slave latch organization, there are two possible gates that can be used. The relationship between them, and their relative affect on the clock splitter and hence power are shown in Figure 5.Figure 5 - PPC440 Clock GatingIn this figure, the early gate blocks the phase 1 clock and prevents the master latch from loading, while the late gate blocks the phase 2 clock and prevents the slave latch from loading. As illustrated in the simplified block diagram of the clock splitter, the early gate must arrive by mid-cycle -- which is when the system clock falls. If the gate is activated by this point, then the net effect is that internal to the clock splitter the fall on the system clock is never observed, and both the phase 1 and the phase 2 clock splitteroutputs remain stable, preventing any downstream master latches from loading, and hence their associated slave latches will not change either. This affords the maximum power savings, with the downstream logic dissipating no power other than leakage, and the clock splitter itself using almost zero power.In the event that the gate for a given latch cannot be determined by mid-cycle, the late gate can be used, which does not prevent the system clock fall and consequent phase 1 clock rise, but does prevent the corresponding next phase 2 clock rise. This does not save as much power, but the timing is much more relaxed and the power savings are still considerable.。

32位PowerPC常用指令集总结材料

32位PowerPC常用指令集总结第一部分PowerPC 精简指令集计算机(RISC)简介PowerPC 体系结构是一种精减指令集计算机(Reduced Instruction Set Computer,RISC)体系结构,定义了200 多条指令。

PowerPC 之所以是RISC,原因在于大部分指令在一个单一的周期内执行,而且通常只执行一个单一的操作(比如将内存加载到寄存器,或者将寄存器数据存储到内存)。

PowerPC 体系结构分为三个级别(或者说是“book”)。

通过对体系结构以这种方式进行划分,为实现可以选择价格/性能比平衡的复杂性级别留出了空间,同时还保持了实现间的代码兼容性。

Book I. 用户指令集体系结构(Power ISA User Instruction Set Architecture)定义了通用于所有PowerPC 实现的用户指令和寄存器的基本集合。

这些是非特权指令,为大多数程序所用。

Book II. 虚拟环境体系结构(Power ISA Virtual Environment Architecture)定义了常规应用软件要求之外的附加的用户级功能,比如高速缓存管理、原子操作和用户级计时器支持。

虽然这些操作也是非特权的,但是程序通常还是通过操作系统调用来访问这些函数。

Book III. 操作环境体系结构(Power ISA Operating Environment Architecture)定义了操作系统级需要和使用的操作。

其中包括用于内存管理、异常向量处理、特权寄存器访问、特权计时器访问的函数。

Book III 中详细说明了对各种系统服务和功能的直接硬件支持。

由于我目前手上的开发板是基于e600内核,所以我在学习PowerPC指令集的过程中,顺便总结了e600内核常用的指令集,如果大家发现我总结的指令集有错误或者不准确的地方,欢迎留言指出来,O(∩_∩)O~第二部分e600指令集飞思卡尔的e600内核实现了booke内核构架中64位指令集的中的32位指令(即在e600的32位寄存器中,第0位相当于booke中的64寄存器的第32位,第31位相当于booke中64寄存器的第63位),E600内核采用大端编码方式,指令的第0位是MSB(Most Significant Bit)位,第31位是LSB(Least Significant Bit)。

PowerPC_学习

Techtalk of Power PC历史1:POWERPOWER 是 Power Optimization With Enhanced RISC 的缩写,是 IBM 的很多服务器、工作站和超级计算机的主要处理器。

POWER 芯片起源于 801 CPU,是第二代RISC 处理器。

POWER 芯片在 1990 年被 RS 或 RISC System/6000 UNIX 工作站(现在称为 eServer 和 pSeries)采用,POWER 的产品有 POWER1、POWER2、POWER3,现在最高端的是 POWER4。

POWER4 处理器是目前单个芯片中性能最好的芯片。

801的设计非常简单。

但是由于所有的指令都必须在一个时钟周期内完成,因此其浮点运算和超量计算(并行处理)能力很差。

POWER 体系结构就着重于解决这个问题。

POWER 芯片采用了 100 多条指令,是非常优秀的一个 RISC 体系结构。

以下对每种 POWER 芯片简单进行一下介绍;更详细的内容请参考参考资料中的链接。

∙POWER1发布于 1990 年:每个芯片中集成了 800,000 个晶体管。

与当时其他的 RISC 处理器不同,POWER1 进行了功能划分,这为这种功能强大的芯片赋予了超量计算的能力。

它还有单独的浮点寄存器,可以适应从低端到高端的 UNIX 工作站。

最初的 POWER1 芯片实际上是在一个主板上的几个芯片;后来很快就变成一个 RSC(RISC 单一芯片),其中集成了100 多万个晶体管。

POWER1 微处理器的 RSC 实现被火星探险任务用作中央处理器,它也是后来 PowerPC 产品线的先驱。

∙POWER2发布于 1993 年,一直使用到 1998 年:每个芯片中集成了 1500 万个晶体管。

POWER2 芯片中新加了第二个浮点处理单元(FPU)和更多缓存。

PSSC 超级芯片是 POWER2 这种 8 芯片体系结构的一种单片实现,使用这种芯片配置的一个 32 节点的 IBM 深蓝超级计算机在 1997 年击败了国际象棋冠军Garry Kasparov。

PowerPC产品介绍

飞思卡尔半导体的PowerPC 处理器是RISC 嵌入式应用的理想基础平台。PowerPC 芯片凭借其出色的性能和高度整合和技术先进特性在网络通信应用, 工业控制应用,家用数字化,网络存储领域,军工领域和电力系统控制等都具有非常广泛的应用。北京国基科技股份有限公司长期致力于基与Freescale PowerPC处理器产品的研发与定制设计,拥有雄厚的研发实力。国基科技推出的PowerPC 全系列开发板,提供全面技术支持,竭诚为广大客户服务。以下是 国基科技PowerPC 开发板硬件介绍。如需了解更详细资料,欢迎登陆:

1 x 10/100/1000M 4-port 10/100 Ethernet switch

1 x PCI 2 x miniPCI

1 x PCI 2 x miniPCI

4 x SATA (可接四个硬盘)

2 x USB 2.0 4 x SATA (可接四个硬盘)

1 x 10/100/1000M 4-port 10/100 Ethernet switch

-MPC8541E 开发套件 -MPC8560 开发套件 -MPC8572E 开发套件(高性能,双核)

PowerPC 载板系列

- Type-N 载板-网络应用 -Type-A 载板-ATCA 或UTCA 系统 - Type-S 载板-网络存储

PowerPC 开发工具 - TRACE32 仿真器 Wind River ICE2 - CodeWarrior for PowerPC 开发环境软件

667HZ 1260MIPS @667MHZ

256M DDR2

8M NOR Flash 32MNAND Flash 256Kbits E2PROM SD 卡(SD 控制器)

嵌入式PowerPC处理器的发展概述

嵌入式PowerPC处理器的发展概述作者:王树争来源:《中国科技纵横》2017年第12期摘要:本文概述了Freescale的PowerPC处理器的发展,按照PowerPC处理器产品出现的先后,以及在工业控制、航空、航天等应用领域的应用,对PowerPC处理器进行了分类介绍。

关键词:嵌入式处理器;PowerPC;嵌入式系统中图分类号:TN911.7 文献标识码:A 文章编号:1671-2064(2017)12-0013-021 概述嵌入式系统的市场日益广阔,嵌入式处理器作为嵌入式系统的关键部件,得到广泛应用。

PowerPC处理器在嵌入式处理器中占据重要地位,PowerPC处理器架构的特点是方便灵活,可伸缩性好。

PowerPC处理器种类很多,在消费类电子产品、大型通信设备、高端的工作站、服务器、桌面计算机系统都有应用,应用范围极其广泛。

本文着重介绍PowerPC处理器的发展。

PowerPC处理器是指使用PowerPC指令集的处理器。

PowerPC指令集为RISC指令集,它排除了CISC指令集处理器中采用的两级微码控制方式,而是在硬件中直接执行一组精选的简单指令和优化的编译程序,以便有效的利用CPU资源来提高程序的运行速度。

PowerPC是Performance Optimized With Enhanced RISC-Performance Computing的缩写,简称PowerPC为PPC。

PowerPC系列处理器的基本设计源自IBM公司的POWER架构,但进行了大量的改动。

例如,POWER系列是大尾段设计,而Power PC系列是open-endian设计;另外,Power PC提供更强的多线程处理能力和浮点处理能力。

总体而言,Power PC和POWER的CPU并无太大的差别,Power PC保留了POWER的绝大部分指令,许多应用程序只需重新编译,就可以分别运行在两个平台上。

IBM、AMCC、Freescale、LSI等公司的PowerPC处理器占主流地位。

飞思卡尔单片机调试接口说明

飞思卡尔单片机调试接口说明1、监控模式(Monitor Mode):飞思卡尔HC(9)08系列单片机应用此种调试方式。

又称MON08。

其主要特点是单线双向异步串行通讯。

为了进入监控模式,在单片机上电复位时,该通讯线要处于高电平状态。

除了该通讯线外,还有一些辅助信号线要处于特定的电位状态。

如果单片机的复位矢量不是处于擦除状态(被烧录过,不是$FFFF),则复位信号线或中断信号线需要特定的监控高电压。

有些单片机还需要外加时钟信号以进入监控状态。

起初工业界并没有一定的接口引脚标准,在摩托罗拉在线模拟器(ICS)的基础上,PEMICRO其中NC表示不接任何信号。

MON4和MON5中的一个引脚为通讯线(MR8除外),另一个和MON6,MON7,MON8为辅助信号线,其使用与否和电平状态视芯片而定。

2、6针背景调试模式(BDM):飞思卡尔HC9S08,HC(S)12(X),RS08等系列单片机应用此种调试方式。

其主要特点是单线双向同步串行通讯。

单片机进入背景调试状态比较简单,在单片机复位时只要通讯线在一定时间内处于低电平即可。

但是背景调试模式对通讯信号的要求比较高,其通讯速度、每个命令的执行时间与单片机总线频率有着直接联系。

注意2:引脚4为RST复位信号,用户应为该信号提供上拉电阻。

注意3:RS08在对闪存进行擦除或烧录时要求引脚4提供12伏稳定电压。

3、10针背景调试模式(BDM):飞思卡尔HC16,68xxx系列单片机应用此种调试方式。

其主要特点是双向同步串行通讯。

同步串行通讯时钟由仿真器提供,并与单片机总线时钟同步。

飞思卡尔对10针BDM接口引脚定义:起初摩托罗拉定义了8针BDM接口引脚,与以上定义的后8针相同。

4、10针背景调试模式(BDM):飞思卡尔PowerPC MPC8xx和MPC5xx系列单片机应用此种调试方式。

其主要特点是双向同步串行通讯。

同步串行通讯时钟由仿真器提供,并与单片机总线时钟同步。

PowerPC_PPC培训教材

PPC培训教材编写:校核:二〇〇七年四月十一日目录第1章PPC体系结构 (1)1.1.MPC8247基本模块 (1)1.2.数据怎样流动? (2)1.3.P OWER PC核的主要部件 (3)第2章EPPC 编程 (4)2.1.编程模式介绍 (4)2.2.用户态编程模式 (5)2.3.监控态编程模式 (6)2.4.数据和指令(1/2) (7)2.5.数据和指令(2/2) (8)2.6.指令总结 (9)2.7.指令总结 (10)2.8.指令总结 (11)2.9.什么是“EIEIO”指令 (12)2.10.什么是EIEIO指令 (13)2.11.指令总结 (14)2.12.什么是执行同步? (14)2.13.什么是同步指令? (15)2.14.什么是同步指令? (16)2.15.指令总结 (16)2.16.什么是“ISYNC”指令。

(17)2.17.指令总结 (18)2.18.指令总结 (18)2.19.指令总结 (19)2.20.解释条件代码(1/2) (20)2.21.解释条件代码(2/2) (21)2.22.使用和记录运算信息 (22)2.23.使用和记录运算信息 (23)2.24.转移类型和选址 (24)2.25.转移操作 (25)2.26.条件转移指令 (26)2.27.条件转移指令----举例 (27)2.28.控制程序流程练习 (28)2.29.控制程序流程练习 (29)2.30.写子程序和I/O处理 (29)第3章HDLC协议 (31)3.1.HDLC帧格式 (31)3.2.HDLC点到点。

(32)3.3.HDLC多点。

(33)3.4.HDLC控制器怎样发送数据。

(34)3.5.基本HDLC接收工作。

(35).HDLC总线配置。

(36)3.7.HDLC总线配置。

(36)3.8.HDLC总线发送工作。

(37)3.9.HDLC定义参数RAM (38)3.10.HDLC定义参数RAM。

PowerPC QorIQ P2020处理器介绍v1.1

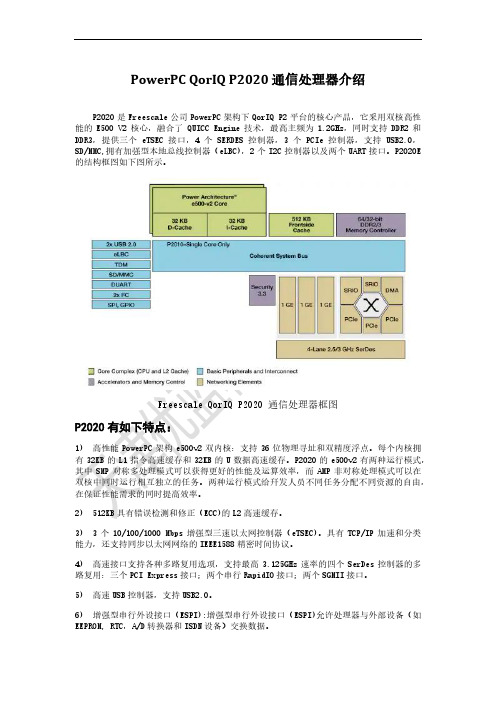

P2020 是 Freescale 公司 PowerPC 架构下 QorIQ P2 平台的核心产品,它釆用双核高性 能的 E500 V2 核心,融合了 QUICC Engine 技术,最高主频为 1.2GHz,同时支持 DDR2 和 DDR3,提供三个 eTSEC 接口,4 个 SERDES 控制器,3 个 PCIe 控制器,支持 USB2.0, SD/MMC,拥有加强型本地总线控制器(eLBC),2 个 I2C 控制器以及两个 UART 接口。P2020E 的结构框图如下图所示。

26 位地址,16 位数据,4 个片选,4 个外部中断 10 路 PPC GPIO,12 路灵活的扩展 GPIO; 支持 RTC,温度监控,看门狗,JTAG 接口; Uboot 引导 VxWorks/linux 操作系统镜像,调试过程更方便;

其他技术指标

供电指标: 电源输入:DC +5V(+/-5%) 功耗 <= 8W

Freescale QorIQ P2020 通信处理器框图

P2020 有如下特点:

1) 高性能 PowerPC 架构 e500v2 双内核:支持 36 位物理寻址和双精度浮点。每个内核拥 有 32KB 的 L1 指令高速缓存和 32KB 的 U 数据高速缓存。P2020 的 e500v2 有两种运行模式, 其中 SMP 对称多处理模式可以获得更好的性能及运算效率,而 AMP 非对称处理模式可以在 双核中同时运行相互独立的任务。两种运行模式给幵发人员不同任务分配不同资源的自由, 在保证性能需求的同时提高效率。 2) 512KB 具有错误检测和修正(ECC)的 L2 高速缓存。 3) 3 个 10/100/1000 Mbps 增强型三速以太网控制器(eTSEC)。具有 TCP/IP 加速和分类 能力,还支持同步以太网网络的 IEEE1588 精密时间协议。 4) 高速接口支持各种多路复用选项,支持最高 3.125GHz 速率的四个 SerDes 控制器的多 路复用:三个 PCI Express 接口;两个串行 RapidIO 接口;两个 SGMII 接口。 5) 高速 USB 控制器,支持 USB2.0。 6) 增强型串行外设接口(ESPI):增强型串行外设接口(ESPI)允许处理器与外部设备(如 EEPROM, RTC,A/D 转换器和 ISDN 设备)交换数据。

PowerPC家族新贵 IBM推高性

PowerPC 家族新贵IBM 推高性

PowerPC 家族新贵IBM 推高性能嵌入式CPU

导语:PowerPC 是一种精简指令集(RISC)架构的CPU,其基本的设计源自IBMPowerPC601 微处理器POWER 架构。

被命名为PowerPC476FP 的新款处理器内核的的出现让IBM 和LSI 有了在嵌入式方面的合作。

并且,这一新

型的PowerPC 内核在其下一代网络应用的多核平台架构中使用。

IBMPowerPC 系列处理器,嵌入式处理器以及内核是IBMPower 架构家族产

品的一部分,其应用范围广泛,小到消费类电子,大到超级计算机。

IBMPower 架构作为开放式的微处理器架构,提供高性能以及低功耗应用。

近期,IBM 发布了堪称业界最高性能嵌入式处理器PowerPC476FP,使得这

一新型的PowerPC 系列处理器更好应用网络环境。

PowerPC476FP 内核。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MC9S12KG256VPVE

MC9S12KT256CPVE

MC9S12KT256VPVE

MC9S12T64CPKE16

MC9S12T64MPKE16

MC9S12XA256VAG

MC9S12XA512VAG

MC9S12XD256VAG

MC9S12XDT512VAA

MC9S12XDT512VAG

MC9S12DJ256VPVE

MC8610TPX800GB MC8610TVT800GB MC7457RX1000LC MC8640HX1067NE MC8640VU1067NE MC8640VU1000HE MC7447AVS1267LB MC7447AVU1267LB MPC7410THX450NE MC7447AVS1167NB MC7447AHX1167NB MC7457RX1000NC MC8610TPX1066JB MC8610TVT1066JB MC7448THX1000ND MC7448TVU1000ND 型 号 MC7457VG1000NC MC8640DHX1000HE MC8640DVU1000HE KMC7447AHX1167NB KMC7447AVS1167NB MC8640DHX1067NE MC8640DVU1067NE MC8640DHX1250HE MPC7410THX500LE MC7448VS1250ND MC7448VU1250ND MC7448HX1250ND MC8640DTHX1000HC MC8640DTHX1000HE MC8610PX1333JB MC8610VT1333JB MC8641DHX1000GE MC7448HX1420LD KMC7457RX1000NC KMC8610VT1333JB

MC9S12E128VFUE

MC9S12E64CFUER

MC9S12XDT512CAAR

MC16Z3BCAG16Байду номын сангаас

MC912DT128CCPVE

MC9S12A32CFUER

MPU E600 CORE 800MHZ 783-PBGA MPU E600 CORE 800MHZ 783-PBGA IC MPU RISC 32BIT 483FCCBGA IC DUAL CORE PROCESSOR 994-CBGA IC MPU SGL CORE E600 1023FCCBGA IC MPU SGL CORE E600 1023FCCBGA IC MPU RISC 1267MHZ 360-FCCLGA IC MPU RISC 32BIT 360-BGA MCU RISC 1.8V 450MHZ 360-CBGA IC MPU RISC 1167MHZ 360-FCCLGA IC MPU RISC 1167MHZ 360-FCCBGA IC MPU RISC 32BIT 483FCCBGA MPU E600 CORE 1066MHZ 783-PBGA MPU E600 CORE 1066MHZ 783-PBGA IC MPU RISC 32BIT 360-FCCBGA MPU 128BIT 1000MHZ 360-CBGA 产品描述 IC MPU RISC 1000MHZ 483FCCBGA IC DUAL CORE PROCESSOR 1023-CBGA IC MPU DUAL CORE E600 1023FCCBGA IC MPU RISC 32BIT 1167MHZ 360BGA IC MPU RISC 1167MHZ 360-LGA IC DUAL CORE PROCESSOR 1023-CBGA IC MPU DUAL CORE E600 1023FCCBGA IC DUAL CORE PROCESSOR 1023-CBGA IC MPU 32BIT 500MHZ 360-CBGA IC MPU RISC 1250MHZ 360-FCCLGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 360-FCCBGA MPU DUAL E600 1023-FCCBGA IC DUAL CORE PROCESSOR 1023-CBGA MPU E600 CORE 1333MHZ 783-PBGA MPU E600 CORE 1333MHZ 783-PBGA IC DUAL CORE PROCESSOR 1023-CBGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 1000MHZ 483BGA IC HOST PROCESS 1333MHZ 783-PBGA IC MCU 256K FLASH 25MHZ 112-LQFP IC MCU 256K FLASH 25MHZ 112-LQFP IC MCU 256K FLASH 25MHZ 112-LQFP IC MCU 64K FLASH 2K RAM 80-LQFP IC MCU 64K FLASH 2K RAM 80-LQFP IC MCU 256K FLASH 144-LQFP IC MCU 512K FLASH 144-LQFP IC MCU 256K FLASH 144-LQFP IC MCU 512K FLASH 80-QFP IC MCU 512K FLASH 144-LQFP IC MCU 16BIT 256K FLASH 112-LQFP IC MCU 16BIT 128K FLASH 80-QFP IC MCU 16BIT 64K FLASH 80-QFP IC MCU 16BIT 512K FLASH 80-QFP IC MCU 16BIT HI SPEED 144-LQFP IC MCU 16BIT 128K FLASH 112-LQFP IC MCU 16BIT 32K FLASH 80-QFP

型 号 MPC7410HX400LE MPC755BVT300LE MPC603RRX300LC MPC745CPX350LE MPC745CVT350LE MPC603RRX266TC MPC745BVT350LE MPC7410HX450LE MPC755BPX350LE MPC755BRX350LE MPC755BVT350LE MPC755CPX350LE MPC755CRX350LE MPC755CVT350LE MC7447AHX733NB MC7447AVU733NB MPC603RVG300LC MPC755BRX350TE MPC755CRX350TE MC7447AHX867NB 型 号 MC7447AVU867NB MC7448VU867ND MC7448HX867ND MPC755CPX400LER2 MPC755CVT400LE MPC7410HX500LE MC7447AHX1000LB MC7447AVU1000LB MC8610VT800GB MC7448VU1000LD MC7410TVU400LE MPC7410THX400LE MPC755CPX400LE MC7448VU1000ND MC7448HX1000ND MC7410VU500LE MC7457VG867NC MPC755CRX400TE KMC7447AVU1000NB MC8610PX1066JB 型 号 MC8610VT1066JB MC7457VG1000LC KMC8610VT1066JB MC7457RX867NC 产品描述 IC MPU 32BIT LP HP 360-CBGA MCU HIP4DP 300MHZ 360-PBGA IC MPU POWERPC 300MHZ 255-CBGA MCU HIP4DP 350MHZ 255-PBGA MCU HIP4DP 350MHZ 255-PBGA IC MPU 32BIT 266MHZ 255-CBGA IC MPU PPC 350MHZ 255-FCPBGA IC MPU 32BIT 450MHZ 360-CBGA MCU HIP4DP 350MHZ 360-PBGA MCU HIP4DP 350MHZ 360-CBGA MCU HIP4DP 350MHZ 360-PBGA MCU HIP4DP 350MHZ 360-PBGA MCU HIP4DP 350MHZ 360-CBGA MCU HIP4DP 350MHZ 360-PBGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 360-BGA MPU RISC PID7V-603E 255FCCBGA MCU HIP4DP 350MHZ 360-CBGA MCU HIP4DP 350MHZ 360-CBGA IC MPU RISC 32BIT 360-FCCBGA 产品描述 IC MPU RISC 32BIT 360-BGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 360-FCCBGA MCU HIP4DP 400MHZ 360-PBGA MCU HIP4DP 400MHZ 360-PBGA IC MPU 32BIT 500MHZ 360-CBGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 360-BGA MPU E600 CORE 800MHZ 783-PBGA IC MPU RISC 32BIT 360-FCCBGA MPU RISC 32BIT 360-CBGA IC MPU 32BIT 400MHZ 360-CBGA IC MPU PPC 400MHZ 360-FCPBGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 32BIT 360-FCCBGA IC MPU RISC 867MHZ 483FCCBGA MCU HIP4DP 400MHZ 360-CBGA IC MPU RISC 32BIT 1000MHZ 360BGA MPU E600 CORE 1066MHZ 783-PBGA 产品描述 MPU E600 CORE 1066MHZ 783-PBGA IC MPU RISC 1000MHZ 483FCCBGA IC HOST PROCESS 1066MHZ 783-PBGA IC MPU RISC 32BIT 483FCCBGA 价格 $53.90 $56.55 $55.90 $53.83 $54.64 $70.88 $56.66 $57.74 $59.22 $68.94 $59.22 $61.87 $73.36 $60.10 $60.29 $67.59 $65.09 $88.54 $76.94 $90.20 价格 $76.50 $84.82 $96.28 $96.53 $95.23 $80.05 $76.85 $79.22 $93.86 $99.33 $93.13 $95.73 ###### $93.70 $92.28 ###### ###### ###### ###### ###### 价格 ###### ###### ###### ###### RoHS 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 RoHS 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 否 RoHS 否 否 否 否