ECL外腔半导体

数字集成电路的分类

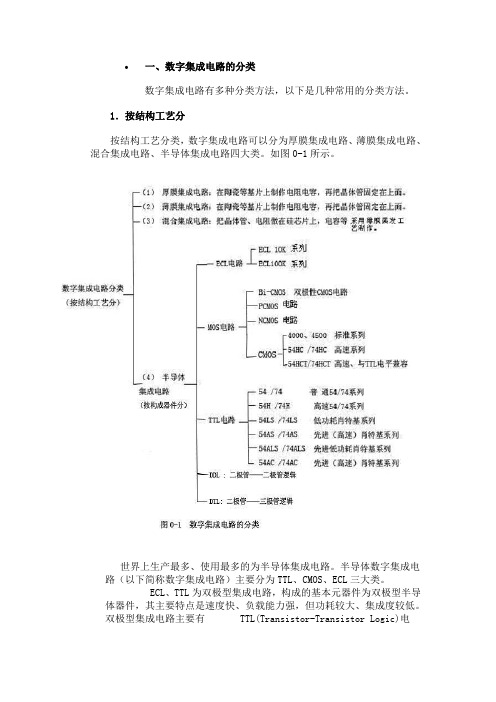

数字集成电路的分类数字集成电路有多种分类方法,以下是几种常用的分类方法。

1.按结构工艺分按结构工艺分类,数字集成电路可以分为厚膜集成电路、薄膜集成电路、混合集成电路、半导体集成电路四大类。

图如下所示。

世界上生产最多、使用最多的为半导体集成电路。

半导体数字集成电路(以下简称数字集成电路)主要分为TTL、CMOS、ECL三大类。

ECL、TTL为双极型集成电路,构成的基本元器件为双极型半导体器件,其主要特点是速度快、负载能力强,但功耗较大、集成度较低。

双极型集成电路主要有TTL(Transistor-Transistor Logic)电路、ECL(Emitter Coupled Logic)电路和I2L(Integrated Injection Logic)电路等类型。

其中TTL电路的性能价格比最佳,故应用最广泛。

ECL,即发射极耦合逻辑电路,也称电流开关型逻辑电路。

它是利用运放原理通过晶体管射极耦合实现的门电路。

在所有数字电路中,它工作速度最高,其平均延迟时间tpd可小至1ns。

这种门电路输出阻抗低,负载能力强。

它的主要缺点是抗干扰能力差,电路功耗大。

MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。

MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。

MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。

常见半导体激光器

常见半导体激光器

半导体激光器是一种利用半导体材料制造的光电子器件。

它在许多应用领域都有广泛的应用,如制造光通信设备、光存储设备、光学传感器和医疗设备等。

常见的半导体激光器有以下几种:

1. 激光二极管(LD):是一种小型、高效的激光器。

它的工作原理是在有源区域中注入电流,通过特殊的发光机构来实现激光放大和反馈,可以用于制造光纤通信设备和光存储设备等。

2. 垂直腔面发射激光器(VCSEL):是一种特殊的激光器,可以

实现垂直方向的激光输出,被广泛应用于光通信和光存储设备等领域。

3. 泵浦激光器:它是一种用于将固体激光器和光纤激光器等其

它类型激光器泵浦的激光器。

常用于制造高功率激光器,如工业制造和医疗设备中的激光切割设备。

4. 外腔半导体激光器(ECL):它是一种通过将外腔加入到半导

体激光器中来控制输出光谱和波长的激光器,被广泛应用于光通信和光存储设备等领域。

5. 量子级联激光器(QCL):它是一种新型的半导体激光器,具

有高效率、高功率和低阈值等优点,被广泛应用于红外光谱学和空间探测等领域。

以上是几种常见的半导体激光器,它们在不同的领域都有其独特的应用价值。

随着科技的不断发展,半导体激光器的应用前景将越来越广阔。

计算机监控FBG-ECLD乙炔吸收稳频技术

第28卷第4期增刊 2007年4月仪 器 仪 表 学 报Chinese Jour nal of Scientif ic InstrumentVol.28No.4Apr.2007 计算机监控FBG2ECLD乙炔吸收稳频技术唐先炜,赵华凤,高海滨,马晓红,李晓芳(清华大学电子工程系 北京 100084)摘 要:报道了基于计算机监控的光纤光栅外腔半导体激光器(FB G2ECLD)乙炔吸收稳频,设计了计算机信号监测和设备控制的平台,实现了在计算机界面上对信号的监测和对稳频控制设备的控制。

系统将光纤光栅外腔半导体激光器的输出光频率稳定在乙炔的一个吸收峰上,稳定度达到10-8量级。

关键词:光纤光栅;外腔半导体激光器;乙炔;计算机;稳频C2H2a bsor ption f r equency sta bilizat ion of F BG2ECLDmon itor ed an d contr olled by computerTang Xianwei,Zhao Huafeng,G ao Hai bi n,Ma X i aohong,Li X iaofang(De pa rtment of E lectronic Enginee ring,Tsinghua University,Beij ing100083,China)Abstract:C2H2abso rption frequency stabilization of FB G2EC L D mo nitored and co ntrolled by comp uter i s reported.A platform fo r sig nal detecting and devices cont rolli ng is set up.S ignal can be show n o n t he monitor and st abilization de2 vices can al so be cont rolled t hrough co mput er soft ser of FB G2EC L D was st abilized at an absorption line of a2 cet ylene.The frequency stabilit y reached10-8.Key words:FB G;ECLD;acet ylene;computer;frequency stabilizat io n1 引 言光纤光栅外腔半导体激光器(FBG2ECLD)是20世纪90年代后期发展起来的新技术,光纤光栅外腔半导体激光器可与光纤系统直接连接,调谐控制简单、稳定,调谐范围较大[1]。

(工艺流程)最简易的半导体制造工艺流程

半导体制造工艺流程N型硅:掺入V族元素--磷P、砷As、锑SbP型硅:掺入III族元素—镓Ga、硼BPN结:半导体元件制造过程可分为前段(FrontEnd)制程晶圆处理制程(WaferFabrication;简称WaferFab)、晶圆针测制程(WaferProbe);後段(BackEnd)构装(Packaging)、测试制程(InitialTestandFinalTest)一、晶圆处理制程晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随著产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之後,接著进行氧化(Oxidation)及沈积,最後进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。

二、晶圆针测制程经过WaferFab之制程後,晶圆上即形成一格格的小格,我们称之为晶方或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是也有可能在同一片晶圆上制作不同规格的产品;这些晶圆必须通过晶片允收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性,而不合格的的晶粒将会被标上记号(InkDot),此程序即称之为晶圆针测制程(WaferProbe)。

然後晶圆将依晶粒为单位分割成一粒粒独立的晶粒三、IC构装制程IC構裝製程(Packaging):利用塑膠或陶瓷包裝晶粒與配線以成積體電路目的:是為了製造出所生產的電路的保護層,避免電路受到機械性刮傷或是高溫破壞。

半导体制造工艺分类半导体制造工艺分类一双极型IC的基本制造工艺:A在元器件间要做电隔离区(PN结隔离、全介质隔离及PN结介质混合隔离)ECL(不掺金)(非饱和型)、TTL/DTL(饱和型)、STTL(饱和型)B在元器件间自然隔离I2L(饱和型)半导体制造工艺分类二MOSIC的基本制造工艺:根据栅工艺分类A铝栅工艺B硅栅工艺其他分类1、(根据沟道)PMOS、NMOS、CMOS2、(根据负载元件)E/R、E/E、E/D半导体制造工艺分类三Bi-CMOS工艺:A以CMOS工艺为基础P阱N阱B以双极型工艺为基础双极型集成电路和MOS集成电路优缺点半导体制造环境要求主要污染源:微尘颗粒、中金属离子、有机物残留物和钠离子等轻金属例子。

RTL,DTL,TTL,CTL,ECL,CMOS等数字电路的定义及区别

RTL,DTL,TTL,CTL,ECL,CMOS等数字电路的定义及区别RTL,DTL,TTL,CTL,ECL,CMOS等数字电路的定义及区别什么叫RTL电路?⼀种由电阻和晶体管组合的逻辑电路,判断逻辑准位的⽅式是以输⼊端回路电流特性⽽定,当输⼊的电压VI低于晶体管导通电压时,就没有导通电流IB,晶体管C-E间成开路状态(截⽌),若输⼊的电压Vi⾼于晶体管导通电压时,⽽且电压越⾼C-E间导通就越多,换句话说这种逻辑族的的逻辑输出准位会受到输⼊准位的影响,所以使⽤时输⼊的逻辑准位必需保持⾜以让RTL能够截⽌或饱和的电压,才能保证下⼀级的逻辑电路能够正常判断,因此这已是⼀个被淘汰的逻辑族。

838电⼦什么叫DTL电路?DTL是⼀种晶体管电路加上⼆极管所设计的逻辑电路,它利⽤了⼆极管正向导通电压(约0.7V)的特性,提⾼逻辑电路VIH的准位电压,以及在晶体管基极加上负的偏压,当⼆极管电路断路时能够迅速使晶体管截⽌改善了RTL 输⼊电压对输出逻辑准位的不良影响,但是需要正负双电源的设计,⽬前也不见有数字系统采⽤这逻辑电路了。

什么叫TTL电路?TTL以晶体管做为逻辑判断及逻辑输出的主要组件,输⼊端的电压低于0.8V为VIL,⾼于2.0V为VIH,这两个电压点之间的范围是⼀个逻辑准位的不明确区,设计电路时要避免有此范围的电压输⼊。

TTL的输出端由两个串接的晶体管负则输出逻辑准位电压,Q3负责接通VCC,Q4负责接通地电位,使得VOH保证⼤于2.4V,VOL 保证⼩于0.4V,逻辑「1」与「0」间更为明显,变化也较RTL、DTL迅速。

由于要保证输⼊及输出的逻辑界定,电源必须为固定值,以74为编号的是商⽤IC,电源为5V,容许误差为±0.25V,⼯作温度范围为℃到7℃,54为编号的是军⽤IC,电源也是为5V,误差可以⼤⼀点为±0.5V,⼯作温度范围为-55℃到125℃。

838电⼦TTL发展⾄今以已有多种改良产品,以表格⽅式介绍及⽐较于下:TTL型别IC编号VOH VIH VOL VIL 传递延迟功率消耗标准型74xx 2.4V 2.0V 0.4V 0.8V 9 nS 10 mW低功率74Lxx 2.4V 2.0V 0.3V 0.8V 33 nS 1 mW⾼速型74Hxx 2.4V 2.0V 0.4V 0.8V 6 nS 23 mW肖特基(Schottky) 74Sxx 2.7V 2.0V 0.5V 0.8V 3 nS 23 mW低功率肖特基74LSxx 2.7V 2.0V 0.5V 0.8V 9.5 nS 2 mW传递延迟:输⼊逻辑准位后到输出反应正确所需时间,此时间越短逻辑电路反应速率越快。

大学微机原理半导体存储器详解演示文稿

不可再次改写。

PROM基本存储电路

PROM的写入要由专用的电路(大

电流、高电压)和程序完成。

第17页,共36页。

第5章 半导体存储器

5.3.2 可擦除的PROM 一、EPROM(紫外线可擦除) 用户可以多次编程。用紫外线照射可全部擦除原有信息(擦除后内容 全为“1” ),便可再次改写。

一、RAM原理

构成

存储体(R-S触发器构成的存储矩阵) 外围电路 译码电路、缓冲器

I/O控制电路

0

0

地

1

1

数

址

存储

据

n位 译

矩阵

缓

地址 码 2n-1

m

冲

器

器

m位 数据

CS 控制 逻辑

R/W

存储芯片构成示意图

第6页,共36页。

第5章 半导体存储器

地址译码器:

接收来自CPU的n位地址,经译码后产生2n个地址选择信号,实现对片

3. 按存储器的功能来分类 ✓按存储器与CPU的关系分类

控制存储器CM 、主存储器MM 、高速缓冲存储器Cache 、

外存储器EM ;

✓按存储器的读写功能分类 读写存储器RWM 、只读存储器ROM;

✓按数据存储单元的寻址方式分类

随机存取存储器RAM 、顺序存取存储器SAM 、直接存取存储器DAM ;

内存储单元的选址。

控制逻辑电路:

接收片选信号CS及来自CPU的读/写控制信号,形成芯片内部控制信号, 控制数据的读出和写入。

数据缓冲器:

寄存来自CPU的写入数据或从存储体内读出的数据。

存储体:

存储体是存储芯片的主体,由基本存储元按照一定的排列规律构成。

数字集成电路的分类

一、数字集成电路的分类数字集成电路有多种分类方法,以下是几种常用的分类方法。

1.按结构工艺分按结构工艺分类,数字集成电路可以分为厚膜集成电路、薄膜集成电路、混合集成电路、半导体集成电路四大类。

如图0-1所示。

世界上生产最多、使用最多的为半导体集成电路。

半导体数字集成电路(以下简称数字集成电路)主要分为TTL、CMOS、ECL三大类。

ECL、TTL为双极型集成电路,构成的基本元器件为双极型半导体器件,其主要特点是速度快、负载能力强,但功耗较大、集成度较低。

双极型集成电路主要有 TTL(Transistor-Transistor Logic)电路、ECL(Emitter Coupled Logic)电路和I2L(Integrated Injection Logic)电路等类型。

其中TTL电路的性能价格比最佳,故应用最广泛。

ECL,即发射极耦合逻辑电路,也称电流开关型逻辑电路。

它是利用运放原理通过晶体管射极耦合实现的门电路。

在所有数字电路中,它工作速度最高,其平均延迟时间tpd可小至1ns。

这种门电路输出阻抗低,负载能力强。

它的主要缺点是抗干扰能力差,电路功耗大。

MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。

MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。

MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。

数字电路ECL技术

数字电路ECL技术数字电路ECL技术(Emitter-Coupled Logic)是一种高速、低功耗的数字电路设计技术,广泛应用于高性能计算、通信和测量设备中。

本文将介绍ECL技术的原理、特点以及其在实际应用中的优势。

ECL技术是一种差分逻辑技术,它基于晶体管的共射结构。

与传统的CMOS(互补金属氧化物半导体)技术相比,ECL技术在速度和功耗方面具有显著的优势。

在ECL电路中,输入电压变化会引起电流的变化,而不是电压的变化,这使得ECL电路可以实现非常低的传输延迟。

另外,ECL技术还具有抗噪能力强、抗辐射能力强等特点,适用于高可靠性和高稳定性要求的应用场景。

ECL电路的核心是差分放大器,它由两个共射晶体管和一个稳压电源构成。

当输入信号变化时,差分放大器会通过电流变化来放大信号。

差分放大器的输出与输入信号之间存在一定的差异电压,这称为差模电压。

通过引入偏置电源和负反馈电路,可以使得差模电压保持在一个恒定的值,从而实现稳定的操作。

ECL技术的特点之一是工作电源电压较高,通常为负电源,可达到-5V或更低。

这种高电压工作使得ECL电路具有更大的噪声裕度,提高了抗噪能力。

同时,高电压还使得ECL电路的输出电平较高,有利于提高电路的驱动能力和抗干扰能力。

另一个重要特点是高速运算。

由于ECL电路采用电流模式传输数据,在信号在电流传输时可以达到较高的速度。

此外,由于ECL技术的共射结构,晶体管的输出响应时间极短,可以实现纳秒级的响应速度,因此ECL电路非常适用于高速计算和通信领域。

除了高速和低功耗外,ECL技术还具有较强的抗辐射能力,这使得它在航天、核能和军事应用中具有重要地位。

对于这些特殊环境,电路对辐射的抗干扰能力至关重要,而ECL技术由于其特殊的差分放大器结构,可以有效地抑制辐射干扰。

尽管ECL技术在一些方面表现出优势,但也存在一些限制。

首先,由于工作电压较高,ECL电路的功耗相对较大,不适用于低功耗应用。

半导体激光器的分类

半导体激光器的分类半导体激光器是一种利用半导体材料产生激光的装置。

它具有体积小、功率高、效率高、寿命长等优点,广泛应用于通信、医疗、材料加工等领域。

根据其工作原理和结构特点的不同,可以将半导体激光器分为以下几类:1. 二极管激光器(LD)二极管激光器是最常见的半导体激光器类型之一。

它是通过注入电流到二极管中,使其产生激光辐射。

二极管激光器具有体积小、功率密度高、效率高等优点,广泛应用于光纤通信、激光打印、激光雷达等领域。

根据工作原理的不同,二极管激光器又可以分为以下几类:•直接泵浦激光器(Direct Pumped Laser Diode,DPLD):通过电流直接激发半导体材料产生激光。

这种激光器通常具有较高的功率和较宽的工作频率范围。

•共振腔激光器(Resonator Laser Diode,RLD):在二极管激光器的两端加上反射镜,构成一个光学共振腔。

通过选择合适的反射镜,可以实现激光的单模或多模输出。

2. 半导体光放大器(SOA)半导体光放大器是一种利用半导体材料增强光信号强度的装置。

它与二极管激光器结构相似,但工作在低注入电流下,不产生激射器。

半导体光放大器具有宽带宽、低噪声、快速响应等优点,广泛应用于光纤通信、光网络等领域。

3. 垂直腔面发射激光器(VCSEL)垂直腔面发射激光器是一种在半导体材料中形成垂直共振腔结构的激光器。

它是通过在半导体材料上增加光学反射镜而实现的。

VCSEL具有发射光束近乎垂直、低阈值电流、高速调制等特点,广泛应用于光纤通信、光存储、光雷达等领域。

4. 外腔激光二极管(ECL)外腔激光二极管是一种将带有光纤输出的半导体激光器。

它利用光纤与半导体激光器之间的耦合结构,将激光输出到光纤中。

ECL具有高度集成、输出功率稳定、光谱纯净等优点,广泛应用于光纤通信、传感器等领域。

5. 量子阱激光器(QL)量子阱激光器是一种利用半导体量子阱结构产生激射器的激光器。

它采用了由狭窄能隙材料构成的量子阱,可以有效地抑制激发态的非辐射复合,从而提高激光器的效率。

TTL逻辑 、CMOS逻辑、ECL逻辑的对比研究

TTL逻辑、CMOS逻辑、ECL逻辑的对比研究逻辑门电路是数字电路中最基本的逻辑元件,逻辑门可以组合使用实现更为复杂的逻辑运算。

常见的逻辑门有TTL逻辑门电路、COMS逻辑门电路和ECL逻辑门电路。

首先,给各个逻辑门电路下个定义。

CMOS是:金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分。

由MOS管构成的集成电路称为MOS集成电路。

TTL 电路是晶体管-晶体管逻辑电路的英文缩写(Transister-Transister-Logic),是数字集成电路的一大门类。

它采用双极型工艺制造,具有高速度低功耗和品种多等特点。

ECL(Emitter Coupled Logic)即发射极耦合逻辑电路,也称电流开关型逻辑电路。

它以多个晶体管的发射极相互耦合加上射极跟随器组成的电路,简称ECL电路。

下面介绍一下COMS电平和TTL电平一、TTL电平:输出高电平>2.4V,输出低电平<0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

即TTL电平标准:输出 L: <0.8V ; H:>2.4V。

输入 L: <1.2V ; H:>2.0V二、CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。

而且具有很宽的噪声容限。

即CMOS电平:输出 L: <0.1*Vcc ; H:>0.9*Vcc。

输入 L: <0.3*Vcc ; H:>0.7*Vcc.另外,CMOS电路不使用的输入端不能悬空,会造成逻辑混乱。

TTL电路不使用的输入端悬空为高电平。

CMOS集成电路电源电压可以在较大范围内变化,因而对电源的要求不像TTL 集成电路那样严格。

用TTL电平他们就可以兼容。

半导体集成电路课程教学大纲

《半导体集成电路》课程教学大纲(包括《集成电路制造基础》和《集成电路原理及设计》两门课程)集成电路制造基础课程教学大纲课程名称:集成电路制造基础英文名称:The Foundation of Intergrate Circuit Fabrication课程类别:专业必修课总学时:32 学分:2适应对象:电子科学与技术本科学生一、课程性质、目的与任务:本课程为高等学校电子科学与技术专业本科生必修的一门工程技术专业课。

半导体科学是一门近几十年迅猛发展起来的重要新兴学科,是计算机、雷达、通讯、电子技术、自动化技术等信息科学的基础,而半导体工艺主要讨论集成电路的制造、加工技术以及制造中涉及的原材料的制备,是现今超大规模集成电路得以实现的技术基础,与现代信息科学有着密切的联系。

本课程的目的和任务:通过半导体工艺的学习,使学生掌握半导体集成电路制造技术的基本理论、基本知识、基本方法和技能,对半导体器件和半导体集成电路制造工艺及原理有一个较为完整和系统的概念,了解集成电路制造相关领域的新技术、新设备、新工艺,使学生具有一定工艺分析和设计以及解决工艺问题和提高产品质量的能力。

并为后续相关课程奠定必要的理论基础,为学生今后从事半导体集成电路的生产、制造和设计打下坚实基础。

二、教学基本要求:1、掌握硅的晶体结构特点,了解缺陷和非掺杂杂质的概念及对衬底材料的影响;了解晶体生长技术(直拉法、区熔法),在芯片加工环节中,对环境、水、气体、试剂等方面的要求;掌握硅圆片制备及规格,晶体缺陷,晶体定向、晶体研磨、抛光的概念、原理和方法及控制技术。

2、掌握SiO2结构及性质,硅的热氧化,影响氧化速率的因素,氧化缺陷,掩蔽扩散所需最小SiO2层厚度的估算;了解SiO2薄膜厚度的测量方法。

3、掌握杂质扩散机理,扩散系数和扩散方程,扩散杂质分布;了解常用扩散工艺及系统设备。

4、掌握离子注入原理、特点及应用;了解离子注入系统组成,浓度分布,注入损伤和退火。

可调谐半导体激光器的发展及应用

可调谐半导体激光器的发展及应用郝秀晴;陈根祥【摘要】如今可调谐半导体激光器的技术日益成熟,其在光通信网络的应用逐渐增加.通过介绍几种常见可调谐半导体激光器的原理及性能,阐述了其在国内外的发展现状;在此基础上指出目前供应商对通信光源的具体需求,从而为今后可调谐激光器的发展指明了方向,最后进一步对其市场应用前景进行了展望.【期刊名称】《光通信技术》【年(卷),期】2010(034)011【总页数】4页(P4-7)【关键词】可调谐半导体激光器;光纤通信;调谐原理【作者】郝秀晴;陈根祥【作者单位】北京交通大学,光波技术研究所,北京,100044;北京交通大学,光波技术研究所,北京,100044【正文语种】中文【中图分类】TN3650 引言随着各种新兴技术特别是波分复用(wavelengthdivision multiplexing,WDM)技术等在光通信领域中的广泛应用,使得人们对作为通信光源的激光器提出了更高的要求。

如果采用传统的固定波长激光器来产生相应频率的光,不但需要封装多个激光器,使光源的体积变得很大,而且还会增加光通信网络的成本,限制了光网络的扩展及网络的灵活性[1]。

通过引入可调谐半导体激光器,不仅可有效节省波分复用系统转换器,减少激光器以及其他模块的数量,还可有效降低光通信网络成本,改进光网络的功能性,并且还能提供动态波长,控制网络流量,自动恢复波长等功能[2]。

1 可调谐半导体激光器发展现状到目前为止,可调谐激光器已发展出多种基于不同理论模型的实现方式,但其基本组成结构大致相同,主要包括具有有源增益区和谐振腔的激光器、改变和选择波长的可调装置以及稳定输出波长装置三个部分组成。

通过直接或间接地改变激光器谐振腔的光学长度,使其中的谐振模式产生微小的变化,再通过选频元件选择出相应频率的光。

其中能在较宽波长范围内产生激光的半导体有源区是必不可缺的,如今半导体有源区大多都采用多量子阱(multiple quantum well,MQW)结构,只要注入半导体内的电流足够大,量子阱结构便能够在很宽的频谱范围内产生光增益[3]。

半导体工艺流程

20世纪50年代: 晶体管技术 20世纪60年代: 工艺技术 20世纪70年代: 竞争 20世纪80年代: 自动化 20世纪90年代: 批量生产

21世纪: 器件进入规模时代和智能时代

前道工序(Front End)制程 晶圆处理制程(Wafer Fabrication;

简称 Wafer Fab) 管芯中测(Wafer Probe);

2000

50mm 100mm 125mm 150mm 200mm

300mm

2′ 4′

5′ 6′

8′

12′

在国内也不是很普及。

不同尺寸的硅片—从开始生产 —到生产高峰 — 再到逐步淘汰的生命周期

100mm 1975年

150mm 19831年4年

200mm 1987年

300mm 20年 1995年

10年 1984年 9年 20年

是为了制作电路的保护层,避免电路受到机械 性划伤或高温破坏。也有不做封装就使用的。

从环境、用途、成本考虑。 用户市场的需求

MOS型

双极型

PMOS型 NMOS型 CMOS型

饱和型

非饱和型

BiCMOS TTL IIL ECL/CML

一 双极型工艺: A 在每个器件间要做隔离区(PN结隔离、全介质隔

离及PN结、介质混合隔离) ECL (非饱和型) (不掺金) 、TTL/DTL (饱和 型) 、STTL (饱和型) B 在元器件间自然隔离 IIL(饱和型)

超净间:洁净等级主要由 灰尘颗粒数/m3

0.1µm 1级 35 10 级 350 100级 NA 1000级 NA

0.2µm 0.3µm 7.5 3 75 30 750 300 NA NA

电化学原子层外延及其制备纳米超晶格热电材料的研究进展

电化学原子层外延及其制备纳米超晶格热电材料的研究进展摘要:电化学原子层外延(ECALE)是电化学沉积和原子层外延技术的结合,通过运用欠电势技术交替电化学沉积化合物的组成元素一次一个原子层而实现外延生长。

详细介绍了电化学原子层外延(ECAID的基本原理和特点,阐述了ECALE 过程几个的影响因素。

此外,本文并进一步介绍了它在纳米超晶格材料制备中的应用研究进展。

关键词:纳米超晶格 ECAIE 欠电位沉积原子层外延Electrochemical Atomic Layer Epitaxy and Research Progress of Its Application in Preparation of nanosuperlattices Materials(College of Material Science and Technology, Shanghai University, Shanghai)Abstract :Electrochemical Atomic Layer Epitaxy( ECALE ) is a combination of two feasible growth techniques,The electrochemical deposition and atomic layer epitaxy.The growth involves the alternating electro-deposition of each component element of a compound .one monolayer at a time by underpotential deposition that is critical in ECALE.In this paper,the principle and characteristics of ECALE is influencing the ECALE progress are analyzed .Besides,the research progress and of ECALE used in preparation of nanosuperlattices material is reviewedKeyword: nanosuperlattices,ECALE,UPD,ALE引言近年来纳米超晶格热电材料及器件的研究与开发越来越引起了人们的关注[1~5],一方面是由于纳米超晶格材料的量子尺寸效应可望大幅度提高材料的热电性能,另一方面纳米薄膜热电材料的加工工艺与微、光电子器件微细加工工艺完全兼容,为实现大规模集成电路、微电子光电子器件的原位高效冷却提供了可能.Venkata subramanian等人报道了采用金属有机物化学气相沉积(MOCVD)法制备的VA—VIA族化合物半导体Bi2Te3/Sb2Te3超晶格热电材料最大优值系数ZT达到了2.4[5],是近年来热电材料研究领域最引人瞩目的进展之一。

mecl电平

"MECL"这个术语通常指的是"Emitter-Coupled Logic"(发射极耦合逻辑),这是一种用于数字集成电路的逻辑族,特别是在高速、低功耗应用中。

MECL系统以其快速的切换速度和稳定的性能而著称,常被应用于高性能计算机、通信设备和其他需要快速数字处理的技术中。

MECL电平在讨论"MECL电平"时,我们通常关注的是该逻辑系列中逻辑"1"和逻辑"0"所对应的电压水平。

MECL电路使用负电源电压,这意味着它的电压水平与传统的TTL(晶体管-晶体管逻辑)或CMOS(互补金属氧化物半导体)电路有所不同。

MECL电路的特点是它们的电压水平较低,通常在负电压范围内操作。

例如,在某些MECL标准中,逻辑"0"可能被定义为-1.8伏特左右,而逻辑"1"可能是-0.9伏特左右。

这些具体电平会根据不同的MECL版本(如MECL 10K、MECL 100K等)而有所变化。

MECL的优点1.高速性:MECL电路可以实现非常高的切换速度,这使得它们适用于高速数据传输和处理应用。

2.低功耗:相对于其他高速逻辑族,MECL在保持高速操作的同时,还能维持较低的功耗水平。

3.稳定性:MECL电路的设计减少了电压摆动,提供了良好的噪声容限和稳定的逻辑电平。

应用领域由于其高速和低功耗的特性,MECL被广泛应用于:•高速数据通信•计算机系统•军事和航空航天领域的电子设备•任何需要快速且可靠的数字逻辑处理的场合结论MECL电平是指在发射极耦合逻辑(MECL)系统中使用的特定电压水平,这些电平代表逻辑状态。

MECL因其高速和低功耗特性而在高性能电子系统中得到广泛应用。

理解MECL电平对于设计和维护这些高速电子系统至关重要。

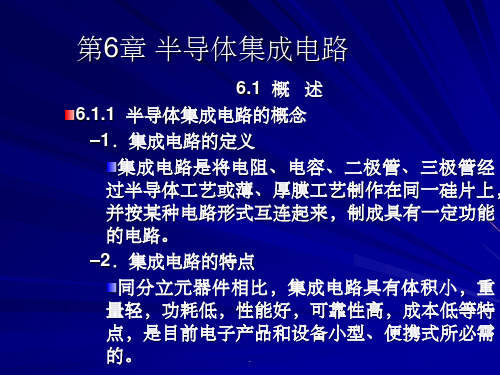

半导体集成电路

(2) 国产TTL电路分类

T1000:标准系列,相当于国际54/75系列 T2000:高速系列,相当于国际54/74H高速系 列 T3000:肖特基系列,相当于国际54/74S肖特 基系列 T4000 : 低功 耗 肖特 基 系列 , 相当 于 国际 54 / 74LS低功耗肖特基系列 T000可分为T000中速系列和T000高速系列 T000中速系列的性能类同于T1000系列 T000高速系列的性能类同于. T2000系列

6.3 各类集成电路的性能比较

6.3.1 TTL集成电路 TTL集成电路的全名称 是晶体管—晶体管逻 辑集成电路。它由 NPN或PNP型晶体管 组成。

.

1.TTL集成电路的分类

(1) 国际通用标准TTL集成电路的分类

– 54/74系列TTL数字逻辑集成电路一般分为六大 类:

– 54/74XX:标准TTL电路系列 – 54/74SXX:肖特基TLL电路系列 – 54/74HXX:高速TTL电路系列 – 54/74LSXX:低功耗肖特基TTL电路系列 – 54/74ASXX:先进肖特基TTL电路系列 – 54/74ALSXX:先进低功耗肖特基TTL电路系

单列直插式集成电路,识别其引脚时应 使引脚向下,面对型号或定位标记,自 定位标记对应一侧的第一只引脚数起, 依次为①,②,③,④……。此类集成 电路上的定位标记一般为色点、凹坑、 小孔、线条、色带、缺角等。

.

有些厂家生产的集成电路,本是同一种芯片,为了 便于在印制电路板上灵活安装,其引脚排列顺序对 称相反。一种按常规排列,即由左向右,另一种则 由右向左。对此类集成电路若封装上有识别标记, 可按上述规律分清其近脚顺序。但也有少数器件上 没有引脚识别标记,这时应从其型号上加以区别。 若其型号后缀中有一字母R,则表明其引脚顺序为 从右到左反向排列。 还有个别集成电路,设计时尾部引出脚为非等距排 列,作为标记。可按此特点来识别引脚顺序。

ecl半导体发展历史

ecl半导体发展历史ECL半导体发展历史ECL(Emitter-Coupled Logic,发射极耦合逻辑)是一种高速、高性能的数字逻辑电路技术,广泛应用于计算机、通信和测量等领域。

本文将回顾ECL半导体的发展历史,探讨其演进过程和应用领域的变化。

ECL半导体技术的起源可以追溯到20世纪50年代末期。

当时,人们开始意识到传统的晶体管逻辑电路在高速运算和大规模集成电路方面存在一些局限性。

为了克服这些限制,研究人员开始寻找新的逻辑电路技术。

1961年,ECL逻辑电路由IBM的物理学家D.H. Rhodes首次提出,并在随后的几十年里得到了广泛的研究和应用。

ECL逻辑电路的核心思想是利用发射极耦合技术实现高速运算。

与传统的基于电压的CMOS(互补金属氧化物半导体)逻辑电路不同,ECL使用电流作为信号传输的基本单位,具有更高的开关速度和更低的功耗。

ECL的工作原理是通过两个发射极耦合晶体管的基极间接触来实现逻辑门的功能。

这种结构使得ECL电路能够在纳秒级别的时间尺度内完成运算,适用于高频率和高速度的应用。

在20世纪60年代和70年代,ECL半导体技术逐渐成熟,并在计算机领域得到了广泛应用。

当时,计算机的主要应用领域是科学计算和军事系统,对高性能和高可靠性的要求很高。

ECL逻辑电路以其出色的性能和可靠性成为首选技术,被用于构建超级计算机和军事雷达等系统。

然而,ECL的高功耗和高成本限制了它在通信和消费电子领域的应用。

随着时间的推移,随着CMOS技术的发展,ECL逻辑电路的地位开始受到挑战。

CMOS逻辑电路通过改善功耗和集成度,逐渐成为主流技术。

然而,ECL在一些特殊领域仍然具有优势。

例如,在高速通信和网络设备中,ECL仍然是一种重要的选择,因为它能够提供更高的工作频率和更低的时延。

近年来,随着物联网和人工智能的兴起,对高速、高性能处理器的需求越来越迫切。

ECL半导体技术在这些领域重新获得了关注。

研究人员和工程师们通过改进电路设计和制造工艺,进一步提升了ECL的性能和集成度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

激光器工作需要两个要素:(1)主动增益介质放大光学信号,和(2)反馈机制,以提供持续的激光振荡。

在法布里-珀罗激光器中,两个反射镜的反射系数分别是r

1和r

2(功率反射率

R1 = r12和R2 = r22),给光场

提供反馈,如图1所示。

图1:法布里-珀罗激光器结构

在长度为L的谐振腔内,光场的往返增益可以表示为:

公式 1:光场的往返增益

其中g和α

i 分别是增益和内损耗系数,λ是真空中的波长,n

eff是有效折射率,

L是腔长。

解析阈值振幅和

相位条件的结果为:

公式2:振幅条件

公式3:相位条件

其中α

定义为镜面损耗,N 是整数下标,代表模式数。

m

在半导体(二极管)激光器中,增益介质是通过向正向偏置二极管的结区域注入电流来激发的。

半导体激光器的人工量子阱结区内的高浓度电子和空穴使产生实现光学增益所需的粒子数反转成为可能。

当增益介质是半导体材料时,可以通过芯片的两个解理面之间的菲涅耳反射建立法布里-珀罗谐振腔。

结区实际上是一个波导,从一个面延伸到另一面。

一个垂直于波导的未镀膜的“解理“面的反射率R大约为30%。

然而,器件的最大输出功率可以通过对端面镀膜,改变端面的反射率来进行优化。

法布里-珀罗激光二极管的最大功率通常是通过在后端面镀高反(HR)膜,在前端面镀低反(LR)膜得到的。

,根据相位公式定义,法布里-珀罗激光二极管器件的发射谱将依赖于注入电流。

当偏置小于阈值时g > α

i

发射谱包含一系列的峰,这些峰对应法布里-珀罗腔的纵模。

不断增加注入电流,直到满足g = α

i+ αm,才会产生激光。

激光波长是由第一个满足阈值条件的纵模决定的。

输出光谱并不总是压缩为单一的辐射波长,也可是纵模组成的窄带光谱。

图2:法布里-珀罗激光器增益曲线

这对基于InP的法布里-珀罗激光器尤其有效,通常它的光学带宽为5到10纳米。

基于GaAs的器件能工作在单纵模模式,但这取决于波长和输出功率,通常它们的输出带宽小于2纳米。

典型的850纳米激光二极管的腔长在300微米左右,群折射率在4左右,其纵模间隔将为0.3纳米,这与1毫米长的1550纳米激光二极管相似。

改变谐振腔的长度或者折射率,比如通过对激光二极管加热或制冷,将会移动整个模式梳,相应地移动了输出波长。

激光器线宽

半导体激光器的单纵模激射线宽(FWHM)由修正的Schawlow和Townes公式定义,公式中加入了Henry :

线宽增强因子α

H[1]

公式4: Schawlow-Townes-Henry 激光线宽

其中hv 是光子能量,v g 是群速度,n sp 是粒子数反转因子,P out 是单面输出功率。

这个公式描述了相位和振

幅波动引起的激光线宽的光谱展宽,光谱展宽是由对相干激射模式不可避免的自发发射光子引起的。

这些所谓的量子噪声波动定义了激光线宽的下限,而这种微小的波动可能会被机械/声音变化或者热变化引起的更大的波动所掩盖。

增加谐振腔的长度将会减小αm (见公式2),从而减小线宽。

这可以通过量子噪声极限线宽理解(见公式

4),量子噪声极限线宽与激射模式中的自发辐射光子数成正比。

增加谐振腔的长度既减少了的自发辐射光子数(通过减少每个纵模的“冷腔”光谱宽度),又增加了谐振腔中的总光子数,实现固定输出功率。

这就是为何Schallow-Townes 公式中谐振腔长度项出现两次的原因。

腔长为0.3毫米的单频分布式反馈(DFB )二极管激光器的将通常具有1MHz 到10MHz 的发射线宽。

举例来说,如果把腔长增加到3厘米,将会使发射线宽变窄超过100倍。

已有报导[2]显示腔长增加的半导体激光器的发射线宽可降低至

单波长工作和调谐

对于许多应用,我们希望得到单纵模(单频)激光,能够调节激光波长,或者两点都能满足。

为了满足这种需求,可在半导体激光器芯片的外部加入波长选择反馈元件,用于选择激射波长。

为了实现这种外腔激光器(ECL )的正确工作,需要抑制半导体芯片法布里-珀罗腔产生的本征光学反馈,从而使它不会干扰外部反馈。

通过在芯片的一个端面镀光学减增透膜(AR ),可以减少增益芯片的法布里-珀罗腔效应。

图3:基于增益芯片的外腔运行

在最小值时,芯片端面反射(R 1)应该比外部反馈(R ext )小20 dB ;也就是,R 1 < 10-2 x R ext [3]。

即使镀了增透膜,法布里-珀罗增益芯片端面的残余反射也常常限制了ECL 的稳定性、输出功率和光谱质量,特别

是如果激光器是可调谐的。

为了进一步减少芯片端面的反射,可以结合使用带角度的波导和增透膜,从而有效地消除来自内部芯片法布里-珀罗腔的大部分反馈[4] 。

该单角度面(SAF)增益芯片为ECL,特别是在宽带可调谐ECL中,提供了优越的结构。

图4:单角度面增益芯片

外腔激光器设计

实现外腔半导体激光器的方法有很多[3]。

对于大多数方法,首先考虑的是选择一个合适的波长选择反馈元件。

最常用的反馈元件之一是衍射光栅,可用作单频和宽带可调谐外腔激光器的反馈元件。

当增益芯片的准直输出光以相对于光栅表面θ角入射到衍射光栅上,并垂直于光栅线时,衍射光束的出射角为θ'由光栅公式确定:

公式5:光栅方程

这里n是衍射级数,λ是衍射波长,d是光栅常数(刻槽之间的距离)。

对n > 0级衍射,衍射光栅将会再空间上分离同一级衍射光中的不同波长成分,因为衍射角θ'与波长有关。

一旦增益芯片的光谱成分被空间分离,可以通过很多方法来选择被反射回增益介质的特定光波长。

Littrow谐振腔ECL结构

最简单的方法之一就是使用Littrow结构,此时衍射光栅的朝向是固定的,所以一级衍射沿入射光方向原路返回到增益芯片中(即上述的公式(5)中θ = θ'):

公式6:光栅公式,Littrow结构

激光器的输出功率可以从光栅的零级反射光得到,通常采用这种方法,因为这种方法构建ECL所需的光学元件最少(只需要一个准直透镜和一个衍射光栅)。

波长调谐是通过旋转衍射光栅实现的,旋转光栅改变反射回波导的光波长。

当选定衍射光栅(光栅常数)、准直透镜和腔长后,在波导的接收角范围内,只有一个纵模被反射回增益芯片,外腔激光器将产生单频激光光谱。

注意准直透镜的选择非常重要,因为准直透镜会影响照射到光栅上的面积,也会影响耦合进半导体增益芯片的聚焦点尺寸。

这种结构的一个缺点是零级输出光的角度随波长的变化而变化。

然而,如果ECL 输出是从SAF增益芯片的垂直面出射的话,这个问题就可以避免。

在这个结构中,SAF垂直面的反射率通常会减少到R ~ 10% ,并选择对所用的衍射级有效衍射的光栅,从而使ECL的输出功率最大。

点击放大

图5:Littrow外腔激光器

Littman-Metcalf ECL结构

另一种常用的ECL实现方法是Littman-Metcalf结构,该结构使用额外的可调节反射镜来选择反馈波长[5]。

相比前一种结构,Littman-Metcalf结构中入射角增加,并在光栅上发生两次衍射,从而使外腔具有更好的波长选择性。

正因如此,Littman-Metcalf ECL的输出光束的线宽通常比类似的Littrow结构的线宽更窄。

在Littman-Metcalf结构中,激光的输出光束通常是衍射光栅的零级反射,这是因为当波长调谐时,传输方向保持不变。

在这种情况下,为了使ECL内的损耗最小,在SAF的垂直面上镀上高反(HR)膜,一般>90%,使输出功率最大。

点击放大

图6:Littman-Metcalf外腔激光器

对于一些应用,可能还是会希望使用SAF芯片的垂直面作为激光器的耦合输出器。

对于这些应用, 需要SAF 芯片垂直面镀低反射率膜,来使激光器的输出功率最大。

Littman-Metcalf设计的一个缺点是其内部损耗要高于Littrow结构,所以通常激光器的输出功率也较低。

其内部损耗增加主要是因为从转向镜反射的零级光束的损耗,以及当用于大角度反射光时,光栅的效率降低引起的损耗增加。

创新的ECL设计

SAF芯片的创新设计非常适合用于外腔激光器,因为它几乎消除了来自增益芯片腔内端面的有害反馈。

Thorlabs提供在垂直面上镀低反膜和高反膜的SAF芯片,以支持各种各样的外腔结构。

关于自定义镀膜来优化特殊外腔激光器结构的性能的信息,请联系技术支持。