韩国ATOsolution的2Gbit的nandflash芯片AFND2G08U3A-CKA

小容量的nand隆重推出

韩国ATO产品-nand flash小容量再生知情的朋友都知道,国际大厂商如三星,hynix,美光等厂商的nand flash 小容量的都已经停产了,目前的情况是,需要告知更多的人,韩国ATO的小容量的NAND flash的推出。

韩国ATO solution,中文名称韩商爱拓,合作与三星,佳能,富士康,通用等公司,ATO的产品主要有:MCP (NAND+DDR2/3,NAND+mobile SDRAM) , 目前这种形式(nand+dd2/3)的MCP产品我们是唯一的一家在做,NAND FLASH我们主要针对三星等大厂即将不做的小容量的进行研发生产,同三星等其他品牌的产品可以兼容。

我司是韩国ATO的一级代理商,可以提供规格书,样品等相关资料,当然我们也有自己的工程师做技术支持。

今天主要介绍一下我们的小容量的NAND FLASH吧。

ATO的nand flash 目前主要以256Mb,512Mb,1Gb为主,相较于高容量产品例如32GB & 64GB,我们的低容量NAND flash主要是用来取代Nor-Flash,主要产品应用于相机、对讲机,手机、LED电视,机顶盒等领域,占总NAND Flash市场约10%。

ATO Solution 自有技术开发设计的SLC 256Mb快闪记忆体(NAND Flash)产品,同时在去年国际积体电路研讨会暨展览会(IIC China)中参展,并将于今年的展会再次跟大家见面。

相对NOR Flash,NAND Flash通常只有在具有技术优越性的国际记忆体大厂才有能力生产。

ATO Solution借由独特性设计技术让产品微型化,大幅提高了ATO产品成本上的竞争力,ATO 256Mb ,512Mb ,1Gb 的NAND Flash SLC以扩大现有低容量产品线阵容。

凭藉着高品质与价格竞争优势,ATO毫无疑问的脱颖而出,ATO的看好市场的空缺,生产的产品不仅可以替代市场上大厂Samsung、Hynix、ST Micron等停产的容量的NAND,同时为工程师们提供了更多的新思路,可以替代之前使用nor flash的产品。

泰利特 2G 3G 4G NB LTE 产品 北美 LE910V2 产品手册说明书

]Delta SW North American LE910 V2 Products80000DSW10127A Rev. 1 – 2018-07-061 6SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICENOTICEWhile reasonable efforts have been made to assure the accuracy of this document, Telit assumes no liability resulting from any inaccuracies or omissions in this document, or from use of the information obtained herein. The information in this document has been carefully checked and is believed to be reliable. However, no responsibility is assumed for inaccuracies or omissions. Telit reserves the right to make changes to any products described herein and reserves the right to revise this document and to make changes from time to time in content hereof with no obligation to notify any person of revisions or changes. Telit does not assume any liability arising out of the application or use of any product, software, or circuit described herein; neither does it convey license under its patent rights or the rights of others.It is possible that this publication may contain references to, or information about Telit products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Telit intends to announce such Telit products, programming, or services in your country. COPYRIGHTSThis instruction manual and the Telit products described in this instruction manual may be, include or describe copyrighted Telit material, such as computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and its licensors certain exclusive rights for copyrighted material, including the exclusive right to copy, reproduce in any form, distribute and make derivative works of the copyrighted material. Accordingly, any copyrighted material of Telit and its licensors contained herein or in the Telit products described in this instruction manual may not be copied, reproduced, distributed, merged or modified in any manner without the express written permission of Telit. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit, as arises by operation of law in the sale of a product.COMPUTER SOFTWARE COPYRIGHTSThe Telit and 3rd Party supplied Software (SW) products described in this instruction manual may include copyrighted Telit and other 3rd Party supplied computer programs stored in semiconductor memories or other media. Laws in the Italy and other countries preserve for Telit and other 3rd Party supplied SW certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Telit or other 3rd Party supplied SW computer programs contained in the Telit products described in this instruction manual may not be copied (reverse engineered) or reproduced in any manner without the express written permission of Telit or the 3rd Party SW supplier. Furthermore, the purchase of Telit products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Telit or other 3rd Party supplied SW, except for the normal non-exclusive, royalty free license to use that arises by operation of law in the sale of a product.USAGE AND DISCLOSURE RESTRICTIONSI. License AgreementsThe software described in this document is the property of Telit and its licensors. It is furnished by express license agreement only and may be used only in accordance with the terms of such an agreement.II. Copyrighted MaterialsSoftware and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, without prior written permission of Telit III. High Risk MaterialsComponents, units, or third-party products used in the product described herein are NOT fault-tolerant and are NOT designed, manufactured, or intended for use as on-line control equipment in the following hazardous environments requiring fail-safe controls: the operation of Nuclear Facilities, Aircraft Navigation or Aircraft Communication Systems, Air Traffic Control, Life Support, or Weapons Systems (High Risk Activities"). Telit and its supplier(s) specifically disclaim any expressed or implied warranty of fitness for such High Risk Activities.IV. TrademarksTELIT and the Stylized T Logo are registered in Trademark Office. All other product or service names are the property of their respective owners.V. Third Party RightsThe software may include Third Party Right software. In this case you agree to comply with all terms and conditions imposed on you in respect of such separate software. In addition to Third Party Terms, the disclaimer of warranty and limitation of liability provisions in this License shall apply to the Third Party Right software.TELIT HEREBY DISCLAIMS ANY AND ALL WARRANTIES EXPRESS OR IMPLIED FROM ANY THIRD PARTIES REGARDING ANY SEPARATE FILES, ANY THIRD PARTY MATERIALS INCLUDED IN THE SOFTWARE, ANY THIRD PARTY MATERIALS FROM WHICH THE SOFTWARE IS DERIVED (COLLECTIVELY “OTHER CODE”), AND THE USE OF ANY OR ALL THE OTHER CODE IN CONNECTION WITH THE SOFTWARE, INCLUDING (WITHOUT LIMITATION) ANY WARRANTIES OF SATISFACTORY QUALITY OR FITNESS FOR A PARTICULAR PURPOSE.NO THIRD PARTY LICENSORS OF OTHER CODE SHALL HAVE ANY LIABILITY FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING WITHOUT LIMITATION LOST PROFITS), HOWEVER CAUSED AND WHETHER MADE UNDER CONTRACT, TORT OR OTHER LEGAL THEORY, ARISING IN ANY WAY OUT OF THE USE OR DISTRIBUTION OF THE OTHER CODE OR THE EXERCISE OF ANY RIGHTS GRANTED UNDER EITHER OR BOTH THIS LICENSE AND THE LEGAL TERMS APPLICABLE TO ANY SEPARATE FILES, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.APPLICABILITY TABLE PRODUCTSLE910-NA V2LE910-NA V2 SINGLE SKULE910-NA1LE910-NA1 SINGLE SKULE910B4-NALE910B1-NALE910B1-NA SINGLE SKULE910B1-SALE910-SV V2LE910-SV1LE910-SVLCONTENTSNOTICE 2COPYRIGHTS (2)COMPUTER SOFTWARE COPYRIGHTS (2)USAGE AND DISCLOSURE RESTRICTIONS (3)I.License Agreements (3)II.Copyrighted Materials (3)III.High Risk Materials (3)IV.Trademarks (3)V.Third Party Rights (3)APPLICABILITY TABLE (4)CONTENTS (5)1.INTRODUCTION (6)2.DELTA SW 20.00.XX4 – 20.00.XX5 (8)New Features (8)General Enhancements (9)3.DELTA SW 20.00.XX2 – 20.00.XX4 (12)New Features (12)General Enhancements (14)4.DOCUMENT HISTORY (17)1. INTRODUCTION1.1. ScopeScope of this document is to detail the corrections, changes or enhancements made to the software of Telit modules.1.2. AudienceThis document is intended for Telit customers.1.3. Contact Information, SupportFor general contact, technical support services, technical questions and report documentation errors contact Telit Technical Support at:•*****************•*********************•*****************Alternatively, use:/supportFor detailed information about where you can buy the Telit modules or for recommendations on accessories and components visit:Our aim is to make this guide as helpful as possible. Keep us informed of your comments and suggestions for improvements.Telit appreciates feedback from the users of our information.1.4. Related Documents•Telit LE910-V2 Modules AT Commands Reference Guide, 80446ST10707A •Telit's Modules Software User Guide, 1vv03007842. DELTA SW 20.00.XX4 – 20.00.XX5New FeaturesDescription SW 20.00.xx5 Added AT#SHSANA and AT#SHSDLY AT commands. ••AT#DTMF=2 has been enabled, AT#OOBTSET has beenintroduced (Cat-1 Ability to control in-band DTMF tones).• Added Cat-1 Ability to control DTMF tone volume separately frommaster volume.• Added store/restore of the APN in the file system for NVMrecovery.Supported DTMF URC on VoLTE. •General EnhancementsFixed Verizon TC 6.2 failure. •Fixed NCM fallback when USB profile is configured as MBIM. •Fixed Verizon TC 7.1.1 and TC 7.1.2 fail due to the calling of• UtaMsNetAttachReq in case of refresh type 0.•Fixed Verizon TC 4.07 fail due to the calling ofUtaMsCallPsDefinePrimaryReq after DETACH.Fix of VoLTE call fail after AT#SGACT command. •Improvement on paging detection in case bad RF condition. ••Fixed unexpected "SIM not inserted" indication appearing during adata session (#QSS: 0 during data session).•Fixed #MONI incorrect response for servant cell when the moduleis registered in GERAN.•Fixed no apparent power saving for CFUN:5 in CMUX. The powerconsumption during CMUX session now follows the physical DTRstate.•Fixed Verizon TC 4.6, 4.9 and 4.11 manage properly the DETACHREQUEST for type 5 REFRESH and type 0 REFRESH in Verizon.•Fix of the first MT SMS which is now queued and handled correctlywhen the SMS client is ready.•AT+CSQ is returning 99,99 when registered.The fix consists also in checking the +CEREG registration status in+CSQ delegation function.Fixed LTE Data Retry handling of event list and counter in Attach• Reject with cause 8 scenario.Fix of memory leek scenario in• TalCatUtaMsSimTkTerminalResponseCnfCb()/SIAL_TOOL_IND.Improvement on updating the neighbors list with AT#MONI,• sometimes the updating was not fast.• SIM Profile Switch management: Add processing ofshutdown/startup indication of "Electrical deinit procedure" in case"SIM init procedure" is running.Also handled proactive command coming when ME currentlyunable to process because bus.• Blocked LDR NVM setting on reading SIM MCC/MNC in Intel CAT interface.Fixed echo issue during MO voice calls by extending Echo• Canceller tuning up to 16 kHz.Extended delay on AT#FTPGETOTA attempts after first successful• download.Fixed IMS registration behavior after switching from USBCFG=3 to• USBCFG=0.Integrated fix for SIB decoding issue. •Removed audio noise on VoLTE calls. •Fixed call drop issues with VOLTE. •Band 13 2nd harmonic margin improvement. •Fixed Verizon 3-Way Calling failures. •Fixed Normal Call and Call Forwarding failure. •Fixed loose registration after PPP section. •Removed wrong PLMN indication sent to AT parser. •• The IPv6 network availability is checked only once in case offailure, witching to IPv4-only connection and reducing an eventualproblem in a ~80 seconds long OMADM session.The management of ACM_PROGRESS_IND and• ACM_DISCONNECTED_IND has been aligned to the one in Intelinterface.Resolved no audio and call drop with “RTP-RTCP Timeout”. •• VoLTE Calls: incoming "Call waiting tone" now doesn’t excludesaudio path.New +CEVDP and +CEMODE default for SKU SV products. •After the attach complete, the module detached and re-attached on• VZWINTERNET. The cause was the incorrect setting of the PCO.Removed double selection request for file PNN. •Modified NVM USBCFG default value. •3.DELTA SW 20.00.XX2 – 20.00.XX4New Features Description SW 20.00.xx4Support VOLTE on SV and NA variant. • DTMF decoding support for VOLTE on SV and NA variant. • AppZone: implemented new m2m_ssl API that allow to set right TLS protocol (TLS1.0/TLS1.1 and TLS1.2).• AppZone: implemented new API m2m_ipraw_cfg for IPRAW IPV4 and IPV6.• AppZone: implemented API to support AUXILIARY UART. • AppZone: implemented new API for Watchdog management. • AppZone: implemented new API to set context on specified CID. • AppZone: implemented new API m2m_hw_sleep_mode_cfg to manage power saving mode.• AppZone: support for easyAT. • Support TLS1.2. • Verizon: Enabling support for SSL Server authentication and TLS 1.2.•Verizon: Support APN location 6, CGDCONT, VZWAPNE updated. Location APN 6 is updated also during OMA-DM.• Support CFUN9 - Incoming GPRS packed wake-up the DUT. • ATT: Adding alert signal on ODIS parameter modification: An alert towards AT&T OMADM server is triggered one minute after eachHostOdis reset or set command.• EasyIP: Increase number of sockets from 6 to 10. •AT#MTUSIZE=<mtu>: implemented new AT command in order to• set the MTU size.MBIM: support multiple bearer connection in parallel. •• AT#APPSSLCFG implemented AT command to configure ciphersuite, auth level and TLS version for a maximum of 5 applications.Added storing of SMS in ME and SM memories. •AT+CMAR/AT#CMAR: Implemented AT command to format NVM• and Filesystem.• AT#IIDIPV6=<cid>,<IID>: Implemented AT command in order toset the IID to a certain CID.AT#MBIMCFG: implemented AT command to configure CID to be• used for MBIM connection.• AT#PDPAUTH: implemented AT command to set theauthentication parameters for all CIDs.AT#RXTOGGLE: Implemented AT command to set main or• diversity antenna, command used in test mode for certificationpurpose.AT+IPR: Update UART speed up to 3Mbps. •General EnhancementsType Description SW 20.00.xx4Improvement the report of AT+CSQ and AT+CESQ, adjust RSSI•calculation.•Manage properly NCM disconnection (AT#NCMD=0) and dialupwhen they are used together.Updated the +CCLK: time zone range to “-96…+96”. •Fix on received URL #DTMFEV with DTMF enabled. •Support +CRSM=192,28423 with a sim with pin enabled. •Improvement on storing #HSMICG in the extended profile. •Restored LTE neighbour information’s in AT#MONI and•AT#MONIZIP, added Added <qrxlevmin> and <pci> for serving cell.restored timers T3402 and T3412 in AT#RFSTS. •Development standard usage of with “[]:”, example•AT#FTPOPEN=”[ipv6_addr]:port_num.Added timestamp on +CMT unsolicited in incoming PDU. •Add conversion table from ISO Latin 8-bit to PCCP437. •Antenna detection: Fix behavior of repGPIO on AT#GSMAD. •STN: 254 not always received when performing a SAT request with•Vodafone. Implemented a better handling for SIM APP ENDindication.Removed SIM switch off when CFUN=4 is issued to avoid IMS•registration issue once CFUN=1 is used again. SIM remains active.•Fixed reply Time on AT#PING, it was not aligned to timeoutconfigured.Improvement on AT#CSURV scan 4G channel without SIM. •#PSNT Corrected handling of technology indication. It reported a•wrong network type when EGPRS.•AppZone: Improvement on #HTTPRCV to reports OK if called fromvirtual com.Improvement on AT+CRSM is locking up the AT interface if SIM•doesn’t include specific folder.MBIMCFG has been extended to allow the selection of both CID 1• and CID 3.Removed DCD glitch when module received an incoming data call. •• Improvement on command AT+CMGL="ALL", it has been extendedto cover also the 5th AT instance that is available only inSMSATRUN and TCPATRUN.• #CMUXMODE=1 - CFUN=5 correctly managed on virtual channelby DTR toggle.• [ATT] SSL certificates update:"GeoTrust Primary Certification Authority" and "GeoTrust Primary Certification Authority - G3" certificates installed on the module,under <CDR-DVM-3953> AT&T requirement.AT&T Changes in default: Default value of AT#ICMP now is 2. •Improvement on AT#CSURV to avoid missing MCC/MNC in LTE• scan response if the same cell is shared by two PLMNs.• Reduce timing to configure GPIOs status during startup of thesystem.• DW Cloud: improvement to support Method execution requestparameters with var is a multiselect string.• FIREWALL: improvement on storing the disable/enable setting inNVM.Improvement on-off procedure to make sure that 5 seconds on-off• are always enough to power on the module after a FW upgradeand in all other scenarios.MBIM command DEVICE_CAPS reports the same version string as• AT+CGMR.I2C Clock Stretching support. •4. DOCUMENT HISTORYRevision Date Changes0 2017-09-12 Delta SW 20.00.xx2 - 20.00.xx41 2018-07-06 Delta SW 20.00-xx4 - 20.00.xx5] 6 1。

腾讯NDA限制-腾讯NDA限制-Jacinto6Eco SoC电源解决方案-DRA72 TDA2

TPS22965 + TPS51200

8

New PDN Concept

0.40 = $3.25

(3 AVS @ 1‐2.5A, Dual 1.8/3.3V IO, DDR3L)

18 + 4 + 4.6 + 4.6 + 4 + 9 = 44

$4.42 128 $2.53 74

$7.32 190 $4.64 119

5. “PDN’s AVS Capability” is the achievable power if all AVS power rails are increased to 90% of capacity while other power rails remain at typical Use Case modelled values.

(3 AVS @ 1‐3.5A, Dual 1.8/3.3V IO, DDR3L) (similar to EVM PDN #0)

49 + 9 + 4 = 62

#8.2 – LP87524 + LP5912 + TLV713 + LP5907 +

9.92

1.26 + 0.19 + 0.07 + 0.10 + 0.10 +

2. PDN Support component (Rs, Cs & Ls) pricing from Mouser Distribution website using single 4k – 10k/reel qty costs as of May 2016. Both PDN Support & PDN Total Costs have been provided for relative comparison only, individual customer volume pricing may vary.

Moxa UC-2100-W Series IIoT 芯片说明书

UC-2100-W SeriesArm Cortex-A81GHz palm-sized IIoT gateways with built-in LTE Cat.M1/NB-IoT moduleFeatures and Benefits•Armv7Cortex-A81000MHz processor•Integrated LTE NB-IoT/Cat.M1module with global band support•LTE-ready computer with Verizon/AT&T certification and industrial-grade CE/FCC/UL certifications•Dual-SIM slots•Moxa Industrial Linux with10-year long-term support•Dual auto-sensing Ethernet ports(10/100Mbps and10/100/1000Mbps)•Dual CAN ports with industrial CAN2.0A/B protocol supported•microSD socket for storage expansion•Programmable LEDs and a programmable button for easy installation andmaintenance•-40to75°C operating temperature rangeCertificationsIntroductionThe UC-2100-W Series computing platform is designed for embedded data acquisition and processing applications.The computer comes with up to two software selectable RS-232/422/485full-signal serial ports and single or dual LAN ports.This palm-sized series of Arm-based computing platforms includes a variety of models for a wide range of interface requirements,such as serial and LAN ports,and wireless connections.The versatile communication capabilities allow users to efficiently adapt the UC-2100-W Series for a variety of complex communications solutions running on a compact palm-sized computer.The UC-2100-W Series has a built-in Cortex-A8Arm-based processor that has been optimized for a variety of industrial solutions.With flexible interface options,this tiny embedded computer is a reliable and secure gateway for data acquisition and processing at field sites and is a useful communication platform for many other large-scale deployments.Models designed for wide-temperature applications are available for extreme environments such as those found in the Oil and Gas industry.Furthermore,all models use Moxa’s industrial-grade Linux platform,which provides optimized software features and superior long-term support.AppearanceUC-2114UC-2116SpecificationsComputerCPU Armv7Cortex-A81GHz DRAM512MB DDR3Storage Pre-installed8GB eMMCPre-installed OS Moxa Industrial Linux(Debian9,Kernel4.4)See /MILComputer InterfaceStorage Slot Micro SD Slot x1Ethernet Ports Auto-sensing10/100Mbps ports(RJ45connector)x1Auto-sensing10/100/1000Mbps ports(RJ45connector)x1Serial Ports RS-232/422/485ports x2,software selectable(DB9male)CAN Ports CAN2.0A/B x2(5-pin terminal block)Cellular Antenna Connector SMA x1GPS Antenna Connector UC-2116-T-LX:SMA x1Number of SIMs2SIM Format NanoConsole Port RS-232(TxD,RxD,GND),4-pin header output(115200,n,8,1)Buttons Reset buttonEthernet InterfaceMagnetic Isolation Protection 1.5kV(built-in)Serial InterfaceBaudrate50bps to921.6kbpsData Bits5,6,7,8Stop Bits1,1.5,2Parity None,Even,Odd,Space,MarkPull High/Low Resistor for RS-4851kilo-ohm,150kilo-ohmsESD Protection4kV,for all signalsFlow Control RTS/CTS,XON/XOFF,ADDC®(automatic data direction control)for RS-485,RTSToggle(RS-232only)Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GNDRS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDCAN InterfaceIndustrial Protocols CAN2.0A,CAN2.0BBaudrate10to1000kbpsIsolation2kV(built-in)Signals GND,CAN_L,CAN_SHLD,CAN_H,CAN_V+Cellular InterfaceBand Options LTE Bands:Band1(2100MHz)/Band2(1900MHz)/Band3(1800MHz)/Band4(1700MHz)/Band5(850MHz)/Band8(900MHz)/Band12(700MHz)/Band13(700MHz)/Band18(850MHz)/Band19(850MHz)/Band20(800MHz)/Band25(1900MHz)/Band26(850MHz)/Band28(700MHz)Carrier Approval:Verizon,AT&TLED IndicatorsSystem Power x1Programmable x1LAN2per port(10/100Mbps)Serial2per port(Tx,Rx)Wireless Signal Strength3CAN2per port(Tx,Rx)Power ParametersInput Voltage9to48VDCPower Consumption 5.8WInput Current0.6A@9VDC,0.12A@48VDCReliabilityAlert Tools External RTC(real-time clock)Automatic Reboot Trigger External WDT(watchdog timer)Physical CharacteristicsHousing MetalDimensions(with ears)111x99x34.5mm(4.37x3.90x1.36in)Weight396g(0.87lb)Installation Wall-mounting,DIN-rail mounting(with optional kit)Environmental LimitsOperating Temperature-40to75°C(-40to167°F)Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsSafety EN62368-1,IEC62368-1,UL62368-1EMC EN55032/24EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:4kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:3V/mIEC61000-4-4EFT:Power:1kV;Signal:0.5kVIEC61000-4-5Surge:Power:0.5kV;Signal:1kVIEC61000-4-6CS:3VIEC61000-4-8PFMFShock IEC60068-2-27Vibration2Grms@IEC60068-2-64,random wave,5-500Hz,1hr per axis(without any USBdevices attached)Hazardous Locations Class I Division2,ATEXCarrier Approvals VerizonAT&TGreen Product RoHS,CRoHS,WEEEMTBFTime UC-2114-T-LX:533,149hrsUC-2116-T-LX:496,650hrsStandards Telcordia(Bellcore)StandardWarrantyWarranty Period5yearsDetails See /warrantyPackage ContentsDevice1x UC-2100-W Series computerInstallation Kit1x power jackCable1x console cableDocumentation1x quick installation guide1x warranty cardDimensionsUC-2114UC-2116Ordering InformationModel Name CPU RAM Storage Serial Ethernet CAN Cellular GPS Operating Temp.UC-2114-T-LX1000MHz512MB8GB22(1GigaLAN)2NB-IoT/Cat.M1–-40to75°CUC-2116-T-LX1000MHz512MB8GB22(1GigaLAN)2NB-IoT/Cat.M1Yes-40to75°CAccessories(sold separately)Power AdaptersPWR-12150-USJP-SA-T Locking barrel plug,12VDC1.5A,100to240VAC,US/JP plug,-40to75°C operating temperature PWR-12150-EU-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,EU plug,-40to75°C operating temperature PWR-12150-UK-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,UK plug,-40to75°C operating temperature PWR-12150-AU-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,AU plug,-40to75°C operating temperature PWR-12150-CN-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,CN plug,-40to75°C operating temperature CablesCBL-F9DPF1x4-BK-100Console cable with4-pin connector,1mAntennasANT-LTEUS-ASM-01GSM/GPRS/EDGE/UMTS/HSPA/LTE,1dBi,omnidirectional rubber-duck antennaANT-LTE-OSM-03-3m BK700-2700MHz,multiband antenna,specifically designed for2G,3G,and4G applications,3m cable ANT-LTE-ASM-04BK704to960/1710to2620MHz,LTE omnidirectional stick antenna,4.5dBiANT-LTE-OSM-06-3m BK MIMO Multiband antenna with screw-fastened mounting option for700-2700/2400-2500/5150-5850MHzfrequenciesANT-LTE-ASM-05BK704-960/1710-2620MHz,LTE stick antenna,5dBiDIN-Rail Mounting KitsDK35A DIN-rail mounting kit,35mm©Moxa Inc.All rights reserved.Updated Apr28,2022.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

韩国ATO公司产品介绍

To Be a World ClassTo Be a World Class Memory Solution ProviderSolution Provider MemoryMemory Solution Provider ATO Solution Co., LtdSolution Co., Ltd ATOJan 2013Jan2013About ATO Solution¾Efficient MCP Memory Solution ProviderSince established in 2007, ATO Solution has been growing as amemory MCP solution provider focusing on Digital Still Camera(DSC) application.ATO Solution has been recognized as one of the most reliable MCP memory f tTo Be The Best Partner For Your Memory Solutionmanufacturer.The 1Fab-less in NAND Flash memory industryFor Your Memory Solution ¾The 1st Fab-less in NAND Flash memory industry In 2012, ATO Solution successfully launched and started mass production for 256Mb, 512Mb SLC NAND Flash memory products, which were developed by its own design technology.ATO Solution expands SLC NAND product line-up by launching 1Gb SLC Flash memory within the Q1’2013.Corporate Core TechnologyThe effective NAND Flash Memory DesignP id d ffi i t M S l ti f t dOptimized NAND Flash Design &SPI Provided efficient Memory Solutions for customer needs Optimized NAND Flash Design & SPITo Be the Best Partner for Memory Solution To Be the Best Partner for Memory SolutionNAND/DRAM MCPNAND SPI(patented)Low Density NANDCompany OutlineOrganizationCEO Chris Park EstablishedOctober 31, 2007CEOHeadquarter705 Loadland EZ Tower, 153 Gumi-dong, Bundang-gu, Seongnam-si, Gyeonggi-do, Korea AdvisorV. Presidenty gg ,Product NAND FlashMCP (NAND+DRAM)13M USD R&D ProductionSupport Sales & Marketing Financial Account QualityCapital 1.3M USD Employees 41peoples Design Prod. Eng’rQuality Management Production Management PurchasingKorea Taiwan ChinaHR IRRevenue 24.3M USD (2012)Web Site2013Mass production start for own 1Gb SLC NAND Flash in Q1Mass production start for own 256Mb/512Mb SLC NAND Flash2012Started consumer MCP delivery for Altek /PentaxStarted own SLC NAND Flash delivery for Ability / Fuji-film 2009~2011Start consumer MCP delivery for SDIC (Samsung Digital Imaging Co.) Mobile MCP registered on Spreadtrum 2G/3G platforms New business started with Asia Optical Flextronics Selected as “Company with Good technology”by Korean Government New business started with Asia Optical Flextronics Development start for SLC NAND Flash (256Mb/512Mb)2008 Company EstablishedSelected as Company with Good technology by Korean Government Acquired ISO9001:2000, ISO14001:20042007Biz start with Foxconn , MCP for Digital Still CameraBusiness Milestone1.Early Positioning with Consumer MCP 2The 1Fab less for NAND Flash Memory2.The 1st Fab-less for NAND Flash Memory3.New innovative solution ; SPI NAND Flash MemoryPhase II ; Low Density NandPhase III ; Nand based SPIProvide NAND-cell based Phase I ; Market Solution Provided Memory Solution Low Density NAND Flash Memory Development & Marketing for Consumer & SPI Flash for PC, Mobile, and Consumer MarketProvided Memory Solution ; MCP for Consumer Marketg Mobile Market`2007`2008`2009`2010`2011`2012`2013`2014`2015Phase I ; MCP Solution for ConsumerPartners CustomersMARKETING /QUALITY SERVICETAM : ~150M set / yearPhase II ; Low Density NAND Flash9IDMs are focusing on high density NAND Flash Memory-Capacity and Technology drivenMarket still needs continuous high reliable product and serviceHigh Competition ply9Market still needs continuous high reliable product and serviceamong MajorSuppliers and/SupDemUnstable supply& Continuous demandSupplyATO Solution’sTarget Marketpp yDemandSuppliers Move256Mb512Mb1Gb2Gb4Gb Density8Gb16GbEdge in design competiveness¾Die Size Comparison TableP d tCDi Si (2)W/FR ti Product Company Die Size (mm2)Tech(nm)W/F Size Ratio 256Mb H35.82908” 2.7435828”274(1.8V/3.3V)M 35.82908 2.74S(EOL)37.449012” 2.86ATO Solution13.07578”1512Mb (1.8V/3.3V)H33.11578” 1.58S 38.476312” 1.85T 29.634312” 1.42ATO Solution20.85578”11Gb (33V)H 30.994812” 1.093090109(3.3V)For 1bit ECCP 30.975012” 1.09ATO Solution28.22578”1Market Outlook _ WW SLC NAND Flash FCST (Consumer)K unit500,000 600,000 128Mb256Mb 512Mb 1Gb 2Gb 4Gb 8Gb200,000 300,000 400,000 Source : Forward Insight (2012. Sep)-100,00020112012201320142015 2016Total Consumer Demand byDensity (kUnits)2011 2012 2013 2014 2015 2016 CAGR<128Mb ------128Mb 6,119 5,074 4,089 2,144 --44145315301900152591925256Mb 44,145 31,530 19,001 5,259 1,925 -512Mb 114,519 96,382 75,177 59,212 47,661 30,157 -23.4%1Gb 147,898 154,362 161,864 167,566 179,001 187,513 4.9%2Gb 109,268 104,836 107,999 112,413 119,733 130,192 3.6%4Gb 54,644 54,906 61,917 73,858 85,309 95,797 11.9%757910037145912164430677411528Gb7,579 10,037 14,591 21,644 30,677 41,152Total (128Mb-8Gb)484,173 457,127 444,637 442,096 464,306 484,812 0.0%¾Global SLC NAND FCST in digital consumer market is estimated as a quite flat.Market Outlook _ WW Mobile Phone FCST2500Smartphone Mid-End Feature Phone Low-End Feature Phone206%1500200025.9%22.3%15.2%23.3%10.2%21.9% 6.7%20.6%358%24.7%26.1%0500100051.7%61.5%67.9%72.7%39.5%35.8%29.5%44.4%2011 2012 2013 2014 2015 2016Source : Forward Insight (2012. Sep)Mobile phone unit forecast (M Units)2,0 11 2,012 2,013 2,014 2,015 2,016 CAGRS t h 471658901112713551566272%Smartphone 471 658 901 1,127 1,355 1,566 27.2%Mid-End Feature Phone 710 596 452 278 203 144 -27.3%Low-End Feature Phone 418 411 389 427 437 444 1.2%¾Global total mobile phone unit shipments will reach to 1.7 billion units in 2013.¾Feature phone have the larger share in 2012 mobile market but its trend is expected to change after 2013Mobile Phones Units 1,599 1,665 1,742 1,832 1,995 2,154 6.1%when smart-phone will take over it.Brief Specification _ 256Mb / 512Mb / 1GbFEATURES DESCRIPTIONDensity 256Mb 512Mb 1GbArchitecture Single-Level CellPower Supply 1.8V: 1.7V ~ 1.95V / 3.3V: 2.7V ~ 3.6V 3.3V: 2.7V ~ 3.6VMemory Cell Array x8 : (32M + 1024K) x 8bits x16 : (16M + 512K) x 16bits x8 : (64M + 2M) x 8bitsX16 : (32M + 1M) x 16bits x8 : (128M + 4M) x 8bitsPage Size x8:(512 + 16)Bytes / x16:(256 + 8)Words x8:(2K + 64)BytesRandom Access 15us(1.8V) / 12us(3.3V)25usSerial Page Access 50ns(1.8V) / 30ns(3.3V)25nsProgram / Block EraseTime 200us(Typ) / 2ms(Typ)Copy Back ProgramOperation Fast Page copy without external bufferingOTP area 16Kbytes/8K words(32 pages)16Kbytes(8 pages)Hardware Data Protection Program / Erase locked during Power transitionsEndurance /Data100K P /E C l ith 1bit ECC /10Endurance / Data Retention 100K Program / Erase Cycles with 1bit ECC / 10years Temperature Range 0℃to +70℃/ -40℃to +85℃P k I f ti 48P TSOP (1220)/48B fBGA (99)48P TSOP (12x20mm)fBGA (9x9mm)Package Information 48P TSOP (12x20mm)/ 48B fBGA (9x9mm)48B fBGA (9x9mm)48B fBGA (6.5x8mm)Phase III ; SPI NAND Flash1Gb (SPI, Quad IO), 3.3V, 104Mhz(133Mhz@15pF), 8x6 WSON -Very high reliability,competitive cost,simpler package form factorHigh VoltageHOLD#Very high reliability, competitive cost, simpler package form factorControl Logic GeneratorI/O Shift RegisterW#CS#SCLKSISOECCGeneratorSPI InterfaceAddress Registerand Counter2K Bytes Data Buffer StatusRegister7FFFFFFh7FE0000hEmbedded ECCX DecoderEmbedded ECCY Decoder0000000h001FFFFhNAND Cell ArraySLC NAND Flash Product Roadmap 20132014ES CS MP Q1Q2Q3Q4Q1Q2Q3Q41.8V/3.3V256Mb 32Mx8 / 16Mx16Small Block TSOP/BGA/MCP1.8V / 3.3V512Mb 1.8V/3.3V64Mx8 / 32Mx16Small Block TSOP/BGA/MCP1.8V / 3.3V1Gb 3.3V128Mx8Large Block 3.3VTSOP/BGA/MCPNOTE) Endurance(256Mb/512Mb/1Gb) : 100K Program/Erase Cycles (with 1bit/528byte ECC)SLC NAND Flash Product Roadmap –cont’20132014ES CS MPQ1Q2Q3Q4Q1Q2Q3Q42Gb 1.8V/3.3V 256Mx8 / 128Mx16Large Block TBDLarge Block4Gb 1.8V/3.3V 512Mx8 / 256Mx16Large Block TBDNOTE) Endurance(2Gb/4Gb) : 100K Program/Erase Cycles (with 4bit/528byte ECC)Serial NAND Flash Product Roadmap20132014 ES CS MPQ1Q2Q3Q4Q1Q2Q3Q4 33V1Gb3.3V(128M+4M)x Bytes104MHzInternal ECC codeti3.3VgenerationWSON/SOP104MHzInternal ECC code2Gb/4GbgenerationTBD NOTE) Endurance : 100K Program/Erase CyclesCertificationsISO9001 : 2008• Oct 02, 2008 Acquired ISO9001ISO14001 : 2004• Oct 02, 2008 Acquired ISO14001Eco-Partner• Feb 09, 2009 Acquired Eco-Partner Di i i C tifi t N R i t ti D t E i d D t SDivision Certificate No.Registration Date Expired Date Sponsor ISO9001: 2008QI8221/082008.102013.11ICRISO14001:2004EI3363/082008.102013.11ICREco-Partner EPC-52452009.02-SAMSUNGco a t e C55009.0S SU GSummary ; Core Competencies Leading edge NAND Memory technology •High level of NAND Flash design experience and capability for optimized architecture D i d D l t C bilit fk ith li bl lit•Design and Development Capability of new packages with reliable quality •Market leading test technology, which is core factor of MCP quality•Stable quality control through field-proven management systemS l ti h ld i t d d li d IP f d Strategic relationship with Supply-ChainStable support with Strategic relationshipATO Solution holds 6registered and 6applied IPs for NAND and NAND SPI •Stable support with Strategic relationship Optimized operation and organization focusing on customer service•Simplified and optimized operation and logistics, which are result in reasonable lead time and customer service Memory specialized human resources•Key Engineering Resources are all from Major Memory Companies with 11+ years experience-Memory : Hynix, Samsung, STMicroelectronics(Numonyx), SMIC-Packaging : Stats ChipPAC, Amkor, Winpac-Test : iTEST, HisemFlexible and dynamic customer service•Customer Specific design and technical solutionThank you for your attention. Thank you for your attentionKOREA(HQ)CHINATAIWAN。

Nand_flash工作原理

Nand flash芯片工作原理------------------------------------Nand flash芯片型号为Samsung K9F1208U0B,数据存储容量为64MB,采用块页式存储管理。

8个I/O引脚充当数据、地址、命令的复用端口。

芯片内部存储布局及存储操作特点:一片Nand flash为一个设备(device), 其数据存储分层为:1 (Device) = 4096 (Blocks)1 (Block) -= 32 (Pages/Rows) 页与行是相同的意思,叫法不一样1 (Page) = 528 (Bytes) = 数据块大小(512Bytes) + OOB 块大小(16Bytes)在每一页中,最后16个字节(又称OOB)用于Nand Flash命令执行完后设置状态用,剩余512个字节又分为前半部分和后半部分。

可以通过Nand Flash命令00h/01h/50h分别对前半部、后半部、OOB进行定位通过Nand Flash内置的指针指向各自的首地址。

存储操作特点:1. 擦除操作的最小单位是块。

2. Nand Flash芯片每一位(bit)只能从1变为0,而不能从0变为1,所以在对其进行写入操作之前要一定将相应块擦除(擦除即是将相应块得位全部变为1).3. OOB部分的第六字节(即517字节)标志是否是坏块,如果不是坏块该值为FF,否则为坏块。

(转载注:应该是每块的第一页的第六个字节。

)4. 除OOB第六字节外,通常至少把OOB的前3个字节存放Nand Flash硬件ECC码NAND FLASH的工作原理- to beginner2007-04-23 23:43NAND FLASH 是一种大容量、高速的存储技术。

其接口较为简单,如果没有专门的nand flash控制器,甚至可以用io口与之对接。

其编程也相对简单,只要了解如下关键概念就可以:1.nand flash内部有管理单元,管理单元负责对nand flash的实际单元的操作。

AFND1G08U(S)3A 1Gb NAND 韩国ATOsolution

Remark Preliminary

- Add 9mmx11mm 63ball BGA PKG option -Added operation voltage 3.3V option - Add 12mmx20mm 48Pin TSOP PKG option - Add 6.5mmx8mm 48ball BGA PKG option - Add 9mmx9mm 63ball BGA PKG option

Rev02 Jul. 2015

Confidential

5

1G bit (128Mx8Bit)NAND FLASH

PIN CONFIGURATION (TSOP1)

N.C N.C N.C N.C N.C N.C R/B RE/ CE/ N.C N.C Vcc Vss N.C N.C CLE ALE WE/ WP/ N.C N.C N.C N.C N.C 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 N.C N.C N.C N.C I/O7 I/O6 I/O5 I/O4 N.C N.C N.C Vcc Vss N.C N.C N.C I/O3 I/O2 I/O1 I/O0 N.C N.C N.C N.C

1G bit (128Mx8Bit)NAND FLASH

1Gb NAND FLASH

Rev02 Jul. 2015

Confidential

1

1G bit (128Mx8Bit)NAND FLASH

Revision No. Rev. 00 Rev.01 Initial Draft

Huatech DH03AE 3节锂电池保护IC数据手册说明书

概述DH03AEFS14/R5是一款专用于3串锂电池或聚合物电池的保护芯片。

它具有高精度的电压检测和电流检测电路,实现过压(OV)保护、欠压(UV)保护、放电过流(DOC)保护、短路(SC)保护、高温(OT)保护和低温(UT)保护。

DH03AEFS14/R5集成了场效应管的驱动电路,DH03AEFS14/R5能够直接驱动N型的充电管和N型的放电管。

DH03AEFS14/R5处于正常状态时消耗的电流低于35uA,断电状态时低于3uA。

DH03AEFS14/R5封装为14引脚的SOP封装。

特点各节电池的高精度电压检测过充电检测电压:4.20V过充电迟滞电压:0.15V过放电检测电压:2.7V过放电迟滞电压: 0.3V3段放电时的过电流检测保护功能过电流检测电压1:100mV过电流检测电压2:200mV短路检测电压:400mV放电过流和短路解除条件:充电器连接或者负载断开。

内建的断线保护。

内建的充电和放电高温保护。

内建的充电和放电低温保护。

低功耗的工作状态:正常状态:<35uA断电状态:<3uA应用电动工具典型应用电路103RTC1K 1K1K 510R 1N4148CHC DHCDH03VMON VCS CUVT COVTCOCT VSS VCCVC3VC2VC1TSVTH1234567891011121314电池3电池2电池10.1u0.1u4.7u0.1u0.1u0.1uR 100R5.1K放电管P-P+2M充电管510K0.1u10K10M1uB=3435R (20K)0.1uR S 1M图1 3串电池包的N 型充电管和N 型放电管的同口典型应用电路图103RTC1K1K 1K51R 1N4148CHC DHCDH03VMON VCS CUVT COVTCOCT VSS VCC VC3VC2VC1TSVTH1234567891011121314电池3电池2电池10.1u0.1u 4.7u0.1u0.1u0.1uR 100R 5.1K放电管P-P+充电管510K0.1u10K10MC-2M1u 0.1u200R 4.7uR S 1MSS34B=3435R (20K)图2 3串电池包的N 型充电管和N 型放电管的分口典型应用电路图产品说明产品名称过充电保护阈值 V OVP 过充电保护解除阈值 V OVR 过放电保护阈值 V UVP 过放电保护解除阈值 V UVR 第一级放电过流保护阈值 V DOCP1 DH03AEFS14/R5AAFS14/R54.20 (±0.028V )4.05 (±0.028V )2.70 (±0.09v )3.00 (±0.09v )0.1 ±0.01V订货信息型号 封装 包装数量 丝印 DH03AEFS14/R5SOP-14卷盘,2500 PCSDH03AE xxxx管脚分布VCS DHC VMON CHC VC2VC3VCC SOP-14123414131211CUVT 5VC110COCTCOVT 67VTH98TS VSS图3 管脚分布管脚描述引脚号 符 号 描 述1CHC 充电控制MOS 栅极连接引脚 2 VMON 负载开路和充电器接入检测引脚 3 DHC 放电控制MOS 栅极连接引脚 4 VCS 充放电过电流检测引脚5 CUVT 接电容,设置放电过流2检测延时6 COVT 接电容,设置过充电检测延时7 COCT 接电容,设置放电过流1检测延时、过放电检测延时8VTH 外部电阻偏置输出引脚,设定和调节保护温度点9 TS 接负温度系数热敏电阻,温度检测 10 VSS 接地引脚11 VC1 第一节电池正极、第二节电池负极连接引脚12 VC2 第二节电池正极、第三节电池负极连接引脚13 VC3 第三节电池正极连接引脚14VCC芯片电源,第三节电池正极连接引脚电气参数(环境温度为25℃)符号项目说明最小值典型值最大值单位过充电和过放电保护阈值V OVP过充电保护阈值 4.20VV OVP- 0.028V OVPV OVP+ 0.028VV OVP_HYS过充电解除迟滞电压0.15 VV OVR过充电解除阈值V OVR = V OVP– V OVP_HYSV OVR- 0.028V OVRV OVR+ 0.028VV UVP过放电保护阈值 2.7VV UVP- 0.090V UVPV UVP+ 0.090VV UVP_HYS过放电解除迟滞电压0.3V V UVP_HYS VV UVR过放电解除阈值V UVR = V UVP + V UVP_HYSV UVR- 0.090V UVRV UVR+ 0.090V放电过流和短路保护V DOCP11级放电过流保护阈值90 100 110 mV V DOCP22级放电过流保护阈值V DOCP2=2*V DOCP1180 200 220 mV V SCP短路保护阈值V SCP=4*V DOCP1360 400 440 mV 放电高温保护和充电高温保护T DOTP放电高温保护阈值根据R VTH设定T DOTP-5 T DOTP T DOTP+5°CT DOTP_HYS放电高温解除迟滞值15 °CT DOTR放电高温解除阈值T DOTR = T DOTP– T DOTP_HYS T DOTR-5 T DOTR T DOTR+5°CT COTP充电高温保护阈值根据R VTH设定T COTP-5 T COTP T COTP+5°CT COTP_HYS充电高温解除迟滞值 5 °CT COTR充电高温解除阈值T COTR = T COTP– T COTP_HYS T COTR-5 T COTR T COTR+5°CT DUTP放电低温保护阈值根据R VTH设定T DUTR-5 T DUTR T DUTR+5°CT DUTP_HYS放电低温解除迟滞值10 °CT DUTR放电低温解除阈值T DUTR = T DUTP + T DUTP_HYS T DUTR-5 T DUTR T DUTR+5°CT CUTP充电低温保护阈值根据R VTH设定T CUTR-5 T CUTR T CUTR+5°CT CUTP_HYS充电低温解除迟滞值 5 °CT CUTR充电低温解除阈值T CUTR = T CUTP + T CUTP_HYS T CUTR-5 T CUTR T CUTR+5°CV IN_DSG放电状态检测电压V VCS>V IN_DSG时电池包被认为是放电状态;否则,电池包被认为是充电状态2 4 6 mV符号项目说明最小值典型值最大值单位外部可编程的保护和解除延迟时间t OVP过压保护延迟时间C COVT=0.1uF 0.7 1.0 1.3 S t UVP欠压保护延迟时间C COCT=0.1uF 0.7 1.0 1.3 S t UV_PD欠压断电延迟时间C COCT=0.1uF 4.3 6.2 8.1 St DOCP11级放电过流保护延迟时间C COCT=0.1uF 0.7 1.0 1.3 St DOCP22级放电过流保护延迟时间C CUVT=0.1uF 0.07 0.1 0.13 St SCP短路保护延迟时间内部固定100 250 500 μS t TDET温度检测周期C COVT=0.1uF 0.7 1.0 1.3 S 电源(VCC)V CC输入电压 4.0 25 V I VCC_NOR电源电流正常状态,V CELL=3.5V 30 35 μAI VCC_PD 断电状态,V CELL=1.8VCTL引脚连接V SS2 3 μAV POR芯片复位电压 4.8 6.0 V V VCC_CHGINI起始充电的VCC电压 1.8 2.2 2.8 V V VREGH放电管的驱动电压V CC>V VREGH+1V 9.0 10.5 12 VV CC<V VREGH+1V V CC-1.5 V CC-1 V CC-0.5 V 电池输入(VC3,VC2,VC1)I VC3V C3正常状态电流3节电池, V CELL=3.5V 1.5 2.5 μAI VCX V C(n)正常状态电流,n=1to2V CELL=3.5V -0.5 +0.5 μA驱动电路(CHC,DHC)I CHC CHC引脚流出电流V CELL=3.5V,V CHC=V CC–3V 3 6 9 μA V CELL=V OVP+0.2V,V CHC=V CC–3VHi-Z μAV DHCHDHC引脚输出电压V VCS=0V V VREGH V V DHCL V VCS>=V DOCP10.4 V功能描述1、过充电状态当任何一节电池电压高于V OVP且时间持续t OVP或更长,DH03AEFS14/R5的CHC引脚将变成高阻态。

2440芯片

2440芯片2440芯片是一款由韩国三星公司开发的基于 ARM920T 核心的嵌入式处理器。

2440芯片主要用于嵌入式系统的设计和开发,包括智能手机、平板电脑、汽车导航、电子书等应用领域。

2440芯片采用了先进的 0.13 微米 CMOS 工艺,整合了 CPU、内存控制器、外设控制器等核心功能模块。

它采用了 16 位宽的内核总线来提供高性能的数据传输能力,可以实现每秒3000 万次的浮点运算。

2440芯片支持多种外设接口,包括 LCD 显示屏接口、触摸屏接口、摄像头接口、以太网接口等。

它还内置了多个串行通信接口,如 UART、SPI、I2C 等,可以方便地与外部设备进行通信,更好地满足不同应用的需求。

2440芯片还具有低功耗和低温升的特点。

它采用了自适应调压(DVFS)技术,可以根据实际负载情况智能调整工作频率和电压,从而降低功耗并延长电池寿命。

此外,2440芯片还采用了三星专利的温度感知功率控制(TPC)技术,可以根据芯片温度自动调整频率和电压,从而保持芯片在安全工作温度范围内。

2440芯片的软件开发支持比较完善。

它支持 Linux、Windows CE、Android 等主流嵌入式操作系统,并提供了丰富的软件开发工具和开发文档,方便开发人员进行应用程序的开发和调试。

此外,2440芯片还提供了一套基于 C 语言的底层驱动库,可以方便地访问芯片的各种功能和外设接口。

总的来说,2440芯片是一款功能强大、性能优越的嵌入式处理器。

它具有高性能、低功耗、低温升等特点,并且支持多种外设接口和主流操作系统,可以广泛应用于各种嵌入式系统的设计和开发。

AFND1G08U3-CKA规格书(K9F1G08)

• Copy-Back PROGRAM Operation - Fast Page copy without external buffering

z Status Register - Normal Status Register (Read/Program/Erase)

• Security features -OTP area, 16Kbytes(8 pages)

Initial Draft

June. 2012

Preliminary

Rev.01

Add new FBGA PKG dimension option (6.5x8.0mm 48B)

Nov. 2012

Rev. 02 Rev. 03

tRP(/RE Pulse Width) 12ns Æ 15ns

- VOH, VIL, VOL values control - Read Operation Figure modification - Write Protect figures added

PACKAGE DIMENSIONS

48-PIN LEAD/LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)

Rev.03 Jan. 2013

Confidential

7

1G bit (128Mx8Bit)NAND FLASH

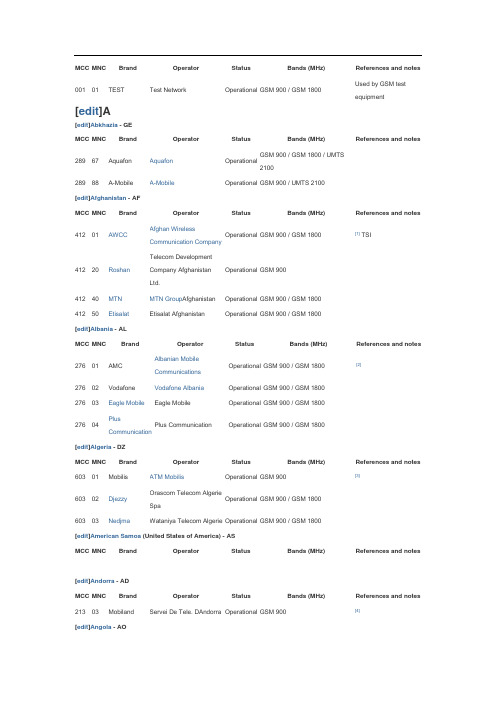

各国各运营商MCC,MNC号

[edit]Angola - AO[edit]Barbados - BB[edit]Republic of the Congo - CG[edit]Egypt - EG[edit]Israel - ILThis section does not cite any references or sources. Please help improve this section by adding citationsto reliable sources. Unsourced material may be challenged and removed. (August 2010)MCC MNC Brand Operator Status Bands (MHz) References and notes 401 01 Beeline KaR-Tel LLP Operational GSM 900 / GSM 1800401 02 Kcell GSM Kazakhstan Ltd Operational GSM 900 / GSM 1800401 07 Dalacom Operational CDMA2000 800401 08 Kazakhtelecom Operational CDMA2000 800 / CDMA2000 450401 77 MobileTelecomServiceMobile Telecom ServiceLLPOperational GSM 900[edit]Kenya - KEMCC MNC Brand Operator Status Bands (MHz) References and notes 639 02 Safaricom Safaricom Limited Operational GSM 900 / GSM 1800 [64]639 03 Airtel Bharti Airtel Operational GSM 900 [24]639 07 OrangeKenyaTelkom Kenya OperationalCDMA2000 / GSM 900 / GSM1800639 05 yu Econet Wireless Kenya Operational GSM 900 / GSM 1800 [64][edit]Kiribati - KIMCC MNC Brand Operator Status Bands (MHz) References and notes545 09 KiribatiFrigateTelecom Services KiribatiLtdOperational GSM 900[edit]North Korea - KPMCC MNC Brand Operator Status Bands (MHz) References and notes467 192 Koryolink Cheo Technology JvCompanyOperational UMTS 2100467 193 SunNet Korea Posts andTelecommunicationsCorporationOperational GSM 900[65] UMTS 2100 ispending[edit]South Korea - KRMCC MNC Brand Operator Status Bands (MHz) References and notes450 02 KT KT Operational CDMA2000 1700 Formerly Hansol PCS, Merged with KT450 03 Power 017 Shinsegi Telecom, Inc. NotoperationalCDMA2000 800Merged with SKTelecom in 2002450 04 KT KT Operational CDMA2000 1700 HSM 450 05 SKT SK Telecom Operational CDMA2000 800 / UMTS 2100 [66] 450 06 LGT LG Telecom Operational CDMA2000 1700450 08 olleh KT Operational UMTS 2100[edit]Moldova - MD[edit]Morocco - MA。

Raveon技术有限公司应用说明书AN238:GPIO开路 放电输出

Application NoteAN238 Raveon Technologies CorpCopyright 2018 1Raveon Technologies Corp.GPIO Open Collector/Drain OutputBy John SonnenbergRaveon Technologies CorpS u m m a r yRaveon has products with various IO options, some of which include Open Drain (OD) or Open Collector (OC) outputs. This Application Note AN238 describes how these kinds of features can be used. These IOs are used to turn things on and off. The RV-M21G and RV-M22G Tech Series radios with the GPIO interface can be configured to have an Open Collector output. Here is a picture of the RV-M21G. This document refers to these M21 and M22 radios at RV-M2x data radios. The RV-M22 is smaller than the RV-M21 version, but less RF output power also.Open Drain outputs are great for turning on lights, valves, relays, and many other devices. Open Drain (OD) connects the load to ground when it is turned on.G P I O I n t e r f a c e o n R V -M 21 a n d R V -M 22 D a t a R a d i o sThe General Purpose IO (GPIO) front panel interface has many IO options on 3 pins to remotely control things or monitor things. Pins 3,4,5 are configurable.A : Digital TTL Inputs, C : Open Drain MOSFETD : DC Power switch outputs.E : Analog Voltage Inputs.GPIO uses the same IO connector as the RS-485, and has serial IO and general purpose IO functions that are software configurable. .Applicatoin NoteAN238 Rev A2O p e n D r a i n v s O p e n C o l l e c t o rOpen Drain means the semiconductor’s output port is directly connected to the "drain" pin of a MOSFET. It is similar to "Open Collector", where the output port is on a collector of a TRANSISTOR. OC is a traditional way, but OD is more power full and more reliable, so we provide Open Drain output to drive relays, lights, and other devices.E n a b l i n g t h e G P I O O p e n D r a i n f e a t u r eRaveon’s Tech Series Radios GPIO General Purpose IO interface pins can be configured in different ways.Connect an RS232 serial port to the RX in and TX outpins of the GPIO interface to send commands anddata into the product. See the user manual on how toenter the command mode. (+++ enters commandmode)To set the IO pin to Open Drain mode, have Raveonconfigure the radio before shipped to you, or use theIOPIN command to configure it.Application NoteAN238 Raveon Technologies Corp IOPIN XX M is the command to set the GPIO bits on the Tech Series GPIO front panel to inputs or outputs. Enter IOPIN <enter> in command mode to read pin settings.XX parameter are the Hexadecimal representation of the pins being configured. For example, to configure bits 0 and 1, XX should be set to 3. FYI: GPIO pin #4 is called IO1 and isdesignated as XX bit 1, which in hex is XX=02.XX is Hexadecimal. To specify all 3 IO pins IO0-IO2, the XX value is 7. (4+2+1)M is the IO Type code A: Digital TTL Inputs, B: Digital TTL Outputs, C: Open Drain MOSFET outputs, D: DC Power switch outputs, E: Analog Voltage Inputs. Different products have different varieties of GPIO features. Check your product’s data sheets to see what GPIO features it supports on which IO pins.IOPIN 1 C command sets The IO pin 0 (first pin) to Open Drain mode.IOPIN 1 C command sets The IO pin 0 (first pin) to Open Drain mode.IOPIN 2 C command sets The IO pin 1 to Open Drain mode.IOPIN 7 C command sets all 3 IO pins to Open Drain mode.H o w O p e n D r a i n w o r k sInside Raveon’s products with GPIO and Open Collector (OD) features, there is an OD output pin connected to the collector of a MOSFET inside the product. The MOSFET is also connected to the ground of the product.Copyright 2018 3 Raveon Technologies Corp.Use Open Drain for enabling: Lights, Relays, LEDs, Valves, AC power switches …When the GPIO pin is OD mode, and the output is SET, the MOSFET is turned on, and the IO pin is shored to ground (GND). The device connected to OD will normally be connected to a voltage power supply (Vcc) or a battery. When the OD pin shorts to ground the device will turn on. The device can be an LED, light, relay, valve, or many other devices. Devices with inductors, such as a relays, should have a diode connected to the device so that the voltage spike that is generated when its turns on and off gets limited.Use a diode to protect the GPIO interface and keep the wires safe. There are many ways to reduce voltage spikes when switching a relay. Some add capacitors, some add extra diodes with resistors. Do the right thing for your system. The Tech Series GPIO interface uses a MOSFET like the NXP PMV130ENEA . Its specs are:drain-source voltage : 40VMax drain current: 2.1Ajunction temperature -55 to 150Celectrostatic discharge voltage 1000VU s i n g t h e O p e n D r a i n(O D)f e a t u r ePower on default mode on OD IO pins is open. The OD output is not shorted to ground when the device powers on. When the device receives an command via the local serial port or over the air using the radio modem, a command can turn on the OD making the OD IO pin short to ground.See the product’s data sheet for information about resi stance to ground and maximum current that should be drawn from the IO pin when the open drain is shored to ground.There are a number of ways to enable on the Open Drain output.A.Local commands in the command mode.B.Remote Over The Air (OTA) commands sent to the products.C.Remote Over The Air (OTA) MODBUS messages sent to the product.L o c a l c o m m a n d s i n t h e c o m m a n d m o d eSee the product’s Technical Manual or User Manual for a list of commands that the product supports. Most products with GPIO support these local commands that can by typed into the product, or sent via software, when the product is in the Command Mode. Raveon products can also utilize a serial port protocol called WMX. WMX enables a user to send commands into a data radio product when it is in operating mode, not command mode, and the WMX command will still be executed in operating mode.Here are the commands the RV-M21 and RV-M22 Tech Series radios support.Application NoteAN238 Raveon Technologies CorpCopyright 2018 5 Raveon Technologies Corp.CBIT command is to clear a bit. It will disable the Open Drain, and the IO output will not connect to ground if the output is cleared with the CBIT command.SBIT command is to set a bit. It will turn on the Open Drain, and the IO output willconnect to ground with the SBIT command if the parameters of the SBIT are for the OD IO pin that is used and configured for OD.TBIT command is to set a bit for some time. It will turn on the Open Drain for some time. The IO output will connect to ground with the SBIT command if the parameters of the SBIT are for the OD IO pin that is used and configured for OD. The specified OD IO pin will stay shored to ground for the number of mS specified in the TBIT command. To enable MODBUS protocol reception on the device, execute the MODB X command. MODB 1 to enable RTU MODBUS.W M X c o m m a n d sAll of the Local Commands specified above can be executed with the WMX message. WMX can be enabled on the product with the command WMX 1.See the WMX Technical Node .PDF and the WMX user manual for more WMX information.Your custom software can issue WMX messages into a data radio and the message will be processed. If you pass in a WMX message to a modem, that has the TOID set to the ID of a remote radio you want the message to be sent to, the radio will send the data in the WMX message to the remote radio. If you tagged the WMX message as a “Command” the remote radio will execute the command when it receives the transmission from the radio that you passed the WMX message into.WMX can pass over two types of data: 1) Actual rad message data. 2)Commands to be executed. Because it has the command feature, you can pass those SBIT, CBIT, TBIT or any other command into a modem using WMX commands messages, and the get sent over-the-air to the remote radio or SCADA device and the command is executed remotely.Over the air WMX command can set and clear the Open Drain IO pins. Most WMX users have incorporated the WMX protocol into their master controller software. OneRaveon’s website is a free software tool called Radio Manager. Radio Manager is for communication to radios via serial ports or TCP/IP connects. It also has a WMX feature to send and receive WMX messages so you can experiment with WMX.M O D B U S c o m m a n d sThe RV-M21 and RV-M22 Tech Series radios have a communication feature option thatis compatible with the MODBUS RTU protocol.You Master Controller computer will pass aMODBUS message to a Data Radio modem. TheRadio modem connected to your PC will transmitthe message to the RV-M2x Tech Series radio thatwill process the MODBUS message, and send the response.For more information about MODBUS RTU messages, seehttps:///modbus-information/or read Raveon’s app note AN234 for SCADA and MODBUS info about Raveon’s SCADA products. In the RV-M21 data radio modem’s software m ust be version D30 or larger to utilize MODBUS.Raveon Application note AN230 contains all information about using the MODBUS protocol AN230 (ModbusMx)With Raveon’s Pro ducts that have GPIO interfaces with Open Drain, such as the RV-M21 and RV-M2 data radio modems.M O D B U S R T U C o m m a n d sModbus is a registered trademark of MODICON, Inc.Messages sent from devices that utilize SCADA and Telemetry protocols such as MODBUS RTU are often called “Telegrams”. The MODBUS function 5 (Force single coil) can be used to set of clear the Open Drain IO pins.Modbus data is specified as big-endian, which means the most significant value is at the lowest address.(05) Force single coil to turn on the Open Drain.To set the state of output bits and Open Drain (OD) pins (MODBUS refers to them “coils”), function code 05 is used to send the set command to the remote device. To set a OD open (coil off) (0) send 0x0000 and to enable and Open Drain output (coil on) (1) send 0x00FF. The data per OD output are two bytes.When broadcast, the same function forces the same data output in all attached slave devices.Function code 05 (Force Coil Status) is the code used in MODBUS to send a message to control an Open Drain. The command structure is:Application NoteAN238 Raveon Technologies CorpThe structure of the 05 (Force Coil Status) response back is:Request:96 05 00 02 FF 00 31 1DResponse:96 05 00 02 FF 00 31 1D (it reported coil 2 is on)The Register control coils in MODBUS is referred to as a “Coil Address” In Applciation note AN230, Raveon’s register list has the register number (Coil address) for all the IO pins and SCADA features that can be accessed with the MODBUS SCADA protocol.IO0 is Register 1. IO1 is Register 2, IO2 is Register 3. Use these register numbers to execute MODBUS messages that set coils or read coil status.For Example, to turn on the Open Drain output (Pin to Ground) for device 30 (0x1E) using a MODBUS “Force Single Coil” message which used function code 5, here are some example messages in hex bytes. Each are 8 bytes long.Device Function Register Data CRCIO0 On:1E 05 00 01 FF 00 DF 95IO1 On:1E 05 00 02 FF 00 2F 95IO2 On:1E 05 00 03 FF 00 7E 55Copyright 2018 7 Raveon Technologies Corp.For additional information, contact: Raveon Technologies Corporation 2320 Cousteau CourtVista, CA 92081 - USAPhone: 1-760-444-5995Fax: 1-760-444-5997Email:****************。

AFND5608U1-CKAK规格书 (K9F5608)