英飞凌推微型晶圆级芯片封装的工业级eSIM卡—SLM 97

全球15家射频器件供应商盘点(附国内上市公司名单)

全球15家射频器件供应商盘点(附国内上市公司名单)如今,手机中射频(RF)器件的成本越来越高。

一个4G全网通手机,前端RF套片的成本已达到8-10美元,含有10颗以上射频芯片,包括2-3颗PA、2-4颗开关、6-10颗滤波器。

未来随着5G的到来,RF套片的成本很可能会超过手机主芯片。

再加上物联网的爆发,势必会将射频器件的需求推向高潮。

成本昂贵,95%的市场被欧美厂商把持通常情况下,一部手机主板使用的射频芯片占整个线路面板的30%-40%。

据悉,一部iPhone 7仅射频芯片的成本就高达24美元,有消息称苹果今年每部手机在射频芯片上的投入将历史性地超过30美元。

随着智能手机迭代加快,射频芯片也将迎来一波高峰。

目前,手机中的核心器件大多已实现了国产化,唯独射频器件仍在艰难前行。

据悉,全球约95%的市场被控制在欧美厂商手中,甚至没有一家亚洲厂商进入顶尖行列。

射频器件细分领域目前,手机中的射频器件主要包括功率放大器(PA)、双工器、射频开关、滤波器(包括SAW与BAW两种)、低噪放大器(LNA)等等。

归结起来,射频器件主要三大细分领域为射频滤波器、射频开关、PA芯片(功率放大器芯片)。

滤波器:对于中国公司来说,滤波器是最难跨过的一道门槛,因为面临着专利和工艺两大难题,所以目前几乎没有能够量产的国产Saw滤波器。

由于芯片太厚,都没法做进集成模块,只能做外挂。

总体而言,国内的滤波器目前还处在中低端。

SOI射频开关:国内做SOI射频开关的公司已有20-30家,价格战已开始进入白热化。

其中,中国电科55所研制生产的GaAs及SOI 移动终端射频开关产品在华为、中兴等知名国产品牌移动终端产品中得到广泛应用,实现年出货量2亿只。

特别是SOI移动终端射频开关产品,采用了GPIO和MIPI控制模式,具有高效率、低损耗、高隔离的技术优势,同时做到了尺寸更小、成本更低、集成度更高。

PA(功率放大器):手机中除主芯片外最重要的外围元件之一,影响着手机的信号强度、通信质量以及基站效率。

IC+最新85NM工艺的PHY IP101G_DS_R01_20121224

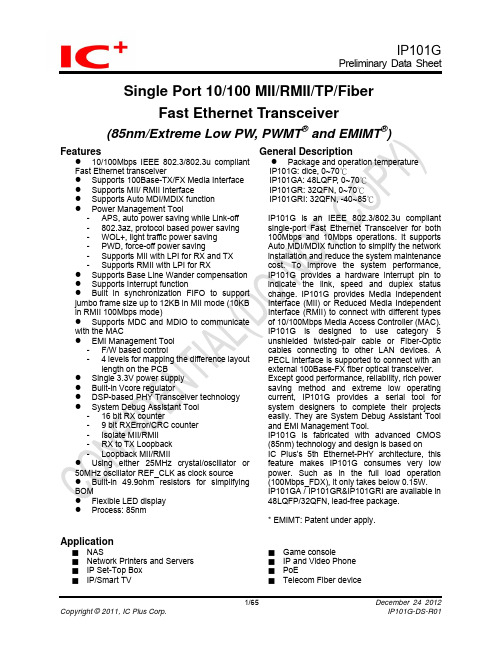

Single Port 10/100 MII/RMII/TP/FiberFast Ethernet Transceiver(85nm/Extreme Low PW, PWMT ® and EMIMT ®)Features General DescriptionIP1IP1IP1IP1z 10/100Mbps IEEE 802.3/802.3u compliant Fast Ethernet transceiverz Supports 100Base-TX/FX Media Interface z Supports MII/ RMII Interfacez Supports Auto MDI/MDIX function z Power Management Tool- APS, auto power saving while Link-off - 802.3az, protocol based power saving - WOL+, light traffic power saving - PWD, force-off power saving- Supports MII with LPI for RX and TX - Supports RMII with LPI for RXz Supports Base Line Wander compensation z Supports Interrupt functionz Built in synchronization FIFO to support jumbo frame size up to 12KB in MII mode (10KB in RMII 100Mbps mode)z Supports MDC and MDIO to communicate with the MACz EMI Management Tool - F/W based control- 4 levels for mapping the difference layoutlength on the PCBz Single 3.3V power supply z Built-in Vcore regulatorz DSP-based PHY Transceiver technology z System Debug Assistant Tool - 16 bit RX counter- 9 bit RXError/CRC counter - Isolate MII/RMII - RX to TX Loopback - Loopback MII/RMIIz Using either 25MHz crystal/oscillator or 50MHz oscillator REF_CLK as clock sourcez Built-in 49.9ohm resistors for simplifying BOMz Flexible LED display z Process: 85nmz Package and operation temperature 01G: dice, 0~70℃01GA: 48LQFP , 0~70℃ 01GR: 32QFN, 0~70℃ 01GRI: 32QFN, -40~85℃IP101G is an IEEE 802.3/802.3u compliant single-port Fast Ethernet Transceiver for both 100Mbps and 10Mbps operations. It supports Auto MDI/MDIX function to simplify the network installation and reduce the system maintenance cost. To improve the system performance, IP101G provides a hardware interrupt pin to indicate the link, speed and duplex status change. IP101G provides Media Independent Interface (MII) or Reduced Media Independent Interface (RMII) to connect with different types of 10/100Mbps Media Access Controller (MAC). IP101G is designed to use category 5 unshielded twisted-pair cable or Fiber-Optic cables connecting to other LAN devices. A PECL interface is supported to connect with an external 100Base-FX fiber optical transceiver. Except good performance, reliability, rich power saving method and extreme low operating current, IP101G provides a serial tool for system designers to complete their projects easily. They are System Debug Assistant Tool and EMI Management Tool.IP101G is fabricated with advanced CMOS (85nm) technology and design is based onIC Plus’s 5th Ethernet-PHY architecture, this feature makes IP101G consumes very low power. Such as in the full load operation (100Mbps_FDX), it only takes below 0.15W. IP101GA / IP101GR&IP101GRI are available in 48LQFP/32QFN, lead-free package.* EMIMT: Patent under apply.Application■ NAS■ Network Printers and Servers ■ IP Set-Top Box ■IP/Smart TV■ Game console■ IP and Video Phone ■ PoE■Telecom Fiber deviceTable Of ContentsTable Of Contents (2)List of Figures (4)List of Tables (5)Revision History (6)Features comparison between IP101G and IP101A/IP101AH (7)Transmit and Receive Data Path Block Diagram (8)1Pin diagram (9)2Dice pad information (11)3Pin description (12)3.1IP101GA pin description (12)3.2IP101GR/GRI pin description (16)4Register Descriptions (19)4.1Register Page mode Control Register (20)4.2MII Registers (20)4.3MMD Control Register (30)4.4MMD Data Register (31)4.5RX Counter Register (34)4.6LED Mode Control Register (35)4.7WOL+ Control Register (35)4.8UTP PHY Specific Control Register (38)4.9Digital IO Pin Control Register (39)5Function Description (41)5.1Major Functional Block Description (41)5.1.1Transmission Description (41)5.1.2MII and Management Control Interface (42)5.1.3RMII Interface (43)5.1.4Flexible Clock Source (45)5.1.5Auto-Negotiation and Related Information (45)5.1.6Auto-MDIX function (46)5.2PHY Address Configuration (46)5.3Power Management Tool (47)5.3.1Auto Power Saving Mode (47)5.3.2IEEE802.3az EEE (Energy Efficient Ethernet) (48)5.3.3Force power down (48)5.3.4WOL+ operation mode (48)5.4LED Mode Configuration (52)5.5LED Blink Timing (52)5.6Repeater Mode (52)5.7Interrupt (52)5.8Miscellaneous (52)5.9Serial Management Interface (53)5.10Fiber Mode Setting (54)5.11Jumbo Frame (54)6Layout Guideline (55)6.1General Layout Guideline (55)6.2Twisted Pair recommendation (55)7Electrical Characteristics (56)7.1Absolute Maximum Rating (56)7.2DC Characteristics (56)7.3Crystal Specifications (57)7.4AC Timing (58)7.4.1Reset, Pin Latched-in, Clock and Power Source (58)7.4.2MII Timing (59)7.4.3RMII Timing (60)7.4.4SMI Timing (61)7.5Thermal Data (61)8Order Information (62)9Physical Dimensions (63)9.148-PIN LQFP (63)9.232-PIN QFN (64)List of FiguresFigure 1 Flow chart of IP101G (8)Figure 2 IP101GA 48 Pin Diagram (9)Figure 3 IP101GR/GRI 32 Pin Diagram (10)Figure 4 IP101G dice pad information (11)Figure 5 LPI transition (43)Figure 6 IP101G/GA/GR/GRI MII Mode with LPI transition Block Diagram (43)Figure 7 IP101G/GA/GR/GRI MII Mode without LPI transition Block Diagram (43)Figure 8 IP101G RMII Mode with internal clock Block Diagram (44)Figure 9 IP101G RMII Mode with external clock Block Diagram (44)Figure 10 IP101G RMII Clock Application Circuit (45)Figure 11 IP101G link speed and EEE ability programming guide (46)Figure 12 PHY Address Configuration (47)Figure 13 Magic Packet Format (49)Figure 14 Sleep or wake up automatically programming guide (50)Figure 15 MAC control sleep or wake up programming guide (51)Figure 16 MDC/MDIO Format (53)Figure 17 IP101G Fiber Mode Setting (54)Figure 18 Reset, Pin Latched-In, Clock and Power Source Timing Requirements (58)Figure 19 MII Transmit Timing Requirements (59)Figure 20 MII Receive Timing Specifications (59)Figure 21 RMII Transmit Timing Requirements (60)Figure 22 RMII Receive Timing Specifications (60)Figure 23 SMI Timing Requirements (61)Figure 24 48-PIN LQFP Dimension (63)Figure 25 32-PIN QFN Dimension (64)List of TablesTable 1 Features comparison between IP101G and IP101A/IP101AH (7)Table 2 Register Map (19)Table 3 Flexible Clock Source Setting (45)Table 4 PHY Address Configuration (47)Table 5 WOL+ operation mode (49)Table 6 LED Mode 1 Function (52)Table 7 LED Mode 2 Function (52)Table 8 LED Blink Timing (52)Table 9 SMI Format (53)Table 10 DC Characteristics (56)Table 11 I/O Electrical Characteristics (56)Table 12 Pin Latched-in Configuration Resistor (57)Table 13 Crystal Specifications (57)Table 14 Reset, Pin Latched-in, Clock and Power Source Timing Requirements (58)Table 15 MII Transmit Timing Requirements (59)Table 16 MII Receive Timing Specifications (59)Table 17 RMII Transmit Timing Requirements (60)Table 18 RMII Receive Timing Specifications (60)Table 19 SMI Timing Requirements (61)Table 20 Thermal Data (61)Table 21 Part Number and Package (62)Revision HistoryRevision # Change DescriptionIP101G-DS-R01 Initial release.IP101G-DS-R01-20120522 1) Correct the typo of Digital IO Pin Control Register.2) Modify the operation voltage REGOUT and DVDD_REGIN of DCCharacteristics.IP101G-DS-R01-20120611 1) Correct the typo of Linear Regulator Output Control Register.2) Correct the typo of pin description for pin type PD and PU.3) Modify the register description for RMII_V12 and RMII_V10.4) Correct the typo of register default values.5) Modify the operation voltage DVDD33_IO of DC Characteristics.IP101G-DS-R01-20120622 Add 30 seconds into the definition for register WOL_PLUS_TIMER_SEL.IP101G-DS-R01-20120629 Add the symbol SC (Self Clear) for PHY MII register 0.15 Reset and 0.9Restart Auto-Negotiation.IP101G-DS-R01-20120709 1) Add LED mode 2 in the pin description and function description.2) Correct the table of LED Blink Timing.3) Add more description of PHY Address Configuration and IEEE 802.3az.4) Add ESD reliability of Absolute Maximum Rating.5) Correct the typo of function description for Auto Power Saving Mode.6) Change register P16R16[10] description from HEART_BEAT_EN toReserved.IP101G-DS-R01-20120719 Correct the table of Register Map for page selection.IP101G-DS-R01-20120726 1) Add more description of Register RX2TX_LPBK P1R23[13] for Rx to Txloopback test.2) Add more description on Fiber Mode Setting and latched-in pin signalson AC Timing.3) Add IP101AH into the table of features comparison.IP101G-DS-R01-20120808 1) Correct the I/O type of IP101GA pin description to O(Ouput) for pin24RXER.2) Change the pin name from DVDD33_IO to VDDIO.IP101G-DS-R01-20120821 1) Change the default value of register P16R27 from 0x0022 to 0x0012.2) Remove I/O Slew Rate Control Register.3) Change the register location RMII_WITH_ER from P16R29[0] toP16R29[7].IP101G-DS-R01-20120927 1) Add more description of low power idle (LPI) state in MII and RMIImodes.2) Correct the typo of Physical Dimensions.IP101G-DS-R01-20121101 Change the LED blink timing from “On 80ms -> Off (20~40)ms” to “On 26ms-> Off 78ms”.IP101G-DS-R01-20121113 Add more function description to support Jumbo Frame.IP101G-DS-R01-20121127 Change the LED mode function as same as IP101A.IP101G-DS-R01-20121224 Add the notice that does not let these PHY address pins floating for thelatched-in settings after the power is ready.DisclaimerThis document probably contains the inaccurate data or typographic error. In order to keep this document correct, IC Plus reserves the right to change or improve the content of this document.Features comparison between IP101G and IP101A/IP101AHTable 1 Features comparison between IP101G and IP101A/IP101AHProduct Name IP101GR IP101G IP101GA IP101A IP101AH Package Type 32pin QFN Dice 48pin LQFP48pin LQFPREGOUT(1) Output Voltage and location 1.0V, pin28 1.0V, pad5and pad111.0V, pin82.5V, pin32REGIN Input Voltage and location NA(2) 1.0V, pad23and pad26NA 2.5V, pin8RMII mode setting Pin4 Pad18 Pin1 Pin1 and pin44Fiber mode setting: Fiber FXSD signal: Pin19Pin1Pad39Pad13Pin22Pin43NA Pin24 and pin48Pin37Number of LED 2 4 4 5LED mode 1 and 2 1 and 2LED Blink Timing On 26ms -> Off 78ms On 26ms -> Off 78msPHY address number(3) Single: 0 ~ 1Multi: 2 ~ 31Single: 0 ~ 7Multi: 8 ~ 31Single: 0 ~ 31Center-tap of transformer Do not connect to any power 2.5V input power Built-in 49.9ohm resistors Yes No Power consumption ~150mW ~480mW Process 85nm 0.25μm IEEE 802.3az Yes No10Base TX amplitude ~1.75V (10Base-Te) ~2.5V (10Base-T) WOL+ (Wake On LAN Plus) Yes NoAnalog OFF Yes No16 bit RX counter Yes No9 bit RXER/CRC counter Yes NoRX to TX Loopback Yes No Loopback MII/RMII Yes YesSNI mode No Yes Note 1: Regulator voltage output is for internal use only. Do not supply to any other device.Note 2: Not available for this function. The 1.0V is supplied by the regulator that built-in the chip.Note 3: Do not let these PHY address pins floating for the latched-in settings after the power is ready.Transmit and Receive Data Path Block DiagramFigure 1 Flow chart of IP101G1Pin diagramRXER CRS/LEDMODRXDV/CRS_DV/FX_HEN X1X2RXD2RXD3RXCLK/50M_CLKO DGNDRXD0NCRESET_N IP101GA (LQFP-48)242322212019181716NC NC TXER/FXSDNC Note:Those pins in "blue "are different from IP101A.NC RXD1INTRNC DGNDNC LED3/PHY_AD3VDDIOFigure 2 IP101GA 48 Pin DiagramIP101GR/GRI(VQFN-32)(GND on bottom of chip)RXD3TXCLK/50M_CLKI RXCLK/50M_CLKO LED0/PHY_AD0LED3/PHY_AD3161514131211109RESET_NISET REGOUT MDI_TN MDI_TP MDI_RP MDI_RN RXD2AVDD33Figure 3 IP101GR/GRI 32 Pin Diagram2Dice pad informationIC LogoPad 1Pad 44Pad 11Pad 45Pad 24Pad 31Pad 12Pad 22Pad 23REGINPHYAD_LED028PHYAD_LED129VSS30PHYAD_LED231PHYAD_LED332VDDIO 33RX_CLK REGOUT 34VSSIO RESET_N 35RXD[3]TXER_FXSD 36RXD[2]VSSIO 37RXD[1]15X138RXD[0]16X239RXDV_FIBMOD 17INTR40CRS18COL_RMII 41RXER_INTR 19TX_EN 4220TXD[3]21TXD[2]22TXD[1]23REGINFigure 4 IP101G dice pad information3 Pin descriptionType Description Type DescriptionLI Latched Input in power up or reset PD Internal Pull-Down 250KΩI/O Bi-directional input and output PU Internal Pull-Up 250KΩI Input Hi-Z High impedanceO Output P PowerOD Open Drain3.1 IP101GA pin descriptionIP101GAPin no. Label Type ResetStateDescriptionSerial Management Interface Pins25 MDC I Hi-Z Management Data Interface Clock: This pin provides aclock reference to MDIO. The clock rate can be up to2.5MHz.26 MDIO I/O(PU)I(PU)Management Data interface Input/Output:Thefunction of this pin is to transfer management informationbetween PHY and MAC.MII/RMII Pins2 TXEN I(PD)I(PD)Transmit Enable or Signal Detect.43 TXER/FXSD I(PD)I(PD)Transmit Error or FXSD:This is a dual-function pin which is determined by themedia type selection. If RXDV/CRS_DV/FX_HEN islatched as “0 (default)” upon reset, the TP interface isselected and its function as TXER. If the fiber interface isselected, this pin’s function as FXSD.FXSD:0: Fiber link down; 1: Fiber link upTransmit Enable:TXEN TXER Description1 1 Transmission errorpropagation.0 1 Combine TXD[3:0] that equalto 0001 for request PHY toenter LPI mode.1 00 0Normal operationThis pin TXER must be either floating or connecting toGND in RMII mode.7 TXCLK/50M_CLKI I/O Hi-Z Transmit Clock output or 50M clock input:In MII mode,this pin provides a continuous 25MHz clockat 100Base-TX and 2.5MHz at 10Base-T.In RMII mode, a 50Mhz clock should input to this pin forthe timing reference of the internal circuit.3,4,5,6 TXD[3:0] I Hi-Z Transmit Data Input:IP101GAPin no.LabelType ResetDescriptionStateIn MII mode, TXD[3:0] is synchronous to TXCLK.In RMII mode, TXD[1:0] is synchronous to 50M_CLKI.22 RXDV/CRS_DV/ FX_HEN O/LI (PD) I (PD)Receive Data Valid or Media Type Selection:FX_HENThe input state is latched upon reset to determine whether TP or fiber interface is selected. If it is at logic “0” (default) state upon reset, the TP interface is selected; otherwise the fiber interface is selected. RXDV/CRS_DVIn MII mode, this pin indicates the Receive Data Valid function.In RMII mode, this pin indicates the Carrier Sense and Receive Data Valid function.16 RXCLK/ 50M_CLKO O Hi-Z Receive Clock:In MII mode, this pin provides 25MHz for 100BT or2.5MHz for 10BT.In RMII mode, this pin output a 50 MHz clock for the timing reference of MAC side.18,19, 20,21 RXD[3:0] O Hi-Z Receive Data: In MII mode, RXD[3:0] is synchronous to RXCLK.In RMII mode, RXD[1:0] is synchronous to 50M_CLKI.24 RXER O Hi-Z Receive error:RXDV RXER Description1 1 Decoding error of thereceived signal0 1 Combine RXD[3:0] equal to0001 indicates PHY isreceiving LPI.1 0Normal operation This pin RXER is an optional input for MAC/CPU device.1 COL/RMII O/LI (PD) I (PD)Collision Detected:During the normal operation, thispin outputs a high status signal it means collision isdetected.RMII Mode Selection: During the power on reset, thispin status is latched to determine what kind MAC interface will be used. Logic “1” is for RMII mode and logic “0” is for MII mode.23 CRS/LEDMOD O/LI (PD) I (PD)Carrier Sense: When signal output from this pin is highindicates the transmission or reception is in process andat low status means the line is in idle state.LEDMOD: During power on reset, this pin status is latched to determine which either LED mode 1 or 2is selected, please refer to the LED pins description.Cable Transmission Interface 34,33 MDI_TP MDI_TN I/O I/O Hi-Z Transmit Output Pair: Differential pair shared by100Base-TX and 10Base-T modes. When configured as100Base-TX, output is an MLT-3 encoded waveform. When configured as 10Base-T , the output is ManchesterIP101GAPin no. Label Type Reset DescriptionStatecode.31,30 MDI_RPMDI_RN I/OI/OHi-Z Receive Input Pair: Differential pair shared by 100Base-TX and 10Base-T modes.Clock and Miscellaneous Pins47 X2 O O25MHz Crystal Output: Connects to crystal to providethe 25MHz output. It must be left open when X1 is drivenwith an external 25MHz oscillator.46 X1 I I 25MHz Crystal Input: Connects to crystal to provide the25MHz crystal input. If a 25MHz oscillator is used,connect X1 to the oscillator’s output. If a 50MHz clock isapplied to pin7 TXCLK/50M_CLKI, X1 must beconnected to GND or AGND33.42 RESET_N I I(PU)RESET_N: Enable a low status signal will reset the chip. For a complete reset function. 25MHz clock (x1) must be active for a minimum of 10 clock cycles before the rising edge of RESET_N. Chip will be able to operate after 2.5ms delay of the rising edge of RESET_N. The 2.5ms extension is to ensure the stability of system power.28 ISET I I Bandgap Circuit Resistor: This pin should beconnected to GND via a 6.19KΩ (1%) resistor to definethe standard current of the internal circuit.48 INTR OD Hi-Z Interrupt: Programmable Interrupt Output, this is anopen drain output, and an external pulled-up resistor isneeded for normal mode operation. Another operationmode is Rx to Tx loopback debugging test (reflect onRegister P1R23[13] RX2TX_LPBK) when connect INTRpin to GND.9 LED0/PHY_AD0 O/LI Hi-Z LED 0 and PHY Address [0]LED 0LED mode1 2LED0Link Link /ACT(blinking)10 LED1/PHY_AD1 O/LI Hi-Z LED 1 and PHY Address [1]LED1LED mode1 2LED1Duplex Duplex /COL (blinking)12 LED2/PHY_AD2 O/LI Hi-Z LED 2 and PHY Address [2]LED2LED mode1 2LED210M Link /ACT10M Link13 LED3/PHY_AD3 O/LI(PD) Hi-Z LED 3 and PHY Address [3]LED3LED mode1 2LED3100M Link /ACT 100M Link27 TEST_ON I I Test Enable: Set this pin to high to enable Test mode.IP101GAPin no. Label Type Reset DescriptionState(PD) (PD)For normal operation, this pin doesn’t need to beconnected.Power and Ground32 NC -- -- It’s a NC pin.8 REGOUT P P Regulator Power Output: This is a regulator poweroutput. A 10uF and 0.1uF should be connected to this pinto filter the power noise.14 VDDIO P P Digital Power input:Either 3.3V or 2.5V for I/O power supply.36 AVDD33 P P 3.3V Analog power input: This is a 3.3V power supplyfor analog circuitry, and it should be decoupled carefully.35 AGND33 P P Ground.29 AGND1V P P Ground45,11,17 DGND P P Ground.3.2 IP101GR/GRI pin descriptionIP101GR/GRIPin no. Label Type ResetStateDescriptionSerial Management Interface Pins22 MDC I Hi-Z Management Data Interface Clock: This pin provides aclock reference to MDIO. The clock rate can be up to2.5MHz.23 MDIO I/O(PU)I(PU)Management Data interface Input/Output:Thefunction of this pin is to transfer management informationbetween PHY and MAC.MII/RMII Pins5 TXEN I(PD)I(PD)Transmit Enable or Signal Detect.1 TXER/FXSD I(PD)I(PD)Transmit Error or FXSD:This is a dual-function pin which is determined by themedia type selection. If RXDV/CRS_DV/FX_HEN islatched as “0 (default)” upon reset, the TP interface isselected and its function as TXER. If the fiber interface isselected, this pin’s function as FXSD.FXSD:0: Fiber link down; 1: Fiber link upTransmit Enable:TXEN TXER Description1 1 Transmission errorpropagation.0 1 Combine TXD[3:0] that equalto 0001 for request PHY toenter LPI mode.1 00 0Normal operationThis pin TXER must be either floating or connecting toGND in RMII mode.10 TXCLK/50M_CLKI I/O Hi-Z Transmit Clock output or 50M clock input:In MII mode,this pin provides a continuous 25MHz clockat 100Base-TX and 2.5MHz at 10Base-T.In RMII mode, a 50Mhz clock should input to this pin forthe timing reference of the internal circuit.6,7,8,9 TXD[3:0] I Hi-Z Transmit Data Input:In MII mode, TXD[3:0] is synchronous to TXCLK.In RMII mode, TXD[1:0] is synchronous to 50M_CLKI.19 RXDV/CRS_DV/FX_HEN O/LI(PD)I(PD)Receive Data Valid or Media Type Selection:FX_HENThe input state is latched upon reset to determinewhether TP or fiber interface is selected. If it is at logic“0” (default) state upon reset, the TP interface isselected; otherwise the fiber interface is selected.RXDV/CRS_DVIn MII mode, this pin indicates the Receive Data ValidIP101GR/GRIPin no.LabelType ResetDescriptionStatefunction.In RMII mode,this pin indicates the Carrier Sense and Receive Data Valid function.14 RXCLK/ 50M_CLKO O Hi-Z Receive Clock:In MII mode, this pin provides 25MHz for 100BT or2.5MHz for 10BT.In RMII mode, this pin output a 50 MHz clock for the timing reference of MAC side.15,16, 17,18 RXD[3:0] O Hi-Z Receive Data: In MII mode, RXD[3:0] is synchronous to RXCLK.In RMII mode, RXD[1:0] is synchronous to 50M_CLKI.21 RXER/INTR_32 O/ODHi-Z The multiplex function of this pin is set by the registerSEL_INTR32, page 16, 29[2]. The default function is RXER.Receive error:RXDV RXER Description 1 1 Decoding error of thereceived signal0 1 Combine RXD[3:0] equal to0001 indicates PHY is receiving LPI. 1 0Normal operationThis pin RXER is an optional input for MAC/CPU device.Interrupt: Programmable Interrupt Output, this is an open drain output, and an external pulled-up resistor is needed.4 COL/RMII O/LI (PD) I (PD)Collision Detected:During the normal operation, thispin outputs a high status signal it means collision isdetected.RMII Mode Selection: During the power on reset, thispin status is latched to determine what kind MAC interface will be used. Logic “1” is for RMII mode and logic “0” is for MII mode.20 CRS/LEDMOD O/LI (PD) I (PD)Carrier Sense:When signal output from this pin is highindicates the transmission or reception is in process andat low status means the line is in idle state.LEDMOD: During power on reset, this pin status is latched to determine which either LED mode 1 or 2is selected, please refer to the LED pins description.Cable Transmission Interface 30,29 MDI_TP MDI_TN I/O I/O Hi-Z Transmit Output Pair: Differential pair shared by100Base-TX and 10Base-T modes. When configured as100Base-TX, output is an MLT-3 encoded waveform. When configured as 10Base-T , the output is Manchester code.27,26 MDI_RP MDI_RN I/O I/O Hi-Z Receive Input Pair: Differential pair shared by100Base-TX and 10Base-T modes.Clock and Miscellaneous PinsIP101GR/GRIPin no. Label Type Reset DescriptionState3 X2 O O25MHz Crystal Output: Connects to crystal to providethe 25MHz output. It must be left open when X1 is drivenwith an external 25MHz oscillator.2 X1 I I 25MHz Crystal Input: Connects to crystal to provide the25MHz crystal input. If a 25MHz oscillator is used,connect X1 to the oscillator’s output. If a 50MHz clock isapplied to pin10 TXCLK/50M_CLKI, X1 must beconnected to GND.32 RESET_N I I(PU)RESET_N: Enable a low status signal will reset the chip. For a complete reset function. 25MHz clock (x1) must be active for a minimum of 10 clock cycles before the rising edge of RESET_N. Chip will be able to operate after 2.5ms delay of the rising edge of RESET_N. The 2.5ms extension is to ensure the stability of system power.25 ISET I I Bandgap Circuit Resistor: This pin should beconnected to GND via a 6.19KΩ (1%) resistor to definethe standard current of the internal circuit.11 LED0/PHY_AD0 O/LI Hi-Z LED 0 and PHY Address [0]LED 0LED mode1 2LED0Link Link /ACT(blinking)12 LED3/PHY_AD3 O/LI(PD) Hi-Z LED 3 and PHY Address [3]LED3LED mode1 2LED3100M Link /ACT 100M Link24 TEST_ON I(PD)I(PD)Test Enable: Set this pin to high to enable Test mode.For normal operation, this pin doesn’t need to beconnected.Power and Ground28 REGOUT P P Regulator Power Output: This is a regulator poweroutput. A 10uF and 0.1uF should be connected to this pinto filter the power noise.13 VDDIO P P Digital Power input:IP101GR: Either 3.3V or 2.5V for I/O power supply.IP101GRI: 3.3V for I/O power supply.31 AVDD33 P P 3.3V Analog power input: This is a 3.3V power supplyfor analog circuitry, and it should be decoupled carefully. BottomPADGND P P Ground.4 Register DescriptionsTable 2 Register MapPage Register Description Default NoteX 20 Page Control Register 0x0010-- 0 Control Register 0x3100-- 1 Status Register 0x7849-- 2 PHY Identifier 1 Register 0x0243-- 3 PHY Identifier 2 Register 0x0C54-- 4 Auto-Negotiation Advertisement Register 0x01E1-- 5 Auto-Negotiation Link Partner Ability Register 0x0000-- 6 Auto-Negotiation Expansion Register 0x0004-- 7 Auto-Negotiation Next Page Transmit Register 0x2001-- 8 Auto-Negotiation Link Partner Next Page Register 0x0000-- 13 MMD Access Control Register 0x0000-- 14 MMD Access Address Data Register 0x000016 16 PHY Specific Control Register 0x000216 17 PHY Interrupt Ctrl/Status Register 0x0F0016 18 PHY Status Monitoring Register 0x020816 26 Digital IO Pin Driving Control Register 0x124916 27 Digital IO Pin Driving Control Register 0x001216 29 Digital I/O Specific Control Register 0x008216 30 PHY MDI/MDIX Control and Specific Status Register 0x0000-- MMD 3.0 PCS Control 1 Register 0x0000-- MMD 3.1 PCS Status 1 Register 0x0000-- MMD 3.20 EEE Capability Register 0x0002-- MMD 3.22 EEE Wake Error Count Register 0x0000-- MMD 7.60 EEE Advertisement Register 0x0002-- MMD 7.61 EEE Link Partner Ability Register 0x00001 17 PHY Specific Control Register 0x00001 18 RX CRC Error Counter Register 0x00001 22 Linear Regulator Output Control Register 0x20201 23 UTP PHY Specific Control Register 0x80002 18 RX Packet Counter Register 0x00003 16 LED Control Register 0x00004 16 WOL+ Control Register 0x5F404 22 Digital IO Pin Driving Control Register 0x40005 16 PHY WOL+ MAC Address Register 0x00008 17 RX Counter Control Register 0x700011 18 UTP PHY Interrupt Control/Status Register 0x0000Page Register DescriptionDefault Note 17 17 PHY WOL+ Status Register0x0000 1817RX Counter Interrupt Control/Status Register0x0000Register descriptionsR/W = Read/Write, SC = Self-Clearing, RO = Read Only, LL = Latching Low, LH = Latching High (TP): for twisted pair operation. (FX): for fiber operation. (e-fuse): only available for IP101G (dice).4.1 Register Page mode Control RegisterMII register 20 PHYMIIROMR/WDescriptionDefaultPage Control Register -- 20[4:0] -- R/W Reg16~31_Page_Sel[4:0] Register Page Select0x10The other Registers are reserved registers. User is inhibited to access to these registers. It may introduce abnormal function to write these registers.4.2 MII RegistersBitNameDescription/UsageDefault value (h): 3100Register 0 : Control Register 15 ResetWhen set, this action will bring both status and control registers of the PHY to default state. This bit is self-clearing. 1 = Software reset 0 = Normal operation0, RW/SC 14 LoopbackThis bit enables loopback of transmit data to the receive data path, i.e., TXD to RXD. 1 = enable loopback 0 = normal operation0, RW 13 Speed SelectionThis bit sets the speed of transmission. 1 = 100Mbps 0 = 10MbpsAfter completing auto-negotiation, this bit will reflect the speed status.(1: 100Mbps, 0: 10Mbps)1, RW 12 Auto-Negotiation Enable This bit determines the auto-negotiation function. 1 = enable auto-negotiation; bits 13 and 8 will be ignored. 0 = disable auto-negotiation; bits 13 and 8 will determine the link speed and the data transfer mode, under this condition.1, RW (TP) 0, RO (FX) 11 Power DownThis bit will turn down the power of the PHY chip and the internal crystal oscillator circuit if this bit is enabled. The MDC and MDIO are still activated for accessing to the MAC. 1 = power down0 = normal operation0, RW 10 Isolate1=electrically Isolate PHY from MII but not isolate MDC and MDIO0,RW。

微斯米微波式芯片公司2014年产品说明书

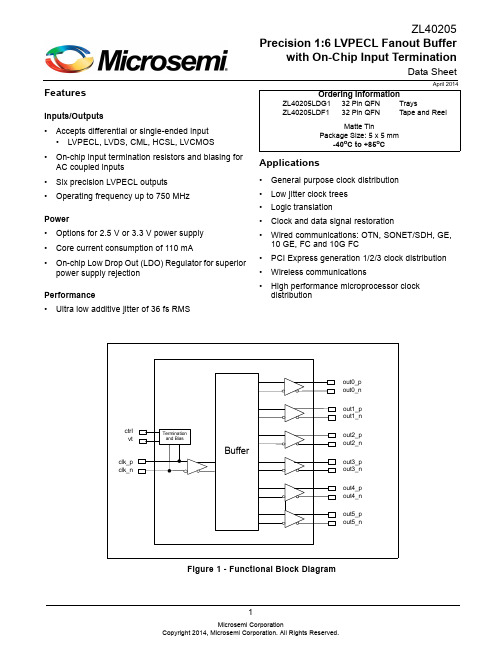

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination resistors and biasing for AC coupled inputs•Six precision LVPECL outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Core current consumption of 110 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 36 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE,10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40205Precision 1:6 LVPECL Fanout Bufferwith On-Chip Input TerminationData SheetOrdering InformationZL40205LDG1 32 Pin QFN TraysZL40205LDF132 Pin QFNTape and ReelMatte TinPackage Size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - Simplified Diagram of Input Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVPECL AC Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - LVPECL AC Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 21 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.8Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. These resistor are not required; however there is no impact to performance if the resistors are included.16Power supply filtering 18Figure 20Clarification of V ID and V OD .Below are the changes from the February 2013 issue to the April 2014 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.Below are the changes from the November 2012 issue to the February 2013 issue:Corrected typo of 0.3 Ohm to 0.15 Ohm.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 728, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40205 is an LVPECL clock fan out buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40205 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40205 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40205 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is logically one and the Vt pin is not connected, the Vt pin can be instead connected to VDD with a capacitor. A capacitor can also help in Figure 4 between Vt and VDD. This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Figure 4 - Clock Input - LVPECL - DC CoupledFigure 5 - Clock Input - LVPECL - AC CoupledFigure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a different device with the same inputs and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40205 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationFigure 16 - LVPECL AC Output TerminationFigure 17 - LVPECL AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40205 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40205 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40205 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive random jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.Figure 18 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40205 is equipped with a low drop out (LDO) regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 19. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 Ohm resistor is recommended3.4.3 PCB layout considerationsThe power nets in Figure 19 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.ZL402051891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 19 - Decoupling Connections for Power PinsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5VDD V 4LVPECL output current I out30mA 5Soldering temperature T260 °C 6Storage temperature T ST-55125 °C 7Junction temperature T j125 °C 8Voltage on input pin V input VDD V 9Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload110mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load209mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1CMOS control logic high-level inputvoltageV CIH0.7*V DD V2CMOS control logic low-level inputvoltageV CIL0.3*V DD V3CMOS control logic Input leakagecurrentI IL1µA V I = V DD or 0 V4Differential input common modevoltageV CM 1.1 2.0V5Differential input voltage difference V ID0.251V6Differential input resistance V IR80100120ohm* This parameter was measured from 125 MHz to 750 MHz.* This parameter was measured from 125 MHz to 750 MHz.Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions7LVPECL output high voltage V OH V DD -1.40V 8LVPECL output low voltage V OL V DD - 1.62V 9LVPECL output differential voltage*V OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3Differential input resistance V IR 80100120ohm 4LVPECL output high voltage V OH V DD -1.40V 5LVPECL output low voltage V OL V DD - 1.62V 6LVPECL output differential voltage*V OD0.40.9VDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAC Electrical Characteristics* - Inputs and Outputs (see Figure 21) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out50100ps4Part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-202Percent6LVPECL Output clock slew rate r SL0.75 1.2V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 21 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1392212.512 kHz - 20 MHz 1093311.0412 kHz - 20 MHz 85442512 kHz - 20 MHz 57550012 kHz - 20 MHz 506622.0812 kHz - 20 MHz 40775012 kHz - 20 MHz36Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1152212.512 kHz - 20 MHz 853311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 55550012 kHz - 20 MHz 486622.0812 kHz - 20 MHz 41775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns.*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 115fs RMS 750MHz25 mV at 100 kHz59fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 2.5 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveformat 155.52 MHzV OD versus FrequencyPropagation Delay versus TemperatureNote:This is for a single device. For more details see thePower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHzPower Supply Tone Magnitude (at 100 kHz) versus PSRR at 125 MHz Power Supply Tone Magnitude (at 100 kHz) versus Additive Jitter at 125 MHz7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

英飞凌智能卡芯片有三大创新

哲介绍了其最新的三大创新。

存储:从ROM到EEPROM 智能卡芯片的ROM会转移

到EEPROM。因为首先是性能的 提升和功耗的降低,半导体业 来说关键之一是线宽。线宽从 最早的0.22μm(220nm)下降到了 0.13μm(130nm),英飞凌现在推广 的主流产品是90nm。通常线宽越 低,功耗越低,性能越好(如图1)。 第二,跟原来基于ROM的硬掩膜 相比,未来基于EEPROM,英飞凌推 出了安全凌捷掩膜,此项技术更具成 本优势和灵活性,也会成为未来的趋 势。但从ROM变到EEPROM,芯片 安全性同样需要关注。英飞凌所做的 EEPROM的工艺,在程序写入后直接 固化,可以达到和ROM一样的安全等 级,甚至提供一些额外的安全性能。 英飞凌现在的EEPROM产品已经获得 了CC EAL 6+(高)证书,市场上大 部分的CC证书是4+或者5+。在针对

EEPROM安全凌捷掩膜产品在 CPU方面有几个优势。第一是真16位 CPU,比旧的CPU性能提升40%,功

耗更低。从目前市场角度讲,如果在 8位CPU里面做一些加速器,可以提 速,但只能针对一些已知算法或交易 流程,一旦交易流程有改变,真16位 的高性能就可以体现出来。例如,一 些城市已经可以用银行卡刷公交卡, 刷公交卡对交易时间有一定要求。最 早的智能卡对交易时间要求小于500 毫秒,这对银行卡支付没有太大问 题;但交通卡的最低要求在300毫秒 以下。现在英飞凌的产品可以做到 200毫秒qPBOC交易时间。

高端应用的产品里会用到6+证书。 过去ROM与EEPROM相结合的产

品较多,这主要和成本有关。不许改 动的内容放在ROM里,要改变的放 在EEPROM,这样的组合会有成本优 势。人们常听到的ROM产品、硬掩膜 产品都属于这类产品。

Testo 最新一代气流速度和空气质量仪测试仪说明书

Latest generation testo air velocity & IAQ probes with fixed cableInstruction manualContents Contents1About this document (3)2Safety and disposal (3)3System description (4)4Description of the instrument (5)4.1Hot wire probe, including temperature sensor (0635 1032) (5)4.2Vane probe (Ø 16 mm) (0635 9532) (6)4.3High-precision temperature/humidity probe up to +180°C (0636 9775) 64.4Lux probe (0635 0551) (7)4.5Turbulence probe (0628 0152) (7)4.6Laboratory flue probe (0635 1052) (8)5Commissioning (9)6Maintenance (9)6.1Maintaining the probes (9)6.1.1Cleaning the instrument (9)6.1.2Calibration (9)7Technical data (10)8Accessories and spare parts (13)1 About this document1About this document•The instruction manual is an integral part of the instrument.•Please read this instruction manual through carefully and familiarize yourself with the product before putting it to use.•Pay particular attention to the safety instructions and warning advice in order to prevent injury and damage to the product.•Keep this documentation to hand so that you can refer to it when necessary.•Always use the complete original instruction manual.•Hand this instruction manual on to any subsequent users of the product.2Safety and disposalSecurity•Only use the product properly, for its intended purpose, and within the parameters specified in the technical data. Do not apply any force. •Dangers may also arise from the systems being measured or the measuring environment: always comply with the locally valid safety regulations when carrying out measurements.•Do not carry out any contact measurements on uninsulated, live parts. •Do not store the product together with solvents. Do not use any desiccants. •Only carry out maintenance and repair work on this instrument which is described in the documentation. Follow the prescribed steps exactly when doing the work. Use only original spare parts from Testo.•Temperature information given on probes/sensors relates only to the measuring range of the sensor technology. Do not expose handles and feed lines to temperatures in excess of 50°C (122°F), unless they are expressly authorized for use at higher temperatures.•Do not operate the instrument if there are signs of damage on the housing or supply lines.33 System description4Disposal• At the end of its useful life, deliver the product to the separate collectionpoint for electric and electronic devices (observe local regulations) or return the product to Testo for disposal.•WEEE Reg. no. DE 753343523 System descriptionYou have acquired a probe, if applicable with additional probe-specific accessories.The probe can be directly connected to the testo 440 measuring instrument.You will find detailed information about how each of the probes works along with the testo 440 measuring instrument in the corresponding chapter of the instruction manual for the measuring instrument.4 Description of the instrument54 Description of the instrument4.1 Hot wire probe, including temperaturesensor (0635 1032)ApplicationIn conjunction with the testo 440, the hot wire probe is suitable for flow and humidity measurements in ventilation ducts. Structure1 Sensor with protective sleeve2 Probe adapter3 Telescope with scaling 4Cable 5 Connection plugCAUTIONDamage to sensor possible! - Do not touch sensor!- Close the protective sleeve after the measurement.Low flow velocities may result in greater measurement uncertainties during temperature and humidity measurement. The probe should be switched on outside a duct under the following conditions: Ambient temperature: 20°C Flow: approx. 0 m/s.Collapse the telescope after use and do not constrict with the cable.4 Description of the instrument64.2 Vane probe (Ø 16 mm) (0635 9532)ApplicationIn conjunction with the testo 440, the vane probe (Ø 16 mm) is suitable for flow measurements in ventilation ducts. Structure1 Probe head2 Telescope3 Telescope handle4 CableCAUTIONDamage to sensor possible! - Do not touch sensor!- Put the protective sleeve on after the measurement.Collapse the telescope after use and do not constrict with the cable. 4.3 High-precision temperature/humidityprobe up to +180°C (0636 9775)ApplicationIn conjunction with the testo 440, the high-precision temperature/humidity probe is used to measure humidity and temperature. Structure1 Probe head 2Sintered cap 3 Probe shaft 4 Handle 5 CableCAUTIONDamage to sensor possible! - Do not touch sensor!4 Description of the instrument74.4 Lux probe (0635 0551)ApplicationIn conjunction with the testo 440, the lux probe is used to determine the illuminance of workplaces. In general, the illuminance measurement of warm light or white LEDs is possible because these types of LED cover the whole spectral range of the human eye. The measurement of one-colour LEDs (e.g. blue LEDs) is not recommended. Structure1 Measuring sensor2 CableCAUTIONDamage to sensor possible! - Do not touch sensor!4.5 Turbulence probe (0628 0152)ApplicationIn conjunction with the testo 440, the turbulence probe is used for temperature and air pressure measurement. Structure1 Sensor2 Guard3 Probe shaft4 Handle5 Cable4 Description of the instrument8Damage to sensor possible! - Do not touch sensor!The probe contains sensitive components. Please handle the probe with care.4.6 Laboratory flue probe (0635 1052)ApplicationIn conjunction with the testo 440, the laboratory flue probe is used to determine flow velocities in laboratory fume cupboards. Structure1 Sensor2 Protective sleeve3 Button 4Handle 5 CableATTENTIONDamage to sensor possible! - Do not touch sensor!- Push the protective sleeve over the sensor after the measurement.The probe contains sensitive components. Please handle the probe with care.Low flow velocities may result in greater measurement uncertainty during temperature measurement!5 Commissioning95 CommissioningDisplaying readings✓Sensor is connected to the measuring instrument.Readings are displayed.6 Maintenance6.1 Maintaining the probes6.1.1 Cleaning the instrumentDo not use any aggressive cleaning agents or solvents; instead use mild household cleaning agents or soapy water.Always keep the connections clean and free from grease and other deposits.Clean the instrument and the connections with a damp cloth and dry them off.6.1.2 CalibrationThe probes are supplied with a factory calibration protocol as standard. Recalibration of the probes once every 12 months is recommended in many applications. This can be carried out by Testo Industrial Services (TIS) or othercertified service providers with the aid of easy-to-use service software. Please contact Testo for further information.7 Technical data107 Technical data• Adjustment conditions for flow probes:Adjustment in free jet Ø 350 mm, reference pressure 1013 hPa, based on testo reference Laser Doppler Anemometer (LDA). • Note for flow probes:Low flow velocities may result in greater measurement uncertainties during humidity and temperature measurement! • Note for humidity probes:Please do not use the humidity probes in condensing atmospheres. For continuous use in high-humidity ranges > 80% RH at ≤ 30°C for > 12 h > 60% RH at > 30°C for > 12 hplease get in touch with Testo Service or contact us via the Testo website.Hot wire probe, including temperature sensor (0635 1032) FeatureValueMeasuring range0 to +30 m/s -20 to +70°C 700 to 1100 hPaAccuracy(at 22°C, ± 1 digit)± (0.03 m/s + 4% of m.v.) (0 to 20 m/s) ± (0.5 m/s + 5% of m.v.) (20.01 to 30 m/s) ± 0.5°C (0 to +70°C) ± 3 hPa Resolution0.01 m/s 0.1°C 0.1 hPaStorage temperature -20°C to +70°C Operating temperature -20°C to +70°C Protection class IP20DimensionsCable length: 1.7 mExtension length with telescope: 850 mm Ø probe head on the sensor: 9 mm Ø end of probe shaft: 12 mm Weight90 gDirectives, standards and testsEU Directive: 2014/30/EU7 Technical data11Vane probe (Ø 16 mm) (0635 9532) FeatureValue Measuring range0.6 to 50 m/s Accuracy(at 22°C, ± 1 digit)± (0.2 m/s +1% of m.v.) (0.6 to 40 m/s) ± (0.2 m/s +2% of m.v.) (40.1 to 50 m/s) Resolution0.1 m/s Storage temperature-10°C to +70°C Operating temperature-10°C to +70°C Protection classIP20 Dimensions Cable length: 1.7 mExtension length with telescope: 850 mmØ probe head: 16 mmØ end of probe shaft: 12 mmWeight 148 gDirectives, standards andtestsEU Directive: 2014/30/EUHigh-precision temperature/humidity probe up to +180°C (0636 9775) FeatureValue Measuring range-20 to +180°C 0 to 100% RH Accuracy(at 22°C, ± 1 digit)±0.5°C (-20 to 0°C) ±0.4°C (0.1 to +50°C) ±0.5°C (+50.1 to +180°C) Accuracy(at 25°C, ±1 digit) ±3% RH (0 to 2% RH) ±2% RH (2.1 to 98% RH)±3% RH (98.1 to 100% RH)Additional uncertainty- Long-term stability: ±1% RH / yearResolution 0.1°C0.1% RHTemperature coefficient type (k=1) ±0.03% RH/K (-20 to +50°C)type (k=1) ±0.06% RH/K (+50 to +180°C)Storage temperature -20 to 60°COperating temperature Handle: -5 to +50°CProbe head: -20 to +180°CProtection classIP207 Technical data12 FeatureValue Dimensions Cable length: 1.4 mOverall probe length: 420 mmProbe shaft length: 270 mmØ probe shaft: 12 mmWeight 255 gDirectives, standards andtestsEU Directive: 2014/30/EULux probe (0635 0551) FeatureValue Measuring range0 to 100,000 lux Accuracy(at 22°C, ±1 digit)DIN EN 13032-1 Appendix B; Class C according to DIN 5032-7 Resolution0.1 lux < 10,000 lux 1 lux ≥ 10,000 lux Storage temperature-20 to +50°C Operating temperature0 to +50°C Ambient humidityPreferred use: 20 to 80% RH DimensionsCable length: 1.4 m Housing: 110 x 55 x 22 mm Weight 110 g Directives, standards andtestsEU Directive: 2014/30/EUTurbulence probe (0628 0152)FeatureValue Measuring range 0 to +5 m/s0 to +50°C700 to 1100 hPaAccuracy (at 22°C, ± 1 digit) ± (0.03 m/s + 4% of m.v.) (0 to +5 m/s)± 0.5°C± 3 hPaResolution 0.01 m/s0.1°C0.1 hPaStorage temperature -20 to +60°COperating temperature0°C to +50°C8 Accessories and spare parts13 FeatureValue Dimensions Cable length: 1.4 mOverall probe length: 400 mmProbe shaft length: 195 mmWeight 250 gDirectives, standards andtestsEU Directive: 2014/30/EULaboratory flue probe (0635 1052) FeatureValue Measuring range 0 to +5 m/s0 to +50°C700 to 1100 hPaAccuracy (at 22°C, ± 1 digit) ± (0.02 m/s + 5% of m.v.) (0 to +5 m/s)± 0.5°C± 3 hPaResolution 0.01 m/s0.1°C 0.1 hPaStorage temperature -20 to +60°COperating temperature 0°C to +50°CDimensions Cable length: 1.4 mOverall probe length: 350 mmProbe shaft length: 195 mmWeight 230 gDirectives, standards andtestsEU Directive: 2014/30/EU8 Accessories and spare partsDescription Order no. Measuring stand with standard-compliant positioning of probes (including bag)0554 15900971 0455 en 03。

英飞凌 FP50R12N2T7P EconoPIM 2 模块 数据表

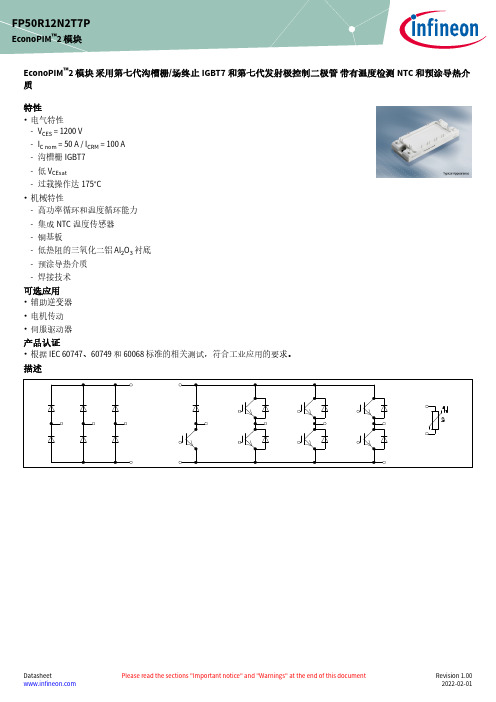

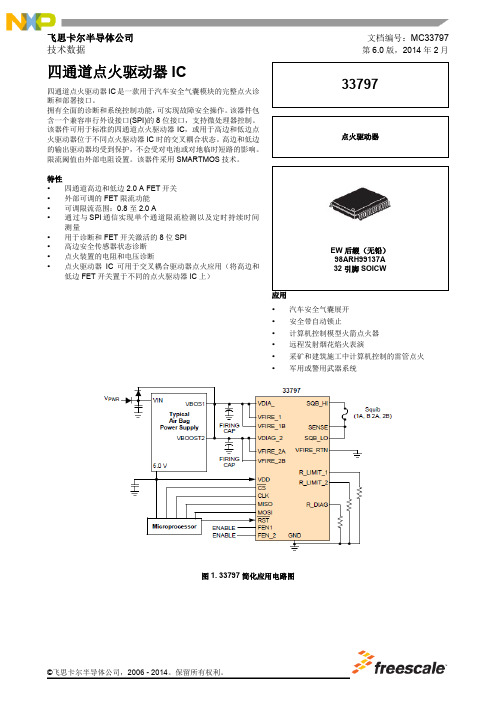

EconoPIM ™2 模块 采用第七代沟槽栅/场终止IGBT7和第七代发射极控制二极管 带有温度检测NTC 和预涂导热介质特性•电气特性-V CES = 1200 V-I C nom = 50 A / I CRM = 100 A -沟槽栅IGBT7-低 V CEsat-过载操作达175°C•机械特性-高功率循环和温度循环能力-集成NTC 温度传感器-铜基板-低热阻的三氧化二铝 Al 2O 3 衬底-预涂导热介质-焊接技术可选应用•辅助逆变器•电机传动•伺服驱动器产品认证•根据 IEC 60747、60749 和 60068标准的相关测试,符合工业应用的要求。

描述FP50R12N2T7PEconoPIM ™2 模块内容描述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1特性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1可选应用 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1产品认证 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1内容 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 1封装 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 2IGBT, 逆变器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 3二极管,逆变器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 4二极管,整流器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 5IGBT, 斩波器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 6Diode-斩波器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 7负温度系数热敏电阻 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 8特征参数图表 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 9电路拓扑图 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 10封装尺寸 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 11模块标签代码 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17修订历史 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18免责声明 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191封装表 1绝缘参数特征参数代号标注或测试条件数值单位绝缘测试电压V ISOL RMS, f = 50 Hz, t = 1 min 2.5kV 模块基板材料Cu内部绝缘基本绝缘 (class 1, IEC 61140)Al2O3爬电距离d Creep端子至散热器10.0mm 电气间隙d Clear端子至散热器7.5mm 相对电痕指数CTI>200相对温度指数 (电)RTI封装140°C 表 2特征值特征参数代号标注或测试条件数值单位最小值典型值最大值杂散电感,模块L sCE35nH 模块引线电阻,端子-芯片R AA'+CC'T H=25°C, 每个开关 5.5mΩ模块引线电阻,端子-芯片R CC'+EE'T H=25°C, 每个开关 4.8mΩ储存温度T stg-40125°C 最高基板工作温度T BPmax150°CM5, 螺丝36Nm 模块安装的安装扭距M根据相应的应用手册进行安装重量G180g注:The current under continuous operation is limited to 50 A rms per connector pin.Storage and shipment of modules with TIM => see AN2012-072IGBT, 逆变器表 3最大标定值特征参数代号标注或测试条件数值单位集电极-发射极电压V CES T vj = 25 °C1200V 连续集电极直流电流I CDC T vj max = 175 °C T H = 90 °C50A 集电极重复峰值电流I CRM t P = 1 ms100A 栅极-发射极峰值电压V GES±20V表 4特征值特征参数代号标注或测试条件数值单位最小值典型值最大值集电极-发射极饱和电压V CE sat I C = 50 A, V GE = 15 V T vj = 25 °C 1.50 1.80VT vj = 125 °C 1.64T vj = 175 °C 1.72栅极阈值电压V GEth I C = 2 mA, V CE = V GE, T vj = 25 °C 5.15 5.80 6.45V 栅极电荷Q G V GE = ±15 V, V CE = 600 V0.92µC 内部栅极电阻R Gint T vj = 25 °C0Ω输入电容C ies f = 100 kHz, T vj = 25 °C, V CE = 25 V, V GE = 0 V11.1nF 反向传输电容C res f = 100 kHz, T vj = 25 °C, V CE = 25 V, V GE = 0 V0.039nF 集电极-发射极截止电流I CES V CE = 1200 V, V GE = 0 V T vj = 25 °C0.01mA 栅极-发射极漏电流I GES V CE = 0 V, V GE = 20 V, T vj = 25 °C100nA开通延迟时间(感性负载)t don I C = 50 A, V CE = 600 V,V GE = ±15 V, R Gon = 7.5 ΩT vj = 25 °C0.059µs T vj = 125 °C0.061T vj = 175 °C0.062上升时间(感性负载)t r I C = 50 A, V CE = 600 V,V GE = ±15 V, R Gon = 7.5 ΩT vj = 25 °C0.043µs T vj = 125 °C0.047T vj = 175 °C0.049关断延迟时间(感性负载)t doff I C = 50 A, V CE = 600 V,V GE = ±15 V, R Goff = 7.5 ΩT vj = 25 °C0.290µs T vj = 125 °C0.380T vj = 175 °C0.420下降时间(感性负载)t f I C = 50 A, V CE = 600 V,V GE = ±15 V, R Goff = 7.5 ΩT vj = 25 °C0.110µs T vj = 125 °C0.200T vj = 175 °C0.270开通损耗能量 (每脉冲)E on I C = 50 A, V CE = 600 V,Lσ = 35 nH, V GE = ±15 V,R Gon = 7.5 Ω, di/dt = 900A/µs (T vj = 175 °C)T vj = 25 °C 5.07mJ T vj = 125 °C 6.76T vj = 175 °C7.72关断损耗能量 (每脉冲)E off I C = 50 A, V CE = 600 V,Lσ = 35 nH, V GE = ±15 V,R Goff = 7.5 Ω, dv/dt =2900 V/µs (T vj = 175 °C)T vj = 25 °C 3.37mJ T vj = 125 °C 5.31T vj = 175 °C 6.58(待续)表 4(续) 特征值特征参数代号标注或测试条件数值单位最小值典型值最大值短路数据I SC V GE≤ 15 V, V CC = 800 V,V CEmax=V CES-L sCE*di/dt t P≤ 8 µs,T vj=150 °C190At P≤ 7 µs,T vj=175 °C180结-散热器热阻R thJH每个 IGBT, Valid with IFX pre-appliedThermal Interface Material0.777K/W 允许开关的温度范围T vj op-40175°C注:T vj op > 150°C is allowed for operation at overload conditions. For detailed specifications, please refer to AN 2018-14.3二极管,逆变器表 5最大标定值特征参数代号标注或测试条件数值单位反向重复峰值电压V RRM T vj = 25 °C1200V 连续正向直流电流I F50A 正向重复峰值电流I FRM t P = 1 ms100A I2t-值I2t V R = 0 V, t P = 10 ms T vj = 125 °C465A²sT vj = 175 °C420表 6特征值特征参数代号标注或测试条件数值单位最小值典型值最大值正向电压V F I F = 50 A, V GE = 0 V T vj = 25 °C 1.72 2.10VT vj = 125 °C 1.59T vj = 175 °C 1.52反向恢复峰值电流I RM I F = 35 A, V R = 600 V,V GE = -15 V, -di F/dt = 900A/µs (T vj = 175 °C)T vj = 25 °C31A T vj = 125 °C39T vj = 175 °C45恢复电荷Q r I F = 50 A, V R = 600 V,V GE = -15 V, -di F/dt = 900A/µs (T vj = 175 °C)T vj = 25 °C 3.96µC T vj = 125 °C7.37T vj = 175 °C9.89(待续)表 6(续) 特征值特征参数代号标注或测试条件数值单位最小值典型值最大值反向恢复损耗(每脉冲)E rec I F = 50 A, V R = 600 V,V GE = -15 V, -di F/dt = 900A/µs (T vj = 175 °C)T vj = 25 °C 1.31mJ T vj = 125 °C 2.52T vj = 175 °C 3.46结-散热器热阻R thJH每个二极管, Valid with IFX pre-appliedThermal Interface Material1.13K/W 允许开关的温度范围T vj op-40175°C注:T vj op > 150°C is allowed for operation at overload conditions. For detailed specifications, please refer to AN 2018-14.4二极管,整流器表 7最大标定值特征参数代号标注或测试条件数值单位反向重复峰值电压V RRM T vj = 25 °C1600V 最大正向均方根电流(每芯片)I FRMSM T H = 60 °C70A最大整流器输出均方根电流I RMSM T H = 60 °C100A 正向浪涌电流I FSM t P = 10 ms T vj = 25 °C560AT vj = 150 °C435I2t-值I2t t P = 10 ms T vj = 25 °C1570A²sT vj = 150 °C945表 8特征值特征参数代号标注或测试条件数值单位最小值典型值最大值正向电压V F I F = 50 A T vj = 150 °C 1.05V 反向电流I r T vj = 150 °C, V R = 1600 V1mA 结-散热器热阻R thJH每个二极管, Valid with IFX pre-appliedThermal Interface Material1.10K/W 允许开关的温度范围T vj, op-40150°C5IGBT, 斩波器表 9最大标定值特征参数代号标注或测试条件数值单位集电极-发射极电压V CES T vj = 25 °C1200V 连续集电极直流电流I CDC T vj max = 175 °C T H = 110 °C25A 集电极重复峰值电流I CRM t P = 1 ms50A 栅极-发射极峰值电压V GES±20V表 10特征值特征参数代号标注或测试条件数值单位最小值典型值最大值集电极-发射极饱和电压V CE sat I C = 25 A, V GE = 15 V T vj = 25 °C 1.60 1.85VT vj = 125 °C 1.74T vj = 175 °C 1.82栅极阈值电压V GEth I C = 0.525 mA, V CE = V GE, T vj = 25 °C 5.15 5.80 6.45V 栅极电荷Q G V GE = ±15 V, V CE = 600 V0.395µC 内部栅极电阻R Gint T vj = 25 °C0Ω输入电容C ies f = 100 kHz, T vj = 25 °C, V CE = 25 V, V GE = 0 V 4.77nF 反向传输电容C res f = 100 kHz, T vj = 25 °C, V CE = 25 V, V GE = 0 V0.017nF 集电极-发射极截止电流I CES V CE = 1200 V, V GE = 0 V T vj = 25 °C0.004mA 栅极-发射极漏电流I GES V CE = 0 V, V GE = 20 V, T vj = 25 °C100nA开通延迟时间(感性负载)t don I C = 25 A, V CE = 600 V,V GE = ±15 V, R Gon = 9.1 ΩT vj = 25 °C0.041µs T vj = 125 °C0.043T vj = 175 °C0.044上升时间(感性负载)t r I C = 25 A, V CE = 600 V,V GE = ±15 V, R Gon = 9.1 ΩT vj = 25 °C0.025µs T vj = 125 °C0.028T vj = 175 °C0.030关断延迟时间(感性负载)t doff I C = 25 A, V CE = 600 V,V GE = ±15 V, R Goff = 9.1 ΩT vj = 25 °C0.230µs T vj = 125 °C0.320T vj = 175 °C0.350下降时间(感性负载)t f I C = 25 A, V CE = 600 V,V GE = ±15 V, R Goff = 9.1 ΩT vj = 25 °C0.140µs T vj = 125 °C0.220T vj = 175 °C0.280(待续)表 10(续) 特征值特征参数代号标注或测试条件数值单位最小值典型值最大值开通损耗能量 (每脉冲)E on I C = 25 A, V CE = 600 V,Lσ = 35 nH, V GE = ±15 V,R Gon = 9.1 Ω, di/dt = 810A/µs (T vj = 175 °C)T vj = 25 °C 1.47mJ T vj = 125 °C 2.05T vj = 175 °C 2.39关断损耗能量 (每脉冲)E off I C = 25 A, V CE = 600 V,Lσ = 35 nH, V GE = ±15 V,R Goff = 9.1 Ω, dv/dt =3120 V/µs (T vj = 175 °C)T vj = 25 °C 1.65mJ T vj = 125 °C 2.58T vj = 175 °C 3.13短路数据I SC V GE≤ 15 V, V CC = 800 V,V CEmax=V CES-L sCE*di/dt t P≤ 8 µs,T vj=150 °C90At P≤ 7 µs,T vj=175 °C85结-散热器热阻R thJH每个 IGBT, Valid with IFX pre-appliedThermal Interface Material1.19K/W 允许开关的温度范围T vj op-40175°C注:T vj op > 150°C is allowed for operation at overload conditions. For detailed specifications, please refer to AN 2018-14.6Diode-斩波器表 11最大标定值特征参数代号标注或测试条件数值单位反向重复峰值电压V RRM T vj = 25 °C1200V 连续正向直流电流I F25A 正向重复峰值电流I FRM t P = 1 ms50A I2t-值I2t V R = 0 V, t P = 10 ms T vj = 125 °C125A²sT vj = 175 °C95表 12特征值特征参数代号标注或测试条件数值单位最小值典型值最大值正向电压V F I F = 25 A, V GE = 0 V T vj = 25 °C 1.83 2.30VT vj = 125 °C 1.70T vj = 175 °C 1.63(待续)表 12(续) 特征值特征参数代号标注或测试条件数值单位最小值典型值最大值反向恢复峰值电流I RM I F = 25 A, V R = 600 V,V GE = -15 V, -di F/dt = 810A/µs (T vj = 175 °C)T vj = 25 °C21.7A T vj = 125 °C26.7T vj = 175 °C29.8恢复电荷Q r I F = 25 A, V R = 600 V,V GE = -15 V, -di F/dt = 810A/µs (T vj = 175 °C)T vj = 25 °C 1.69µC T vj = 125 °C 3.29T vj = 175 °C 4.29反向恢复损耗(每脉冲)E rec I F = 25 A, V R = 600 V,V GE = -15 V, -di F/dt = 810A/µs (T vj = 175 °C)T vj = 25 °C0.63mJ T vj = 125 °C 1.28T vj = 175 °C 1.69结-散热器热阻R thJH每个二极管, Valid with IFX pre-appliedThermal Interface Material1.63K/W 允许开关的温度范围T vj op-40175°C注:T vj op > 150°C is allowed for operation at overload conditions. For detailed specifications, please refer to AN 2018-14.7负温度系数热敏电阻表 13特征值特征参数代号标注或测试条件数值单位最小值典型值最大值额定电阻值R25T NTC = 25 °C5kΩR100偏差ΔR/R T NTC = 100 °C, R100 = 493 Ω-55%耗散功率P25T NTC = 25 °C20mW B-值B25/50R2 = R25 exp[B25/50(1/T2-1/(298,15 K))]3375K B-值B25/80R2 = R25 exp[B25/80(1/T2-1/(298,15 K))]3411K B-值B25/100R2 = R25 exp[B25/100(1/T2-1/(298,15 K))]3433K 注:根据应用手册标定7 负温度系数热敏电阻9电路拓扑图图 110封装尺寸图 211模块标签代码图 3修订历史修订历史修订版本发布日期变更说明1.002022-02-01Initial version商标所有参照产品或服务名称和商标均为其各自所有者的财产。

英飞凌推出用于LTE和3G的两颗射频芯片

P lan O p t ik AG

成功 研 发用 于 半 导体 工 艺的 玻 璃 载体

生产用于 M EM S 产品的玻璃和石英玻璃晶圆器件供应商P lan O p t ik A G 成 功研发出用于半导体工艺的玻璃载体。 半导体晶圆产品的发展趋势是越来越薄, 并且背面减薄和划片等工艺中对厚 度变化和表面质量等方面精度的要求也越来越高, 精准的加工载体是上述各工艺 操作的先决条件。玻璃具有较好的热稳定性和抗酸性, 因此是最理想的衬底材料。 此外, 这些玻璃载体还可以重复使用, 即环保又降低了成本。P lan O p tik 现在生产 R ○ ○ R ○ R TM 的这种载体可以用于 3 M 和B rew er S cience �EV G W a fer B ond 系统。 这些玻璃载体采用最新的研磨和抛光技术制成, 研磨和抛光精确度较高, 总

SM A R T iLU 是一颗符合 3GPP R el. 7 和R el. 8 规范、 高集成、 支持 2G �3G � L T E 多模式的射频发射器件。这颗芯片在支持四波段 GS M �ED GE 的同时, 还

可以同时支持六个 3G 和 L T E 波段。 在该芯片丰富的功能列表中, 包括 L T E FDD clas s 5 (下行速率最大可达 150 兆比特每秒, 上行速率最大可达 50 兆比特 每秒)、 M I M O R x d ive rs ity (两个下行+ 一个上行 )、 H SPA + 、 H SPA 、 W CDMA 和 GSM � GPR S �ED GE。 该芯片如此广泛的射频波段支持能力, 使其能够极好地 与全球H SPA � L TE 网络无缝配合。SM A R T i LU 所采用的符合M IP I D igR F v4 标准的数字基带芯片接口, 为手机系统设计 “全数字化” 树立了一个新的里程 碑, 使得基带芯片设计向进一步集成化、 向 32 nm 或更精密半导体技术前进提供 了保障。 SM A R T i LU 基于全球主要半导体生产厂商共同遵循的 65nm 生产工 艺, 样片和性能测试报告计划在今年巴塞罗那全球无线大会上全面展示。 单 SM A R T iU Em icro 是为配合低端 3G 手机需求设计的一颗 CM O S 工艺、 芯片、 同时支持 2G �3G 网络的射频发射器件。通过遵循D igR F v3109 基带芯片 通讯接口, 该器件在软件和硬件上都达到了先后兼容性。 通过减少外接低噪声 放大器 (LNA s ) 和采用无接受滤波器的带内射频前端等技术创新, SM A R T i U Em icro 在支持双波段或四波段 GS M �ED GE 和最多三个W CDM A 波段时, 达 到了系统成本最优化, 适合用于超低端 3 G 手机。从 2009 年二季度开始, 客户即 可从英飞凌获得 SM A R T i U Em icro 的样片。预计在 2009 年底, 采用该芯片的客 户将 摘

英飞凌推出创新型H-PSOF封装技术

技术 ,为纯电动汽车和混合动力汽车等要求苛刻的 率 。新 推 出的 T O封装符合 J D C标准 H P O EE —S F

( 热 型塑料 小 外 形 扁平 引线 ) 散 。首批 推 出的采 用 H— S F封 装 技 术 的产 品 是 4 VO t S ET PO 0 pi F 2功 MO

D P引擎助 力 N P车载系统 S X

T nic esi la日前 宣布 , 车载娱 乐 系 统 厂商 N P半 X 导体 , 已经 成 功地 移植 T nic on esia nX基 带 D P引 l C S

M SE O F T专业技术 , 以处理 3A以上应用并增加功 0 率密度。 ( 自飞兆半导体 ) 来

右 ,高度几乎是 D P K的一半 。 ( 自英 飞凌公 决方案 。 2A 来

司 )

T n lG o n e s ia C n X基 带 i

同级最佳 的 D — C转换效率和热性能的需求 。这 CD

项 协 议 利 用 了 两 家 企 业 的 非 对 称 结 构 功 率 级 双

播、 移动 H T D V以及汽车通信领域 的高度灵活的基

交通 系统 的现 场实 验 中去 。 ( 自 T nic ) 来 esia l

带处理器。日后 ,该处理器会运用到全球多个智能 础 之 全 新 F AM 产 品 系 列 ,包 括 MB 5 C 4 和 R 8R 6V 电压下运作 。 富士通半导体此次推出的全新 5 C VI I

( O 2 3) 言 , — S F封 装 的尺 寸更 小 , T 一6 而 H PO 高度 更 低 。 — S F封 装 的面积 比 目前 的 D P K小 2 %左 H PO 2A 0 MO F T产 品系列 的组 成部 分 ,为 电源设 计人 员提 SE

LN9T11LN9T39LN9T36LN9T33力生美电源管理芯片

LN9T11LN9T39LN9T36LN9T33⼒⽣美电源管理芯⽚LN9T11/LN9T39/LN9T36/LN9T33描述:LN9T11 是⾼性能、⾼集成度电流模式PWM 控制器,可以⽅便地在应⽤中构建满⾜CoC V5 及Do2016 等6 级能效的低待机功耗、低成本、⾼性能的解决⽅案。

PWM开关频率由芯⽚内部设定并具有全温度补偿,其最⼤值被设定在65kHz. 在空载或轻载条件下,IC可⼯作在智能断续模式以减少开关损失,因此可以达到很好的转换效率同时⼜具有较⼩的待机功耗。

很低的VDD 启动电流与⼯作电流可以使LN9T11拥有⾮常⾼的可靠性和使⽤寿命,⼀个较⼤阻值的电阻即可⽤来完成电路的启动⼯作,这也减少了启动电阻的损失,进⼀步降低了系统待机功耗。

内置的电流斜坡补偿功能则极⼤地优化了电路在较⼤的PWM 占空⽐时的可靠性LN9T33 是⼀款⾼性能、⾼集成度电流模式PWM控制器功率开关,可以⽅便地在应⽤中构建满⾜CoC V5 及DoE 6 级能效的低待机功耗、低成本、⾼性能的解决⽅案。

PWM开关频率由芯⽚内部设定并具有全温度补偿,其最⼤值被设定在65kHz. 在空载或轻载条件下,IC 可⼯作在智能断续模式以减少开关损失,因此可以达到很好的转换效率同时⼜具有较⼩的待机功耗。

很低的VDD 启动电流与⼯作电流可以使LN9T33 拥有⾮常⾼的可靠性和使⽤寿命,⼀个较⼤阻值的电阻即可⽤来完成电路的启动⼯作,这也减少了启动电阻的损失,进⼀步降低了系统待机功耗。

内置的电流斜坡补偿功能则极⼤地优化了电路在较⼤的PWM占空⽐时的可靠性,避免了可能出现的次谐波振荡现象。

内置的前沿消隐电路避免了电感开启电流尖峰对电流采样的⼲扰以及缓冲⼆极管反向恢复电流的影响LN9T39 是⼀款⾼性能、⾼集成度电流模式PWM控制器功率开关,可以⽅便地在应⽤中构建满⾜CoC V5 及DoE 6 级能效的低待机功耗、低成本、⾼性能的解决⽅案。

智慧社区应用案例

智慧社区与商业应用●日海物联是深圳日海通讯技术股份有限公司全资子公司,母公司日海通讯成立于1994年,2009年在深交所上市(代码:002313)。

6000万美●2017年9月,日海通讯联合大股东润良泰基金,出资元入股全球领先的物联网云平台企业Ayla Networks,并通过日海物联联合美国Ayla Networks成立合资公司日海艾拉Ayla Sunsea。

深圳研发中心(4200 m2)1.7亿元资金收购全球领先的无线通讯模块企●同时,日海物联以业龙尚科技。

●公司主要提供物联网云平台、模组、应用解决方案、电信业务虚拟运营等业务。

现有员工200余人,其中研发人员超过一半。

深圳生产中心 (60000 m2)全球物联网云平台领导品牌4G 模块出货量中国第一 中国第一家量产商用NB-IoT 模组 +SaaS 应用 云平台 “云”模组 终端SIM 卡 “端”移动端 Ayla Sunsea 移动应用 开发库 & AMAP 设备端Ayla Sunsea 嵌入式代理Linux / RTOS Gateway / SOC云端 Ayla Sunsea PaaS Cloud 云端增值服务规则引擎Ayla Sunsea Insights监控分析 NB-IoT客户只需要1个云平台,即可实现智能产品的全球部署遵循各地关于安全隐私的法律法规亚太、北美、欧洲的本地云服务 & 本地化技术支持团队 物联生态建立 开放性 安全性 SOC3国内唯一 每月处理20亿个请求可扩展性 每秒处理2000万个请求数据分析 360ºAyla Insight 稳定性 99.9% 99.99% 2017 2018基于ADI 芯片的2G 模块首发第一款3G 模块推出货, 世界上最薄的 HSUPA 模块国内2G 模块出货量第一 2005.11 2007.06. 2007.072007.10 2008.09公司成立,建立自主品牌’LongSung ’, 开始无线模块研发2009.320102009.07 为沃达丰定制3G 无线固话TD-SCDMA 模块国内出货量第一和英飞凌达成战略合作签署高通LICIENCE20133G 模块国内出货量三甲 2014.12推出国内第一款7模LTE 模块2016.10 推出世界上第一款NB-IoT/eMTC/GPRS 全模模块2G模块国内第一3G出货量国内领先LTE国内第一NB-IoT模块第一家量加入日海集团产商用车载●汽车前装●车辆跟踪●车队管理●OBD●两客一危●船舶跟踪●后视镜安防●视频监控●门禁●气体探测●烟雾探测●固定资产监控●入侵探测●动态感应能源●电表●气表●水表●发电机●充电桩●智能电网支付●无线POS●扫码支付●收银机●ATM机工业●工业路由器●工业PDA/扫描枪●工业电脑●机器人●流量计●无人机消费电子●PAD●电子书●PC●个人穿戴●宠物追踪●儿童手机●商务话机农业和环境●食品溯源●农田监控●养殖监控●野生动物保护●气象站●污染检测●农田灌溉医疗和健康●老人防护●可穿戴●远程医疗设备●血糖仪●血压仪●病人检测智慧城市●路灯●交通信号灯●智慧消防●电梯监控●停车场●广告机●垃圾箱监控智慧社区相关子系统智慧社区平台采用C/S、B/S、手机APP共享机制,基于电力自动化系统,并在此基础上进行专业化的研发,综合工业自动化软件和管理信息化软件的特点,具备脚本功能,支持二次开发,具有高安全性、响应速度快、模块化设计、扩展性强和运行稳定等特点;同时,平台自带大量应用库,可根据不同行业需求截剪出不同的应用系统。

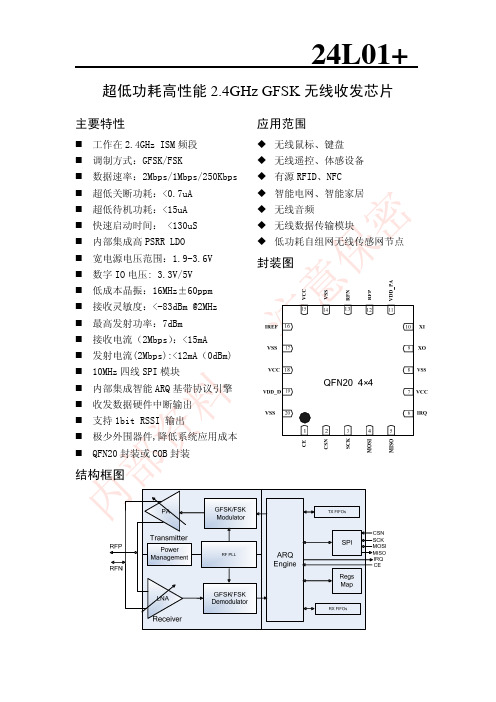

24l01(1)

24L01+超低功耗高性能 2.4GHz GFSK 无线收发芯片主要特性 工作在 2.4GHz ISM 频段 调制方式:GFSK/FSK 数据速率:2Mbps/1Mbps/250Kbps 超低关断功耗:<0.7uA 超低待机功耗:<15uA 快速启动时间: <130uS 内部集成高 PSRR LDO 宽电源电压范围:1.9-3.6V 数字 IO 电压: 3.3V/5V 低成本晶振:16MHz±60ppm 接收灵敏度:<-83dBm @2MHz 最高发射功率:7dBm 接收电流(2Mbps) :<15mA 发射电流(2Mbps):<12mA(0dBm) 10MHz 四线 SPI 模块 内部集成智能 ARQ 基带协议引擎 收发数据硬件中断输出 支持 1bit RSSI 输出 极少外围器件,降低系统应用成本 QFN20 封装或 COB 封装应用范围 无线鼠标、键盘 无线遥控、体感设备 有源 RFID、NFC 智能电网、智能家居 无线音频 无线数据传输模块 低功耗自组网无线传感网节点封装图结构框图24L01+术语缩写术语 ARQ ART ARD BER CE CRC CSN DPL GFSK IRQ ISM LSB Mbps MCU MHz MISO MOSI MSB PA PID PLD RX TX PWR_DWN PWR_UP RF_CH RSSI RX RX_DR SCK SPI TX TX_DS XTAL 描述 Auto Repeat-reQuest Auto ReTransmission Auto Retransmission Delay Bit Error Rate Chip Enable Cyclic Redundancy Check Chip Select Dynamic Payload Length Gaussian Frequency Shift Keying Interrupt Request Industrial-Scientific-Medical Least Significant Bit Megabit per second Micro Controller Unit Mega Hertz Master In Slave Out Master Out Slave In Most Significant Bit Power Amplifier Packet Identity Payload RX TX Power Down Power UP Radio Frequency Channel Received Signal Strength Indicator Receiver Receive Data Ready SPI Clock Serial Peripheral Interface Transmitter Transmit Data Sent Crystal 中文描述 自动重传请求 自动重发 自动重传延迟 误码率 芯片使能 循环冗余校验 片选 动态载波长度 高斯频移键控 中断请求 工业-科学-医学 最低有效位 兆位每秒 微控制器 兆赫兹 主机输入从机输出 主机输出从机输入 最高有效位 功率放大器 数据包识别位 载波 接收端 发射端 掉电 上电 射频通道 信号强度指示器 接收机 接收数据准备就绪 SPI 时钟 串行外设接口 发射机 已发数据 晶体振荡器24L01+目 录1、简介.................................................. 4 2、引脚信息 .............................................. 5 3、工作模式 .............................................. 6 4、寄存器映射表 .......................................... 9 5、主要参数指标 ......................................... 10 6、封装................................................. 12 7、典型应用原理图 ....................................... 14 8、订单信息 ............................................. 17附: 典型配置方案 ....................................... 1924L01+1、简介24L01 是一颗工作在2.4GHz ISM频段,专为低功耗无线场合设计,集成嵌 入式 ARQ 基带协议引擎的无线收发器芯片。

英飞凌与英特尔合作开发高密度SIM卡解决方案

【 ! i

“ 高基 ” 核 重大专 项论证 会 委员会 “ 端通 用芯 高

片” 组的专家们重点就企业的经济数据 、 研发投入与 规划 、 人员及研发能力 、 知识产权状况等情况听取 了

议, 并就企业 的一些 问题 进行 了详细 的交 流 。

t e 公司以及华威国际。公司计划将此轮资金用于 企业的汇报 ,就政府扶持 、管理等听取了企业 的建 us r 加速其利用先进的半导体工艺技术对 SC 台产品 o平

国科 、 正 、 科等 l 方 芯 5家企业进 行 了专题 座谈 。 考察 和调 研, 与 由 I 并 C基地 组 织 的具代 表 性 的 国微

h H n . i hIr电c ■ 巾a gd路 in成 u 集 e r nt Ci a t

北京都设立了研发中心 , 并在美国加洲圣塔克拉拉,