makefile新手教程

makefile的使用

makefile的使用

Makefile是一种文本文件,由Make程序读取和执行,用于编译和生成可执行文件、库文件等。

Makefile规定了文件依赖关系和编译指令,通过执行Makefile 文件,可以自动化编译程序和生成可执行文件。

Makefile的使用:

1. 编写Makefile文件:Makefile文件是一个文本文件,可以使用任何文本编辑器进行编写。

Makefile文件应该包含编译指令、文件依赖关系和可执行文件的生成指令等。

2. 执行Makefile文件:在命令行输入“make”命令,Make程序将读取并执行Makefile文件。

若Makefile文件中存在错误,Make程序将报告错误并停止执行。

3. 维护Makefile文件:Makefile文件应该随着代码的变化而更新和维护,以确保编译指令正确地反映了代码的依赖关系。

常用命令:

1. make:执行Makefile文件,开始编译程序。

2. make clean:清除所有中间文件和生成的可执行文件。

3. make install:将生成的可执行文件安装到指定目录中。

4. make uninstall:从系统中卸载指定的可执行文件。

5. make help:显示Makefile文件中定义的所有命令和说明。

linux makefile流程

linux makefile流程

在Linux系统中,Makefile是一种用于管理和自动化构建过程的工具。

它定义了

编译、链接和其他操作的规则,以及这些操作所依赖的文件和目标。

下面是Makefile的基本流程:

1. 确定目标:Makefile中首先需要指定要构建的目标,这些目标可以是执行文件、库文件或其他想要生成的输出。

2. 定义变量:在Makefile中,变量用于存储要使用的命令、编译器选项、源文件

列表等信息。

通过定义变量,可以简化Makefile的维护和修改。

3. 定义规则:规则描述了如何生成目标文件的过程。

每条规则包括目标、依赖和

命令。

目标是要生成的文件或动作,依赖是生成目标所需的文件或动作,命令是

执行操作的命令。

4. 构建依赖关系:Makefile使用依赖关系来确定何时重新构建目标。

依赖关系指

定了目标所依赖的文件或其他目标。

5. 执行命令:当执行make命令时,Makefile会检查目标及其依赖关系,并根据

需要执行相关命令。

Makefile会自动判断哪些文件需要重新构建,以及构建的顺序。

6. 更新目标:如果目标不存在或其依赖发生了变化,Makefile会根据规则中定义

的命令重新生成目标。

7. 清理目标:可以在Makefile中添加一个"clean"规则来删除生成的目标文件和其

他中间文件,以便重新构建项目。

8. 终止构建:在构建过程中,如果发生错误或出现其他异常情况,可以通过抛出

错误或使用特定命令来停止构建过程。

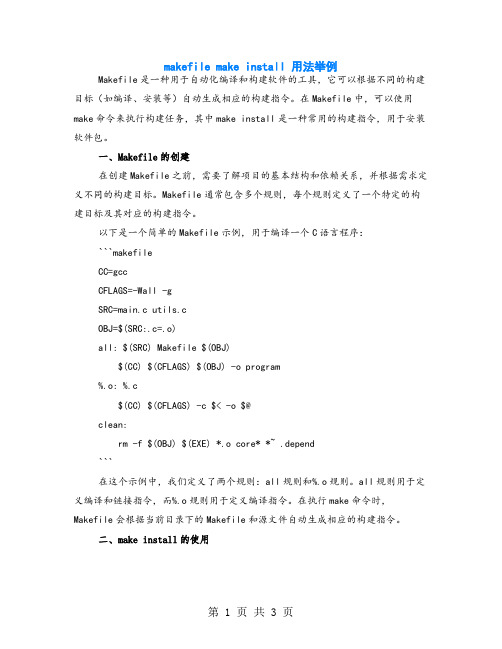

makefile make install 用法举例

makefile make install 用法举例Makefile是一种用于自动化编译和构建软件的工具,它可以根据不同的构建目标(如编译、安装等)自动生成相应的构建指令。

在Makefile中,可以使用make命令来执行构建任务,其中make install是一种常用的构建指令,用于安装软件包。

一、Makefile的创建在创建Makefile之前,需要了解项目的基本结构和依赖关系,并根据需求定义不同的构建目标。

Makefile通常包含多个规则,每个规则定义了一个特定的构建目标及其对应的构建指令。

以下是一个简单的Makefile示例,用于编译一个C语言程序:```makefileCC=gccCFLAGS=-Wall -gSRC=main.c utils.cOBJ=$(SRC:.c=.o)all: $(SRC) Makefile $(OBJ)$(CC) $(CFLAGS) $(OBJ) -o program%.o: %.c$(CC) $(CFLAGS) -c $< -o $@clean:rm -f $(OBJ) $(EXE) *.o core* *~ .depend```在这个示例中,我们定义了两个规则:all规则和%.o规则。

all规则用于定义编译和链接指令,而%.o规则用于定义编译指令。

在执行make命令时,Makefile会根据当前目录下的Makefile和源文件自动生成相应的构建指令。

二、make install的使用make install是Makefile中常用的一种构建指令,用于将软件包安装到目标系统中。

使用make install命令时,需要指定安装的目标目录和安装选项。

下面是一个简单的示例:假设我们有一个名为myapp的软件包,将其安装到/usr/local/目录下:```bashmake install prefix=/usr/local/```在这个示例中,我们使用make install命令将myapp软件包安装到/usr/local/目录下。

windows makefile编译

windows makefile编译随着仓库中的代码越来越复杂,对于不同的平台和系统,不同的编译工具都被用来生成可执行文件。

在Windows平台上,Makefile是一种非常流行的编译工具,这篇文章将会详细介绍如何使用Windows Makefile来编译。

下面我们将分步骤阐述这个过程。

1. 安装编译工具首先需要安装MinGW编译工具。

MinGW是一个Windows下基于GNU编译器集合的开发环境,它包含了编译器和各种实用程序。

你可以在MinGW的官网上下载。

下载完成后,进行安装并将MinGW添加到系统路径中。

2. 创建Makefile接下来,需要创建一个Makefile来告诉Make怎么去编译代码以及链接库文件。

在Makefile中,可以定义一些常量和变量,来提高Makefile的重用性。

同时,还需要定义源代码和头文件的位置,以及生成的可执行文件的名称。

3. 编写Makefile下面是一个简单的Makefile的例子:```CC=gccCFLAGS=-c -WallLDFLAGS=-lmSOURCES=main.cOBJECTS=$(SOURCES:.c=.o)EXECUTABLE=myappall: $(SOURCES) $(EXECUTABLE)$(EXECUTABLE): $(OBJECTS)$(CC) $(OBJECTS) $(LDFLAGS) -o $@.c.o:$(CC) $(CFLAGS) $< -o $@```在这个例子中,我们定义了CC变量为gcc编译器,CFLAGS变量为编译选项。

同时,还定义了LDFLAGS变量为链接选项,SOURCES变量为源代码文件名称,OBJECTS变量为生成的目标文件对象名称,EXECUTABLE变量为生成的可执行文件名称。

对于Makefile中的命令,需要使用Tab键缩进来区分命令和规则。

在这个例子中,我们定义了一个默认目标all,它依赖于源代码和可执行文件。

python makefile 用法

python makefile 用法在使用Python编写程序时,我们通常需要编译和运行代码,这就需要用到makefile。

makefile是一种可以自动化地构建程序的工具,它可以根据代码修改的情况自动判断哪些文件需要重新编译,从而提高程序的编译效率。

使用makefile的基本步骤如下:1. 创建一个名为makefile的文件,通常放在程序的根目录下。

2. 在makefile中定义一些变量,如编译器、编译选项等。

3. 定义一些规则,如编译规则、目标规则等。

4. 运行make命令,根据makefile的规则进行编译和链接。

下面是一个简单的makefile示例:```# 定义编译器和编译选项CC=gccCFLAGS=-Wall -g# 定义编译规则%.o: %.c$(CC) $(CFLAGS) -c $< -o $@# 定义目标规则main: main.o sub.o$(CC) $(CFLAGS) main.o sub.o -o main# 清除中间文件clean:rm -f *.o main```在这个示例中,我们定义了两个变量CC和CFLAGS,分别表示编译器和编译选项。

接着定义了一个编译规则,表示将.c文件编译成.o文件的过程。

其中,$<表示依赖文件(即输入文件),$@表示目标文件(即输出文件)。

最后定义了一个目标规则,表示将main.o和sub.o链接成可执行文件main。

最后,我们定义了一个清除中间文件的规则,可以通过运行make clean来清除中间文件。

可以通过运行make命令来编译和链接程序。

例如,如果你有一个名为main.c和sub.c的源文件,并想将它们编译成可执行文件main,可以在终端中输入以下命令:```$ make main```这将根据makefile中定义的规则自动编译和链接程序,并生成可执行文件main。

总之,makefile是一个非常有用的编译工具,可以帮助我们自动化地构建程序,提高编译效率。

makefile的通用编写 -回复

makefile的通用编写-回复Makefile是一种用于自动化构建和管理项目的工具,它使用一种被称为Makefile的文件来指定构建和管理项目的规则。

Makefile通常由一系列目标(target)、依赖关系(dependencies)和命令(commands)组成。

在本文中,我们将详细介绍Makefile的通用编写方法,从创建一个简单的Makefile文件开始,到使用变量、条件、循环和函数等高级特性,帮助读者更好地理解和使用Makefile。

让我们一步一步地回答您的问题,教您如何编写一个高效的Makefile。

第一步:创建一个简单的Makefile文件为了开始编写Makefile,我们首先需要在项目的根目录下创建一个名为Makefile的文本文件。

可以使用任何文本编辑器来创建并编辑这个文件。

在开始编写之前,我们需要了解一些基本的语法和规则。

Makefile文件由一系列规则组成,每个规则包含一个或多个目标、依赖关系和命令。

例如,我们可以创建一个简单的规则来构建一个名为hello的可执行文件:hello: main.ogcc -o hello main.omain.o: main.cgcc -c main.c在这个例子中,我们创建了一个名为hello的目标,它依赖于main.o 文件。

我们还创建了一个名为main.o的目标,它依赖于main.c文件。

每个目标都有相应的命令,用于构建目标所需的文件。

第二步:使用变量变量是Makefile中非常常用的机制,它可以帮助我们更好地管理和维护项目。

可以通过在Makefile文件中定义变量,然后在规则和命令中使用这些变量来简化代码。

例如,我们可以使用变量来代替文件名:CC = gccCFLAGS = -chello: main.o(CC) -o hello main.omain.o: main.c(CC) (CFLAGS) main.c在这个例子中,我们定义了两个变量CC和CFLAGS。

linux makefile 写法

linux makefile 写法Linux Makefile 写法Makefile 是一种用于组织和管理软件项目的文件格式,它指导着编译器如何构建程序。

在Linux 环境下,Makefile 是一种特别常见的构建工具,它通过定义目标和规则,使得软件开发人员能够轻松地构建、编译和部署项目。

本文将一步一步回答关于Linux Makefile 写法的问题,帮助你深入了解如何编写高效的Makefile。

第一步:创建Makefile 文件首先,你需要在你的Linux 环境中创建一个名为"Makefile" 的文本文件。

你可以使用任何文本编辑器,如Vim、Nano 或者Emacs 来完成这个任务。

确保你的Makefile 文件保存在项目的根目录下,这样Make 命令才能找到它。

第二步:定义变量在Makefile 中,你可以定义各种变量来存储重复使用的值,如编译器名称、编译选项和目标文件名。

定义变量的语法是"变量名=值",例如:CC=gccCFLAGS=-Wall -WerrorTARGET=myprogram在上面的例子中,我们定义了三个变量:`CC`、`CFLAGS` 和`TARGET`。

`CC` 变量的值是`gcc`,指定了使用GCC 编译器。

`CFLAGS` 变量的值是`-Wall -Werror`,这些编译选项用于启用所有警告,并将警告视为错误。

`TARGET` 变量的值是`myprogram`,这是我们期望生成的最终可执行文件的名称。

第三步:指定编译规则在Makefile 中,你需要指定编译规则来告诉编译器如何构建你的程序。

编译规则由目标、依赖和命令组成。

下面是一个简单的例子:(TARGET): main.o utils.o(CC) (CFLAGS) -o (TARGET) main.o utils.o在上面的例子中,我们指定了一个名为`(TARGET)` 的目标,它依赖于`main.o` 和`utils.o` 两个文件。

makefile基本使用方法

makefile基本使用方法makefile是一种用来管理和自动化构建程序的工具。

它可以根据源代码文件的依赖关系和编译规则来自动构建目标文件和可执行文件。

makefile的基本使用方法如下:1. 创建makefile文件:在项目的根目录下创建一个名为makefile 的文件。

2. 定义变量:在makefile中,可以使用变量来存储一些常用的参数和路径,以便于后续的使用。

例如,可以定义一个名为CC的变量来指定编译器的名称,如:CC=gcc。

3. 编写规则:在makefile中,可以使用规则来指定如何编译源代码文件和生成目标文件。

一个规则由两部分组成:目标和依赖。

目标是要生成的文件,依赖是生成目标文件所需要的源代码文件。

例如,可以编写以下规则:```target: dependency1 dependency2command1command2```其中,target是目标文件,dependency1和dependency2是依赖的源代码文件,command1和command2是生成目标文件所需要执行的命令。

4. 编写默认规则:在makefile中,可以使用一个默认规则来指定如何生成最终的可执行文件。

默认规则的目标通常是可执行文件,依赖是所有的源代码文件。

例如,可以编写以下默认规则:```all: target1 target2```其中,target1和target2是生成的目标文件。

5. 编写clean规则:在makefile中,可以使用clean规则来清理生成的目标文件和可执行文件。

例如,可以编写以下clean规则: ```clean:rm -f target1 target2```其中,target1和target2是要清理的目标文件。

6. 运行make命令:在命令行中,使用make命令来执行makefile 文件。

make命令会自动根据规则和依赖关系来编译源代码文件和生成目标文件。

例如,可以运行以下命令:``````make命令会根据makefile文件中的规则和依赖关系来编译源代码文件并生成目标文件和可执行文件。

makefile基础教程-GNUmake介绍

第二章:GNU make 介绍make在执行时,需要一个命名为Makefile的文件。

这个文件告诉make以何种方式编译源代码和链接程序。

典型地,可执行文件可由一些.o文件按照一定的顺序生成或者更新。

如果在你的工程中已经存在一个活着多个正确的Makefile。

当对工程中的若干源文件修改以后,需要根据修改来更新可执行文件或者库文件,正如前面提到的你只需要在shell下执行“make”。

make会自动根据修改情况完成源文件的对应.o文件的更新、库文件的更新、最终的可执行程序的更新。

make通过比较对应文件(规则的目标和依赖,)的最后修改时间,来决定哪些文件需要更新、那些文件不需要更新。

对需要更新的文件make就执行数据库中所记录的相应命令(在make读取Makefile以后会建立一个编译过程的描述数据库。

此数据库中记录了所有各个文件之间的相互关系,以及它们的关系描述)来重建它,对于不需要重建的文件make什么也不做。

而且可以通过make的命令行选项来指定需要重新编译的文件。

Problems and Bugs=================If you have problems with GNU `make' or think you've found a bug, please report it to the developers; we cannot promise to do anything but we might well want to fix it.Before reporting a bug, make sure you've actually found a real bug.Carefully reread the documentation and see if it really says you can do what you're trying to do. If it's not clear whether you should be able to do something or not, report that too; it's a bug in the documentation!Before reporting a bug or trying to fix it yourself, try to isolate it to the smallest possible makefile that reproduces the problem. Then send us the makefile and the exact results `make' gave you, including any error or warning messages. Please don't paraphrase these messages: it's best to cut and paste them into your report. When generating this small makefile, be sure to not use any non-free or unusual tools in your commands: you can almost always emulate what such a tool would do with simple shell commands. Finally, be sure to explain what you expected to occur; this will help us decide whether the problem was really in the documentation.Once you have a precise problem you can report it in one of two ways.Either send electronic mail to:bug-make@or use our Web-based project management tool, at:/projects/make/In addition to the information above, please be careful to include the version number of `make' you are using. You can get this information with the command `make --version'. Be sure also to include the type of machine and operating system you are using. One way to obtain this information is by looking at the final lines of output from the command`make --help'.以上时GNU make的bug反馈方式。

makefile笔记

makefile笔记Makefile是一个用来组织和管理程序编译和链接的工具。

通过定义一系列规则和命令,我们可以使用Makefile来自动化构建和管理大型项目的编译过程。

本文将介绍Makefile的基本语法和常用命令,以及如何编写一个简单的Makefile文件。

一、Makefile基本语法1. 标准格式Makefile由一系列规则组成,每个规则包含了一个目标(target)、我们想要生成的文件名,以及生成目标所需要的依赖关系(prerequisites)和命令(recipe)。

通常一个规则的基本格式如下:```makefiletarget: prerequisitesrecipes```其中,target是需要生成的文件名,prerequisites是依赖文件,recipes是生成目标所需要执行的命令。

2. 规则的执行原则- 如果target不存在或者target的依赖文件比target更新,那么执行recipes中的命令。

- 如果target的依赖文件有更新,那么也会执行recipes中的命令。

3. 空格和Tab键缩进在Makefile中,空格和Tab键具有不同的含义。

空格用来分隔目标、依赖和命令,而Tab键则用来标识命令行。

因此,在Makefile中,必须使用Tab键来缩进每条命令。

二、Makefile常用命令1. makemake命令是用来执行Makefile中的规则的。

通过运行make命令,可以自动编译和链接项目。

```shellmake target```2. make cleanclean是一个常用的命令,用于清除编译生成的文件。

在Makefile中,我们可以定义一个clean规则,然后通过运行make clean命令来执行清除操作。

```makefileclean:rm -f target```3. make allall是另一个常用的命令,在Makefile中可以定义一个all规则,用于执行整个项目的编译和生成。

make使用方法以及makefile的编写

make使用方法以及makefile的编写make是一个常用的构建工具,通过解析Makefile文件来完成代码的编译、链接和打包等操作。

下面是make的使用方法以及Makefile的编写方法:使用方法:1. 创建一个名为Makefile的文件,并在该文件中定义编译规则。

2. 在命令行中进入到Makefile所在的目录。

3. 执行make命令即可开始编译。

4. make根据Makefile文件中的规则来判断哪些文件需要重新编译,然后执行相应的编译命令。

Makefile的编写:1. 编写规则格式如下:target: dependencies<tab> command其中,target是规则的目标文件,dependencies是依赖的文件,command 是执行的命令。

2. 使用变量来简化编写过程,例如:CC=gccCFLAGS=-Walltarget: dependencies(CC) (CFLAGS) -o target source.c这里的CC是编译器,CFLAGS是编译选项。

3. 使用通配符(如"%")来表示一组文件或者目录,例如:objects := (patsubst %.c, %.o, (wildcard *.c))target: (objects)(CC) (CFLAGS) -o target (objects)这里使用wildcard获取所有的.c文件,然后使用patsubst将.c替换为.o。

4. 可以定义伪目标(phony target)来执行一些特殊的命令,例如:.PHONY: cleanclean:rm -f target (objects)这里的clean是一个伪目标,rm命令会删除目标文件以及所有的依赖文件。

5. 可以使用条件语句来根据不同的条件执行不同的命令,例如:ifdef DEBUGCFLAGS += -gendiftarget: dependencies(CC) (CFLAGS) -o target source.c这里的ifdef DEBUG表示只有在定义了DEBUG宏的情况下才启用-g(调试)选项。

makefile 速成

分享一篇前短时间总结的makefile速成,教你一天搞定makefile,略加实践掌握其最核心部分。

可以从下面的几个维度来学习和理解makefile:∙规则∙变量∙函数∙命令∙make的命令选项∙一个大型项目的makefile例子∙make –p的输出概览在正式介绍makefile的以上四个方面之前,首先一句话概括一下makefile 是什么:makefile是用来描述文件依赖关系,并告诉make命令如何根据这种依赖关系,调用shell完成目标文件建立的文件。

makefile的执行时通过两步来完成的,第一步是扫描文件中的依赖关系,并藉此建立依赖关系树,然后从最底层想上来执行。

1.规则(rule)Makefile从本质上说就是描述项目中文件依赖关系的文件。

这种依赖关系的描述就是规则。

Makefile的编写中的一切都是围绕规则来展开的,上面提到的四个方面:规则、变量、函数、命令都是为了规则能够方便快捷的发挥作用才引入的。

一个简单规则可以表述为:目标文件:依赖文件(不同文件以空格分隔)<tab>得到目标文件需要的命令规则的常见种类有:●∙Explicit Rule最简单的rule,明确指出了目标和依赖,以及如何有依赖得到目标。

举例:Hello.o:hello.cppg++ -c hello.cpp●∙Pattern Rule使用了wildcard(通配符)的规则。

makefile中的通配符是百分号%,相当于bash中的*,在描述规则的时候使用的都是%。

makefile中也可以看到通配符*,这个一般是出现在命令之中,命令是要放到shell中运行的,所以要使用*作为通配符。

举例:prog:*.cg++ -o prog $^●∙Suffix Rule顾名思义,是只使用后缀来描述的rule,描述的时候不使用pattern,举例:.c.o:$(COMPILE.C) $(OUTPUT_OPTION) $<这个suffix rule的作用和下面这个pattern rule的作用是完全一样的。

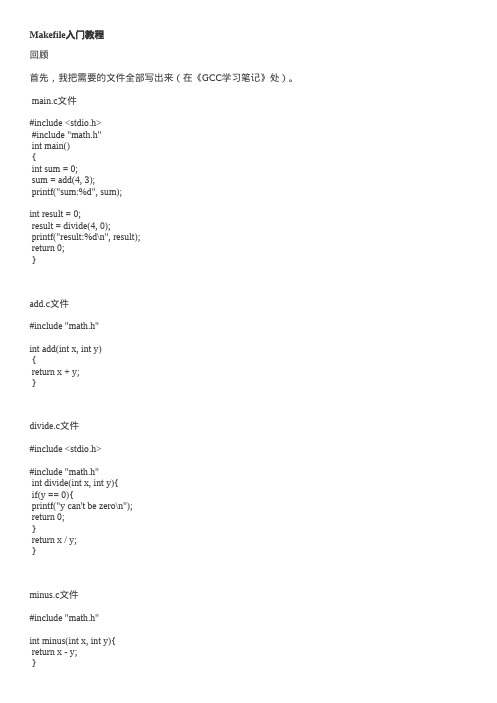

Makefile入门教程

multiply.c文件

#include "math.h"

int multiply(int x, int y){ return x * y; }

math.h文件

int add(int x, int y);

int minus(int x, int y);

一个工程中的源文件不计数,其按类型、功能、模块分别放在若干个目录中,makefile定义了一系列的规 则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至于进行更复杂的 功能操作,因为makefile就像一个Shell脚本一样,其中也可以执行操作系统的命令. 使用规则

目标文件 : 先决条件

int divide(int x, int y);

int multiply(int x, int y); 现在,在我的当前目录下有main.c add.c minus.c divide.c multiply.c 和math.h六个文件,下面的内容就会 围绕这几个文件来举例讲述。

问题

在《gcc学习笔记》一节,我已经提到过,如果要对add.c minus.c divide.c multiply.c这四个中其中一个 作修改,那么就需要重新编译相应的源文件,生成新的目标文件,然后再进行链接,才可以生成修改后 的执行文件。大家想想,如果说我们做的是一个大工程,那文件可是成千上百个啊!如果我们还是像现 在这样,一个个地重新编译文件,那效率是极其低下的。于是就出现了makefile工具解决这个问题。 什么是makefile

rm calculate main.o add.o divide.o minus.o multiply.o clean在这里不是一个文件,是一个标签,它冒号后面什么也没有,那就是说make不会自动去找文件的依 赖性,也就不会自动执行其后所定义的命令。

makefile 的简单使用方法

makefile 的简单使用方法【最新版3篇】《makefile 的简单使用方法》篇1Makefile 是一个工程文件的编译规则,用于描述整个工程的自动编译和链接的规则。

它可以简单的认为是一个批处理文件,可以自动执行编译、链接等命令。

以下是一个简单的Makefile 的使用方法:1. 创建一个Makefile 文件,通常以.make 为扩展名。

2. 在Makefile 中指定需要编译的源文件和目标文件,以及编译命令和链接命令。

3. 在Makefile 中定义变量,用于存储编译和链接过程中的相关信息,例如编译器路径、目标文件路径等。

4. 在Makefile 中使用条件语句,根据不同的条件来指定不同的编译和链接规则。

5. 在Makefile 中使用include 语句,将多个Makefile 文件包含在一起,以便更好地组织和管理编译规则。

6. 在Makefile 中使用注释,用于说明编译规则的详细信息和用途。

7. 执行Makefile 命令,使Makefile 中的编译和链接规则生效,生成所需的目标文件。

以上是Makefile 的一个简单使用方法,具体的使用方法还需要根据具体的需求进行调整和修改。

《makefile 的简单使用方法》篇2Makefile 是一个工程文件的编译规则,用于描述整个工程的自动编译和链接的规则。

它可以简单的认为是一个批处理文件,可以自动化编译和链接过程,避免手动执行编译和链接命令。

以下是Makefile 的简单使用方法:1. 创建Makefile 文件:在工程目录中创建一个名为“Makefile”的文件,该文件包含工程的编译规则。

2. 编写Makefile 文件:在Makefile 文件中,编写工程的编译规则,包括显式规则、隐晦规则、变量定义、文件指示和注释等。

3. 编译工程:在命令行中进入工程目录,执行“make”命令,Makefile 会自动执行编译和链接命令,生成可执行文件。

Makefile入门教程

Makefile ⼊门教程Makefile介绍make是⼀个命令⼯具,它解释Makefile 中的指令(应该说是规则)。

在Makefile⽂件中描述了整个⼯程所有⽂件的编译顺序、编译规则。

Makefile 有⾃⼰的书写格式、关键字、函数。

像C 语⾔有⾃⼰的格式、关键字和函数⼀样。

⽽且在Makefile 中可以使⽤系统shell所提供的任何命令来完成想要的⼯作。

Makefile格式最简单的Makefile以Hello World为例:(1) 先编写好源⽂件(.c⽂件),然后在同⼀⽬录下新建名为Makefile(之前⾸字母必须⼤写,现在⼤⼩写都⾏)的⽂本⽂件。

(2) 编写Mikefile(3)打开终端,运⾏make命令,即可⽣成可执⾏⽂件hello,运⾏hello,即输出Hello World.1 target: prerequisites2 commands345 ⽬标⽂件: 依赖项6 命令变量的定义及使⽤实际效果没变,只是便于修改某些参数使⽤变量替换后的情况:同时编译多个可执⾏⽂件例如:bar.c包含求数组中最⼤值函数,foo.c包含求数组中最⼩值函数,各⾃对应的头⽂件是bar.h、foo.h,main_max调⽤求最⼤值函数来打印最⼤值,main_min调⽤求最⼩值函数打印最⼩值。

Makefile可如下编写:1 CC = gcc #定义变量并赋值2 CFLAGS = -lm -Wall -g34 hello: hello.c5 $(CC) $(CFLAGS) hello.c - o hello #引⽤前⾯定义的变量,$(变量名),这种形式1 CC = gcc2 CFLAGS = -O -Wall -m64 -std=gnu893 LIBS = -lm45 all: main_max main_min #必须写成all 这样的形式,否则只会⽣成前⼀个可执⾏⽂件main_max67 main_max: main_max.c bar.o foo.o8 $(CC) main_max.c bar.o foo.o -o main_max910 main_min: main_min.c bar.o foo.o11 $(CC) main_min.c bar.o foo.o -o main_min1213foo.o: foo.c14 $(CC) -c foo.c1516bar.o: bar.c17 $(CC) -c bar.c1819.PHONY: clean20 clean:21rm *.o main_max main_minclean由于源代码发布通常不会有可执⾏⽂件和.o⽂件,使⽤ rm *.o xx(可执⾏⽂件名) ,再输⼊make clean命令就可以⾃动清除。

Linux下Makefile简单教程

目录一:Makefile基本规则1.1示例1.2 隐式规则1.3 伪目标1.4 搜索源文件二:变量2.1使用变量定义变量值2.2追加变量三:条件判断四:函数Linux下Makefile总结——一步MakeFile可以看做是一种简单的编程语言,其诞生的本质目的是实现自动化编译。

以Linux下gcc-c编译器为例,编译一个c语言程序需要经过以下几个步骤:1.将c语言源程序预处理,生成.i文件;2.预处理后的.i语言编译成汇编语言,生成.s文件;3.汇编语言经过汇编,生成目标文件.o文件;4.将各个模块的.o文件链接起来,生成一个可执行程序文件。

我们知道,在Visual C++6.0中,可以新建一个工程,在一个工程当中能够包含若干个c语言文件,则编译的时候直接编译整个工程便可。

Linux下无法为多个c语言文件新建工程,但可以通过MakeFile实现它们的整合编译。

如上gcc-c编译步骤,如果使用Makefile则过程为:.C文件——>.o文件——>可执行文件当然,Makefile中也加入了自己的设置变量方法与集成了一些函数,能够更有效地方便用户使用。

/**************************分隔符********************************/ 一:Makefile基本规则1.1示例target ... : prerequisites ...command......target也就是一个目标文件,可以是Object File,也可以是执行文件。

prerequisites就是,要生成那个target所需要的文件或是目标。

command也就是make需要执行的命令。

(任意的Shell命令)为了方便理解,我们来看一个示例:/*Makefile示例*/edit : main.o kbd.o command.o display.o /insert.o search.o files.o utils.ogcc -o edit main.o kbd.o command.o display.o /insert.o search.o files.o utils.omain.o : main.c defs.h #生成main.ogcc -c main.ckbd.o : kbd.c defs.h command.h #生成kdb.ogcc -c kbd.ccommand.o : command.c defs.h command.h #生成command.ogcc -c command.cdisplay.o : display.c defs.h buffer.h #生成display.ogcc -c display.cinsert.o : insert.c defs.h buffer.h #生成insert.ogcc -c insert.csearch.o : search.c defs.h buffer.h #生成search.ogcc -c search.cfiles.o : files.c defs.h buffer.h command.h #生成files.ogcc -c files.cutils.o : utils.c defs.h #生成utils.ogcc -c utils.cclean :rm edit main.o kbd.o command.o display.o /insert.o search.o files.o utils.o/*END*/执行输入:make -s edit反斜杠(/)是换行符的意思。

makefile基础实例讲解

Makefile基础实例讲解一、makefile简介定义:makefile定义了软件开发过程中,项目工程编译链、接接的方法和规则。

产生:由IDE自动生成或者开发者手动书写。

作用:Unix(MAC OS、Solars)和Linux(Red Hat、Ubuntu)系统下由make命令调用当前目录下的makefile文件执行,可实现项目工程的自动化编译。

二、语法规则target:prerequisitescommand其中,target为需要生成的目标,prerequisites为依赖项,command为make需要执行的命令(任意的Shell命令)。

注意:其中command前必须以tab键开始。

三、makefile内容Makefile里主要包含了五个东西:显式规则、隐晦规则、变量定义、文件指示和注释。

1.显式规则。

显式规则说明了,如何生成一个或多的的目标文件。

这是由Makefile的书写者明显指出,要生成的文件,文件的依赖文件,生成的命令。

2.隐晦规则。

由于我们的make有自动推导的功能,所以隐晦的规则可以让我们比较粗糙地简略地书写Makefile,这是由make所支持的。

3.变量的定义。

在Makefile中我们要定义一系列的变量,变量一般都是字符串,这个有点你C语言中的宏,当Makefile被执行时,其中的变量都会被扩展到相应的引用位置上。

4.文件指示。

其包括了三个部分,一个是在一个Makefile中引用另一个Makefile,就像C语言中的include一样;另一个是指根据某些情况指定Makefile中的有效部分,就像C 语言中的预编译#if一样;还有就是定义一个多行的命令。

有关这一部分的内容,请参考文末的参考资料。

5.注释。

Makefile中只有行注释,和UNIX的Shell脚本一样,其注释是用“#”字符,这个就像C/C++中的“//”一样。

如果你要在你的Makefile中使用“#”字符,可以用反斜框进行转义,如:“\#”。

跟我一起学makefile

Makefile学习教程: 跟我一起写Makefile o0 Makefile概述▪0.1 关于程序的编译和链接o 1 Makefile 介绍▪1.1 Makefile的规则▪1.2 一个示例▪1.3 make是如何工作的▪1.4 makefile中使用变量▪1.5 让make自动推导▪1.6 另类风格的makefile▪1.7 清空目标文件的规则o 2 Makefile 总述▪2.1 Makefile里有什么?▪2.2Makefile的文件名▪2.3 引用其它的Makefile▪2.4 环境变量MAKEFILES▪2.5 make的工作方式o 3 Makefile书写规则▪3.1 规则举例▪3.2 规则的语法▪3.3 在规则中使用通配符▪3.4 文件搜寻▪3.5 伪目标▪3.6 多目标▪3.7 静态模式▪3.8 自动生成依赖性o 4 Makefile 书写命令▪4.1 显示命令▪4.2 命令执行▪4.3 命令出错▪4.4 嵌套执行make▪4.5 定义命令包什么是makefile?或许很多Winodws的程序员都不知道这个东西,因为那些Windows的IDE都为你做了这个工作,但我觉得要作一个好的和professional 的程序员,makefile还是要懂。

这就好像现在有这么多的HTML的编辑器,但如果你想成为一个专业人士,你还是要了解HTML的标识的含义。

特别在Unix下的软件编译,你就不能不自己写makefile了,会不会写makefile,从一个侧面说明了一个人是否具备完成大型工程的能力。

因为,makefile关系到了整个工程的编译规则。

一个工程中的源文件不计数,其按类型、功能、模块分别放在若干个目录中,makefile定义了一系列的规则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至于进行更复杂的功能操作,因为makefile就像一个Shell脚本一样,其中也可以执行操作系统的命令。

C++学习进阶之Makefile基础用法详解

$(TARGET):$(TESTOBJ) $(LIB) $(CXX) $< -o $@ $(LDFLAGS) $(LDLIBS)

$(LIB):$(OBJS) $(CXX) -shared $^ -o $@

$(TESTOBJ) $(OBJS):%.o:%.cpp $(CXX) $(CXXFLAGS) $< -o $@

makefile 文件可改为:

TARGET = simpletest OBJS = simple.o simpletest.o

$(TARGET):$(OBJS) g++ $(OBJS) -o $(TARGET)

simple.o:simple.cpp simpletest.o:simpletest.cpp clean:

绝大多数的 IDE 开发环境都会为用户自动编写 Makefile。

Make 是怎么工作的?

Make 工作的原则就是:

一个目标文件当且仅当在其依赖文件(dependencies)的更改时间戳比该目标文件的创建时间戳新时,这个目标文件才需要 被重新编译。

Make 工具会遍历所有的依赖文件,并且把它们对应的目标文件进行更新。编译的命令和这些目标文件及它们对应的依赖文件 的关系则全部储存在 Makefile 中。

Makefile 中也指定了应该如何创建,创建出怎么样的目标文件和可执行文件等信息。

除此之外,你甚至还可以在 Makefile 中储存一些你想调用的系统终端的命令,像一个 Shell 脚本一样使用它。

作用:

Makefile 文件告诉 Make 怎样编译和连接成一个程序

可用命令 dnf install make 安装make功能

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

makefile新手教程

2013-11-08

本文翻译自/tutorials/

Makefiles

--通过示例说明

编译源代码是沉闷的,尤其是当你想要include一些源代码,却又每次都需要手动敲编译命令的时候。

恩,我有个好消息告诉你...你用手敲命令行去编译的日子(基本上)一去不复返了,因为你将会学习如何编写Makefile。

Makefile是配合make命令使用的特殊文件,make命令则会帮助你自动地、神奇般地管理你的工程。

这里你需要先准备以下文件:

main.cpp

hello.cpp

factorial.cpp

functions.cpp

我建议你新建一个空的目录,然后将上述4个文件放入其中。

注意:我使用g++命令编译。

你完全可以换成别的编译器

make工具

如果你运行make 它会去寻找当前目录下名字为makefile的文件,并按里面的内容执行。

如果你有很多makefile文件,那么可以用这个命令来执行:

当然还有其他的参数来使用make工具,详情请man make。

构建过程

1.编译器编译源代码文件,输出到目标文件

2.链接器将目标文件链接,并创建可执行文件

手动编译

手动编译并获得可执行文件,是一种琐碎的方式:

基本的Makefile

基本的makefile文件组成如下:

将此语法应用到我们的例子中,就是: all: g++ main.cpp hello.cpp factorial.cpp -o hello 我们将此文件保存为Makefile-1。

要运行此makefile,则输入:make -f Makefile-1 在这个例子中可以看到,我们的target叫做all。

这是makefile中的默认target。

若无指定参数,make工具将按这个target 执行。

我们同时发现,这个例子中的target,也就是all,没有dependencies(依赖文件),因此make会安全地执行后续的system commands(系统命令)。

最后,make根据我们设定的命令完成了编译。

使用依赖文件

有时候使用多个不同的target会很有用,因为当你只修改了工程中的一个文件时,不必重新编译所有代码,只需要编译修改过的部分。

比如:

点此下载

我们发现目标all只有依赖关系,没有系统命令。

为了让make命令正确执行,需要保证能满足所调用target的依赖关系(本例中是all)。

所有target中的依赖项都会被搜索,并且一旦发现,就会执行后续的系统命令。

本例中,我们有一个target叫做clean。

当想要快速除去所有目标文件和可执行文件时,它将很有帮助。

使用变量和注释

当编写Makefile时,可以使用变量。

当你想要更换编译器或者编译选项的时候,将会很方便。

正如你所见,变量有时很有用。

要使用它们,只需在开始写target之前为其赋值。

然后,使用$(VAR)的形式表示对应的值。

接下来怎么做

通过上面对Makefile的简短介绍,你可以在工程中创建十分复杂结构。

然而,这只是冰山一角。

我并不期望谁能在不查询Make documentation的情况下,能完全理解下面给出的例子(当然,我自己也不得不查看了一下这个文档。

或者可以查看Unix book中347到354页)。

点此下载

如果理解了最后这个例子,那么只需修改其中两行就可以用于任意工程了,无论添加了什么额外的文件!

说明:$<表示cpp文件,$@表示目标文件,所以修改上述代码4、6两行,分别改为你的工程中的源代码文件和生成目标,就可以使用了!。