基于RRAM型FPGA的编程结构

基于ARM和FPGA的嵌入式数控系统设计

现有的数控系统中多采用工控机加运动控制卡的计算机数控系统方案进行运动控制器的设计。

随着工控机整体功能日趋复杂,对运动控制系统的体积、成本、功耗等方面的要求越来越苛刻。

现有计算机数控系统在运动控制方面逐渐呈现出资源浪费严重、实时性差的劣势。

此外,数控系统的开放性、模块化和可重构设计是目前数控技术领域研究的热点,目的是为了适应技术发展和便于用户开发自己的功能。

本文基于ARM和FPGA的硬件平台,采用策略和机制相分离的设计思想,设计了一种具有高开放性特征的嵌入式数控系统。

该数控系统不仅具备了以往大型数控系统的主要功能,还具备了更好的操作性和切割性能,而且在开放性方面优势更为突出,使数控系统应用软件具有可移植性和互换性。

1 基于ARM和FPGA的嵌入式数控系统整体方案基于ARM和FPGA的嵌入式数控系统结构如图1所示。

按照模块划分的思想,本文将控制器分为人机交互、插补算法和通信三部分。

系统中ARM采用三星公司推出的16/32位RISC微处理器S3C2440A,它采用了ARM920T内核,核心频率高达400MHz。

FPGA采用Xilinx公司Spartan 3E系列的XC3S250E。

图1 基于ARM FPGA的嵌入式数控系统结构2 S3C2440A控制系统ARM作为数控系统的控制核心主要负责对从数据存储器中读取或直接从上位PC或网络获得的零件加工代码和控制信息进行译码、运算、逻辑处理,完成加工数据的粗插补以及人机界面和数据通信。

ARM系统是整个数控系统的控制核心,在嵌入式操作系统的管理下,采用分时处理的方式实现整个系统的信息处理和粗插补运算,通过键盘、触摸屏等输入装置输入各种控制指令,对数控系统的实时运行状态通过LCD、指示灯等显示,实现人机友好交互。

基于S3C2440A控制器有各种通信接口,包括RS232、RS485、以太网口、USB等接口模块。

通过这些接口实现文件传输和网络控制。

嵌入式数控的软件系统总体结构如图2所示。

基于ARM+FPGA的重构控制器设计.

基于ARM+FPGA的重构控制器设计基于ARM+FPGA的重构控制器设计可重构技术是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。

常规SRAM工艺的FPGA都可以实现重构,利用硬件复用原理,本文设计的可重构控制器采用ARM核微控制器作为主控制器,以FPGA芯片作为协处理器配合主控制器工作。

用户事先根据需求设计出不同的配置方案,并存储在重构控制器内部的存储器中,上电后,重构控制器就可以按需求将不同设计方案分时定位到目标可基于ARM+FPGA的重构控制器设计可重构技术是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。

常规SRAM工艺的FPGA都可以实现重构,利用硬件复用原理,本文设计的可重构控制器采用ARM核微控制器作为主控制器,以FPGA芯片作为协处理器配合主控制器工作。

用户事先根据需求设计出不同的配置方案,并存储在重构控制器内部的存储器中,上电后,重构控制器就可以按需求将不同设计方案分时定位到目标可编程器件内,同时保持其他部分电路功能正常,实现在系统灵活配置,提高系统工作效率。

1 SVF格式配置文件很多嵌入式系统中都用到了FPGA/CPLD等可编程器件,在这些系统中利用SVF 格式配置文件就可以方便地通过微控制器对可编程器件进行重新配置。

目前可编程芯片厂商的配套软件都可以生成可编程器件的SVF格式配置文件,串行矢量格式(SVF)是一种用于说明高层IEEE 1149.1(JTAG)总线操作的语法规范。

SVF由Texas Instruments开发,并已成为数据交换标准而被Teradyne,Tektronix等JTAG测试设备及软件制造商采用。

Xilinx的 FPGA以及配置PROM 可通过JTAG接口中TAP控制器接收SVF格式的编程指令。

由于SVF文件由ASCII语句构成,它要求较大的存储空间,并且存储效率很低,无法胜任嵌入式应用。

基于FPGA的SDRAM控制器的设计与实现

基于FPGA的SDRAM控制器的设计与实现引言:随着技术的发展,FPGA在数字电路设计领域得到了广泛的应用。

而SDRAM是一种常见的存储器设备,具有容量大、速度快等特点,被广泛应用于各种计算机系统中。

本文将介绍基于FPGA的SDRAM控制器的设计与实现。

设计目标:本次设计的目标是实现一个能够控制SDRAM读写操作的FPGA控制器。

通过该控制器,可以实现对SDRAM的读写操作,从而实现数据的存储与获取。

设计方案:本次设计采用Verilog语言进行RTL级的设计。

设计方案包括以下几个模块:初始化模块、控制模块、读写模块和时序控制模块。

1.初始化模块:初始化模块用于对SDRAM进行初始化配置,包括设置时钟频率、设置SDRAM的工作模式等。

在该模块中,需要配置SDRAM的控制寄存器,以便于后续的读写操作。

2.控制模块:控制模块用于接收外部的读写指令,并将其转化为SDRAM的控制信号。

该模块包括读写指令的解析、地址生成、数据缓存等功能。

通过该模块,可以实现对SDRAM的读写操作。

3.读写模块:读写模块用于控制SDRAM的读写操作。

读操作包括向SDRAM发送读指令、读地址和读请求信号,并接收SDRAM返回的读数据;写操作包括向SDRAM发送写指令、写地址和写数据,并接收SDRAM的写完成信号。

4.时序控制模块:时序控制模块用于控制SDRAM的时序,包括时钟信号的生成、读写时序的控制等。

通过该模块,可以确保SDRAM的读写操作按照正确的时序进行。

实现步骤:1.根据SDRAM的规格书,了解SDRAM的控制信号和时序要求。

2.设计并实现初始化模块,完成对SDRAM的初始化配置。

3.设计并实现控制模块,包括读写指令解析、地址生成、数据缓存等功能。

4.设计并实现读写模块,完成对SDRAM的读写操作。

5.设计并实现时序控制模块,确保SDRAM的读写操作按照正确的时序进行。

6.进行功能仿真,验证设计的正确性。

总结:通过本次设计与实现,我们成功实现了基于FPGA的SDRAM控制器。

RRAM及其在FPGA设计中的应用研究开题报告

RRAM及其在FPGA设计中的应用研究开题报告题目:RRAM及其在FPGA设计中的应用研究摘要:随着芯片技术的不断发展,各种新型存储器技术逐渐出现,其中基于阻变效应的抗褪色存储器(RRAM)具有极高的集成度、低功耗、高速度等优点,正逐渐成为替代闪存和DRAM的新兴存储器技术。

本文首先介绍了RRAM的基本原理及其优缺点,然后重点探讨了RRAM在FPGA设计中的应用,包括FPGA中各种存储器单元的设计和优化、逻辑单元的实现以及硬件加速等方面。

通过对比不同存储器单元的性能、功耗和面积等指标,支持基于RRAM的存储器单元设计。

关键词:RRAM;FPGA;存储器单元;逻辑设计;硬件加速1. 研究背景和意义FPGA作为一种可编程硬件平台,具有广泛的应用,其中存储器单元是FPGA设计中最常用的功能单元之一。

随着FPGA设计中存储器容量和速度等需求的不断提高,各种新型存储器技术也应运而生。

基于阻变效应的抗褪色存储器(RRAM)是一种新兴存储器技术,其具有读写速度快、能耗低、可重置等特点,在FPGA设计中应用前景广阔。

因此,对RRAM 技术及其在FPGA设计中的应用研究具有重要的意义。

2. 研究内容及方案(1)RRAM的基本原理及其优缺点本文将介绍RRAM的基本原理,包括其存储机制、写入与读出方式等方面,同时讨论其特点、优缺点以及与其他存储器技术的比较。

(2)RRAM在FPGA设计中的应用本文将着重探讨RRAM在FPGA设计中的应用,包括存储器单元、逻辑单元和硬件加速三个方面。

存储器单元的设计和优化:本文将介绍基于RRAM的存储器单元的设计,包括基本读写操作、数据保护与纠错等问题。

对比不同存储器单元的性能、功耗和面积等指标,并提出优化措施。

逻辑单元的实现:本文将介绍通过基于RRAM的逻辑单元的实现,提高FPGA的整体性能和可重构性。

主要包括基本逻辑单元(与、或、非等)和复杂逻辑单元(寄存器、计数器等)的设计。

硬件加速:本文将介绍如何利用RRAM实现硬件加速,如基于RRAM的加速器设计和自适应加速等。

阻变随机存储器(RRAM)综述(自己整理)汇总.

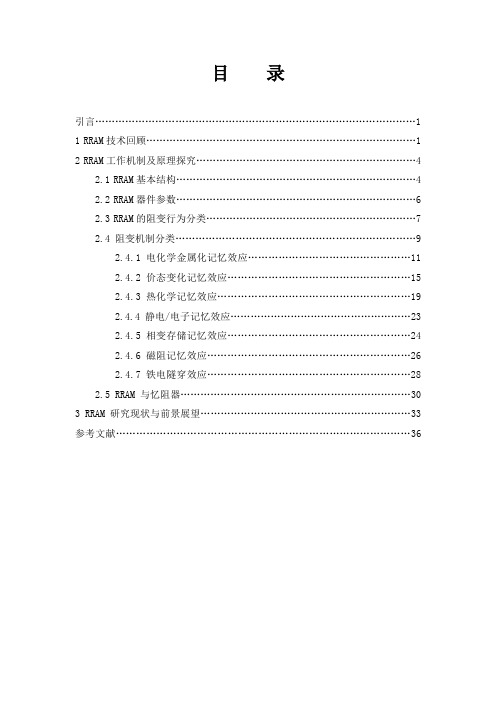

目录引言 (1)1 RRAM技术回顾 (1)2 RRAM工作机制及原理探究 (4)2.1 RRAM基本结构 (4)2.2 RRAM器件参数 (6)2.3 RRAM的阻变行为分类 (7)2.4 阻变机制分类 (9)2.4.1电化学金属化记忆效应 (11)2.4.2价态变化记忆效应 (15)2.4.3热化学记忆效应 (19)2.4.4静电/电子记忆效应 (23)2.4.5相变存储记忆效应 (24)2.4.6磁阻记忆效应 (26)2.4.7铁电隧穿效应 (28)2.5 RRAM与忆阻器 (30)3 RRAM研究现状与前景展望 (33)参考文献 (36)阻变随机存储器(RRAM)引言:阻变随机存储器(RRAM)是一种基于阻值变化来记录存储数据信息的非易失性存储器(NVM)器件。

近年来,NVM器件由于其高密度、高速度和低功耗的特点,在存储器的发展当中占据着越来越重要的地位。

硅基flash存储器作为传统的NVM器件,已被广泛投入到可移动存储器的应用当中。

但是,工作寿命、读写速度的不足,写操作中的高电压及尺寸无法继续缩小等瓶颈已经从多方面限制了flash存储器的进一步发展。

作为替代,多种新兴器件作为下一代NVM器件得到了业界广泛的关注[1、2],这其中包括铁电随机存储器(FeRAM)[3]、磁性随机存储器(MRAM)[4]、相变随机存储器(PRAM)[5]等。

然而,FeRAM及MRAM 在尺寸进一步缩小方面都存在着困难。

在这样的情况下,RRAM器件因其具有相当可观的微缩化前景,在近些年已引起了广泛的研发热潮。

本文将着眼于RRAM 的发展历史、工作原理、研究现状及应用前景入手,对RRAM进行广泛而概括性地介绍。

1 RRAM技术回顾虽然RRAM于近几年成为存储器技术研究的热点,但事实上对阻变现象的研究工作在很久之前便已开展起来。

1962年,T. W. Hickmott通过研究Al/SiO/Au、Al/Al2O3/Au、Ta/Ta2O5/Au、Zr/ZrO2/Au以及Ti/TiO2/Au等结构的电流电压特性曲线,首次展示了这种基于金属-介质层-金属(MIM)三明治结构在偏压变化时发生的阻变现象[6]。

零基础学FPGA (二十三) SDR SDRAM(架构篇)

零基础学FPGA (二十三)SDR SDRAM(架构篇)今日我们来讲的是SDRAM的架构以及设计,这也是小墨第一次接触架构,也谈不上给大家讲,就是把我理解的当做一个笔记共享给大家,有什么错误也请乐观指正,究竟我也是没有教师教,也是自己试探的,难免有些不合理的地方。

一、SDRAM 工作部分1、上电初始化我们先来看第一部分,上电初始化。

上电初始化我们知道,上电之后我们需要等待200us的稳定期,这段时光我们可以用一个定时器来计数,这没什么问题,然后进入的是预充电部分,这个时候,预充电的时候,sdram_cmd模块会检测此时的初始化状态机的状态,若处于预充电状态,那么sdram_cmd模块向SDRAM发指令,详细指令sdram的datasheet 里面有,发的是一个precharge,即预充电,发完指令之后,需要等待一段时光,来确保这个指令被SDRAM捕捉,这等待的时光,特权教师用的方式我觉得很好用一个宏定义,当计数器计数到相应的时光后,预充电完成参数置位即end_trp 置位,下面的使用也是一样,即当时始化状态机进入预充电状态i_pre时,计数器开启,开头计数,计数完成,也就是预充电结束的时候,计数器复位,这个复位的控制,可以用case语句来检测初始化状态机的状态,在相应的状态赋予相应的复位与置位接下来是8个自刷新,操作和预充电一样到了模式寄存器的配置阶段,我们需要选定L_bank,以及SDRAM工作模式的配置,当sdram_cmd模块检测到初始化状态机到达模式寄存器配置阶段时,我们的给SDRAM的sdram_bank端口赋相应的值,并且设置地址当时始化结束的时候,标记位init_done置位,告知工作状态机,初始化状态机已经结束,进入工作状态。

下面是我用word做的上电初始化的状态转移图2、自刷新初始化结束之后,SDRAM为了防止数据走失,要举行自刷新,上一篇文章已经讲过了,刷新2^12行需要64ms,也就是每15us刷新一行,也就是我们需要每15us发送一次自刷新哀求给SDRAM工作状态机,状态机一旦检测到自刷新哀求信号,就告知sdram工作模块,然后工作模块就向SDRAM发送自刷新指令,即CMD_A_PEF下面是自刷新的状态转移图3、读写状态初始化结束以后,SDRAM就处于工作状态,每15us举行一次自刷新,这个时候,假如想要读或写数据的话,即向工作状态机sdram_work_FSM 发送读写哀求,假如是读哀求,那么工作状态机进入行有效状态,也即激活状态w_active,此时,sdram_cmd模块会发送行有效指令,即CMD_ACTIVEA同时,我们需要将我们的12位行地址送给我们的sdram地址总线sdram_addr,然后便是一个等待时光段,TRCD,这个时光段里我们是不需要做什么工作的,只需等待TRCD结束TRCD结束的时候,工作状态机进入读状态,此时,我们需要发送列地址选中我们的存储单元,并告知sdram_cmd模块发送读指令,这个过程是读指令和列地址同时发送的。

基于ARM和FPGA的多通道信号模拟系统设计_麻军伟

设计与应用计算机测量与控制.2011.19(7) Com puter Measurement &C ontrol收稿日期:2010-12-03; 修回日期:2011-01-13。

基金项目:水下信息处理与控制国家级重点实验室基金(9140C2302061001);船舶预研基金(08J3.9.9)。

作者简介:麻军伟(1983-),男,陕西蒲城人,汉,硕士研究生,主要从事控制理论与控制工程方向的研究。

刘卫东(1962-),男,陕西西安人,博士,教授,主要从事计算机测控系统、水下航行器控制与导引系统、计算机网络多媒体方向的研究。

文章编号:1671-4598(2011)07-1767-04 中图分类号:T P302文献标识码:A基于ARM 和FPGA 的多通道信号模拟系统设计麻军伟1,刘卫东1,2,雷 娟1(11西北工业大学航海学院,陕西西安 710072;21水下信息处理与控制国家级重点实验室,陕西西安 710072)摘要:信号模拟系统在设备测试、数据处理等领域都有重要的意义;为了解决设备测试对多通道同步信号的需求,提出了一种基于ARM 和FPGA 的多通道信号模拟系统设计方法,主要介绍了以FPGA 为核心的模拟输出控制模块,其中采用ARM 进行多任务管理,用FPGA 实现时序转换和控制,FPGA 的控制逻辑采用VH DL 和原理图相结合的方法设计,使用FPGA 提高了系统性能并简化了外围电路设计,最后给出了模拟系统的实验结果,整个设计系统可模拟输出多路0101H z~40M H z 的任意信号,说明了这种设计方案的有效性。

关键词:信号模拟;多通道;FPGA;ARMDesign of Multi -channel Signal Simulator Based on ARM and FPGAMa Junw ei 1,Liu Weido ng1,2,Lei Juan1(11Co llege of M arine,No rthw ester n P olytechnica l U niver sity,Xi .an 710072,China;21N atio nal K ey L abo rato ry on U nderw ater Info rmatio n Pro cess and Contr ol,Xi .an 710072,China)Abstract:Signal Simulator is of gr eat importan ce for facility testing,signal proces sing and other field.In order to achieve the demand of m ulti-chann el s ynch ron ou s sign al for facility testing,a design m ethod of M ulti-chan nel Signal Sim ulator based on FPGA and ARM is pres -ented,and the con tr ol m odules of analog output implemented in FPGA are in tr odu ced in detail.ARM is mainly us ed for tasks managem ent and states supervision.FPGA is mainly used for timin g con version and control.C ontrol logic in the circuit design of FPGA combing VHDL w ith principle chart.T he use of FPGA improves the s ystem .s performan ce and s implifies design of the peripheral circuits.Experiment re -s ults demons trate that the n ew design approach for electrical sign al sim ulator is valid.Key words :s ignal s imulator;mu lti-channel;FPGA;ARM0 引言信号模拟系统主要用于对特定信号进行模拟仿真和外场采集数据回放,以进行设备测试或数据分析,在水声、雷达、导航、科研以及教学等领域有着广泛的应用。

毕业设计(论文)-基于fpga的sdram控制器的实现(软件部分)[管理资料]

![毕业设计(论文)-基于fpga的sdram控制器的实现(软件部分)[管理资料]](https://img.taocdn.com/s3/m/0426a5c767ec102de3bd8968.png)

毕业设计(论文)机械与电气工程学院电气工程及其自动化专业毕业设计(论文)题目基于FPGA的SDRAM控制器的实现(软件部分)学生姓名班级电气工程及其自动化学号指导教师完成日期2012 年 6 月 6 日基于FPGA的SDRAM控制器的实现(软件部分)The realization of SDRAM controller based on FPGA (software)总计毕业设计(论文) 41 页表格 6 个插图 21 幅摘要文中介绍了FPGA的开发流程、硬件开发语言及其开发环境QuartusII和SDRAM的结构特点和工作原理,根据SDRAM的工作原理、控制时序和指令特点,设计一种基于FPGA的SDRAM控制器的方案。

SDRAM控制器的设计主要由主控制模块、信号产生模块、数据路径模块和参数模块组成。

本设计解决SDRAM控制复杂、不方便的问题,并用Verilog给予仿真结果。

仿真结果表明使用该方法设计实现的控制器能够使系统方便,可靠的对SDRAM进行操作。

关键字:SDRAM控制器FPGA 控制模块软件仿真AbstractThis paper introduces the development process and FPGA hardware development language and the development environment of SDRAM QuartusII and structural characteristics and working principle, according to the working principle of SDRAM, sequence control and instruction characteristics, a scheme based on FPGA SDRAM controller is designed. SDRAM controller design mainly by the master control module, signal module, data path module and parameter module composition. This design solved a problem about the controlling complexity of SDRAM controller, and gives the simulation results by using Verilog. The simulation results show that using this method to design the controller can realize the system is convenient, reliable operation of SDRAM.Key words: SDRAM controller FPGA Control module Software simulation目录摘要 (I)Abstract (II)第一章绪论 (1)课题背景 (1)课题研究的意义 (1)第二章FPGA与Quartus II软件简介 (2)FPGA简介 (2)FPGA背景 (2)FGPA结构原理 (2)Quartus II软件简介 (3)硬件描述语言Verilog (4)FPGA开发过程 (5)第三章SDRAM的技术介绍 (6) (6)SDRAM简介 (6)SRAM和DRAM (6)SDRAM发展过程 (7)SDRAM工作原理和基本操作 (8)SDRAM存储的工作原理 (9)SDRAM 的引脚信号 (9)SDRAM基本命令 (10)SDRAM初始化 (10)SDRAM读、写操作 (11)终止操作 (12)第四章 SDRAM控制器设计 (12)SDRAM控制器 (13)主控制模块 (14)信号产生模块 (16)参数模块 (18)数据通路模块 (19)第五章SDRAM的读、写仿真 (19)SDRAM控制器时序仿真 (20)Quartus II (20)读仿真时序 (20)写仿真时序 (21)仿真结果分析 (22)结论 (24)参考文献 (25)致谢 (26)附录 (27)第一章绪论课题背景伴随着电子信息技术的飞速发展和其在通讯、工业、商业、医疗等方面的广泛应用,人们对信息的需求逐渐向着更快、更多、更准确发展。

基于FPGA的SDRAM控制器设计

基于FPGA的SDRAM控制器设计摘要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器设计方法,采用Verilog语言完成的控制器的设计,可以很方便地对SDRAM进行操作。

控制器在大容量数据记录仪扩展缓存得到了很好的应用。

关键字:FPGA;SDRAM;V erilog;1 引言在进行高速数据记录仪的开发中,由于硬盘固有的寻道延时,不能实现外部数据实时写入。

采用固态硬盘成本又比较高,所以在设计中考虑外加大容量数据缓存。

在各种随机存储器件中,SRAM的价格低,设计简单,但容量一般都不大;DDR速度快、容量大,但硬件和软件设计都比较复杂。

SDRAM具价格低、体积小、速度快、容量大的优点,是满足高速数据记录设计带宽的理想器件。

但是,与SRAM相比较,SDRAM的控制逻辑复杂,接口方式与普通的存储器差异很大。

为了解决这个矛盾,需要设计专用的SDRAM控制器,本文中提出了SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。

该设计采用了Altera公司的CycloneII系列EP2C35F484C8N作为主控芯片。

系统工作时钟为75M。

2 SDRAM工作原理简介本设计采用SDRAM芯片选用Winbond公司的W982516,4M×4BANKS×16BIT,两片并成32位数据总线,突发读写速度可达到300Mbytes/s。

W982516采用了54引脚的TSOP封装,工作电压为3.3V,并且采用同步接口方式(所有的信号都是时钟信号的上升沿触发),与系统时钟同步运行。

W982516行地址数目是13,列地址数目是9。

与各种SDRAM 一样,这种SDRAM具有以下几个特点:(1)采取行列地址复用原则,SDRAM的地址线在不同的命令下提供不同的地址,行列地址复用13根地址线。

(2)需要定时刷新。

(3)在进行读写时,需先激活行。

换页读写时要预充关闭的行,然后再激活新的行进行读写。

基于fpga的sdram课程设计

基于FPGA的SDRAM控制器课程设计一、引言随着嵌入式系统应用的不断扩展,高速大容量存储器的需求日益增长。

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存取存储器)作为一种高速动态存储器,广泛应用于各种高性能系统中。

为了实现高效的数据存储和读取,基于FPGA(Field Programmable Gate Array,现场可编程门阵列)的SDRAM控制器设计成为了研究的热点。

本课程设计将介绍基于FPGA的SDRAM控制器设计的相关知识,并探讨其实现方法。

二、SDRAM控制器设计原理SDRAM控制器的主要功能是实现SDRAM芯片与FPGA之间的通信。

它需要将FPGA发出的时序和控制信号转换为符合SDRAM规格的信号,以实现对SDRAM芯片的读写操作。

在设计SDRAM控制器时,需要考虑以下几个关键因素:1.SDRAM规格:不同的SDRAM芯片具有不同的规格,包括数据宽度、工作电压、刷新周期等。

在设计控制器时,需要了解目标SDRAM芯片的规格,以确保正确的通信。

2.时序控制:SDRAM通信涉及到复杂的时序控制,包括数据读写时序、刷新时序等。

控制器需要根据SDRAM规格生成正确的时序信号,以保证数据正确读写。

3.地址管理:SDRAM控制器需要管理SDRAM芯片的地址,包括行地址和列地址。

控制器需要生成正确的地址信号,并根据地址信号实现数据读写。

4.数据传输:控制器需要实现数据的正确传输,包括数据的读写操作和数据的格式化。

根据目标应用需求,可以选择合适的传输模式,如突发传输、页模式传输等。

三、基于FPGA的SDRAM控制器设计实现基于FPGA的SDRAM控制器设计可以通过硬件描述语言(如VHDL或Verilog)实现。

以下是一个简单的基于FPGA的SDRAM控制器设计的实现步骤:1.确定SDRAM规格:首先需要确定目标SDRAM芯片的规格,包括数据宽度、工作电压、刷新周期等。

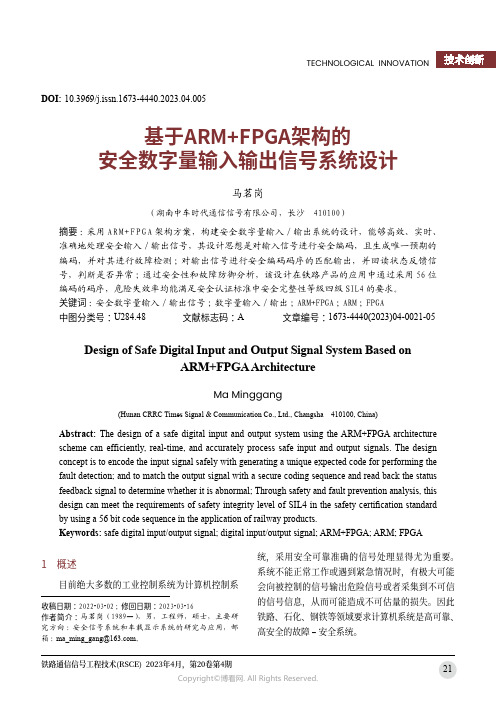

211133170_基于ARM+FPGA架构的安全数字量输入输出信号系统设计

基于ARM+FPGA架构的安全数字量输入输出信号系统设计马茗岗(湖南中车时代通信信号有限公司,长沙 410100)摘要:采用A R M +F P G A 架构方案,构建安全数字量输入/输出系统的设计,能够高效、实时、准确地处理安全输入/输出信号,其设计思想是对输入信号进行安全编码,且生成唯一预期的编码,并对其进行故障检测;对输出信号进行安全编码码序的匹配输出,并回读状态反馈信号,判断是否异常;通过安全性和故障防御分析,该设计在铁路产品的应用中通过采用56位编码的码序,危险失效率均能满足安全认证标准中安全完整性等级四级SIL4的要求。

关键词:安全数字量输入/输出信号;数字量输入/输出;ARM+FPGA ;ARM ;FPGA 中图分类号:U284.48 文献标志码:A 文章编号:1673-4440(2023)04-0021-05Design of Safe Digital Input and Output Signal System Based onARM+FPGA ArchitectureMa Minggang(Hunan CRRC Times Signal & Communication Co., Ltd., Changsha 410100, China)Abstract: The design of a safe digital input and output system using the ARM+FPGA architecture scheme can efficiently, real-time, and accurately process safe input and output signals. The design concept is to encode the input signal safely with generating a unique expected code for performing the fault detection; and to match the output signal with a secure coding sequence and read back the status feedback signal to determine whether it is abnormal; Through safety and fault prevention analysis, this design can meet the requirements of safety integrity level of SIL4 in the safety certification standard by using a 56 bit code sequence in the application of railway products.Keywords: safe digital input/output signal; digital input/output signal; ARM+FPGA; ARM; FPGADOI: 10.3969/j.issn.1673-4440.2023.04.005收稿日期:2022-03-02;修回日期:2023-03-16作者简介:马茗岗(1989—),男,工程师,硕士,主要研究方向:安全信号系统和车载显示系统的研究与应用,邮箱:********************。

RRAM及其在FPGA设计中的应用研究中期报告

RRAM及其在FPGA设计中的应用研究中期报告尊敬的评委老师们:我是某大学电子工程专业的硕士研究生XX,本篇报告是关于RRAM及其在FPGA设计中的应用研究的中期报告。

一、研究背景及意义RRAM(Resistive Random Access Memory)是一种新型的非挥发性存储器,与传统的DRAM和Flash以及基于硅的存储器技术相比,RRAM具有更低的功耗、更高的密度和更高的速度,且可以实现多层次存储和三维垂直结构,是未来存储器发展的趋势。

FPGA(Field-Programmable Gate Array)是一种灵活的可编程逻辑器件,可以用于各种不同的应用场合,同时也是各种数字电路和系统的重要组成部分。

但是,随着技术的不断发展,FPGA的功耗和密度等问题越来越引人关注,因此研究如何优化FPGA的设计和实现方式是非常必要和重要的。

二、研究内容及进展本研究的主要目标是探索RRAM在FPGA设计中的应用。

具体而言,我们的研究分为以下几个方面:1. 分析RRAM存储器的特性及其对FPGA设计的影响。

RRAM存储器由基本的阻变材料构成,它的读写速度和功耗等特性与已有存储器的差异较大,因此需要对此进行系统的分析和总结,并研究如何将其应用于FPGA设计中。

2. 设计基于RRAM的FPGA存储器模块。

本研究将设计一种基于RRAM的FPGA存储器模块,并结合现有存储器模块进行性能比较和优化分析。

3. 设计FPGA逻辑架构和电路结构优化算法。

本研究将针对FPGA的逻辑架构和电路结构进行研究,并开发相应的优化算法,以实现功耗和密度的优化。

4. 开展仿真和验证实验。

本研究将对所设计的FPGA存储器模块和优化算法进行仿真和验证实验,以验证其性能和可行性。

目前,我们已经完成了对RRAM存储器的分析和总结,初步设计了基于RRAM的FPGA存储器模块,并对FPGA逻辑架构和电路结构进行了探索研究。

下一步,我们将进一步优化设计,并开展仿真和验证实验。

一种基于SRAM型FPGA的配置芯片设计

一种基于SRAM型FPGA的配置芯片设计

庄雪亚;李蕾蕾

【期刊名称】《电子与封装》

【年(卷),期】2018(018)003

【摘要】随着设计工艺的飞速发展,SRAM型FPGA的规模也越做越大,对配置芯

片的存储容量、配置速度提出了更高的要求.基于SRAM型FPGA,采用BPI接口和大容量FLASH,并通过JTAG接口转BPI接口的软核,代替传统配置芯片内部的JTAG模块,完成了基于SRAM型FPGA的配置芯片设计,其结构简单、芯片面积小、存储容量大、速度快,兼容性好.通过数字仿真波形分析和FPGA原型验证,验证了设计方法的可行性和正确性.

【总页数】4页(P29-32)

【作者】庄雪亚;李蕾蕾

【作者单位】中国电子科技集团公司第五十八研究所,江苏无锡 214072;中国电子

科技集团公司第五十八研究所,江苏无锡 214072

【正文语种】中文

【中图分类】TN402

【相关文献】

1.一种用于FPGA的片上可配置SRAM设计 [J], 王文;曹靓;王栋

2.一种SRAM型FPGA互连资源的位流码配置方法 [J], 李智华;黄娟;李威;杨立群;黄俊英;杨海钢;

3.一种SRAM型FPGA互连资源的位流码配置方法 [J], 李智华;黄娟;李威;杨立群;黄俊英;杨海钢

4.基于SRAM并部分可重配置的FPGA设计ECU [J], Francisco Fons;Mariano Fons

5.基于SEM IP和部分重配置的SRAM型FPGA单粒子故障注入 [J], 王梦茹;周珊;薛盼盼;孔璐;王金波

因版权原因,仅展示原文概要,查看原文内容请购买。

工程师深谈ARM+FPGA的设计架构

工程师深谈ARM+FPGA的设计架构最近学习了ARM+FPGA的设计架构,ARM和FPGA结构的通信大致可以分为两种:一种是数据量小、通信速率要求不高的情况,可以考虑采用SPI、IIC等差UN星通信方式。

ARM都带有相关的SPI通信控制器等,在ARM端直接对相关的SPI通信控制器操作就可以了。

而FPGA这一端可作为SPI从,按照SPI协议的时序写好从设备接口,这个工作量没有多大,所以相对都比较容易。

另一种是数据量大、通信速率要求较高的情况,就要采用并行总线的方式了。

这时把FPGA当做ARM的一个片外的SRAM访问就可以,可以在FPGA内部生成一个双口RAM,输出的数据总线管腿直接连接到ARM的并行总线的数据总线上,双口RAM一端的地址总线也一样直接连接到ARM的并行总线中的地址总线。

这样就可以实现FPGA从DPRAM一端读写,ARM从DPRAM的另一端读写的功能了,当然还需要其他一些使能或片选的控制信号。

这里FPGA一侧较好实现,而ARM一侧需要开发SRAM(FPGA)驱动,这个还没有实际做过,所以没有把握。

NXP的ARM即LPC系列的并行总线称之为外扩地址与数据总线,由EMC(外部存储器控制器)控制,通过对EMC寄存器的控制就可以实现在外扩地址和数据总线上的数据收发。

若是采用LPC系列ARM加一片FPGA,实现他们通信的关键应该在于这个EMC寄存器的控制,不知道按照一定的顺序操作这个寄存器组写出来的数据收发程序是不是就可以称之为所谓的驱动,求大神解释。

TI 的ARM 或DSP 都有一个GPMC(通用内存控制器),它类似于LPC 的EMC,是TI 的芯片中用于与外部存储设备如NORFLASH、NANDFLASH、SRAM 等通信的一个借口。

对于这个同样也有上边的那个疑问。

三星的S5PV210 则是有一组并行总线接口,称之为SROM,同样也有一个SROM 控制器,支持外扩的NORFALSH、NANDFLASH、SRAM 等,应该也类似于LPC 系列的EMC。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A Study on the Programming Structures for RRAM-Based FPGA Architectures Xifan Tang,Student Member,IEEE,Gain Kim,Student Member,IEEE, Pierre-Emmanuel Gaillardon,Member,IEEE,and Giovanni De Micheli,Fellow,IEEEAbstract—Field Programmable Gate Arrays(FPGAs)can ben-efit non-volatility and high-performance by exploiting Resistive Random Access Memories(RRAMs).In RRAM-based FPGAs, the memories do not only replace the SRAMs and store config-urations,but they can also replace the transmission gates and propagate datapath signals.The high-performance achievable by RRAM-based FPGAs comes from the fact that the on-resistance of the memory devices R LRS is smaller than the equivalent re-sistance of a transmission gate.Efficient programming structures for RRAMs should provide high current density with a small area footprint,to obtain a low R LRS.In this paper,wefirst examine the efficiency of the widely-used2Transistor/1RRAM (2T1R)programming structure and identify four major limita-tions of the2T1R structure.To overcome these limitations,we pro-pose a2Transmission-Gates/1RRAM(2TG1R)and a4Transistor/ 1RRAM(4T1R)programming structures.We perform both the-oretical analysis and electrical simulations on the evaluated pro-gramming structures.4T1R programming structure is the best in terms of current density with1.4×and1.1×as compared to 2T1R and2TG1R counterparts,respectively.We also investigate the effect of boosting the programming voltage V prog of the programming structures.Experimental results show that boosting V prog for all the programming structures improves driving cur-rent of the evaluated programming structures by3×and area efficiency by1.7×on average.Index Terms—FPGA,programming structure,resistive memory.I.I NTRODUCTIONR ESISTIVE random access memory(RRAM)technology[1]–[3]is one of the most promising candidates for next generation non-volatile memory(NVM)technology[4]. From a circuit-level perspective,RRAMs can be regarded as programmable resistors.By applying suitable programming voltages and currents,RRAMs can be set/reset into two stable resistance states:the low-resistance state(LRS)and the high-resistance state(HRS).Compatible with CMOS fabrication techniques,RRAMs can be integrated between metal layersManuscript received August19,2015;revised December15,2015;accepted January4,2016.Date of publication March10,2016;date of current version April15,2016.This work was supported by the Swiss National Science Foun-dation under the project number200021-146600.This paper was recommended by Associate Editor M.Hashimoto.X.Tang,P.-E.Gaillardon,and G.De Micheli are with the Integrated Sys-tems Laboratory,School of Computer and Communication Sciences,École Polytechnique Fédérale de Lausanne(EPFL),Vaud,Switzerland(e-mail:xifan. tang@epfl.ch).G.Kim is with the Microelectronic System Laboratory,School of Electri-cal Engineering,École Polytechnique Fédérale de Lausanne(EPFL),Vaud, Switzerland.Color versions of one or more of thefigures in this paper are available online at .Digital Object Identifier10.1109/TCSI.2016.2528079over transistors during a back-end-of-line(BEoL)process, bringing opportunities to high-density co-integration.Device parameters of RRAMs,such as resistances and programming voltages,are dependent on the employed materials,the stack architecture and the fabrication techniques[3].The large range of achievable device properties enable RRAMs to meet the different application needs,such as dense memory arrays[5] or non-volatile FPGAs[6].RRAM technology has attracted intensive research interests in novel FPGA architectures[6]–[12].These proposed RRAM-based FPGA architectures employ RRAMs not only to store configurations,i.e.,replacing SRAMs,but also to propagate datapath signals,i.e.,replacing transmission gates.RRAMs reduce the transistor area thanks to BEoL process and lead to a higher density of integration.In addition,the low-resistance state R LRS of RRAMs introduces a equivalent resistance in datapaths lower than the transmission gates,improving the per-formance of routing elements.Programming structures allow individual access to the RRAMs and provide the voltage and current required during the resistance state switching.Efficient programming structures for RRAMs should employ a small area footprint while providing the high current density required to program a low R LRS.Previous works[6]–[11]use2Tran-sistor/1RRAM(2T1R)programming structure to program the RRAMs.The2T1R programming structure consists of two n-type transistors.However,the n-type transistors may suffer seri-ous body effects when propagating high programming voltages, weakening their current density.Therefore,it is necessary to precisely study the properties of a2T1R programming scheme. In this paper,wefirst examine the efficiency of2T1R pro-gramming structure and identify four major limitations:1)it provides a rather low current density due to imbalanced voltage drops across transistors;2)its bulk connections cause serious body effects;3)it requires driving inverters that introduce voltage drops and reduce the current density;4)the same tran-sistors are used for the different programming phases requiring worst case condition designs and resulting in area inefficien-cies.To avoid problems1)and2),we introduce transmission-gates(TGs)in2T1R structure,called2TG1R programming structure.To alleviate all the2T1R limitations,we propose a more advanced4T1R programming structure that uses two pairs of p-type and n-type transistors to set/reset RRAMs.We perform both theoretical analysis and electrical simulations on the introduced programming circuits.Simulation results show that4T1R programming structure is the best in terms of current density with1.4×and1.1×as compared to2T1R and 2TG1R counterparts,respectively.We investigate the effect of1549-8328©2016IEEE.Personal use is permitted,but republication/redistribution requires IEEE permission.See /publications_standards/publications/rights/index.html for more information.Fig.1.(a)RRAM structure and illustration on conductingfilaments;(b)bipolar RRAM I–V characterization.boosting programming voltage V prog on the three programming circuits.Experimental results show that boosting V prog for all the programming structures can improve driving current by3×and area efficiency by1.7×on average.The rest of this paper is organized as follows.Section II in-troduces background information about RRAM technology and RRAM-based FPGA architectures.Section III shows the exper-imental methodology used in the paper.Section IV analyzes in detail the2T1R programming structure,while Section V and Section VI introduce the2TG1R and4T1R programming structures,respectively.Section VIII concludes this paper.II.B ACKGROUND AND M OTIVATIONSIn this section,we give a brief introduction on RRAM technologies and RRAM-based FPGA architectures.A.Overview of RRAM TechnologyRRAM technologies have been heavily studied in recent years[1]–[3].RRAMs can be considered as two-terminal pro-grammable resistors,consisting of three layers:the top metal electrode,the switching metal oxide and the bottom metal elec-trode,as shown in Fig.1(a).The conductivity of the metal oxide can be modified by applying a programming voltage between the electrodes,leading to a switching event between two stable resistance states:the low resistance state(LRS)and the high resistance state(HRS).According to its switching mechanism, RRAMs can be classified into categories,unipolar resistive switching(URS)and bipolar resistive switching(BRS)[3]. In this paper,we only focus on BRS RRAMs whose I–V char-acteristics are illustrated in Fig.1(b).Before usage,RRAMs have to go through a forming process,during which the conduc-tivity of the switching metal oxide is initialized.After forming, applying a positive programming voltage V set induces a switch-ing event from HRS to LRS,called the set process.Conversely, a negative programming voltage V reset invokes a switching event from LRS to HRS,called the reset process.Note that there are threshold voltages for both V set and V reset.Switching events in metal oxide happen when the applied programming voltage is above the threshold voltage.However,a current compliance I set is often enforced during the set process to avoid a permanent breakdown of the device.Besides a threshold in programming voltage,conductivity switching in metal oxide also requires a minimum pulse width of programming voltage. The pulse width of programming voltage determines the writing speed of a RRAM device[3].The conductivity of the switching metal oxide is determined by conductingfilaments,which are formed during switching and whose widths depend on the programming current.The wider thefilament is,the higher the conductivity is and the lower the R LRS is.Therefore,a lower/higher resistance of RRAMs can be obtained by drivinga higher/lower the programming current during the set process[16].For example,the redfilament in Fig.1(a),which is achieved by the red set process in Fig.1(b),leads to a lower R LRS than the greenfilament in Fig.1(a),which is achieved by the green set process in Fig.1(b).The tunable R LRS is a unique property of RRAM devices.In addition,RRAMs should be able to afford a reason-ably large number of writing operations,expressed by the endurance,and also should be able to maintain the resistance state for a long period without degradation,expressed by the data retention.Back-End-Of-Line(BEoL)technology allows RRAM to be fabricated on the top of,or between,metal layers, with a effective memory cell area as low as4F2,where F is the feature size[17].The BEoL integration leads to a low additional cost in fabrication,and thefilament mechanism determines that RRAMs can be scaled down like transistors.B.RRAM-Based FPGA ArchitectureFig.2describes the principles of the FPGA architecture, where an array of heterogeneous blocks is surrounded by global routing architecture.Heterogeneous blocks consist of config-urable logic blocks(CLBs),memory banks and digital signal processor(DSP)blocks.The global routing architecture is built with connection blocks(CBs)highlighted in green,which con-nect heterogeneous blocks to routing tracks,and switch boxes (SBs)highlighted in red,which interconnect routing tracks to-gether.Inside a CLB,there is a number of basic logic elements (BLEs)each of which consists of a look up table(LUT),a Dflip-flop(FF),and an output selector(2:1multiplexer).A group of multiplexers called local routing architecture interconnect the CLB input/output pins to BLE input/output pins.Modern FPGAs[18],[19]exploits more complex CLB architectures with additional circuitry such as hard carry chains or shift registers,in order to boost the performances of the architecture. Modern FPGA architectures exploit a high density of logic and routing resources,leading to∼108programming bits[8].In RRAM-based FPGAs[6]–[11],the static random access memories(SRAMs),used to store the configurations,are re-placed with non-volatile SRAMs as shown in Fig.2(a).In addition to non-volatility,RRAMs can also bring performance improvements to multiplexers as shown in Fig.2(b).In the RRAM-based multiplexers,SRAMs and transmission gates are replaced by RRAMs and2Transistors/1RRAM(2T1R) programming structures.RRAMs are employed not only for storing routing configurations but also to route signals.When programmed into LRS,the RRAMs propagate signals within the datapaths,having the same functionality as transmissionTANG et al.:A STUDY ON THE PROGRAMMING STRUCTURES FOR RRAM-BASED FPGA ARCHITECTURES505Fig.2.RRAM-based FPGA architecture and circuit designs:(a)Non-volatile scan-chain SRAM;(b)RRAM-based multiplexer.gates in on state.In contrast,when programmed into HRS, the RRAMs block signals in datapaths,corresponding to the transmission gates in off pared to the transmission gates,the RRAMs can reduce the equivalent resistances of data-paths by up to75%,significantly improving the performance of multiplexers.When employed at nominal supply voltage,RRAM-based FPGAs can reduce the area by7%–15%,increase the per-formance by45%–58%,and reduce the power consumption by20%–58%,compared to SRAM-based FPGAs[6]–[10]. Additionally,compared to transmission gates,the resistance values of RRAMs do not degrade when the operating voltage Fig.3.System-level implementations exploiting the2T1R programming struc-ture:(a)scan chain[6];(b)memory bank[8].decreases[11].Furthermore,the use of proper programming transistor sizing technique can further reduce the area,de-lay of RRAM-based circuits[11].Operated in the near-V t regime,RRAM-based FPGAs can achieve20%area saving, 10%performance gain and65%power reduction,compared to mainstream SRAM-based FPGAs[11].C.Strategies for Individual RRAM AccessPrevious works[6]–[11]mainly exploit two different strate-gies to access the individual2T1R memory elements.A scan-chain organization,as shown in Fig.3(a),has been proposed in [6]while a memory bank arrangement,as shown in Fig.3(b), has been employed in[8].With the scan-chain organization that is similar to modern FPGAs,RRAMs are programmed through flip-flop(FF)outputs when signal prog is set to1.For example, when Q0=1,Q1=0,a set process for RRAM0is started. In a memory bank arrangement,the RRAMs are programmed through bit lines(BLs)and word lines(WLs).For instance, when WL[1]=1,WL[2]=1,BL[0]=1,BL[2]=0,a set process for RRAM is initiated.Note that,with this strategy, only one RRAM is programmed at a given time—allowing to limit the programming current to be delivered to the chips. Programming structures are of great importance for RRAM-based FPGAs,as they must provide high current to efficiently achieve low R LRS while minimizing the area footprint.Previ-ous works[6]–[11]propose that high current can be achieved by increasing the sizes of the transistors.Note that the principles in the circuit designs of programming structures are differ-ent from logic gates,because the programming structures are driving a resistive load instead of a capacitive one.To drive a resistive load like a RRAM,the source-to-drain voltages V DS of transistors should be large enough in order to ensure506IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I:REGULAR PAPERS,VOL.63,NO.4,APRIL2016 a high current.Moreover,when the V DS voltage drops ofthe transistors take most of the supply range V prog and thevoltage difference between the RRAM electrodes goes belowthe programming threshold voltage,a correct programmingcannot be guaranteed.To the best of our knowledge,previousliterature treated RRAMs as standard CMOS loads,i.e.,mostlycapacitive,in the2T1R structures[6]–[11]and the details of theassociated programming circuit design were not investigated.In this work,we study the specificities and limitations of2T1Rprogramming structures through both theoretical analysis andelectrical simulations,and propose solutions to the associatedshortcomings,such as low current density and area inefficiency.III.E XPERIMENTAL M ETHODOLOGYIn this paper,we consider the RRAM model in[13],whose V set/V reset is1.3V/−1.3V respectively,R LRS is500Ω,and R HRS is20kΩ(R HRS/R LRS=40).The current compliance I set is set to1mA to avoid permanent device breakdown while the reset current I reset is1mA.The minimum required pulse width for programming the RRAM element is100ns.The programming structures discussed in the paper are implemented with I/O transistors(W/L=320nm/270nm)from a commer-cial45nm process technology.The associated transistor model is based on BSIM4.The standard V GS and V DS of transistors are 2.5V.The transistors can be over-driven up to3.0V.The ratio between p/n-type transistorsβis set to3.In this paper,we also consider the area overhead of the P-well of p-type transistors for which a penalty factorγ=1.2is set.Electrical simulations are run with HSPICE simulator[21]. The time step of electrical simulations is set to0.1ps.In each simulation,the RRAM is initialized to the HRS and then transistors are turned on to program the RRAM into LRS.At the end of programming period,we measure the voltage difference between the RRAM electrodes and the current passing through to calculate the LRS resistance R LRS.We sweep two parameters:the width of transistors W prog and the programming voltage V prog,to study their impact on the performance of programming structures.W prog is defined as the width of the n-type transistors used in the structures expressed by the minimal size transistors.W prog is swept in the range from1to5with a0.1step.V prog is swept in the range from2.5V to3.0V with a0.1V step.Note that,to achieve significant FPGA improvements,a R HRS of at least20MΩmust be employed[23].However, as the presented methodology and structures are general for any device parameters and for the sake of reproducibility, we present results using the base parameters of the RRAM model in[13].IV.2T1R P ROGRAMMING S TRUCTUREIn this section,wefirst introduce the circuit design of the 2T1R programming structure and then discuss the limitations of the2T1R structure with theoretical analysis and electrical simulations.In the rest of the paper,we focus on the set process when conducting theoretical analysis.Without loss of general-ity,our approach can be applied to the reset process as well.Fig.4.A2T1R programming structure extracted from system-level implemen-tations in Fig.3.A.2T1R Circuit StructureIn Fig.4,we extract a2T1R structure along with its driving inverters from the system-level implementation shown in Fig.3. A2T1R structure requires driving inverters to provide the voltage levels of V progTE and V progBE during a programming phase.In a set process,the terminals of2T1R structure V progTE and V progBE are driven by a p-type transistor P1and a n-type transistor N3,respectively.As illustrated in Fig.4,the driving inverters introduce two potential voltage drops caused by the drain-to-source voltage V DS3and V DS4of transistors P1and N3,while the2T1R structure has two built-in voltage drops caused by V DS1and V DS2of transistors N1and N2.In a reset process,the terminals of2T1R structure V progTE and V progBE are driven by a n-type transistor N4and a p-type transistor P2, respectively.Similar,another two drain-to-source voltage drops of transistors P2and N4are introduced.To avoid the effect of V DS3and V DS4,the sizes of transistors P1and N3have to be far larger than N1and N2,so that V DS3and V DS4can be neglected compared to V DS1and V DS2.We take this assumption in the rest of the analysis.B.I–V Characteristics of2T1R StructureIn this part,we consider the voltage drops V DS1and V DS2in Fig.4and discuss the I–V characteristics of a2T1R structure. By considering Kirchhoff circuit laws⎧⎪⎨⎪⎩I ds=f(V GS1,V DS1)=f(V GS2,V DS2)V RRAM=I ds R RRAMV prog=V DS1+V DS2+V RRAM.(1)where I ds is the current passing through the transistors and RRAM.R RRAM denotes resistance of RRAM.f(V GS1,V DS1) and f(V GS2,V DS2)represent the I–V relationships of transis-tors N1and N2in Fig.4.To give an intuition on the operat-ing points of transistors,we consider the following transistor model:I ds=k n WL(V GS−V T)V DS−12V2DS,V DS<V GS−V T 12k n WL(V GS−V T)2,V DS≥V GS−V T(2)TANG et al.:A STUDY ON THE PROGRAMMING STRUCTURES FOR RRAM-BASED FPGA ARCHITECTURES507Fig.5.I–V characteristics of the2T1R structure.where k n denotes the process transconductance parameter ofa n-type transistor and V T represents its threshold voltage.W and L are the width and length of channel,respectively.V GS is the voltage difference between the gate and source terminals.V DS is the voltage difference between the drain andsource terminals.The intuitive results obtained with the modelwill be subsequently validated by SPICE simulations.In the theoretical analysis,we focus on studying how the currentI ds is changed with V GS1,V GS2,V DS1and V DS2during a set programming phase.Fig.5illustrates the I–V curve of the transistors N1and N2during the programming phase.A programming phase starts when the transistors N1and N2are turned on and the RRAMis in HRS.At the start point P,I ds is close to zero because theHRS resistance R HRS of the RRAM typically is very high,lead-ing to V DS1and V DS2approaching zero.V RRAM is above theprogramming threshold voltage V set,and therefore a resistive transition occurs and the resistance decreases.Note that V GS2equals to V G2because the source voltage of transistors N2isGND,while V GS1=V G1−V TE,is much smaller than V GS2. Then,the resistance of the RRAM is gradually decreasing fromR HRS to R LRS,leading to an increase in I ds.The growth inI ds creates a positive feedback:V DS1and V DS2are increasing to provide a higher current which leads the voltage difference across the RRAM to decrease.The positive feedback continues until the V RRAM reaches the V set of the RRAM,i.e.,the memory cannot switch anymore.At this point,I ds,V DS1and V DS2reach their peak values.Note that during the programming phase,V GS1is increasing as the source voltage of transistors N1,V TE,is decreasing,but it is still smaller than V GS2.The difference in V GS causes a V DS gap because V DS1has to be larger than V DS2in order to drive the same current.Therefore, transistor N1may work in deep linear region or even saturation region while transistor N2has to work in linear region,causing the programming current to be much lower than what saturated transistors can offer.Boosting V prog can reduce the difference between V DS1andV DS2,improving the driving strength of transistors.Its effortwill be studied by electrical simulations.C.Considerations About Bulk ConnectionsTypically,in digital circuit designs,the bulks of n-type transistors are connected to GND,as shown in Fig.6(a). However,the regular bulk connections for the2T1R structure causes serious body effects.In a set process where V progTE≈V prog and V progBE≈GND,the V SB=V S1of transistor N1Fig.6.(a)Asymmetric bulk management of the2T1R structure.(b)Symmetric bulk management of the2T1R structure.(c)Single well application of layout.(d)Triple well application of layout.in Fig.6(a)is larger than V set=V S1−V D2,which leads to a high threshold voltage of transistor N1and reduces its driving strength.Note that the V SB of transistor N2is negligible due to the V DS3and V DS4and its driving strength is reduced as well.Similar conclusion can be drawn in a reset process where V progTE≈GND and V progBE≈V prog.To alleviate the serious body effect,a symmetric bulk connection can be envisaged as shown in Fig.6(b).When V progTE≈V prog and V progBE≈GND,the V SB of transistor N1equals to V DS which is smaller than in the previous case and improves the driving strength.The V SB of transistor N2is strictly zero,totally eliminating the body effect.Similar conclu-sion can be drawn when V progTE≈GND and V progBE≈V prog. However,when a symmetric bulk is implemented with a single-well technology as shown in Fig.6(c),the substrate is connected to two voltage sources V progTE≈V prog and V progBE≈GND,resulting in a high leakage current I sub. Besides,the junction diode at the source of transistor N1is pos-itively biased,introducing another high leakage current I diode.I sub can be reduced to zero with a triple-well technology as shown in Fig.6(d),but I diode remains a concern.In short,there exist serious problems in connecting the bulks of2T1R struc-ture,limiting its feasibility from a physical design perspective.D.Area EstimationWe estimate the area of the programming structures in terms of minimal size transistors.While we only considered the set process,it is worth noticing that in the2T1R structure,the same transistors N1and N2are used in reset process as well. Typically,the reset current is not the same as the set current[3]. To be applicable in both set and reset,the size of transistors N1and N2should be determined by the largest of set/reset currents.Assume W prog,set and W prog,reset are the transistor sizes required for the set and reset operations,respectively.In the context of a memory bank,we assume that a driving inverter for a BL is shared by N2T1R structures2W prog,set+2·(1+βγ)W inv/N,I set≥I reset2W prog,reset+2·(1+βγ)W inv/N,I set<I reset(3)508IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I:REGULAR PAPERS,VOL.63,NO.4,APRIL2016Fig.7.Transient analysis on voltages and current in the2T1R structure during a set process(W prog=5,V prog=3.0V,W inv=20,1W prog=320nm). whereβis the ratio of p-type and n-type transistors andγis the penalty factor for the area overhead of the P-well of p-type transistors.W inv is the size of driving inverters.When the set current is larger than the reset current,the area is determined by W prog,set.When the reset current is larger than the set current, the area is determined by W prog,reset.In this case,during the set process,transistor N1and N2should be under-drived by reducing V G1,V G2and V prog to respect the current compliance. Unlike the W prog,set,a large W prog,reset does not contribute to a high R HRS.In others words,a large W prog,reset does not improve the performance as the W prog,set does.Therefore, when I set<I reset,the area consumed by a large W prog,reset is not directly contributing to a performance improvement.E.Electrical SimulationsFirst,we validate our theoretical intuitions by presenting the SPICE transient analysis of the2T1R structure.Then,we show the SPICE results of the V DS and programming current I ds of the2T1R structure.1)Transient Analysis:Fig.7illustrates current and voltage waveforms of the2T1R structure during a set process.After the transistors are turned on,a voltage difference V MAX between the RRAM electrodes is applied,initiating the set transition on the memory.The reduction on the resistance of the RRAM leads to an increase in I ds.To support the growing I ds,the V DS of transistors have to increase,leading to V TE is decreasing and V BE is increasing.The RRAM stays in programming phase until V TE−V BE reaches the threshold voltage V set.2)V DS of Transistors N1and N2:Fig.8(a)shows the trend of V DS in a2T1R structure by sweeping W prog and V prog,where W inv is20in order to keep V DS3and V DS4 negligible.The V DS difference reaches0.65V when V prog= 2.5V on average.Boosting V prog can reduce the V DS difference down to0.5V.A larger V prog can increase the V DS2by2.8×.Fig.8(b)depicts the trend of V DS in2T1R structure by sweeping W prog and W inv,where V prog is3.0V.Increasing W inv can effectively reduce the V DS gap by15%.3)Programming Current I ds:The achievable programming currents I ds are determined by V DS.A high V prog canincrease for the same W inv,we can improve3.4×I ds by boosting V prog from2.5V to3.0V on average.W inv is another important factor that influences the I ds.A large W inv can reduce V DS3 and V DS4while increase V DS1and V DS2.As shown in Fig.9(b), a large W inv,such as20,leads to a3.8×higher I ds than the smallest W inv=1on average.In short,boosting V prog is an efficient method in improving I ds,which avoids the use of large transistors.A large W inv(i.e.,=20)must be applied to avoid a serious degradation on I ds.TANG et al.:A STUDY ON THE PROGRAMMING STRUCTURES FOR RRAM-BASED FPGA ARCHITECTURES509Fig.9.(a)I ds in2T1R structure under diverse V prog(W inv=20);(b)I ds in 2T1R structure under diverse W inv(V prog=3.0V).(1W prog=320nm).F.Discussion About LimitationsFrom theoretical analysis and electrical simulations,we see four major limitations of2T1R structure:1)Its current density is low due to the intrinsic low V DS2;2)Its bulk connections lead to a high leakage current;3)Its current density is weakened by a small W inv;4)Its area is bounded by the maximum of W prog,set andW prog,reset,which is not efficient when I reset is large.5)It is not manufacturable due to the layout issues.Hence,in the rest of the paper,we only refer to it when compar-ing the current density.V.2TG1R P ROGRAMMING S TRUCTUREIn this section,we improve the previous2T1R circuit by replacing the n-type transistors and propose a2TG1R program-ming structure.The2TG1R circuit,comprising of four transis-tors,increases the current density significantly and overcomes the bulk management problem.The solution is validated using the electrical simulations.Fig.10.A2TG1R programming structure extracted from system-level imple-mentations in Fig.3.A.2TG1R Circuit StructureReplacing the n-type transistors in2T1R structure with trans-mission gates is a solution to the bulk management and driving strength.As shown in Fig.10,the bulks of the n-type and p-type transistors(in total4transistors)are connected respectively to the highest and lowest potentials,similarly to common digital design practice,removing the bulk leakage and body effects. The driving inverters are still required to provide the voltage levels of V progTE and V progBE during the programming phases. Whatever in a set or reset process,there always exist a p-type transistor and a n-type transistor whose V SB=0.Therefore, these two transistors whose V SB=0can provide higher current than2T1R structure.Although the other two transistors(weak p-type and weak n-type)suffer serious body effects,they still contribute to the currents.Hence,the total current offered by 2TG1R structure is higher than2T1R structure.B.Area EstimationWe consider the area of a2TG1R structure in the context of a memory bank as well.By considering the area of two p-type transistors,the area of a2TG1R structure is:2·(1+βγ)W prog,set+2·(1+βγ)W inv/N,I set≥I reset 2·(1+βγ)W prog,reset+2·(1+βγ)W inv/N,I set<I reset.(4) In summary,the area of2TG1R circuit is still bounded to the largest of W prog,set and W prog,reset.When I set<I reset,area investment on W prog,reset does not bring any improvement on performance.This is extremely inefficient when W prog,reset is large.A2TG1R circuit leads to a even larger area overhead than 2T1R structure due to the use of p-type transistors.C.Electrical SimulationsIn this section,we show the electrical simulation results of 2TG1R structure.We focus on the improvements on V DS andI ds of2TG1R structure,compared to the baseline2T1R element.1)Transient Analysis:Basically,the waveforms of the tran-sient analysis on a2TG1R are the same as2T1R structure.The only difference lies in the slope rate of V TE and V BE during the programming phase.In2TG1R,V TE decreases at the same rate。