基于FFT谱分析测频算法的FPGA实现

基于fpga的1 024点 fft算法的实现

基于fpga的1 024点 fft算法的实现下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!基于FPGA的1,024点FFT算法的实现一、简介傅立叶变换(FFT)是数字信号处理中常用的算法之一,它能够将时域信号转换为频域信号,实现信号频谱分析和滤波等功能。

快速傅里叶变换FFT的FPGA设计与实现--电科1704 郭衡

快速傅里叶变换FFT的FPGA设计与实现学生姓名郭衡班级电科1704学号17419002064指导教师谭会生成绩2020年5 月20 日快速傅里叶变换FFT 的设计与实现一、研究项目概述非周期性连续时间信号x(t)的傅里叶变换可以表示为:=)(ϖX dt tj et x ⎰∞∞--1)(ϖ,式中计算出来的是信号x(t)的连续频谱。

但是,在实际的控制系统中能够式中计算出来的是信号x(t)的连续频谱。

但是,在实际的控制系统中能够算信号x(t)的频谱。

有限长离散信号x(n),n=0,1,…,N-1的DFT 定义为:∑-=-=-==102,1.....10)()(N n Nj N knNeW N k W n x K X π、、。

可以看出,DFT 需要计算大约N2次乘法和N2次加法。

当N 较大时,这个计算量是很大的。

利用WN 的对称性和周期性,将N 点DFT 分解为两个N /2点的DFT ,这样两个N /2点DFT 总的计算量只是原来的一半,即(N /2)2+(N /2)2=N2/2,这样可以继续分解下去,将N /2再分解为N /4点DFT 等。

对于N=2m 点的DFT 都可以分解为2点的DFT ,这样其计算量可以减少为(N /2)log2N 次乘法和Nlog2N 次加法。

图1为FFT 与DFT-所需运算量与计算点数的关系曲线。

由图可以明显看出FFT 算法的优越性。

图1 FFT 与DFT 所需乘法次数比较X[1]将x(n)分解为偶数与奇数的两个序列之和,即x(n)=x1(n)+x2(n)。

x1(n)和x2(n)的长度都是N /2,x1(n)是偶数序列,x2(n)是奇数序列,则∑∑=--=-=+2)12(1202)1.....,0()(2)(1)(N n kn N N n km N N k W n x W n x K X所以)1...,0()(2)(1)(1222120-=+=∑∑-=-=N k W n x W W n x K X N n km N k N km N Nn由于kmN N jkm Njkm NW eeW2/2/2222===--ππ,则)1.....,0)((2)(1)(2)(1)(122/1202/-=+=+=∑∑-=-=N k k X W k X W n x W W n x K X kN N n km N k N Nn kn N其中X1(k)和X2(k)分别为x1(n)和x2(n)的N /2点DFT 。

FFT算法的一种FPGA实现

FFT算法的一种FPGA实现摘要:FFT运算在OFDM系统中起调制和解调的作用。

针对OFDM系统中FF T运算的要求,研究了一种易于FPGA实现的FFT处理器的硬件结构。

接收单元采用乒乓RAM结构,扩大了数据吞吐量。

中间数据缓存单元采用双口RAM,减少了访问RAM的时钟消耗。

计算单元采用基2算法,流水线结构,可在4个时钟后连续输出运算结果。

各个单元协调一致的并行工作,提高了系统时钟频率,达到了高速处理。

采用块浮点机制,动态扩大数据范围,在速度和精度之间得到折衷。

模块化设计,易于实现更多点数的FFT运算。

关键词:FFT;FPGA;蝶型运算;乒乓RAM结构1引言OFDM(正交频分复用)是一种多载波数字调制技术,被公认为是一种实现高速双向无线数据通信的良好方法。

在OFDM系统中,各子载波上数据的调制和解调是采用FFT(快速傅里叶变换)算法来实现的。

因此在OFDM系统中,FFT的实现方案是一个关键因素。

其运算精度和速度必须能够达到系统指标。

对于一个有512个子载波,子载波带宽20 kHz的OFDM系统中,要求在50 μs内完成512点的FFT运算。

硬件实现FFT算法的主要方案有:DSP(通用数字信号处理器);FFT专用芯片;FPGA(现场可编程门阵列)。

DSP具有纯软件实现的灵活性,适合用于流程复杂的算法,例如在通信系统中的信道编、解码,QAM映射等算法。

如果在DSP中完成FFT运算,不仅要占用大量D SP的运算时间,使整个系统的数据吞吐率降低,也无法发挥DSP软件实现的灵活性。

因此,前端的FFT运算应由ASIC或FPGA完成。

采用专用的FFT处理芯片,虽然速度能达到要求,但其可扩展性差。

FPGA具有硬件结构可重构的特点。

适合于算法结构固定、运算量大的前端数字信号处理。

新近推出的FPGA产品都采用多层布线结构,更低的核心电压,更丰富的IO管脚,容量可达到100 k个逻辑单元(LES),内置嵌入式RAM资源,内部集成多个数字锁相环,多个嵌入的硬件乘法器,所有这一切都使得FPGA在数字信号处理领域显示出自己特有的优势。

fft傅里叶变换的qpsk基带信号频偏估计和补偿算法fpga实现

fft傅里叶变换的qpsk基带信号频偏估计和补偿算法fpga实现FFT(快速傅里叶变换)是一种常用的信号处理算法,可以将时域信号转换为频域信号。

在通信系统中,频偏是指信号的实际频率与理论频率之间的差异。

频偏会导致接收到的信号与发送信号不匹配,从而影响系统的性能。

因此,频偏的估计和补偿是通信系统中的重要问题之一。

QPSK(四相移键控)是一种常用的调制方式,它将两个比特映射到一个符号上。

在QPSK调制中,每个符号代表两个比特,因此可以提高频谱效率。

然而,由于信号传输过程中的各种因素,如多径效应、多普勒效应等,会导致信号的频偏。

为了解决QPSK基带信号频偏的问题,可以使用FFT算法进行频偏估计和补偿。

首先,将接收到的信号进行FFT变换,得到信号的频谱。

然后,通过分析频谱的特征,可以估计信号的频偏。

最后,根据估计的频偏值,对接收到的信号进行补偿,使其恢复到理论频率。

在FPGA(现场可编程门阵列)实现FFT傅里叶变换的QPSK基带信号频偏估计和补偿算法时,需要设计相应的硬件电路。

首先,需要将接收到的信号进行采样,并存储到FPGA的存储器中。

然后,通过使用FFT算法,对存储的信号进行频谱分析。

接下来,根据频谱的特征,计算信号的频偏值。

最后,使用频偏值对信号进行补偿,并输出补偿后的信号。

在FPGA实现中,需要考虑硬件资源的限制和性能要求。

为了提高计算速度,可以使用并行计算的方法,将FFT算法分解为多个子模块,并行计算每个子模块的结果。

此外,还可以使用流水线技术,将计算过程划分为多个阶段,以提高计算效率。

总之,FFT傅里叶变换的QPSK基带信号频偏估计和补偿算法在通信系统中具有重要的应用价值。

通过使用FPGA实现,可以提高计算速度和性能,满足实时信号处理的需求。

未来,随着通信技术的不断发展,这种算法和实现方法将会得到更广泛的应用。

基于FPGA的FFT算法硬件实现

基于FPGA的FFT算法硬件实现引言:FFT是一种用于将时域信号转换为频域信号的算法,常用于信号处理和图像处理领域。

由于FFT的高计算复杂度,硬件实现可以提供更高的计算效率和并行处理能力。

本文将介绍基于FPGA的FFT算法硬件实现,并详细解释算法的原理和实现过程。

一、快速傅里叶变换(FFT)算法简介快速傅里叶变换(FFT)是一种将一个N点离散序列转换为频域离散序列的算法。

它的时间复杂度为O(NlogN),相比于传统的傅里叶变换算法的时间复杂度O(N^2),FFT算法具有更高的计算效率。

FFT算法的核心思想是将一个N点离散序列划分为其各个子序列,然后再分别计算各个子序列的傅里叶变换,并将结果通过一系列的蝶形运算合并得到最终的频域信号。

二、FFT算法的硬件实现原理基于FPGA的FFT算法实现可以充分发挥FPGA的并行计算能力和灵活性。

硬件实现的核心是设计一个包含多个计算单元的并行处理模块。

常见的FFT硬件实现架构包括基于蝶形运算的位递归FFT算法和基于矩阵运算的线性变换FFT算法。

1.基于蝶形运算的位递归FFT算法实现首先将输入序列分为奇数位和偶数位两个子序列,然后分别对这两个子序列进行FFT计算。

然后将得到的结果通过蝶形运算合并得到最终的频域信号。

在硬件实现中,可以设计一个包含多个蝶形运算单元的并行计算模块。

每个蝶形运算单元包括两个输入通道和两个输出通道,通过并行计算可以同时进行多个蝶形运算操作,提高计算效率。

2.基于矩阵运算的线性变换FFT算法实现线性变换FFT算法将FFT计算表示为矩阵运算的形式,可以充分利用FPGA的向量计算能力。

这种实现方法将输入序列表示为一个复数矢量,然后通过矩阵运算得到最终的频域信号。

在硬件实现中,可以设计一个包含多个矩阵运算单元的并行计算模块。

每个矩阵运算单元可以同时对多个输入进行矩阵运算,提高计算效率。

三、基于FPGA的FFT算法硬件实现步骤1.硬件资源规划:根据需要计算的样本点数N,确定所需的FPGA资源,包括DSP片上资源、BRAM资源和IO资源等。

用FPGA实现FFT的方法

用FPGA实现FFT的方法使用FPGA(Field-Programmable Gate Array)实现FFT(Fast Fourier Transform)可以提供高性能的信号处理能力。

FFT是一种将时域信号转换为频域信号的算法,广泛应用于数字信号处理、通信系统、图像处理等领域。

下面将介绍一种常见的方法来使用FPGA实现FFT。

首先,需要了解FFT算法的基本原理。

FFT将长度为N的离散时间信号x(n)转换为N个频谱分量X(k),其中k=0,1,...,N-1、FFT算法的核心是蝶形运算,通过将信号分解成不同的频率分量并逐步组合来实现。

下面是使用FPGA实现FFT的具体步骤:1.设计数据缓存器:在FPGA内部设计一个数据缓存器用于存储输入信号x(n)和输出信号X(k)。

缓存器的宽度和深度取决于输入信号的采样位数和FFT的长度。

2. 数据采集与预处理:使用FPGA的输入模块采集外部信号,并通过FIFO(First In First Out)缓冲区将数据传输到数据缓存器中。

为了提高计算速度,可以使用预处理方法如窗函数、数据重排等来优化输入信号的质量。

3.蝶形运算模块设计:FFT算法的核心是蝶形运算。

在FPGA中,设计一个蝶形运算模块用于计算FFT算法中的每一个蝶形运算,即通过求解两个复数的乘积,并进行加法运算得到结果。

该模块需要实现乘法器和加法器,并对数据进行并行计算。

4.快速蝶形运算网络构建:将蝶形运算模块按照FFT算法中的乘积因子进行连接,并根据FFT的长度设计合适的网络结构。

可以使用串行-并行方式或并行-串行方式来实现FFT算法。

需要注意的是,为了减少延迟,可以采用流水线技术来提高运算速度。

5.数据输出与后处理:设计一个输出模块将计算得到的频域信号X(k)输出到外部。

可以通过FPGA的输出模块将数据传输到外部存储器、显示器或其他设备进行后续处理。

6. 时钟和时序设计:在FPGA中需要设计合适的时钟频率和时序来保证FFT算法的准确性和稳定性。

fpga 快速傅里叶变换实现卷积

标题:FPGA实现快速傅里叶变换加速卷积的原理与应用在当今信息时代,数字信号处理和数据处理已经成为许多领域中不可或缺的部分。

而在处理这些信号和数据时,快速傅里叶变换(FFT)和卷积运算是常用的数学工具。

在很多实际应用中,由于其高复杂度,这两个运算往往需要花费大量的时间和资源。

然而,通过利用现代的FPGA技术,我们可以实现这些运算的高效加速,本文将探讨如何利用FPGA来加速实现快速傅里叶变换卷积。

1. 背景介绍快速傅里叶变换(FFT)是一种离散傅里叶变换(DFT)的快速算法。

它不仅可以用于频域分析和信号处理,还被广泛应用于图像处理、通信、雷达和生物医学领域等。

而卷积运算则是数字信号处理和图像处理中常见的运算之一,用于实现信号的滤波、特征提取和模式识别等。

然而,这两种运算都具有较高的计算复杂度,特别是在涉及大规模数据时,传统的处理方法往往效率低下。

2. FPGA加速计算的优势FPGA(Field-Programmable Gate Array)是一种灵活可编程的数字集成电路,它通过可编程的逻辑单元和可编程的连接网络,可以实现大规模的并行计算和高速数据处理。

这使得FPGA在加速计算领域具有独特的优势。

与传统的CPU和GPU相比,FPGA可以根据具体的应用需求进行快速定制和优化,提供更高的计算密度和更低的功耗。

利用FPGA来加速实现FFT和卷积运算,可以大幅提高运算速度和效率。

3. FPGA实现快速傅里叶变换在实现FFT时,FPGA可以充分利用其并行计算的特性,通过设计合适的硬件结构和算法,实现FFT运算的高效加速。

可以采用基于蝶形运算单元(Butterfly)的并行计算结构,利用FPGA的片上资源进行数据流控制和计算单元的并行化。

通过巧妙的数据流设计和数据重用策略,还可以有效地减少时序延迟和资源消耗,进一步提高FFT算法的运行速度。

在实际应用中,基于FPGA的FFT加速器已经被广泛应用于通信系统、无线电频谱监测和图像处理等领域。

FFT的FPGA实现

fft的fpga实现1.引言DFT及其快速算法FFT是信号处理领域的核心组成部分。

FFT算法多种多样,按数据组合方式不同一般分时域和频域,按数据抽取方式的不同又可分为基2,基4等。

各算法的优缺点视不同的制约因素而不同。

FFT的实现方法也多种多样,可以用软件实现,也可以用硬件实现,用软件在PC机或工作站上实现则计算速度很慢。

一般多结合具体系统用硬件实现。

例如用单片机或DSP实现。

但是速度仍然很慢,难以与快速的A/D器件匹配。

在雷达信号处理领域主要追求的目标是速度,即实时性的要求非常高。

针对这种快速信号处理的要求及FPGA器件的特点,本文采用的是一种基2固定几何结构的FFT算法。

采用的是Altera公司推出的最新器件Stratix来做硬件仿真。

Stratix器件是一款采用高性能结构体系的PLD器件。

它结合了强大内核性能,大存储带宽,数字信号处理(DSP)功能,高速I/O性能和模块化设计与一体的PLD。

其内嵌的DSP模块具有很高的乘法运算速度。

在用VHDL编程时可以用MegaWizard的方法指定用DSP模块生成乘法器,用这种乘法器来做蝶形,用多个蝶形来构成FFT运算级,通过循环即可实现FFT核心运算的并行化。

用Altera公司的Quartus软件做逻辑分析和波形分析。

Quartus软件具有很强的硬件仿真和逻辑分析功能,它可将用VHDL编写的硬件描述综合到FPGA中。

2.算法介绍为了说明问题的方便,下面以基2,八点FFT为例加以说明。

传统的基2变几何结构算法如下(图一):箭头上的数字代表旋转因子中的k。

图中输入采用的是按码位颠倒的顺序排放的。

输出是自然顺序。

这种结构的特点是每个蝶形的输出数据仍然放在原来的输入的数据存储单元内,这样只需要2N个存储单元(FFT中的数据是复数形式,每点需要两个单元存储)。

其缺点是不同级的同一位置蝶形的输入数据的寻址不固定,难以实现循环控制。

用FPGA编程时难以并行实现,数据处理速度慢。

LTE物理上行共享信道中FFT算法分析与FPGA实现

Abs r t F s t ac : a tFoure a f m i he o e t c ir Tr nsor s t c r e hni SP,a d ispe f m i i e ss que ofD n t ror ng tm i hore fw sa e t ra e tg s t n D F ,nd i he T E s se FT a m p t n pp iai nsF ed Pr r m m a e G ae Ar a s a e , y ha Tsa n t L y t m F h si ora ta lc to .i l og a bl t ry i n vr pe t ofpr  ̄ a m a l e i e a gh s e e e o o m be d v c thi pe d d v l pm e ti e e ty a s n n r c n e r.Thi p rsu e h m p e e tto T spa e t dist e i l m n ai n ofFF

町以满足 一般实时信号处理的要求。

关 键 字 :L E;非 基2 ei gH ;Go d T o s F T ;vro DL l o — h ma F T;F G P A实现 ;

中 图分 类 号 :T 2 . N9 95 文 献标 识 码 :A

Al r t go ihm nayssofFFT n PU SCH nd FPG A a l i i a

ma lm e ai n a d ts yse . pe ntto n etoft s t m Thi sg d pt heag rt he sdei n a o st l o ihm ofGoo d—Th om a, nd raie a a l oi s s a e l sav r b ep nt z i FF s t m sngV eiogH D L.The tfn s ssm u ai s t ssa rfc to ft yse o itx4 The T yse by u i r l n i i ihe i lton, he i ndve i ai n o hes t m n V re . yn i sm u ai ndc tst a he r s l ac lton c n r a h e ui lntp e ii a he o rton s e fFF c n i lton i iae h tt e utofc lu ai a e c q vae r cson nd t pe ai pe d o T a stsyt e uetofc m o y ra—tl i a r esng aif her q s om nl e l inesg lp oc si . n Ke ywor : dsLTE: N on—rdi a x一2; veiogH D L; Goo rl d—Th om a FT ; F sF PG A m plm e tton; i e n ai

FPGA课程设计128点FFT变换的FPGA实现

Busy: 在Start生效之后,FFT运算器将其拉高。表明开始一帧数据的输入,运算与输出。此时不能将Start再次拉高,只有Busy恢复低电平时,才能将Start拉高进行下一帧。

2

2.1 OFDM 的基本原理

正交频分复用(OFDM)技术与已经普遍应用的频分复用技术十分相似。与普通的频分复用基本原理相同,OFDM 把高速的数据流通过串并变换分配到速率相对较低的若干个频率子信道中进行传输,不同的是,OFDM 技术更好地利用了控制方法,使频谱利用率有所提高。

2.1.1 OFDM 的产生和发展

1.1.1 无线通信的发展和现状

现代无线通信技术的发展始于本世纪 20 年代,经历了早期专用移动通信系统的发展,公用移动通信业务的发展,到 1978 年底,美国贝尔试验室研制成功先进移动电话系统(AMPS),建成了蜂窝状移动通信网,大大提高了系统容量。随后投入商用,服务区域在美国逐渐扩大。其它工业化国家也相继开发出蜂窝式公用移动通信网,这种模拟通信系统被称为第一代移动通信系统。

(3-13)

(3-14)

这样一个N点的DFT就被拆分成为了两个N/2点的DFT。式(3-7)和式(3-8)说明了原N点的DFT和这两个N/2点的DFT之间的关系。

采用蝶形运算符号的这种图示方法,可以用图3-1来表示前面所讲到的运算。在图3.2中,N= =8,式(3-13)给出了X(0)~X(3)的计算方法,而式(2-14)给出了X(4)~X(7)的计算方法。

, (3-5)

, (3-6)

那么x(n)的DFT为

(3-7)

由于

(3-8)

基4FFT算法的FPGA实现

基4FFT算法的FPGA实现基4FFT算法是一种优化的快速傅里叶变换(Fast Fourier Transform, FFT)算法,它能有效地将长度为4的离散序列转换为其频域表示。

在FPGA上实现基4FFT算法可以提高傅里叶变换的计算速度和效率,适用于音频处理、无线通信、图像处理等领域。

FPGA(Field Programmable Gate Array)是一种可编程逻辑设备,其灵活性和高度并行的特性使其成为FFT算法的理想硬件实现平台。

下面将从优化策略、架构设计和性能分析三个方面来讨论FPGA上基4FFT算法的实现。

一、优化策略基于FPGA的FFT算法实现的优化策略包括算法优化和硬件优化两个方面。

1.算法优化:基4FFT算法的关键特性是将长度为4的序列分解为两个长度为2的序列,再进行运算。

通过在算法级别上进行优化,可以减小计算量和存储量。

例如,采用切比雪夫多项式代替蝶形运算,减少乘法操作。

此外,使用采样点的对称性和周期性,可以进一步简化计算过程。

2.硬件优化:在FPGA的架构设计方面,可以采用流水线化和并行计算的方法来提高计算效率。

流水线化可以将计算过程划分为多个阶段,实现多个计算阶段的并行化,从而提高吞吐量。

并行计算可以通过使用多个处理单元来同时执行多个计算操作,进一步增加计算能力。

二、架构设计基于FPGA的基4FFT算法实现的架构设计主要包括数据存储和运算单元的设计。

1. 数据存储:基于FPGA的FFT算法实现中,需要使用存储单元来存储输入序列和中间结果。

常用的存储单元包括FIFO(First-in-First-out)队列和RAM(Random Access Memory)。

存储单元的设计需要考虑读写速度和存储容量。

2.运算单元:基于FPGA的FFT算法实现中,需要设计运算单元来进行乘法和加法运算。

运算单元的设计需要考虑乘法器的使用,乘法操作是FFT计算的关键部分,可以采用片上乘法器和并行乘法器来提高计算速度。

基于FFT的校频技术及其FPGA实现

为零均值 、 复高斯 白噪声 , 其中 ( )和 ( )为相互 凡 凡 独立的实高斯随机变量, 方差均为 c / (r为 ( ) r 2c 2 2 凡 的

方 差 ) 。

频率的最大似然估计为… :

Ⅳ 一1

= rmx∑xn 巾 a , ( e 2 g aI )

=

( 2 )

匹配滤 波后 提取 的第 个复样 点 可 以表示为 : r = ̄ dep j2 f + ) / x [(wAn 0 ]+ P () 5

I ≤

( ) =A 儿 妒 ( ) 凡 e + 凡 n=0 l … ,r , , ^ —l () 1

有 J >J 『 『 v v

,

其算杂为 l ' 乘 运复度 等g 次 。 0 复 2 N

为了降低频率估计运算 的复杂度 , 研究人员提 出 了其他一些次最佳的方法 , 如基 于 自相 和基 于相 位展开 的方法 等 。 。

叶淦华 张邦 宁 , , 陆锐敏

( .总参第6 1 3研究所 , 江苏省南京市 200 ; .解放军理工大学通信工程学院, 10 7 2 江苏省南京市 200 ) 107 摘 要: 在全数 字化 M S ( P K 多相移键控 ) 解调 中, 有时存在着相 当大的相对载波频偏 , 导致接收机

・

通信技术 ・

电 子 工 蠢 野

20 0 7年 2月

2rM 操 作 , 以得 到 :  ̄ / 可

c td+o o( so  ̄ o

) 皇 : 【赫 。 l :I 审! ’ 。

图 1 MP K 载 波 恢 复 结构 S

=

2f. "n+ t T r A

( d' ( m " 9 o2 ) 1 )

2 MP K 调制信号载波恢复算法 s

快速傅里叶变换FFT的FPGA设计与实现--电科1704 郭衡

快速傅里叶变换FFT的FPGA设计与实现学生姓名郭衡班级电科1704学号17419002064指导教师谭会生成绩2020年5 月20 日快速傅里叶变换FFT 的设计与实现一、研究项目概述非周期性连续时间信号x(t)的傅里叶变换可以表示为:=)(ϖX dt tj et x ⎰∞∞--1)(ϖ,式中计算出来的是信号x(t)的连续频谱。

但是,在实际的控制系统中能够式中计算出来的是信号x(t)的连续频谱。

但是,在实际的控制系统中能够算信号x(t)的频谱。

有限长离散信号x(n),n=0,1,…,N-1的DFT 定义为:∑-=-=-==102,1.....10)()(N n Nj N knNeW N k W n x K X π、、。

可以看出,DFT 需要计算大约N2次乘法和N2次加法。

当N 较大时,这个计算量是很大的。

利用WN 的对称性和周期性,将N 点DFT 分解为两个N /2点的DFT ,这样两个N /2点DFT 总的计算量只是原来的一半,即(N /2)2+(N /2)2=N2/2,这样可以继续分解下去,将N /2再分解为N /4点DFT 等。

对于N=2m 点的DFT 都可以分解为2点的DFT ,这样其计算量可以减少为(N /2)log2N 次乘法和Nlog2N 次加法。

图1为FFT 与DFT-所需运算量与计算点数的关系曲线。

由图可以明显看出FFT 算法的优越性。

图1 FFT 与DFT 所需乘法次数比较将x(n)分解为偶数与奇数的两个序列之和,即x(n)=x1(n)+x2(n)。

x1(n)和x2(n)的长度都是N /2,x1(n)是偶数序列,x2(n)是奇数序列,则∑∑=--=-=+2)12(1202)1.....,0()(2)(1)(N n kn N N n km N N k W n x W n x K X所以)1...,0()(2)(1)(1222120-=+=∑∑-=-=N k W n x W W n x K X N n km N k N km N Nn由于kmN N jkm Njkm NW eeW2/2/2222===--ππ,则)1.....,0)((2)(1)(2)(1)(122/1202/-=+=+=∑∑-=-=N k k X W k X W n x W W n x K X kN N n km N k N Nn kn N其中X1(k)和X2(k)分别为x1(n)和x2(n)的N /2点DFT 。

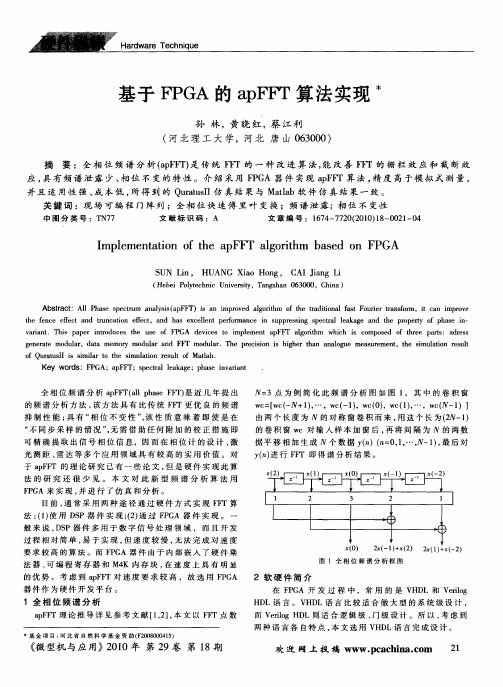

基于FPGA的apFFT算法实现

I lme tto ft e a F T ag rt m a e n F mpe n ain o h p F loi h b s d o ito u e te s o P d vc s o mp e n a F T ag r h a a t hs i p p r n r d c s h u e f F GA e ie t i lme t p b lo i m w ih s o o e o h e a :a r s t h c i c mp s d f tr e p  ̄s d e s g n r t d lr aa me r d l n Fr mo u a .T e r c s n i i h r t a n l g e me s r me t h i lt n rs l e e ae mo u a ,d t moy mo u a a d F T d l r h p e ii s h g e h n a ao u a u e n ,t e smu ai e u t r o o

S i UN Ln, HUANG a n Xio Ho g, CAIJa g L in i

( b iP ltc nc He e oye h i Unv ri iest y,T n sa 6 0 0,C ia) aghn 0 3 0 hn

A src : l P ae set m a a s (p FP sa mpoe lo tm o et dtn atF u e rnfr tcn ipoe b t t Al h s p c u n l i aF l n i rvd agrh ft r io a fs o r rt s m,i a m rv a r ys )i i h a il i a o

基于FPGA的FFT信号处理器的设计与实现的开题报告

基于FPGA的FFT信号处理器的设计与实现的开题报告一、研究背景与意义傅里叶变换(FFT)是一种非常重要的信号处理算法,在数字信号处理、通信系统、雷达系统等领域广泛应用。

FFT的计算过程需要大量的运算,实时性和精度是实现FFT的核心问题。

目前,计算FFT的方式种类繁多,常用的有软件算法、ASIC芯片和FPGA等硬件实现。

其中,基于FPGA的FFT信号处理器具有低功耗、高性能、可重构性等优点,在某些场合得到了广泛的应用和推广。

本项目立足于FPGA高性能计算平台上,通过对FFT算法和FPGA硬件设计的研究,设计并实现一种含有多路输入、高速计算和低延迟的基于FPGA的FFT信号处理器。

该处理器可以广泛应用于各种领域中的实时信号处理、通信系统等方面,对于提升信号处理的效率和性能具有一定的实际应用价值和业务推广前景。

同时,也会对FPGA的设计和实现技术的研究提供宝贵的经验和思路参考。

二、研究内容和方案根据本项目研究要求,我们将从以下几个方面入手,逐步实现基于FPGA的FFT信号处理器:1. 算法研究:研究FFT算法的数学原理和实现思路,了解不同FFT 算法之间的差异和优劣。

结合FPGA硬件设计的实际限制和特点,选择适合的FFT算法和计算方式,寻求提高算法性能的方法和技巧。

2. 系统框架设计:设计FFT信号处理器的硬件框架,包括时序控制单元、外部存储器接口、数据输入输出接口等。

考虑多路输入、高速计算和低延迟等要求,优化系统内部的硬件电路。

3. 实现与调试:编写VHDL语言描述FFT处理器的硬件电路,并利用Quartus II软件进行综合和布局布线,生成可用于载入FPGA的映像文件。

在硬件实现完成后,进行各种测试和验证,优化调试系统的性能和稳定性。

4. 性能评估和对比:对设计和实现的FFT信号处理器进行性能评估,包括计算速度、功耗、延迟等指标的测试和分析。

同时,对比与其他实现FFT处理器的方式,说明基于FPGA的FFT信号处理器所具有的优势和不足之处。

基于FPGA实现的FFT速度与规模分析

Tab.2 The formula to calculate and parameter of

Quaruts contrast table

名称

N=8M=9 N=8M=18

N=16M=9 N=16M=18

公式计算值

12

24

24

48

Quartus 计算值

speed

名称

顺序型

并联型

级联型

阵列型

乘法器数量

96

48(基-2)

344

196

运算速度

4 个周期

4 个周期

1 个周期

1 个周期

3 FPGA 最高频率分析 如图 1袁FPGA 中计算最小时钟周期公式为[5]院

. All Rights Reserved.

tclk skew 为时钟偏斜遥

FPGA 运行的最高频率为最小时钟周期的倒数遥

K=L 而级联型和阵列型是由多个蝶形单元同时计算袁所用时间为 1 个 计算周期遥 即院

192 科技视界 Science & Technology Vision

Science & Technology Vision

科技视界

K=1

对于使用蝶形单元的个数院 顺序型的特点是只有一个基-r 的蝶

形单元袁其中 r=N袁所有点都由一个蝶形单元顺序完成袁即:

tclk =Microtco +tlogic +tnet +Microtsu -tclk skew 其中袁tclk skew =tCD1 -tCD2 式中院tclk 为时钟的最小周期曰 Microtco 为寄存器固有时钟输出延时曰 tlogic 为同步元件之间的组合逻辑延迟曰 tnet 为网线延迟曰 Microtsu 为寄存器固有时钟建立延时曰

基于FPGA的混合基FFT算法设计与实现

第19卷 第2期太赫兹科学与电子信息学报Vo1.19,No.2 2021年4月Journal of Terahertz Science and Electronic Information Technology Apr.,2021 文章编号:2095-4980(2021)02-0303-05基于FPGA的混合基FFT算法设计与实现侯晓晨,孟骁,陈昊(北京理工大学信息与电子学院,北京 100081)摘 要:目前,研究资源节约型的低复杂度混合基快速傅里叶变换(FFT)设计技术具有重要的应用价值。

本文基于现场可编程逻辑门阵列(FPGA)平台提出并实现了一种新型混合基FFT分解算法。

该算法基于原位存储结构设计,采用素数因子分解与库利-图基分解相结合的混合分解模式,在省去了一步旋转因子乘法运算的同时也有效减小了存储空间和运算量,并采用通用蝶形单元模块设计使得算法能够同时适应基2、基3、基4的FFT运算。

仿真结果表明,该算法可以极大提高FFT处理点数的灵活性,有效节省运算资源。

关键词:快速傅里叶变换;混合基算法;通用蝶形单元;现场可编程逻辑门阵列中图分类号:TN79+1文献标志码:A doi:10.11805/TKYDA2019435Design and implementation of mixed-radix FFT algorithm based on FPGAHOU Xiaochen,MENG Xiao,CHEN Hao(School of Information and Electronics,Beijing Institute of Technology,Beijing 100081,China)Abstract:Recently, researches on resource-saving mixed-radix Fast Fourier Transform(FFT) technology with low complexity and high efficiency are of vital importance in digital signal processing.In this paper, a new mixed-radix FFT decomposition algorithm based on Field Programmable GateArray(FPGA) is proposed and implemented. The proposed in-place algorithm adopts a hybriddecomposition mode combining prime factorization algorithm and Cooley-Tukey algorithm, which cansave one-step multiplication operation of the rotation factor and also reduce the storage space andoperation amount effectively, while it also uses the universal butterfly unit module to accommodate tothe radix-2, radix-3, and radix-4 FFT operations. The simulation results indicate that the proposedalgorithm can greatly improve the flexibility of FFT processing points and effectively save computingresources.Keywords:Fast Fourier Transform;mixed-radix algorithm;universal butterfly unit;Field Programmable Gate Array快速傅里叶变换(FFT)算法具有计算量小的显著优点,在信号处理技术领域得到了广泛应用,现已成为数字信号处理强有力的工具。

用FPGA实现FFT算法

用FPGA实现FFT算法引言DFT(Discrete Fourier Transformation)是数字信号分析与处理如图形、语音及图像等领域的重要变换工具,直接计算DFT的计算量与变换区间长度N的平方成正比。

当N较大时,因计算量太大,直接用DFT算法进行谱分析和信号的实时处理是不切实际的。

快速傅立叶变换(Fast Fourier Transformation,简称FFT)使DFT运算效率提高1~2个数量级。

其原因是当N较大时,对DFT进行了基4和基2分解运算。

FFT算法除了必需的数据存储器ram和旋转因子rom外,仍需较复杂的运算和控制电路单元,即使现在,实现长点数的FFT仍然是很困难。

本文提出的FFT 实现算法是基于FPGA之上的,算法完成对一个序列的FFT计算,完全由脉冲触发,外部只输入一脉冲头和输入数据,便可以得到该脉冲头作为起始标志的N点FFT输出结果。

由于使用了双ram,该算法是流型(Pipelined)的,可以连续计算N点复数输入FFT,即输入可以是分段N点连续复数数据流。

采用DIF(Decimation In Frequency)-FFT和DIT(Decimation In Time)-FFT对于算法本身来说是无关紧要的,因为两种情况下只是存储器的读写地址有所变动而已,不影响算法的结构和流程,也不会对算法复杂度有何影响。

算法实现的可以是基2/4混合基FFT,也可以是纯基4FFT和纯基2FFT运算。

傅立叶变换和逆变换对于变换长度为N的序列x(n)其傅立叶变换可以表示如下:N nkX(k)=DFT[x(n)] =Σ x(n)Wn=0式(1)其中,W=exp(-2π/N)。

当点数N较大时,必须对式(1)进行基4/基2分解,以短点数实现长点数的变换。

而IDFT的实现在DFT的基础上就显得较为简单了:式(2)由式(2)可以看出,在FFT运算模块的基础上,只需将输入序列进行取共轭后再进行FFT运算,输出结果再取一次共轭便实现了对输入序列的IDFT运算,因子1/N对于不同的数据表示格式具体实现时的处理方式是不一样的。

基于FPGA的FFT处理器的设计与实现

基于FPGA的FFT处理器的设计与实现作者:胡其明曹闹昌刘东斌来源:《现代电子技术》2008年第02期摘要:对FFT处理器的实现算法-频域抽取基4算法做了介绍。

介绍一种以FPGA作为设计载体,设计和实现一套集成于FPGA内部的FFT处理器的方法和设计过程。

FFT处理器的硬件试验结果表明该处理器的运算结果正确,并且具有较高运算速度。

该方法具有设计简单灵活,体积小等优点,可用于雷达处理、高速图像处理和数字通信等应用场合。

关键词:FFT;FPGA;基4算法,硬件实验结果中图分类号:TP368.1 文献标识码:B 文章编号:1004-373X(2008)02-074-03(Engineering College,Air Force Engineering University,Xi′an,710038,ChinaAbstract:The paper firstly introduces the arithmetic of FFT processor-Radix-4,and introduces the method and process of design and realizes a FFT processor,which is integrated in FPGAchip,regarding FPGA as design carrier.The result of hardware test of FFT processor shows that the processor works well and has high speed.The design has the advantages of simple ness,agility and small bulk.It can be used in many application situations,such as radar signals process,high speed image process and digitaKeywords:FFT;FPGA;radix-数字信号处理领域中FFT作为时域和频域转换的基本运算,是数字谱分析的必要前提。

基于FPGA的FFT算法硬件实现

FFT(快速傅里叶变换)是一种非常重要的算法,在信号处理、图像处理、生物信息学、计算物理、应用数学等方面都有着广泛的应用。

在高速数字信号处理中,FFT的处理速度往往是整个系统设计性能的关键所在。

FPGA(现场可编程门阵列)是一种具有大规模可编程门阵列的器件,不仅具有ASIC(专用集成电路)快速的特点,更具有很好的系统实现的灵活性。

基于FPGA的设计可以满足实时数字信号处理的要求,在市场竞争中具有很大的优势。

因此,FPGA为高速FFT算法的实现提供了一个很好的平台。

1 FFT算法的硬件实现1.1 系统框图本设计利用流水线技术来提高系统的性能,系统框图,如图1所示。

其中,地址产生单元生成RAM读写地址,写使能信号以及相关模块的启动、控制信号,是系统的控制核心;4点蝶形运算单元的最后一级输出不是顺序的;旋转因子产生单元生成复乘运算中的旋转因子的角度数据;旋转因子ROM中预置了每一级运算中所需的旋转因子。

在FPGA设计中,为提高系统的运行速度,而将指令分为几个子操作,每个子操作由不同的单元完成,这样,每一级的电路结构得到简化,从而减少输入到输出间的电路延时,在较小的时钟周期内就能够完成这一级的电路功能。

在下一个时钟周期到来时,将前一级的结果锁存为该级电路的输入,这样逐级锁存,由最后一级完成最终结果的输出。

也就是说,流水线技术是将待处理的任务分解为相互有关而又相互独立、可以顺序执行的子任务来逐步实现。

本设计中,4点蝶形运算单元、旋转因子复乘模块以及最后的精度截取模块采用流水线技术来处理。

1.2 基4蝶形运算算法原理式(1)为基4蝶形运算单元的一般表达式,其中,,N为FFT运算的点数,本设计中为1 024,p为旋转因子W的相位角,其规律将在1.4节讨论。

X(0)、X(1)、X(2)、X(3)为原始数据,顺序输入RAM后蝶形倒序输出,与旋转因子复乘再进行4点蝶形运算,而X1(0)、X1(1)、X1(2)、X1(3)即为第1级蝶形运算的结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FFT谱分析测频算法的FPGA实现

作者:闫斌

来源:《科技创新与应用》2013年第35期

摘要:在FPGA实验中,主要是用FPGA来实现FFT,使其完成对信号的频谱分析。

实验中设计流水线结构FFT,主要是进行蝶形单元的设计;旋转参数生成;FFT系统仿真测试。

关键词:FPGA;QuartusⅡ;FFT处理器

1 实验原理及步骤

1.1 QuartusⅡ开发环境

QuartusⅡ是Altera公司提供的FPGA/CPLD集成开发软件,在QuartusⅡ上可以完成设计输入、HDL综合、布新布局(适配)、仿真和选择以及硬件测试等流程,它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、开始处理和器件编程。

QuartusⅡ具备

仿真功能,同时支持第三方的仿真工具(如ModelSin)。

此外,QuartusⅡ与MATLAB和DSP Builder结合,可用进行基于FPAG的DSP系统开发,是DSP硬件系统实现的工具EDA工具。

FFT算法种类很多,基本上可分为两大类:一类是针对N等于2的整数次幂的算法,如基2算法、基4算法和分裂基算法等;另一类是针对N不等于2的整数次幂的算法,以Winograd 为代表,它们有重要的理论价值,但是不适于硬件实现。

基2算法结构简单,但运算量大。

基4算法相对于基2算法更为复杂,但是计算量减少了。

FFT算法按分解方式的不同又可以分为时域抽取算法(decimation in time,DIT)和频域抽取算法(decimation in frequency,DIF)两种。

这两种算法在本质上都是一种基于标号分解的算法,在运算量和复杂性等方面完全一样。

考虑到本设计FFT运算的点数不是太多,故选用了时域抽取基2算法(DIT)。

1.3 按时间抽取的基-2FFT算法(DIT-基2-FFT)原理

FFT算法由多级蝶形运算构成,具体运算流图也有多种形式。

本设计选用了输入倒序、输出顺序的运算流图,图3所示为N=8点时的DIT-FFT运算流图。

这种运算流图是同址运算,其优点是:在同一级运算中,每个蝶形的两个输入数据只对计算本蝶形有用,而且蝶形的输入输出数据节点又同在一条水平线上,这就意味着计算完一个蝶形运算后,所得输出数据可以立即存入元出入数据所占用的存储器。

因此,在硬件实现时可以节省存储单元。

1.4 FFT处理器结构设计

FFT算法的FPGA硬件实现在Altera公司的MAX+plusⅡ系统环境下开发完成,选用基于查找表结构内嵌存储器的APEX20系列FPGA器件。

图4为FFT处理器的结构图。

本设计采

用单元结构设计思路,整个处理器由数据接收单元、运算单元、旋转因子存储单元、地址产生单元和中央控制单元5个单元组成,各单元在中央控制单元的控制下协调工作。

其中,内部接收单元采用乒乓RAM结构,扩大了数据吞吐量,计算单元采用流水与并行结合的结构,加快了运算速。

1.5 中央控制单元

中央控制单元是整个系统的控制核心,其主要功能是控制数据流向,协调各单元之间的运行。

中央控制单元根据系统时钟确定当前蝶型运算所处的级数m和个数n,并把m、n传送给地址产生单元。

地址产生单元产生蝶型运算两个输入数据和旋转因子的地址,并把地址传送给运算RAM和旋转因子存储器。

在中央控制单元读使能信号控制下两个输入数据和旋转因子被读出。

读出的数据进行必要的延迟和定标处理后,送给运算单元。

经过蝶型运算后,运算结果按原址写入RAM。

1.6 数据接收单元

数据接收单元主要功能是按帧接收外部数据,并将每帧数据按码位倒置的顺序乒乓存入接收RAM1或接收RAM2。

中央控制单元交替的对接收RAM中的数据进行处理,当中央控制单元将接收RAM1中的数据取出,经过蝶型运算,结果存入运算RAM1的同时上一帧数据的FFT运算结果从运算RAM2取出。

接收RAM用FPGA的片上双口RAM实现,接收单元控制写端口,中心控制单元控制读端口。

1.7 运算单元

运算单元由蝶型运算器和运算RAM组成。

蝶型运算器完成对输入数据的蝶型运算,运算RAM作为FFT的中间数据缓存。

蝶型运算器输入数据为A=Ap+Aqj,B=Bp+Bqj,旋转因子WrN=Wp+Wqj,蝶型运算输出如式(3)所示。

根据式(3),蝶型运算器可由一个复数乘法和两个复数加(减)法器组成。

为了提高运算速度采用并行运算,用四个实数乘法器、三个实数加法器、三个实数减法器组成。

蝶型运算器实现框图如图5所示。

蝶型运算各个模块利用MAX+plusⅡ开发软件中所提供的宏单元生成。

运算RAM1和运算RAM2作为FFT的中间数据缓存。

两块RAM交替作为数据读出和运算结果写入单元,直到第6级蝶型运算完成。

1.8 旋转因子存储单元

旋转因子存储单元,存储FFT运算所需要的旋转因子WrN,WrN=e(-j2?仔/N)r

(r=0,1,…,N/2-1)。

旋转因子先在Matlab中分实部和虚部产生,转化成16位定点数,并将结果保存成hex文件格式。

利用MAX+plusII软件提供的ROM宏模块“lpm_rom”产生两个(N/2)×16bit的ROM,并分别用旋转因子实部和虚部对应的hex文件对两个ROM初始化,

这样旋转因子的值就固化在了FPGA中。

对应不同级的蝶型运算,地址产生器产生相应的地址送给ROM将旋转因子读出。

1.9 地址产生单元

1.10 块浮点单元

块浮点单元采用文献提出的算法和实现方法。

其基本思想是每级蝶型运算结果动态扩展但最大扩展2位。

块浮点单元对蝶型运算结果的高3位进行检测,判断当前结果动态范围扩展位数,记录当前级的最大扩展位数。

下一级蝶型运算时,根据前一级的最大扩展位数,对读出的数据进行定标,选取数据送入蝶型运算器。

块浮点单元将每一级运算结果动态范围扩展位数进行累加,和FFT运算结果一同输出。

1.11 FFT处理器功能仿真与设计验证

3 结束语

由图7~图9所示可以看出,由于处理器采用定点运算,在进行乘法和加法运算时不可避免的造成一定的误差,尤其是在功率谱接近零值的这些点上,相对误差较大;但是在我们无奈所关心的功率谱的幅值点上,相对误差仅为百分之一左右,完全可以满足大多数应用对于运算精度的需求。

参考文献

[1]张辉,张集龙.基-2 FFT处理器的FPGA实现[J].计算机与现代化,2009.

[2]程佩青.数字信号处理教程.第三版[M].北京:清华大学出版社,2007.

[3]袁俊泉,孙敏琪,曹瑞.Verilog HDL数字系统设计及其应用[M].西安:西安电子科技大学出版社,2002.

[4] 谢彦林.可变点流水线结构FFT处理器的设计及其FPGA实现[D].西安:西安电子科技大学,2007.

[5]云霄.可配置FFT/IFFT处理器的设计及其FPGA构造[D].西安:西安电子科技大学,2009.

[6]蔡可红.基于FPGA的FFT设计与实现[D].南京:南京理工大学,2006.。