IEEE754标准的32位低功耗浮点乘法器设计

IEEE 754浮点存储格式

度来说,k=11,则bias=1023) 此时m的计算公式:m=1.M表示的数值(754标准规定此时小数点左侧的隐 含位为1,。如M=‘101’,则1.M=1.101表示的数值为1.625,m=1.625)

二、IEEE754有五种类型浮点数据

2、非规格化数:当E的二进制位全部为0时,N 为非规格化数。此时e,m的计算公式: e=1-bias m=0.M这个二进制位表示的数字 3、特殊数值:当E的二进制位全为1时为特殊数 值。此时若M的二进制位全为0,则n表示无穷大 (看S位1还是0,从而表示负无穷大和无穷大); 若M的二进制位不全为0,表示不是一个合法实数 或者无穷。

例2、把浮点数 11000001110010010000000000000000 解:1、符号位:1;阶码位E:10000011; 尾数:1001 0010 0000 0000 0000 000 2、还原阶码位:e=E-bias=131-127=4 3、写出浮点数的规格化形式: 1.1001001*24 (其中前面的1.是因为规格化数 的隐含位而来) 4、该浮点数的非规格化形式: 11001.001 5、转化为十进制数为-25.125

这里介绍IEEE标准754规定的两种浮点数格式: 单精度和双精度。 单精度:N共32位,其中S占1位,E占8位,M站 23位。

31 30 S E 23 22 0 M

双精度:N共64位,其中S占1位,E占11位,M 占52位。

63 62 52 51 0

S

E

M

一、浮点数的格式

S 0/1 0/1 0/1

二、IEEE754有五种类型浮点数据

1、将十进制数转换成二进制数; 2、规格化二进制数:改变阶码,使小数点前面仅 有第一位有效数字; 3、计算阶码: 单精度浮点数的阶码加上偏移量127, 7FH(01111111B) 双精度浮点数的阶码加上偏移量,1023, 3FFH(001111111111B) 4、以浮点数据格式存储。

ieee754标准32位浮点数和普通浮点数

IEEE 754标准32位浮点数和普通浮点数作为计算机科学领域中的重要概念,浮点数在计算机程序与数据处理中扮演着至关重要的角色。

而其中IEEE 754标准32位浮点数和普通浮点数更是在计算机的底层运算中发挥着关键作用。

本文将深入探讨这两种浮点数,并从不同角度进行全面评估,以便更好地理解其深度和广度。

1. 普通浮点数的基本概念普通浮点数是一种十进制系统的数值表示方式,可以表示实数并支持浮点运算。

它由三个部分组成:符号位、尾数和指数。

符号位用来表示数值的正负性,尾数用来表示有效数字,指数则用来表示位置和值的大小。

常见的浮点数表示方法有单精度浮点数和双精度浮点数,分别占用4字节和8字节的存储空间。

2. IEEE 754标准32位浮点数的特点IEEE 754标准32位浮点数是一种二进制浮点数的表示方式,广泛应用于计算机系统中。

它同样由三个部分组成:符号位、尾数和指数。

不同的是,IEEE 754标准采用了规范化表示和偏置指数的方式,使得浮点数的表示更加简洁和高效。

IEEE 754标准还规定了一些特殊的浮点数值,如正无穷大、负无穷大和NaN(非数值)等,以满足不同的计算需求。

3. 深度分析:IEEE 754标准32位浮点数和普通浮点数的区别在数字表示和计算精度方面,IEEE 754标准32位浮点数与普通浮点数存在一些显著的区别。

普通浮点数采用十进制系统表示,可以精确表示大多数的小数,但无法精确表示一些特定的无限循环小数,导致精度损失。

而IEEE 754标准32位浮点数采用二进制系统表示,可以精确表示某些无限循环小数,但对一些十进制无限循环小数的精度依然存在限制。

IEEE 754标准32位浮点数在存储空间和计算速度上具有显著的优势,适合于大规模数据计算和图形处理等应用场景。

4. 广度探讨:IEEE 754标准32位浮点数和普通浮点数的应用领域由于其在计算机底层运算中具有高效性和精度,IEEE 754标准32位浮点数被广泛应用于科学计算、工程仿真、金融计算、图形处理等领域。

ieee754标准32位浮点数和普通浮点数

ieee754标准32位浮点数和普通浮点

数

IEEE 754标准是一种被广泛使用的浮点数表示方法,它规定了浮点数的表示

格式和计算规则。

在计算机中,浮点数被用来表示实数,包括小数和无限大。

IEEE 754标准定义了32位浮点数和64位浮点数两种格式,其中32位浮点数是最常用的。

在IEEE 754标准中,32位浮点数被分为三个部分:符号位、指数位和尾数位。

符号位用来表示浮点数的正负,占1位;指数位用来表示浮点数的指数,占8位;尾数位用来表示浮点数的小数部分,占23位。

在计算浮点数时,首先要根据指数位的值来确定浮点数的范围和精度,然后根据尾数位的值来确定浮点数的小数部分。

普通浮点数是指在计算机中用常规方式表示的实数。

它通常用定点数表示,也可以用浮点数表示。

在普通浮点数中,小数点的位置是固定的,而在IEEE 754标准中,小数点的位置是可以浮动的。

这种可变性使得IEEE 754标准能够更好地适应不同情况下的精度需求。

在IEEE 754标准中,32位浮点数的精度比普通浮点数更高。

由于它使用了更多的位数来表示小数部分,因此它可以更精确地表示小数。

此外,IEEE 754标准

还支持负指数和无穷大的表示,这使得它能够更好地处理特殊情况。

总之,IEEE 754标准是一种非常优秀的浮点数表示方法,它具有高精度、范

围大、易读易懂等优点。

相比之下,普通浮点数的表示方法则显得较为简单粗糙。

因此,在需要高精度计算或处理特殊情况时,我们应该优先考虑使用IEEE 754标准的32位浮点数。

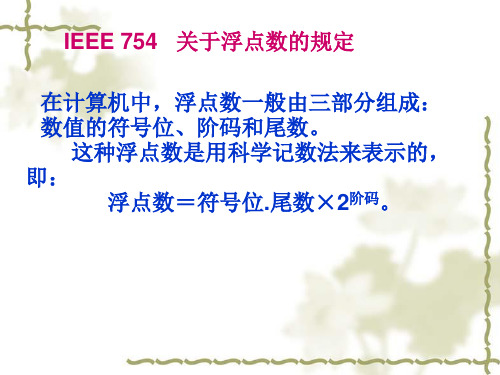

IEEE 754关于浮点数的规定

把十进制数100.25转换成协处理器中的 例1 把十进制数 转换成协处理器中的 浮点数 解:1、进制转换: 、进制转换: (100.25)10=(1100100.01)2 2、规格化: 、规格化: (1100100.01)2=1.10010001×26 × =1.10010001×2110 × 3、计算阶码: 、计算阶码: 110+01111111=10000101 = 4、数值的符号位为:0, 、数值的符号位为: , 阶码为: 阶码为:10000101, , 尾数为: 尾数为: 1001 0001 0000 0000 0000 000

一、 IEEE754对阶码作如下规定 对阶码作如下规定

偏移阶码E 0 1 2 … 127 128 129 … 254 255 实际阶码值 保留做操作数 -126 -125 0 1 2 127 保留做操作数

ቤተ መጻሕፍቲ ባይዱ

二、对上溢和下溢的处理 当运算结果小于规格化浮点数所能表示的 最小值时,以前硬件处理策略,或者结果置0 最小值时,以前硬件处理策略,或者结果置 或者产生一个下溢陷阱, 或者产生一个下溢陷阱 , 这两种方案均不能 令人满意。 令人满意。 IEEE754处理方法是使用非规格化数 。 处理方法是使用非规格化数。 处理方法是使用非规格化数 这时阶码为0(即移码-127),尾数没有隐含 这时阶码为 (即移码 ) 最高位是0。 位,最高位是 。 这样的结果是降低精度,扩大表示范围。 这样的结果是降低精度,扩大表示范围。 如原来规格化单精度最小值是1.0x2-126,而非 如原来规格化单精度最小值是 而非 规格化单精度最小值是2 只有1 规格化单精度最小值是 -23 x2-126=2-149(只有 只有 位有效位) 位有效位 。

ieee754的32位浮点数的标准

ieee754的32位浮点数的标准IEEE 754是一种被广泛使用的浮点数标准,它定义了各种浮点数的表示方式、舍入规则以及常见运算操作。

在IEEE 754标准中,32位浮点数是其中的一种表示方式,该标准用于在计算机科学领域中表示和处理浮点数。

32位浮点数的IEEE 754标准定义了如下几个部分:1. 符号位(S):占据第31位,0表示正数,1表示负数。

2. 指数位(E):占据第30到第23位,用于表示浮点数的指数部分。

3. 尾数位(M):占据第22到第0位,用于表示浮点数的尾数部分。

根据上述定义,32位浮点数的表示可以用如下公式表示:(-1)^S × (1.M) × 2^(E-127)其中,S为符号位(0表示正数,1表示负数),M为尾数部分(用二进制表示的小数),E为指数部分(用无符号二进制表示),127为偏置值。

为了更好地理解32位浮点数的IEEE 754标准,让我们以一个例子来说明。

假设我们要表示十进制数 -12.25,首先我们需要将其转换为二进制数。

-12.25的二进制表示为-1100.01。

1. 符号位:由于-12.25是一个负数,所以符号位为1。

2. 尾数部分:我们需要将二进制小数点移动到左边第一位,即-1.10001。

3. 规一化:对尾数部分进行规一化,即将小数点移动到左边第一位,同时对指数进行相应的调整。

这一步中,我们需要左移使得小数点在整数位左边,因此尾数部分为1.10001,指数部分为4。

4. 指数部分:根据规定,浮点数的指数部分需要加上一个偏置值。

对于32位浮点数,偏置值为127。

因此,指数部分为4 + 127 = 131。

5. 写入32位:将符号位、指数部分和尾数部分写入32位浮点数。

符号位为1,指数部分为10000011(用二进制表示的131),尾数部分为10001000000000000000000。

最终,我们得到32位浮点数的表示为:11000001100010000000000000000000。

ieee754浮点数的标准运算

IEEE 754标准是浮点数运算中广泛使用的一种标准,它定义了浮点数的表示和算术运算规则。

使用IEEE 754标准的浮点数在计算机科学和工程中扮演着重要的角色,因此对其标准运算进行深入的学习和理解具有重要意义。

1. IEEE 754浮点数的表示IEEE 754标准定义了浮点数的表示方式,它主要由三部分组成:符号位、指数位和尾数位。

具体而言,对于单精度浮点数,其总位数为32位,其中1位表示符号位,8位表示指数位,23位表示尾数位;对于双精度浮点数,其总位数为64位,其中1位表示符号位,11位表示指数位,52位表示尾数位。

通过这种表示方式,可以表示从非常小的数到非常大的数,以及在这些数之间的所有可能数值。

2. IEEE 754浮点数的算术运算IEEE 754标准定义了浮点数的算术运算规则,包括加法、减法、乘法和除法。

在这些算术运算中,需要考虑到浮点数的表示方式和精度限制,以及可能出现的溢出和舍入误差。

在进行浮点数的算术运算时,需要特别注意以下几点:a. 舍入误差由于浮点数的表示精度是有限的,因此在进行算术运算时往往会产生舍入误差。

这种误差可能会在多次运算后累积,导致最终结果的精度下降。

为了尽可能减小舍入误差,可以使用一些数值稳定的算法和技巧,例如Kahan算法和扩展精度算法等。

b. 溢出和下溢在进行加法、减法、乘法和除法运算时,需要考虑到可能出现的溢出和下溢情况。

当两个大数相加或相乘时,很可能会超出浮点数所能表示的范围,导致溢出;而当两个小数相减或相除时,很可能会得到一个接近于零的结果,导致下溢。

为了避免这些情况的发生,可以采用一些有效的方法,例如对数据进行归一化处理、使用大数运算库等。

3. IEEE 754浮点数的特殊值在IEEE 754标准中,还定义了一些特殊的浮点数值,例如正无穷大、负无穷大、NaN(Not a Number)等。

这些特殊值在实际计算中往往需要特别处理,以避免产生不确定的结果。

强烈推荐IEEE754标准的32位浮点数格式.ppt

0,100 0010 1,100 1000 1000 0000 0000 0000 表示为十六进制的代码:课4件2C88000H短。浮点数格式

把浮点数C1C90000H转成十进制数。 ⑴ 十六进制→ 二进制形式,并分离出符号位、阶码和尾数。

阶码8位 课件 尾数23位

例3:将(100.25)10转换成短浮点数格式。 ⑴ 十进制数→二进制数 (100.25)10=(1100100.01)2 ⑵ 非规格化数→规格化数 1100100.01=1.10010001×26 ⑶ 计算移码表示的阶码(偏置值+阶码真值)

1111111+110=10000101 ⑷ 以短浮点数格式存储该数。

课件

试1将-(0.11)用IEEE短实数浮点格式表示。

2

31 30

23 22

0

S

数符

阶码

尾数

解:-(0.11) = -(1 + 0.1) 2 -1 ;隐含尾数最高位为1 2 数符:为1

阶码:阶码 = 阶码真值 + 127= -1+127=126=(01111110)2 尾数:为 0.100 0

该浮点代码为 1,01111110,100 0

IEEE754标准的32位浮点数格式

课件

IEEE754标准的32位浮点数格式为:

31 30

S

23 22

0

数符

阶码

尾数

S:数符,0正1负。 阶码:8位以2为底,阶码 = 阶码真值 + 127 。 尾数:23位,采用隐含尾数最高位1的表示方法,

实际尾数24位,尾数真值 = 1 + 尾数 这种格式的非0浮点数真值为:(-1)S 2阶码-127(1 + 尾数)

IEEE-754-32位单精度浮点数计算VB源码知识讲解

大学生对手工艺制作兴趣的调研If UBound(TmpS) = 1 Then

For n = 1 To Len(TmpS(1))

If Mid(TmpS(1), n, 1) = "1" Then BinToOct = BinToOct + (2 ^ (-1 * n))

Next n

Dim n As Integer

Dim TmpS() As String

体现市民生活质量状况的指标---恩格尔系数,上海也从1995年的53.4%下降到了2003年的37.2%,虽然与恩格尔系数多在20%以下的发达国家相比仍有差距,但按照联合国粮农组织的划分,表明上海消费已开始进入富裕状态(联合国粮农组织曾依据恩格尔系数,将恩格尔系数在40%-50%定为小康水平的消费,20%-40%定为富裕状态的消费)。

If Left(TmpBin, 1) = "1" Then GetData = "-" & GetData

End Function

Private Function HexToBin(TmpHex As String) As String

Dim n As Integer

Dim I As Integer

(3)心态问题End If

(一)创业机会分析

End Function

功能性手工艺品。不同的玉石具有不同的功效,比如石榴石可以促进血液循环,改善风湿和关节炎;白水晶则可以增强记忆力;茶晶能够帮助镇定情绪,缓解失眠、头昏等症状。顾客可以根据自己的需要和喜好自行搭配,每一件都独一无二、与众不同。For n = 1 To Len(TmpS(0))

If Mid(TmpS(0), n, 1) = "1" Then BinToOct = BinToOct + (2 ^ (Len(TmpS(0)) - n))

ieee754标准32位浮点数和普通浮点数

ieee754标准32位浮点数和普通浮点数浮点数是计算机中常用的一种数据类型,用来表示实数。

在计算机中,浮点数采用科学计数法形式存储,具有有效数字和指数部分。

IEEE754标准是一种用于表示浮点数的二进制标准,其中32位浮点数是其中的一种变体。

首先,我们来介绍普通的浮点数表示方式。

普通浮点数采用符号位、指数位和尾数位的形式进行存储。

其中符号位用于表示浮点数的正负,指数位用于表示浮点数的数量级,尾数位用于表示浮点数的精度。

然而,普通浮点数的表示方式存在一些问题。

例如,对于小数点后面的位数,普通浮点数的表示精度相对较低。

此外,普通浮点数的表示方式对于极大或极小的数值表达能力不足。

因此,IEEE754标准引入了32位浮点数的表示方式。

IEEE754标准32位浮点数采用了单精度浮点数的格式进行存储。

它与普通浮点数相比,在表示范围和精度方面有所优化。

32位浮点数使用了1个符号位、8个指数位和23个尾数位。

符号位用于表示浮点数的正负,0表示正数,1表示负数。

指数位用于表示浮点数的数量级,通过对指数位的移位操作,可以实现对浮点数表示范围的扩展。

尾数位用于表示浮点数的精度,通过对尾数位的有效位数进行调整,可以实现对浮点数表示精度的控制。

由于32位浮点数的表示方式相对于普通浮点数来说更为精确,因此在科学计算、图形处理等领域广泛应用。

它能够满足大部分计算需求,并且具有较高的计算速度和较小的存储空间。

总之,IEEE754标准32位浮点数和普通浮点数都是计算机中常用的表示实数的方法。

普通浮点数适用于一般计算需求,而32位浮点数则在对浮点数精度和表示范围要求较高的场景下更具优势。

了解它们的特点和应用场景,对于正确、高效地使用浮点数具有重要意义。

IEEE754标准的32位低功耗浮点乘法器设计

西安邮电大学毕业设计(论文)题目:32位低功耗浮点乘法器设计学院:电子工程学院专业:集成电路设计与集成设计班级:电路1303学生姓名:白进宝学号:05136073导师姓名:邢立冬职称:高级工程师起止时间:2017年3月6日至2017年6月11日毕业设计(论文)声明书本人所提交的毕业论文《32位低功耗浮点乘法器设计》是本人在指导教师指导下独立研究、写作的成果,论文中所引用他人的文献、数据、图件、资料均已明确标注;对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式注明并表示感谢。

本人完全理解《西安邮电大学本科毕业设计(论文)管理办法》的各项规定并自愿遵守。

本人深知本声明书的法律责任,违规后果由本人承担。

论文作者签名:日期:年月日西安邮电大学本科毕业设计(论文)选题审批表西安邮电大学本科毕业设计(论文)开题报告西安邮电大学毕业设计 (论文)成绩评定表摘要乘法器是高性能数字信号处理芯片的关键部件,也是实时、高速数字信号处理器的核心。

乘法单元具有面积大、延时长、结构复杂的特点,如何设计出高速、低功耗、结构简单的乘法单元是近些年来的一大难题。

本文比较各种乘法器设计的算法与结构,分析它们的面积、速度与功耗。

最终找出最优的设计方案,完成32位浮点乘法器的电路设计。

本文首先介绍IEEE-754浮点数标准和浮点操作,对IEEE-754浮点运算标准的浮点表示格式、精度、范围、规格化进行分析,并对决定乘法器性能的实现算法与实现结构进行深入研究。

其中实现浮点乘法的重点是实现整数的乘法。

其主要实现途径有移位相加结构和华莱士树型结构。

移位相加乘法结构简单,但是延时较长;华莱士树型乘法延时较短,但是结构比较复杂。

为了进一步提高运算速度,将乘法器改为流水线结构,达到时间上的并行。

最后应用低功耗设计方法对电路进行优化设计以降低系统功耗。

关键词:IEEE-754;乘法器;移位相加;华莱士树;流水线;低功耗ABSTRACTMultiplier is the key component of high performance digital signal processing chip, and also the core of real-time and high-speed digital signal processor. The multiplication unit has the characteristics of large area, long delay and complex structure. How to design a multiplication unit with high speed, low power consumption and simple structure is a difficult problem in recent years.In this paper, the algorithms and structures of various multipliers are compared, and their area, speed and power consumption are analyzed. Finally, the optimal design scheme is found, and the circuit design of 32 bit floating point multiplier is completed.This paper first introduces the IEEE-754 floating point standard and floating point operations on floating-point IEEE-754 floating-point standard expression analysis format, accuracy, scope, standard, and implementation of the decision performance of multiplier algorithm in-depth research and implementation of structure. Among them, the key point of floating point multiplication is to achieve the multiplication of integers. The main implementation methods include shift adding structure and Wallace tree structure. The shift addition and multiplication structure is simple, but the time delay is long; the Wallace tree type multiplication delay is shorter, but the structure is complex. In order to further improve the speed of operation, the multiplier is changed into pipelined structure to achieve parallel time. Finally, the low power design method is applied to optimize the circuit to reduce system power consumption.Key words: IEEE-754;Multiplier;Shift addition;Wallace tree;Assembly line;low power consumption目录第一章绪论 (1)1.1 研究意义 (1)1.2 研究的主要内容 (1)1.3 论文结构安排 (1)第二章设计原理概述 (3)2.1 浮点数格式 (3)2.2 IEEE-754浮点数标准 (3)2.3 浮点乘法运算原理 (5)第三章浮点乘法器电路设计 (7)3.1 无符号数一位乘法 (7)3.2 超前进位加法器设计 (8)3.3 移位相加乘法结构 (9)3.4 华莱士树结构 (10)3.5 尾数的舍入与规格化 (17)3.6 阶码的处理 (19)3.7 符号位处理 (20)3.8 浮点乘法器总体结构 (20)3.9 流水线结构 (21)3.9.1 流水线技术简介 (21)3.9.2 流水线浮点乘法器设计 (21)3.10 低功耗设计 (22)3.10.1 低功耗设计背景 (22)3.10.2 低功耗设计方法 (22)3.10.3 浮点乘法器的低功耗设计 (24)3.11 本章小结 (25)第四章仿真验证与逻辑综合 (26)4.1 功能仿真 (26)4.1.1 尾数运算功能仿真 (26)4.1.2 浮点乘法器功能仿真 (27)4.1.3 流水线结构浮点乘法器功能仿真 (28)4.2 浮点乘法器逻辑综合 (29)4.3 浮点乘法器时序仿真 (30)4.4 功耗分析 (30)结束语 (32)致谢 (33)参考文献 (34)附录 (35)第一章绪论1.1 研究意义进入21世纪以,来大数据、互联网+、人工智能等新兴技术正在逐步进入到我们的生活当中。

ieee754标准浮点数

ieee754标准浮点数IEEE 754标准浮点数,是一种用于表示和计算浮点数的二进制编码格式。

它由国际电气电子工程师学会(IEEE)制定,被广泛应用于计算机和计算领域。

一、引言随着计算机的快速发展,计算机需要能够处理和表示实数,而实数是一个无穷的集合。

然而,计算机只能处理有限的数据和位数,因此需要一种方法来表示和计算实数,并且要在有限的位数范围内获得尽可能高的精度。

二、浮点数的表示浮点数的表示通常由三个部分组成,分别是符号位(sign),指数位(exponent)和尾数(fraction/mantissa)。

其中符号位用于表示实数的正负,指数位用于表示小数点的位置,尾数用于表示实数的小数部分。

三、单精度和双精度浮点数IEEE 754标准定义了两种主要的浮点数格式,分别是单精度浮点数和双精度浮点数。

单精度浮点数占据32位,双精度浮点数占据64位。

其中,单精度浮点数有1位用于符号位,8位用于指数位,23位用于尾数;双精度浮点数有1位用于符号位,11位用于指数位,52位用于尾数。

四、浮点数的规范化浮点数的规范化是指将浮点数表示为一个标准格式,使得尾数部分的最高位为1。

这样可以减少尾数的位数,提高浮点数的精度。

规范化的过程包括移位和调整指数。

五、浮点数的运算浮点数的加法、减法、乘法和除法都需要按照IEEE 754标准进行。

其中,加法和减法操作使用尾数对齐并相加,然后根据指数的差值进行尾数的移位,最后进行舍入操作。

乘法和除法操作涉及到指数和尾数的运算,需要分别进行处理。

六、浮点数的舍入浮点数的舍入是指将计算结果调整为有限位数的过程。

IEEE 754标准定义了五种舍入方式,分别是向最近的偶数舍入(round to nearest even)、向零舍入(round towards zero)、向正无穷舍入(round towards positive infinity)、向负无穷舍入(round towards negative infinity)和向最近的整数舍入(round to nearest integer)。

ieee754单精度浮点数格式

ieee754单精度浮点数格式IEEE 754 单精度浮点数格式是一种用于描述浮点数的二进制格式。

它是以科学计数法的形式存储数值,包含一个符号位、一个阶码和一个尾数。

按照规格形式,32位的 IEEE 754 格式浮点数可以被分为三个部分:符号位(1 bit),阶码(8 bits)和尾数(23 bits),它们的结合表示了一个浮点数的实际值。

符号位:IEEE 754 标准浮点格式规定,符号位是浮点数表示中的第一位,值为0或1,用于表示浮点数的正负。

如果符号位为1,则表示这个浮点数是负数。

反之,如果符号位为0,则表示它是正数。

在单精度浮点格式中,符号位用一个 0 或 1 表示,占用 1 个 bit。

阶码:阶码用于表示浮点数中的科学计数法指数部分。

在单精度浮点格式中,阶码占用 8 个 bits,可以表示从 -126 到 +127 的数值。

为了在阶码和尾数中存储较大的数值,IEEE 754 规范采用了偏移值的技术。

在单精度浮点格式中,偏移值为 127,即实际阶码的范围是从 -126 到+127。

尾数:尾数表示浮点数的小数部分。

在单精度浮点格式中,尾数占用 23 个bits,并且在位数部分(又称为小数部分)上具有隐式前导位。

换句话说,在单精度浮点数格式中,数值总共有 24 位有效数字,其中 23 位用于表示数值,另一位用于表示隐式前导位。

这样复杂的存储技术可以使得单精度浮点数表示的范围更广,可以表示的精度更高。

总结:总的来说,IEEE 754 单精度浮点数格式是一种有助于在计算机系统中表示和操作浮点数的技术。

单精度浮点数格式的主要优势在于它可以在没有过多占用存储空间的情况下提供更高的运算速度。

但同时也有着它的缺陷,那就是会有一些浮点数在单精度浮点格式中出现精度丢失的问题。

尽管如此,IEEE 754 单精度浮点数格式仍被广泛应用于各种实际计算机系统中,不仅可以用于数字处理、科学计算、工程应用等领域,而且还可以用于网络传输以及多媒体存储和处理等。

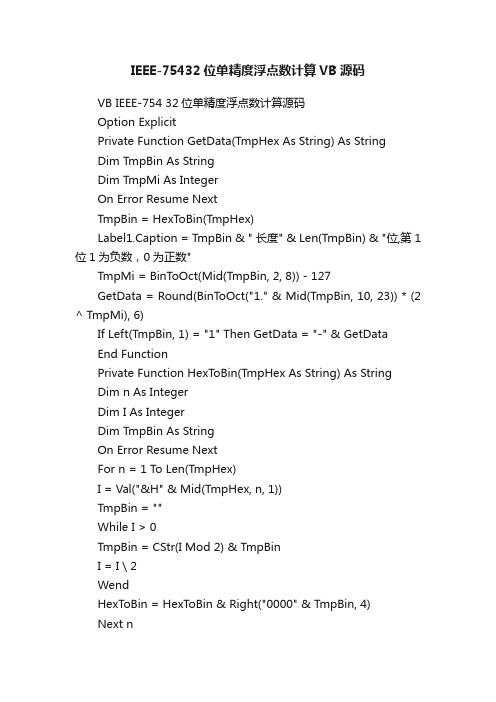

IEEE-75432位单精度浮点数计算VB源码

IEEE-75432位单精度浮点数计算VB源码VB IEEE-754 32位单精度浮点数计算源码Option ExplicitPrivate Function GetData(TmpHex As String) As StringDim TmpBin As StringDim TmpMi As IntegerOn Error Resume NextTmpBin = HexT oBin(TmpHex)Label1.Caption = TmpBin & " 长度" & Len(TmpBin) & "位,第1位1为负数,0为正数"TmpMi = BinT oOct(Mid(TmpBin, 2, 8)) - 127GetData = Round(BinT oOct("1." & Mid(TmpBin, 10, 23)) * (2 ^ TmpMi), 6)If Left(TmpBin, 1) = "1" Then GetData = "-" & GetDataEnd FunctionPrivate Function HexToBin(TmpHex As String) As StringDim n As IntegerDim I As IntegerDim TmpBin As StringOn Error Resume NextFor n = 1 To Len(TmpHex)I = Val("&H" & Mid(TmpHex, n, 1))TmpBin = ""While I > 0TmpBin = CStr(I Mod 2) & TmpBinI = I \ 2WendHexToBin = HexToBin & Right("0000" & TmpBin, 4)Next nEnd FunctionPrivate Function BinToOct(TmpBin As String) As DoubleDim n As IntegerDim TmpS() As StringOn Error Resume NextTmpS = Split(TmpBin, ".")For n = 1 To Len(TmpS(0))If Mid(TmpS(0), n, 1) = "1" Then BinT oOct = BinToOct + (2 ^ (Len(TmpS(0)) - n)) Next nIf UBound(TmpS) = 1 ThenFor n = 1 To Len(TmpS(1))If Mid(TmpS(1), n, 1) = "1" Then BinT oOct = BinToOct + (2 ^ (-1 * n)) Next nEnd IfEnd Function。

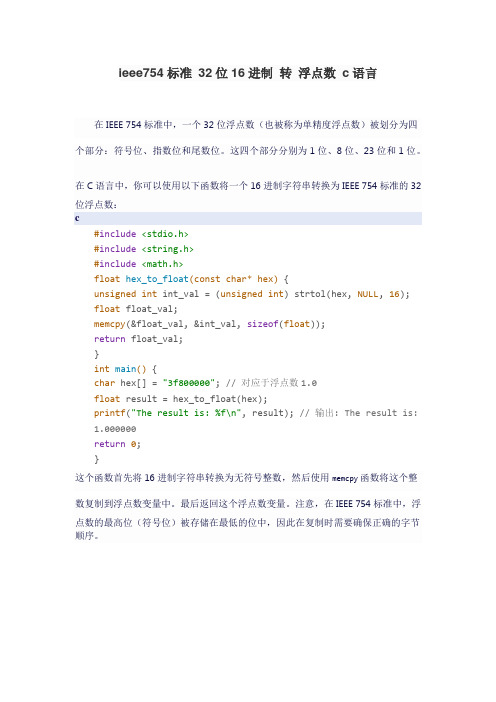

ieee754标准 32位16进制 转 浮点数 c语言

ieee754标准32位16进制转浮点数c语言在IEEE 754标准中,一个32位浮点数(也被称为单精度浮点数)被划分为四个部分:符号位、指数位和尾数位。

这四个部分分别为1位、8位、23位和1位。

在C语言中,你可以使用以下函数将一个16进制字符串转换为IEEE 754标准的32位浮点数:c#include<stdio.h>#include<string.h>#include<math.h>float hex_to_float(const char* hex) {unsigned int int_val = (unsigned int) strtol(hex, NULL, 16);float float_val;memcpy(&float_val, &int_val, sizeof(float));return float_val;}int main() {char hex[] = "3f800000"; // 对应于浮点数1.0float result = hex_to_float(hex);printf("The result is: %f\n", result); // 输出: The result is:1.000000return0;}这个函数首先将16进制字符串转换为无符号整数,然后使用memcpy函数将这个整数复制到浮点数变量中。

最后返回这个浮点数变量。

注意,在IEEE 754标准中,浮点数的最高位(符号位)被存储在最低的位中,因此在复制时需要确保正确的字节顺序。

32位单精度浮点乘法器的FPGA实现

32位单精度浮点乘法器的FPGA实现作者:胡侨娟仲顺安陈越洋党华 | 来源:现代电子技术 | 日期:2007-11-28 | 被阅读:7 次【小中大】摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综...摘要: 采用Verilog HDL语言, 在FPGA上实现了32位单精度浮点乘法器的设计, 通过采用改进型Booth编码,和Wallace 树结构, 提高了乘法器的速度。

本文使用Altera Quartus II 4.1仿真软件, 采用的器件是EPF10K100EQ 240 -1, 对乘法器进行了波形仿真, 并采用0.5CMOS工艺进行逻辑综合。

关键词: 浮点乘法器; Boo th 算法; W allace 树; 波形仿真随着计算机和信息技术的快速发展, 人们对微处理器的性能要求越来越高。

乘法器完成一次乘法操作的周期基本上决定了微处理器的主频, 因此高性能的乘法器是现代微处理器中的重要部件。

本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

1 乘法计算公式32 位乘法器的逻辑设计可分为: Booth编码与部分积的产生, 保留进位加法器的逻辑, 乘法阵列的结构。

1.1 Booth编码与部分积的逻辑设计尾数的乘法部分,本文采用的是基4 Booth编码方式, 如表1。

首先规定Am 和Bm表示数据A和B的实际尾数,P 表示尾数的乘积, PPn表示尾数的部分积。

浮点32 位数, 尾数是带隐含位1 的规格化数, 即: Am =1×a22a21….a和Bm= 1×b22b21.…b, 由于尾数全由原码表示,相当于无符号数相乘, 24 × 24 位尾数乘积P 的公式为:1.2 乘法器的阵列结构本文采用的是3 -2 加法器, 输入3 个1 位数据: a, b,ci; 输出2 个1 位数据: s, Co。

IEEE754标准的32位浮点数格式

阶码8位

尾数23位

例3:将(100.25)10转换成短浮点数格式。 ⑴ 十进制数→二进制数 (100.25)10=(1100100.01)2 ⑵ 非规格化数→规格化数

1100100.01=1.10010001×26 ⑶ 计算移码表示的阶码(偏置值+阶码真值)

IEEE754标准的32位浮点数格式

IEEE754标准的32位浮点数格式为:

31 30

S码

尾数

S:数符,0正1负。 阶码:8位以2为底,阶码 = 阶码真值 + 127 。 尾数:23位,采用隐含尾数最高位1的表示方法,

实际尾数24位,尾数真值 = 1 + 尾数 这种格式的非0浮点数真值为:(-1)S 2阶码-127(1 + 尾数)

试1将-(0.11)用IEEE短实数浮点格式表示。

2

31 30

23 22

0

S

数符

阶码

尾数

解:-(0.11) = -(1 + 0.1) 2 -1 ;隐含尾数最高位为1 2 数符:为1

阶码:阶码 = 阶码真值 + 127= -1+127=126=(01111110)2 尾数:为 0.100 0

于是有 X=(-1)s×1.M×2e =+(1.011011)×23 =+1011.011=(11.375)10

1011.112 1 23 0 22 1 21 1 20 0 21 1 22 1 23 10 11.37510

[例4] 将十进制数数20.59375转换成32位浮点数的二进制 格式来存储。

[解:]首先分别将整数和分数部分转换成二进制数:

20.59375=10100.10011

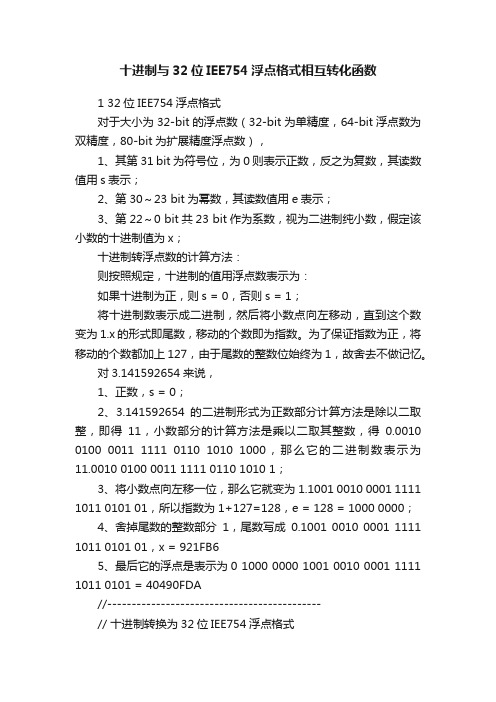

十进制与32位IEE754浮点格式相互转化函数

十进制与32位IEE754浮点格式相互转化函数1 32位IEE754浮点格式对于大小为32-bit的浮点数(32-bit为单精度,64-bit浮点数为双精度,80-bit为扩展精度浮点数),1、其第31 bit为符号位,为0则表示正数,反之为复数,其读数值用s表示;2、第30~23 bit为幂数,其读数值用e表示;3、第22~0 bit共23 bit作为系数,视为二进制纯小数,假定该小数的十进制值为x;十进制转浮点数的计算方法:则按照规定,十进制的值用浮点数表示为:如果十进制为正,则s = 0,否则s = 1;将十进制数表示成二进制,然后将小数点向左移动,直到这个数变为1.x的形式即尾数,移动的个数即为指数。

为了保证指数为正,将移动的个数都加上127,由于尾数的整数位始终为1,故舍去不做记忆。

对3.141592654来说,1、正数,s = 0;2、3.141592654的二进制形式为正数部分计算方法是除以二取整,即得11,小数部分的计算方法是乘以二取其整数,得0.0010 0100 0011 1111 0110 1010 1000,那么它的二进制数表示为11.0010 0100 0011 1111 0110 1010 1;3、将小数点向左移一位,那么它就变为1.1001 0010 0001 1111 1011 0101 01,所以指数为1+127=128,e = 128 = 1000 0000;4、舍掉尾数的整数部分1,尾数写成0.1001 0010 0001 1111 1011 0101 01,x = 921FB65、最后它的浮点是表示为0 1000 0000 1001 0010 0001 1111 1011 0101 = 40490FDA//--------------------------------------------// 十进制转换为32位IEE754浮点格式//--------------------------------------------void ConvertDexToIEE754(float fpointer,ModRegisterTpyedef *SpModRegister){double integer,decimal;unsigned long bininteger,bindecimal;Uint8 _power,i;decimal = modf(fpointer,&integer);if(decimal || integer){bindecimal = decimal * 0x800000; //2^23while((bindecimal & 0xff800000) > 0)bindecimal >>= 1;if(integer > 0){bininteger = integer;for(i=0;i<32;i++) //计算整数部分的2的幂指数{if(bininteger&0x1)_power = i;bininteger >>= 0x1;}bininteger = integer;bininteger &= ~(0x1 << _power); //去掉最高位的1if(_power >= 23) //如果幂指数>23 则舍弃小数位部分{bininteger >>= (_power-23);bindecimal = 127+_power;bininteger |= bindecimal << 23;}else{bininteger <<= (23 - _power);bindecimal >>= _power;bininteger |= bindecimal;bindecimal = 127+_power;bininteger |= bindecimal << 23;}}else if(integer == 0){bindecimal <<= 9;_power = 0;bininteger = bindecimal;while(bininteger == ((bindecimal<<1)>>1)){_power++;bindecimal <<= 0x1;bininteger = bindecimal;}_power++;bindecimal <<= 0x1;bindecimal >>= 9;bininteger = bindecimal;bindecimal = 127-_power;bininteger |= bindecimal << 23;}i = 0;SpModRegister->RegByte[i++] = (bininteger >> 24) & 0xff; SpModRegister->RegByte[i++] = (bininteger >> 16) & 0xff;SpModRegister->RegByte[i++] = (bininteger >> 8 ) & 0xff;SpModRegister->RegByte[i++] = bininteger & 0xff;}}浮点数转十进制的计算方法:则按照规定,浮点数的值用十进制表示为:=(-1)^s * (1 + x) * 2^(e –127)对于49E48E68来说,1、其第31 bit为0,即s = 02、第30~23 bit依次为100 1001 1,读成十进制就是147,即e = 147。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西安邮电大学毕业设计(论文)题目:32位低功耗浮点乘法器设计学院:电子工程学院专业:集成电路设计与集成设计班级:电路1303学生姓名:***学号:05136073导师姓名:邢立冬职称:高级工程师起止时间:2017年3月6日至2017年6月11日毕业设计(论文)声明书本人所提交的毕业论文《32位低功耗浮点乘法器设计》是本人在指导教师指导下独立研究、写作的成果,论文中所引用他人的文献、数据、图件、资料均已明确标注;对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式注明并表示感谢。

本人完全理解《西安邮电大学本科毕业设计(论文)管理办法》的各项规定并自愿遵守。

本人深知本声明书的法律责任,违规后果由本人承担。

论文作者签名:日期:年月日西安邮电大学本科毕业设计(论文)选题审批表西安邮电大学本科毕业设计(论文)开题报告西安邮电大学毕业设计 (论文)成绩评定表摘要乘法器是高性能数字信号处理芯片的关键部件,也是实时、高速数字信号处理器的核心。

乘法单元具有面积大、延时长、结构复杂的特点,如何设计出高速、低功耗、结构简单的乘法单元是近些年来的一大难题。

本文比较各种乘法器设计的算法与结构,分析它们的面积、速度与功耗。

最终找出最优的设计方案,完成32位浮点乘法器的电路设计。

本文首先介绍IEEE-754浮点数标准和浮点操作,对IEEE-754浮点运算标准的浮点表示格式、精度、范围、规格化进行分析,并对决定乘法器性能的实现算法与实现结构进行深入研究。

其中实现浮点乘法的重点是实现整数的乘法。

其主要实现途径有移位相加结构和华莱士树型结构。

移位相加乘法结构简单,但是延时较长;华莱士树型乘法延时较短,但是结构比较复杂。

为了进一步提高运算速度,将乘法器改为流水线结构,达到时间上的并行。

最后应用低功耗设计方法对电路进行优化设计以降低系统功耗。

关键词:IEEE-754;乘法器;移位相加;华莱士树;流水线;低功耗ABSTRACTMultiplier is the key component of high performance digital signal processing chip, and also the core of real-time and high-speed digital signal processor. The multiplication unit has the characteristics of large area, long delay and complex structure. How to design a multiplication unit with high speed, low power consumption and simple structure is a difficult problem in recent years.In this paper, the algorithms and structures of various multipliers are compared, and their area, speed and power consumption are analyzed. Finally, the optimal design scheme is found, and the circuit design of 32 bit floating point multiplier is completed.This paper first introduces the IEEE-754 floating point standard and floating point operations on floating-point IEEE-754 floating-point standard expression analysis format, accuracy, scope, standard, and implementation of the decision performance of multiplier algorithm in-depth research and implementation of structure. Among them, the key point of floating point multiplication is to achieve the multiplication of integers. The main implementation methods include shift adding structure and Wallace tree structure. The shift addition and multiplication structure is simple, but the time delay is long; the Wallace tree type multiplication delay is shorter, but the structure is complex. In order to further improve the speed of operation, the multiplier is changed into pipelined structure to achieve parallel time. Finally, the low power design method is applied to optimize the circuit to reduce system power consumption.Key words: IEEE-754;Multiplier;Shift addition;Wallace tree;Assembly line;low power consumption目录第一章绪论 (1)1.1 研究意义 (1)1.2 研究的主要内容 (1)1.3 论文结构安排 (1)第二章设计原理概述 (3)2.1 浮点数格式 (3)2.2 IEEE-754浮点数标准 (3)2.3 浮点乘法运算原理 (5)第三章浮点乘法器电路设计 (7)3.1 无符号数一位乘法 (7)3.2 超前进位加法器设计 (8)3.3 移位相加乘法结构 (9)3.4 华莱士树结构 (10)3.5 尾数的舍入与规格化 (17)3.6 阶码的处理 (19)3.7 符号位处理 (20)3.8 浮点乘法器总体结构 (20)3.9 流水线结构 (21)3.9.1 流水线技术简介 (21)3.9.2 流水线浮点乘法器设计 (21)3.10 低功耗设计 (22)3.10.1 低功耗设计背景 (22)3.10.2 低功耗设计方法 (22)3.10.3 浮点乘法器的低功耗设计 (24)3.11 本章小结 (25)第四章仿真验证与逻辑综合 (26)4.1 功能仿真 (26)4.1.1 尾数运算功能仿真 (26)4.1.2 浮点乘法器功能仿真 (27)4.1.3 流水线结构浮点乘法器功能仿真 (28)4.2 浮点乘法器逻辑综合 (29)4.3 浮点乘法器时序仿真 (30)4.4 功耗分析 (30)结束语 (32)致谢 (33)参考文献 (34)附录 (35)第一章绪论1.1 研究意义进入21世纪以,来大数据、互联网+、人工智能等新兴技术正在逐步进入到我们的生活当中。

集成电路产业是电子信息产业的核心对我国的经济政治和国防安全有着重大影响[1]。

为此我国把集成电路产业定为重点战略产业,制定了一系列的相关政策确保我国经济建和国防安全。

目前包括微处理器在内的集成电路的发展一直严格遵循摩尔定律。

处理器中的浮点乘法单元是整个电路设计中需要着重考虑的对象。

在某些领域中需要很高精度的浮点运算,而功耗大、面积大是高精度浮点运算部件的固有特性[2]。

因此浮点乘法器性能的优劣关乎到信号处理的能力。

正因为高性能的浮点乘法器的广泛应用,故近几十年来其一直是研究的热点。

1.2 研究的主要内容本论文的主要的研究内容是设计出性能符合要求的32位低功耗浮点乘法器,要求在高可靠性的基础上,工作速度达到50MHz。

依据性能的要求,乘法器每次乘法运算的时间应在20ns以内。

首先介绍浮点数标准及其运算,深入研究32位低功耗浮点乘法器设计当中的常见的电路结构和算法确定乘法单元的结构。

浮点乘法器的设计重点是尾数乘法器的设计,其性能优劣决定了整个设计是否能够达到要求[3]。

对比移位相乘结构和华莱士树结构的优劣,深入研究Wallace树形结构,在Wallace树形结构的基础上改进为流水线浮点乘法器。

由于近些年来移动设备的普及,本次浮点乘法器的设计适当加入了低功耗的内容。

通过功能仿真来验证设计的原理是否正确。

再通过逻辑综合和时序仿真看其性能是否达到要求。

在满足性能的要求上,选取合理的设计结构和器件。

1.3 论文结构安排第一章绪论。

介绍论文研究的意义、研究的主要内容、论文结构安排。

第二章设计原理概述。

主要介绍浮点数的表示格式,浮点数的规格化,IEEE-754浮点数标准,简要介绍浮点乘法运算的基本原理。

第三章浮点乘法器电路设计。

对实现尾数相乘运算的两种结构进行比较分析。

移位相加乘法结构是最简单的乘法算法结构,结构简单,便于设计,但是延时较长,只能在工作频率较低的系统中工作;华莱士树乘法结构利用并行计算的思想,能够极大的降低延时,但同时带来的是面积与功耗的增加。

最后介绍尾数的舍入与规格化、阶码的处理和符号位处理。

将浮点乘法器改为流水线结构进一步提高运算速度。

在功能正确的基础上适当加入低功耗设计内容把系统的功耗降低。

第四章仿真验证与逻辑综合。

通过功能仿真、逻辑综合和时序仿真观察运算结果,分析性能是否达到要求。

第五章结论。

总结32位低功耗浮点乘法器的完成情况,并分析本次设计存在的问题为进一步研究提供方向。

第二章设计原理概述2.1 浮点数格式计算机中的浮点数是用一个定点的尾数再乘以一个基为2的阶数得到。

计算机内部用定点数表示数值数据的范围比浮点数小很多。

例如,对于n位带符号整数,其表示范围为-2n-1~(2 n-1-1),运算结果很容易溢出,此外,用定点数也不能表示出大量的带有小数点的实数。

因此,计算机内部会专门定义浮点数格式用以表示更大范围的实数。

对于任意一个实数X,都可以表示为:X=(−1)S×M×R E(2-1) 其中,S取值为0或1,用来决定X的正负,通常情况下0表示正数,1表示负数;M是定点小数用来表示实数X的尾数;E是一个二进制定点整数,称为X的阶码或指数;R是基数,可以约定为2、4、8等。