一种快速浮点加法器的设计与优化方法

Xilinx Vivado HLS中Floating-Point(浮点)设计介绍

Xilinx Vivado HLS中Floating-Point(浮点)设计介绍

编码风格与技巧

尽管通常Fixed-Point(定点)比FloaTIng-Point(浮点)算法的FPGA实现要更快,且面积更高效,但往往有时也需要FloaTIng-Point来实现。

这是因为Fixed-Point有限的数据动态范围,需要深入的分析来决定整个设计中间数据位宽变化的pattern,为了达到优化的QoR,并且要引入很多不同类型的Fixed-Point中间变量。

而FloaTIng-Point具有更大的数据动态范围,从而在很多算法中只需要一种数据类型的优势。

Xilinx Vivado HLS工具支持C/C++ IEEE-54标准单精度及双精度浮点数据类型,可以比较容易,快速地将C/C++ FloaTIng-Point算法转成RTL代码。

与此同时,为了达到用户期望的FPGA资源与性能,当使用Vivado HLS directives时需要注意C/C++编码风格与技巧相结合。

编码风格

1.1 单双精度浮点数学函数

#include

float example(float var)

{

return log(var); // 双精度自然对数

}

在C设计中,这个例子,Vviado HLS 生成的RTL实现将输入转换成双精度浮点,并基于双精度浮点计算自然对数,然后将双精度浮点输出转换成单精度浮点。

#include

float example(float var)

{

return logf(var); // 单精度自然对数

}

在C设计中,logf才是单精度自然对数,这个例子Vviado HLS 生成的RTL实现将基。

32位浮点加法器设计

32位浮点加法器设计32位浮点加法器是一种用于计算机中的算术逻辑单元(ALU),用于执行浮点数的加法运算。

它可以将两个32位浮点数相加,并输出一个32位的结果。

设计一个高效的32位浮点加法器需要考虑多个方面,包括浮点数的表示形式、运算精度、舍入方式、运算逻辑等。

下面将详细介绍32位浮点加法器的设计。

1.浮点数的表示形式:浮点数通常采用IEEE754标准进行表示,其中32位浮点数由三个部分组成:符号位、阶码和尾数。

符号位用来表示浮点数的正负,阶码用来表示浮点数的指数,尾数用来表示浮点数的小数部分。

2.运算精度:在浮点数加法运算中,精度是一个重要的考虑因素。

通常,浮点数加法器采用单精度(32位)进行设计,可以处理较为广泛的应用需求。

如果需要更高的精度,可以考虑使用双精度(64位)浮点加法器。

3.舍入方式:浮点数加法运算中,结果通常需要进行舍入处理。

常见的舍入方式有以下几种:舍入到最近的偶数、舍入向上、舍入向下、舍入到零。

具体的舍入方式可以根据应用需求来确定。

4.运算逻辑:浮点数加法运算涉及到符号位、阶码和尾数的加法。

首先,需要判断两个浮点数的阶码大小,将较小的阶码移到较大的阶码对齐,并相应调整尾数。

然后,将尾数进行相加并进行规格化处理。

最后,根据求和结果的大小,进行溢出处理和舍入操作。

在32位浮点加法器的设计中,还需要考虑到性能和效率。

可以采用流水线技术来提高运算速度,将加法运算划分为多个阶段,并在每个阶段使用并行处理来加速运算。

此外,还可以使用硬件加速器和快速逻辑电路来优化运算过程。

总结起来,设计一个高效的32位浮点加法器需要考虑浮点数的表示形式、运算精度、舍入方式、运算逻辑以及性能和效率。

在实际设计中,还需要根据具体应用需求进行功能扩展和优化。

通过合理的设计和调优,可以实现高性能的浮点加法器,满足不同应用场景的需求。

一种64位浮点乘加器的设计与实现

关 键 词 改进 B t oh 2算 法 浮 点 乘 加 器

Wa ae l c 树 全 定制 l

文 章 编 号 1 0 — 3 1 ( 0 6 1 — 0 5 0 文献 标 识 码 A 0 2 8 3一 20 )8 0 9 — 4 中图 分 类 号 T 3 2 P 1

( o e e o C mp t ce c , otw s r o tc nclU i r t, ia 0 2 C l g f o ue S i e N r et n P l eh i nv s y X ’n 7 7 ) l r n h e y a ei 1 0

Ab t a t T e sr c : h mu t l — d p rt n s f n a na n ma y s i n i c n e g n e n p l a in , s e il n t e l py a d o e ai i u d me t l i n c e t a d n i e r g a p i t s e p ca l i h i o i f i c o y i d f ma e r c s i a d f l o i g p o e s g n DS t e l a ig— on mu t l a d r a b e w d l u e . mi g t o r C 0 e e n P.h f t o n p it l py- d e h s e n i e y s dAi n a P we P 6 3 i mirp c so s se , 6 b t c r e s r y tm a 4一 i o o mu t l a d u e f ai g- on u i l p y— d f s d l t i o n p it nt wh c s p o t E ih u p rs I EE一 5 d u l p e iin 7 4 o b e r cso l t n tn a d s f ai g — i t sa d r i mp e n e n MI 02 u o n p o i lme t d i S C .5 m 1 5 CMOS e h oo y wi h t o f p st e d r c in P M tc n lg t t e me h d o o i v i t h i e o f l c so c r u t& ly u e in I U e o r h n ie meh d n l dn mp v d o t l oi m , la e o — ul u tm i i — c a o t d s . S S a c mp e e sv t o i cu i g i r e B h a g rt g t o h Wa l c c n p e s g te — n t b ln e - o rs o o i g o aa c d 4 2 c mp e s g u i n ar — a e a d r t . rs i r e u i a a c d 4 2 c mp e s c mp sn f b ln e - o r s i nt a d c r s v d e s e c n n s y Ke wo d :i r v d B t l o i m , l p y a d, a lc r e f l c so d sg y r s mp o e o h a g r h mu t l- d W l e te ,u l u t m e i t i a — n

32位浮点加法器设计

32位浮点加法器设计一、基本原理浮点数加法运算是在指数和尾数两个部分进行的。

浮点数一般采用IEEE754标准表示,其中尾数部分采用规格化表示。

浮点加法的基本原理是将两个浮点数的尾数对齐并进行加法运算,再进行规格化处理。

在加法运算过程中,还需考虑符号位、指数溢出、尾数对齐等特殊情况。

二、设计方案1. 硬件实现方案:采用组合逻辑电路实现浮点加法器,以保证运算速度和实时性。

采用Kogge-Stone并行加法器、冒泡排序等技术,提高运算效率。

2.数据输入:设计32位浮点加法器,需要提供两个浮点数的输入端口,包括符号位、指数位和尾数位。

3.数据输出:设计32位浮点加法器的输出端口,输出相加后的结果,包括符号位、指数位和尾数位。

4.控制信号:设计合适的控制信号,用于实现指数对齐、尾数对齐、规格化等操作。

5.流程控制:设计合理的流程控制,对各个部分进行并行和串行处理,提高加法器的效率。

三、关键技术1. Kogge-Stone并行加法器:采用Kogge-Stone并行加法器可以实现多位数的并行加法运算,提高运算效率。

2.浮点数尾数对齐:设计浮点加法器需要考虑浮点数尾数的对齐问题,根据指数大小进行右移或左移操作。

3.溢出判断和处理:浮点加法器需要判断浮点数的指数是否溢出,若溢出需要进行调整和规格化。

4.符号位处理:设计浮点加法器需要考虑符号位的处理,确定加法结果的符号。

四、性能评价性能评价是衡量浮点加法器设计好坏的重要指标。

主要从以下几个方面进行评价:1.精度:通过与软件仿真结果进行比较,评估加法器的运算精度,误差较小的加法器意味着更高的性能。

2.速度:评估加法器的运行速度,主要考虑延迟和吞吐量。

延迟越低,意味着加法器能够更快地输出结果;吞吐量越高,意味着加法器能够更快地处理多个浮点加法运算。

3.功耗:评估加法器的功耗情况,低功耗设计有助于提高整个系统的能效。

4.面积:评估加法器的硬件资源占用情况,面积越小意味着设计更紧凑,可用于片上集成、嵌入式系统等场景。

基于IEEE754浮点数的快速反码加法器设计

符

c l

图 2 3位 加 法 器

图 3 由 3 加 法 器 构 造 的 9位 超 前 进 位 加 法器 位

第 一级 超前 进位 逻辑 的输 出可 由( ) 3 式递 推得 到 : = o 0 。 C G +尸 c C =G + 1 1 1 P G + 1 0 0 2 1 P C =G + 1 0 P 尸 C 由此类 推 , C =G + 2 1 2 1 0 2 P C 3 2 P G +P P G +P P10 0 在这 一组 3位加 法器 中 , 可令 在 组进位 c 表 达式 中

成原码 , 最快的方法是使 用反 码运算 系统 。试应用超前进位和 反码运 算 系统原理设 计 了单精 度 浮点数

的快 速 的 阶码 减 法 器 和 尾 数 加 法 器/ 法 器 。 减

[ 关键 词] 浮点数 ; 加法器 ; 反码 ; 超前进位 [ 中图分类 号]T 1 [ 献标 识码 ]A P3 文 [ 文章编号 ]10 6 2 2 0 )6- 0 3一 5 0 6— 4 X(0 7 0 0 8 o

达式 为 : S =AoB oC C =AB +( iC … A +B )

() 1

() 2

第 二个 等式可 以写 为 :

C+ 1= Gf Pi + C

其 中 : AB ; =A + G = i B;

[ 收稿 日 ]0 7 O 一 8 期 2 0 一 3 O [ 作者简介 ] 李澄举 (9 9 , , 14 一) 男 广东梅县人 , 副教授 , 主要研究方 向: 计算机硬件设计 。

C + = G +Pi 1+ Pi 1Gf 2+ … +P 1 P1 1 Gi Pi P … G0+PE 1 o 0 P …P C

多工位级进模设计实例

多工位级进模设计实例在计算机科学领域中,多工位级进模设计是一种用于提高处理器性能的技术。

它通过将处理器划分为多个工位,并在每个工位上同时执行不同的指令,以实现指令级并行处理。

本文将介绍几个多工位级进模设计的实例,以帮助读者更好地理解这一概念。

实例一:乘法器设计乘法运算是计算机中常见的运算之一。

在传统的乘法器设计中,需要进行多次乘法和加法操作,整个运算过程比较耗时。

而采用多工位级进模设计,可以将乘法运算拆分为多个阶段,每个阶段在一个工位上并行执行。

例如,可以将乘法器划分为部分积生成、部分积累加和最终结果生成等多个工位,在每个工位上同时执行不同的操作。

这样可以大大提高乘法器的运算速度。

实例二:浮点数加法器设计浮点数加法是计算机中常见的浮点运算之一。

在传统的浮点数加法器设计中,需要进行多次位运算和规格化等操作,整个运算过程较为复杂。

而采用多工位级进模设计,可以将浮点数加法器划分为多个阶段,每个阶段在一个工位上并行执行。

例如,可以将浮点数加法器划分为对阶段、对尾数相加和规格化等多个工位,在每个工位上同时执行不同的操作。

这样可以显著提高浮点数加法器的运算速度。

实例三:流水线设计流水线是多工位级进模设计中常用的一种技术。

它将处理器的指令执行过程划分为多个阶段,并在每个阶段上同时执行不同的指令。

例如,可以将流水线划分为取指、译码、执行、访存和写回等多个阶段,在每个阶段上并行执行不同的指令。

这样可以大大提高处理器的指令执行效率。

实例四:并行排序算法设计排序算法是计算机中常用的一种算法。

传统的排序算法通常是串行执行的,即每次只处理一个元素。

而采用多工位级进模设计,可以将排序算法划分为多个阶段,每个阶段在一个工位上并行执行。

例如,可以将排序算法划分为分组、局部排序和合并等多个工位,在每个工位上同时处理不同的元素。

这样可以显著提高排序算法的执行速度。

多工位级进模设计是一种提高处理器性能的重要技术。

通过将处理器划分为多个工位,并在每个工位上同时执行不同的指令,可以实现指令级并行处理,从而大大提高处理器的运算速度和指令执行效率。

一种高速浮点加法器的优化设计

Ab ta t sr c :H ih p r o ma c l a i g p i t d e h o t n a t f d r c o r c s o s lo i h e lt g - e f r n ef t - o n d ri t e i o n a s mp ra t rso p mo e n mir p o e s r ,a s st e r a— i me i g r c s i g a d d g t l in l r c s ig c r ,a d t e k y t h c o r c s o a a p o e sn a h,t e c c e ma e p o e s n n i i g a o e sn o e n h e o t e mir p o e s rd t - r c s i g p t as p h y l o a i a d t n o e a in d cd d t e mir - r q e c ft e d vc . W e p e e t a n w e in o EEE c mp i n fb sc d i o p r t e ie h c o fe u n y o h e ie i o r s n e d sg f I o l t a d u l p e ii n f a i g p i ta d rb sn a i u p i z t n t c n q e , u h a wo d t a h s p r t n, h e o b e r c s l t n d e y u ig v ro s o t o o n o mia i e h iu s s c s t a a p t e a a i t r e o o p p l e s a e ,a t s 4 b CL a d r a n w A g c f rhg - p e l a i g p i ta d r i ei t g s f s e t5 A d e , e LZ l i i h s e d fo t - o n d e .wh c to u e aro n o o n ih i r d c sa p i f n f s a al l n iia o y a i me i o a t i a el a i g z r i ft e r s l o u ta t n wih u n wi g wh t e a tp r l t p t r rt ea c h tct n i p t e d n - e o b t o h e u t fs b r c i t o tk o n eh r c s o t e r s t s p st e o e a ie Al f a o e f c i ey i c e s t e s e d o f a ig p i t a d r n t Afe h e e i o i v r n g t . i v l b v e f t l n r a e h p e f l t - o n d e u i, o e v o n tr

FPGA典型设计方案精华汇总

FPGA典型设计方案精华汇总FPGA(现场可编程逻辑阵列)是一种可重构硬件设备,它可以根据用户的需求进行定制化的硬件设计。

FPGA在各个领域,如通信、计算机视觉、嵌入式系统等都得到了广泛的应用。

在设计FPGA时,能够选择合适的设计方案非常重要,下面是一些FPGA设计中的典型方案的精华汇总。

1.浮点加法器:浮点加法器是一种用来实现浮点数相加的重要组件。

在FPGA设计中,使用阵列乘法器和加法器可以实现浮点数相加的功能。

同时,还可以使用流水线技术提高浮点加法器的性能。

此外,还需要注意设计中的浮点数格式、舍入策略等问题。

2. 快速傅里叶变换(FFT):FFT是一种用来对离散数据进行频域分析的方法。

在FPGA设计中,可以使用蝶形运算单元(butterfly)来实现FFT。

通过并行计算和流水线技术,可以提高FFT的性能。

3.加密算法:加密算法在信息安全领域中起到非常重要的作用。

在FPGA设计中,可以使用硬件加速器来实现快速的加密算法。

同时,还需要考虑加密算法的安全性和延迟等因素。

4.VGA显示控制器:VGA显示控制器是一种用来控制显示器输出的组件。

在FPGA设计中,可以使用时序电路和状态机来实现VGA显示控制器。

通过设置合适的显示分辨率和刷新率,可以实现高质量的图像显示。

5.视频编码器:视频编码器是一种将视频信号进行压缩的组件。

在FPGA设计中,可以使用视频编码标准(如H.264)来实现视频编码器。

通过使用硬件并行计算和流水线技术,可以实现实时的视频编码。

6.数字滤波器:数字滤波器是一种用来处理数字信号的重要组件。

在FPGA设计中,可以使用FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器来实现数字滤波器。

通过优化滤波器的结构和算法,可以实现高性能和低延迟的数字信号处理。

7. 通信接口:通信接口是一种用来实现不同设备之间数据传输的组件。

在FPGA设计中,可以使用串行通信接口(如UART、SPI、I2C)和并行通信接口(如Ethernet、PCIe)来实现高速数据传输。

一种深度流水线的浮点加法器

关键 词 : 浮点加法器;P A 流水线; FG ; 吞吐量

中图分 类号 : N 3 . T 4 12

文献 标识码 : A

文章 编 号 :o 59 9 ( o 7 O -9 o l o -4 O 2 o ) 3o 儿-4

b t d xo rt na dma t s p r t n, d io ds b rcinwees p r t p r sp e n e Fo i— o hi e p ai ni ao ai n e o n s e o a dt na u t t r e aae a a t i n a o d wa rs td e rsn

.

gepeio 3 i ) p rt n we s tr ’ Srt Ifmi h ,ahee ru h u ts n r ta 5 l r s n(2bt o ai , e Al aS t i I a l c i ci d t o g p t ae oe h n3 6 ci s e o u d e a x y p v h r r

S HAO Ji , U n ln YU n c e g e Wa —e g. Ha —h n

(olg f If r t nS i c n eh oo y, n igUnvri f rn ui C l e n omai c n e d T cn lg Na jn ies yo Aeoa t s& As 0 “i5 e o o e a t c tm t , r c " 1 0 6 C ∞ ) g2 0 1

M Hzb ih-tg epy pp l i . yeg t a ed e l iei u s ng Ke o d :la ig p i ta d r PGA ;p p l i g h o g p t y w r s fo tn - on d e ;F iei n ;t r u h u n

4位快速加法器设计原理

4位快速加法器设计原理快速加法器是一种计算器件,可以快速地对两个二进制数进行加法运算。

相对于一般的加法器,它具有更高的速度和效率。

本文主要介绍4位快速加法器的设计原理。

1.基本概念在二进制加法中,加法器通过对两个二进制数分别进行逐位相加的方法,得到它们的和。

二进制加法的基本规则如下:0+0=0;1+0=1;0+1=1;1+1=0(进位1)。

在四位二进制数的加法中,每位相加可以得到一个位和进位两位。

4位快速加法器在计算时需要考虑到位和进位两个方面。

2.快速加法器的组成4位快速加法器可以由4个1位全加器和1个2位全加器组成。

1位全加器的输出等于输入A、B和进位C的和。

输出S等于(A xor B) xor C,进位C 等于AB+C(A xor B)。

2位全加器是由两个1位全加器和一个2选1选择器组成。

输入A和B分别与这两个全加器相连,进位C输入到这两个全加器的进位端。

选择器的选择信号是两个输入和上一个全加器的进位,选择器的输出连接到2位全加器的进位输出。

3.原理图4位快速加法器的原理图如下所示:每个1位全加器都由具有相同运算功能的逻辑门电路组成。

在1位全加器中,输入A、B和进位C分别与XOR、AND和OR门相连,这些门的输出再次进行逻辑运算得到输出S和新的进位C。

2位全加器由两个1位全加器和一个2选1选择器组成。

选择器的选择信号是上一个1位全加器的进位和两个输入的和。

这两个1位全加器的进位输出也分别与这个选择器相连。

4.流程图4位快速加法器的计算流程图如下所示:将输入的两个4位二进制数的第0位分别输入到1位全加器1和2中。

这两个全加器的进位C0均为0,得到第0位的位和(S0)和进位(C1)。

然后,将输入的两个4位二进制数的第1位分别输入到1位全加器3和4中。

全加器3的进位C1为1,因为它是在第0位加法器的进位C1的基础上进行的。

全加器4的进位C2为全加器3的进位C2与两个输入的和的2选1选择器输出的结果。

32位浮点加法器设计[整理版]

![32位浮点加法器设计[整理版]](https://img.taocdn.com/s3/m/c6464a9e2af90242a895e5f9.png)

32位浮点加法器设计

苦行僧宫城

摘要:运算器的浮点数能够提供较大的表示精度和较大的动态表示范围,浮点 运算已成为现代计算程序中

不可缺少的部分。浮点加法运算是浮点运算中使用频率最高的运算。因此,浮 点加法器的性能影响着整个

CPU勺浮点处理能力。文中基于浮点加法的原理,采用Verilog硬件描述语言

设计32位单精度浮点数加法

f)规格化移位:对尾数加减结果进行移位,消除尾数的非有效位,使其最高位为

1。Байду номын сангаас

g)舍入:有限精度浮点表示需要将规格化后的尾数舍入到固定结果。 由以上 基本算法可见,它包含2个全长的移位即对阶移位和规格化移位,还要包括3个全 长的有效加法,即步骤c、d、g。由此可见,基本算法将会有很大的时延。

2 32位浮点加法器设计与实现

器,并用modelsim对浮点加法器进行仿真分析,从而验证设计的正确性和可 行性。

关键词:浮点运算 浮点加法器Verilog硬件描述语言

Studying on Relation of Technology and Civilization苦行僧宫城

(School of Mechatronic Engineering and Automation, Shanghai

University, Shanghai,China)

Abstract: The floating-point arithmetic provides greater precision and greater dynamic representation indication range, with floating point calculations have become an indispensable part of the program.Floatingpoint adder is the most frequently used floating point arithmetic. Therefore, the performance of floating point adder affecting the entire CPU floating point processing capabilities. In this paper the principlebased floating-point addition, Verilog hardware description language

一种CORDIC算法优化及32位浮点反正切函数FPGA实现

一种CORDIC算法优化及32位浮点反正切函数FPGA实现鲍宜鹏【摘要】通过对反正切函数实现算法的研究,在传统CORDIC算法的基础上,提出了一种以超前进位加法器为基本单元的迭代结构,双时钟输入,完成了反正切函数的ASIC电路设计。

该算法采用TSMC 55 nm工艺,在Synopsys/syn10.12环境中综合实现。

该算法的关键路径由原来的2.9 ns提升至1.3 ns,最高运算频率可以达到769 MHz,即优化后的CORDIC算法比优化前速率提高了2倍多。

%Through the study of algorithms implements of the arctangent function, proposed a hierarchical carry lookahead adder structure as the basic unit of iterations basing on traditional CORDIC algorithms, double clock input, completed the ASIC circuit design of the arctangent function. The algorithm applied TSMC 55 nm process and achieved a comprehensive in Synopsys/syn 10.12 environment. The key way of the algorithm was reduced from 2.9 ns to 1.3 ns, the highest operation frequency is able to reach 769 MHz, the speed of the whole system was twice more than the original design.【期刊名称】《电子与封装》【年(卷),期】2015(000)003【总页数】4页(P22-25)【关键词】CORDIC算法;分层次超前进位加法;反正切函数【作者】鲍宜鹏【作者单位】中国电子科技集团公司第58研究所,江苏无锡 214035【正文语种】中文【中图分类】TN402在导航通信、数字信号处理等许多领域都会大量使用反正切函数进行必要的计算。

基于FPGA的高速浮点加法器的实现

第一作者简介 : 秀芳(97 )女 , 族 , 士 , 授 , 究 方 向: 王 16 一 , 汉 博 教 研 无线通信。 通 讯 作 者 简 介 : 振 龙 ( 9 5 ) 男 , 族 , 士 研 究 生 , 究 方 侯 18 一 , 汉 硕 研 向 : 息 传输 及 处理 。 信

2 浮点加法器的硬件实现过程

的硬 件实 现注入 了新 的活力 。

位、 双精 度 6 4位 。以单精 度 浮点 数 为 例 , 计 了 3 设 2

位 的高 速浮 点加法 器 。

s

— 一 E —

—— —— ——— ÷ ・——— 一M — — ——— —+

文献 [ ] 计 了高速 的 F T 处 理 器 , 内部 正 2设 F1 I 其 是使用 了浮点算 法 单 元 。 由于 其 使用 的是 1 6位 浮 点算 法 , 整个设 计 的精 度 方 面还 有 待 提 高 。文 献 在 [] 3 利用 V ro D ei gH L语 言设 计 了一 种 浮点 加 法 器 , l 系统最 高 时钟频 率达 到 8 MH , 是应 用 在 实 时 信 0 z但 号处理 领 域 , 钟频 率 还有 很 大 的提 高 。文 献 [ 时 4]

Sm S i E进 行 联 合 仿 真 结 果 表 明 , 系统 的运 行 精 度 可 以达 到 1 数 量 级 , 时该 设 计 可 参 数 化 、 作 为 独 立 的 子 系统 应 用 于 其 0 同 可

他 数 字 信 号处 理 领 域 。

关键词

IE 7 4 E E 5

可 编程 逻 辑 门 阵 列

第 l 0卷

第2 5期

21 0 0年 9月

科

学

技

术

与

32位高速浮点乘法器优化设计

集成电路设计与开发n墨i乒mdD目幛l叩m∞IofIc32位高速浮点乘法器优化设计周德金1,孙锋2,于宗光2(1.江南大学信息工程学院,江苏无锡214036;2.中国电子科技集团公司第五十八研究所,江苏无锡214035)摘要:设计了一种用于频率为200MHz的32位浮点数字信号处理器(DSP)中的高速乘法器。

采用修正B∞tll算法与wa‰e压缩树结合结构完成Carrysum形式的部分积压缩,再由超前进位加法器求得乘积。

对乘法器中的4.2压缩器进行了优化设计,压缩单元完成部分积压缩的时间仅为1.47曲,乘法器延迟时间为3.5哪。

关键词:浮点乘法器;Bootll编码;4.2压缩器;超前进位加法器中图分类号:TN332.22文献标识码:A文章编号:1003.353x(200r7)10J0000.04Des咖ofa32.bitIIigh-Speednoa铀g-PoiIltMultiplierzHouDe.jinl,suNFen92,Yuz叽分gua孑(1.删钿m砌nE喈打姗{嗜,瑚t豇l如,SD砒册毙rlg娩‰妙,阢硝2l加36,嘶u;2.77le58山脑凹旆触出地,凹粥,‰i214035,C越眦)Abs仃act:Allig}I-speedmultiplierin200MHz32bitnoating—pointDSP啪8p陀鸵nted.M0d正edb∞tllalgoritllm如dtlleWallacetr∞wem岫edto剐ucetllec盯rys盯epaItialproductto蛐matldc邺r、nect0坞,aca玎ylook-alleadadd盯w∞d鹤ignedtocon、rerttlIe8岫“c缸ryve=cto糟tofinalfom蚍.Theope珀tir唔cycletin抡oftllecoⅡlpre鹪ionuIliti81.47n8by叩tiIIIi五ngthe4—2coⅡ甲r嘲晦。

计算机浮点运算详解深入学习计算机组成原理

深入剖析浮点运算性能优化

04

策略

减少不必要的数据转换和传输延迟

数据重用

避免不必要的数据类型转换

尽量保持数据在运算过程中的类型一致,避免频繁 进行数据类型转换,以减少转换带来的性能开销。

通过缓存最近使用过的数据,减少从主存中 加载数据的次数,从而降低数据传输延迟。

优化数据布局

合理安排数据在内存中的布局,使得访问局 部性更好,减少缓存失效和页面换入换出的 次数。

性能问题

浮点运算通常比整数运算更复杂,需要更多的CPU周期和内存带宽。这可能导致性能瓶颈,特别是在需要大量浮点运 算的应用中。

兼容性问题

不同的计算机系统和编程语言可能采用不同的浮点表示方法和运算规则,这可能导致兼容性问题。例如, 一个系统上的计算结果可能在另一个系统上无法重现。

未来发展趋势预测及建议

• 精度提升:随着计算机硬件和算法的不断进步,未来浮点运算的精度将得到进 一步提升。例如,采用更高精度的浮点数表示方法和更精确的运算算法。

• 性能优化:为了提高浮点运算的性能,未来可能会采用更高效的硬件设计、并 行计算技术和优化算法。例如,利用GPU和TPU等专用硬件加速浮点运算, 以及采用分布式计算等技术提高大规模浮点运算的效率。

进行实验和编程实践

通过编写程序和使用相关工具 进行实验,加深对浮点数运算 的理解和掌握程度。

THANKS

感谢观看

数值积分与微分

利用浮点运算进行数值积分和微 分,可以求解函数的定积分、不 定积分、导数等。

图形图像处理领域应用

01

3D图形变换

02

03

图像滤波与处理

计算机视觉

在3D图形处理中,浮点运算用于 实现各种复杂的图形变换,如旋 转、缩放、平移等。

一种高性能四倍精度浮点乘加器的设计与实现

d e c r e a s e d . A n d b y m a k i n g u s e o f p a r a me t e r i z e d d e s i g n a n d v e r i i f c a t i o n me t h o d o l o g y , t h e c o r r e c t i o n o f t h e Q P F MA i s v e r i i f e d e ic f i e n t l y .

第4 0 卷 第 2 期

Vo 1 . 40

NO . 2

计

算

机

工

程

2 0 1 4年 2月

Fe b r u a r y 2 01 4

Co mp u t e r En g i n e e r i n g

・

开发研究与工程应用 -

一

3 t l t m- g - : 1 0 0 一 3 4 2 8 ( 2 0 l 4 ) 0 2 9 4 _ _ 0 6 文 献l ; i 嘏码: A

HE Ju n, HUANG Yon g - qi n, ZHU Yi ng ( S h a n g h a i Hi g h P e r f o r ma n c e I n t e g r a t e d Ci r c u i t De s i g n C e n t r e , S h a n g h a i 2 0 1 2 0 4 , C h i n a )

中图 分类号: T P 3 6 8 ・ 1

种 高性能四倍 精度 浮点乘加 器的设计 与实现

何 军 ,黄永勤 ,朱 英

( 上海 高性 能集 成 电路设 计 中心 ,上海 2 0 1 2 0 4 )

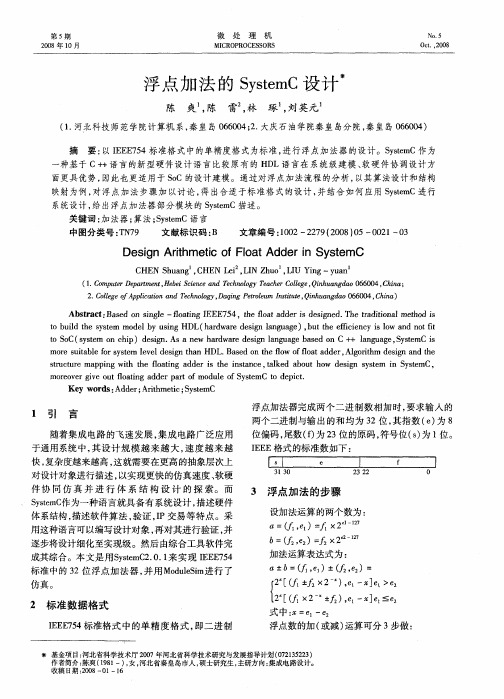

浮点加法的SystemC设计

Abta tB sdo ige一 o£ gI E 7 4 h o £ d e ei e . h aioa m t di Src : ae ns l Ⅱ a n E E 5 ,fe 1a ad r sds d T et df nI eh n i f i r j o s

t b i ess m m d l yuigHD ( ad aed s nl g ae ,u eef i c w adnt i o u dt yt o e b s L hrw I ei n ug ) b th fc n yi l n o f l h e n | g a t ie so t t SC ss m o hp ei . sa e ad aed s nl g ae ae nC+ l g ae Ss m o o ( yt nc i)d s n A w h rw r ei n u g sdo + a ug ,yt C i e g n g a b n e s

mo e s i b e frs se l v l e i t a L. a e n t en w o o t d e , g r h d s n a d te r ut l o y tm e e s h n HD B s d o h o fn a d r Al oi m e i n a d f a t g h

moeVr i u ot ga d r at f d l 0 ytm e i . r0e V ot ai d e r 0 ue f s C t d pc ge n n p mo S e o t

Ke r s Ad e ; i mei ; v tmC y wo d : d r Ar h t S se t c

smc u e ma p n t h ka i g a d r i h n tn e, ak d a o t h w sg s se i y tmC, t tr p i g wih t e f tn d e s t e i sa c tl e b u o de i n y tm n S se

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

!

引言 浮点加减法运算是浮点预算中最常用的操作 !

其中 ! # 表示浮点数 ! 的符号 % $ 表示 % 的指数 部分 !它是一个 6 位的带 2!& 位偏移量 &&0" ! "0" 时 除外 ’ 的无符号数 % " 表示 % 的小数部分 ! 它是一个

浮点加减 法 的 性 能 对 整 个 浮 点 运 算 器 的 性 能 起 到 决定性的作用 " 由于浮点预算包括一系列独立 # 复杂而又费时 的操作 ! 如指数对齐 # 移位 # 尾 数 加 减 # 结 果 的 四 舍 五入及规范化处理等 ! 如果不使用优化技术而顺序 执行上列的步骤 !其时延将无法忍受 " 为此 ! 本文从 算法和结构等多方面考虑 ! 采用了多种优化技术 ! 使本文提出的单精度浮点加法器能达到 ’""()* 的 频率 ! 达到了优化的目的 " 由于文献 +!, 已 经 对 该 浮 点 加 法 器 的 结 构 给 予 了详细的介绍 ! 本文将重点介绍该结构所采用的优 化技术 "

!’ 位的无符号数 " 因此 ! 可以用 7#8&+&$",! " +!!$", 5 来

表示一个单精度浮点数+’," 浮点加法器应以两个标准的浮点数作为输入 ! 在指定运算类型 & 加 或 减 ’ 及 四 舍 五 入 模 式 的 情 况 下 ! 输出一个仍符合 -... 标准格式的结果 "

"#" $%%% 四舍五入模式

8:(09,;0< -> @KFD EBEAC8 LA ECADA>@ B ><ZAW ?ADFX> <G -... V<\EWFB>@ DF>XWA ECAVFDF<> GW<B@F>X E<F>@ B??AC3 ]KA B??AC BVKFAZA? KFXK EACG<C\B>VA =E @< ’""()* =>?AC "326!\ @AVK><W<X[ ^[ =DF>X ZBCF<=D <E@F\F*B@F<> @AVK>F_=AD8 D=VK BD @L< ?B@B EB@K DAEBCB@F<>8 @KCAA EFEAWF>A D@BXAD8 M: A>V<?AC8 CA?=VA? -... C<=>?F>X \<?AD B>? EBCBWWAW ECAGF‘ B??AC A@V3 =’> !39-"< 4W<B@F>X E<F>@ B??AC8 M: A>V<?AC8 %<=>?F>X8 5BCBWWAW ECAGF‘ B??AC

选择出大小操 作 数 ! 并 进 行 指 数 对 阶 移 位 ! 这 些 大 致需要 , 个逻辑级延时 " 第二级执行 23 编码操作 ! 前导零预测 ! 使用 !, 位的并行前缀加法器执行尾 数的相减操作 !共需要 M 个逻辑级 " 在第三级中 !执 行规格化处理 &, 个逻辑级 ’" 综上 !3>DEFG 关键路 径的长度不超过 M 个逻辑级 "

! %! F 0P $N ’

该 方 法 中 !$KO 与 &’( 的 不 同 仅 在 于 当 8H E

)9HG9!: [ ! 且 9! 的 最 低 有 效 位 为 H 时 ! 因 此 ! 在 修 正

结果时 ! 在上述情况下将 9! 的最低位强制为零即 可) 对舍入模式的简化 ! 使得相应的逻辑电路在时 间和面积上都得到相应优化 )

根据式7*: !定义 5 为 (

( 5E/G1 7=: 并行前缀加法器 ! 如 QR%’44B- 或 R6%’44B- ! 可 以同时计算出 5 和 5GH) 则可根据 5 的符号 !选择 & 或 5GH 作为结果 ) 在 $%&’() 中 ! 由于四舍五入可能产生进位 ! 因

此也可以利用并行前缀加法器的上述特性 ! 同时计 算出 .*+, 和 .*+,GH! 最终结果的选择根据四舍五 入部分的进位来决定 )

"!,

微电子学与计算机

!""# 年第 !! 卷第 !" 期

一种快速浮点加法器的设计与优化方法

刘哲

摘

付宇卓

&上海交通大学微电子学院 ! 上海 !"""’" ’ 要 ! 本文提出了一种快速单精度浮点加法器的设计 方 法 ! 重 点 介 绍 了 该 浮 点 加 法 器 所 采 用 的 各 种 优 化 技 术 !

四舍五入的模式决定了浮点运算的精确度!

-...%&/# 规定浮点运算中所用到的 # 种标准四舍

五入模式 ! 它们分别是

125 向零进位 $ 即将最低有效位后的所有位直接

舍去 %

1!5 向最近的高位进 位 &9:;$9<=>? @< :ABCAD@ "

浮点数标准和基本算法 本节介绍浮点数的 -... 标准表示法和基本的 浮点加法运算的算法 "

#%!

流水线划分及时延分析 兼顾到面积和速度的需要 ! 该浮点加法器采用

* 级流水线结构 ! 其详细结构图请见附录 ’" 采 用 文 献 -#/ 中 以 逻 辑 级 为 基 本 单 位 的 时 延 分 析方法. 分别对 3>DEFG 和 H>DEFG 进行分析 " 在 3>DEFG 中 ! 流水线第一级将计算指数差异 !

> 个逻辑级 "

若把这样一个加法器运用到一个浮点 ?6@ 上 ! 在时延 分 析 时 ! 还 需 考 虑 到 加 法 器 外 围 电 路 的 延 时 " 假定有四个通用寄存器可参与浮点运算 ! 则为 从这四个寄存器中作选择 ! 又需要两个逻辑级 " 再 考虑到对于溢出等情况进行处理的监控逻辑 ! 整个 加法器的每级流水线延时不会超过 = 个逻辑级 " 采用 6.31&A.A 公司的 4BA053 81C&0DB- 工具进行 综合 ! 综合的结果表明该浮点加法器的关键路径在

式 ! 即在原操作的基础上加上一个根据舍入模式得 到的插入数值 &6"7 $) 对单精度数 ! 插入的定义如下 (

"F $ NK7E % ! F

& %!!

%>#

0P $% 0P $KZ 7H":

& %!T

$%&’() 的第二级 " !"!

部分压缩编码进行前导零预测 本文引入 !%" 编码及其相关理论来计 算 前 导 零的个数 " 定义 #( 设 !"!##!!##"$$$!$ 为一个 # 位的借位保存 编码串 ! 对它进行 @ 编码得到 $ ! 即 $E@ 7%:F 则 $ 为 一个 #GH 位的借位保存编码串 $&$#$#%HIII%"! 且 )

’!故 # 对齐操作的移位数目至多为 ’$ # 指数差的计算只需抽取最末两位 $ # 不需要进行四舍五入 " 在 H>DEFG 中 ! 或者进行加法 ! 或者进行指数差

异较大的减法 !故

# 最后结果在规格化时至多只需要左移一位 $ # 尾数运算结果始终为正 ! 不需要取反 "

与传统的双数据通道划分方法相比 ! 该结构在

文章编号 ! 2"""%&26" (!""#) !"%"!,-,*

&’()*+ ,+- ./0)1)2,0)3+ 34 , 5,(0 563,0)+* 73)+0 8--’9

Q-; RKA! S; T=U*K=<

&OVK<<W <G (FVC<AWAV@C<>FVD. OKB>XKBF YFB<@<>X ;>FZACDF@[. OKB>XKBF !"""’" /0123’

如双数据通道划分 "’ 级流水线结构 "M: 编码 " 简化的四舍五入模式及并行前缀加法器等 ! 使得该浮点加法器的频 率能够达到 ’""()* ! 能在高性能浮点 NOM 中得到很好的应用 # 关键词 ! 浮点加法器 !M: 编码 ! 四舍五入 ! 并行前缀加法器 中图法分类号 ! )&*+

!! 文献标识码 ! P

!%&

简化的四舍五入模式 根据 S2’8);#<! 将 NOOO 的四舍五入模式简化为

T 种 ! 即 ( 向 零 舍 入 &$U$! 向 无 穷 舍 入 &$N $! 向 最 近 的偶数进位 &$KO $) V OWOK 和 @ X 6B4BD;!< 还通过 引入插入 &03YB8(013 $ 的方法进一步简化了舍入模

#

优化技术 根据以上的分析 ! 本设计采用了一系列的优化 这样划分的优点是 # 在 3>DEFG 中 ! 由于两操作数指数差异不超过

方法 !来降低整个浮点运算的操作时延 " 在结构上 ! 采用优化的双通道方案 ! 并提出 * 级流水线的划分 方法 $ 在算法上 ! 使用 23 编码进行指数差前导零的 预测 ! 采用简化的 四 舍 五 入 模 式 % 带 流 水 线 结 构 的 并行前缀加法器等优化技术 ! 并在细节上尽量增加 并行运算的可能 " 下面将对这些优化技术作详细介绍 " 这里 ! 将 以 !4+"#. $#. %#(. &4+"’. $’. %’( 表示两操作数 !() 表示 将进行的运算 &5 为加 !’ 为减 ’!678 表示采用的四 舍五入的模式 !*+&",. $,. %, ) 表示 - %& 中较大的操作 数 !./&"". $". %") 表示较小的操作数 ! 9:;< 表示 %0 ()