Cadence原理图输入(精选)

cadence使用技巧

点击dsn后,Tools→Generate Part,在Part name中输 入要生成的元件名,点OK确定完成。元件化的原理图当做 元件使用,通常使用频率高的模块可以生成元件来使用。

自动备份设置

Options→Autobackup,设置间隔时间、备份数目和存放目录。

添加原理图库

如果采用现有自创的原理图库,可以右击Library,点Add File, 找到库存放的路径及库名,点打开添加。

未连接管脚处理

→Place→No Connect,在未连接管脚上放置“×”符号。

添加文本

→点击右端的Place text工具栏图标,输入文字内容,点击 Color的下拉菜单,选择喜欢的颜色。然后点击Font下的 Change后,选择brary下的库,按Delete键删除或右击鼠标,选Cut删除。

Capture库

orcad元件列表

capture库

总线连接

→放置总线的命令是Place→Bus或点击右端工具栏图标, 按住shit键可以画出斜线。

总线支线

→Place→Bus Entry可以放置一小段斜线,即总线支线。

第二章Cadence的原理图设计

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:图2-1 启动Design Entry CIS这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

cadence原理图快捷键整理

1. shift+鼠标滚轮 左右移动

2. Ctrl+鼠标滚轮 放大缩小

3. Alt+鼠标滚轮 上下移动

4. 按下鼠标滚轮可任意方向拖动图纸(可以一直保持按下状态或者按一下松开)

15. b : 放置总线 bus

பைடு நூலகம்

16. e : 放置总线管脚

17. g/f : 放置电源和地 g和f两个快捷键的效果是一样的,ground/frame

18. z : 查询本地元件与网上元件

19. w : 放置导线

20. h :水平镜像

10. i : 放大图纸 (zoom in 聚焦,镜头拉近放大物体)

11. o : 缩小图纸 (zoom out扩焦,镜头拉远缩小物体)

12. r : 元件旋转 rotate

13. p : 放置元件 place

14. n : 放置网络标号 number

5. CTRL+鼠标左键 : 元件叠选

6. CTRL+鼠标左键拖动 : 复制该元件,元件标号自动加一

7. ALT+F4 退出当前窗口

8. CTRL+E 编辑元件属性(要先选中)

9. CTRL+Z 撤消上步操作

21. z :上下镜像

22. t : 放置文本

23. j : 放置连接点

24. F6 : 把鼠标变成大的十字光标,方便对齐操作

25. F10 : 跳转到下一页

26. ESC :退出当前命令

注:以上涉及到快捷按键的操作均需要在英文输入法状态下才有效。

Cadence软件学习:绘制原理图

Cadence软件学习:绘制原理图基本操作:1、 Place Part(P):放置元件2、 Place wire(W):连接相连的pin脚3、 Place Auto wire:自动连线4、 Place bus(B):总线连接5、 Place junction(J):交叉点连接,两条wire相交有两种连接关系:连或不连,加J为连6、Place bus entry(E):可以理解为总线入口,有bus必有entry7、 Place net alias(N):相当于wire,用于连接距离远的Pin 脚,仅限于同一page电气连接8、 Place power(F):放置电源9、 Place ground(G):放置地10、 Place off-page connector:类似alias,但alias仅用于同一页面,而off-page用于不同页面之间的电气连接11、Place no connect(X):用于无电气连接的pin脚,不放会报错12、 Place text(T):放置文本常用操作:1、按住Ctrl滚动鼠标滚轮放大缩小原理图(以鼠标指针为中心);直接滚动鼠标滚轮上下移动;按住Shift滚动左右移动2、改变原理图尺寸大小:options->Schematic Page Properties->Page Size3、旋转器件:放置器件前直接按R可旋转,放置后选中按R旋转4、选中单个或者多个器件,按住Ctrl,鼠标左键在选择器件上按住拖动可复制所选器件5、连线时改变连线角度需先按shift键6、元件镜像:选定后V键(垂直)和H键(水平)7、鼠标右键选End mode结束当前操作8、连线时,终点如不是管脚脚,双击结束9、管脚之间不要直接相连,通过线连接以防出错(软件设置不允许连接的方法:Options/Preferences->Miscellaneous->Wire Drag 打钩去掉)10、总线命名规则:后期处理:1、浏览原理图:选中 .dsn , edit->browse可以浏览parts、nets等,主要检查是否有漏掉的信息,双击可以打开原理图并高亮显示所选内容2、元件替换和更新:右键需要修改的元件,选择Replace cache 或Update CacheReplace cache:用于替换Update Cache:用于更新1、 Cleanup Cache:右键Design Cache选择Cleanup Cache 用于检测Design Cache与原理图是否一致,并删除多余的内容2、移动:默认连线与移动元件一同移动,按住Alt 移动仅元件移动3、自动编号:右键.dsn 选Annotate 。

CADENCE应用---HDL原理图+Allegro基本操作

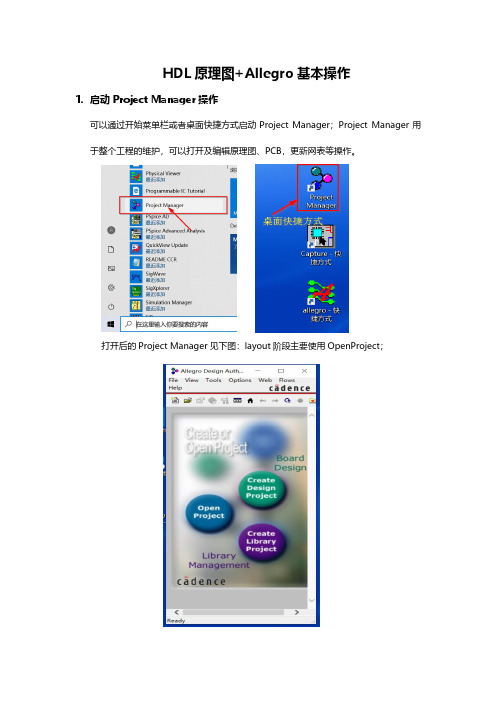

HDL原理图+Allegro基本操作1.启动Project Manager操作可以通过开始菜单栏或者桌面快捷方式启动Project Manager;Project Manager用于整个工程的维护,可以打开及编辑原理图、PCB,更新网表等操作。

打开后的Project Manager见下图:layout阶段主要使用OpenProject;2.原理图与PCB打开操作介绍A.Project Manager默认选择下图所示版本B.点击Project Manager界面中的OpenProject按钮,选择需要打开的工程;C.需要选择的文件为cpm后缀的文件,见下图:D.选择cpm文件后,打开后的Project Manager界面如下图所示:E.说明:①工程需要完整,不能缺失文件,否则打开容易出错;客户提供文件要提供完整的工程文件夹;②PCB需要放在physical文件夹下,这样才能方便后续的同步更新网表及PCB与原理图同步关联;physical文件夹是worklib文件夹的子文件夹;3.更新网表操作HDL更新第一方网表有2种操作:A.直接生成网表,然后在PCB中导入网表不勾选update PCB…,生成的网表在packaged文件夹下;PCB中导入网表操作:如下图,选择HDL格式,Import directory需要网表所在位置;B.第二种方法:直接同步关联,在生成网表的同时对PCB进行更新;在export physical时勾选下图所示“update PCB …”,PCB文件放在physical文件夹下;其中“1”选择的为需要更新网表的PCB文件;“2”为更新网表之后的PCB;建议此处命名和“1”处做区分;点击OK,进行网表更新,直至提示完成为止;更新网表时,不要打开PCB文件;4.原理图和PCB关联操作在Project Manager界面分别打开PCB和原理图文件,此时的PCB和原来图时关联的关系;原理图与PCB抓取器件操作:A.在PCB中启动移动命令;B.切换到原理图界面,选择symbol;如下图,只勾选symbol;C.在原理图中框选器件,被框选的器件会高亮:使用如下图命令进行器件框选;上图所示命令的图标显示如下图,可以将图标调出,放在工具栏,方便使用;D. 关于抓取器件的具体操作:1启动框选命令;2鼠标在原理图适当位置单击一下;3然后移动鼠标,出现一个矩形框,此矩形框随鼠标移动而变化尺寸;4想要框选的器件都在或者大部分都在框内时,单击鼠标左键;5.完成框选,被框选的器件高亮,如下图:6.移动鼠标光标至任意被高亮器件上,单击鼠标中键,此时被框选器件会闪动;7.闪动结束,则PCB中对应器件被选中;此时切换到allegro界面,在PCB上点击一下鼠标左键,则被选中的器件随鼠标移动;E.其他a.高亮器件类似上述操作;b.在原理图中查找器件命令:Ctrl+F;…..。

学习使用Cadence设计原理图

正确 错误

不要在元件引脚上做T型连接, 需引出一段后在分叉!

以下内容很重要!!

1、如果有已验证过的电路,尽量拷贝使用! 2、芯片的design guide,仔细阅读! 3、如果PCB面积够,每个电源脚都接个去耦电容! 4、电容要注意耐压值,尽量大于2倍工作电压! 5、按键部分应有去抖电路! 6、对关键信号,需要预留测试点,以便调试使用! 7、最好留有GND测试点,以便连接示波器探头! 8、最后最重要,尽量使用公司已有元器件!

注: 如果电阻额定功率和精度有特殊要求,必须标注功率和精度; 特殊要求的标注和阻值在同一栏中,各项标注以横线隔开,但其中的字母必须大写,如

“10k-1%-1/2W”, 精度要求在前、额定功率要求在后。

电容标称要求

≤1pF ≤999pF ≤999nF

≥1uF

以小数加p表示,

例如 0.47pF ;

整数表示为XXp, 例如 100pF,470pF;

遵循统一的要求 能提高设计图纸的 可读性、方便维护

减少错误!

电阻标称要求

≤1Ω ≤999Ω

≤999K

≥1M

以小数表示为0RXX, 例如 0R47,0R033 ; 整数表示为XXR, 例如 100R,470R; 包含小数表示为XRX, 例如 4R7,4R99,49R9 ; 整数表示为XXK, 例如 100K,470K; 包含小数表示为XKX, 例如 4K7,4K99,49K9 ; 整数表示为XXM,out out

总线连接

省时 省力 简单 易懂

必要的电气连接 处于不同的页面上

接

终于完成器件摆放和电气连接

完事了, 大功告成! ??

添加或修改 Footprint 信息

添加或修改 Footprint 信息

Cadence学习笔记1__原理图

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

点击左侧工具栏make图标 ,所有的横线和竖线都变成粉红色的,这就生成了一个表格,鼠标右击选择Tag Pin Name,在引脚名这一列点一下,会在这一列最上面出现“Name”,同样的,右击选择TagPin Number,在引脚编号这一列点一下,会在这一列最上面出现“Num”,如果放错了,比如说该放Name的地方放成了Num,可以在放Num之后再点一次,Num就消失了,产生的结果如上图右。

cadence原理图设计实例教程

器件放置

• 也可以按下步骤放置uA741:

➢ 执行P1ace/Part命令 ➢ 在 Part中输“ *741* ” , ➢ 点击Part Search, ➢ 点击Begin Search, ➢ 在Library 库中寻找到

uA741/opamp.olb ➢ 单击“OK” ➢ 执行前面的步骤,单击

“OK”,放置器件,断开放 置

放置电容符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中选

择“ANALOG” ➢ 在 “Part”列表框中选择

“ C” ➢ 单击“OK” ➢ 将电阻C移至合适位置,

(按键盘中的R键,器件旋 转)按鼠标左键放置 ➢ 按ESC键(或鼠标右键点 end mode)结束绘制元器

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有 定义的管脚封装图,出现MAXECO提示说明,确定

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有定义的管脚封 装图, 点Link existing footprint to component来查找连接封装。

Place net name

放置分页图纸间的接口

原理图绘制

(二) 原理图绘制

以声控开关为例(电源是直流12V,负载为发光二极管)见下 图:

放置集成块运放uA741

• 执行P1ace/Part命令 • 在 “Libraries”列表

框中选择“OPAMP” 库 • 在 “Part”列表框中 选择“uA741” • 单击“OK” • 将集成块移至合适位 置,按鼠标左键 • 按ESC键或鼠标右键点 end mode以结束绘 制元器件状态

原理图输入设计方法

找到平衡性能和成本的最 佳方案,以实现可行的设 计。

工具和软件准备

选择适合的设计软件和工具,如EDA软件和CAD工具,以提高效率和准确性。

元器件和材料收集

识别和收集所需的电子元器件和材料,确保可用性和符合设计要求。

电路图和连接方式

电路图设计

根据需求和规格绘制高质量的电 路图。

连接方式选择

选择最佳的连接方式,以确保电 路正常工作。

原理图输入设计方法

原理图输入是电路设计的关键步骤之一。通过以下方法实现高效而准确的原 理图输入。

确定目的和需求

明确原理图输入的目标和要求,如电路功能、信号处理需求和系统互联等。

技术规格和要求

1 高性能要求

考虑信号质量、噪音和功 耗等技术要求。

Байду номын сангаас

2 符合标准

3 成本效益

确保设计符合国际和行业 标准,如EMC和安全要求。

焊接技术

了解和应用适当的焊接技术,确 保电路连接牢固可靠。

设计优化和检查

针对电路功能和性能进行优化和检查,以满足设计目标和规格要求。

电路仿真和调试

使用仿真工具模拟电路行为,进行性能评估和故障排除。

电路性能测试和评估

通过测试和评估,验证电路的性能和可靠性,确保其符合设计要求。

[笔记]CadenceConceptHDL原理图输入

![[笔记]CadenceConceptHDL原理图输入](https://img.taocdn.com/s3/m/036686030a4e767f5acfa1c7aa00b52acfc79c10.png)

Allegro Design Entry HDL原理图输入方式00孙海峰00Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL 环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

00接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

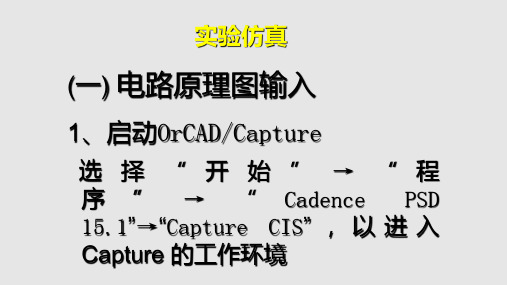

00一、进入Design Entry HDL用户界面00进入HDL原理图输入界面的步骤如下。

001、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框002、进入产品界面,弹出Open Project对话框00其中Open Recent用以打开最后运行的项目;0Open Open an Existing Project用以打开一个已有的项目;00Create a New Project用以新建一个项目。

003、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保00存位置,如下图。

004、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库005、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可00以填写新建项目名称,也可以选择已有元件,对其进行修改。

06、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

007、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,00并出现原理图工作界面。

00其中:(1)标题栏——显示文件所在路径和文件名称;00(2)菜单栏——项目所有相关操作的集合;00包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、00模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗00口菜单和帮助菜单。

Cadence原理图输入

Instance放置

点击放置按钮 ; 从Library Browser – Add Instance窗口 选择元件,View选择symbol; 调整元件姿态 输入元件属性 单击鼠标放置

Wire连接

单击wire(narrow)按钮 鼠标单击选中起始点; 再点击鼠标选中第二点; 双击——画出终点; Wire(wide)的绘制方法与此相同,二者无 本质区别。

建库

选择CIW中的菜单:File->New->Library… 指定库名、路径和工艺文件

创建基本单元

选择CIW中的File->New->Cell View… 输入单元名、ViewName、所属库

电路图组成

Instance Wire Wire name Pin 以上元素的复制、移 动、删除操作相 同,属性编辑也相 同。

节点悬空 输出短路 输入开路

生成symbol

选择COMPOSER的菜单:Design->Create Cellview->From Cellview… 填入库名、单元名 设置pin名称与位置

逻辑输入

调用基本单元:

基本单元往往由厂商或系统提供。 可以调用其它库中的单元(不能循环调用) 本层电路调用的是底层单元的symbol

上层单元与基本单元没有本质区别都是只包含下层的symbol信息下层单元是只读的层次原理图输入下层单元改变后要重新进行checksave被调用单元的接口改变后要重新生成symbol上层单元才会更新

Cadence原理图输入

清华大学微电子所 2002年8月

Cadence的文件组织

设计库

工艺库(techfile)

基本单元有的含有参数有的是固定属性的。 电气互连:wire(narrow)/wire(wide),wire Name

Cadence学习笔记1__原理图

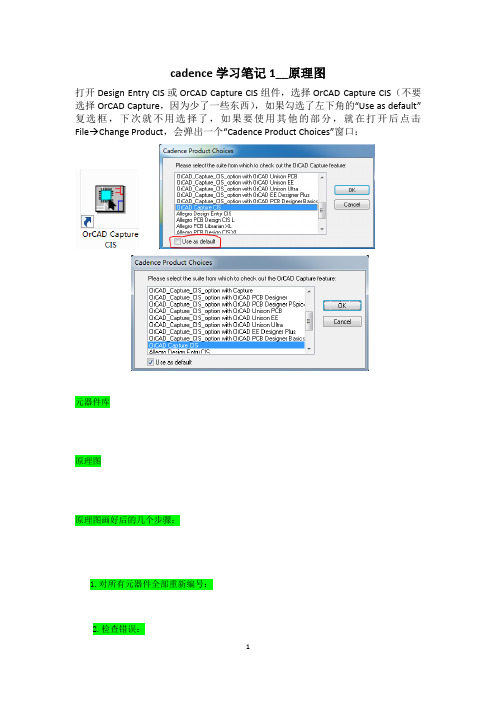

cadence学习笔记1__原理图打开Design Entry CIS或OrCAD Capture CIS组件,选择OrCAD Capture CIS(不要选择OrCAD Capture,因为少了一些东西),如果勾选了左下角的“Use as default”复选框,下次就不用选择了,如果要使用其他的部分,就在打开后点击File→Change Product,会弹出一个“Cadence Product Choices”窗口:元器件库File→New→Library新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是New Part From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCB Footprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

中间的虚线框是这个元件的区域,右边会有一个工具栏,画直线、方框、圆、曲线,也可以输入一些字符,或者点放置一组引脚,放置结束后鼠标右击选择End Mode或按键盘左上角Esc键使命令结束,放置一组引脚的时候,还可以设置引脚的类型,比如输入、输出、双向、电源等等,这个没有区分电源和地,电源和地都是power型的,现在输入下面的几个数字,线型都是默认的Passive,引脚间距Pin Spacing设为1,点击ok,放置好后成为下面的样子,有些部分不需要显示,双击空白处弹出一个属性对话框,虚框里面的数字是PinName,虚框外面的数字是PinNumber,如果可视属性改成False就不显示了。

如果想改变其中一个引脚的引脚名、引脚编号、引脚类型,选中该引脚,右击选择Edit Properties,或者双击该引脚,如下图:画直线的时候,这里默认是按照栅格点为最小单位的,可以改变这种限制,画出任意长度任意角度的线,在工具栏Options Grid Display中,不要勾选Pointer snap to grid就可以了,记得画完想要的任意直线后,再将这里勾选,这是一个好习惯,可以让画出的线更规则整齐。

Cadence教程(D422)

规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为键盘功能键;“单击"指鼠标左键按下一次。

实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法.[1]启动IC Design 软件:首先,登陆Linux,在username文件夹中建立一个你命名的文件夹,然后在Terminal 窗口中进入这个文件夹,在该文件夹目录下输入:icfb&,(这样,你在cadence 中做的一切工作都会自动保存在这个文件夹中,如果直接icfb&的话,会导致你的工作成果,例如:电路图、仿真结果等,会在/home中保存,影响其他人的使用)[2]建立新库、新单元以及新视图(view):首先,输入icfb&后,出现下图窗口在图中CIW窗口中依次打开:Tools—>Library Manager,出现下图窗口:在图中窗口中依次打开:File—〉New—〉Library,出现下图窗口:输入Library Name:test,然后点OK。

(注意下面的保存路径就是你第一步建立的文件夹)出现下一个窗口:选中Attach to an existing techfile,然后OK.出现下一个窗口:选中右下方Technology Library:chrt35dg_SiGe,然后OK.下面我们来画一个nand2电路。

选中左侧的test,在Library Manager 窗口,File—〉New—〉Cellview,如下图:在弹出的“Create New File"窗口Cell Name栏中,nand2 Tool栏中,选Composer-SchematicOK,如下图[3]添加元件(实例instance)在弹出的“Virtuos o Schematic Editing:…”窗口中,左边为工具栏,选instance 图标(或i)单击“Add instance”窗口Library栏最右侧Browser,弹出“Library Browser—…”窗口,Library选chrt35dg_SiGe,Cell选nmos_3p3, View选symbol鼠标回到“Add instance”窗口,Model name栏:nmos_3p3, width(Total Width):3。

Cadence_电原理图输入简易使用手册

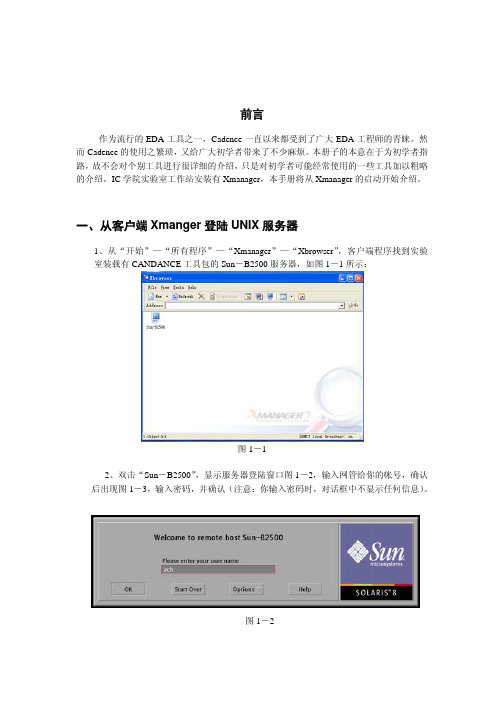

Cadence 电路编辑 简易使用手册东南大学IC学院实验室2005年11月前言作为流行的EDA工具之一,Cadence一直以来都受到了广大EDA工程师的青睐。

然而Cadence的使用之繁琐,又给广大初学者带来了不少麻烦。

本册子的本意在于为初学者指路,故不会对个别工具进行很详细的介绍,只是对初学者可能经常使用的一些工具加以粗略的介绍。

IC学院实验室工作站安装有Xmanager,本手册将从Xmanager的启动开始介绍。

一、从客户端Xmanger登陆UNIX服务器1、从“开始”—“所有程序”—“Xmanager”—“Xbrowser”,客户端程序找到实验室装载有CANDANCE工具包的Sun-B2500服务器,如图1-1所示:图1-12、双击“Sun-B2500”,显示服务器登陆窗口图1-2,输入网管给你的帐号,确认后出现图1-3,输入密码,并确认(注意:你输入密码时,对话框中不显示任何信息)。

图1-2图1-3如果你输入的帐号密码正确,经过服务器确认后,你就远程登陆到服务器上了(显示图1-4)。

图1-4二、启动Candence在屏幕空白处点击鼠标右键并如图2-1选择“hosts”—“Terminal Console”;图2-1出现Console对话窗口图2-2,图2-2输入icfb&并回车就运行Candence了;运行Candence后就会出现CIW窗口,图2-3;图2-3三、库文件的管理3.1建立自己的工作库启动了Cadence后,就可以利用File菜单建立自己的工作库,点击CIW窗口上的File 菜单,选定其中的New lib项,弹出如图3-1所示的对话框;图3-1输入库名并选择相应的工艺库,然后选择ok,这时在CIW的显示区会出现如下提示:Created library "mylib" as "/space/home/zch/mylib"!3.2在库中生成自己所需的单元新建的库是一个空的库,里面什么也没有,用户可在库中生成自己所需的单元。

Cadence16.5学习笔记之(一)—器件库、原理图

Cadence16.5学习笔记之(一)—器件库、原理图Cadence16.5学习笔记之(一)—器件库、原理图一、简单快捷键R—旋转器件方向(选中时)V—元件的镜像(水平)H—元件的镜像(竖直)F—放置电源G—放置地W—放置连线J—放置节点N—放置网络标号T—放置文本备注(Ctrl + Enter:换行)B—放置总线X—放置电器不连接F4—自动放置线,一直按一直放。

元件的复制:Ctrl + C或按住Ctrl,拖动元件即可。

放置全局网络标号(级联多个原理图):Place—Off-Page Connector放置线、总线时,任意角度走线—按住Shift键,再走线。

二、查找元件、网络连接等对整个工程、或单个的页面进行如下类似操作。

Edit->Browse->Parts:原理图画好了,选中工程,检查、查找定位器件Edit->Browse->Nets:网络连接,对于检查电源连接有帮助Edit->Browse->Off-Page Connector:显示工程中所有,原理图页面之间的网络连接(即归纳显示出所有全局网络标号)Edit->Browse->DRC Markers:DRC检查,显示出DRC电器检查的错误。

(删掉这些错误:Tools->Designe Rules Cheak->Yes->Action->Delete existing DRC marker->Yes)Ctrl + F:搜索定位元件、网络,如在PCB布局、布线时(勾选)。

以下类型选项:Parts:查找元件Nets:查看网络连接Power/GND:查看电源、地的网络连接Flat Nets:查看电源、地的网络连接(功能更强大)三、元件的更新或替换选择工程对话框中的File ->Design Cache->右键->Replace Cach->....->是否保留元件的遗留属性,可以将封装更新过来同样的操作,如果器件库中器件属性有改动,则更新元件(但不能将封装更新过来):File ->Design Cache->右键->Updata Cach四、选中元件1、单个选中、Ctrl + 选中元件、区域选中(整体移动),移动时电气连接是存在的,如果按住Alt再移动,则电气连接断开。

Cadence新建原理图工程

原理图工程的建立1、打开OrCAD Capture CIS打开OrCAD Capture CIS弹出一个Cadence Product Choices对话框,选择OrCAD Capture CIS(比Capture CIS功能强大)点击OK。

2、新建工程File-New-Project。

选择Schematic给工程取一个名字(最好为纯英文、数字。

而且随后的PCB文件名称需与原理图的名称一致,否则不能成功地从PCB中回注编号),选择保存路径。

这里也可以选择PC Board Wizard,不知道两者有什么区别。

3、创建元件库file -> new ->library,元件库被自动加入到工程中4、放置元器件cadence原理图库在\Cadence\SPB_16.6\tools\capture\library这个路径下面。

放置元器件,快捷键P,输入原器件名,enter放置。

(封装名要与库中相同)。

5、重新编号对原理图重新编号:选.dsn 文件,tool->annotate弹出annotate 对话框,其中把Action 这一项先设置为Reset part reference to“?”确定。

然后再重来一次Action选择Incremental reference update,确定。

即先取消所有索引编号,再重新编号。

6、规则检查回到.opj窗口,选中.dsn-SCHEMA TIC1下的原理图文件,Tools-DRC进行DRC规则检查。

7、生成网表选中.dsn文件,Tools-create Netlist(有时生成错误可能是有元器件未导入封装)。

原理图技巧1、鱼眼功能:点击小眼睛,再按Q键2、原理图文件夹的创建鼠标选择.dsn 文件,选design –〉new schematic 或鼠标右键-> new schematic。

原理图文件的创建选择原理图文件夹,选design –〉new schematic page 或鼠标右键->new page。