System block diagram(Main)

机械手的系统工作原理及检测传感装置构成的总结与分析

机械手的系统工作原理及检测传感装置构成的总结与分析1.引言1. Introduction近20年来,气动技术的应用领域迅速拓宽,尤其是在各种自动化生产线上得到广泛应用。

电气可编程控制技术与气动技术相结合,使整个系统自动化程度更高,控制方式更灵活,性能更加可靠;气动机械手、柔性自动生产线的迅速发展,对气动技术提出了更多更高的要求;微电子技术的引入,促进了电气比例伺服技术的发展。

现代控制理论的发展,使气动技术从开关控制进入闭环比例伺服控制,控制精度不断提高;由于气动脉宽调制技术具有结构简单、抗污染能力强和成本低廉等特点,国内外都在大力开发研究。

Over the past 20 years, the application of pneumatic technology fields expand rapidly, especially widely used in all kinds of automatic production line. Electrical programmable control technology combined with pneumatic technology, automation degree higher, the whole system control method is more flexible, more reliable performance; Pneumatic manipulator, the rapid development of flexible automatic production line of pneumatic technology is put forward more higher requirement; The introduction of microelectronics technology, promote the development ofelectric proportional servo technology. Pneumatic technology from the development of modern control theory, the switch control in closed loop proportional servo control, improving control precision; Because the gas artery width modulation technique has simple structure, strong ability to resist pollution and low cost etc., are vigorously develop research at home and abroad.2.气动技术发展状况及优缺点2. The pneumatic technology development status and the advantages and disadvantages气动技术是一门正在蓬勃发展的新技术,气动元件是气动技术中最重要的组成部分,用气动元件组成的传动和控制系统己广泛应用于国民经济各部门的成套设备和自动化生产线上。

主板架构及硬体知识

如果是Intel chipset, 因為產品種類多, 為避免衝突, 則不一定會在第一個字, 如 845 系列早期Intel 內部稱呼為Brookdale, 我們就取P4'B'. 另一個865系列 (Springdale), 因為不可能取名P4„S‟, 這樣會和SIS的機種 衝突, 於是取第二個字'P', 就是P4P800系列. 875則因為原名Canterwood, 所以取'C'叫作P4C800系列. 915系列(Grantsdale)就是P5GD1, 925X(Alderwood)就是P5AD2. 至於其他3rd party的chipset則因為機種數較少, 都直接取公司名, 如P4S800 (SIS), P4V8X-X (VIA), K8N (Nvidia), P4U800-X (ULI).

Socket 754是2003年9月AMD64位桌面平台最初发布时的CPU接 口,目前采用此接口的有低端的Athlon 64和高端的Sempron,具有754 根CPU针脚。

第二部分: CPU辨别 Socket 939 Socket 939是AMD公司2004年6月才推出的64 位桌面平台接口标准,目前采用此接口的有高端的 Athlon 64以及Athlon 64 FX,具有939根CPU针脚。

第一部分

第四個字以後常常接了數字, 有時是代表FSB, 有時是DDR的速度, 有時 是AGP的速度, 不一定會是哪一個,原則是先考慮FSB, 如果沒啥特別再 考慮AGP, 最後才是DDR速度.如P4P800, P4C800, P4S800, P4V800-X 都代表support FSB800. 再來是8X, P4V8X-X, A7V8X-X, 因為他們的FSB都沒啥特別的或規格 不夠新潮(如次一級的FSB533), 就會退而求其次 還有些機種是以DRAM的速度命名, 如P4S133, P4S333,A7V266, A7S266-VM, ...這是因為他們的FSB, AGP速度都不是最新規格, 所以用 DRAM速度來區分. 之外還有很多特例, 如P4V880, 是因為chipset 名稱叫作PT880, 並非support FSB880.A7V600, 是因為chipset叫KT600,

直流润滑油泵控制箱中英文说明书(操作说明书)

JY-ZK IntelligentJY-ZK智能型DC MotorControl Cabinet直流电机控制箱Operation Manual使用说明书Shaanxi Jinyuan Automation Technology Co., Ltd.XX金源自动化科技XX一、Overview概述JY-ZK Intelligent DC motor control cabinet lubricating products are aimed at generating power plant system design a new type of lubricant replacement products, mainly used for steam turbine and generator of the main bearings, thrust bearing and the disk devices to provide lubricating oil vehicle control, as well as the generator seal oil system provides oil to ensure the safe operation of the pressure of the oil control. Generator control system equipment lubricants usually are:lubricating oil tank, main oil pumps, AC lubricating oil pump (#1 machine 2 Units), Oiler,and Oil cooler, emergencyDC pumps, jacking oil pumpsystem, oil-fume separatedevices andpurifyingSystem and so on. In normal operation, all the lubricant oil supply from the main oil pump. When the main pump failure resulted in reduced a certain value, AC, DC lubrication pump automatically linkage.JY-ZK智能型直流润滑电机控制箱系列产品是针对发电厂发电机润滑油系统设计的新型换代产品,主要用于汽轮机和发电机各主轴承、推力轴承和盘车装置提供润滑油的控制,以及对发电XX封油系统提供油源,确保系统平安运行的压力油控制。

sobel算子图像边缘检测研究外文翻译

Real-time FPGA Based Implementation of ColorImage Edge DetectionAbstract—Color Image edge detection is very basic and important step for many applications such as image segmentation, image analysis, facial analysis, objects identifications/tracking and many others. The main challenge for real-time implementation of color image edge detection is because of high volume of data to be processed (3 times as compared to gray images). This paper describes the real-time implementation of Sobel operator based color image edge detection using FPGA. Sobel operator is chosen for edge detection due to its property to counteract the noise sensitivity of the simple gradient operator. In order to achieve real-time performance, a parallel architecture is designed, which uses three processing elements to compute edge maps of R, G, and B color components. The architecture is codedusing VHDL, simulated in ModelSim, synthesized using Xilinx ISE 10.1 and implemented on Xilinx ML510 (Virtex-5 FX130T) FPGA platform. The complete system is working at 27 MHz clock frequency. The measured performance of our system for standard PAL (720x576) size images is 50 fps (frames per second) and CIF (352x288) size images is 200 fps.Index Terms—Real-time Color Image Edge Detection, Sobel Operator, FPGA Implementation, VLSI Architecture, Color Edge Detection ProcessorI. INTRODUCTIONHigh speed industrial applications require very accurate and real-time edge detection. Edge detection in gray images does not give very accurate results due to loss of color information during color to gray scale image conversion. Therefore, to achieve desired accuracy, detection of edges in color images is necessary. The main challenge for real-time implementation of color image edge detection is in processing of high volume of data (3 times as compared to gray images) within real-time constraints. Therefore, it is hard to achieve real-time performance of edge detection for PAL sizes color images with serial processors. Due to inherent parallelism property, FPGAs can deliver real-time time performance for such applications. Furthermore, FPGAs provide the possibility to perform algorithm modifications in later stages of the system development [1].The main focus of most of the existing FPGA based implementations for edge detection using Sobel operator has been on achieving real-time performance for gray scale images by using various architectures and different design methodologies. As edge detection is low-level image processing operation, Single Instruction Multiple Data (SIMD) type architectures [2] are very suitable for edge detection to achieve real-time performance. These architectures use multiple data processing elements and therefore, require more FPGA resources. The architecture clockfrequency can be improved by using pipelining. A pipelined architecture for real-time gray image edge detection is presented in [3]. Some computation optimized architectures are presented in [4, 5]. Few more architectures for real-time gray image edge detection are available in [6 - 11]. In [12, 13], the architectures are designed using MA TLAB-Simulink based design methodology.In this paper, we show that real-time Sobel operator based color image edge detection can be achieved by using a FPGA based parallel architecture. For each color component in RGB space, one specific edge computation processor is developed. As Sobel operator is sliding window operator, smart buffer based Memory architecture is used to move the incoming pixels in computing window. The specific datapaths are designed and controller is developed to perform the complete task. The design and simulation is done using VHDL. The design is targeted to Xilinx ML 510 (Virtex –5 FX130T) FPGA platform. The implementation is tested for real world scenario. It can robustly detect the edges in color images.The rest of the paper is organized in the following way . In section 2 we describe the original Sobel operator based edge detection algorithm. We show, in section 3, the customized architecture for algorithm implementation and how each stage works. In section 4, practical tests are evaluated and synthesis results are shown taking into account system performance. Finally conclusions anddiscussions are presented in section 5.II. EDGE DETECTION SCHEMEIn this section the used algorithm is briefly described, for a more detailed description we refer to [14, 15]. The Sobel operator is widely used for edge detection in images. It is based on computing an approximation of thegradient of the image intensity function. The Sobel filter uses two 3x3 spatial masks which are convolved with the original image to calculate the approximations of thegradient. The Sobel operator uses two filters Hx and Hy.⎥⎥⎥⎦⎤⎢⎢⎢⎣⎡---=101202101X H (1)⎥⎥⎥⎦⎤⎢⎢⎢⎣⎡=1211001-2-1-y H (2)These filters compute the gradient components across the neighboring lines or columns, respectively. The smoothing is performed over three lines or columns before computing the respective gradients. In this Sobel operator, the higher weights are assigned in smoothing part to current center line and column as compared to simple gradient operators. The local edge strength is defined as the gradient magnitude given by equation 3.()22,Hy Hx y x GM += (3)This equation 3 is computationally costly because of square and square root operations for every pixel. It is more suitable computationally to approximate the square and square root operations by absolute values.()Hy Hx y x GM +=, (4)This expression is much easy to compute and still preserves the relative changes in intensity (edges in images).This above mentioned scheme is for gray scale images. For color images (RGB color space) this scheme is applied separately for each color component. Final color edge map of color image is computed by using the edge maps of each color component [16].)(B Edge or G Edge or EdgeR ColorEdge (5)III. PROPOSED ARCHITECTURETo detect edges in real-time in PAL (720x576) size color images, dedicated hardware architecture is implemented for Sobel operator based edge detection scheme. Fig. 1 shows the conceptual block diagram of complete system. The hardware setup includes a video camera, a video daughter card, and FPGA board. The video output of camera connects to Digilent VDEC1 Video Decoder Board which is interfaced with Xilinx ML510 (V irtex –5 FX130T) board using Interface PCB. Display Monitor is connected to the board using DVI connector. The video signals are decoded in Camera Interface Module. The output RGB data of camera interface module is applied to edge detection block. The edge detected output from the Edge Detection Block is displayed on the display monitor using DVI controller. The camera interface module also generates video timing signals which are necessary for proper functioning of edge detection block and DVI controller. A more detailed description of this Camera Interface Design can be found in[17].Figure 1. Complete System Block DiagramFig. 2 shows the basic block level data flow diagram for computation of edges in color images using Sobel operator. The goal is to perform edge detection three times, once each for red, green, and blue, and then the output is fused to form one edge map [16]. There are mainly four stages. First stage is Buffer Memory stage. In this stage, the three color components are separated andstored in three different memories. The second stage is gradient computation stage. In this stage the gradient is computed for each color component by adding absolute values of horizontal and vertical gradients. In third stage, the edge map is computed for each color component by comparing the gradient values with threshold. Final edge map is computed by combining the edge maps of each color components in stage four.Figure 2. Edge Detection in Color Images using Sobel OperatorThe streaming data processing cannot be used because the edge detection using Sobel operator algorithm is window based operation. Therefore, input data from camera is stored in on-chip memory (BRAM and Registers) before processing it on FPGA. The Sobel edge detection logic can begin processing as soon as two rows arrived in Buffer Memory. The Smart Buffer based Buffer Memory architecture [18] is used in the proposed Sobel operator based color edge detection implementation for data buffering. This approach (Fig. 3) works if one image pixel is coming from camera interface module in one clock cycle. The pixels are coming row by row. When buffers are filled, this architecture provides the access to the entire pixel neighborhood every clock cycle. The architecture places the highest demand on internal memory bandwidth. Because modern FPGA devices contain large amount of embedded memory, this approach does not cause problems [19]. The length of the shift registers depends on the width of input image. ForPAL (720x576) size images the length of FIFOs is 717 (i.e. 720 - 3). For CIF (352x288) size images, it is 349 (i.e. 352 – 3).Figure 3. Sliding Window Memory Buffer ArchitectureThe absolute values of gradient Hx and Hy for pixel data P2,2 is given by following expressions.())())*21333123,21,13,1,,,((P P P P P P Hx -+-+-= (6)())())*23,1332,12,31,11,3P P P P P P Hy -+-+-=,(( (7)The processing modules architectures for computing these horizontal and vertical gradients for each color components are shown in Fig. 4. Both the architectures are same except the inputs applied to them at a particular time. Each processing module performs additions, subtractions, and multiplication. The multiplication is costly in digital hardware but multiplication by 2 is easily achieved by shift operation.The complete architecture (Fig. 5) uses three processing elements in parallel (each for R, G , and B color components). The data coming from camera interface module is 24-bit RGB data. Incoming data is separated in three color components R, G , and B. Each color component data is of 8-bit (i.e. any value from 0 to 255). Three smart buffer based Sliding Window Memories are used to store two rows of the three color components. Each memory uses two First-in First-out (FIFO) shift-registers and 9 registers. The width of FIFOs and registers is 8-bit. Therefore, in total 6 FIFOs and 27 registers are required for designing Sliding Window Buffer Memory for RGB color image edge detection architecture. The designing of FIFOs using available registers in FPGA occupies large area in FPGA. Therefore, available Block RAMs on FPGA are used for designing the FIFOs. This resulted in efficient utilization of FPGA resources.Figure 4. Gradient Hx and Hy Computation Module ArchitecturesFor detecting edge in PAL (720x576) size color images, it takes 1440 (720x2) clock cycles to fill the two rows of image data in buffer memory. After this, in every clock cycle, each color component (R, G , and B) of new pixel is moved in their respective computing window (consists of 9 registers). The available 9 pixels in computing window (P1,1, P1,2, P1,3, P2,1, P2,2, P2,3, P3,1, P3,2, P3,3) are used for computing the Hx and Hy gradient values. These are computed according to equations 6 and 7 by using the processing module architectures shown in Fig 4. The approximate magnitude of the gradient is computed along each color component by adding the absolute values of Hx and Hy. After this, the approximate gradient of each color component is compared with a user defined threshold value. If the approximate value of gradient is more than the user defined threshold, the comparator output for that color component is 1 else it is 0. Theoutputs of all three comparators (R, G, and B) are finally fused to find the final edge map. The final edge map is computed by ORing the Edge Map outputs of each color component. It requires one three input OR gate. If the final edge map output is one, the each color component value is set to 11111111 else it is set to 00000000. These values are used by DVI controller to display the result on display Monitor.Figure 5. Complete Architecture for Color Image Edge Detection using Sobel OperatorIV. RESULTSThe proposed architecture is designed using VHDL and simulated in ModelSim. Synthesis is carried out using Xilinx ISE 10.3. Final design is implemented on Xilinx ML510 (Virtex–5 FX130T) FPGA board. It utilizes 294 Slice Registers, 592 Slice LUTs, 206 FPGA Slices, 642 LUT Flip Flop Pairs, 116 Route-thrus and 3 Block RAMS. The synthesis results (Table I) reveal that the FPGA resources utilized by proposed architecture are approximately 1% of total available resources. The FPGA resource utilization table is only for proposed color image edge detection architecture (i.e. buffer memory, gradient computation, edge map computation) and excludes the resources utilized by camera interface and display logic. The measured performance of our system at 27 MHz operating frequency for PAL (720x576) size images is 50 fps (frames per second), CIF (352x288) size images is 200 fps and QCIF (176x144) size images is 800 fps. PAL and CIF images are most commonly used video formats. Therefore, implemented system can easily detect edges in color images in real-time.TABLE I. SYNTHESIS RESULTSFigure 6. Input Color Image and Output Edge Detected ImageFigure 7. Input Color Image and Output Edge Detected ImageFigure 8. Input Color Image and Output Edge Detected ImageFigure 9. Complete SystemIn Fig. 6-8, the input PAL (720x576) size color test images taken from camera and respective output edge detected images produced by proposed architectures are shown. Fig. 9 shows the complete system. The images are captured by using Sony EVI D70P analog camera, processed by designed VLSI architecture running on FPGA, and displayed on monitor.V. CONCLUSIONIn this paper, the hardware architecture for Sobel operator based color image edge detection scheme has been presented. The architecture used approximately 1% of total FPGA resources and maintained real-time constraints of video processing. The system is tested for various real world situations and it robustly detects the edge in real-time with a frame rate of 50 fps for standard PAL video (60 fps for NTSC video) in color scale. The speed could be further improved by adding pipelining stages in gradient computation modules at the expense of increasing FPGA resources usage. The Xilinx ML510 (Virtex-5 FX130T) FPGA board is chosen for this implementation due to availability of large number of FPGA resources, Block RAMs, and PowerPC processor (for hardware-software co-design) so that same board can be used to implement other complex computer vision algorithms which make use of edge detection architecture. The proposed architecture is very suitable for high frame rate industrial applications. The future work will look at the use of this architecture for finding the focused areas in a scene for surveillance applications.A CKNOWLEDGMENTThe authors express their deep sense of gratitude to Director, Dr. Chandra Shekhar, forencouraging research and development. Also the authors would like to express their sincerethanks to Dr. AS Mandal and Group Leader, Raj Singh,for their precious suggestions in refining the research work. Authors specially thank Mr. Sanjeev Kumar, Technical Officer, for tool related support. We thank to reviewers, whose constructive suggestions have improved the quality of this research paper.REFERENCES[1] H. Jiang, H. Ardo, and V. Owall (2009), A Hardware Architecture for Real-Time Video Segmentation Utilizing Memory Reduction Techniques, IEEE Transactions on Circuits and Systems for V ideo Technology, vol. 19, no. 2, pp. 226–236.[2] R.L. Rosas, A.D. Luca, and F.B. Santillan (2005), SIMD Architecture for Image Segmentation using Sobel Operators Implemented in FPGA Technology, In Proceedings of 2nd International Conference on Electrical and Electronics Engineering, pp. 77-80.[3] T.A. Abbasi and M.U. Abbasi (2007), A Novel FPGA-based Architecture for Sobel Edge Detection Operator, International Journal of Electronics, vol. 94, no. 9, pp. 889-896, 2007.[4] Z.E.M. Osman, F.A. Hussin, And N.B.Z. Ali (2010a), Hardware Implementation of an Optimized Processor Architecture for Sobel Image Edge Detection Operator, In Proceeding of International Conference on Intelligent and Advanced Systems (ICIAS), pp. 1-4.[5] Z.E.M. Osman, F.A. Hussin, And N.B.Z. Ali (2010b), Optimization of Processor Architecture for Image Edge Detection Filter, In Proceeding of International Conference on Computer Modeling and Simulation, pp. 648-652[6] I. Y asri, N.H. Hamid, And V.V. Y ap (2008), Performance Analysis of FPGA based Sobel Edge Detection Operator, In Proceedings of International Conference on Electronic Design, pp. 1-4. [7] V. Sanduja and R. Patial (2012), Sobel Edge Detection using Parallel Architecture based on FPGA, International Journal of Applied Information Systems, vol. 3, no. 4, pp. 20-24.[8] G. Anusha, T.J. Prasad, and D.S. Narayana (2012), Implementation of SOBEL Edge Detection on FPGA, International Journal of Computer Trends and Technology, vol. 3, no. 3, pp. 472-475. [9] L.P. Latha (2012), Design of Edge Detection Technique Using FPGA(Field Programmable Gate Array) and DSP (Digital Signal Processor), VSRD International Journal of Electrical, Electronics & Communication Engineering, vol. 2, no. 6, pp. 346-352.[10] A.R. Ibrahim, N.A. Wahed, N. Shinwari, and M.A. Nasser (2011), Hardware Implementation of Real Time Video Edge Detection With Adjustable Threshold Level (Edge Sharpness) Using Xilinx Spartan-3A FPGA, Report.[11] P.S. Chikkali and K. Prabhushetty (2011), FPGA based Image Edge Detection and Segmentation, International Journal of Advanced Engineering Sciences and Technologies, V ol. 9, Issue 2, pp. 187-192.[12] R. Harinarayan, R. Pannerselvam, M.M. Ali, And D.K. Tripathi (2011), Feature extraction of Digital Aerial Images by FPGA based implementation of edge detection algorithms, In Proceedings of International Conference on Emerging Trends in Electrical and Computer Technology, pp. 631-635.[13] K.C. Sudeep and J. Majumdar (2011), A Novel Architecture for Real Time Implementation of Edge Detectors on FPGA, International Journal of Computer Science Issues, vol. 8, no. 1, pp. 193-202.[14] W. Burger and M.J. Burge (2008), Digital Image Processing: An Algorithmic Introduction Using Java, New Y ork: Springer, 120-123.中文翻译:基于FPGA的实时彩色实现图像边缘检测Sanjay Singh Saini *,阿尼尔库马尔,拉维赛尼IC设计组CSIR中央电子工程研究所,拉贾斯坦,印度333031个学位-。

温度监测中英文翻译

土壤温度测量的设计1. 简介温度是土壤的一个十分重要的环境因素,它直接影响微生物的活跃性及有机物的分解,影响植物的根吸收水分与矿物质,同时它在植物生长率及根的范围上发挥着重要作用。

据统计,植物的根一般在地下50厘米范围内,因此测量这一范围内不同深度的土壤温度变得十分有意义。

目前,土壤温度测量仪器可分为三类。

第一种,是利用热敏电阻与土壤温度之间的关系测量实际温度。

在使用这类仪器前,系统参数需要校正,同时当解决系统遇到的问题时,十分不便。

第二种是非接触式的土壤测温仪器,它通过红外线测量温度,这种设备价格昂贵。

第三种,通过数字温度计测量温度。

目前,这类仪器不仅可测量一点的土壤温度,还可将数据进行存储与传输。

总之,上述设备因为价格过于昂贵或功能过于简单,而得不到广泛应用。

因此,一种价格更廉价,更能更强大的仪器需要去开发设计。

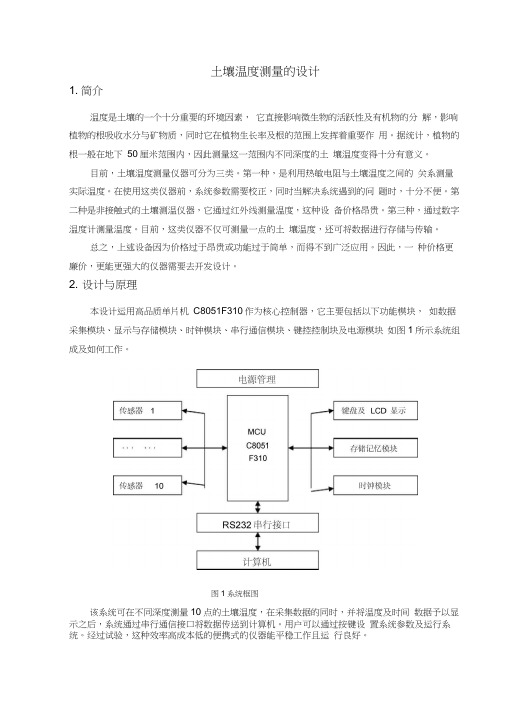

2. 设计与原理本设计运用高品质单片机C8051F310作为核心控制器,它主要包括以下功能模块,如数据采集模块、显示与存储模块、时钟模块、串行通信模块、键控控制块及电源模块如图1所示系统组成及如何工作。

图1系统框图该系统可在不同深度测量10点的土壤温度,在采集数据的同时,并将温度及时间数据予以显示之后,系统通过串行通信接口将数据传送到计算机。

用户可以通过按键设置系统参数及运行系统。

经过试验,这种效率高成本低的便携式的仪器能平稳工作且运行良好。

2.1硬件设计在硬件设计中,系统可利用的部分包括C8O51F310单片机、DS18B2C数字温度传感器、ISL6292可编程锂电池充电管理芯片、NCP500电压管理芯片以及DS1302时钟芯片,它们通过相应的外围电路连接在一起,同时这几部分是系统的核心结构。

下面就介绍这些核心部分及其外围电路。

2.1.1高质量C8051F310单片机C8051F310是一款兼容8051指令集的完全集成的混合信号ISP型MCU芯片。

C8051F31C主要由CIP-51内核、外围模拟电路、数字I/O 口及电源模块组成。

自动控制理论第五章习题

第五章习题E5.2 The engine,body,and tires of a racing vehicle affect the acceleration and speed attainable.The speed control of the car is represented by the model shown in FigureE5.2.(a)Calculate the steady-state error of the car to a step command in speed.(b)Calculate overshoot of the speed to a step command.E5.3 For years,Amtrak has struggled to attract passengers on its routes in the Midwest,using technology developed decades ago.During the same time,foreign railroads were developing new passenger rail systems that could profitably compete with air travel.Two of these systems,the French TGV and the Japanese Shinkansen,reach speed of 160 mph.The Transrapid-06,a U.S. Experimental magnetic levitation train,is shown in Figure E5.3(a).The use of magnetic levitation and electromagnetic propusion to provide contactless vehicle movement makes the Transrapid-06 technolog radically different from the existing Metroliner.The underside of the TR-06 carriage(where the wheel trucks would be on a conventional car)wraps around a guideway.Magnets on the bottom of the guideway attract electromagnets on the "wraparound,"pulling it up toward the guideway.This suspends the vehicles about one centimeter above the guideway.The levitation control is represented by Figure E5.3(b).(a)usingTable 5.6 for a step input,select K so that the system provide anoptimum ITAE response.(b)Using Figure5.3 determine the expected overshoot to a step input of I(s).E5.5 A low-inertia plotter is shown in Figure E5.5(a).This system may be represented by block diagram shown in Figure E5.5(b).(a)Calculate the steady error for a ramp input.(b)Select a value of K that will result in zero overshoot to a step input.Provide the most rapid response that is attainable.Plot the poles and zeros of the system and discuss the dominance of the complex poles.What overshoot for a step input do you expect?E5.6 Effective control of insulin injection can result in better lives for diabetic persons.Automatically controlled insulin jection by means of a pump and a sensor that measures blood sugar can be very effective.A pump and injection system has a feedback control as shown in Figure E5.6.Calculate the suitable gain K,so that the overshoot of the step response due to the drug injection is approximately 7%.R(s) is the desired blood-sugar level and Y(s),is the actual blood-sugar level.Figure E5.6E5.8 A unity negative feedback control system has the plant transfer function(a)Determine the percent overshoot and setting time (using a 2% setting criterion) due to a unit step input.(b)For what range of K is the setting time less than 1 second?E5.10 A system with unity feedback is shown in Figure E5.10.Determine the steady-state error for a step and ramp input whenE5.11 We are all familiar with the Ferris wheel featured at state fairs and carnivals,George Ferris was born in Galesbueg,Illinois,in 1859;he later moved to Nevada and then graduated from Rensselaer Polytechnic Institute in 1881. By 1891,Ferris had considerable experience with iron,steel,and bridge construction.He conceived and constructed his famous wheel for the 1893 Columbian Exposition in Chicago. To avoid upsetting passegers,set a requirement that the steady-state speed must be controlled to within 5% of the desired speed for thesystem shown in Figure E5.11.(a)Determine the required gain K to achieve the steady-state requirement.(b)For the gain of the part(a),determine and plot the error e(t) for a distrbance D(s)=1/s.Does the speed change more than 5%?(set R(s)=0 for ease of computation.)E5.13 A feedback system is shown in Figure E5.13.(a)Determine the steady-state error for a unit step when K=0.4 and G p(s)=1.(b)Select an appropriate value for G p(s) so that the steady-state error is equal to zero for the unit step input.E5.16 A closed-loop control system transfer function T(s) has two dominant complex conjugate poles.Sketch the region in the left-hand s-plane where the complex poles should be located to meet the given specifications.E5.17 A system is shown in Figure E5.17(a).The response to a unit step,when K=1,is shown in Figure E5.17(b).Determine the value of K so that the steady-state error is equal to zero.P5.1 A important problem for television systems is the jumping or wobbling of the picture due to the movement of thecamera.This effect occurs when the camera is mounted in a moving truck or airplane. The Dynalens system has been designed to reduce the effect of rapid scanning motion;see Figure P5.1. A maximum scanning motion of 25% is expected.Let K g=K f=1 and assume that τg is negligible.(a)Determine the error of the system E(s).(b)Determine the necessary loop gain,K a K m Kt,when a 10/s steady-state error is allowable.(c)The motor time constant is 0.40s.Determine the necessary loop gain so that the setting time(to within 2% of the final value of v b) is less than or equal to 0.03s.P5.2 A specific closed-loop control system is to be designedfor an underramped response to a step input.The specification for the system are as follows:10%<percent overshoot<20%, Setting time<0.6s.(a)Identify the desired area for the dominant roots of the sytem(b)Determine the smallest value of a third root,r3 ,if the complex conjugate roots are to represent the dominant response.(c)The closed-loop system transfer function T(s) is third-order,and the feedback has a unity gain, Determine the forword transfer function,G(s)=Y(s)/E(s).when the setting time to within 2% of the final value is 0.6s and the percent overshoot is 20%.P5.5 A space telescope is to be launched to carry out astronamical experiments.The pointing control system is desried to achieve 0.01 minute of arc and track solar objects with apparent motion up to 0.21 minute per second. Tne system is illustrated in Figure P5.5(a).The control system is shown in Figure P5.5(b). Assume that τ1 =1second and τ2 =0(an approximation).(a)Determine the gain K=K1K2 required so that the response to a step command is as rapid as reasonable with an overshoot of less than 5%(b)Determine the steady-state error of the system for a step and ramp input(c)Determine the value of K1K2 for ITAE optimal system for (1) a step input and (2)a ramp input.P5.6 A robot is programmed to have a tool or welding torch follow a prescribed path. Consider a robot tool that is to follow a sawtooth path.as shown in Figure P5.6(a).The transferfunction of the plant isThe transfer function of the plant is for the closed-loop system shown in Figure P5.6(b).Calculate the steady-state error.P5.7 Astronaut Bruce McCandless II took the first unthethered walk in space on February 7,1984,using the gas-jet propulsion device illustrated in Figure P5.7(a).The controller can be represented by a gain K2 , shown in Figure P5.7(b).The inertia of the equipment and man with his arms at his sides is 25 Kg-m2.FIGURE P5.7 (a)Astronaut Bruce McCandless II is shown a few meters away from the earth-orbiting space shuttle, Challenger. He used a nitrogenpropelled handcontrolled device called the manned maneuvering unit.(Courtesy of National Aeronautic and space Administration) (b)Block diagram of controller(a)Determine the necessary gain K3to maintain a steady-state error equal to 1 cm when the input is a ramp r(t)=t(meters). (b)With this gain K3,determine the necessary gain K1K2 in order to restrict the percent overshoot to 10%.(c)Determine annalytically the gain K1K2 in order to minimize the ISE performance index for a step input.P5.16 Electronic pacemakers for human hearts regulate the speed of the heart pump.A proposed closed-loop system that includes a pacemaker and measurement of the heart rate is shown in Figure P5.16.The transfer function of the heart pump and the pacemake is found to be:Design the amplifier gain to yield a system with a setting time to a step disturbance of less than 1 second.The overshoot to a step in desired heart rate should be less than 10%.FIGURE P5.16 Heart pacemaker(a)Find a suitable range of K(b)If the nominal value of K is K=10,find the sensitivity of the system to a small change in K.(c)Evaluate the sensitivity of part(b) at DC(set s=0).(d)Evaluate the magnitude of the sensitivity at normal heart rate of 60 beats/minute.P5.19 A system is shown in Figure P5.19.(a)Determine the steady-state error for a unit step input in terms of K and K1,where E(s)=R(s)-Y(S).(b)Select K1 so that the steady-state error is zero.AP5.1 A closed-loop transfer function is(a)Determine the steady-state error for a unit step input R(s)=1/s(b)Assume that the complex poles dominate,and determine the overshoot and setting time to within 2% of the final value(c)Plot the actual system response,and compare it with the estimate of part(b).AP5.3 A closed-loop system is shown in Figure AP5.3.Plot the response to a unit step input for system with τp=0, 0.5, 2,and 5. Record the percent overshoot,rise time,and settling time(with a 2% criterion) as τp varies.Describe the effect of varying τp .Compare the location of the closed-loop roots.AP5.4 The speed control of a high-speed train is represented by the system shown in Figure AP5.4.Determine the equation for steady-state error for K for a unit step input r(t).Consider the three values for equal to 1, 10, 100.(a)Determine the steady-state error.(b)Determine and plot the response y(t) for (i) a unit step input r(t) and (ii) a unit step disturbance input d(t).(c)Creat a table showing overshoot,setting time (with a 2% criertion),e ss for r(t),and |y/d|max for the three values of K.Select the best comprise value.AP5.6 The block diagram model of an armature-current-controlled DC motor is shown in FigureAP5.6.(a)Determine the steady-state error for a step input r(t)=t,t>=0, in terms of K,K b,and K m .(b)Let K m=10 and K b=0.05,and select K so that steady-state error is equal to 1.(c)Plot the response to a unit step and a unit ramp input for 20 seconds,Are the responses acceptable?。

工艺管道英文代号及缩写

石油天然气工艺管道安装常用英语缩写1、SWAGEDNIPPLECONCSMLS.:大小头同心无缝2、BLE/PSE:BeveledLargeEnd/PlainSmallEnd大端开破口/小端平端3、PE/PE、PBE、BLE/PSE、BSE/PLE:平端/平端、两端平端、大端开破口/小端平端、小端开破口/大端平端4、ELBOW90DEGLRBWSMLS.:弯头90度长半径(R=1.5DN)对焊无缝5、PIPESMLSPE/BE:无缝管平口/坡口6、GASKETFLATRING:垫圈平面环形7、compressedasbestosfiberjointingsheet:石棉胶板8、SPECTACLEBLIND:8字盲板9、STUDBOLTALLOYSTEEL:双头螺栓合金钢10、SR:短半径(R=1.0DN)11、MildSteel软钢;低碳钢软钢丝12、MildSteelArcWeldingElectrode低碳钢焊条13、MildSteelChannel槽钢14、MildSteelCheckeredPlate花纹钢板15、MildSteelEqualAngle等边角钢16、MildSteelExpandedSheets钢板网17、MildSteelFireBox软钢板火箱18、MildSteelHexagonalBolts六角螺丝梗19、MildSteelHexagonalBoltsAndNuts六角螺丝闩20、MildSteelI-Beam低碳工字钢21、MildSteelIngot低碳钢锭22、MildSteelPlate软钢板23、MildSteelReinforcement(含钢量0.12--0.25%)软钢钢筋24、MildSteelShank软钢手柄25、MildSteelSheet软钢皮26、TS:螺母(nut的复数)27、BOLT:螺栓28、FULLBORE:与管子等径的、直通式(ValveBall,FullBore全通径球阀)29、REDUCED/REGULARBORE:缩径(ValveBall,Reduced/RegularBore缩径球阀)30、SWENDS/CARBONSTEELBODY/DIMSTOBSEN:承插焊/碳钢阀体/尺寸按照英国及欧洲标准31、RFFLANGEDENDS:凸面法兰连接(表示阀门连接形式)32、TEEEQUAL:等径三通33、SOCKOLET:承插支管台34、THREBOLET:螺纹支管台35、常见阀门连接面英文表示:⑴LUGGED??------>凸耳对夹式的,法门的一种结构形式.一般用于大直径的止回阀或蝶阀,属于对夹连接的一个变种,要配对法兰.连接螺栓要加长⑵RINGTYPEJOINT------>环连接面,这是法兰密封面的类型,一般这样写要法兰的.⑶SOCKETWELD------>承插焊连接,不需法兰⑷THREADED---->螺纹连接,不要法兰⑸WAFER------>对夹式连接,类似于凸耳的,也是一种阀门的结构形式,属于FLANGELESS阀门,阀门本体没有法兰,但是要有配对法兰连接.螺栓要加长⑹BUTTERWELD/THREADED------>对焊/罗纹.都不要法兰,一般是用于描述小阀门,两端的连接形式不同的情况⑺SOCKETWELD/THREADED--->承插焊/螺纹,都不要法兰,一般是用于描述小阀门,两端的连接形式不同的情况36、VALVEGATE/SOLIDWEDGE:闸阀/整体楔形闸板37、MANUFACTURERSSTANDARD:行业标准38、union:通常指的是活接头,也就是老师傅常说的“油印”;nipple:一般是指用于软管站连接软管的接头,连接方式为多样(焊接/丝接/法兰连接);pipe:一般就指短管,其中的couple特指两头带法兰的短管连接,即俗称的“车轱辘管”。

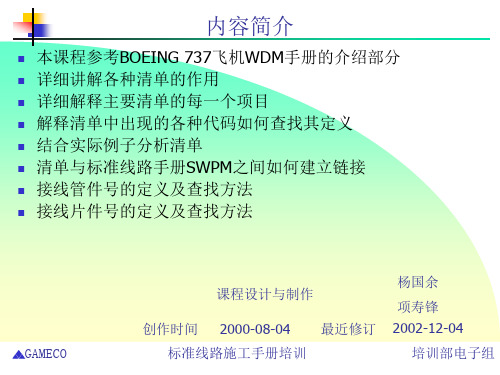

WDM使用方法

91-06-10 SYSTEM BLOCK DIAGRAM FAIL-PASSIVE AUTOLAND ELECTRONIC POWER

91-06-11 SYSTEM BLOCK DIAGRAM FAIL - PASSIVE AUTOLAND INERTIAL REF SYSTEM

GAMECO

标准线路施工手册培训

培训部电子组

WDM 91章目录说明

91-01-08 INSTALLATION OF DUAL GROUNDS

91-02 - CIRCUIT BREAKER LIST 91-02-00 CIRCUIT BREAKER LIST 91-03 91-03-01 E1-1 ELECTRONIC SHELF 91-03-02 E1-2 ELECTRONIC SHELF 91-03-03 E1-3 ELECTRONIC SHELF 91-03-04 E2-1 ELECTRONIC SHELF 91-03-05 E2-2 ELECTRONIC SHELF 91-03-06 E2-3 ELECTRONIC SHELF 91-03-07 E2-4 ELECTRONIC SHELF 91-03-08 E3-1 ELECTRICAL SHELF

简言之,可通过设备号找件号。 在设备清单中不包括

连接管 接地 终端 线束

在A320飞机上与BOEING设备号(Equipment Number)相对应 的概念是功能设备号(Function Item Number)

可通过功能设备号找件号 比BOEING设备号有更多更广的用途

GAMECO

TMS320C6748 原理图

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99

(3) uP_EMIFA_WAIT1 (3) uP_EMIFA_WAIT0 (3) uP_EMIFA_WEn (3) uP_EMIFA_OEn (3) uP_EMIFA_RnW (3) uP_EMIFA_CLK (3) (3) (3) (3) uP_EMIFA_CSn5 uP_EMIFA_CSn4 uP_EMIFA_CSn3 uP_EMIFA_CSn2 uP_EMIFA_D0 uP_EMIFA_D1 uP_EMIFA_D2 uP_EMIFA_D3 uP_EMIFA_D4 uP_EMIFA_D5 uP_EMIFA_D6

Rev 3

Sheet

Project OMAP-L138

1

1

of

9

5

4

3

2

5

4

3

2

1

02 - BASEBOARD CONNECTORS

PERIPHERAL IO

5V_IN

D

PERIPHERAL IO

VRTC_IN uP_VPIF_DOUT[15..0] (5) 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80 82 84 86 88 90 92 94 96 98 100 DGND MAIN_BATT_IN J2 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 uP_EMIFA_D7 uP_EMIFA_D8 uP_EMIFA_D9 uP_EMIFA_D10 uP_EMIFA_D11 uP_EMIFA_D12 uP_EMIFA_D13 uP_EMIFA_D14 uP_EMIFA_D15 uP_EMIFA_A0 uP_EMIFA_A1 uP_EMIFA_A2 uP_EMIFA_A3 uP_EMIFA_A4 uP_EMIFA_A5 uP_EMIFA_A6 uP_EMIFA_A7 uP_EMIFA_A8 uP_EMIFA_A9 uP_EMIFA_A10 uP_EMIFA_A11 uP_EMIFA_A12 uP_EMIFA_D[15..0] (3) MAIN_BATT_IN

PLC(电力载波)

Automatic Meter Reading (AMR) System Overview:The remote Automatic Meter Reading (AMR) System is a host driven, multi-level network system consisting of a Host Central Station (HCS), Data Concentrator Units (DCU) and Meter Interfacing Units (MIU), with built-in flexibility and expandability. Each HCS, while working independently, can also be integrated with an existing corporate information management system through software interface. With additional hardware and software support, the HCS can function as a workstation in an existing Local Area Network (LAN) and becomes a member of the entire system, or several HCS can be connected together to form a network of their own.Automatic Meter Reading (AMR) system can be connected to any Electricity, Gas, Water and flow Meters with pulse output for Meter Readings.Automatic Meter Reading (AMR) System Block Diagram:The DCU and all the MIUs and meters connected to it can be considered as a sub-system of the HCS. The sub-system is set up with a DCU monitoring the low voltage power zone downstream of a Distribution Transformer. The DCU can be viewed as the front end of the sub-system, collecting meter readings from all the MIUs connected to it through the low voltage power line carrier (PLC) and communicating with the HCS through the communication channel. There are two types of MIUs, a single-channel type connected to a single meter only, and a multi-channel type, which can be connected up to 16 meters. In projects where meters are scattered around in an open area, single-channel MIUs are usually used for individual meters. But for projects where meters are grouped together in a meter room or cabinet, Multi-channel Meter Interface Units (MMIU) are more cost effective. There are basically two stages of communication in the system, namely, that between the MIUs and the DCU, and that between the DCUs and the HCS. The communication channel or medium used between MIU and DCU is the Power Line; and the channel used between DCU and HCS can be the Public Switched Telephone Network (PSTN), GSM network, radio network, or directly with handheld terminals and notebook computers with a standard RS-232 interface or through a modem.Operating Principle:The communication device for the PLC communication system is a built-in Power Line Modem (PLM), which transmits and receives data over the power line. Both the MIU and the DCU contain the PLM device. The binary data stream is keyed onto a carrier signal by means of the Frequency Shift Keying (FSK) technique. The central frequency is shifted +0.3KHz to represent 1 or 0 of the binary data stream. This signal is then coupled onto the power line by the PLM. At the receiving end, an identical PLM will detect the signal and convert it back to a binary data stream. The PLMs operate in a Half Duplex, two-way, Time Division Multiplex communication mode. Two-way communication between DCU and MIU is essential in establishing a proper communication channel, for system synchronization and status reporting.In AMRS, transmission speed is not a great concern but reliability is important. The data rate of the PLC channel is set at 600 bps, to ensure communication over a longer distance and reduced transmission error. Every MIU is also equipped with repeater function. If required, the DCU can designate any MIU in the sub-system as a repeater to enhance communication with a particular MIU. With the sensitive signal detection and sophisticated digital filtering technique, this PLC communication is highly immune to electrical noise and interference.PLC Schematics:Signal, Data and Information Flow:The MIU is an intelligent device, which can collect, process, and record power consumption data from the electric meter. It picks up the pulse output of the meter and converts the measurement of the meter into a digital format suitable for data processing. Thus it is possible to monitor the electrical load in real time. The MIU saves the data collected in non-volatile memory, and all data and settings are protected against power failure. It will automatically resume normal operation when power returns after a power failure. After receiving a Multi-rate Tariff command and loading the time-of-use table from the DCU, the MIU will process energy consumption data according to pre-set time intervals. It will update the peak values and their time of occurrence at each tariff rate providing real time information of electrical consumption for the information management system. Data stored in the MIU are transmitted to the DCU via the power line through the built-in Power Line Modems (PLM). Communication is initiated by the DCU, which polls the MIU by calling its address. Data received from different MIUs are stored in the corresponding Load Data Records in the Flash memory of the DCU. The DCU supports communication with any upward equipment in conformity with RS-232 standard, e.g. a handheld computer. In most cases, the DCU communicates with the remote Host Central Station through standard modem via the existing telephone line or the GSM network. The Host Central Station (HCS) is the control center of the system, where all the functions of the system are controlled and monitored. The HCS passes instructions and information requests onto the Data Concentrator Units (DCU) by calling their addresses (or the telephone numbers in case of a public switched network), and the DCU will respond accordingly. The address codes (telephone number) of the DCUs are stored in the HCS. With sufficient mass storage, theoretically all DCUs can be covered by the HCS, in actual fact the maximum number of DCUs can be connected to a HCS is about 1000 as it will be limited by the required response time and efficiency of data management. In case of failures in self-diagnostics or any abnormal behavior of the MIUs, the DCU can also make requests to report by dialing to the HCS. The HCS will convert the data received into a text file compatible with the corporation's existing Meter Reading Management System, and store it in the Hard Disk Drive. File transfer between the HCS and the Corporation's MIS system can be done through standard input/output ports, such as RS-232.Product LineSl Item Code Description Rate (Rs.)1 ATL90115-1 Embedded PLC Modem - 1 Phase 16702 ATL90115-3 Embedded PLC Modem - 3 Phase 27503 PLC101s-12 Embedded PLC Modem - 1 Phase (1200bps) 23104 PLC103s-12 Embedded PLC Modem - 3 Phase (1200bps) 32505 ATL60142E Broadband Power Line Carrier Modem 40006 MIU 101 Single Phase Meter Interface Unit 23007 MMIU-16 Multi-channel Meter Interface Unit (16 channel) 180008 LXSG-15Y Water Meter with pulse output 32509 DCU220 Data Concentrator Unit 8770010 HHU Handheld Programming Unit 3695011 PSS100-12 Switching Power Supply (+/-12VDC) 150012 PMIU Meter Interface Unit with power cut-off function 416013 EM-1-A Single-phase AMR Electronic Watt-hr Meter 416014 EM-3-A 3-phase 4-wire AMR Electronic Watt-hr Meter 970015 ATL57001 Public Lighting Control Unit 7400Terms:Power Line Carrier Communicationa) Sales Tax : Extrab) Freight & Forwarding : Extrac) Delivery : 2-3 weeks subjected to ready stock.d) Payment terms : 50 % Advance, 50 % on D.O.D. Basise) Warranty : 1 year from date of deliveryf) Excise Duty : N.A.g) AMR Software : Demo version available FOC against purchase.。

NuMaker-emWin-RDK-N9H30 用户手册说明书

ARM® ARM926EL-S Based32-bit MicroprocessorNuMaker-emWin-RDK-N9H30User ManualNUMAKER-EMWIN-RDK-N9H30 USER MANUALThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.Nuvoton is providing this document only for reference purposes of NuMicro microprocessor based systemdesign. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1Overview (3)2Board Feature List (4)3Function Description (5)System Block Diagram (5)System Power Scheme (6)I/O or Jumper Description (6)3.3.1Power-on Setting (6)3.3.2SD Connector (7)3.3.3UART Interfaces (7)3.3.4USB Port (8)3.3.5RS485 Interface (9)3.3.6CAN Interface (9)3.3.7Ethernet Port (9)3.3.8JTAG Port (10)4NuMaker-emWin-RDK-N9H30 Demo Board Schematic (11)Main Block (11)Flash Memory (12)NUMAKER-EMWIN-RDK-N9H30 USER MANUALLCD Interface (13)N9H30F61I (14)Power (15)UART (16)USB (17)ETH_PHY&CAN (18)5Revision History (19)1 OverviewThe NuMaker-emWin-RDK-N9H30 demo board is N9H30 series product. Users can use theboard to develop and verify the emWin application program easily.The N9H30 series embedded the ARM®926 core for HMI applications which need highcomputing power and rich communication interfaces. The CPU can run up to 300 MHz andequipped with USB2.0 high speed device, USB2.0 high speed host, Ethernet interfaces and otherrich peripherals, such as LCD, NAND, SD, ADC, UART, SPI, I²C, I²S, CAN, RTC…etc.NUMAKER-EMWIN-RDK-N9H30 USER MANUALFigure 1-1 NuMaker-emWin-RDK-N9H30 Demo Board2 Board Feature List1. Adopted Nuvoton ARM926EJS-based MPU N9H30F61I, it can run up to 300MHz.2. NAND Flash used Winbond W29N01GV 128MB with 8-bit data bus width.3. SPI Flash used W25Q128FVSG 16MB.4. Boot selection by NAND or SPI or USB.5. One DB9 RS232 port with N9H30 UART0 for debugging.6. One DB9 RS232 port with N9H30 UART2 for user application.7. Installed SN65HVD230 transceiver for CAN bus communication.8. Installed MAX3485 transceiver for RS485 device connection.9. USB supports both HS USB2.0 device with micro USB connector and HS USB 2.0 host withtype-A connector.10. Provided one Micro-SD/TF card slot for data storage with SD memory card.11. Used 7” TFT LCD and embedded that resistive type touch panel.12. Reserved an external coin-cell socket for RTC power backup with CR2032 battery.13. Provided one10/100Mb Ethernet RJ45 port.14. Provided one buzzer device for user application.15. JTAG interface is reserved for software development advanced.16. System powered could be supplied by DC-5V adaptor or USB VBUS. NUMAKER-EMWIN-RDK-N9H30 USER MANUAL3 Function DescriptionSystem Block DiagramNUMAKER-EMWIN-RDK-N9H30 USER MANUALSystem Power Scheme NUMAKER-EMWIN-RDK-N9H30 USER MANUALI/O or Jumper Description3.3.1 Power-on SettingSW1 Function Description:NuMaker-emWin-RDK-N9H30 provided system program code booting source from NAND Flash,SPI-NOR Flash or USB. In the board we have programmed a sample emWin code to NANDflash for demonstration.About USB booting purpose is for Flash memory programming through the NuWriter of PC utilitytool, regarding the NuWriter operation please refer the user manual to get for detail.NUMAKER-EMWIN-RDK-N9H30 USER MANUALSW1-1 SW1-2Boot FromON ON booting from USB for PC communicationON OFF booting from NAND Flash OFF OFFbooting from SPI Flash3.3.2 SD ConnectorJP7: NuMaker-emWin-RDK-N9H30 provided a micro SD connector for user use what program accesses or data storage.Note. N9H30 cannot support system booting.3.3.3 UART Interfaces●CON5: One DB-9 connector for RS232 communication, the UART signals are from N9H30UART0 TXD and RXD interfaces and through the RS232 transceiver, SP3232EEN. This port isdedicated for message debugging.●CON4: One DB-9 connector for RS232 communication, the UART signals are from N9H30UART2 TXD and RXD interfaces and through the RS232 transceiver, SP3232EEN. This port isreserved for user application.3.3.4 USB Port NUMAKER-EMWIN-RDK-N9H30 USER MANUAL●CON1: This is a Micro USB connector, it is for PC communication and the signals are fromN9H30 USB port-0●CON2: This is a Type-A USB HOST connector, it is for USB devices connection and the signalsare from N9H30 USB port-1Note. CON1 VBUS can power supplied for system if connected with PC or notebook.3.3.5 RS485 Interface●J5: NuMaker-emWin-RDK-N9H30 provided a two-pin terminal connector with 3.5mm pitch forRS485 device connection.Note. MAX3485 is RS485 (half-duplex communication) transceivers and built in to NuMaker-emWin-RDK-N9H30 demo board already.3.3.6 CAN InterfaceNUMAKER-EMWIN-RDK-N9H30 USER MANUAL●CON7: NuMaker-emWin-RDK-N9H30 provided a two-pin terminal connector with3.5mm pitch forCAN bus device communication with N9H30 CAN0 port.Note. CAN transceivers,SN65HVD230 have built in to NuMaker-emWin-RDK-N9H30 demoboard already.3.3.7 Ethernet Port●CON6: NuMaker-emWin-RDK-N9H30 provided a standard RJ-45 port for 10M/100M Ethernetcommunication.Note. NuMaker-emWin-RDK-N9H30 has built in the RMII-PHY, IC+ IP101GR on board already.3.3.8 JTAG PortJ2: NuMaker-emWin-RDK-N9H30 demo board provided one male header x6 connector with pitch NUMAKER-EMWIN-RDK-N9H30 USER MANUAL2.54mm for N9H30 JTAG signals; user can make that wiring connection with Keil- ICE forsoftware development advanced.NUMAKER-EMWIN-RDK-N9H30 USER MANUAL4 NuMaker-emWin-RDK-N9H30 Demo Board SchematicMain BlockLCDLCD DGND VDD33LVSYNC LHSYNC LCD_B[7:0]LCD_G[7:0]LCD_R[7:0]LCD_CLK Y+X-Y-X+PWM VDD5V N9H30F61IN9H30F61I485_TXEN 485_TXD 485_RXD UART0_TX UART0_RX 232TXD 232RXDPH0USB0_DM USB0_DP DP1DN1RTC_XO RTC_XI nRESET 12M_XO 12M_XI VDD18VDD12VDD33DGNDLVSYNC LHSYNC LCD_B[7:0]LCD_G[7:0]LCD_R[7:0]LCD_CLKSM_D[7:0]SM_RBn SM_REn SM_CS0n SM_CLE SM_ALE SM_WEn SM_WPn SPICS SPICLK SPIWp/D2SPIDo/D0SPIDi/D1SPIHOLD/D3RTCVD Y+Y-X+X-PWM SDCd SDCmd SDD[3:0]SDCLK PHY_MDIO PHY_MDC PHY_TXEN PHY_TXD0PHY_TXD1PHY_RXD0PHY_RXD1PHY_CRSDV PHY_RXERR MAC_REFCLKCAN_TX0CAN_RX0PHY_RSTPHY_RSTFLASHFlashSM_D[7:0]SM_RBn SM_REn SM_CS0n SM_CLE SM_ALE SM_WEn SM_WPnVDD33DGNDSPICS SPICLK SPIWp/D2SPIDo/D0SPIDi/D1SPIHOLD/D3SDD[3:0]SDCmd SDCd SDCLK UARTUART485_RXD 485_TXD 485_TXEN VDD33232RXD232TXD DGND UART0_RXUART0_TX FGND VDD5VVDD5VIN USBUSB USB0_DM USB0_DPPH0VDD5VIN FGNDDN1DP1POWERPowerVDD5VVDD33VDD12VDD18RTC_XO RTC_XI 12M_XI 12M_XO nRESETDGNDRTCVD PWM 485_TXEN 485_TXD 485_RXD UART0_TX UART0_RX 232TXD TitleSize Document Number Rev Date:SheetofMAIN_BLOCK1.0N9H30F51I_HMI_DEMOB18Tuesday , Nov ember 27, 2018232RXDPH0USB0_DM USB0_DP DP1DN1RTC_XO RTC_XI nRESET 12M_XO 12M_XI VDD18VDD12VDD33VDD33DGNDDGNDVDD5VIN FGND VDD5VFGNDVDD5VIN VDD5VLVSYNC LHSYNC LCD_B[7:0]VDD5VLCD_G[7:0]LCD_R[7:0]LCD_CLK DGND VDD33SDCd SM_D[7:0]SDCmd SM_RBn SM_REn SDD[3:0]SM_CS0n SM_CLE SM_ALE SM_WEn SM_WPn SDCLK ETH_PHY&CANETH_PHY&CANPHY_RXD0PHY_RXD1PHY_CRSDV PHY_MDIO PHY_MDC PHY_RXERRMAC_REFCLK PHY_TXEN PHY_TXD0PHY_TXD1VDD33DGNDCAN_TX0CAN_RX0FGND PHY_RSTPHY_MDIO SPICS PHY_MDC SPICLK PHY_TXEN SPIWp/D2SPIDo/D0SPIDi/D1PHY_TXD1PHY_TXD0PHY_RXD1PHY_RXD0PHY_CRSDV PHY_RXERR MAC_REFCLK CAN_TX0CAN_RX0SPIHOLD/D3DGNDVDD33RTCVD Y+VDD33DGND FGNDY-X+X-NUMAKER-EMWIN-RDK-N9H30 USER MANUALFlash MemoryNAND FLASHVDD33VDD33SM_D[7:0]VDD33SM_D[7:0]U1W29N01GVNC 1NC 2NC 3NC 4NC 5NC 6R/B 7RE 8CE 9NC 10NC 11Vcc 12Vss 13NC 14NC 15CLE 16ALE 17WE 18WP 19NC 20NC 21NC 22NC 48NC 47NC 46NC 45I/O744I/O643I/O542I/O441NC 40NC 39NC 38Vcc 37Vss 36NC 35NC 34NC 33I/O332I/O231I/O130I/O029NC 28NC 27NC 23NC 24NC 26NC25DGND R110KSM_D7SM_RBn SM_D6SM_REn SM _RBn SM_CS0nSM_REn SM_D5SM_CS0nSM_D4SM_CLE SM_ALE VDD33SM_WEn SM_ALE SM_CLE VDD33SM_WPnSM_WEn SM_D3R1410K SM_WPnSM_D2SM_D1R310K/N O PSM_D0VDD33VDD33C B10.1uFDGNDTitleSize Document Number Rev Date:SheetofFlash1.0N9H30F51I_HMI_DEMOA 38Tuesday , Nov ember 27, 2018SPICS SPICLK SPIWp/D2SPIDo/D0SPIDi/D1SPIHOLD/D3C210UF/25V C0805U2SRV05-4SOT23-6CH46CH23CH34Vn 2Vp 5CH11U3SRV05-4SOT23-6CH46CH23CH34Vn 2Vp 5CH11R2SDVD33VDD33DAT3C11UFC0603VDD33DGNDCB20.1uFSDD[3:0]SPI FalshR1810K JP7B8502A-13SB-HPA (T-Flash Card)DAT21DAT32CMD 3VDD 4CLK 5VSS 6DAT07DAT18CD9GND10GND 11GND 12GND 13R1910KSDD[3:0]R2010KR647SDD2R747DGND SDCmdSDD3DAT2R847U5W25Q128/CS 1Do/D12Wp/D23GND 4Di/D05CLK 6Hld/D37VCC 8SDVD33SDCmdSPICS CMD SPIHOLD/D3SPIDi/D1R1047SPIWp/D2SDCLKSPIDo/D0SPICLK CLK SDVSS R1347C3NC SDD0R1547DAT0L1600次@100M H ZL0603SDCdSDD1R1647DAT1SDVSSCDSDCdVDD33VDD33R1710KR510K DGNDVDD33R910KVDD33R410K R110DGND TF CARDVDD33R1210K SDCLKSDVD33DAT2CLKSDVSSDAT3CMDCDSDVD33DAT1SDVSS DAT0LCD InterfaceNUMAKER-EMWIN-RDK-N9H30 USER MANUALN9H30F61IU8N9H30F61I00000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000NUMAKER-EMWIN-RDK-N9H30 USER MANUALPowerTitleSize Document Number Rev Date:SheetofPower1.0N9H30F51I_HMI_DEMO A 68Tuesday , Nov ember 27, 2018VDD5VL10 4.7uHVDD33U9ZT7103TTSOT-25EN1GND 2SW 3Vin 4FB5C32470pFCB220.1uFDGND R50680KDGNDDGND R52150K32768H z C r y s t a l12M H z C r y s t a lDGNDDGNDVDD5VX1TXC-9H T9 SMD 32.768KHz 30ppmR5310KRTC_XI RTC_XOC3815pFC3915pFVDD5VL12 4.7uHU11ZT7103TTSOT-25EN1GND 2SW 3Vin 4FB5DGNDDGNDC361nFDGND R54120KC40NC DGNDR55120KDGND R561MDGND12M_XI12M_XO DGNDX212MHz CRYSXIN1GND 2GND 4XOUT 3VDD5VC4215pFR5710KC4515pFDGND VDD5VDGNDL13 4.7uHDGNDU12ZT7103TTSOT-25EN1GND 2SW 3Vin 4FB5DGNDC441nFC46NCDGND R58200KDGNDR59100KDGNDDGNDDGNDC3510UF/25V C0805C4110UF/25V C0805C4710UF/25V C0805C3710UF/25V C0805C4310UF/25V C0805VDD12JP8SIP/2P SW_PB2_B1_SMD12VDD18C3410UF/25V C0805VDD5VVDD33DGNDVDD12VDD18L18600次@100MHZL0603RTC_XIRTC_XO12M_XI12M_XOU10TLV809GND1/RESET 2VDD3R E S E TC 330.1uFVDD33R51R490DGNDL11600次@100MHZL0603nRESETnRESETDGNDRTCVDD12RB521S-3012VDD33D13RB521S-3012BT1CR2032BAT\CR2032-4-2\smdCB230.1uF DGNDDGNDRTCVDD9SMAJ5.0CAD10SMAJ5.0CAD11SMAJ5.0CALED1GREEN LED 12R601KVDD33DGNDNUMAKER-EMWIN-RDK-N9H30 USER MANUALUARTRS485RS232000000000000RS23200000NUMAKER-EMWIN-RDK-N9H30 USER MANUALUSBU S B 0 D e v i c eR6920K USB0_DMR704.7USB0_DPR714.7PH0UDO1UDO0PH0FGNDR7239KFGNDFGNDVDD5VINTitleSize Document Number Rev Date:SheetofUSB1.0N9H30F51I_HMI_DEMOA 88Tuesday , Nov ember 27, 2018D1-D1+FGNDFGNDVDD5VINVDD5VIN CON1USB MICRO-AB RECEP.MICRO_USB_AB_LSVBUS 1D-2D+3GND5ID 4Shield 6Shield 7Shield 8Shield9C 751uFL15600次@100MHZL0603D161N4148VBUSVDD5VINUSB HostL16600次@100M H Z 12CON2USB TYPE-A B4P_ATYPEVBUS 1D-2D+3GND4Shield 5Shield6VBUS1DN1R73 4.7DN1C 570.1uFDP1R74 4.7DP1L17600次@100M H Z12FGND FGNDC5610UF/25V C0805L14600次@100M H Z 12U16SRV05-4SOT23-6C H 46C H 23C H 34V n 2V p 5C H 11U17SRV05-4SOT23-6C H 46C H 23C H 34V n 2V p 5C H 11F1FUSE(6V/1A)NUMAKER-EMWIN-RDK-N9H30 USER MANUALETH_PHY&CANR940R0603VDD33DGND U20SN65HVD230SO-8D 1GND 2VCC 3R4Rs 8CANH 7CANL 6Vref5CAN_TX0DGND CAN_RX0CB270.1uF C0603DGNDCON7SIP\2P\5MM SIP/2P_3.5MM12CAN_TX0CAN_RX0R96120R0603CAN0H CAN0L50MClkiPHY_RST Phy AD3CRS TitleSize Document Number Rev Date:SheetofETH_PHY&CAN1.0N9H30F51I_HMI_DEMOB 28Tuesday , Nov ember 27, 2018CON6RJ-45 8P8C_LED R/ARJ45\8P\JA\LEDTX+1TX-2RX+3NC 4NC 5RX-6NC 7NC8Shield 13Shield 14LED-9LED+10LED-11LED+12R841M R0603CT210uFR8975R78Col Col C760.01uF/2KVCK05CRSCT310uFC657pF C0603C640.1uFR9075R795.1K R0603R835.1K R0603C637pF C0603R8210K R0603C62N.C.C0603R850R0603R9275C670.1uFC660.01uF U19TS8121CTX+16TX-14NC 13TD-3TD+1RD+6RD-8NC5RX-9RX+11CT 2NC 4CT 7CT 10NC12CT 15R766.19K +/-1%R0603U18IP101GR TxEr/FxSD 1Xi 2Xo 3Col/RMII 4TxEn 5TxD36TxD27TxD18TxD09TxClk/50MClki 10LED0/Phy AD011LED3/Phy AD312IOVDD 13RxClk/50M_Clko 14RxD315RxD216TestOn 24MDIO 23MDC 22RxEr/Int3221CRS/LEDMod 20RxDV/CRS_DV 19RxD018RxD117nRst 32AVD3331MDiTp 30MDiTn 29RegOut 28MDiRp 27MDiRn 26Iset 25R88330R0603RMii0TxD1RMii0TxD0RMii0MDC R9175RMii0RxD1RMii0RxD0CT110uFRMii0MDio RMiiRxErr RMii0CRSDV MDI_TN MDI_TP RMii0TxEn C680.01uFMDI_RP MDI_RNX325MHz CRYSXIN1GND 2GND 4XOUT 3EthX1R95 5.1KCB250.1uF R770R0603CT410uF C690.01uF/2KVR86330R0603EthX0R8110K R0603EthX1R805.1K R0603EthX0R935.1KCB260.1uF R870R0603PHY_RXD0Phy AD0PHY_MDIO PHY_CRSDV PHY_RXD1MAC_REFCLKPHY_RXERR PHY_MDCPHY_TXD0PHY_TXEN DGNDVDD33PHY_TXD1Phy AVD33PHY_RSTRegOut DGNDPhy IOVD33RegOutDGNDDGNDDGNDDGND DGNDDGNDVDD33DGNDPhy AVD33Phy IOVD33DGNDDGND Phy IOVD33DGNDVDD33VDD33DGNDDGNDFGNDDGNDFGNDDGNDDGND RMii0MDio RMiiRxErr DGND FGND VDD33VDD33DGNDFGND50MClki RMii0Ref Clk FGNDR10210K R0603PHY_RST RMii0CRSDV C771uF C0603DGNDRX+TX-RX-TX+MDI_TNMDI_TP Phy AD3Phy AD3MDI_RP MDI_RNE t h e r n e t T P o r tPhy AD0Phy AD05 Revision HistoryDate Revision Description2018.10.03 1.00 1. Initially.2018.11.27 2.00 1. PCB version 2.1, supports Ethernet and CAN2021.03.26 2.01 1. Rename NuMaker-emWin-RDK-N9H30Important NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties layclaimsto Nuvoton as a result of customer’s Insecure Usage, custome r shall indemnify thedamages and liabilities thus incurred by Nuvoton.NUMAKER-EMWIN-RDK-N9H30 USER MANUAL。

SPI文档(Moto)