A DYNAMIC RECONFIGURABLE CLOCK GENERATOR

开机自检时出现问题后会出现的BIOS语句

开机自检时出现咨询题后会出现各种各样的英文短句,短句中包含了特不重要的信息,读明白这些信息能够自己解决一些小咨询题,然而这些英文难倒了一局部朋友,下面是一些常见的BIOS短句的解释,大伙儿能够参考一下。

〔1〕.CMOSbatteryfailed中文:CMOS电池失效。

解释:这讲明CMOS电池差不多快没电了,只要更换新的电池即可。

〔2〕.CacheMemoryBad,DoNotenableCache解决方法:主板高速缓存损坏导致,寻售后解决〔3〕.CMOSchecksumerror-Defaultsloaded中文:CMOS执行全部检查时发现错误,要载进系统预设值。

解释:一般来讲出现这句话根基上讲电池快没电了,能够先换个电池试试,要是咨询题依旧没有解决,那么讲明CMOSRAM可能有咨询题,要是没过一年就到经销商处换一块主板,过了一年就让经销商送回生产厂家修一下吧!〔4〕.CMOSChecksumErrordefaultsloaded解决方法:也有可能是电池没有电所致,然而更换后还出现那个咨询题,有可能是CMOS数据错误或主板电容咨询题,寻售后〔5〕.解决方法:Boot.ini文件中的代码被更改,能够将下面的代码保持到c:\boot.ini 中[bootloader]-timeout=10/default=multi(0)disk(0)rdisk(0)partition(1)\WINDOWS[operatingsystems]multi(0)disk(0)rdisk(0)partition(1)\WINDOWS="MicrosoftWindowsXPPro fessional"/NOEXECUTE=OPTIN/FASTDETECT〔6〕.PressESCtoskipmemorytest中文:正在进行内存检查,可按ESC键跃过。

解释:这是因为在CMOS内没有设定跃过存储器的第二、三、四次测试,开机就会执行四次内存测试,因此你也能够按ESC键结束内存检查,只是每次都要如此太苦恼了,你能够进进COMS设置后选择BIOSFEATURSSETUP,将其中的QuickPowerOnSelfTest设为Enabled,储存后重新启动即可。

内存时序调节

内存时序调节主流DDR400内存时序参数的意义与设定方法大家在购买内存时往往会注意到内存的标签上往往帖有“3-4-4-8”或“3-8-4-4”这类数字,这些数字就是内存SPD 设定的时序参数,举例来说在标识为“3-4-4-8”的参数下分别对应的参数是“CL-tRCD-tRP-tRAS”。

下面我们将着重介绍这四个参数的意义与设定方法。

SPD=Serial Presence Detect,配置(存在位)串行探测芯片,主要用来存放内存的配置信息,如Bank 数量、电压、行地址/列地址数量、位宽、各种主要操作时序的设定参数(如CL、tRCD、tRP、tRAS等),一般说来内存的SPD设定参数比较保守,但工作稳定。

普通用户或硬件菜鸟在使用内存时,无需了解那些复杂内存时序参数的含义,仅需在Bios里将内存参数设置为“By SPD”就可放心使用,而玩家或发烧友要想达到系统性能最优化的话,则需将BIOS设置为“EXPERT”或“Manual”进行手动调节。

CAS Latency Control(“3-4-4-8”中的第1个参数,即CL参数。

也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“内存读写操作前列地址控制器的潜伏时间”。

CAS控制从接受一个指令到执行指令之间的时间。

因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。

内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。

一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。

首先是行地址,然后初始化tRCD,周期结束,接着通过CAS访问所需数据的精确十六进制地址。

期间从CAS开始到CAS结束就是CAS延迟。

SDRAM的相关时序参数设置

SDRAM的相关时序参数设置SDRAM(Synchronous Dynamic Random Access Memory)是一种高速的内存类型,它与处理器进行同步工作,提供快速的数据传输和读写能力。

SDRAM的性能受到各种时序参数的影响,正确设置这些参数对于系统的稳定性和性能至关重要。

下面将详细介绍SDRAM的各个时序参数及其设置方法。

1. 刷新周期(Refresh Cycle)SDRAM是一种动态存储器,需要定期进行刷新操作。

SDRAM芯片上的一个刷新周期包括多个刷新行为,以保持内存中的数据。

刷新周期由刷新间隔(Refresh Interval)和刷新行数(Number of Refreshes)两个参数决定。

刷新间隔表示两次刷新之间的时间间隔,通常以行数或毫秒计算;刷新行数表示每次刷新执行的行数。

刷新周期的设置应该满足芯片厂商的规格要求,并考虑到系统的稳定性和性能需求。

2. CAS延迟(CAS Latency)CAS延迟是SDRAM的一项重要参数,表示从引脚触发读操作时到真正开始执行读操作之间的时间延迟。

CAS延迟的设置影响总线的延迟时间和读取速度。

较低的CAS延迟值可以提高性能,但可能会增加系统的稳定性问题。

在选择CAS延迟值时,需要根据具体平台的要求和SDRAM芯片的规格进行合理设置。

3. RAS到CAS延迟(RAS to CAS Delay)RAS到CAS延迟表示从行地址选定到列地址选定期间的时间延迟。

它是影响SDRAM读取性能的另一个重要参数。

较低的RAS到CAS延迟值可以提高读取速度,但可能会增加系统稳定性问题。

在设置RAS到CAS延迟值时,需要综合考虑平台要求、SDRAM芯片规格和稳定性需求。

4. 前导延迟(Precharge Delay)前导延迟是指当一个行被关闭之后,必须等待一段时间才能执行新的行访问操作。

较低的前导延迟值可以减少访问延迟,提高系统性能,但可能会增加稳定性问题。

Timing Advance Processor EG DYNAMIC用户手册说明书

Timing Advance ProcessorEG DYNAMICuser manualver. 2.7.1 dated 2021-06-22This instruction can be also downloaded from:https://europegas.pl/en/wsparcie-techniczne/Table of content1. Timing Advance Processor “EG Dynamic” description (3)2. Description of signal connections (4)2.1. Power supply source (4)2.2. MAP signal (optional) (5)2.3. TPS signal (5)2.4. Activation signal (5)2.5. Crankshaft position sensor and camshaft position sensor signals (5)2.6. Diagnostic interface plug (6)2.7. Proper installation of TAP EG Dynamic ECU (7)3. Software description (8)3.1. Right panel – actual value of system parameters: (8)3.2. Left panel – Settings bookmark (9)3.3. Middle panel – Maps (11)4. EG Dynamic TAP Calibration step-by-step (12)Hint: Click with Your left mouse button on any of above chapters to go to its page.1. Timing Advance Processor “EG Dynamic” description.EG DYNAMIC Timing advance processor dynamically changes the moment of engine's ignition while it is running on LPG/CNG fuel to improve combustion process efficiency. This way vehicle's engine works more dynamically. Power losses during acceleration are practically eliminated. Advance of ignition is very important when engine runs on CNG because CNG-air mixture combustion time is much longer comparing to combustion time of petrol-air mixture. Usage of Timing Advance Processor also eliminates risk of backfiring and significantly reduces gas consumption. We can say that it is temporarily adapting the original vehicle's ignition system to use LPG/CNG so the difference between driving on both fuel is practically imperceptible.Main advantages of EG DYNAMIC Timing Advance Processor are:∙It is no longer necessary to keep different TAP models depending on type of the crankshaft/camshaft position signal type in particular car.EG DYNAMIC is scanning, learning and supporting all inductive and digital crankshaft and camshaft signals.∙Very easy calibration and configuration process with usage of multipliers user interface.∙Possibility of dynamic and smooth advancing or delaying of ignition angle up to +-30 degrees, depending on the current values of TPS position, RPM and MAP signals.∙Single TAP device supports one inductive sensor and up to two digital sensors simultaneously (STD version) or three digital sensors simultaneously (3D version). It is possible to connect them in any configuration.∙Flexible adjustment of TAP activation moment . Advancing of ignition depends on actual values of RPM and TPS signal and can be activated by “+” or by “-” signal.∙Deactivation of TAP and restoring the original RPM signal in case of emergency can be done easily by pulling out the fuse from fuse holder.2. Description of signal connections2.1. Power supply sourceAttention:Device is destined to be used in cars with +12V power supply installation.Power supply should be connected to such a place from where the device is powered all the time while engine is running. It should be present from the moment of turning ignition key in ACC position until the engine will be switched off. It is unacceptable to connect this line to places where +12V might dissapear: for example, where voltage may drop out while engine is in the cut-off conditions.Hint: In OSCAR-N SAS ECU we should connect it to the red-white wire connected to the +12V ignition from the key.Power supply wire is equipped with 1A circuit fuse, which after removal allows us to disable TAP operation and restore the original RPM signal without necessity of shortening the original camshaft/crankshaft signal wires.2.2. MAP signal (optional)V oltage signal taken from the signal wire of Manifold Absolute Pressure sensor.This connection enables to measure the vacuum signal in the intake manifold so it is possible to make corrections of ignition point angle depending on engine load.Hint: In OSCAR-N SAS ECU we should connect it to the blue wire which goes to mapsensor [pin no. 3 in 4-pole AMP mapsensor plug].2.3. TPS signalSignal of Throttle position sensor or acceleration pedal sensor. Connecting that signal is required for proper calibration and detection of idle and cut-off conditions. TPS signal wire is the one on which voltage (regarding the ground ) changes its value fluently (eg. from 0 to 5V) when we are pressing on the accelerator pedal when vehicle's ignition key is on.2.4. Activation signalSignal which indicates when vehicle is running on gas and when on petrol. It is being used for activation of TAP to start advancing the original RPM signal when all cylinders has been switched to gas fuel.Hint. In case of use of OSCAR-N SAS system the best way of taking the activation signal is connecting to pink wire also used for disconnection of petrol fuel pump when system is on gas.Negative (“-”) signal appears on pink wire when OSCAR-N system is completely switched to gas and disappears in the moment when the system is switched back to petrol.We can also take positive (“+”) activation signal from +12V solenoid valve wire. In such case we should set proper type of gas activation signal (by “+”) in the EG Dynamic software. Gas controller should also be configured in such way to eliminate delays between moment of activating solenoid valves and changeover to gas.2.5. Crankshaft position sensor and camshaft position sensor signalsTo correct configuration we need to properly identify and connect the crankshaft position sensor and the camshaft position sensor(-s) (if present), are located. First, we set the sensor type: •if the connector have two pins, it is an inductive sensor type (resistance value for a typical inductive sensor is approximately 1 kOhm)•if connector has three-pins, it can be inductive sensor type(two pins sensor, the third pin ground. The resistance between the two pins of the sensor is approximately 1 kOhm, and the third pin from the ECU is connected to the ground)•if connector has three-pins, it can be digital sensor type(ground, power supply, signal).One pin from the ECU is connected to ground, the other is power "+12V from the ignition key", the third one is a signal cable).Attention: In controllers equipped with 3 digital channels (3D) it is not possible to configure the inductive sensor (the program automatically detects the type of device).Crankshaft position sensor signal:Main and most important signal to connect is the crankshaft position sensor signal. Camshaft position sensor signal don't have to be connected if it is not necessary to do so. This kind of necessity might happen when the original ECM of the car is report errors related with not synchronizing the camshaft position signal while advancing the signal from crankshaft position sensor. At first we should identify the type of sensor. Inductive sensor -usually it has pins which goes to two lines covered by a screen. Resistance measured between these two lines is around 1000 Ohm. If there are three pins, two of them are connected to signal lines and third one is connected with screen which is the ground signal of vehicle's ECU.Hint if possible we should find the place to cut into signal wires at where additional cover/screen insulation of signal wires is not present. First we should identify two signal wires, cut them and make serial connection by connecting proper pairs of wires from TAP device.There are four wires used to cut into vehicle's inductive signal wires: yellow and white -channel A, green and brown -channel B. We should start with cutting only one signal wire at a time (let's name it 'signal wire A') and connect first pair of inductive signal wires from TAP device:•yellow wire -should be connected with vehicle's inductive signal wire A input going from the inductive sensor•white wire -should be connected with vehicle's inductive signal wire A output going to the petrol ECU Then we proceed with cutting second signal wire (let's name it 'signal wire B') and connect remaining pair of inductive signal wires from TAP device:•green wire -should be connected with vehicle's inductive signal wire B input going from the inductive sensor•brown wire -should be connected with vehicle's inductive signal wire B output going to the petrol ECUAttention: If above connections will be made improperly we may be be not possible to start the vehicle.Camshaft position sensor:Digital sensor. Usually that kind of sensor have three lines signal, ground, power supply: +5V or +12V signal. We should cut only the signal wire and connect it serial to digital channel pair of wires.Hint: The original wire of signal input from digital sensor should be always connected to the color wire with black stripe (blue- black or yellow-black color). The adequate color wire without stripe should always be connected to that part of original vehicle's sensor signal wire which goes to the petrol ECU (blue or yellow color). Otherwise it might cause problem with engine work2.6. Diagnostic interface plugDiagnostic interface wire plug should be connected to EG Dynamic interface. It is possible to establish connection only if the TAP device is powered by +12V (the ignition key is on).2.7. Proper installation of TAP EG Dynamic ECUDuring the installation of TAP EG Dynamic ECU is suggested for the wire set to point downwards. It is also suggested that it should be placed in such a way to avoid the negative impact of high temperature and humidity. It is highly prohibited to spray ECU box with water jets or expose it to long lasting contact with water.3. Software description3.1. Right panel – actual value of system parameters:•Shifting – this value is informing if the impulses are being advanced or delayed (ON) or not (OFF) at the present moment.•Gas– this value is signaling on what fuel the car the car is actually running: on gas (ON) or petrol (OFF).•Angle [`] - angle value (in degrees) by which the current revolutions signal is being shifted.•RPM– rotary engine speed value.•TPS [%]– position of throttle position percentage (accelerator pedal).•MAP [kPa]– actual value of pressure in the intake manifold (engine load).•Inductive [Hz] - the current number of pulses per second for a signal from the inductive sensor.•Digital 1 [Hz] - The current number of pulses per second for a digital sensor signal no.•Digital 2 [Hz] - The current number of pulses per second for a digital sensor signal no.•Power supply [V]- power supply value. This value shouldn't be lower than 9V and not higher than 15V.If any parameter is marked by purple colour, it means that its value is out of allowed working range which determines when signal shifting can be done. Eg. the car is not in gas mode or the TPS signal is below minimum value which has been programmed to start shifting..If any parameter is marked by red colour, it means that its value is beyond the border value. Itprevents proper operation of TAP device. It might also mean that device does not recognize the shape of sensor signal wave. In such case it is necessary to physically check the signal connection and do another signal scanning from the software.3.2. Left panel – Settings bookmark•TPS Calibration - calibration of the minimum and maximum TPS input voltages for fully depressed and pressed accelerator pedal.•Enabling configuration - conditions that must be fulfilled so in the automatic mode the signal pulses shifting can be done.•Advanced◦Pressure sensor - selects the type MAP pressure sensor connected (in OSCAR-N SAS it's ABS400kPa).◦Signaling work on the gas- the choice of polarization of signal which enables shifting the signal pulses: If the TAP activation wire connection has been done topositive signal wire (like +12V solenoid valve wire) we need to choose “plus”. Ifwe've connected it to fuel pump disconnection signal (pink wire from OSCAR-NSAS which gives “ground” signal) we need to choose “minus”.◦TPS acceleration correction - the choice of TPS signal changes sensitivity. It's helpful in cases at which original ignition signal angle temporary increasessignificantly when accelerating. This allows to temporary increase the angle of signalshifting by extra velue for the rapid accelerations to compensate this signal change. Itworks only if RPM value is less than 1500 RPM.Attention: It is not reccomended to increase value of that parameter if it is notnecessary.◦Allowed retard – extends shift range for negative value. Default setting is OFF. Only for conversion from CNG to LPG use this option to retard ignition.•Inductive sensor, digital sensor 1, digital sensor 2◦Connections - selection of type of shaft where signal has been connected.◦Impulses per 1 revolution: number of pulses per revolution detected during a scan run (control value)◦Scan – starts automatic scanning the sensor signal wave. Should be carried out under stable conditions when the engine is running on idle. It is necessary to provide the actualvalue of engine rotary speed before starting scanning.In case that we've already scanned the wave of crankshaft sensor signal, and we need toget the shape of camshaft position signal wave we can select that option to allow thesignal to be read from that channel.Attention:It is very important to always start scanning from the crankshaft sensorsignal, and proceed to scanning of the camshaft sensors signals (if they have beenconnected)◦Preview - feature which enable us to check the shape of scanned sensor signal wave.3.3. Middle panel – MapsMap of the angle shifting regarding enginerotary speed.Point of the violet line indicates the currentsignal pulses shifting offset (in degrees).It is recommended to set a lower angle valueat higher rotary speeds.Multiplier Correction (eg. 1.0 is 100%, 0.6 is60% of original shifting offset) of the angleregarding the engine manifold absolutepressure(load).For heavy loads is recommended to set theadjustment below 1.0 to do not increase theengine knock value.Multiplier Correction (eg. 1.0 is 100%, 0.6 is60% of original shifting offset) of the angleregarding the TPS signal value.For idle conditions signal pulses shiftingshould be disabed , because it can lead toengines RPM waving in some type ofvehicles.We can do it by lowering themultiplier line on the map or in the Settingspanel.Allowed shortcuts and controls for map modification:•Left mouse button - move the points in the X and Y axis.•Right mouse button - move only points in Y axis.•Double click by left mouse button -add or remove point.•Arrow left, arrow right - selection of point.•Shift + arrow left, Shift + arrow righ t - selection of a group of points.•Ctrl + A – selection of all the points.•Arrow up, Arrow down - moving points in the Y-axis.•Home, End - moving points in the Y-axis with a higher speed•Ctrl + arrow up, Ctrl + down, Ctrl + left, Ctrl + right -moves points in the X and Y•Insert - adds another point•Delete - removes the selected point•Page Up, Page Down - moves the whole multiplier line in the Y-axis4. EG Dynamic TAP Calibration step-by-step.1.Establishing a connection– Turn on the ignition key to give +12V to the TAP device.Please select the right the serial port number from "Port" menu to establish a connection with diagnostic interface device.2.Calibrate TPS - while the engine is off, please make sure that ignition from the key is stillon and TAP device is being powered by +12V. In"TPS calibration", press"Set"button when the accelerator is fully depressed to remember that value as “Bottom TPS Threshold”.Then fully press the pedal all the way down and press "Set" button to store the maximum TPS voltage value as“Top TPS Threshold”.Check if changing the position of the acceleration pedal causes changing the current value of the TPS smoothly from 0 to 100%3.Selection of pressure sensor. -after selecting the appropriate sensor type when engine is off,and +12V from igniton on, the value of this parameter to indicate the MAP should be about 100 kPa. The default pressure sensor for OSCAR-N SAS is ABS400kPa.4.Selection of the activation of signal which indicates that vehicle is workng on gas-depending on where you connect the activation signal of TAP activation wire. If it has been connected to positive signal wire (eg. +12V solenoid valve wire) we need to choose “plus”.If we've connected it to fuel pump disconnection signal (eg. pink wire from OSCAR-N SAS which gives “ground” signal) we need to choose “minus”.5.Crankshaft sensor configuration - depending on the type of sensor and connection made toit (inductive or digital) we need to select proper type of that sensor in“Settings”panel.Then we should run a scan when the car is having working temperature and it is running on idle conditions..6.Camshaft sensors configuration–camshaft sensors should be connected only whennecessary (eg. when while shifting only the pulses from the crankshaft sensor, there is a check-engine associated with the camshaft sensor). The process of configuration is the same as in the case the crankshaft sensor configuration.7.Configuration of conditions of shifting the sensors pulses-In "Enabling configuration"panel we have to select the desired scopes of the TPS position, rotary speed, and select the “Shifting mode” to “automatic”. Mode “Always”which is permanently forcing TAP to shitf the signal pulses should be used onlyfor diagnostic purposes.8.Setting the map – We can leave default maps of sensor signal shifting or we can modify itaccording our requirements depending on the rotary speed, and the correction of the position of the TPS and MAP (load).。

PIC16LF1508-ISS;PIC16F1508-ISS;PIC16LF1509-ISS;PIC16F1509-ISS;中文规格书,Datasheet资料

Trademarks The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC32 logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, , dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, , PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. © 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved. Printed on recycled paper. ISBN: 978-1-61341-726-3

CY7C63723-PC中文资料

元器件交易网CY7C63743CY7C63722/23CY7C63743enCoRe™ USBCombination Low-Speed USB & PS/2Peripheral ControllerTABLE OF CONTENTS1.0 FEATURES (5)2.0 FUNCTIONAL OVERVIEW (6)2.1 enCoRe USB - The New USB Standard (6)3.0 LOGIC BLOCK DIAGRAM (7)4.0 PIN CONFIGURATIONS (7)5.0 PIN ASSIGNMENTS (7)6.0 PROGRAMMING MODEL (8)6.1 Program Counter (PC) (8)6.2 8-bit Accumulator (A) (8)6.3 8-bit Index Register (X) (8)6.4 8-bit Program Stack Pointer (PSP) (8)6.5 8-bit Data Stack Pointer (DSP) (9)6.6 Address Modes (9)6.6.1 Data (9)6.6.2 Direct (9)6.6.3 Indexed (9)7.0 INSTRUCTION SET SUMMARY (10)8.0 MEMORY ORGANIZATION (11)8.1 Program Memory Organization (11)8.2 Data Memory Organization (12)8.3 I/O Register Summary (13)9.0 CLOCKING (14)9.1 Internal/External Oscillator Operation (15)9.2 External Oscillator (16)10.0 RESET (16)10.1 Low-voltage Reset (LVR) (16)10.2 Brown Out Reset (BOR) (16)10.3 Watchdog Reset (WDR) (17)11.0 SUSPEND MODE (17)11.1 Clocking Mode on Wake-up from Suspend (18)11.2 Wake-up Timer (18)12.0 GENERAL PURPOSE I/O PORTS (18)12.1 Auxiliary Input Port (21)13.0 USB SERIAL INTERFACE ENGINE (SIE) (22)13.1 USB Enumeration (22)13.2 USB Port Status and Control (22)14.0 USB DEVICE (24)14.1 USB Address Register (24)14.2 USB Control Endpoint (24)14.3 USB Non-control Endpoints (25)14.4 USB Endpoint Counter Registers (26)15.0 USB REGULATOR OUTPUT (27)16.0 PS/2 OPERATION (27)17.0 SERIAL PERIPHERAL INTERFACE (SPI) (28)17.1 Operation as an SPI Master (29)17.2 Master SCK Selection (29)17.3 Operation as an SPI Slave (29)17.4 SPI Status and Control (30)17.5 SPI Interrupt (31)17.6 SPI Modes for GPIO Pins (31)18.0 12-BIT FREE-RUNNING TIMER (31)19.0 TIMER CAPTURE REGISTERS (32)20.0 PROCESSOR STATUS AND CONTROL REGISTER (35)21.0 INTERRUPTS (36)21.1 Interrupt Vectors (37)21.2 Interrupt Latency (37)21.3 Interrupt Sources (37)22.0 USB MODE TABLES (42)23.0 REGISTER SUMMARY (47)24.0 ABSOLUTE MAXIMUM RATINGS (48)25.0 DC CHARACTERISTICS (48)26.0 SWITCHING CHARACTERISTICS (50)27.0 ORDERING INFORMATION (55)28.0 PACKAGE DIAGRAMS (55)LIST OF FIGURESFigure 8-1. Program Memory Space with Interrupt Vector Table (11)Figure 8-2. Data Memory Organization (12)Figure 9-1. Clock Oscillator On-chip Circuit (14)Figure 9-2. Clock Configuration Register (Address 0xF8) (14)Figure 10-1. Watchdog Reset (WDR, Address 0x26) (17)Figure 12-1. Block Diagram of GPIO Port (one pin shown) (19)Figure 12-2. Port 0 Data (Address 0x00) (19)Figure 12-3. Port 1 Data (Address 0x01) (19)Figure 12-4. GPIO Port 0 Mode0 Register (Address 0x0A) (20)Figure 12-5. GPIO Port 0 Mode1 Register (Address 0x0B) (20)Figure 12-6. GPIO Port 1 Mode0 Register (Address 0x0C) (20)Figure 12-7. GPIO Port 1 Mode1 Register (Address 0x0D) (20)Figure 12-8. Port 2 Data Register (Address 0x02) (21)Figure 13-1. USB Status and Control Register (Address 0x1F) (23)Figure 14-1. USB Device Address Register (Address 0x10) (24)Figure 14-2. Endpoint 0 Mode Register (Address 0x12) (25)Figure 14-3. USB Endpoint EP1, EP2 Mode Registers (Addresses 0x14 and 0x16) (26)Figure 14-4. Endpoint 0,1,2 Counter Registers (Addresses 0x11, 0x13 and 0x15) (26)Figure 17-1. SPI Block Diagram (28)Figure 16-1. Diagram of USB-PS/2 System Connections (28)Figure 17-2. SPI Data Register (Address 0x60) (29)Figure 17-3. SPI Control Register (Address 0x61) (30)Figure 17-4. SPI Data Timing (31)Figure 18-1. Timer LSB Register (Address 0x24) (31)Figure 18-2. Timer MSB Register (Address 0x25) (32)Figure 18-3. Timer Block Diagram (32)Figure 19-1. Capture Timers Block Diagram (33)Figure 19-2. Capture Timer A-Rising, Data Register (Address 0x40) (33)Figure 19-3. Capture Timer A-Falling, Data Register (Address 0x41) (34)Figure 19-4. Capture Timer B-Rising, Data Register (Address 0x42) (34)Figure 19-5. Capture Timer B-Falling, Data Register (Address 0x43) (34)Figure 19-6. Capture Timer Status Register (Address 0x45) (34)Figure 19-7. Capture Timer Configuration Register (Address 0x44) (34)Figure 20-1. Processor Status and Control Register (Address 0xFF) (35)Figure 21-1. Global Interrupt Enable Register (Address 0x20) (38)Figure 21-2. Endpoint Interrupt Enable Register (Address 0x21) (39)Figure 21-3. Interrupt Controller Logic Block Diagram (40)Figure 21-4. Port 0 Interrupt Enable Register (Address 0x04) (40)Figure 21-5. Port 1 Interrupt Enable Register (Address 0x05) (40)Figure 21-6. Port 0 Interrupt Polarity Register (Address 0x06) (41)Figure 21-7. Port 1 Interrupt Polarity Register (Address 0x07) (41)Figure 21-8. GPIO Interrupt Diagram (41)Figure 26-1. Clock Timing (51)Figure 26-2. USB Data Signal Timing (51)Figure 26-3. Receiver Jitter Tolerance (52)Figure 26-4. Differential to EOP Transition Skew and EOP Width (52)Figure 26-5. Differential Data Jitter (52)Figure 26-7. SPI Slave Timing, CPHA = 0 (53)Figure 26-6. SPI Master Timing, CPHA = 0 (53)Figure 26-8. SPI Master Timing, CPHA = 1 (54)Figure 26-9. SPI Slave Timing, CPHA = 1 (54)LIST OF TABLESTable 8-1. I/O Register Summary (13)Table 11-1. Wake-up Timer Adjust Settings (18)Table 12-1. Ports 0 and 1 Output Control Truth Table (21)Table 13-1. Control Modes to Force D+/D– Outputs (24)Table 17-1. SPI Pin Assignments (31)Table 19-1. Capture Timer Prescalar Settings (Step size and range for FCLK = 6 MHz) (35)Table 21-1. Interrupt Vector Assignments (37)Table 22-1. USB Register Mode Encoding for Control and Non-Control Endpoints (42)Table 22-2. Decode table for Table 22-3: “Details of Modes for Differing Traffic Conditions” (44)Table 22-3. Details of Modes for Differing Traffic Conditions (45)Table 28-1. CY7C63722-XC Probe Pad Coordinates in microns ((0,0) to bond pad centers) (57)1.0 Features•enCoRe™ USB - enhanced Component Reduction—Internal oscillator eliminates the need for an external crystal or resonator—Interface can auto-configure to operate as PS/2 or USB without the need for external components to switch between modes (no GPIO pins needed to manage dual mode capability)—Internal 3.3V regulator for USB pull-up resistor—Configurable GPIO for real-world interface without external components•Flexible, cost-effective solution for applications that combine PS/2 and low-speed USB, such as mice, gamepads, joysticks, and many others.•USB Specification Compliance—Conforms to USB Specification, Version 2.0—Conforms to USB HID Specification, Version 1.1—Supports 1 Low-Speed USB device address and 3 data endpoints—Integrated USB transceiver—3.3V regulated output for USB pull-up resistor•8-bit RISC microcontroller—Harvard architecture—6-MHz external ceramic resonator or internal clock mode—12-MHz internal CPU clock—Internal memory—256 bytes of RAM—8 Kbytes of EPROM—Interface can auto-configure to operate as PS/2 or USB—No external components for switching between PS/2 and USB modes—No GPIO pins needed to manage dual mode capability•I/O ports—Up to 16 versatile General Purpose I/O (GPIO) pins, individually configurable—High current drive on any GPIO pin: 50 mA/pin current sink—Each GPIO pin supports high-impedance inputs, internal pull-ups, open drain outputs or traditional CMOS outputs —Maskable interrupts on all I/O pins•SPI serial communication block—Master or slave operation—2 Mbit/s transfers•Four 8-bit Input Capture registers—Two registers each for two input pins—Capture timer setting with 5 prescaler settings—Separate registers for rising and falling edge capture—Simplifies interface to RF inputs for wireless applications•Internal low-power wake-up timer during suspend mode—Periodic wake-up with no external components•Optional 6-MHz internal oscillator mode—Allows fast start-up from suspend mode•Watchdog Reset (WDR)•Low-voltage Reset at 3.75V•Internal brown-out reset for suspend mode•Improved output drivers to reduce EMI•Operating voltage from 4.0V to 5.5VDC•Operating temperature from 0 to 70 degrees Celsius•CY7C63723 available in 18-pin SOIC, 18-pin PDIP•CY7C63743 available in 24-pin SOIC, 24-pin PDIP•CY7C63722 available in DIE form•Industry standard programmer support2.0 Functional Overview2.1enCoRe USB - The New USB StandardCypress has re-invented its leadership position in the low-speed USB market with a new family of innovative microcontrollers. Introducing...enCoRe USB—“enhanced Component Reduction.” Cypress has leveraged its design expertise in USB solutions to create a new family of low-speed USB microcontrollers that enables peripheral developers to design new products with a minimum number of components. At the heart of the enCoRe USB technology is the breakthrough design of a crystal-less oscillator. By integrating the oscillator into our chip, an external crystal or resonator is no longer needed. We have also integrated other external components commonly found in low-speed USB applications such as pull-up resistors, wake-up circuitry, and a 3.3V regulator. All of this adds up to a lower system cost.The CY7C637xx is an 8-bit RISC One Time Programmable (OTP) microcontroller. The instruction set has been optimized specif-ically for USB and PS/2 operations, although the microcontrollers can be used for a variety of other embedded applications. The CY7C637xx features up to 16 general purpose I/O (GPIO) pins to support USB, PS/2 and other applications. The I/O pins are grouped into two ports (Port 0 to 1) where each pin can be individually configured as inputs with internal pull-ups, open drain outputs, or traditional CMOS outputs with programmable drive strength of up to 50 mA output drive. Additionally, each I/O pin can be used to generate a GPIO interrupt to the microcontroller. Note the GPIO interrupts all share the same “GPIO” interrupt vector. The CY7C637xx microcontrollers feature an internal oscillator. With the presence of USB traffic, the internal oscillator can be set to precisely tune to USB timing requirements (6 MHz ±1.5%). Optionally, an external 6-MHz ceramic resonator can be used to provide a higher precision reference for USB operation. This clock generator reduces the clock-related noise emissions (EMI). The clock generator provides the 6- and 12-MHz clocks that remain internal to the microcontroller.The CY7C637xx has 8 Kbytes of EPROM and 256 bytes of data RAM for stack space, user variables, and USB FIFOs.These parts include low-voltage reset logic, a watchdog timer, a vectored interrupt controller, a 12-bit free-running timer, and capture timers. The low-voltage reset (LVR) logic detects when power is applied to the device, resets the logic to a known state, and begins executing instructions at EPROM address 0x0000. LVR will also reset the part when V CC drops below the operating voltage range. The watchdog timer can be used to ensure the firmware never gets stalled for more than approximately 8 ms. The microcontroller supports 10 maskable interrupts in the vectored interrupt controller. Interrupt sources include the USB Bus-Reset, the 128-µs and 1.024-ms outputs from the free-running timer, three USB endpoints, two capture timers, an internal wake-up timer and the GPIO ports. The timers bits cause periodic interrupts when enabled. The USB endpoints interrupt after USB transactions complete on the bus. The capture timers interrupt whenever a new timer value is saved due to a selected GPIO edge event. The GPIO ports have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each GPIO pin. The interrupt polarity can be either rising or falling edge.The free-running 12-bit timer clocked at 1 MHz provides two interrupt sources as noted above (128 µs and 1.024 ms). The timer can be used to measure the duration of an event under firmware control by reading the timer at the start and end of an event, and subtracting the two values. The four capture timers save a programmable 8 bit range of the free-running timer when a GPIO edge occurs on the two capture pins (P0.0, P0.1).The CY7C637xx includes an integrated USB serial interface engine (SIE) that supports the integrated peripherals. The hardware supports one USB device address with three endpoints. The SIE allows the USB host to communicate with the function integrated into the microcontroller. A 3.3V regulated output pin provides a pull-up source for the external USB resistor on the D– pin.The USB D+ and D– USB pins can alternately be used as PS/2 SCLK and SDATA signals, so that products can be designed to respond to either USB or PS/2 modes of operation. PS/2 operation is supported with internal pull-up resistors on SCLK and SDATA, the ability to disable the regulator output pin, and an interrupt to signal the start of PS/2 activity. No external components are necessary for dual USB and PS/2 systems, and no GPIO pins need to be dedicated to switching between modes. Slow edge rates operate in both modes to reduce EMI.3.0 Logic Block Diagram4.0 Pin Configurations5.0 Pin AssignmentsNameI/O CY7C63723CY7C63743CY7C63722Description18-Pin 24-Pin 25-Pad D–/SDATA,D+/SCLK I/O 121315161617USB differential data lines (D– and D+), or PS/2 clock and data signals (SDATA and SCLK)P0[7:0]I/O1, 2, 3, 4,15, 16, 17, 181, 2, 3, 4,21, 22, 23, 241, 2, 3, 4,22, 23, 24, 25GPIO Port 0 capable of sinking up to 50 mA/pin, or sinking controlled low or high programmable current.Can also source 2 mA current, provide a resistive pull-up, or serve as a high-impedance input. P0.0 and P0.1 provide inputs to Capture Timers A and B, respec-tively.P1[7:0]I/O5, 145, 6, 7, 8,17, 18, 19, 205, 6, 7, 8,18, 19, 20, 21IO Port 1 capable of sinking up to 50 mA/pin, or sinking controlled low or high programmable current. Can alsosource 2 mA current, provide a resistive pull-up, or serve as a high-impedance input.Wake-Up 12-bit Timer USB &D+,D–P1.0–P1.7Interrupt ControllerPort 0P0.0–P0.7GPIO8-bit RISC Xtal RAM 256 Byte EPROM 8K ByteCoreBrown-out Reset XcvrWatch Timer Dog 3.3V Port 1GPIO Capture TimersUSB Engine PS/2Internal Oscillator Oscillator Low ResetVoltage RegulatorTimerSPIXTALOUTXTALIN/P2.1VREG/P2.01234569111516171819202221P0.0P0.1P0.2P0.3P1.0P1.2VSS VREG/P2.0P0.6P1.5P1.1P1.3D+/SCLK P1.7D–/SDATA VCC14P0.710VPPXTALIN/P2.1XTALOUT121378P1.4P1.62423P0.4P0.524-pin SOIC/PDIPCY7C6374312346781011121315161817P0.0P0.1P0.2P0.3VSS VREG/P2.0P0.4P0.6P0.7D+/SCLK D–/SDATA VCC18-pin SOIC/PDIPP0.59VPPXTALIN/P2.1XTALOUTCY7C63723514P1.0P1.1Top View4 5 6 7 8 93 P 0.21 P 0.0 2 P 0.125 P 0.4 24 P 0.523 P 0.622 21 20 19 1811121314151617P0.3P1.0P1.2P1.4P1.6 VSS VSS V P P X T A L I N /P 2.1V R E G X T A L O U T V C C D -/S D A T A D+/SCLK P0.7P1.1P1.3P1.5P1.7CY7C63722-XCDIE106.0 Programming ModelRefer to the CYASM Assembler User’s Guide for more details on firmware operation with the CY7C637xx microcontrollers.6.1Program Counter (PC)The 14-bit program counter (PC) allows access for up to 8 Kbytes of EPROM using the CY7C637xx architecture. The program counter is cleared during reset, such that the first instruction executed after a reset is at address 0x0000. This instruction is typically a jump instruction to a reset handler that initializes the application.The lower 8 bits of the program counter are incremented as instructions are loaded and executed. The upper 6 bits of the program counter are incremented by executing an XPAGE instruction. As a result, the last instruction executed within a 256-byte “page”of sequential code should be an XPAGE instruction. The assembler directive “XPAGEON” will cause the assembler to insert XPAGE instructions automatically. As instructions can be either one or two bytes long, the assembler may occasionally need to insert a NOP followed by an XPAGE for correct execution.The program counter of the next instruction to be executed, carry flag, and zero flag are saved as two bytes on the program stack during an interrupt acknowledge or a CALL instruction. The program counter, carry flag, and zero flag are restored from the program stack only during a RETI instruction.Please note the program counter cannot be accessed directly by the firmware. The program stack can be examined by reading SRAM from location 0x00 and up.6.28-bit Accumulator (A)The accumulator is the general-purpose, do everything register in the architecture where results are usually calculated.6.38-bit Index Register (X)The index register “X” is available to the firmware as an auxiliary accumulator. The X register also allows the processor to perform indexed operations by loading an index value into X.6.48-bit Program Stack Pointer (PSP)During a reset, the program stack pointer (PSP) is set to zero. This means the program “stack” starts at RAM address 0x00 and “grows” upward from there. Note that the program stack pointer is directly addressable under firmware control, using the MOV PSP ,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and RETI instructions under firmware control.During an interrupt acknowledge, interrupts are disabled and the program counter, carry flag, and zero flag are written as two bytes of data memory. The first byte is stored in the memory addressed by the program stack pointer, then the PSP is incremented.The second byte is stored in memory addressed by the program stack pointer and the PSP is incremented again. The net effect is to store the program counter and flags on the program “stack” and increment the program stack pointer by two.The return from interrupt (RETI) instruction decrements the program stack pointer, then restores the second byte from memory addressed by the PSP . The program stack pointer is decremented again and the first byte is restored from memory addressed by the PSP . After the program counter and flags have been restored from stack, the interrupts are enabled. The effect is to restore the program counter and flags from the program stack, decrement the program stack pointer by two, and re-enable interrupts.The call subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by two.XTALIN/P2.1IN 912136-MHz ceramic resonator or external clock input, or P2.1 inputXTALOUT OUT1013146-MHz ceramic resonator return pin or internal oscillator outputV PP 71011Programming voltage supply, ground for normal operation V CC111415Voltage supplyVREG/P2.0 81112Voltage supply for 1.3-k Ω USB pull-up resistor (3.3V nominal). Also serves as P2.0 input.V SS699, 10Ground5.0 Pin Assignments (continued)NameI/O CY7C63723CY7C63743CY7C63722Description18-Pin 24-Pin 25-PadThe return from subroutine (RET) instruction restores the program counter, but not the flags, from program stack and decrements the PSP by two.Note that there are restrictions in using the JMP, CALL, and INDEX instructions across the 4-KB boundary of the program memory. Refer to the CYASM Assembler User’s Guide for a detailed description.6.58-bit Data Stack Pointer (DSP)The data stack pointer (DSP) supports PUSH and POP instructions that use the data stack for temporary storage. A PUSH instruction will pre-decrement the DSP, then write data to the memory location addressed by the DSP. A POP instruction will read data from the memory location addressed by the DSP, then post-increment the DSP.During a reset, the Data Stack Pointer will be set to zero. A PUSH instruction when DSP equals zero will write data at the top of the data RAM (address 0xFF). This would write data to the memory area reserved for a FIFO for USB endpoint 0. In non-USB applications, this works fine and is not a problem.For USB applications, the firmware should set the DSP to an appropriate location to avoid a memory conflict with RAM dedicated to USB FIFOs. The memory requirements for the USB endpoints are shown in Section 8.2. For example, assembly instructions to set the DSP to 20h (giving 32 bytes for program and data stack combined) are shown below:MOV A,20h; Move 20 hex into Accumulator (must be D8h or less to avoid USB FIFOs)SWAP A,DSP; swap accumulator value into DSP register6.6Address ModesThe CY7C637xx microcontrollers support three addressing modes for instructions that require data operands: data, direct, and indexed.6.6.1DataThe “Data” address mode refers to a data operand that is actually a constant encoded in the instruction. As an example, consider the instruction that loads A with the constant 0x30:•MOV A, 30hThis instruction will require two bytes of code where the first byte identifies the “MOV A” instruction with a data operand as the second byte. The second byte of the instruction will be the constant “0xE8h”. A constant may be referred to by name if a prior “EQU” statement assigns the constant value to the name. For example, the following code is equivalent to the example shown above:•DSPINIT: EQU 30h•MOV A,DSPINIT6.6.2Direct“Direct” address mode is used when the data operand is a variable stored in SRAM. In that case, the one byte address of the variable is encoded in the instruction. As an example, consider an instruction that loads A with the contents of memory address location 0x10h:•MOV A, [10h]In normal usage, variable names are assigned to variable addresses using “EQU” statements to improve the readability of the assembler source code. As an example, the following code is equivalent to the example shown above:•buttons: EQU 10h•MOV A,[buttons]6.6.3Indexed“Indexed” address mode allows the firmware to manipulate arrays of data stored in SRAM. The address of the data operand is the sum of a constant encoded in the instruction and the contents of the “X” register. In normal usage, the constant will be the “base” address of an array of data and the X register will contain an index that indicates which element of the array is actually addressed:•array: EQU 10h•MOV X,3•MOV A,[x+array]This would have the effect of loading A with the fourth element of the SRAM “array” that begins at address 0x10h. The fourth element would be at address 0x13h.7.0 Instruction Set SummaryRefer to the CYASM Assembler User’s Guide for detailed information on these instructions. Note that conditional jump instructions (i.e., JC, JNC, JZ, JNZ) take 5 cycles if jump is taken, 4 cycles if no jump.MNEMONIC Operand Opcode Cycles MNEMONIC Operand Opcode Cycles HALT 007NOP 204ADD A,expr data014INC A acc214ADD A,[expr] direct026INC X x224ADD A,[X+expr] index037INC [expr] direct237ADC A,expr data044INC [X+expr] index248ADC A,[expr] direct056DEC A acc254ADC A,[X+expr] index067DEC X x264SUB A,expr data074DEC [expr] direct277SUB A,[expr] direct086DEC [X+expr] index288SUB A,[X+expr] index097IORD expr address295SBB A,expr data0A4IOWR expr address2A5SBB A,[expr] direct0B6POP A2B4SBB A,[X+expr] index0C7POP X2C4OR A,expr data0D4PUSH A2D5OR A,[expr] direct0E6PUSH X2E5OR A,[X+expr] index0F7SWAP A,X2F5AND A,expr data104SWAP A,DSP305AND A,[expr] direct116MOV [expr],A direct315AND A,[X+expr] index127MOV [X+expr],A index326XOR A,expr data134OR [expr],A direct337XOR A,[expr] direct146OR [X+expr],A index348XOR A,[X+expr] index157AND [expr],A direct357CMP A,expr data165AND [X+expr],A index368CMP A,[expr] direct177XOR [expr],A direct377CMP A,[X+expr] index188XOR [X+expr],A index388MOV A,expr data194IOWX [X+expr] index396MOV A,[expr] direct1A5CPL 3A4MOV A,[X+expr] index1B6ASL 3B4MOV X,expr data1C4ASR 3C4MOV X,[expr] direct1D5RLC 3D4reserved 1E RRC 3E4XPAGE 1F4RET 3F8MOV A,X404DI 704MOV X,A414EI 724MOV PSP,A604RETI 738CALL addr50 - 5F10JMP addr80-8F5JC addr C0-CF 5 (or 4) CALL addr90-9F10JNC addr D0-DF 5 (or 4)JZ addr A0-AF 5 (or 4)JACC addr E0-EF7JNZ addr B0-BF 5 (or 4)INDEX addr F0-FF148.0 Memory Organization8.1Program Memory Organization[1]After reset Address14 -bit PC0x0000Program execution begins here after a reset.0x0002USB Bus Reset interrupt vector0x0004128-µs timer interrupt vector0x0006 1.024-ms timer interrupt vector0x0008USB endpoint 0 interrupt vector0x000A USB endpoint 1 interrupt vector0x000C USB endpoint 2 interrupt vector0x000E SPI interrupt vector0x0010Capture timer A interrupt Vector0x0012Capture timer B interrupt vector0x0014GPIO interrupt vector0x0016Wake-up interrupt vector0x0018Program Memory begins here0x1FDF8 KB PROM ends here (8K - 32 bytes). See Note below Figure 8-1. Program Memory Space with Interrupt Vector TableNote:1.The upper 32 bytes of the 8K PROM are reserved. Therefore, the user’s program must not overwrite this space.8.2Data Memory OrganizationThe CY7C637xx microcontrollers provide 256 bytes of data RAM. In normal usage, the SRAM is partitioned into four areas: program stack, data stack, user variables and USB endpoint FIFOs as shown below:After reset Address8-bit DSP8-bit PSP0x00Program Stack Growth(User’s firmware movesDSP)8-bit DSP User Selected Data Stack GrowthUser Variables0xE8USB FIFO for Address A endpoint 20xF0USB FIFO for Address A endpoint 10xF8USB FIFO for Address A endpoint 0Top of RAM Memory0xFFFigure 8-2. Data Memory Organization8.3I/O Register SummaryI/O registers are accessed via the I/O Read (IORD) and I/O Write (IOWR, IOWX) instructions. IORD reads the selected port into the accumulator. IOWR writes data from the accumulator to the selected port. Indexed I/O Write (IOWX) adds the contents of X to the address in the instruction to form the port address and writes data from the accumulator to the specified port. Note that specifying address 0 with IOWX (e.g., IOWX 0h) means the I/O port is selected solely by the contents of X.Note:All bits of all registers are cleared to all zeros on reset, except the Processor Status and Control Register (Figure20-1). All registers not listed are reserved, and should never be written by firmware. All bits marked as reserved should always be written as 0 and be treated as undefined by reads.Table 8-1. I/O Register SummaryRegister Name I/O Address Read/Write Function Fig. Port 0 Data0x00R/W GPIO Port 012-2 Port 1 Data0x01R/W GPIO Port 112-3 Port 2 Data0x02R Auxiliary input register for D+, D–, VREG, XTALIN 12-8 Port 0 Interrupt Enable0x04W Interrupt enable for pins in Port 021-4 Port 1 Interrupt Enable0x05W Interrupt enable for pins in Port 121-5 Port 0 Interrupt Polarity 0x06W Interrupt polarity for pins in Port 021-6 Port 1 Interrupt Polarity 0x07W Interrupt polarity for pins in Port 121-7 Port 0 Mode0 0x0A W Controls output configuration for Port 012-4 Port 0 Mode10x0B W12-5 Port 1 Mode00x0C W Controls output configuration for Port 112-6 Port 1 Mode10x0D W12-7 USB Device Address0x10R/W USB Device Address register14-1 EP0 Counter Register0x11R/W USB Endpoint 0 counter register14-4 EP0 Mode Register0x12R/W USB Endpoint 0 configuration register14-2 EP1 Counter Register0x13R/W USB Endpoint 1 counter register14-4 EP1 Mode Register0x14R/W USB Endpoint 1 configuration register14-3 EP2 Counter Register0x15R/W USB Endpoint 2 counter register14-4 EP2 Mode Register0x16R/W USB Endpoint 2 configuration register14-3 USB Status & Control0x1F R/W USB status and control register13-1 Global Interrupt Enable0x20R/W Global interrupt enable register21-1 Endpoint Interrupt Enable0x21R/W USB endpoint interrupt enables21-2 Timer (LSB)0x24R Lower 8 bits of free-running timer (1 MHz)18-1 Timer (MSB)0x25R Upper 4 bits of free-running timer18-2 WDR Clear0x26W Watchdog Reset clear-Capture Timer A Rising0x40R Rising edge Capture Timer A data register19-2 Capture Timer A Falling0x41R Falling edge Capture Timer A data register19-3 Capture Timer B Rising0x42R Rising edge Capture Timer B data register19-4 Capture Timer B Falling0x43R Falling edge Capture Timer B data register19-5 Capture TImer Configuration0x44R/W Capture Timer configuration register19-7 Capture Timer Status0x45R Capture Timer status register19-6 SPI Data0x60R/W SPI read and write data register17-2 SPI Control0x61R/W SPI status and control register17-3 Clock Configuration0xF8R/W Internal / External Clock configuration register9-2 Processor Status & Control0xFF R/W Processor status and control20-1。

EM4205-4305 125kHz RFID 卡

EM4205 EM4305EM MICROELECTRONIC - MARIN SAHandling ProceduresAbsolute Maximum RatingsTiming CharacteristicsData Extractor timeout (t MONO)COIL1-COIL2TIMEOUTFIELD STOP t MONOTPower-up initialization (t PU)t PUFigure 3After the supply voltage crosses the POR threshold, the logic reads configuration word and then enters in default read mode. t PU is the time from turning on transmitter field to start of the default read mode.Block DiagramBlock DescriptionPower SupplyThis block integrates an AC/DC converter, which extracts the DC power from the incident RF field. It also acts as a limiter, which clamps the voltage on the coil terminals to avoid chip destruction in strong RF fields.Power On Reset (POR)When the EM4205/4305 with its attached coil enters the electromagnetic field, the built in AC/DC converter supplies voltage to the chip. The DC voltage is monitored and a Reset signal is generated to initialize the logic. The Power On Reset is also provided in order to make sure that the chip will start issuing correct data.Hysteresis is provided to avoid improper operation at the limit level. Data ExtractorThe transceiver generated field is amplitude modulated (field stops) to transmit data to the EM4205/4305. The Data Extractor detects absence of extracted clocks for periods longer than T MONO.ModulatorThe Data Modulator is driven by Logic. When the Modulator is switched ON, it draws a large current from the coil terminals, thus amplitude modulating the RF field. LogicLogic is composed of several sub-blocks, which are described in the following text.C CControllerEEPROM Organization512 bits of EEPROM are organized in 16 words of 32 bits.The EEPROM words are numbered from 0 to 15.The bits, in a word, are numbered from 0 to 31. The LSB first principle is always respected.The 32 bits of EEPROM word are programmed with one Write Word Command.Word 0 is assigned either to factory programmed Chip Type, resonant capacitor version and Customer Code number, or it can be reprogrammed by user to store some other data. Since this word is not part of the default message, it can be used to store some useful information which can only be accessed by the Read Word command.Word 1 contains the IC unique identification number (UID) RP: access using Read Word and Protect commandOrganization of Word 0Word 0 is factory programmed with information on:Chip Type: fixed 4 bit number indicating member ofthe compatible family of chips.On-chip resonant capacitor values: 210pF, 250pF, or330pF10 bit Customer codeWord 0 can be reprogrammed by the user.Note 1: RF/40 data rate only available on the EM4305 – 330pF Cres version. RF/40 data rate is linked with Manchester and Biphase data encodings. configured as following:co12 – co13Bi-phaseManchester00 Nodelay01 Delayed On – 8 RF clocks10 Delayed On – 16 RF clocks11 Nodelayco 14- co 17 Last Default Read Word (LWR).continue with the 16 LSB bits of Word 7.After sending us 15 of Word 7, readout continues without interruption with the first bit of Word 5.This data structure permits the locking of48 bits of the pigeon code and allows modification of the last 16 bits before the race.co 27 - co 31: Reserved for future use These bits must be set to logic 0.Words 14 and 15: Protection Wordsfollowed by the actual write operation. Should the operation be interrupted for any reason (e.g. tag removal from the field) the double buffer scheme ensures that no unwanted "0"-Protection Bits (i.e unprotected words) are introduced.EEPROM Delivery State Forward Link CommunicationRecommendations for Reader to Tag Timings14 RF periods. Increasing the field stops up to 23 RFFigure 10EM4095inputsFirst Field Stop“0’’ “1’’ “0’’ “0’’ “1’’MOD-ONMOD-OFFCommandssending any password protected command. In the Login command a 32 bit password including parity bits is sent as the command argument. The 32 bit password is sent according to the Data structure defined in table 12 (45 bits including parity). When the parity bits are correct and 32 bit password sent matches the content of Word 1, the login flag is set.Login flag is set until the next power-up, which means that Login command has to be sent only once after power up to enable execution of password protected commands. word is reloaded from the EEPROM, a preamble pattern (00001010) is sent and the chip returns to Default Read mode.Loading of Configuration word is useful when the Configuration word has just been changed so that new settings are loaded.If the Write Word command is not accepted (error in parity or at least one of the checks failed) error pattern 00000001 is sent and the IC returns to Default Read mode.Read Word CommandIn Read Word command the 4-bit word address is sent as command argument according to the structure described in table 11. When the command is correctly processed, a preamble pattern (00001010) followed bythe content of the 32 bit word is sent. Please, note thatDisable CommandData T PC T WEEAddressT PP Preamble READER "0011" Password Timings T PPProtectEM4205/4305 Default Read PreambleDefault ReadREADER "1100" Protection Timings T PCT PRDisableEM4205/4305 Default Read Disabled Mode READER "1010" "all1" data TimingsFigure 12EM4205 – EM4305 state transition diagramReturn Link EncoderEM4205 Pad LocationFigure 15Figure 16Pad DescriptionPad Name Function1 Coil2 Coil connection 22 Test Test purpose (NC) - Active pad3 V test 1 Test purpose (NC) - Active pad4 V test 2 Test purpose (NC) - Active pad5 Coil 1 Coil connection 1Table 13Note: Test pads (Test, Vtest1 and Vtest2) are electrically active and used for test purposes only, no connection allowed.Packaging informationPart NumberICReferenceIC ResonantcapacitorDeliveryformatRemarksEM4205V4DF2C+ EM4205 210pF Loose form Resonant capacitor trimmed (tolerance +/- 3%) EM4305V3DF2C+ EM4305 330pF LooseformTable 16Ordering Information – Die formPart Number Package Delivery FormEM4205V2WS11sawn wafer Wafer on frameEM4305V1WS11E sawn wafer Wafer on frameEM4305V2WS11E sawn wafer Wafer on frameEM4305V3WS11E sawn wafer Wafer on frameEM4305VXYYY-%%% Custom CustomTable 17EM Microelectronic-Marin SA (EM) makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in EM's General Terms of Sale located on the Company's web site. EM assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of EM are granted in connection with the sale of EM products, expressly or by implications. EM's products are not authorized for use as components in life support devices or systems.。

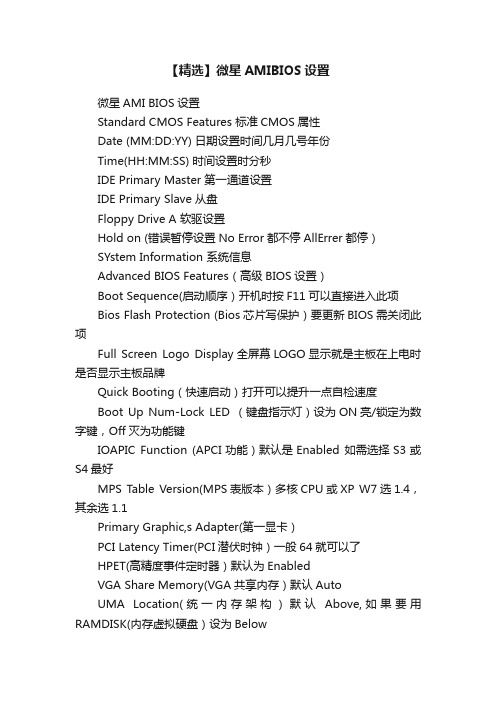

【精选】微星AMIBIOS设置

【精选】微星AMIBIOS设置微星AMI BIOS设置Standard CMOS Features 标准CMOS属性Date (MM:DD:YY) 日期设置时间几月几号年份Time(HH:MM:SS) 时间设置时分秒IDE Primary Master 第一通道设置IDE Primary Slave 从盘Floppy Drive A 软驱设置Hold on (错误暂停设置No Error都不停AllErrer都停)SYstem Information 系统信息Advanced BIOS Features(高级BIOS设置)Boot Sequence(启动顺序)开机时按F11可以直接进入此项Bios Flash Protection (Bios芯片写保护)要更新BIOS需关闭此项Full Screen Logo Display全屏幕LOGO显示就是主板在上电时是否显示主板品牌Quick Booting(快速启动)打开可以提升一点自检速度Boot Up Num-Lock LED (键盘指示灯)设为ON亮/锁定为数字键,Off灭为功能键IOAPIC Function (APCI功能)默认是Enabled 如需选择S3或S4最好MPS Table Version(MPS表版本)多核CPU或XP W7选1.4,其余选1.1Primary Graphic,s Adapter(第一显卡)PCI Latency Timer(PCI潜伏时钟)一般64就可以了HPET(高精度事件定时器)默认为EnabledVGA Share Memory(VGA共享内存)默认AutoUMA Location(统一内存架构)默认Above,如果要用RAMDISK(内存虚拟硬盘)设为BelowTCG/TPM(可信赖计算组/信任平台模块)我国禁止按住TPM模块CPU Feature是控制cpu状态(主要就是温度)用的[Press Enter]回车Support支持Chipset Feature (高级芯片组设置)默认为Auto HPET高精度事件定时器Boot Sequence(启动顺序)1st boot device 第一启动光盘1st FLOPPY DRI 第一软盘驱动器2nd boot device串口硬盘Boot From Other Device引导到其他设备默认EnabledtTrusted Computing可信任计算TPM Enable/Disable Status启用/禁用TPM芯片No state无状态Pooled state池状态TPM Owner Status(TPM的身份,地位)Integrated Peripherals(整合周边设备)USB Controller (南桥里的USB控制器)默认EnabledUSB Device Legacy Support(传统USB设备支持)针对USB键鼠默认EnabledOnboard LAN Controller(板载网卡)默认EnabledLAN Option ROM(网卡ROM(只读内存)启动)默认Diasabled Jmicron368 ATA Controller (Jmicron 368 ATA控制器)AMD平台默认EnabledOnboard USB3.0 Controller(板载USB3.0控制器)默认Enabled HD Audio Controller(高保真声卡)默认EnabledOn Chip ATA Device(芯片内ATA设备)PCI IDE Bus Master(PCI IDE总线控制)默认Disabled On Chip ATA Controller(芯片内SATA 控制器(南桥SATA控制器的开关)默认EnabledRAID Mode(RIDE模式)回车有三项:1IDE是把SATA硬盘桥接成IDE模式的硬盘,此模式安装XP 很方便;2 RAID是用2块及以上的SATA硬盘组建RAID阵列的设置。

艾默生质量流量计故障诊断和常见问题

Numbers correspond to terminal strip.

传感器故障诊断

• 驱动线圈和检测线圈阻值

(T)/(others) • 驱动 – 棕色到红色: 8 to 500/2650 ohms • LPO – 绿色到白色: 16 to 1000/300 ohms • RPO – 蓝色到灰色: 16 to 1000/300 ohms

外壳和显示可以 90 旋转360 .

用Prolink II故障诊断

常见诊断代码

代码

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14

A16 A17 A18

275显示信息

EEPROM Checksum - Core Processor RAM Error - Core Processor Sensor failure Temperature out of range Input over range Field device not characterizeded Real time interrupt failure Density outside limits Field device warming up Calibration failed Excess calibration correction, zero too low Excess calibration correction, zero too high Process too noisy to perform auto zero Electronics failure

2、流量计前方是否需安装消气器?管线存在气体怎么解决计量问题? 对管线是否存在气体的监控措施?

• 可用过密度测量值并辅助驱动增益(Drive%)来检测含气条件。 小口径的流量计(<=3”),当驱动增益超过15% 大口径的流量计(>=4”),当驱动增益超过20%

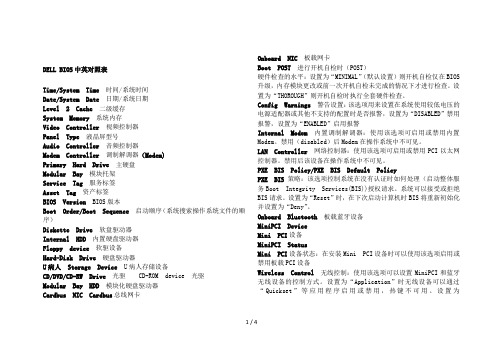

DEll电脑BIOS选项中英文对照

DELL BIOS中英对照表Time/System Time时间/系统时间Date/System Date日期/系统日期Level 2 Cache二级缓存System Memory系统内存Video Controller视频控制器Panel Type液晶屏型号Audio Controller音频控制器Modem Controller 调制解调器(Modem)Primary Hard Drive主硬盘Modular Bay模块托架Service Tag服务标签Asset Tag资产标签BIOS Version BIOS版本Boot Order/Boot Sequence启动顺序(系统搜索操作系统文件的顺序)Diskette Drive软盘驱动器Internal HDD内置硬盘驱动器Floppy device软驱设备Hard-Disk Drive硬盘驱动器U病人Storage Device U病人存储设备CD/DVD/CD-RW Drive光驱CD-ROM device 光驱Modular Bay HDD 模块化硬盘驱动器Cardbus NIC Cardbus总线网卡Onboard NIC板载网卡Boot POST 进行开机自检时(POST)硬件检查的水平:设置为“MINIMAL”(默认设置)则开机自检仅在BIOS 升级,内存模块更改或前一次开机自检未完成的情况下才进行检查。

设置为“THOROUGH”则开机自检时执行全套硬件检查。

Config Warnings 警告设置:该选项用来设置在系统使用较低电压的电源适配器或其他不支持的配置时是否报警,设置为“DISABLED”禁用报警,设置为“ENABLED”启用报警Internal Modem 内置调制解调器:使用该选项可启用或禁用内置Modem。

禁用(disabled)后Modem在操作系统中不可见。

LAN Controller 网络控制器:使用该选项可启用或禁用PCI以太网控制器。

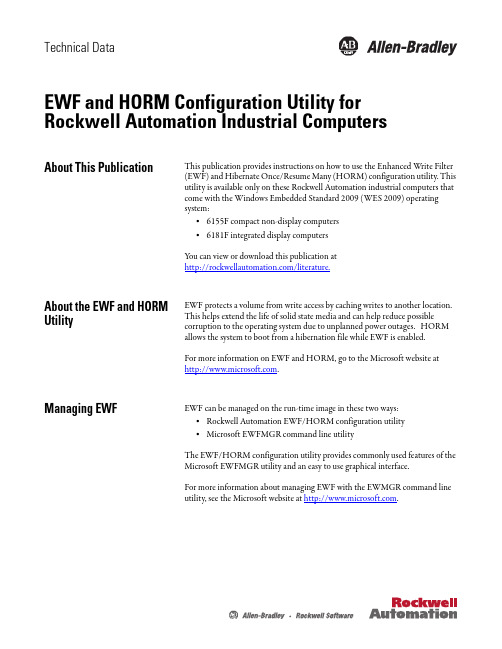

罗克威尔自动化工业电脑 - 增强写滤镜(EWF)和休眠一次唤醒多次(HORM)配置实用程序说明书

Technical DataEWF and HORM Configuration Utility for Rockwell Automation Industrial ComputersAbout This Publication This publication provides instructions on how to use the Enhanced Write Filter(EWF) and Hibernate Once/Resume Many (HORM) configuration utility. Thisutility is available only on these Rockwell Automation industrial computers thatcome with the Windows Embedded Standard 2009 (WES 2009) operatingsystem:•6155F compact non-display computers•6181F integrated display computersY ou can view or download this publication at/literature.About the EWF and HORM Utility EWF protects a volume from write access by caching writes to another location. This helps extend the life of solid state media and can help reduce possible corruption to the operating system due to unplanned power outages. HORM allows the system to boot from a hibernation file while EWF is enabled.For more information on EWF and HORM, go to the Microsoft website at .Managing EWF EWF can be managed on the run-time image in these two ways:•Rockwell Automation EWF/HORM configuration utility•Microsoft EWFMGR command line utilityThe EWF/HORM configuration utility provides commonly used features of theMicrosoft EWFMGR utility and an easy to use graphical interface.For more information about managing EWF with the EWMGR command lineutility, see the Microsoft website at .2 EWF and HORM Configuration Utility for Rockwell Automation Industrial ComputersStart the Utility The EWF/HORM configuration utility is pre-installed on all WES 2009 imagesand can be found as ‘EWFHORM Utility.exe’ in C:\ProgramFiles\EWFHORM Utility\. A shortcut has been provided for the initialadministrator logon.T o start the utility, double-click the EWFHORM utility shortcut.The shortcut loads the utility and displays this dialog box.TIP Only users with administrator rights can make changes to theEWF/HORM utility.Field Descriptions FieldDescription Overlay Type Displays the current mode of EWF. RAM (Reg) is the only mode supported on Rockwell Automation WES 2009 images and cannot be changed. This mode caches all writes to the physical random access memory (RAM) and the configuration information is stored in the system registry.Protected Drive Displays the volume protected by EWF. This will default to C: and cannot be changed on the run-time image.Overlay Level Some EWF configurations can allow multiple overlays. The RAM (Reg) mode allows only a single overlay and cannot be changed.Available RAM Displays the amount of physical RAM available to the system.EWF can attempt to allocate more physical RAM than is installed on the computer. The system can become unstable and unresponsive if the amount of physical RAM is too low. See Commit Changes to Disk for methods to free up physical RAM.For instructions on adding more RAM, see your computer’s user manual.EWF Status Displays the current status of the EWF. For more information on managing EWF, see the following sections.Overlay SizeDisplays the current size of the overlay size. This must be less than the amount of available RAM or else the system can become unstable. For more information on managing the overlay size, see the following sections.EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers 3Enable EWF The factory image comes with EWF in the disabled state.Follow these steps to enable EWF.1.Click Enable.2.Click Yes to enable EWF.Enabling EWF requires a system restart.3.Click Yes to restart.HORM StatusDisplays the current status of HORM. This is enabled by default. For more information on managing HORM, see Enable HORM and Disable HORM .Hibernate Hibernates the system.HORM must be enabled for the system to hibernate. If hibernation is not enabled on the system, the Hibernate button will put the system into standby.Reboot Restarts the system.CloseCloses the application. Minimizing the application at any time will then display an icon in the system tray.Field DescriptionsFieldDescription TIP Enable is unavailable if EWF is already enabled.4 EWF and HORM Configuration Utility for Rockwell Automation Industrial ComputersOnce EWF is enabled, the status screen displays Enabled.Disable EWF The following method is used to clear the contents of the overlay and disableEWF for RAM (Reg) overlay types.Please see Commit Changes to Disk if you would like to commit changes inaddition to disabling EWF.Follow these steps to disable EWF.1.Click Disable.2.Click Yes to disable EWF.Disabling the EWF requires a system restart.3.Click Yes to restart.4.Once the system restarts, start the utility.5.Click Commit/Disable EWF to complete the disable process.TIP Disable is unavailable if EWF is already disabled.EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers 5This will make sure the overlay is empty and immediately disable EWF.No restart is necessary after this step.6.Click Yes to commit/disable EWF.The EWF state will then change to disabled and all RAM utilized for the overlay will be returned to the operating system.Commit Changes to Disk All changes to a system are lost on a power outage or restart while EWF isenabled, unless they are committed to disk.Follow these steps to commit changes to disk.1.Click Commit.ATTENTION: Enabling EWF for long periods of time can fill theRAM overlay. The system will become unstable if changes are notcommitted to disk or restarted before the physical RAM isdepleted.If the overlay continually becomes full, examine your applications’use of RAM or consider adding more RAM to your system.For more information about adding RAM to your system, see yourcomputer’s user manual.TIP Commit is unavailable if EWF is not enabled.6 EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers2.Click Yes to commit changes. Commiting changes requires a system restart.3.Click Yes to restart.The changes will be committed and EWF will remain enabled once the system restart. Commit Changes and Disable EWF Follow these steps to commit changes and disable EWF.1.Click Commit/Disable EWF.2.Click Yes to commit/disable EWF.No restart is necessary after this step. The changes will be written to diskand EWF will be in a disabled state.TIP The Commit/Disable EWF button is unavailable if EWF is not enabled.EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers 7Enable HORMFollow these steps to enable HORM.1.Click Enable.2.Click Yes to enable HORM. 3.Click Yes to restart. Disable HORM Follow these steps to disable HORM.1.ClickDisable . 2.Click Yes to disable HORM.TIP Enable is unavailable if HORM is already enabled.TIP Disable is unavailable if HORM is disabled.Allen-Bradley, Rockwell Software, Rockwell Automation, and TechConnect are trademarks of Rockwell Automation, Inc.Trademarks not belonging to Rockwell Automation are property of their respective companies.Rockwell Otomasyon Ticaret A.Ş., Kar Plaza İş Merkezi E Blok Kat:6 34752 İçerenköy, İstanbul, T el: +90 (216) 5698400Publication 6000-TD003A-EN-P - April 2010Copyright © 2010 Rockwell Automation, Inc. All rights reserved. Printed in the U.S.A.3.Click Yes to restart.。

映泰A770L3主板 BIOS说明书

免责说明

本手册内容系 BIOSTAR®知识产权,版权归 BIOSTAR®所有。我们本着对用户负 责的态度,精心地编写该手册,但不保证本手册的内容完全准确无误。BIOSTAR® 有权在不知会用户的前提下对产品不断地进行改良、升级及对手册内容进行修正, 实际状况请以产品实物为准。本手册为纯技术文档,无任何暗示及影射第三方之 内容,且不承担排版错误导致的用户理解歧义。本手册中所涉及的第三方注册商 标所有权归其制造商或品牌所有人。

SATA II

板载串行ATA控制器

数据传输率为3 Gb/s 符合SATA 2.5 规范

网络

Realtek RTL 8102EL

10 / 100 Mb/s自适应传输模式 半双工/全双工工作模式

音效

ALC662 / VT1708B

6声道音频输出 支持高清音频

PCI Express Gen2 x16 插槽

注意: 此附件内容可能会因区域或主板版本而异。

1

主板手册

1.3 主板特性

SPEC

CPU

Socket AM3 AMD Sempron / Athlon II / Phenom II处理器 (最大瓦数:95W)

AMD 64架构兼容32和64位 支持Hyper Transport 3.0技术

支持HyperTransport 3.0

amdsb710环境控制ite8721hw监控高级io控制器提供最基本的io功能风扇速度控制器低管脚数接口ites智能保护功能双通道模式ddr3内存模块ddr3dimm插槽x2支持ddr380010661333主内存最大内存容量为8gb支持ddr31600oc每个dimm支持512mb1gb2gb4gbddr3不支持registereddimm和eccdimmmultiworddma多字节dmaide板载ide控制器ultradma3366100133总线控制模式数据传输率为3gbssataii板载串行ata控制器符合sata25规范10100mbs自适应传输模式网络realtekrtl8102el半双工全双工工作模式6声道音频输出音效alc662vt1708b支持高清音频pciexpressgen2x16插槽x1支持pciegen2x16扩展卡插槽pciexpressgen2x1插槽x1支持pciegen2x1扩展卡pci插槽x3支持pci扩展卡软驱接口x1每个接口支持2个软驱打印机接口x1每个接口支持1个打印机端口板载接口ide接口x1每个接口支持2个ide设备sata接口x4每个接口支持1个sata设备2a770l3spec前置面板接口x1支持前置面板设备前置音频接口x1支持前置音频功能spdif输出接口x1支持数字音频输出功能cpu风扇接头x1cpu风扇电源智能风扇功能系统风扇接头x1系统风扇电源清空cmos数据接头x1清空cmos数据usb接口x2每个接口支持2个前置面板usb端口电源接口24pinx1连接电源电源接口4pinx1连接电源ps2键盘x1连接ps2键盘ps2鼠标x1连接ps2鼠标串行端口x1连接rs232端口后置面板接口lan端口x1连接rj45以太网数据线usb端口x4连接usb设备音频插孔x3提供音频输入输出和连接麦克风接口主板尺寸182mmwx305mmlatx特性支持raid0110如有增加或减少任何os支持biostar保留不预先通操作系统支持windowsxpvista7知的权利

msi微星785G-E45开核及超频--要点小记

msi微星785G-E45开核及超频--要点小记微星785GTM-E45的话,CPU是AMD5000AD5000开核设置:启动按DELL键进入COMS设置,进入gree power(微星节能软件)CPU phase comtrol (微星独有的DRMOS技术) 【Disabled】进入CELL Menu。

1、AMD COOL’n’Quiet:(冷又静)【Disabled】节能设置是让桌上系统平台能更降温。

设为:[AUTO] 自动调整处理器速率。

设为:【Disabled】关闭节能设置2、Adjust cpu FSB Frequency:(调整前端总线频率)[273]设为[200]=2.2G /[273]=3G 自己可设置其他频率,这个是超频用的。

可设低一点,稳定第一。

3、Unlock CPU Core:(CPU核心开锁)【Enablde】设为【Enablde】开启被屏蔽的核心4、Aduancde clock calibration :(高级时钟校准功能)【ALL CORES】开启这个以后会出来Value (all cores) 加电压,+4%5、CPU Core control:(高级芯片效验功能)【AUTO】设置项有Auto(默认)和Manual。

一般默认的Auto即可,当Auto无法确定开启的核心是否有BUG时,可以手选。

6、FSB/DRAM Ratio:(设置同异步)[1:1]或者【1:1.33】不超频一般设置【AUTO】这个设置看内存的好坏。

因为板子本身只支持800的内存,所以1.33就可以。

7、HT LINK SPEED:(超传输总线)这个是外频和倍频的关系,一般设置成6倍。

8、auto disable dram/pci frequency :(自动关闭dram/pci 时钟信号) 【Disabled】9、spread spectrum :(展频技术) 【Disabled】。

全面教你玩超频 十分钟教你跨入5GHz时代(绝对详细2

华硕的AI Booster自动超频工具这是由于这个原因,不少主板厂商都开发除了专门的软件自动超频工具,能够直接在Windows操作系统中实现对CPU、主板、内存频率的设置。

如华硕的AI Booster、技嘉的EasyTune、微星的CoreCell等等,这些软件均能够支持自动超频功能,即在CPU满负荷工作的情况下,可以适当的超频来达到更好的性能,而在CPU低负荷运转的时候,又能够保持默认的频率不变,从而实现有选择性的超频。

技嘉的EasyTune自动超频工具另一方面,这类软件一般都会有5%——15%的超频限制当CPU频率超过预先所设定的超频范围后,系统会自动报警,限制用户的超频。

这样看来,这类软件同样存在着一些局限性。

首先,相应的软件必须要配合厂商各自相应的主板才能够使用,缺乏通用性。

另外,软件所提供的超频幅度相对较小,很难满足用户的超频需求。

因此,在这里我们为大家推荐一款第三方超频软件——ClockGen,不但功能强大,同时具备很好的通用性,能够在不同平台的不同芯片组上进行使用。

ClockGen软件截图ClockGen是第三方超频软件中的典型代表,在它的软件界面中,系统当前CPU、前端总线、内存以及总线的频率都会非常直观的显示出来,当按下“Get Values”选项时便能够拖动软件界面中的滑杆来进行处理器外频的调节了,当调节到一个相对合适的频率时,点击“Set Values”即可生效。

不过值得注意的是,ClockGen超频软件会根不同的主板发生器设计版本有所不同,要根据主板的具体型号来选择相应的软件版本。

MemSet软件主界面前面曾经提到,一次成功的超频和内存的品质和正确设定内存参数有着极为密切的关系。

既然有相应的软件支持CPU超频,那么有没有什么软件能够直接在Windows操作系统实现对内存参数的调节呢?答案当然是肯定的。

MemSet软件可用在Intel支持双通道内存的主板上,从865到975X均能使用,足够超频玩家使用。

英伟达显卡性能优化工具的使用步骤

Kepler BIOS Tweaker 是一款英伟达显卡性能优化软件,可利用成熟的技术来调整BIOS文件中的数值。

用户可以在软件层方便顺利得修改BIOS默认的频率值以及电压和TDP用OPEN BIOS打开BIOS按键选择刚刚保存下来的BIOS文件!Kepler BIOS Tweaker 是一款英伟达显卡性能优化软件,可利用成熟的技术来调整BIOS文件中的数值。

用户可以在软件层方便顺利得修改BIOS默认的频率值以及电压和TDP用OPEN BIOS打开BIOS按键选择刚刚保存下来的BIOS文件!所有人都可以安全刷kepler显卡的vbios,不再受制于人,简直比当年nibitor还好用国内软件,貌似各种问题,我就没刷成功过说明:就拿KBE来说,他那个电压修改有问题,不太准,设1.165就能达到1.200其实应该1.175 boost 1.200,然后是1.1875 boost 1.2125这个硬极限电压结果我用1.175时,KEB给我来个超限,导致显卡在游戏中定屏同时,因为tdp表那里也缺少一些参数,再加上对vbios的兼容不够全面,连classified都识别不了,因此我只能放弃当时还只是单卡,更是不懂,弄了半天怎么都不灵双卡以来,一直是默电1.150 boost 1.175,强操1254频率在重载时发现不太稳(从卡影驰吃亏),导致偶尔驱动重置昨天玩了会儿孤岛3,同样情况出现我一想,没别的,完全是vbios中的各种限制造成的,就从外国找软件先是看到kepler goden bios editor,结果这个更是废柴,现在到0.62了,很不好用意外发现kepler bios tweaker,进行了如下操作:1、找到KBT之前,先用KBE给影驰刷电压1.165v,摸清了电压(其余所有参数暂不变),1.165可以boost到1.200,安全可游戏,但tdp这块还是用的原厂设置,严重影响超频2、参考classified的tdp阶段设置,结果KBE不能识别,用KGB查了一下,因为软件废柴也不能加压3、找到KBT,经过查看,发现vbios都可以修正,就将两张显卡的tdp和电压完全统一,修正为1.175 to 1.200,把影驰显卡的渣到爆的tdp设置,通过KBT 改为了和classified完全一样的配置影驰的tdp,非常保守evga的tdp,具有超频的属性这就是KBT了,根据evga显卡的vbios,生产出第二个影驰vbios用nvflash到bios界面去刷,结果别人说新版软件可以在windows桌面下刷解锁tdp之后,boost的程度从默认的5*13=65mhz,直接翻了一倍上去,达到100以上了(8*13=104),这是因为显卡可以根据电压和tdp来综合计算出boost所能达到的高值,在默认vbios下,这些都是常规值并且被约束的`很严格影驰的vbios电压表,其实所有680的电压表都是这样,evga classified也一样刷完之后的电压表是这个样子,两块卡都刷成1.175,如前述,boost 1.200这是影驰的新版tdp表,完全和evga一样了我们仅仅把电压增加30毫伏不到,同时把tdp统一为强卡标配——结果就是一天一地。

华大单片机深度休眠时RTC与LPUART同时工作设置方法

华大单片机深度休眠时RTC与LPUART同时工作设置方法

华大单片机L系列为其超低功耗(LOW POWER)系列单片机,可以做到低功耗为0.5uA以内,唤醒时间4us。

其低功耗性能在行业内也是可圈可点。

有个别模块可以工作在深度休眠模式中,如RTC、LPTIMER、LPUART和比较器等。

有工程师反应RTC与LPUART一起用时会出问题,其它这是因为模块的时钟没有配置好造成的。

首先看下RTC的时钟配置如下:RTC_CR1寄存器的CKSEL位为RTC时钟选择,对应的选项为:00x: XTL 32.768K

01x: RCL 32K

100: XTH/128 (晶振为 4M 时选择此项)

101: XTH/256 (晶振为 8M 时选择此项)

110: XTH/512 (晶振为 16M 时选择此项)

111: XTH/1024 (晶振为 32M 时选择此项)

当进入深度休眠后只有低速时钟可以工作,因此只能选XTL32768或RCL32K。

再看下LPUART的时钟配置如下:

LPUARTx_SCON寄存器的SCLKSEL位为传输时钟选择位,对就应的选项为:

00,01:PCLK;

10:XTL;

11:RCL;

再结合波特率的计算和RCL的设置可以知道,当选择为RCL38.4K 时可以产生常用的9600波特率。

由上面知道因为38.4K这个时钟比较特殊,所以先要确定LPUART 的时钟为RCL,并把RCL的TRIM设置为38.4K。

当RCL为38.4K时是不能为RTC时钟,因些RTC的时钟只能使用外接的XTL32.768K时钟。

这样就可以解决RTC和LPUART两个模块在深度休眠模式下同时工作的问题。

技嘉BIOS中英翻译

技嘉BIOS中英翻译MB Intelligent Tweaker(M.I.T)(频率/电压控制)Standard CMOS Features(标准CMOS设置)Advanced BIOS Features(高级BIOS设置)Integrated Peripherals(集成设备或周边设备)Power Management Setup(电源管理设置)PC Health Status(电脑健康状态)Load Fail-Safe Defaults(装载安全预设配置)Load Optimized Defaults(装载最佳预设配置)Set Supervisor Password(设置管理员密码)Set User Password(设置使用者密码)Save and Exit Setup(保存当前设置并退出)Exit Without Saving(直接退出,不保存当前设定)=====BIOS频率/电压控制基础项中英文对照表===== Advanced Frequency Settings(高级频率设置)CPU Clock Ratio(CPU倍频)CPU Frequency(CPU内频率)Advanced CPU Core Features(CPU核心参数高级设置)Intel(R) Turbo Boost Tech(是否启动INTEL CPU加速模式)CPU Cores Enabled(启动CPU多核心技术)CPU Multi-Threading(启动CPU超线程技术)CPU Enhanced Halt (C1E) (Intel C1E功能)C3/C6/C7 State Support(是否允许CPU进入C3/C6/C7模式)CPU Thermal Monitor (Intel TM功能)CPU EIST Function (Intel EIST功能)Bi-Directional PROCHOT(是否启动PROCHOT功能)Virtualization Technology(是否启动INTEL虚拟化技术)QPI Clock Ratio(设置QPI倍频)QPI Link Speed(设置QPI速度)Uncore Clock Ratio(设置UNCORE倍频)Uncore Frequency(显示BCLK Frequency(MHz)*Uncore Clock Ratio 结果)Base Clock(BCLK) Control(CPU基频控制)BCLK Frequency(Mhz)(CPU基频调整)Extreme Memory Profile (X.M.P.)(开启BIOS读取XMP规格内存模块的SPD资料,可增强内存效能)System Memory Multiplier (SPD)(内存倍频调整)Memory Frequency(Mhz) (内存频率调整)PCI Express Frequency(Mhz) (PCI Express插口时钟调整)C.I.A.2(第二代智能CPU效能加速器设置)CPU Clock Drive(CPU时钟振幅调整)PCI Express Clock Drive(PCI Express时钟振幅调整)CPU Clock Skew(CPU时钟超前芯片组偏移量)Extreme Memory Profile (X.M.P.) (开启BIOS读取XMP规格内存模块的SPD资料,可增强内存效能)System Memory Multiplier (SPD)(内存倍频调整)Memory Frequency(Mhz) (内存频率调整)Performance Enhance(增强系统性能)DRAM Timing Selectable (SPD)(动态记忆体时序选择)Profile DDR Voltage(DDR电压概要)Profile QPI Voltage(QPI电压概要)Channel Interleaving(通道交织)Rank Interleaving(排列交织,天缘也不知道如此翻译是否准确,大家可以看英文释义:/showFreeBOG.aspx?lang=0&bogno=231)CAS Latency Time()tRCD()tRP()tRAS()tRC()tRRD()tWTR()tWR()tWTP()tWL()tRFC()tRTP()tFAW()Command Rate(CMD)(控制速度)B2B CAS Delay(B2B CAS延迟)Round Trip Latency(往返延迟)Different DIMMs ()Different Ranks()On The Same Rank()Load-Line Calibration(是否启动Load-Line校准功能)CPU Vcore(CPU 核心电压设置)QPI/Vtt Voltage(QPI/Vtt电压设置)PCH Core(PCH核心设置)CPU PLL(CPU锁相环设置)DRAM Voltage(DRAM电压)DRAM Termination(DRAM结点)Ch-A Data VRef.()Ch-B Data VRef.()Ch-A Address VRef.()Ch-B Address VRef.()Miscellaneous Settings(其它设置)Isochronous Support(同步支持)=====BIOS标准CMOS基础项中英文对照表=====Date (mm:dd:yy) (日期)Time (hh:mm:ss)(时间)IDE Channel 0, 1 Master/Slave(第一二组主/从IDE/SATA通道)IDE Channel 2, 3 Master, 4, 5 Master/Slave(第三四组主、五六组主/从IDE/SATA通道)Drive A(软驱设定)Halt On(系统停机设定)Memory(内存)Base Memory(传统内存,会保留640KB为MS-DOS系统使用)Extended Memory(扩展内存)Total Memory(系统上的总内存)=====BIOS高级功能设置中英文对照表=====Hard Disk Boot Priority(硬盘启动优先级)Quick Boot(快速启动)First/Second/Third Boot Device(第一二三启动设备)Floppy(软盘)LS120(LS120磁盘)Hard Disk(硬盘)CDROM(光驱)ZIP(ZIP盘)USB-FDD(USB软盘)USB-ZIP(USB ZIP)USB-CDROM(USB光驱)USB-HDD(USB 硬盘)Legacy LAN(网卡开机)Password Check(密码检查,每次开始是否需要输入密码)HDD S.M.A.R.T. Capability(硬盘自动监控报警是否开启)Limit CPUID Max. to 3(最大CPUID极限值)No-Execute Memory Protect(INTEL防病毒功能是否开启)Delay For HDD (Secs)(硬盘延迟读取时间)Full Screen LOGO Show(全屏LOGO显示)Backup BIOS Image to HDD(备份BIOS到硬盘上)Init Display First(开机显卡配置)=====BIOS周边设备配置中英文对照表=====SATA RAID/AHCI Mode (SATA设备RAID/AHCI模式配置)SATA Port0-3 Native Mode(SATA端口0-3Native mode是否开启)USB Controllers(USB控制器)USB Legacy Function(是否在DOS下使用USB键盘)USB Storage Function(是否在BIOS的POST阶段检测USB设备)Azalia Codec(集成音效功能设定)Onboard H/W 1394(集成1394功能设定)Onboard H/W LAN(集成网卡设置)Green LAN(无网络链接时是否自动关闭网络芯片)SMART LAN(智能网卡侦测)Link Detected(HUB传输速度)Cable Length(电缆长度)Onboard LAN Boot ROM(集成网卡的开机功能)Onboard SATA/IDE Device(是否启用集成SATA/IDE控制器)Onboard SATA/IDE Ctrl Mode(是否启用集成SATA/IDE控制器的RAID 功能)Onboard Serial Port 1(串口1)=====BIOS电源管理配置中英文对照表=====ACPI Suspend Type(系统休眠模式设置)Soft-Off by PWR-BTTN (开机方式)PME Event Wake Up(电源管理事件的唤醒功能)Power On by Ring(是否允许被具有唤醒功能的数据机唤醒开机)Resume by Alarm(定时开机)HPET Support(是否开启高精度定时器功能)HPET Mode(HPET 模式设置:32位或64位)Power On By Mouse(是否开启鼠标双击开机)Power On By Keyboard(键盘开机功能设定,支持密码开机、电源键开机)KB Power ON Password(键盘开机的密码设定)AC Back Function(电源中断后,电源恢复时的系统状态选择)=====BIOS电脑健康状态配置中英文对照表=====Reset Case Open Status(重置机壳状态)Case Opened(机壳开启状况)Current Voltage(V) Vcore/DDR15V/+5V/+12V(检测系统电压)Current System/CPU Temperature(CPU温度)Current CPU/SYSTEM FAN Speed (RPM)(系统风扇速度)CPU Warning Temperature(CPU温度告警)CPU/SYSTEM FAN Fail Warning(CPU风扇故障告警)CPU Smart FAN Control(CPU风扇智能控制)11。

BIOS出错英文提示详解

BIOS出错英文提示详解Drive A error 驱动器A错误System halt 系统挂起Keyboard controller error 键盘控制器错误Keyboard error or no keyboard present 键盘错误或者键盘不存在BIOS ROM checksum error BIOS ROM校验错误Single hardisk cable fail 当硬盘使用Cable选项时硬盘安装位置不正确FDD Controller Failure BIOS 软盘控制器错误HDD Controller Failure BIOS 硬盘控制器错误Driver Error 驱动器错误Cache Memory Bad, Do not Enable Cache 高速缓存Cache损坏,不能使用Error: Unable to control A20 line 错误提示:不能使用A20地址控制线Memory write/Read failure 内存读写失败Memory allocation error 内存定位错误CMOS Battery state Low CMOS没电了Keyboard interface error 键盘接口错误Hard disk drive failure 加载硬盘失败Hard disk not present 硬盘不存在Floppy disk(s) fail (40) 软盘驱动器加载失败,一般是数据线插反,电源线没有插接,CMOS 内部软驱设置错误CMOS checksum error-efaults loaded. CMOS校验错误,装入缺省(默认)设置Detecting floppy drive A media... 检测软驱A的格式Drive media is : 1.44Mb1.2Mb 720Kb 360K 驱动器格式是1.44Mb、12Mb、720kb、360kb的一种DISK BOOT FAILURE, INSERT SYSTEM DISK AND PRESS ENTER 磁盘引导失败,插入系统盘后按任意键继续Invalid partition table 无效的分区表Error loading operating system 不能装入引导系统Missing operating system 系统引导文件丢失Invalid system disk 无效的系统盘Disk I/O error, Replace the disk and press any key. 磁盘I/O错误,替换磁盘后按任意键,当C 盘系统文件丢失或被破坏时出现。

开机bios含义及各设置详解

开机BIOS语言开机自检时出现问题后会出现各种各样的英文短句,短句中包含了非常重要的信息,读懂这些信息可以自己解决一些小问题,可是这些英文难倒了一部分朋友,下面是一些常见的BIOS短句的解释,大家可以参考一下。

1.CMOS battery failed 中文:CMOS电池失效。

解释:这说明CMOS电池已经快没电了,只要更换新的电池即可。

2.CMOS check sum error-Defaults loaded 中文:CMOS 执行全部检查时发现错误,要载入系统预设值。

解释:一般来说出现这句话都是说电池快没电了,可以先换个电池试试,如果问题还是没有解决,那么说明CMOS RAM可能有问题,如果没过一年就到经销商处换一块主板,过了一年就让经销商送回生产厂家修一下吧! 3.Press ESC to skip memory test 中文:正在进行内存检查,可按ESC键跳过。

解释:这是因为在CMOS内没有设定跳过存储器的第二、三、四次测试,开机就会执行四次内存测试,当然你也可以按 ESC 键结束内存检查,不过每次都要这样太麻烦了,你可以进入COMS设置后选择BIOS FEATURS SETUP,将其中的Quick Power On Self Test设为Enabled,储存后重新启动即可。

4.Keyboard error or no keyboard present 中文:键盘错误或者未接键盘。

解释:检查一下键盘的连线是否松动或者损坏。

5.Hard disk install failure 中文:硬盘安装失败。

解释:这是因为硬盘的电源线或数据线可能未接好或者硬盘跳线设置不当。

你可以检查一下硬盘的各根连线是否插好,看看同一根数据线上的两个硬盘的跳线的设置是否一样,如果一样,只要将两个硬盘的跳线设置的不一样即可(一个设为Master,另一个设为Slave)。

6.Secondary slave hard fail 中文:检测从盘失败解释:可能是CMOS设置不当,比如说没有从盘但在CMOS里设为有从盘,那么就会出现错误,这时可以进入COMS设置选择IDE HDD AUTO DETECTION进行硬盘自动侦测。

ug909-vivado-partial-reconfiguration