一种快速CRC算法的硬件实现方法

CRC校验算法详解及代码实现

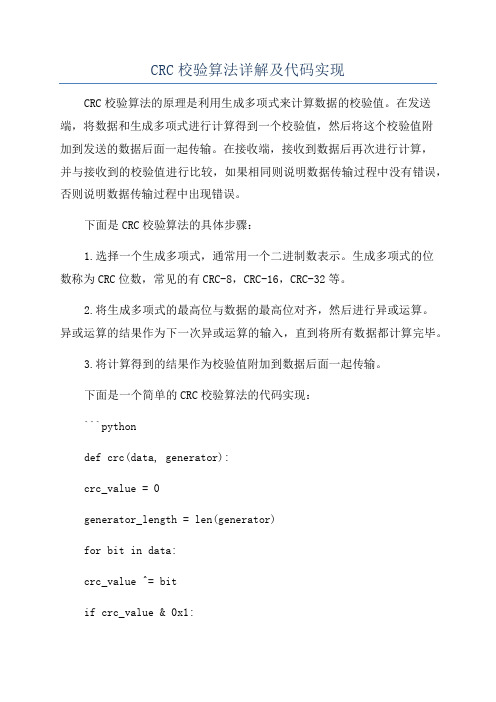

CRC校验算法详解及代码实现CRC校验算法的原理是利用生成多项式来计算数据的校验值。

在发送端,将数据和生成多项式进行计算得到一个校验值,然后将这个校验值附加到发送的数据后面一起传输。

在接收端,接收到数据后再次进行计算,并与接收到的校验值进行比较,如果相同则说明数据传输过程中没有错误,否则说明数据传输过程中出现错误。

下面是CRC校验算法的具体步骤:1.选择一个生成多项式,通常用一个二进制数表示。

生成多项式的位数称为CRC位数,常见的有CRC-8,CRC-16,CRC-32等。

2.将生成多项式的最高位与数据的最高位对齐,然后进行异或运算。

异或运算的结果作为下一次异或运算的输入,直到将所有数据都计算完毕。

3.将计算得到的结果作为校验值附加到数据后面一起传输。

下面是一个简单的CRC校验算法的代码实现:```pythondef crc(data, generator):crc_value = 0generator_length = len(generator)for bit in data:crc_value ^= bitif crc_value & 0x1:crc_value = (crc_value >> 1) ^ int(generator, 2)else:crc_value = crc_value >> 1return crc_value#测试数据data = [1, 0, 1, 1]generator = "1011"#进行CRC校验residue = crc(data, generator)print(residue)```在上面的代码中,`data`表示要进行校验的数据,以列表的形式表示,每个元素是一个二进制位。

`generator`表示生成多项式,以字符串的形式表示,每个字符是一个二进制位。

程序输出的结果为校验值。

总结:本文详细介绍了CRC校验算法的原理和步骤,并给出了一个简单的代码实现。

一种CRC并行计算原理及实现方法

一种CRC并行计算原理及实现方法CRC(Cyclic Redundancy Check)是一种常见的错误检测方法,通过对数据进行位运算来生成一个校验值,用于校验数据的完整性和准确性。

CRC的并行计算原理和实现方法有以下几种:1.位并行原理:CRC计算通常采用二进制多项式除法,利用位运算进行计算。

在CRC 计算中,数据被看作是一个多项式,通过多项式除法,将数据除以生成多项式,得到余数作为校验值。

位并行原理是指对输入数据的每一位和校验值的对应位进行并行运算,通过异或操作(XOR)得到新的校验值。

具体实现方法如下:1)初始化校验值为全0;2)遍历输入数据的每一位,从高位到低位,利用异或操作将其与校验值的对应位进行运算;3)运算结果作为新的校验值;4)重复以上步骤,直到遍历完所有的位;5)最终的校验值即为CRC值。

2.字节并行原理:在字节并行原理中,将输入数据和CRC校验值都看作是字节序列,通过对每个字节进行并行运算来计算CRC校验值。

这种方法可以提高计算速度和效率。

具体实现方法如下:1)初始化校验值为全0;2)将输入数据按字节分割,每次处理一个字节;3)将每个字节与校验值的最低8位进行异或运算;4)将结果右移8位;5)用字节查找表(Lookup Table)查找对应的校验值,将结果与校验值的最低8位进行异或运算;6)重复以上步骤,直到处理完所有的字节;7)最终的校验值即为CRC值。

3.广义并行原理:广义并行原理是在字节并行原理的基础上进一步拓展,将输入数据和校验值分组处理,并行计算多个字节的CRC校验值。

这种方法在一些场景下可以进一步提高计算速度和效率。

具体实现方法如下:1)初始化校验值为全0;2)将输入数据按照一定的分组规则分割成多个字节组,每个字节组包含多个字节;3)将每个字节组与校验值进行异或运算;4)使用查找表查找每个字节组的校验值,并与校验值的最低8位进行异或运算;5)重复以上步骤,直到处理完所有的字节组;6)最终的校验值即为CRC值。

CRC计算实现方法

CRC计算 实现 方法

文 /杨 卫平

本 文 讨论 一 种 通 用 CRC计 算 f

实现 方法。 该 方法 采用 纯硬 件 方 》

法 实现 CRC计 算 ,可 灵 活 配 置、

计 算 速度 快 , 无需 CPU计 算, 适

d

用 于 任 意 CRC类型 、 任 意 CRC生

接 收方 已知接 收 的数 据 包含 K位 DATA 信 息 码 与 R位 CRC 校 验 码 。接 收 方 将 收 到 的 数 据 同 样 处 理 : 假 设 前 K 位 数 据 用 信 息 多 项 式 D(x)表 示 , 将 D(x)左 移 R 位 , 则 可 表 示 成 D(x) 2的 R 次 方 , 这 样 D(x)的 右边 就 会 空 出 R位 , 这 就 是 校 验 码 的 位 置 。 通 过 D(x) 2 的 R次方除 以生成 多项式 G(x)得 到的余 数就 是校验 码,用 R(x)表 示。将 接收 的后 R位 数 据与 CRC校验结 R(x)系 数比较 ,如果 有不一 致 则 说 明 该 笔 数 据 传 输 有 误 。

C LK C0 NFlG RESULT

厂—]

X

CONF ̄

X

一 —— ]

】 )

Calc stai"I

—— __、

厂—]

:

X

( RESULT OUT X

Calc end

过程 中,发送 方 将 K位信 息 码在 前 、R位校 验码在后拼接 的共 N位数据发送 。

CRC编码 和解 码方 法简 单,检 错和 纠错 能 力 强 ,在 通 信 领域 广泛 地 用 于 实 现 差 错 控 制 。

CRC冗余校验编码与解码的FPGA实现

CRC冗余校验编码与解码的FPGA实现CRC(Cyclic Redundancy Check)冗余校验编码是一种常用的错误检测技术,它通过对数据进行多项式除法运算,生成一个校验码。

接收方可以利用这个校验码来检测数据传输是否出现错误或损坏。

在FPGA中实现CRC的编码和解码功能可以提供硬件级别的实时性能和效率,并且可以与其他模块轻松集成在一起。

首先,我们需要准备FPGA开发板、软件开发工具和一个CRC多项式。

CRC多项式的选择取决于所使用的CRC标准和数据宽度。

编码的FPGA实现主要包含以下步骤:1.数据输入:将待编码的数据通过输入端口输入到FPGA中。

2.除数寄存器初始化:初始化一个与CRC多项式位数相等的寄存器,初始值为0。

3.循环除法:采用循环除法算法,将输入数据和除数寄存器中的值进行除法运算。

每次计算结果都更新除数寄存器。

4.生成校验码:当所有输入数据都被除尽后,生成最终的校验码。

5.输出校验码:将生成的校验码通过输出端口输出到外部。

解码的FPGA实现主要包含以下步骤:1.接收数据:将接收到的数据通过输入端口输入到FPGA中。

2.除数寄存器初始化:与编码过程相同,初始化一个与CRC多项式位数相等的寄存器。

3.循环除法:采用同样的循环除法算法进行运算,将输入数据和除数寄存器中的值进行除法运算。

4.判断错误:当除数寄存器的值为零,说明数据没有出现错误。

否则,数据出现错误。

通过使用FPGA来实现CRC冗余校验编码和解码,可以获得高速、高效的数据传输,尤其适用于在低延迟和高吞吐量的系统中。

此外,FPGA的可编程性使得我们可以灵活地配置不同标准和多种数据宽度的CRC。

需要注意的是,在实现CRC编码和解码时,需要根据具体的CRC标准和数据宽度来确定多项式的选择以及对应的除法算法。

此外,合理的硬件设计和时序控制对于FPGA实现CRC的性能和正确性也至关重要。

综上所述,CRC冗余校验编码与解码的FPGA实现可以提供高效的数据传输和错误检测功能,适用于各种应用场景。

CAN总线中CRC编码的硬件实现

Ha d r m p e e a i n o r wa e I l m nt to f CRC c di g i En o n n CAN u b s

( e a t et fEl toi D p rm n e rnc o c s& C mp tr f G inU iesyo eh oo y, u n x 4 04, hn ) o ue ul nvri f T c nlg G a g i 1 0 C i o i t 5 a

维普资讯

2 o 年 1 月 08 o

第1 期 o

电 子 测 斌

EL cTR E 0Nl Es C T T

Oc . 0 t20 8

No. 0 1

C N 总线 中 C A RC编 码 的硬 件 实 现

陈 飞 ( 桂林工学 院电子与计算机系 桂林 5 10 ) 4 0 4

1 C C编 码 原 理 R

C C编码 的基本 思想 是利用 线性 编码理论 , R 在

发送 端根 据要传 送 的 k位二 进制 序 列 , 以一定 的规

则产 生一 个 校 验 用 的 r位监 督 码 ( 即所 谓 的 C C R

位错误 、 位填充 错误 、 固定形 式错 误 和应答 错 误 , 接

t = U

, 1 一

∑R 一[ ( ) m d g x ] g ) z x ] o E ( ) , ( 为生成多项

— U

R 一l _ R 一2 R 3

_ 一 1 -r

式 , 为 检验符 号 ; 字多 项式 为 : ( ) ∑ C R 码 cz 一 i, x

收端可 以通过 C C检 验来 发现 错误 。某 个 节点 发 R

CRC码生成与校验电路的设计与实现

CRC码生成与校验电路的设计与实现CRC码(Cyclic Redundancy Check)是一种常用于错误检测的校验码。

在数据通信和存储领域广泛应用。

CRC码生成与校验电路的设计与实现是指设计并搭建能够正确生成和校验CRC码的电路。

本文将从CRC码的原理、设计方案、实现步骤以及一些应用举例进行详细说明。

一、CRC码的原理CRC码利用除法操作来生成校验码,基本原理如下:1.以二进制形式将待传输或存储的数据进行编码表示。

2.选定一个固定的生成多项式G(x)。

3.将编码后的数据与生成多项式进行除法运算,得到余数,将余数添加到编码数据末尾,形成含有校验码的编码数据。

4.接收端根据相同的生成多项式进行除法运算,得到余数,如果余数为零,则认为数据传输或存储没有错误,否则,认为有错误发生。

二、CRC码的设计方案根据CRC码的原理,我们可以进行如下的设计方案:1.确定生成多项式。

生成多项式的选择非常重要,通常使用CRC-16或CRC-32等标准的生成多项式。

不同的生成多项式会导致CRC码的性能不同,可以根据需要进行选择。

2.确定初始寄存器值。

初始寄存器值决定了CRC码的初始状态,常见的初始值为全1或全0。

3.实现生成多项式的除法运算。

可以利用硬件电路或软件算法来实现多项式的除法运算。

硬件电路比较高效,适合于大规模的数据传输或存储系统。

三、CRC码的实现步骤CRC码的实现一般包括以下步骤:1.初始化寄存器值为初始值。

2.读入待编码数据。

3.将待编码数据与寄存器值进行异或操作。

4.判断待编码数据的最高位是否为1,如果为1,则将生成多项式与寄存器值进行异或操作,否则,寄存器值左移一位。

5.重复以上步骤,直到所有待编码数据被处理完毕。

6.将最终的寄存器值添加到编码数据末尾,形成含有校验码的编码数据。

四、CRC码的应用举例CRC码广泛应用于数据通信和存储领域,以下是一些应用举例:1.以太网通信:在以太网通信中,CRC码用于检测数据在传输过程中的错误。

crc硬件电路原理

crc硬件电路原理CRC硬件电路原理简介CRC(Cyclic Redundancy Check)是一种常用的错误检测技术,它通过在发送的数据后添加一些冗余位,以实现对数据传输的可靠性检验。

在现代的通信系统中,CRC已经成为了一种标准的数据传输协议。

CRC的原理CRC的原理比较复杂,但可以简单概括为以下几个步骤:1.生成多项式:选择一个特定的生成多项式,一般情况下会使用二进制表示的多项式,例如x^16 + x^12 + x^5 + 1。

2.生成除数:将生成多项式转化为除数,也是一个二进制数。

3.帧计算:将发送的数据帧与生成的除数进行模2除法运算,得到余数。

余数的位数通常等于生成多项式的次数减1。

4.添加余数:将余数添加到原始数据帧的末尾,形成最终的发送帧。

5.接收端校验:接收端在接收到数据后,将接收到的数据帧与生成的除数进行模2除法运算,得到余数。

如果余数为0,则认为数据传输无误。

CRC的硬件实现原理CRC的硬件实现主要是通过使用逻辑门和寄存器来进行计算的。

整个过程可以分为以下几个步骤:1.寄存器初始化:将寄存器的值设置为0。

2.数据移入:将发送的数据逐位输入到寄存器中,逐位进行计算。

3.异或运算:将寄存器中的某些位与生成多项式中的对应位进行异或运算。

4.寄存器移位:将寄存器中的数据向左移动一位。

5.判断是否继续:如果寄存器中还有数据需要进行计算,则返回到第3步执行,否则进入下一步。

6.余数输出:将寄存器中的数据作为余数输出。

CRC硬件电路的优势与软件实现相比,CRC硬件电路具有以下几个优势:1.速度更快:硬件电路采用并行计算的方式,可以大大加快计算速度。

2.占用资源更少:硬件电路可以直接嵌入到通信芯片中,不需要占用额外的芯片资源。

3.可靠性更高:硬件电路可以实时进行数据校验,并且无法被恶意篡改。

结论CRC硬件电路原理是一种重要的数据校验技术,它在现代通信系统中得到了广泛应用。

通过硬件电路的并行计算方式,CRC可以快速、高效地对数据传输进行可靠性检验,提高了数据传输的准确性与安全性。

crc原理

crc原理

CRC(Cyclic Redundancy Check)是一种在计算机网络中常用的错误检测方法,它通过对数据进行循环冗余校验,来检测数据在传输过程中是否发生了错误。

CRC原理的核心是利用多项式除法来实现对数据的校验,下面我们将详细介绍

CRC的原理和实现方法。

首先,CRC的计算过程是将要传输的数据看作一个二进制多项式,然后利用除法运算来生成校验码。

具体步骤如下,首先选择一个固定的生成多项式,然后将要传输的数据与生成多项式进行模2除法运算,得到余数作为校验码。

在接收端,同样利用相同的生成多项式对接收到的数据进行除法运算,如果余数为0,则说明数

据传输正确,否则说明数据存在错误。

其次,CRC的实现方法包括两种常用的方式,硬件实现和软件实现。

硬件实现是通过专门的CRC芯片来实现数据的校验,速度快,但成本较高。

软件实现则是

通过计算机程序来实现CRC校验,相对较慢但成本较低,适用于软件开发领域。

此外,CRC校验的优点是可以检测多种类型的错误,包括单比特错误、双比特错误以及所有奇数个比特错误。

而且CRC校验的计算效率高,适用于大规模数据

的传输和存储。

最后,需要注意的是CRC校验并不能纠正数据错误,它只能检测出数据是否

存在错误。

因此在实际应用中,通常会结合其他纠错编码方法来提高数据传输的可靠性。

总之,CRC是一种高效的数据校验方法,通过多项式除法来实现对数据的校验,具有检测多种错误类型、计算效率高的优点。

在计算机网络和数据存储领域得到了广泛的应用。

希望本文能够帮助读者更加深入地理解CRC的原理和实现方法。

网络传输中CRC的硬件实现

该 代码 短小 精悍 ,但 能够实 现 四种功 能 :即在数 据 串行传输

过程 中实时 的产 生 C RC 一 5 、C R C 一 1 6校验码 ,并 对 接 收 的数 据进行 两种校 验码 的校验 。

C RC的应 用 范 围非 常 广泛 ,研 究 C RC的硬 件 实现 具 有

S YS P R AC T I C E 系统 实践

网络传输中 C R C的硬件实现

◆ 姜 晓 峰 王 立 新

摘要 :讨论 了串行计算循 环冗余校 验码 ( CRC)的原理 ,并给 出了对应的硬件 实现 。 关键 词 :CRC;网络传输 ;V e r i l o g HDL

由于 电磁 干扰 的存 在 , 网络 的 物理 层 通 信 不 能保 证 百 分 之 百 的 传输 正 确 性 ,因此 数 据 的正 确 性 校 验 是不 可缺 少

P ( X 、 =1 x +0 x +0 x +1 x + I x 。 +l x + 0 x +1 x 。

P ( x ) 通过除以 C R C多项 式 G ( x ) 后 ,得 到一 个余 数 R ( x ) 和商 Q ( x ) ,这 个 R ( X ) 就 是我 们需 要 的 C R C校 验值 ,用 公 式

C R C校验采 用 的生 成多项 式为 :G f x ) :X +x +1 ,如果 数据

准确无误地接收到,接收机中的 5 位余数应该是 O 1 1 0 0 。1 6

位C R C校验使 用的生成 多项 式是 :c ( x ) = x + x + x 2 +1 , 接 收机 中正 确的余数是 1 0 0 0 0 0 0 0 0 0 0 0 1 1 0 1 。 为 什 么 数 据 校 验过 程 产 生 的 余数 不 是 0呢? 这 是 由网 络 传 输协 议 中的 C R C原 理得 到 的 。 网络传 输 协议 为 了保护 包 的最 高 位 为 0 的 数 据传 输 ,为 接 收 或发 送 的数 据 包都 加

一种CRC并行计算原理及实现方法

一种CRC并行计算原理及实现方法CRC(Cyclic Redundancy Check)是一种多项式编码校验方法,广泛应用于数据通信、存储系统和数据传输网络中,用于检测数据传输过程中可能出现的错误。

CRC的计算原理是通过对数据进行多项式除法运算,将余数作为校验码发送,并在接收端对接收到的数据再次进行多项式除法运算,通过比较余数是否为零来判断数据是否正常。

具体实现步骤如下:1.初始化多项式和初始校验码:选择一个合适的生成多项式作为校验多项式,通常使用的是多项式的二进制表示形式,如生成多项式CRC-32(32位长)可以表示为0x04C11DB7、另外,还需要初始化一个初始校验码。

2.将数据分割成多个子数据块:将待发送的数据按照指定的块大小划分成多个子数据块,长度与生成多项式的位数相同。

3.并行计算多项式除法:对每个子数据块进行多项式除法计算,即将生成多项式与子数据块进行异或运算,得到一个新的除数,将新的除数继续与生成多项式进行异或运算,直到剩余的位数小于生成多项式的位数。

4.得到子数据块的校验码:最终余数即为该子数据块的校验码。

5.对校验码进行运算:将所有子数据块的校验码进行一定的运算,如按位异或,得到最终的校验码。

6.将原数据与校验码组合:将原数据与最终的校验码进行组合,发送给接收端。

在接收端,实现CRC的校验过程也是通过并行计算的方式进行。

接收端首先获取到发送端发送的原数据以及校验码,将原数据按照指定的块大小进行分割,然后对每个子数据块进行多项式除法计算,得到余数。

对所有子数据块的余数进行一定的运算,如按位异或,如果最终结果为零,则表示数据传输没有错误。

CRC并行计算的优点是能够提高计算效率,同时适合硬件实现,如使用FPGA等硬件加速器进行计算,可以实现快速的CRC校验。

另外,由于CRC是通过多项式除法运算实现的,因此可以检测到多位错误。

总之,CRC并行计算是一种高效、可靠的校验方法,可以在数据传输过程中进行快速的错误检测,提高数据传输的可靠性。

CRC算法原理及C语言实现(介绍了3种方法)

CRC算法原理及C语言实现(介绍了3种方法)摘要本文从理论上推导出CRC算法实现原理,给出三种分别适应不同计算机或微控制器硬件环境的C语言程序。

读者更能根据本算法原理,用不同的语言编写出独特风格更加实用的CRC计算程序。

关键词 CRC 算法 C语言1 引言循环冗余码CRC检验技术广泛应用于测控及通信领域。

CRC计算可以靠专用的硬件来实现,但是对于低成本的微控制器系统,在没有硬件支持下实现CRC检验,关键的问题就是如何通过软件来完成CRC 计算,也就是CRC算法的问题。

这里将提供三种算法,它们稍有不同,一种适用于程序空间十分苛刻但CRC计算速度要求不高的微控制器系统,另一种适用于程序空间较大且CRC计算速度要求较高的计算机或微控制器系统,最后一种是适用于程序空间不太大,且CRC计算速度又不可以太慢的微控制器系统。

2 CRC简介CRC校验的基本思想是利用线性编码理论,在发送端根据要传送的k位二进制码序列,以一定的规则产生一个校验用的监督码(既CRC码)r位,并附在信息后边,构成一个新的二进制码序列数共(k+r)位,最后发送出去。

在接收端,则根据信息码和CRC码之间所遵循的规则进行检验,以确定传送中是否出错。

16位的CRC码产生的规则是先将要发送的二进制序列数左移16位(既乘以)后,再除以一个多项式,最后所得到的余数既是CRC码,如式(2-1)式所示,其中B(X)表示n位的二进制序列数,G(X)为多项式,Q(X)为整数,R(X)是余数(既CRC码)。

(2-1)求CRC码所采用模2加减运算法则,既是不带进位和借位的按位加减,这种加减运算实际上就是逻辑上的异或运算,加法和减法等价,乘法和除法运算与普通代数式的乘除法运算是一样,符合同样的规律。

生成CRC码的多项式如下,其中CRC-16和CRC-CCITT产生16位的CRC码,而CRC-32则产生的是32位的CRC码。

本文不讨论32位的CRC算法,有兴趣的朋友可以根据本文的思路自己去推导计算方法。

crc的并行实现原理

crc的并行实现原理

CRC(循环冗余校验)是一种常用的数据校验算法,用于检测和纠正传输过程中可能发生的错误。

CRC的并行实现原理主要是通过使用位级操作和并行计算来提高效率。

CRC的核心思想是通过生成多项式对数据进行除法运算,将余数作为校验码附加到原始数据中。

在并行实现中,可以使用并行计算的方式来加速这个除法运算过程。

具体的并行实现原理如下:

1. 将待校验的数据划分为多个字节或比特。

每个字节或比特可以独立进行计算,以提高并行计算的效率。

2. 将生成多项式表示为一个二进制数,并将其转换为一个位级多项式。

该多项式通常表示为一个二进制数,例如CRC-32所使用的生成多项式为0x04C11DB7,表示为一个位级多项式为x^32 + x^26 + x^23 + x^22 + x^16 + x^12 + x^11 + x^10 + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1。

3. 对于每个字节或比特,执行以下步骤:

a. 将字节或比特与校验寄存器进行异或运算。

b. 如果最高位为1,则将校验寄存器左移一位,并与生成多项式进行异或运算。

c. 如果最高位为0,则将校验寄存器左移一位,不做任何异或操作。

4. 重复步骤3,直到所有字节或比特都处理完毕。

5. 最终的校验寄存器的值就是CRC校验码。

通过并行实现,可以同时对多个字节或比特进行校验计算,从而提高了校验的效率。

但需要注意的是,并行实现可能会增加硬件资源的需求,需要根据具体情况选择合适的实现方式。

CRC算法在以太网数据帧中的应用及其硬件实现

新二 术一 一 业= 技= .新二 务一

X + X2 + X + 1 8

1 0 0 0 1 1 l 0 0

当数 据 单 元 到 达 接 收 端 时 是 数 据 先 到 , 后 面 跟 着

图3用 多项式表示 除数

因此 , 在 接 收 端 进 行 的 运 算 就 可 以 写 为

对 应 的 长 度 为 ( + 1 i 二 进 制 序 列 P, 得 出 商 是 Q n )bt 的

1 C C R 算法的数学原理

在 模 运 算 中, 模 2]减 法 的结 果 都 是 相 同 的 , 都 可 以 N J 用 逻 辑 运 算 “ 或 ” 完 成 , 模 2 法 运 算 可 以用 逻 辑 运 算 异 乘 “ ” 完 成 , 模 2 法 只 在 除 数 为 1 有 效 , 并 且 结 果 维 持 与 除 时 不 变 ,也 可 以看 作 是 “ 或 ” 运 算 。CR 异 C编 码 方 法 是 把 需 要 发 送 的 数 据 流 M在 后 面 加 上 n 0 然 后 除 以 事 先 确 定 的 个 , n 生 成 多 项 式 所 对 应 的 (l1 次 r )位 二 进 制 序列 P 到 的 余 + 得

应用。

特 流 在 传 送 过 程 中发 生 错 误 ,那 么这 样 的 除 法就 产 生 非 零 的 余 数 , 因 而 这个 数据 单 元 就 不 能 正 确 接 收 。 图 2 出 了 计 算 CRC编 码 序 列 的 详 细 过 程 。 在 数 据 给

流 M后 面 添 加 n 个 0 以 事 先 选 定 好 的 n 生 成 多 项 式 所 除 次

个 生 成 多 项 式 至 少 要 有 以 下特 性 才 能被 选 用

通用并行CRC计算原理及其硬件实现方法

・ ( ) R( ) M z + z.

n 位

I.... ..... .... ....

Ⅺ x ()

( ) 传 送 的数 据序 列 a被

M (

IJ

[ 稿 日期 ]2 O 收 O O一0 3—2 1 【 作者 简 介 ]李 永 忠 (9 1 )男 , 肃 兰州 市 人 , 教 授 , 16 一 , 甘 副 主要 从 事 通信 及 计 算 机 信息 处 理 .

一

3 3

维普资讯

3 )忽 略 其 商 , 仅 将 其 余 数 R( ( B C)取 出 , 将 其 与 仅 z) 即 C 并

成 为高次多项 式 , 称为 位 序列多 项式 用 M ( 也 z)表 示 , 此 多 项 式 用 预 先 规 定 的 生 成 多 项 式 将

g z)C ekn oy o a) 除, ( ( hc igP cn mi 去 1 再将其 余数 码 B C BokC ekC d ) 加在 所 传数 据 的 C ( l h c o e 附 e 尾 部一并 传送 . 在接 受方 , 接 受到 的附加 B C的数据 用 同样 的生成 多项 式 g z) 除, 除 将 C ( 去 若 得 的 结 果 余 数 值 为 0 则 可 判 断所 接 受 的 数 据 是 正 确 的 , 则 , 受 的数 据 有 误 码 . , 否 接

1 C RC校 验 的 数 学原 理 循环冗 余 校验码 一般 简称为 循环冗余 码或 C RC码 ( yl d n a c h c ), 一 种 检 C ci Reu dn yC ek 是 c

出概 率高 、 易于 用 硬件实 现 的检错 码 . R 且 C C码 是 由一个生 成 多 项式 ( 高次 幂 为 )产 生 , 最 k 次 幂的生成 多项 式可产 生 一1 的冗余 码 . 当选取生 成多项 式可 以使 C C 能检 出所 有奇 位 适 R 码 数位 的随机误 码 ,以及 突发 长度小于 k一1的突发误码 【 2 ,1 1 ,4. .3 C C是 一种多 用 于同步通 信 方式 中的差 错检 出方式 . 这种 方式 中, 所 传数 据序 列看 R 在 将

聊一聊CRC算法的硬件电路实现:串行电路和并行电路

聊一聊CRC算法的硬件电路实现:串行电路和并行电路

这一篇文章聊一聊CRC算法的硬件电路实现:串行电路和并行电路。

下面的内容还是IC君的朋友文武写的,IC君稍微做了优化排版和少量的编辑工作提升大家的阅读体验。

1

CRC硬件电路的实现很简单,下图给出教科书上任意生成多项式G(X)=gnXn+gn-1Xn-1+···+g1X+g0的电路结构:

为什么从右边输入data?

因为CRC是除余数,所以从右边输入数据,相当于把信息位data先左移位。

以简单的CRC8举例,多项式G(x)=X8 +X7 +X6 +X4 +X2 +1 的电路示意图如下:

对应的Verilog code代码如下:

上面的Verilog code上用了LFSR这种变量声明,有没有感到奇怪?

LFSR(线性移位寄存器)和CRC的算法很像的,有兴趣的可去看看LFSR的相关知识。

一位串行输入的CRC电路实现方法很简单,每周期的组合逻辑链路简单延时短。

它的缺点是输入位宽只有一位,所以一个clock周期只能算一位,如果是64bit的信息位就要64个clock周期。

如果需要传输的位数比较多,会对系统的性能产生比较大的影响。

假设要把输入位宽变成8位(byte)输入,电路将是什么样的呢?并行的CRC其实也简单,可以用提前抽取的概念来实现。

用下图来解释一下,CRCM有M个校验位就是有M个寄存器,现在把输入变成N位。

提前抽取就是通过关系函数得到下一个clock寄存器的输入nxt_crc[M-1:0]:

关系函数CN如下:

nxt_crc=CN(crc_out,data),。

CRC校验编程和硬件快速校验探讨

CRC校验编程和硬件快速校验探讨循环冗余校验(Cyclic Redundancy Check,CRC)是最为常用的计算机和仪表数据通信的校验办法。

CRC码是一种线性分组码,编码容易但具有很强的检错纠错能力。

除了各种仪表、变频器等设备,还有一些数字型的输出数据也提供CRC码,如数字DS18B20、集成温湿度采集芯片SHT11等。

但是,各厂商所提供的CRC校验多项式(用于同通信码模除)互有差别,且有CRC8和CRC16之分。

另外,规定模除余数初始值全部的位有全清0或全置1之分(其CRC硬件生成不同),故其模除求余的运算过程也不相同。

初接触者往往难以领晤,省略CRC校验使通信的牢靠性降低。

而不少程序,运算时需要用法较多的RAM单元,较难在80C51、16等低档上运行。

因此,对于嵌入式系统中的CRC校验,事先按照特定的校验多项式,算出1字节数据范围所对应的256个余数,将其作为表格,编程写到程序存储器中查询而避开在线运算,已是十分通用的做法。

鉴于此,有些厂商在解释书中就挺直给出了这个列表。

但假如是CRC16校验,存储表格要占512字节(CRC32则需要1 KB),对于有限的单片机ROM资源来说所占比例不小,往往只由于多装了此表,就不得不升级单片机的型号。

本文分析和说明了实际CRC校验码的生成特点,据此给出节约RAM和ROM且运算迅速的通用CRC校验编程思想和程序结构,并探讨了用少量硬件实现迅速、牢靠CRC校验的办法。

1 CRC原理和实际校验码的反序生成特点机台一个k位二进制数据在传送时,按一定逻辑附加一些冗余位而增大其码距,就能检错和纠错。

标准CRC码是将原数据左移r位,再用r+1位的特殊商定多项式 (polynomial function) 模除之,获得最多为r (8、16、32)位的余数,尾随原数据之后生成k+r位的编码发送。

接收方再用相同的商定多项式,模除收到的数据,余数为0则传输无误,为其他值则对应各个位的出错。

一种CRC并行计算原理及实现方法

一种CRC并行计算原理及实现方法一种常用的CRC并行计算原理及实现方法是通过使用查表法(Table-Driven)。

CRC(循环冗余校验码)是一种常用的数据校验方法,它通过对数据进行异或运算,生成一个校验值,再将校验值附加到数据中传输,接收方根据接收到的数据和附加的校验值进行计算,如果计算的结果与已知的校验值相同,则数据传输没有错误,否则存在错误。

在CRC并行计算中,常见的被检验的数据流是按位顺序传输的。

为了加速计算过程,可以使用查表法来并行计算CRC。

查表法的基本原理是预先计算不同输入字节(8位)对应的CRC,然后利用这些预先计算的结果来进行CRC计算。

具体步骤如下:1.预先计算CRC表:可以根据CRC算法的多项式生成一张256行的CRC查表。

表中每一行对应一个8位字节,每行包含一个32位的CRC值。

这些预先计算的CRC值是通过不断对每个字节进行异或操作来计算出来的。

2.初始化CRC寄存器:将CRC寄存器初始化为全0。

3.逐字节计算:按照顺序读取待计算的数据流中的每个字节。

4.异或操作:将CRC寄存器中的高8位与当前读取的字节进行异或操作,并且将结果作为索引在CRC表中查找。

得到的结果是一个32位的CRC。

5.更新CRC寄存器:将CRC寄存器的高24位更新为从CRC表中查找到的32位CRC值。

6.继续计算:如果数据流还没有结束,重复步骤3至5,直到处理完所有字节。

7.计算结果:最后得到的CRC寄存器中的值就是校验结果,可以将其附加到数据中进行传输。

通过使用查表法的并行计算,可以加快CRC的计算速度。

因为预先计算CRC表的过程只需要进行一次,在后续的计算中只需要进行查表和异或操作,而不需要再进行CRC算法的计算。

此外,还有一些其他的CRC并行计算方法,如使用移位寄存器进行计算等。

这些方法根据具体的场景和需求选择使用。

总之,CRC并行计算的关键是预先计算CRC表并将结果存储起来,然后根据输入的数据进行查表和异或操作,通过并行计算的方式加速CRC的计算过程。

crc知识点总结

crc知识点总结概述循环冗余校验(CRC, Cyclic Redundancy Check)是一种错误检测技术,常用于网络通信、存储系统、通信协议等领域。

它利用除法运算和多项式运算,通过对数据进行计算生成校验码,用于检测数据传输过程中的错误。

CRC的应用范围非常广泛,其简单、高效的特性使得它成为了数据通信中重要的一环。

在现代通信系统中,CRC已经成为了各种通信协议的标准之一,如以太网、WiFi、蓝牙等都应用了CRC进行数据的校验。

本文将对CRC的原理、计算方法、性能评估等知识点进行总结和讨论。

CRC原理CRC的基本原理是通过对数据进行除法运算,利用多项式来生成校验码。

通常情况下,发送方将数据和计算得到的校验码一起发送给接收方,接收方通过对接收的数据和计算校验码进行同样的计算,如果计算得到的校验码与接收到的校验码一致,说明数据传输正确。

CRC可以看作是对多项式的模运算。

对于给定的生成多项式G(x),发送方对数据D(x)进行计算,生成校验码R(x),使得数据发送为D(x) * 2^k + R(x),接收方再对接收到的数据进行同样的计算,得到的余数如果为0则说明数据传输正确。

CRC计算方法CRC的计算方法主要包括两种:硬件实现和软件实现。

硬件实现是指将CRC算法实现为硬件电路的形式,它具有计算速度快、稳定可靠等优点。

通常情况下,硬件实现可以集成到通信芯片、存储芯片等设备中,实现对数据的快速校验。

软件实现是指利用软件程序来实现CRC算法,其优点是易于开发和调试。

通常情况下,可以利用现成的CRC算法库来实现CRC校验功能。

CRC的计算方法可以分为两种:直接计算法和表查找法。

直接计算法是最基本的一种计算方法,其思想是模拟除法运算,通过位运算来逐位计算余数。

这种方法的计算速度相对较慢,但实现起来比较简单。

表查找法是一种优化的计算方法,它利用预先计算好的CRC表来实现CRC校验。

通过查表的方式来实现CRC的计算,可以极大地提高计算速度和效率。

循环冗余校验码_CRC_的硬件并行实现

1引言信息在传递过程中,可能因为各种原因使传输或接收的数据发生错误。

为了能在接收端判断数据的正确性,使用校验码是一种常用的方法。

循环冗余校验码CRC(CyclicRedundancyCode)就是其中的一种。

CRC在通讯传输中的应用范围十分广泛,如USB协议、IEEE802.3标准、IEEE802.11标准、RFID协议等都采用了CRC作为正确性校验的方法。

实际应用的过程一般是在发送端计算发送信息的CRC值,并将它作为信息包/帧的一部分传递给接收端;接收端将对接收到的信息进行CRC计算,并与发送过来的CRC进行比较,从而判断接收的信息是否正确。

CRC的计算实现可以有多种方法,它可以通过软件方式计算,也可以通过硬件方式计算,还可以通过查表得到。

发送时,CRC的计算过程可以在传输之前完成,也可以在传输过程中进行;对CRC的校验可以在接收的同时进行,也可以在传输完成之后进行。

CRC的计算可以是按位串行进行的,也可以是多位并行进行的。

本文将对CRC的原理和并行计算方法进行介绍,并以USB协议中使用的CRC的计算硬件设计实现为例进行讨论。

2循环冗余校验码(CRC)的原理CRC校验利用的是线性编码理论,对于要进行检验的n位二进制码序列,在发送端以一定的规则产生一段k位的校验码(即CRC码),附在信息后边,构成一个新的二进制码序列,共(n+k)位,并发送给接收方。

在接收端,则根据接收的数据部分和CRC码之间是否符合一定的关系来判断传送中是否出现错误。

CRC码的计算和检验过程是将要传送的数据看作是一个多项式M(x),根据要保护的数据长度确定CRC码的长度k和一个生成多项式G(x),然后利用二阶有限域上的除法运算得出M(x)xk/G(x)的余式C(x),这个余数就是CRC码,将它附加在原始数据M(x)之后一起发出。

在接收方的检验方法有两种,一种是针对发送的数据部分采用与发送过程同样的方法进行计算,并与接收到的CRC部分进行比较看是否相同;另一种是针对发送数据M(x)和校验码C(x)部分共同构成的数据按照CRC生成的方法进行计算,按照有限域上的除法计算得出的结果应当是全0。

简单有效的单片机CRC快速算法

简单实用的单片机CRC快速算法1 引言CRC(循环冗余码)检验技术广泛应用于测控及通信领域。

在很多情况下,CRC计算是靠专用的硬件来实现的,但是对于小型低成本的单片机系统来说,若要在没有这些硬件的支持下实现CRC检验,首先要解决的就是如何通过软件高效快速地完成CRC计算的问题,也就是CRC算法的问题。

这里将提供两种算法,它们稍有不同,一种适用于程序空间大一些的51系列等单片机,另一种适用于程序空间的使用条件十分苛刻的PIC单片机。

这些算法按字节进行计算,仅使用查表和简单的异或运算等操作,所以,计算过程相当简捷,而计算速度却很快。

下面先简述一下CRC原理,然后再以CRC-CCITT标准生成多项式为例对算法进行说明,并给出一个51系列单片机子程序和一个PIC单片机子程序。

2 CRC原理CRC检验原理实际上就是在一个p位二进制数据序列之后附加一个r位二进制检验码(序列),从而构成一个总长为n=p +r位的二进制序列,例如,p位二进制数据序列D=[dp-1dp-2 ......d1d0],r位二进制检验码R=[rr-1 rr-2....r1 r0],所得到的这个n位二进制序列就是M=[dp-1dp-2 ......d1d0 rr-1 rr-2....r1 r0];附加在数据序列之后的这个检验码与数据序列的内容之间存在着某种特定的关系。

如果因干扰等原因使数据序列中的某一位或某些位发生错误,这种特定关系就会被破坏,因此,通过检查这一关系, 就可以实现对数据正确性的检验。

校验码R是通过对数据序列D进行二进制除法取余式运算得到的,它被一个称为生成多项式的(r+1)位二进制序列G =[gr gr-1 .... g1 g0]来除,用多项式形式表示为其中,xrD(x)表示将数据序列D左移r位(即在D的末尾再增加r个0位),Q(x)代表这一除法所得的商,R(x)就是所需的余式。

这一运算关系还可以用式(2)来表达其中,Re[ ]表示对括号内的式子进行取余式运算。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

由于数据在传输和存储时可能会由于干扰等原因发生变化,所以一般会采用数据校验来确保数据的完整性。

CRC(循环冗余码)算法是把原始数据输入到一个校验公式中,生成一定长度的校验码,然后把校验码添加到原始数据的后面,组成新的数据,对于串行输入输出的系统,需要循环计算校验码,直到数据全部计算结束[1]。

CRC校验码的作用是保证数据的可靠性,它本身并不是系统要求传输的数据,所以对于系统来说是冗余的。

计算CRC、组成新数据的过程是编码,用相同的方法把数据译码,就可以发现数据是否变化。

CRC算法可以用软件实现,也可以用硬件实现,但软件计算的速度受限于系统CPU的速度,使用硬件方式来实现可以提高计算速度,从而提升系统的通信效率。

最普通的CRC硬件实现方法是串行计算方法,使用一位数据输入,n位长度的原始数据连续计算 n 次后得出校验码,串行计算的电路结构简单,容易实现,可以工作在较高的时钟频率下。

但随着通信速度的不断提高,高的数据传输带宽要求CRC的计算速度越来越快,串行计算的方法已经不适应要求,所以越来越多的使用并行计算方法[2]。

本文先讲述串行计算的实现方法,再在此基础上作一些改进,产生并行计算的电路结构。

1CRC算法

在模运算中,模2[3]加减法的结果是相同的,都可以用逻辑运算“异或”完成,模2乘法运算可以用逻辑运算“与”完成,模2除法只在除数为1时有效,并且结果维持不变,也可以看作是“异或”运算[3]。

二进制序列数据流,可以用模2多项式表示,多项式的系数就是序列的值。

如1010

11可以表示为1×x5,二进制序列最左边的二进

制位表示次数最高的多项式系数[3]。

(x)就是CRC校验码,多项式最高次数为k-1。

编码之后的数据为F(x)=x k×M(x)+R(x),因为模2加减法运算的结果相同,所以F(x)=x k×M(x)-R(x)=Q(x)×G(x),在译码的时候,对F(x)作模运算,结果应该为0。

如果结果不为0,说明 数据在编码后已经发生了变化。

常用的CRC校验公式[3]:

2串行实现

串行计算时,每次输入一位数据,输入数据和上一次异或运算的结果组成新数据,循环进行异或运算,直到所有数据都已经输入,整个电路可以用移位寄存器加异或门实现。

CRC串行实现的电路结构如图1所示[5]。

g

i的取值范围是0或1,取0时,表示断路,不需要异或运算,取1时,表示通路,需要异或运算,其中g0和g k都为1。

对于k位的CRC校验,需要k个寄存器,当有新的数据输入后,异或运算立刻得出新的CRC,寄存器在时钟沿移位,等待新的输入数据,反复循环,就可以计算出CRC的值。

串行的方法虽然可以计算各种CRC,但是一个时钟周期只能计算一位数据,效率比较低,只适用于低速的串行输入输出系统,而当数据传输的速度很高,或者是多位数据并行传输时,需要引入并行计算的实现方法,并行的实现方法可以在一个时钟内对多位数据进行编码,从而提高了CRC 的计算速度。

3并行实现

并行CRC计算,可以在串行计算的基础上改进电路结构来实现。

在串行实现中一个时钟周期处理一位数据,如果能够把串行实现中多个时钟周期处理的数据集中到一个时钟周期内处理,就达到并行处理的目的了。

先分析一下串行实现中每一位CRC校验码的生成过程,CRC的模2多项式为[4]

CRC的长度为k,R j是在计算j位原始 数据后CRC的值所对应的模2多项式,r i、j表示第i位的值, r i-1、j-1是R j-1第i-1位寄存后的值,g i是校验公式对应的数据位(g0、g k为1),d j是输入的第j位原始数据。

所以有

这个函数关系式表示R2j+1只和R2j-1、d2j、d2j+1有关,所以在电路实现时只计算R2j-1,而不用计算R2j,,就可以计算出R2j+1。

从R2j-1到R2j+1计算两位数据的输入,在串行实现中移位寄存两次,需要两个时钟周期,现在一个周期就可以完成,说明串行实现可以转化为两位的并行实现。

图2和图3比较了串行实现和并行实现结构上的区别。

具体到CRC每一位的值,在串行实现中有

上面的公式将串行的电路结构转换成了两位输入的并行电路结构,根据相应的校验公式,可

以得出具体的电路。

用上述方法,串行实现的可以根据需要转化为任意多位并行实现,如果并行处理的位数为w,只需用相同的方法将r i、j推算到r i、j-w一级就可以了。

对于算法CRC-16,如果计算的数据长度是100个字节,时钟频率为1MHz,串行计算的时间为8 00μs,而16位并行输入的计算时间为50μs。

并行实现的计算速度是串行实 现的w倍(w是并行数据输入的宽度),所以当并行输入的数据宽度比较大时,速度上的差异是非常明显的。

并行计算的缺点是使用了多级组合逻辑的反馈,将产生较大的门延迟,特别是在计算时钟的频率很高时,时钟周期非常小,对时延的要求比较高,比如实现32位并行输入的CRC-32,会产生3 1次异或操作,电路的门延时可能会很大,而超出系统的时延限度,这取决于组合电路的具体结构。

组合逻辑在综合的时候,将产生图4的电路结构[5]。

图4所示结构的组合逻辑的延时是各个异或门的累加,异或次数多了以后,延时是很大的,所以要对上面的组合逻辑结果进行优化。

将逻辑组合改成Z=(A^B)^(C^D)^(E^F),电路的功能不变,但综合出的电路结构如图5所示。

优化后的结构利用了电路的并行性,将在串行电路中累加的延时分散到多个并行的分支上,将门延时从5级降低到3级。

对于w位数据的异或操作,图4的结构将产生w1级门延时,图5的结构将产生{log2w}({}表示取小数部分不等于0就加1)级门延时,优化后的结构的延时以指数级减少。

4结束语

CRC的硬件实现可以有串行、并行两种方式,本文在串行实现的基础上对电路进行了改进,实现了CRC的并行计算。

并行实现方式适用于各种数据宽度CRC校验,并行输入的数据宽度越宽,速度越快,由于并行计算是通过多级反馈来实现的,所以复杂的反馈组合电路会带来较大的门延迟,通过优化组合电路的结构,可以很大程度上降低延迟,使电路适用于比较高的时钟频率。

。