第七章 C6713的集成外设7

DSP(TMS320C6713)入门之旅五、I2C的理解和使用

一般DSP上面都集成了I2C模块,这样在连接外部器件时可以很方便的控制外部的器件。

I2C 基本上都是用于外部控制的,因为是是串行总线。

在我们的实验板上I2C总线连接到了两个从设备上面,一个是我们的eeprom,另一个是我们的音频芯片AIC23。

通过I2C协议我们写入和读取eeprom数据,控制AIC23的声音一些属性!简介一下I2C协议的规则:一. 技术性能:工作速率有100K和400K两种;支持多机通讯;支持多主控模块,但同一时刻只允许有一个主控;由数据线SDA和时钟SCL构成的串行总线;每个电路和模块都有唯一的地址;每个器件可以使用独立电源二. 基本工作原理:以启动信号START来掌管总线,以停止信号STOP来释放总线;每次通讯以START开始,以STOP结束;启动信号START后紧接着发送一个地址字节,其中7位为被控器件的地址码,一位为读/写控制位R/W,R/W位为0表示由主控向被控器件写数据,R/W为1表示由主控向被控器件读数据;当被控器件检测到收到的地址与自己的地址相同时,在第9个时钟期间反馈应答信号;每个数据字节在传送时都是高位(MSB)在前;写通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后开始发送第一个数据字节;5. 被控器收到数据字节后发送一个ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;读通讯过程:1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线;2. 发送一个地址字节(包括7位地址码和一位R/W);3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK);4. 主控收到ACK后释放数据总线,开始接收第一个数据字节;5. 主控收到数据后发送ACK表示继续传送数据,发送NACK表示传送数据结束;6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线;DSP中IIC模块框图:1. 总线空闲状态SDA和SCL两条信号线都处于高电平,即总线上所有的器件都释放总线,两条信号线各自的上拉电阻把电平拉高;2. 启动信号START时钟信号SCL保持高电平,数据信号SDA的电平被拉低(即负跳变)。

DSP(TMS320C6713)入门之旅三、中断的理解和使用

学习一个芯片的功能时,我的建议是先学会如何用C语言点亮一个LED灯,然后就是学习一下使用他的中断,因为在做芯片的时候,各个厂家有自己的一套自己的方法。

所以使用中断的就必须了解很多概念,比如如何打开中断,如何安装自己的中断子服务程序,等等!先介绍一下什么叫中断:你在下象棋,突然电话响了,你回屋接电话,然后回来继续下象棋,这个过程就叫做中断响应过程(中断过程)。

CPU执行正常任务———————下象棋保护现场———————————-你已经想好要―将军‖,先在脑海中记下来。

中断发生———————————-电话响-中断服务程序—————————-接电话恢复现场———————————-回来后恢复刚才想法中断返回———————————-你回来继续下象棋中断屏蔽———————————-Boss 正在训话,要求所有电话关机,你不能接电话了。

非屏蔽中断——————————-你内急,即使是Boss 在训话,你还是得到外面去嘘嘘。

可屏蔽中断——————————-你在―闭关修炼‖,可以不受外界干扰所以我们在使用中断之前先得告诉CPU,我们要使用那个中断,当中断发生的时候,你的执行程序的去向(也就是中断服务子程序),最后在返回我们被中断的函数。

这样就完成了我们的中断历程!看看6713执行中断的流程:一、使能了全局中断和子中断,那么CPU每执行一条指令之前就去查询一下有没有中断被置位,如果有产生的,那么CPU就要跳转!二、软件把CPU内部的寄存器A0~A15,B0~B15,等等这些寄存器的值推入堆栈保存,把当前PC寄存器的值放入IRP寄存器中以备中断返回能找到当前被打断的位置(保存现场,中断函数前面得加interrupt关键字)三、CPU的PC指针读出中断向量表的地址,也就是把(ISTP寄存器的值+子中断向量偏移量)装入PC寄存器,这样就执行跳转。

四、在中断向量表里一般有就用跳转指令,这样就可以跳转到我们用C语言编写的中断服务子程序中。

一种高性能浮点DSP芯片TMS320C6713及其最小系统的设计

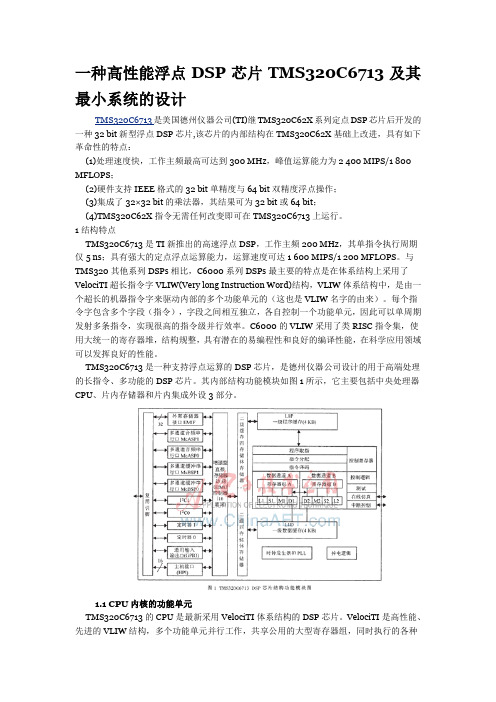

一种高性能浮点DSP芯片TMS320C6713及其最小系统的设计TMS320C6713是美国德州仪器公司(TI)继TMS320C62X系列定点DSP芯片后开发的一种32 bit新型浮点DSP芯片,该芯片的内部结构在TMS320C62X基础上改进,具有如下革命性的特点:(1)处理速度快,工作主频最高可达到300 MHz,峰值运算能力为2 400 MIPS/1 800 MFLOPS;(2)硬件支持IEEE格式的32 bit单精度与64 bit双精度浮点操作;(3)集成了32×32 bit的乘法器,其结果可为32 bit或64 bit;(4)TMS320C62X指令无需任何改变即可在TMS320C6713上运行。

1结构特点TMS320C6713是TI新推出的高速浮点DSP,工作主频200 MHz,其单指令执行周期仅5 ns;具有强大的定点浮点运算能力,运算速度可达1 600 MIPS/1 200 MFLOPS。

与TMS320其他系列DSPs相比,C6000系列DSPs最主要的特点是在体系结构上采用了VelociTI超长指令字VLIW(Very long Instruction Word)结构,VLIW体系结构中,是由一个超长的机器指令字来驱动内部的多个功能单元的(这也是VLIW名字的由来)。

每个指令字包含多个字段(指令),字段之间相互独立,各自控制一个功能单元,因此可以单周期发射多条指令,实现很高的指令级并行效率。

C6000的VLIW采用了类RISC指令集,使用大统一的寄存器堆,结构规整,具有潜在的易编程性和良好的编译性能,在科学应用领域可以发挥良好的性能。

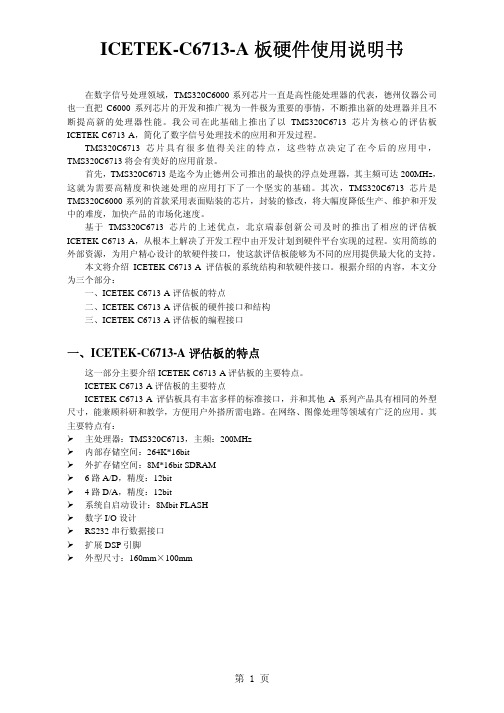

TMS320C6713是一种支持浮点运算的DSP芯片,是德州仪器公司设计的用于高端处理的长指令、多功能的DSP芯片。

其内部结构功能模块如图1所示,它主要包括中央处理器CPU、片内存储器和片内集成外设3部分。

1.1 CPU内核的功能单元TMS320C6713的CPU是最新采用VelociTI体系结构的DSP芯片。

6713DSK硬件简介

《DSP原理及应用》

11

任海鹏

《DSP原理及应用》

4

任海鹏

为子卡预留的标准扩展连接器

通过板上JTAG仿真器与USB主机接口

或外部仿真器连接进行JTAG仿真 单电源+5V供电 一个AIC23立体声编解码器

《DSP原理及应用》

5

任海鹏

统一编址

内部存储器地址0—0x00030000h 0x00030000h—0x7FFFFFFFh保留或

为外设接口 0x80000000h—0xFFFFFFFFh外部存 储器分为四个存储区CE1—CE3

《DSP原理及应用》

6

任海鹏

《DSP原理及应用》

7

任海鹏

《DSP原理及应用》

8

任海鹏

未焊接

《DSP原理及应用》

9

任海鹏

《DSP原理及应用》

10

任海鹏

DSK板为开发提供了必要的硬件和软件环境

2013.01

主讲教师:任海鹏

结构 特点 存储器映射 配置开关设定 连接器 电路板平面视图

2

《DSP原理及应用》

任海鹏

《DSP原理及应用》

3

任海鹏

225MHz

CPU时钟 8MB同步DRAM 512KB非易失性FLASH存储器 4个用户可访问LED和4个DIP 通过CPLD中的寄存器进行目标板软件 配置 可配置的启动选项

c6713例程

c6713例程C6713是一款由德州仪器(Texas Instruments)生产的微控制器,广泛应用于各种嵌入式系统。

以下是C6713的例程,涵盖了其主要功能和特性。

一、C6713简介C6713是一款高性能的32位浮点微控制器,具有强大的运算能力和高速的数字信号处理能力。

它采用TI的Code Composer Studio(CCS)集成开发环境进行开发,可使用TI的MSP430 GCC编译器进行编译。

C6713具有丰富的外设接口,包括UART、SPI、I2C、ADC、DAC等,适用于各种嵌入式系统开发。

二、C6713例程:LED闪烁本例程将展示如何使用C6713控制LED的闪烁。

假设我们已经将LED 连接到P1.0引脚。

1.打开CCS,创建一个新的MSP430项目。

2.在项目中添加main.c源文件,并编写以下代码:c复制代码#include <msp430.h>void main(void){P1DIR |= BIT0; // 设置P1.0为输出引脚while(1){P1OUT |= BIT0; // 打开LED__delay_cycles(50000); // 延时50msP1OUT &= ~BIT0; // 关闭LED__delay_cycles(50000); // 延时50ms }}3.编译并下载程序到C6713。

4.观察LED的闪烁效果。

这个例程演示了如何使用C6713控制LED的闪烁。

通过设置P1DIR 寄存器,我们指定P1.0为输出引脚。

在while循环中,我们使用P1OUT 寄存器控制LED的开关状态,并使用__delay_cycles()函数实现延时。

通过调整延时时间,可以改变LED闪烁的速度。

三、C6713例程:ADC采样本例程将展示如何使用C6713的ADC模块进行模拟信号采样。

假设我们已经将一个模拟信号连接到P2.0引脚。

1.在CCS中打开C6713项目。

一种高性能浮点DSP芯片TMS320C6713及其最小系统的设计

一种高性能浮点DSP芯片TMS320C6713及其最小系统的设计为了实现TMS320C6713的最小系统设计,我们需要考虑以下几个方面:芯片与外围设备的连接、外围电路的设计和电源管理。

首先,为了确保TMS320C6713与外部设备的连接,我们需要提供一些必要的接口和功能模块。

这包括存储器接口、外部总线接口、模数转换器(MCP)接口和通用输入/输出(IO)接口。

存储器接口可以连接闪存和动态随机存储器(DRAM),以提供程序和数据的存储空间。

外部总线接口可以连接其他外围设备,如外部协处理器或通信接口。

MCP接口可以连接模拟信号源,如声音或视频输入。

通用IO接口可以连接其他外设,如显示器、键盘或鼠标。

其次,为了保证TMS320C6713的正常工作,我们还需要设计一些外围电路。

这包括时钟和复位电路、电源管理模块和稳压器。

时钟和复位电路提供了时序控制信号和系统复位信号,以确保芯片的正确初始化和稳定运行。

电源管理模块可以监控芯片的电源供应情况,并在需要时提供稳定的电源。

稳压器可以稳定供应芯片所需的电压,以保证其正常工作。

最后,为了实现TMS320C6713的最小系统设计,我们还需要考虑适当的外围电路连接和布局。

这些包括将上述模块连接到芯片的引脚上,并尽量减小信号传输线的长度和干扰。

此外,还需要对整个系统进行适当的布局和散热设计,以保证芯片的稳定性和可靠性。

总而言之,TMS320C6713是一种高性能浮点DSP芯片,其最小系统设计需要考虑与外围设备的连接、外围电路设计和电源管理。

通过合理连接和布局各个模块,并采取有效的电源管理和散热设计,可以实现TMS320C6713的高性能和稳定运行。

TMS320C6713 DSP的SPI接口设计

|

此位必须为 0(SINGLE)

MCBSP_FMKS(RCR, RFRLEN2, DEFAULT)

|

MCBSP_FMKS(RCR, RWDLEN2, DEFAULT)

|

MCBSP_FMKS(RCR, RCOMPAND, DEFAULT)

|

MCBSP_FMKS(RCR, RFIG, DEFAULT)

|

MCBSP_FMKS(SPCR, FREE, DEFAULT)

|

MCBSP_FMKS(SPCR, SOFT, DEFAULT)

|

MCBSP_FMKS(SPCR, FRST, YES)

|

MCBSP_FMKS(SPCR, GRST, YES)

|

//YES-0; NO-1 //YES-0; NO-1

MCBSP_FMKS(SPCR, XINTM, XRDY)

|

//采样率发生器时钟由 DSP

内部提供

MCBSP_FMKS(SRGR, FSGM, DXR2XSR)

|

|

MCBSP_FMKS(SPCR, XSYNCERR, DEFAULT)

|

MCBSP_FMKS(SPCR, XEMPTY, DEFAULT)

|

MCBSP_FMKS(SPCR, XRDY, DEFAULT)

一种高性能浮点DSP芯片TMS320C6713及其最小系统的设计

?}竺量:竺耋兽去。 2・2竺萋竺焉烹銎。.。。.。。 +。。。。。+。。 。;。套辇翼竺慧攀銎三。,。鼍象专鬯D。。S+P竺兰寰序要譬

≤芸;菱裔善囊萎;’溢≤毒蓊。军茹嘉瘩LSC器菩莴盖;

笔芝甚;姜薹赛嘉-薪苡蒙南黼}菖笔蒌尽昌磊薹三霁 储i"器la:F气蕊;‘石善;蒹磊三!”…“4。。、…。“““

级—

四

●

脚

叫定时器1 I.+ Hl定时器0卜◆

+—叫通用输入k+

l输出VI(GPIO)l

卜

存 储

体

叫f

级搬存攀JI

{时钟发生器和PLL} I掉电逻辑l

存

储

叫黹口卜

器

图1 TMS320C6713

DSP芯片结构功能模块罔

执行的各种操作是由VLIW的长指令分配模块进行同 步协调的,这种结构使其成为多通道、多功能以及高性 能应用的首选器件。,CPU内核作为DSP芯片的运算和控 制中心,包括以下几部分:(1)程序取指令单元、指令分 配单元、指令译码单元;(2)2个数据通道A、B,每个通道 中包括*个由16个32 bit寄存器组成的寄存器组和4

800MFLOPS;

要的特点是在体系结构上采用了VelociT!超长指令字 VLIW(Very

long Instruction

Word)结构,VLIW体系结构

中,是由一个超长的机器指令字来驱动内部的多个功能 单元的(这也是VLIW名字的由来)。每个指令字包含多 个字段(指令),字段之间相互独立,各自控制一个功能 单元,因此可以单周期发射多条指令,实现很高的指令 级并行效率。C6000的VLIW采用了类RISC指令集,使 用大统一的寄存器堆,结构规整,具有潜在的易编程性 和良好的编译性能,在科学应用领域可以发挥良好的性能。 TMs320C6713是一种支持浮点运算的DSP芯片,是 德州仪器公司设计的用于高端处理的长指令、多功能的 DSP芯片。其内部结构功能模块如图1所示,它主要包 括中央处理器CPU、片内存储器和片内集成外设3部分。

TMS320C6713 DSP的Flash启动设计

/data/html/2007-6-15/41753.html引言随着近年来数字信号处理器(DSP)技术的迅猛发展,其越来越广泛地应用于国民经济的各个领域中。

其中,TI公司推出的TMS320C6000系列DSP器件更是在许多需要进行大量数字信号处理运算并兼顾高实时性要求的场合得以应用。

TMS320C6000系列DSP的系统设计过程中,DSP器件的启动加载设计是较难解决的问题之一。

C6000系列DSP的启动加载方式包括不加载、主机加载和EMIF加载3种。

3种加载方式的比较:不加载方式仅限于存储器0地址不是必须映射到RAM空间的器件,否则在RAM空间初始化之前CPU会读取无效的代码而导致错误;主机加载方式则要求必须有一外部主机控制DSP的初始化,这将增加系统的成本和复杂度,在很多实际场合是难以实现的;EMIF加载方式的DSP与外部ROM /Flash接口较为自由,但片上Bootloader工具自动搬移的代码量有限(1 KB/64 KB)。

本文主要讨论常用的EMIF加载方式。

1 EMIF加载分析实际应用中,通常采用的是EMIF加载方式,把代码和数据表存放在外部的非易失性存储器里(常采用Flash 器件)。

下面以TMS320C6000系列中最新的浮点CPU——TMS320C6713(简称“C6713”)为例,详细分析其EMIF 加载的软硬件实现。

硬件方面,其与16位宽度的Flash器件的接口如图1所示。

对于不同的DSP器件,加载方式的配置引脚稍有不同。

C6713的配置引脚及其定义如表1所列。

应用程序的大小决定了片上的Bootloadet工具是否足够把所有的代码都搬移到内部RAM里。

对于C6713,片上的Bootloader工具只能将1 KB的代码搬入内部RAM。

通常情况下,用户应用程序的大小都会超过这个限制。

所以,需要在外部Flash的前1 KB范围内预先存放一小段程序,待片上Bootloader工具把此段代码搬移入内部并开始执行后,由这段代码实现将Flash中剩余的用户应用程序搬移入内部RAM中。

DSP(TMS320C6713)入门之旅一、LED的点亮

最近很多朋友开始学习DSP了(小双同志也加入这个团伙),本人基本上入门。

在此给他家分享一下DSP的入门经验。

其实DSP和我们本科所使用的单片机基本上架构一致,只是在它的内部集成了一系列的运算单元和逻辑移位单元,并且安排了指令流水,这样在运算性能上大大的提高,可以完成一系列的复杂计算。

当然DSP内部也集成了一系列外设,我这儿使用的是TMS320C6713 DSP,这块DSP主频可以达到450M,可以安排8级指令流水,在同一时刻可以同时执行8条指令,当然这要求的是CPU内部的运算单元不能冲突!好了,在此我就不多介绍了,免得把大家说得晕呼呼的!我们刚才是入门了解这些基本上没用,我们得一步一步的按着简单的东西一步一步的做实验。

所以我们今天开始一个最简单的实验—LED灯的点亮!我们一般学习是要买一块开发板,在此我不做推销,其实每一块开发板都基本上差不多,很多就是按照TI公司的Demo板,而设计的。

如果没有学习板,自己看书看了半年,还不如我拿到板子调试一个月的效果,因为很多东西是要在实际中才知道他的作用。

我们用一个板子一般要几样东西:一、原理图(知道每一根信号线的走向,比如我们的LED就连接到DSP的GPIO的13脚)二、芯片资料(芯片的总的芯片Datasheet和子模块的Datasheet,一般在芯片资料中总的芯片资料会告诉大家芯片的整体规划,比如内存分布,特殊寄存器的分布和具体的地址,而子模块资料会把这个模块的功能和使用介绍得更为详细)三、电路板和仿真器(这个是投入较大的一笔了)四、编译软件和计算机(希望在做实验之前大家用过编译器,不一定是CCS,因为所有基于windows上的编译软件都是一个样)我们来开始第一步,查看我们的电路板上的LED灯的位置和DSP的信号线的连接:从左边的几个原理图的截图我们可以清晰的看到LED灯接到了GPIO的13脚,中间用了一个缓冲器过度了一下,实际的控制信号还是来自DSP的GPIO13。

ICETEK-C6713-A 硬件使用说明书

16

A17 C6713 地址线 A17

17

GND 地线

18

GND 地线

19

D0 C6713 数据线 D0,双向总线,

20

D1 C6713 数据线 D1

21

D2 C6713 数据线 D2

22

D3 C6713 数据线 D3

23

D4 C6713 数据线 D4

24

D5 C6713 数据线 D5

25

D6 C6713 数据线 D6

7

NC

保留

8

A20

C6713 地址线 A20

9

NC

保留

10

A21

C6713 地址线 A21

11

NC

保留

12

NC

保留

13

CLKS0 定时器 0 输出

14

NC

保留

15

CLKS1 定时器 1 输出

16

NC

保留

17

GND 地线

18

GND 地线

19

SDA0 I2C 数据接口

20

SCL0 I2C 时钟接口

21

NC

(10). P5:C6713 的仿真接口,用于连接 ICETEK-5100 系列的仿真器或兼容产 品。注意,使用的仿真器必须支持 3.3V 仿真。

(11). J4,J5:D/A 功能选择跳线,进行 7616、7617 芯片选择。(由厂家跳线) (12). J7:4 个用户开关输入。可以用作 DSP 的输入信号。软件可以读取它的状

小。下面是这个接口的插孔示意图:

+5V

地(GND) 图 2.2 电源插孔示意图 (2). P6:9 针 D 型连接器,异步串口连接器,符合 RS-232 规范,输出电平为正负 12V。下面是 9 针连接器的管脚定义:

SEED-DEC6713 实验指导书

DSP实验指导书李忠明2011.5机电工程实验教学中心DSP实验箱组成及调试工具安装1.实验箱整体配置实验箱原理框图SEED-DTK_FPD实验箱由以下几部分构成:1. SEED-DEC6713 实验箱DSP基本系统z高性能的32-位浮点DSP(TMS320C6713):主频可达300MHz,处理性能高达2400MIPS;z SDRAM:2M×32-位(可扩展至4M×32位)z Flash:256K×16-位(可扩展至1M×16位)z提供看门狗电路、电源监视、上电复位、手动复位z2路编程可选的RS232/RS422/RS485z AC97标准的Audio音频接口z2路McASP2. SEED-MMI5402 实验箱人机接口模块z处理器为 TMS320C5402 DSPz SRAM:64K×16-位(可扩展至256K×16位)z Flash:256K×16-位(用于存放二级标准汉字库及驻留实验程序)z提供看门狗电路、电源监视、上电复位、手动复位z1路RS232接口z1路12位10μS建立时间±10V输出D/A,可扩充至17路z 19键薄膜键盘z 240*128大屏幕液晶显示3. SEED-DTK_IO 实验箱输入/输出模块z 64个宏单元可编程CPLD,完成交通灯和I/O实验z音频驱动电路,直接驱动8Ω无源音箱z MIC接口,Line In接口z电源工作指示z D/A输出测试端z步进和直流伺服电机z立体声耳麦,音频线4. SEED-DTK_CPLD 实验箱CPLD实验模块z 64个宏单元可编程CPLDz6位7段LED显示,完成计数实验z CPLD编程JTAG接口z8个LED指示灯2 CCS安装在实验箱使用过程中主要使用的是CCS6000,在此仅介绍 CCS6000的安装与使用。

步骤如下:第一步:双击setup图标,选择Code Composer Studio开始安装;第二步~第五步:采用默认选择;第六步:默认安装路径为c:\ti;此路径可更改。

TMS320C6713B DSP的外部FLASH引导

TMS320C6713B DSP 的外部FLASH 引导1 引言目前,TI 公司的TMS320C6713B 已经在生化分析仪器中广泛实用。

其运算速度快、精度高。

使其在牛化分析仪中具有独特的优势。

其改进的哈佛结构、先进的多总线和多级流水线机制、专用的硬件乘法器、高效的指令集,使其易于嵌入信号滤波、信息融合算法,而不会牺牲其实时性。

TMS320C6713B 的速度快、精度高、体积小、成本低、开发周期短、可靠性高以及抗干扰能力强等优点,可以满足生化分析仪对硬件系统的要求。

TMS320C6000 系列数字信号处理器(DSP)是TMS320 DSP 家族的重要系列。

该系列DSP 芯片具有定点和浮点两种,其中,TMS320C62x 和TMS320C64x 为定点系列,而TMS320C67x 为浮点系列。

目前,TMs320c6000 系列数字信号处理器均无程序存储器,必须进行扩展,才能用于生化分析仪。

2 DSP 芯片TMS320C6713BTMS320C6713B 是r11 公司推出的高性能浮点数字信号处理器,采用先进的超长指令字(VLIW)结构,最高时钟频率可达300MHz,每个时钟周期可以执行8 条32 位指令。

该芯片可以方便地与SDRAM,SBSRAM,SRMA,ROM 和FLASH 相连接。

由于该DSP 速度快,精度高,所以该DSP 广泛用于分析仪器、语音信号处理、各种计算模块等。

TMS320C6713B 还具有两个12C 接口、主机并行接口(HPI)、两个多通道音频串行口(MeASPs)、两个多通道缓冲串行口等。

可以方便的与外部器件接口。

由于其内部RAM(256K)空问较大,所以作为一般的应用,不必外扩RAM。

TMS320C6713B 具有三种引导(启动)方式:。

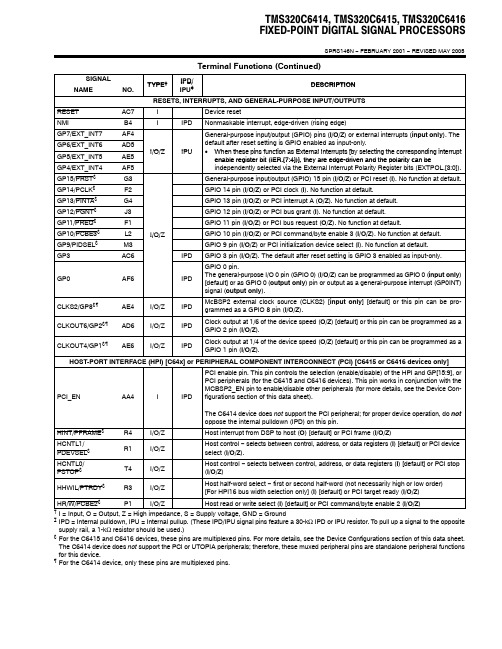

MEMORY存储芯片TMS320C6713GDP中文规格书

TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005Terminal Functions (Continued)SIGNALNAMENO.TYPE †IPD/IPU ‡DESCRIPTION RESETS, INTERRUPTS, AND GENERAL-PURPOSE INPUT/OUTPUTS RESETAC7I Device reset NMIB4I IPD Nonmaskable interrupt, edge-driven (rising edge)GP7/EXT_INT7AF4General-purpose input/output (GPIO) pins (I/O/Z GP6/EXT_INT6AD5General purpose input/output (GPIO) pins () or external interrupts (input only ). The default after reset setting is GPIO enabled as input-only.GP5/EXT_INT5AE5I/O/Z IPU •When these pins function as External Interrupts [by selecting the corresponding interrupt GP4/EXT_INT4AF5enable register bit (IER.[7:4])], they are edge-driven and the polarity can be independently selected via the External Interrupt Polarity Register bits (EXTPOL.[3:0]).GP15/PRST §G3General-purpose input/output (GPIO) 15 pin (I/O/Z ) or PCI reset (I ). No function at default.GP14/PCLK §F2GPIO 14 pin (I/O/Z ) or PCI clock (I ). No function at default.GP13/PINTA §G4GPIO 13 pin (I/O/Z ) or PCI interrupt A (O/Z ). No function at default.GP12/PGNT §J3GPIO 12 pin (I/O/Z ) or PCI bus grant (I ). No function at default.GP11/PREQ §F1GPIO 11 pin (I/O/Z ) or PCI bus request (O/Z ). No function at default.GP10/PCBE3§L2GPIO 10 pin (I/O/Z ) or PCI command/byte enable 3 (I/O/Z ). No function at default.GP9/PIDSEL §M3I/O/Z GPIO 9 pin (I/O/Z ) or PCI initialization device select (I ). No function at default.GP3AC6IPD GPIO 3 pin (I/O/Z ). The default after reset setting is GPIO 3 enabled as input-only.GP0AF6IPD GPIO 0 pin.The general-purpose I/O 0 pin (GPIO 0) (I/O/Z ) can be programmed as GPIO 0 (input only )[default] or as GPIO 0 (output only ) pin or output as a general-purpose interrupt (GP0INT)signal (output only ).CLKS2/GP8§¶AE4I/O/Z IPD McBSP2 external clock source (CLKS2) [input only ] [default] or this pin can be pro-grammed as a GPIO 8 pin (I/O/Z ).CLKOUT6/GP2§¶AD6I/O/Z IPD Clock output at 1/6 of the device speed (O/Z ) [default] or this pin can be programmed as aGPIO 2 pin (I/O/Z ).CLKOUT4/GP1§¶AE6I/O/Z IPD Clock output at 1/4 of the device speed (O/Z ) [default] or this pin can be programmed as aGPIO 1 pin (I/O/Z ).HOST-PORT INTERFACE (HPI) [C64x] or PERIPHERAL COMPONENT INTERCONNECT (PCI) [C6415 or C6416 devices only]PCI_EN AA4I IPD PCI enable pin. This pin controls the selection (enable/disable) of the HPI and GP[15:9], orPCI peripherals (for the C6415 and C6416 devices). This pin works in conjunction with theMCBSP2_EN pin to enable/disable other peripherals (for more details, see the Device Con-figurations section of this data sheet).The C6414 device does not support the PCI peripheral; for proper device operation, do notoppose the internal pulldown (IPD) on this pin.HINT/PFRAME §R4I/O/Z Host interrupt from DSP to host (O ) [default] or PCI frame (I/O/Z )HCNTL1/PDEVSEL §R1I/O/Z Host control − selects between control, address, or data registers (I ) [default] or PCI device select (I/O/Z ).HCNTL0/PSTOP §T4I/O/Z Host control − selects between control, address, or data registers (I ) [default] or PCI stop (I/O/Z )HHWIL/PTRDY §R3I/O/Z Host half-word select − first or second half-word (not necessarily high or low order)[For HPI16 bus width selection only] (I ) [default] or PCI target ready (I/O/Z )HR/W/PCBE2§P1I/O/Z Host read or write select (I ) [default] or PCI command/byte enable 2 (I/O/Z )†I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground ‡IPD = Internal pulldown, IPU = Internal pullup. (These IPD/IPU signal pins feature a 30-k Ω IPD or IPU resistor. T o pull up a signal to the opposite supply rail, a 1-k Ω resistor should be used.)§For the C6415 and C6416 devices, these pins are multiplexed pins. For more details, see the Device Configurations section of this data sheet.The C6414 device does not support the PCI or UTOPIA peripherals; therefore, these muxed peripheral pins are standalone peripheral functions for this device.¶For the C6414 device, only these pins are multiplexed pins.TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005 Terminal Functions (Continued)SIGNAL NAME NO.TYPE†IPD/IPU‡DESCRIPTIONEMIFB (16-bit) − CONTROL SIGNALS COMMON TO ALL TYPES OF MEMORY||kBCE3A13O/Z IPUBCE2C12O/Z IPU EMIFB memory space enablesBCE1B12O/Z IPU•Enabled by bits 26 through 31 of the word address BCE0A12O/Z IPU•Only one pin is asserted during any external data accessBBE1D13O/Z IPU EMIFB byte-enable control•Decoded from the low-order address bits. The number of address bits or byte enables used depends on the width of external memoryBBE0C13O/Z IPUused depends on the width of external memory.•Byte-write enables for most types of memory•Can be directly connected to SDRAM read and write mask signal (SDQM)BPDT E12O/Z IPU EMIFB peripheral data transfer, allows direct transfer between external peripheralsEMIFB (16-BIT) − BUS ARBITRATION||kBHOLDA E13O IPU EMIFB hold-request-acknowledge to the hostBHOLD B19I IPU EMIFB hold request from the hostBBUSREQ E14O IPU EMIFB bus request outputEMIFB (16-BIT) − ASYNCHRONOUS/SYNCHRONOUS MEMORY CONTROL||kBECLKIN A11I IPD EMIFB external input clock. The EMIFB input clock (BECLKIN, CPU/4 clock, or CPU/6 clock) is selected at reset via the pullup/pulldown resistors on the BEA[15:14] pins.BECLKIN is the default for the EMIFB input clock.BECLKOUT2D11O/Z IPD EMIFB output clock 2. Programmable to be EMIFB input clock (BECLKIN, CPU/4 clock, or CPU/6 clock) frequency divided by 1, 2, or 4.BECLKOUT1D12O/Z IPD EMIFB output clock 1 [at EMIFB input clock (BECLKIN, CPU/4 clock, or CPU/6 clock) frequency].BARE/BSDCAS/ BSADS/BSRE A10O/Z IPUEMIFB asynchronous memory read-enable/SDRAM column-address strobe/programmablesynchronous interface-address strobe or read-enable•For programmable synchronous interface, the RENEN field in the CE Space SecondaryControl Register (CExSEC) selects between BSADS and BSRE:If RENEN = 0, then the BSADS/BSRE signal functions as the BSADS signal.If RENEN = 1, then the BSADS/BSRE signal functions as the BSRE signal.BAOE/BSDRAS/ BSOE B11O/Z IPUEMIFB asynchronous memory output-enable/SDRAM row-address strobe/programmablesynchronous interface output-enableBAWE/BSDWE/BSWE C11O/Z IPU EMIFB asynchronous memory write-enable/SDRAM write-enable/programmable synchro-nous interface write-enableBSOE3E15O/Z IPU EMIFB synchronous memory output enable for BCE3 (for glueless FIFO interface) BARDY E11I IPU EMIFB asynchronous memory ready input†I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground‡IPD = Internal pulldown, IPU = Internal pullup. (These IPD/IPU signal pins feature a 30-kΩ IPD or IPU resistor. T o pull up a signal to the opposite supply rail, a 1-kΩ resistor should be used.)||These C64x™ devices have two EMIFs (64-bit EMIFA and 16-bit EMIFB). The prefix “A” in front of a signal name indicates it is an EMIFA signal whereas a prefix “B” in front of a signal name indicates it is an EMIFB signal. Throughout the rest of this document, in generic EMIF areas of discussion, the prefix “A” or “B” may be omitted from the signal name.k To maintain signal integrity for the EMIF signals, serial termination resistors should be inserted into all EMIF output signal lines.。

第七章C6713的集成外设7

第七章C6713的集成外设7概述——资源BIT / TI2概述——框图BIT / TI概述——资源BIT / TI7两级存储资源两级存储结构由27个控制寄存器完成维护和控制From:To:外部存储器片内数据存储器片内数据存储器片内程序存储器程序启动–向主控制寄存器START域写入00b,停止当前通道数据整序BIT / TI28BIT / TI EDMA —结构16组通道传输参数69组重加载参数空闲区32 BIT / TI设置TCC和CCER通道链接使能寄存器BIT / TI 框图C6201/C6701的HPI41C6211/C6711的HPIBIT / TI帧同步信号FSR激活数据的接收操作?SPCR寄存器中的RRDY位标示接受状态?RRDY=1表示数据接收寄存器(DRR)已准备好?帧同步信号FSX激活数据移位输出?SPCR寄存器中的XRDY位标示发送状态?XRDY=1表示数据发送寄存器(DXR)已空典型传输时序每帧包含两个相(Phase)每帧包含两个相(Phase)phase 1中包含1个8-bit 的数据单元BIT / TI 59传输—例子3忽略帧位数据数据延迟范围:0~2个周期?给用户提供了更大的灵活性BIT / TI传输—例子44个8-bit 数据(R/X)PHASE=0(R/X)FRLEN1=3h (R/X)WDLEN1=0改为1个32-bit 数据(R/X)PHASE=0(R/X)FRLEN1=0(R/X)WDLEN1=5h压/扩硬件框图扩展数据格式DXR中的数据BIT / TI66使能所有的数据单元,没有屏蔽?都会执行DXR-XSR 禁止/屏蔽所有单元,选择0号子帧中的通道1和3发送使能/屏蔽所有单元,选择0号子帧中的通道1和3所有通道都执行DXR-XSR 70屏蔽所有单元,选子帧的)发)选择的发送通道被输出屏蔽不影响BIT / TI71TDM 总线上的多个McBSPDSP1作为主控?三者分时占有串行总线进行传输?dummychannel 用来避免切换时总线竞争McBSP作主控:提供时钟和设备使能McBSP为从模式:接收时钟和设备使能BIT / TI74SPI—控制CLKSTP=10b时的SPI 传输McBSP可设置参数:时钟无效期间的电平收发数据的边沿有无延迟接口实例—AIC例子实例—VBAPBIT / TI 寄存器设置BIT / TIMcBSP控制寄存器设置@ 200MHz CPU clock定时器—框图寄存器控制各个开关点时钟模式FUNC = 0可以控制TSTAT输出C621x/C671x EMIF 信号BIT / TI。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

概述——资源

BIT / TI2概述——框图

BIT / TI

概述——资源

BIT / TI7

两级存储资源

两级存储结构

•由27个控制寄存器完成维护和控制

From:To:

外部存储器片内数据存储器

片内数据存储器片内程序存储器

•程序启动

–向主控制寄存器START域写入00b,停止当前通道

数据整序

BIT / TI28

BIT / TI EDMA —结构

•16组通道传输参数

•69组重加载参数

•空闲区

32 BIT / TI

•设置TCC和CCER

通道链接使能寄存器

BIT / TI 框图

C6201/C6701的HPI

41

C6211/C6711的HPI

BIT / TI

•帧同步信号FSR激活数据的接收操作•SPCR寄存器中的RRDY位标示接受状态•RRDY=1表示数据接收寄存器(DRR)已准备好•帧同步信号FSX激活数据移位输出•SPCR寄存器中的XRDY位标示发送状态•XRDY=1表示数据发送寄存器(DXR)已空

典型传输时序

•每帧包含两个相(Phase)

•每帧包含两个相(Phase)

•phase 1中包含1个8-bit 的数据单元BIT / TI 59

传输—例子3

•忽略帧位数据

•数据延迟

•范围:0~2个周期•给用户提供了更大的灵活性

BIT / TI

传输—例子4

4个8-bit 数据(R/X)PHASE=0(R/X)FRLEN1=3h (R/X)WDLEN1=0

改为1个32-bit 数据(R/X)PHASE=0(R/X)FRLEN1=0(R/X)WDLEN1=5h

压/扩硬件框图

扩展数据格式

DXR中的数据

BIT / TI66

使能所有的数据单元,没有屏蔽•都会执行DXR-XSR 禁止/屏蔽所有单元,选择0号子帧中的通道1和3发送

使能/屏蔽所有单元,选择0号子帧中的通道1和3

•所有通道都执行DXR-XSR 70

屏蔽所有单元,选子帧的)发)选择的发送通道被输出屏蔽不影响BIT / TI

71

TDM 总线上的多个McBSP

•DSP1作为主控•三者分时占有串行总线进行传输•dummy channel 用来避免切换时总线竞争

McBSP作主控:

提供时钟和设备使能McBSP为从模式:

接收时钟和设备使能

BIT / TI74

SPI—控制

CLKSTP=10b时的SPI 传输

McBSP可设置参数:

•时钟无效期间的电平

•收发数据的边沿

•有无延迟

接口实例—AIC例子实例—VBAP

BIT / TI 寄存器设置

BIT / TI

McBSP控制寄存器设置@ 200MHz CPU

clock

定时器—框图

寄存器控制各个开关点

•

•时钟模式

•FUNC = 0

•可以控制

TSTAT

输出

C621x/C671x EMIF 信号BIT / TI。