LDMOS静电

demos与ldmos工作原理

demos与ldmos工作原理在现代电子设备中,demos(Double-diffused Metal Oxide Semiconductor)和ldmos(Lateral Double-diffused MetalOxide Semiconductor)是常用的半导体器件。

它们在许多领域中都发挥着重要作用,如通信、功率放大器和射频应用。

本文将介绍这两种器件的工作原理和特点。

demos和ldmos都是金属氧化物半导体场效应晶体管(MOSFET)的变种。

它们的工作原理基于PN结和场效应晶体管的结合。

在demos中,PN结的扩散区域被双重扩散,从而形成了一个耐压区。

而在ldmos中,扩散区域是沿着晶体管表面扩散的,这种结构使得器件在导通状态下具有更低的电阻。

在demos中,PN结的双重扩散使得器件具有更高的耐压能力。

当器件处于关断状态时,PN结的扩散区域可以承受较高的电压而不会发生击穿。

这使得demos在高压应用中具有优势,如电源管理和功率放大器。

而ldmos则通过沟道扩散技术,使得器件在导通状态下具有更低的电阻,从而在功率放大器和射频应用中表现出色。

除了耐压能力和导通电阻之外,demos和ldmos还有许多其他特点。

例如,它们通常具有较高的开关速度和较低的漏电流,这使得它们在高频和低功耗应用中具有优势。

此外,它们的制造工艺相对成熟,成本较低,因此在大规模生产中具有竞争优势。

总的来说,demos和ldmos是两种在不同应用领域中发挥作用的重要器件。

它们的工作原理基于PN结和场效应晶体管的结合,具有耐压能力强、导通电阻低、开关速度快和制造成本低等特点。

随着电子技术的不断发展,相信它们将在更多领域中发挥重要作用。

新型NBL改善LDMOS器件的ESD性能

sr c u e o de —s u c tu t r fUn r o r e NBL i h D r tc ie cr u th s g o fe to n t e ES p o e tv ic i a o d e c n HBM&MM d . mo e

着非 常 好的 效果 .可 以在功 能相 当的情 况下 ,大大 节 省器件 的面 积 。

关 键 词 :互补型金属 氧化物品体管 ;埋藏层;静电放电;横向扩散

中图分 类号 :T 3 618 (0 8 3 0 0 — 4 6 2 5 6 2 0 )0 — 0 9 0

摘 要 :介绍了几种常见的 N型埋藏层 (B )静电放电 (S )器件 ,阐述 了 N L E D的影响,提出了 NL ED B 对 S

新 结构 的 N L器 件 ( n e- o reNB ) 比较 U d rsuc B B U d rs uc L 。 n e o r N L器 件 和其 它常 用器 件 的优 缺点 ,对 比了它 和 - e 传统 器 件 的 E D测试 数 据 :结果 表 明 ,U d rsu e B S n e-o r L器 件在 横 向 扩 散 MO ( D O ) E D 保 护 电路 中 有 c N S LM S S

I p o i g t e ES Pe f r a c fLDM O S De ie m r vn h D ro m n e o vc wih Ne NBL t w

LU Y - ig E G We -i U S u y n I u qn ,D N n j,H h - u

A b t a t S v rlkn s o S e ie t tp u e a e NB ) ae it d c d h sr c : e ea id fE D d vc swi N— y e b r d ly r f L r nr u e .T e h i o

LDMOS简介

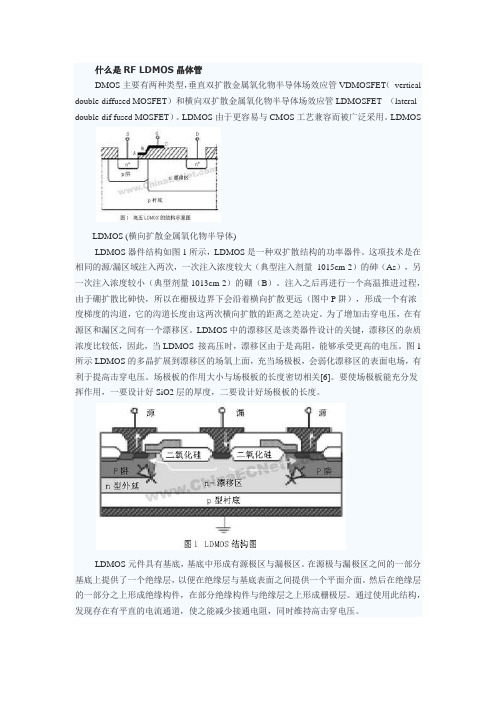

什么是RF LDMOS晶体管DMOS主要有两种类型,垂直双扩散金属氧化物半导体场效应管VDMOSFET(vertical double-diffused MOSFET)和横向双扩散金属氧化物半导体场效应管LDMOSFET (lateral double-dif fused MOSFET)。

LDMOS由于更容易与CMOS工艺兼容而被广泛采用。

LDMOSLDMOS (横向扩散金属氧化物半导体)LDMOS器件结构如图1所示,LDMOS是一种双扩散结构的功率器件。

这项技术是在相同的源/漏区域注入两次,一次注入浓度较大(典型注入剂量1015cm-2)的砷(As),另一次注入浓度较小(典型剂量1013cm-2)的硼(B)。

注入之后再进行一个高温推进过程,由于硼扩散比砷快,所以在栅极边界下会沿着横向扩散更远(图中P阱),形成一个有浓度梯度的沟道,它的沟道长度由这两次横向扩散的距离之差决定。

为了增加击穿电压,在有源区和漏区之间有一个漂移区。

LDMOS中的漂移区是该类器件设计的关键,漂移区的杂质浓度比较低,因此,当LDMOS 接高压时,漂移区由于是高阻,能够承受更高的电压。

图1所示LDMOS的多晶扩展到漂移区的场氧上面,充当场极板,会弱化漂移区的表面电场,有利于提高击穿电压。

场极板的作用大小与场极板的长度密切相关[6]。

要使场极板能充分发挥作用,一要设计好SiO2层的厚度,二要设计好场极板的长度。

LDMOS元件具有基底,基底中形成有源极区与漏极区。

在源极与漏极区之间的一部分基底上提供了一个绝缘层,以便在绝缘层与基底表面之间提供一个平面介面。

然后在绝缘层的一部分之上形成绝缘构件,在部分绝缘构件与绝缘层之上形成栅极层。

通过使用此结构,发现存在有平直的电流通道,使之能减少接通电阻,同时维持高击穿电压。

LDMOS与普通MOS管主要有两点区别:1,采用LDD结构(或称之为漂移区);2,沟道由两次扩散的横向结深控制。

LDMOS 的优势• 卓越的效率,可降低功率消耗与冷却成本• 卓越的线性度,可将信号预校正需求降到最低• 优化超低热阻抗,可缩减放大器尺寸与冷却需求并改善可靠度• 卓越的尖峰功率能力,可带来最少数据错误率的高3G 数据率• 高功率密度,使用较少的晶体管封装• 超低感抗、回授电容与串流闸阻抗,目前可让LDMOS 晶体管在双载子器件上提供7 bB 的增益改善• 直接源极接地,提升功率增益并免除BeO 或AIN 隔离物质的需求• 在GHz 频率下拥有高功率增益,带来更少设计步骤、更简易更具成本效益的设计(采用低成本、低功率驱动晶体管)• 绝佳的稳定性,由于负漏极电流温度常数,所以不受热散失的影响• 比双载子更能忍受较高的负载未匹配现象(VSWR),提高现场实际应用的可靠度• 卓越的射频稳定度,在栅极与漏极间内置隔离层,可以降低回授电容• 在平均无故障时间(MTTF) 上有相当好的可靠度LDMOS主要的缺点1.功率密度低;2.容易受到静电的破坏。

ldmos工作原理

ldmos工作原理LDMOS工作原理。

LDMOS(Laterally Diffused Metal Oxide Semiconductor)是一种常见的功率MOSFET(金属氧化物半导体场效应晶体管),在射频和微波功率放大器中得到广泛应用。

LDMOS器件具有低电阻、高电压和高频特性,因此在无线通信、广播、雷达和其他射频应用中具有重要作用。

本文将介绍LDMOS的工作原理,以便更好地理解其在功率放大器中的应用。

LDMOS的结构。

LDMOS器件通常由N型衬底上的P型沟道和N型扩散层组成。

在P型沟道区域,有一层金属氧化物绝缘层(MOS结构),用于控制沟道中的电子流。

P型沟道和N型扩散层之间的结构使得LDMOS器件具有较高的耐压能力,适合用于高电压应用。

LDMOS的工作原理。

当在LDMOS器件的门极上施加正向电压时,形成的电场使P型沟道中的电子被吸引到N型扩散层,从而形成导通通道。

当信号电压施加在沟道上时,电子将在沟道中形成连续的电流,从而实现信号的放大。

在LDMOS器件中,电子的主要流动路径是沿着P型沟道和N型扩散层的界面。

由于P型沟道的电阻较低,电子在沟道中的移动速度较快,因此LDMOS器件能够实现较高的电流传输能力。

同时,N型扩散层的结构使得LDMOS器件能够承受较高的电压,适合用于功率放大器等高压应用。

LDMOS的优势。

与其他功率MOSFET相比,LDMOS器件具有较低的电阻和较高的耐压能力,适合用于高频、高功率的射频应用。

同时,LDMOS器件的制造工艺成熟,成本相对较低,因此在市场上得到了广泛的应用。

总结。

LDMOS器件是一种常见的功率MOSFET,具有较低的电阻、较高的耐压能力和较高的频率特性。

其工作原理是通过在P型沟道和N型扩散层之间形成导通通道,实现信号的放大。

在射频和微波功率放大器中,LDMOS器件具有重要作用,广泛应用于无线通信、广播、雷达等领域。

通过本文的介绍,相信读者对LDMOS器件的工作原理有了更深入的理解,能够更好地应用于实际工程中。

射频LDMOS器件结构和ESD保护研究的开题报告

射频LDMOS器件结构和ESD保护研究的开题报告一、选题背景及研究意义射频LDMOS(Laterally-diffused Metal-Oxide-Semiconductor)器件是一种广泛应用于无线通信、卫星通信及高功率射频设备中的功率放大器器件。

由于其具有高频及高功率的特点,因此在通信领域应用广泛。

在实际应用中,射频LDMOS器件很容易被静电放电(ESD)所破坏,因此需要在器件设计中加入ESD保护措施,以保证其稳定工作和长寿命。

本文将重点研究射频LDMOS器件结构和ESD保护,旨在提高其稳定性和可靠性,在应用中发挥更加出色的性能。

二、研究内容1. 射频LDMOS器件结构研究介绍射频LDMOS器件的结构和工作原理,分析各个结构单元的参数,包括沟道长度、沟道深度、栅极长度等对器件性能的影响,同时对比分析各种结构对器件性能的影响,为器件的优化设计提供参考。

2. ESD保护研究研究射频LDMOS器件的ESD保护问题,分析器件面临的ESD危害,总结已有的保护措施,包括电路设计和器件结构等,并针对不同的应用场合提出不同的保护措施,提高器件的可靠性和稳定性。

三、研究方法及内容组织本文将采用文献调研、理论分析和实验研究相结合的方法,对射频LDMOS器件结构和ESD保护进行研究。

第一部分:绪论介绍选题背景、研究意义、研究现状和发展趋势。

第二部分:射频LDMOS器件结构研究介绍射频LDMOS器件的结构和工作原理,分析各个结构单元的参数,包括沟道长度、沟道深度、栅极长度等对器件性能的影响,同时对比分析各种结构对器件性能的影响,为器件的优化设计提供参考。

第三部分:ESD保护研究研究射频LDMOS器件的ESD保护问题,分析器件面临的ESD危害,总结已有的保护措施,包括电路设计和器件结构等,并针对不同的应用场合提出不同的保护措施,提高器件的可靠性和稳定性。

第四部分:实验研究选取常见的ESD保护方案对射频LDMOS器件进行保护实验研究,并对不同保护方案进行对比分析,为实际应用提供参考。

射频LDMOS的击穿电压与静电保护的开题报告

射频LDMOS的击穿电压与静电保护的开题报告一、选题背景射频LDMOS晶体管是一种广泛使用于无线通信和其他射频应用中的电子元件。

由于其高功率、高效率和低噪音等优点,它已成为当前射频技术中最重要的组成部分之一。

在使用LDMOS晶体管时,击穿电压和静电保护是需要考虑的重要问题。

二、研究目的本研究的目的是通过对射频LDMOS晶体管的击穿电压和静电保护进行研究,探究其特性和影响因素,为LDMOS晶体管在射频应用的设计和使用提供实用的指导和建议。

三、研究内容1. 对射频LDMOS晶体管的基本结构、工作原理和特性进行介绍。

2. 通过实验测试,探究射频LDMOS晶体管的击穿电压特性,分析电流和电压之间的关系,研究影响击穿电压的因素,如温度、功率等。

3. 分析射频LDMOS晶体管的静电保护方法,比较其优缺点和适用范围,并就不同情况下选择静电保护方法提出建议。

4. 结合实际应用需求,针对射频LDMOS晶体管进行性能测试和优化。

四、研究意义随着无线通信市场的快速发展,射频LDMOS晶体管已成为其中不可缺少的组成部分。

本研究可以对射频LDMOS晶体管的特性、击穿电压和静电保护进行深入研究,为相关产品的研发和生产提供基础数据和指导。

同时,通过对射频LDMOS晶体管的分析和优化,可以提高其性能和可靠性,为无线通信市场的发展做出贡献。

五、预期成果1. 对射频LDMOS晶体管的击穿电压和静电保护进行研究,掌握相关理论基础和实验方法。

2. 对射频LDMOS晶体管的特性进行分析,为实际应用提供有效的参考。

3. 研究并优化射频LDMOS晶体管的性能,提高其性能和可靠性。

4. 发表研究论文,为相关领域的发展提供贡献。

LDMOS器件在ESD保护中的应用

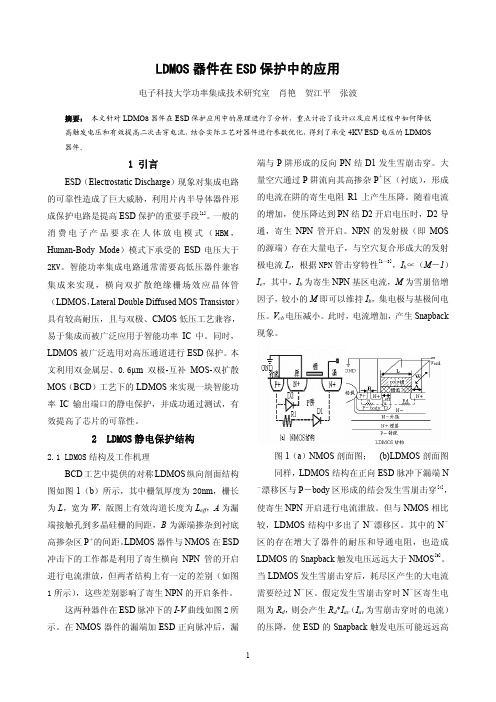

LDMOS器件在ESD保护中的应用电子科技大学功率集成技术研究室肖艳 贺江平 张波摘要: 本文针对LDMO S器件在ESD保护应用中的原理进行了分析,重点讨论了设计以及应用过程中如何降低高触发电压和有效提高二次击穿电流,结合实际工艺对器件进行参数优化,得到了承受4KV ESD电压的LDMOS 器件。

1 引言ESD(Electrostatic Discharge)现象对集成电路的可靠性造成了巨大威胁,利用片内半导体器件形成保护电路是提高ESD保护的重要手段[1]。

一般的消费电子产品要求在人体放电模式(HBM,Human-Body Mode)模式下承受的ESD电压大于2KV。

智能功率集成电路通常需要高低压器件兼容集成来实现,横向双扩散绝缘栅场效应晶体管(LDMOS,Lateral Double Diffused MOS Transistor)具有较高耐压,且与双极、CMOS低压工艺兼容,易于集成而被广泛应用于智能功率IC中。

同时,LDMOS被广泛选用对高压通道进行ESD保护。

本文利用双金属层、0.6µm 双极-互补MOS-双扩散MOS(BCD)工艺下的LDMOS来实现一块智能功率IC输出端口的静电保护,并成功通过测试,有效提高了芯片的可靠性。

2 LDMOS静电保护结构2.1 LDMOS结构及工作机理BCD工艺中提供的对称LDMOS纵向剖面结构图如图1(b)所示,其中栅氧厚度为20nm,栅长为L,宽为W,版图上有效沟道长度为L eff,A为漏端接触孔到多晶硅栅的间距,B为源端掺杂到衬底高掺杂区P+的间距。

LDMOS器件与NMOS在ESD 冲击下的工作都是利用了寄生横向NPN管的开启进行电流泄放,但两者结构上有一定的差别(如图1所示),这些差别影响了寄生NPN的开启条件。

这两种器件在ESD脉冲下的I-V曲线如图2所示。

在NMOS器件的漏端加ESD正向脉冲后,漏端与P阱形成的反向PN结D1发生雪崩击穿。

LDMOS介绍

现状

目前,LDMOS已经发展到比较成熟的阶段,国外各大公司都有多种LDMOS产品面世,满足从 300MHz~3GHz各个频段,各种功率的需求。 Motorola公司生产多种LDMOS产品。MRF282、284、286系列产品,在2GHz下对三个器件分别输 入0.5、2.4、4.75W的功率,各器件相应的峰值包络功率为10、30、60W。MRF1507是GSM基站用的 900MHz的LDMOS晶体管,是宽带通信和工业应用的一种低成本产品。MRF1507在520MHz下输出功 率为5W,增益为10dB,效率为63%,在7.5v直流供电便携式FM(频率调制)装置中用作UHF、VHF功率 放大器特别适合。目前,Motorola公司已经推出了针对GSM、EDGE、CDMA和W-CDMA基站放大器 应用的第六代LDMOS产品。第六代射频LDMOS技术的热性能也达到了业界领先。例如,125W(P1dB) 器件的热阻达到了0.4℃/w。正在开发的第七代LDMOS产品使用经济高效的超模压塑料封装和金属陶瓷 封装(采用飞思卡尔低热阻(Low Rth技术)来提高功率,降低成本。 Ericsson公司是生产LDMOS产品的主要厂商之一。相继研制出了工作于1.8-2.0GHz的增强型 LDMOS器件PTF10120和工作在2.1-2.17GHz的LDMOS器件PTF10134。PTFIO120型产品包含四个芯 片并安装推挽结构,输入输出端口设有内匹配电路。在1.8-2.0GHz的频率范围内,具有120W的峰值包 络功率,功率增益10.5dB。PTF10134是适用于PCS基站的金一金属化LDMOS晶体管。在2.110.5dB PTF10134 PCS LDMOS 2.12.17GHz的WCDMA中可提供100W的峰值包络功率,1dB压缩点的输出功率是110W。此外,Ericsson 公司推出了系列可以满足CDMA和WCDMA的线性和峰值功率需求的大功率LDMOS器件。它采用全金 金属化和氮化硅钝化层,使用周期长,可靠性高。 Philips公司推出了1030-l090MHz频率范围内输出功率200W,增益14dB,效率大于40%的LDMOS 产品。Philips公司生产的BLF0810一180LDMos晶体管用于CDMA蜂窝电话基站。与其他同类产品相比, 该技术使用更少数量的元件设计出封装尺寸更小、性能更高的晶体管。此外,这些晶体管采用双层金属 化和金线间连接技术,使得其平均无故障时间(MTBF)提高8一10倍。飞利浦已发展到第五代LDMOS, 生产的盯功率晶体管栅长只有0.4µm,四层金属镀膜,其推出的BLFSG22-100,增益达到17dB。 与国外大的半导体厂商相比,国内LDMOS研究起步较晚,加上现有工艺条件不是很成熟,与国外 差距较大,目前还处于探索研制阶段。仅有个别高校或研究机构针对LDMOS进行理论的研究和器件结 构上的调整,很少有真正立足于实现产品化而进行研究的。对于微波功率应用的LDMOS,中国电子科 技集团公司第十三研究所针对未来军事装备的需求进行了初步设计和研制,于2003年3月报道了采用 Mo栅工艺研制出的1GHz连续输出30W、增益11dB、漏极效率60%、IMD3为-30dB的LDMOS器件。 2005年5月报道了10Hz连续波输出60w、1oow的LDMOS器件,100W的LDMOS器件增益10.5dB,漏极 效率57.6%。国内其他研究机构鲜有器件性能报道。

LDMOS介绍

现状

目前,LDMOS已经发展到比较成熟的阶段,国外各大公司都有多种LDMOS产品面世,满足从 300MHz~3GHz各个频段,各种功率的需求。 Motorola公司生产多种LDMOS产品。MRF282、284、286系列产品,在2GHz下对三个器件分别输 入0.5、2.4、4.75W的功率,各器件相应的峰值包络功率为10、30、60W。MRF1507是GSM基站用的 900MHz的LDMOS晶体管,是宽带通信和工业应用的一种低成本产品。MRF1507在520MHz下输出功 率为5W,增益为10dB,效率为63%,在7.5v直流供电便携式FM(频率调制)装置中用作UHF、VHF功率 放大器特别适合。目前,Motorola公司已经推出了针对GSM、EDGE、CDMA和W-CDMA基站放大器 应用的第六代LDMOS产品。第六代射频LDMOS技术的热性能也达到了业界领先。例如,125W(P1dB) 器件的热阻达到了0.4℃/w。正在开发的第七代LDMOS产品使用经济高效的超模压塑料封装和金属陶瓷 封装(采用飞思卡尔低热阻(Low Rth技术)来提高功率,降低成本。 Ericsson公司是生产LDMOS产品的主要厂商之一。相继研制出了工作于1.8-2.0GHz的增强型 LDMOS器件PTF10120和工作在2.1-2.17GHz的LDMOS器件PTF10134。PTFIO120型产品包含四个芯 片并安装推挽结构,输入输出端口设有内匹配电路。在1.8-2.0GHz的频率范围内,具有120W的峰值包 络功率,功率增益10.5dB。PTF10134是适用于PCS基站的金一金属化LDMOS晶体管。在2.110.5dB PTF10134 PCS LDMOS 2.12.17GHz的WCDMA中可提供100W的峰值包络功率,1dB压缩点的输出功率是110W。此外,Ericsson 公司推出了系列可以满足CDMA和WCDMA的线性和峰值功率需求的大功率LDMOS器件。它采用全金 金属化和氮化硅钝化层,使用周期长,可靠性高。 Philips公司推出了1030-l090MHz频率范围内输出功率200W,增益14dB,效率大于40%的LDMOS 产品。Philips公司生产的BLF0810一180LDMos晶体管用于CDMA蜂窝电话基站。与其他同类产品相比, 该技术使用更少数量的元件设计出封装尺寸更小、性能更高的晶体管。此外,这些晶体管采用双层金属 化和金线间连接技术,使得其平均无故障时间(MTBF)提高8一10倍。飞利浦已发展到第五代LDMOS, 生产的盯功率晶体管栅长只有0.4µm,四层金属镀膜,其推出的BLFSG22-100,增益达到17dB。 与国外大的半导体厂商相比,国内LDMOS研究起步较晚,加上现有工艺条件不是很成熟,与国外 差距较大,目前还处于探索研制阶段。仅有个别高校或研究机构针对LDMOS进行理论的研究和器件结 构上的调整,很少有真正立足于实现产品化而进行研究的。对于微波功率应用的LDMOS,中国电子科 技集团公司第十三研究所针对未来军事装备的需求进行了初步设计和研制,于2003年3月报道了采用 Mo栅工艺研制出的1GHz连续输出30W、增益11dB、漏极效率60%、IMD3为-30dB的LDMOS器件。 2005年5月报道了10Hz连续波输出60w、1oow的LDMOS器件,100W的LDMOS器件增益10.5dB,漏极 效率57.6%。国内其他研究机构鲜有器件性能报道。

新型SCR-LDMOS输出端的静电放电保护结构

第30卷 第6期2007年12月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.6D ec.2007A N ovel SCR 2LDMOS ESD Pr otect ion Str uct ur e o f Fan 2outX I Yu ,L I De 2cha n g ,Q U Yue(School o f Technical P hysics ,Xi di an Univers it y ,Xi ’an 710071,Chi na)Abstract :We descri be a new ESD protection st ruct ure wit h em bedded SCR 2LDMO S ,by i nsert ing a P +dif 2f usion into t he drain regio n ,t hat device can be i mproved.We si mulat e t he breakdown characte r of t he de 2vice and analyze t he enhancement reason of enhancement of I t2.ISE si mul ation shows t hat t his st ruct urehave a good on 2st ate ,I t2and ESD (elect rost atic discha rge )endura nce vol tage are 8.5time s higher hi gher t han a conve ntional LDMO S ;off 2stat e di splay a higher BV D B and it can need to t he application.K ey w or ds :LDMOS ;SCR 2LDMOS ;ESD ;I t2EEACC :2315新型SCR 2LDMOS 输出端的静电放电保护结构习 毓,李德昌,曲 越(西安电子科技大学技术物理学院,西安710071)收稿日期2823作者简介习 毓(82),女,研究生,主要研究方向为半导体器件的结构设计和SD 保护,xy8@6摘 要:研究了一种新的具有ESD 自保护结构的SCR 2LDMOS ,它是通过在漏极加入P +扩散对传统LDMOS 结构的改进.模拟了器件的击穿特性并分析了二次电流I t2提高的原因.ISE 软件模拟结果表明:该结构具有良好的开启态,二次击穿电流和ESD 耐压是传统LDMOS 的8.5倍;关闭态有比较高的BV DB 可以满足使用的要求.关键词:LDMOS ;SCR 2LDMOS ;ESD ;二次电流I t2中图分类号:TN 432 文献标识码:A 文章编号:100529490(2007)0622104204 静电放电(ESD )是造成大多数电子元器件或电路系统破坏的主要原因.因此,电子器件必须加上ESD 保护,提供ESD 电流的泄放路经.LDMOS 在小功率IC 设计中被广泛用作输出级的驱动,由于尺寸较小使它的ESD 可靠性和提高ESD 能力一直都是强大的挑战.在MOSF ET 中用崩塌击穿来解释ESD 引起的失效.器件的击穿分为两种:第一雪崩击穿,雪崩击穿点定义为(V t1,I t1),对许多传统的MOSF ET 在第一雪崩击穿区就会使器件失效.第二崩塌击穿,崩塌击穿点定义为(V t2,I t2),它是由非均匀电流集中导致的大量的热引起的失效.因此对给定类型的LDMO S 有两种不同的失效模式,这与器件的栅宽和尺寸有关.对40V 2LDMOS ,当有异常大的ESD 脉冲时,LDMOS 可以工作在一次雪崩击穿后的大电流区,此时LDMOS 自身属于自保护器件,但是由于横向寄生npn 晶体管Q1在ESD 脉冲下有时很难开启,所以容易受ESD 脉冲的冲击而损坏.为提高ESD保护能力可采取多种方法如:漏加深结构[122]、槽栅结构[3]或采用钳位方案.漏加深结构有较好的ESD 能力,但各部分的掺杂浓度限制很严格,会给工艺带来相当的不便;把栅极埋到硅里的槽栅结构复杂;钳位法的静电保护能力不是很强.因此我们模拟了一种内嵌式的SCR 2LDMOS 结构,如图1(B ),即在漏极加一个P +区,使器件形成一个横向的np n 晶体管Q 1和一个纵向的pnp 晶体管Q 2,这两个晶体管可以组成一个pnpn 闸流管,当有ESD 冲击时,闸流管会迅速导通进入低阻抗的导通模式,给ESD 电流提供低阻抗的放电路径.SCR 2LDMOS [425]是对横向LDMOS 的改进结构,它有很强的ESD 能力,在开态同普通的LDMOS 一样的工作,在关态有较高的击穿电压BV D B 8:200700:197E 17112.co m..1 器件结构及等效电路图1是LDMOS 和SCR 2LDMOS 两种器件的结构和等效电路.图1(a)是R ESU RF LDMOS 的结构图,由图可知,该器件的漂移区为N 2drif t ,表面源极通过重掺杂的P +与衬底连通,沟道由双扩散形成,该结构有一个横向寄生np n 晶体管Q 1.图1(b)是SCR 2L DMOS 的结构图,两个结构的不同之处为在漏极N +区引入P +区,这个结构有两个寄生晶体管(横向npn 晶体管Q 1及纵向p np 晶体管Q 2),这样就会产生由Q 1和Q 2构成的寄生p np n 闸流管.两个器件的尺寸完全相同.(a)LDMOS(b )SCR 2LDMOS图1 LDMOS 和SCR 2LDMOS 结构1 LDMOS 的T LP 测量[6]I 2V 特性曲线一般LDMOS 的栅氧化层的击穿我们采用钳位二极管来保护,这里只讨论ESD 电流对漏极的影响.图2中,B VDB 是漏极雪崩击穿电压;V t1是Snapback 的触发电压;I t1是在V t1点的漏极电流;V h old 是维持寄生晶体管导通的电压,即崩塌时电压的最小值;I hold 是在V ho ld 点对应的电流;V t2是二次击穿的漏极电压;I t2是在V t2点的漏极电流;ΔV snap 是Snapback 过程中的电压降;I t1.ii 是碰撞电离产生的空穴驱动电流;I mo s.sat 是LDMO S 的饱和电流;I B.t1是触发点的有效体电阻;R of f 是BJ T 触发的漏源电阻;R on 是BJ T 触发后的漏源电阻.由上图可以看出:ΔV =I (R B +R ff )()ΔV =V BV D B()I =I I (3)图2 典型的Snap back I 2V 特性曲线由图2和等式(3)可知,随着栅偏压的增大,LDMOS 的饱和电流I mos.sat 在增加,所以碰撞电离产生的空穴驱动电流I t1.ii 减小,因此触发电压就会变小.下面只讨论零偏时LDMOS 的特性曲线.由上图可以看出,二次电流越大器件所能承受的ESD 电压越高.LDMO S 的击穿机理如下:在ESD 脉冲加到LDMOS 的漏极上时,漂移区和沟道区的结反偏,器件进入高阻抗的状态,直到达到击穿时为止.由于此过程是高场,在耗尽区产生电子、空穴对,电子被漏接触电极所收集,空穴流入衬底.这样,相对于接地的源,p 型沟道区的局部电势不断的增加.当局部的电势增加到足以使源沟道结正偏的情况下.电子就从源区注入到了漏区.在此过程中,漏极相当于集电极,衬底和沟道区相当于基极,源极相当于发射极.以普通LDMOS 为例(参看图3):普通LDMOS 有一个寄生npn 晶体管Q 1,当P -和源极的N +正偏且达到npn 晶体管的开启电压时,该npn 晶体管触发导通.此时源极是发射极,P -是基区,漏极则是集电极.器件正常工作时在A 点开始雪崩击穿;当有静电加到保护结构的漏极,寄生横向BJ T 在漏衬结雪崩击穿后很快在B 点开启,之后寄生BJ T 可以自己提供所需的基极电流,保持自偏置导通状态,基极电流不再需要漏端雪崩倍增产生,而是由工作在放大区的晶体管提供,这样原先漏衬结的大电压突然减小,电压降至接近寄生晶体管的集电极2发射极导通电压C 点,即保护结构的保持电压.C 点与D 点之间为BJ T 的Snapback 区,即ESD 保护的崩塌区.如果在此期间ESD 电流不能被有效泄放,则电流会集中而产生局部热点,当达到硅的熔点,会因为热而烧毁器件,即到达D 点器件的二次击穿点之后,器件就会失效.SCR 2LDMOS 的击穿机理与普通LDMO S 相似由图3和图模拟结果可以看出在崩塌区,电压变化只有约55V ,而温度却由3K 迅速上升到5K ,变化量为K;在雪崩击穿区,电压变5012第6期习 毓,李德昌等:新型SCR 2LDMOS 静电放电保护结构8t 1.ii .t 1o 1t ri gg t 1-2t 1.ii t 1-mo s.sa t.4:.701701200图3 LDMOS 的电热模拟I 2V 特性化约为36V 而温度的变化只有70K 左右.因此可以认为器件的损坏确实是由二次击穿电流I t2引起的局部热击穿.3 二维器件模拟与分析本文采用二维器件模拟软件ISE ,对内嵌pnp n 结构的SC R 2LDMOS 进行模拟,主要对器件的二次击穿电流I t2[7]进行相应的分析和比较.结果显示SC R 2LDMOS 的二次电流比普通L DMOS 提高了8.5倍,击穿电压有所退化但满足使用要求.2.1 模拟结果图4是SCR 2LDMOS 漏极电压、漏极电流和器件温度之间的变化曲线.与图3的击穿机理相同,SCR 2LDMOS 在A 点雪崩击穿;在B 点寄生pnpn 闸流管或npn 双极晶体管开启;在C 点到达保护结构的保持电压;在D 点器件二次击穿.由模拟结果可知:图4的C 点二次电流I t2=3×10-2A/μm ,二次击穿电压V t2=11V ,二次击穿点的结温T =1570K;击穿电压BV D B=39V ;图3的C 点二次电流I t2=4×10-3A/μm ,二次击穿电压V t2=26V ,二次击穿点的结温T =1550K;击穿电压BV D B =58V.图4 SCR 2LDMOS 电热模拟I 2V 特性曲线SCR 2LDMO S 的I t2=3×10-2A/μm ,体电模型的电阻为1.5k Ω,可以估算出器件的ESD 耐压为5V μ;同样LDMOS 的I =×3μ,SD 耐压为6V μ比较可知,因为二次击穿电流的提高,S R 2LDMOS 的SD 能力提高了85倍,虽然击穿电压有所退化,但满足使用要求.如果需要提高击穿电压,则可以通过降低衬底掺杂浓度或增加漂移区的长度实现.3.2 二次电流分析二次电流可由下式计算:I t2=4πλ(T C -T 0)V t2lnt fτth+2-V DL D(4)其中,λ是硅的热传导系数;t f 是失效时间;W D 是耗尽层的厚度;L D 是耗尽层的长度;T C 是器件失效的临界温度;T 0是环境温度(300K );t h 是沿L D 方向建立热平衡的时间;t h 与L D 有关,可由下式计算τth =L D 2ρC p4πλ(5)这里,ρ是硅的质量密度;C P 是硅的比热.比较两种结构可以看出:SCR 2LDMOS 的二次电流比普通LDMOS 的二次电流提高了大约一个数量级,二次击穿电压降低了15,T C 2T 0升高了22K ,耗尽层宽度增加了1μm.由(4)式可以看出:I t2与T C 2T 0成正比、与V t2成反比,在L D 不变的情况下随W D 的增加而增加.因此可以得出结论:在漏极N +区引入P +扩散的SCR 2LDMOS 结构大大的提高了二次电流,从而提高了器件的ESD 能力.3.3 电子电流密度分布从图5中我们可以观察到崩塌区的电子电流密(a )LDMOS(b )SCR 2LDMOS图5 电子电流密度分布度,密度最大的地方是漏极N +区.比较可知SCR 2LDMOS 的电流有一部分通过漏极的+区进入衬底电流线的分布还表明,S R 2LDMOS 的纵向寄生晶体管Q 打开后会给衬底注入一部分空6012电 子 器 件第30卷84/m t 2410-A/m E /m.C E .P .C p np 2穴,使横向寄生npn 晶体管Q 1比较容易开启;而LDMOS 只有雪崩击穿电流才能注入到衬底而产生衬底电动势,使衬底和源极正偏后才能打开横向的寄生npn 晶体管,但这个晶体管比较难打开.结论:SC R 2LDMO S 提高了横向np n 晶体管的开启,从而使寄生pnpn 闸流管迅速进入低阻抗的导通模式,使ESD 电流迅速泄放.从而使SCR 2LDMOS 即使在受外界较大的静电脉冲冲击时也不会失效,提高了器件的可靠性.3.4 电场分布从图6两种结构的电场分布可知,LDMOS 最大电场集中在漏极的N +上,因此电流不能均匀的分布在N 2drift 漂移区,器件的击穿发生在漏极;而SC R 2LDMOS 电场分布比较均匀的分布在N 2drift 区,减小了电流集中效应,使漏极不会因为电流太大而损坏器件.(a)LDMOS(b )SCR 2LDMOS图6 LDMOS 和SCR 2LDMOS 电场分布4 结论内嵌pnpn 闸流管的SCR 2LDMOS 已成功地设计出来,模拟显示该结构改善了器件的ES D 特性.由于漏极P +区的加入,可使漏极附近电场减小、电流均匀地分布在整个漂移区,从而减小了电流的集中现象,提高了二次电流.在满足使用要求的情况下,由于二次电流的提高使其ESD 能力比普通LDMOS 提高了约8.5倍,从而提高了器件的ESD 能力.参考文献:[1] Vijay Part hasarat hy ,Vis hnu Khemka ,Ro nghua Zhu ,J am esWhi tfiel d ,Am i tava B o se ,and Richar d Ida.A Double R E 2SU R F LDMOS wit h Drai n Profil e Engineering for Impro ved ESD Robus tnes s.IEEE Elect ron Device Let t ers ,Ap ril ,2002,23(NO.4):2122214.[2] Vijay Part hasarat hy ,Vis hnu Khemka ,Ro nghua Zhu ,J am esWhi tfiel d ,Am i tava B o se ,and Richar d Ida.A Double R E 2SU R F LDMOS Wit h Drai n Profile Engi neeri ng fo r Impro ved ESD Robus tnes s.IEEE Elect ron Device Let t ers ,Ap ril ,2002,23(4):2122214.[3] Nao hiro Suzuki ,Hito shi Yamag uchi and Satos hi Shiraki.Break 2Through of t he Trade 2off Bet ween o n 2Resist ance and ESD Endurance in LDMOS[C ]//IEE E Proceedi ngs of t he 17#Internatio nalSymposi umonPowerSem ico nduct orDevi ces &IC ’s ,S ant a Barbara ,CA ,pp23226,May ,2005.[4] Lee J ian 2Hsi ng ,Shih J R ,Tang C S ,Liu K C ,Wu Y H ,Shi ue RY ,Ong T C ,l ’eng Y K and Yue J T.No vel ESD Pro tect ion St ruct ure wit h Embedded SCR LDMOS for Smart PowerTech 2nology[C ]//IEE E02C H373320.40t hAnnual lnt emat ional R e 2l iabi lit y Phys i cs Sy m po s i um ,Dall as ,Texas ,2002,1562161.[5] Pend har kar Sam eer ,Teggat z Ros s.Devore J oe ,C arpent erJ oh n ,Efland Taylor ,Tsai Chi n 2yu ,SCR 2L DMOS ∃A No vel LDMOS Device wi t h ESD Rob ust ness [C ]//IE EE ISPSD ’2000.May 22225.To ul ouse.France ,3412344.[6] Mar kus Mergens ,W il keni ng W olfgang ,Met t ler St ep han ,WolfHein rich ,St ricker And reas ,Fi cht ner Wolfgang .Anal ysis and Compact Modeling of L at eral DMOS P o wer Devi ces U nderESD St ress C o nditio ns[C ]//IE EEEOS/ESDSYMPOSIU M :129,9921.[7] Chung Y o ung ,Xu Ho ng zho ng ,Ida Richard ,Bai rd B o b.Snap 2back B reakdown Dynamics and ES D Suscept ibilit y of L DMOS [C ]//IE EE 06C H3772844t h Ann ual Internatio nal Reliabilit y Physics Symposiu m ,San Jo se ,3522355,2006.7012第6期习 毓,李德昌等:新型SCR 2LDMOS 静电放电保护结构8。

LDMOS器件静电放电失效原理

LDMOS器件静电放电失效原理随着集成度的提高及器件特征尺寸的减小,如何确保器件的可靠性已变得越来越重要。

据统计,在相关的半导体集成电路的失效因素中,电过应力(EOS)和静电放电(ESD)损伤约占40%的比例。

原因是静电放电和电过应力带来的高电场或瞬间大电流会令器件局部过热,引起介质层击穿、多晶Sj或金属连线烧毁、钝化层破坏和pn结乃至器件的二次热击穿、甚至熔化Si片管芯等问题.LDMOS器件作为功率输出级器件,其静电放电防护能力是其可靠性的重要指标之一,抗静电击穿能力已经成为器件设计的关键。

本文首先探讨了LDMOS器件在静电放电脉冲作用下的失效机理,阐述了LDMOS 在快速静电放电脉冲作用下的电流集中和器件局部温度过高导致的金属接触孔熔融等现象以及静电放电脉冲过后的器件性能退化乃至烧毁的问题。

之后通过对不同器件结构LDMOS的静电放电防护性能的分析对比,指出带埋层的深漏极注入双RESURF结构LDMOS器件在静电防护方面的优势。

1 静电放电脉冲作用下的LDMOS 器件失效1.1 LDMOS器件的静电放电及其损伤的原理 LDMOS器件作为输出驱动器件,尺寸较大,当寄生npn管完全导通时可以承受较大的静电放电电流,因此与常规MOS器件相比具备一定的自保护能力,标准CMOS工艺下的LDMOS器件典型结构如图l所示。

图2为LDMOS器件在静电放电脉冲下的,-V特性曲线,当正向静电放电脉冲来临,漏源电压达到寄生npn晶体管导通所需的触发电压Vn.,时,n型外延层/p阱形成的pn结将发生雪崩击穿,碰撞电离产生的空穴电流会使p阱和源之间的pn结正偏,寄生npn管导通,电子从源极发射进入阱区。

这些电子在源漏电场的作用下加速,使得载流子碰撞电离概率增加,从而形成更多的电子空穴对,漏源电流逐渐增大。

当其超过维持电流时,器件将进入寄生npn管完全导通的大电流工作区,此时LDMOS器件将吸收大量的静电放电脉冲电流[5]。

LDMOS横纵向电场同时优化及关键技术

LDMOS横纵向电场同时优化及关键技术LDMOS横纵向电场同时优化及关键技术LDMOS(Laterally Diffused Metal Oxide Semiconductor)是一种常用于功率放大器的半导体器件。

它具有高电压处理能力和低电流漏泄的特点,广泛应用于射频功率放大、调制、天线开关等领域。

然而,LDMOS器件在工作过程中还存在一些问题,如电场集中、漏电流增加等。

为了优化LDMOS器件的工作性能,需要同时优化横向和纵向电场分布。

横向电场集中导致电导丧失,纵向电场集中会导致漏电流增加。

因此,要同时优化这两者是非常重要的。

在优化LDMOS器件的横向电场分布时,可以采用多种方法。

一种方法是通过改变多晶硅的浓度分布来调整电场分布。

这可以通过在表面引入P型离子来完成,从而降低表面电导率,减少横向电流。

另一种方法是在晶体管的表面加上掺杂剂层,形成渐变掺杂电场,使电场均匀分布。

对于纵向电场的优化,常用的方法是采用隔离结构和结阻控技术。

隔离结构可以将漏电流限制在所需的范围内,减少电场集中。

结阻控技术包括增加漏结电阻和优化源漏结电容,以降低漏电流的影响。

除了以上的优化方法,还有一些关键技术可以提高LDMOS器件的性能。

一种关键技术是缩小LDMOS器件的结构尺寸。

通过缩小尺寸,可以提高器件的开关速度和功耗。

另一个关键技术是改善接触电阻。

接触电阻会导致能量损失和热耗散,所以改善接触电阻对于提高LDMOS器件的效率非常重要。

此外,制造工艺的改进也是提高LDMOS器件性能的关键。

对于LDMOS器件来说,源漏电极和栅极之间的电极距离、掺杂浓度和材料选择等都会影响器件的性能。

因此,优化这些工艺参数对于提高LDMOS器件的性能非常重要。

综上所述,LDMOS横纵向电场的同时优化是提高器件性能的关键。

通过采用适当的技术和工艺,我们可以有效地改善LDMOS器件的横向和纵向电场分布,并提高器件的电导能力和降低漏电流。

在继续深入研究中,我们可以进一步探索新的方法和技术,以进一步提高LDMOS器件的性能和应用综合以上所述,采用隔离结构和结阻控技术是优化LDMOS 器件纵向电场分布的常用方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LDMOS器件在ESD保护中的应用电子科技大学功率集成技术研究室肖艳 贺江平 张波摘要: 本文针对LDMO S器件在ESD保护应用中的原理进行了分析,重点讨论了设计以及应用过程中如何降低高触发电压和有效提高二次击穿电流,结合实际工艺对器件进行参数优化,得到了承受4KV ESD电压的LDMOS 器件。

1 引言ESD(Electrostatic Discharge)现象对集成电路的可靠性造成了巨大威胁,利用片内半导体器件形成保护电路是提高ESD保护的重要手段[1]。

一般的消费电子产品要求在人体放电模式(HBM,Human-Body Mode)模式下承受的ESD电压大于2KV。

智能功率集成电路通常需要高低压器件兼容集成来实现,横向双扩散绝缘栅场效应晶体管(LDMOS,Lateral Double Diffused MOS Transistor)具有较高耐压,且与双极、CMOS低压工艺兼容,易于集成而被广泛应用于智能功率IC中。

同时,LDMOS被广泛选用对高压通道进行ESD保护。

本文利用双金属层、0.6µm 双极-互补MOS-双扩散MOS(BCD)工艺下的LDMOS来实现一块智能功率IC输出端口的静电保护,并成功通过测试,有效提高了芯片的可靠性。

2 LDMOS静电保护结构2.1 LDMOS结构及工作机理BCD工艺中提供的对称LDMOS纵向剖面结构图如图1(b)所示,其中栅氧厚度为20nm,栅长为L,宽为W,版图上有效沟道长度为L eff,A为漏端接触孔到多晶硅栅的间距,B为源端掺杂到衬底高掺杂区P+的间距。

LDMOS器件与NMOS在ESD 冲击下的工作都是利用了寄生横向NPN管的开启进行电流泄放,但两者结构上有一定的差别(如图1所示),这些差别影响了寄生NPN的开启条件。

这两种器件在ESD脉冲下的I-V曲线如图2所示。

在NMOS器件的漏端加ESD正向脉冲后,漏端与P阱形成的反向PN结D1发生雪崩击穿。

大量空穴通过P阱流向其高掺杂P+区(衬底),形成的电流在阱的寄生电阻R1上产生压降。

随着电流的增加,使压降达到PN结D2开启电压时,D2导通,寄生NPN管开启。

NPN的发射极(即MOS 的源端)存在大量电子,与空穴复合形成大的发射极电流I e,根据NPN管击穿特性[1~3],I b∝(M-1)I e,其中,I b为寄生NPN基区电流,M为雪崩倍增因子,较小的M即可以维持I b,集电极与基极间电压。

V cb电压减小。

此时,电流增加,产生Snapback现象。

图1(a)NMOS剖面图; (b)LDMOS剖面图 同样,LDMOS结构在正向ESD脉冲下漏端N -漂移区与P-body区形成的结会发生雪崩击穿[4],使寄生NPN开启进行电流泄放。

但与NMOS相比较,LDMOS结构中多出了N-漂移区。

其中的N-区的存在增大了器件的耐压和导通电阻,也造成LDMOS的Snapback触发电压远远大于NMOS[5]。

当LDMOS发生雪崩击穿后,耗尽区产生的大电流需要经过N-区。

假定发生雪崩击穿时N-区寄生电阻为R d,则会产生R d*I av(I av为雪崩击穿时的电流)的压降,使ESD的Snapback触发电压可能远远高于击穿电压,这样一来,就会出现输出级静电保护失效。

图2 LDMOS 在ESD 脉冲下工作时I -V 曲线图I t2(二次击穿电流)是LDMOS 在ESD 条件下工作的一个重要参数,HBM 模式下测量的器件能够承受的ESD 电压可以用I t2估算:V ESD =I t2×1500其中1500为HBM 模式模型中等效人体电阻,单位:OhmLDMOS 同NMOS 一样,其I t2与M 、β(寄生NPN 的电流放大系数)和衬底寄生电阻R sub 有关[6]。

除此之外,I t2的大小还与N -区到漏N +的间距有关[7],所以用LDMOS 作为ESD 器件时,需要做更多的考虑。

2.2 等效保护电路在IC 正常工作条件下,LDMOS 处于关断状态,不影响IC 电路正常的输出,保护电路等效为图3所示。

图3 ESD 保护电路图每个端口ESD 保护都需要有正负两个通道。

当加正向ESD 脉冲时,依上述的工作机理,寄生NPN 管开启泄放电流。

当加负脉冲时,漏端与P -body 区形成的二极管D 开启,进行电流泻放,电流泄放通道如图3虚线所示。

2.3 应用过程中重要参数设置及物理实现:利用LDMOS 结构实现ESD 保护时,要降低触发电压,提高I t2电流,就需要在物理实现过程中适当进行参数选取。

当然,这对器件的Layout 也提出了一定的要求。

2.3.1 物理实现的重要参数根据现有的工艺条件,需要借助以上分析,对以下重要参数进行适当选取:1) 有效沟道长度L eff (如图1中(b )影响到寄生NPN 的β值。

当增大L eff 时,β减小,I t2值会降低,且会增大寄生电阻R 。

增大R 虽有利于减小触发电压,但不利于反向ESD 脉冲下电流的泄放;L eff 过小还会影响到LDMOS 的耐压,需要折中考虑这些影响。

2) N -区长度L N_:如图1中(b)即为L N_=L -L eff ;这个参数直接影响到寄生电阻R d 。

在保证击穿电压的情况下,尽量减小L N -。

这样可以减小Snapback 触发电压,且可以避免雪崩击穿后耗尽层中的电子在达到N +区前达到饱和速度而使其承受的ESD 电压减小[7],也有利于器件泄放反向通道的ESD 电荷。

3) 漏端接触孔到多晶硅栅的间距A :一方面,雪崩击穿发生在沟道与漏端交界处,形成的高电场和大电流会产生较高的热量,若接触孔与多晶硅栅间距不够大,则产生的热量会使接触孔被烧毁,造成ESD 保护失败。

再者,物理实现一般采用插指结构,插指结构可能会造成电流集中,导致ESD 保护失败。

拉长漏端宽度形成了镇流电阻,能够改善这种现象。

准确地说,在LDMOS 结构中,这个间距应该是漏端接触孔到P -body 的间距。

4) 源端掺杂到衬底高掺杂区P +的间距B :这个参数决定了寄生电阻R 的大小,当雪崩电流一定时,R 越大,P-body 与源形成的PN 结开启越容易。

以上参数讨论是要保证不改变此工艺的情况下LDMOS 结构的击穿电压。

针对这些参数,借助版图进行优化来实现有效的保护,版图如图4所示。

图4 LDMOS 的布局2.3.2 版图优化:为了减小Snapback 的触发电压,从两个方面进行版图优化:(1)适当增加B 值以增大寄生电阻R ;(2)适当减小L N_值以减小寄生电阻R d 。

同时,不改变Bv ,适当减小了L eff 大小,以提高β值。

漏端用上层金属M 2覆盖包括多晶栅的区域,此举使连接源和衬底端的M 1(底层金属)与M 2形成一定的电容,有利于抑制噪声信号对IC 的干扰。

采用插指结构,在电流易集中的地方,如多晶硅栅拐角以及结的拐角处,进行了拐角处理。

图5 不同参数下LDMOS 的击穿I -V 测试曲线3 测试结果流片后,通过测试证明优化出的LDMOS 器件的Snapback 触发电压为18V ~19V ,根据HBM 测试报告,得到的LDMOS 器件能够承受的ESD 电压为4KV ,达到了设计要求。

击穿I -V 测试曲线如图5所示。

当N -漂移区间距越大,Snapback 触发电压是增大的,不利于ESD 电流泄放。

而随着源端掺杂到衬底高掺杂区P +间距B 的减小,寄生电阻R 减小,需要更大的触发电流来保证寄生NPN 管的开启,增大间距B 就要求更大的面积,测试图上B =1.5μm 的器件所占尺寸为36.1μm×84.5μm ,而B =0μm 的器件所占面积为32.2μm×84.5μm ,减小了10.8%。

4 结论本文利用LDMOS 的高击穿电压特性,将其应用于功率集成电路的ESD 防护。

通过对LDMOS 击穿特性的物理分析,结合具体工艺要求设计了ESD 防护结构;测试结果表明LDMOS 器件可以有效防护ESD 对功率集成电路的破坏。

参 考 文 献[1] A.Z.Wang, H.G .Feng, K. Gong, R.Y .Zhan,J.Stine.On-chip ESD protection design for integrated circuit: an overview for IC design. Microelectronics Journal, 2001; 32(2001)733-747[2] R.W. Dutton. Bipolar transistor modeling of avalanchegeneration for computer circuit simulation. IEEE Trans. Elec. Dev., 1975; ED-22: p.334-338[3] 陈星弼,唐茂成. 晶体管原理. 电子科技大学出版社,1991,p.133-154.[4] 陈星弼. 功率MOSFET 与高压集成电路. 电子工业出版社, 1989, 225-315.[5] M.Mergens, W.Wilkenning, S.Mettler, H.Wolf,etc.Analysis of lateral DMOS power devices under ESD stress condition. IEEE Trans. Electron Devices, 2000;vol.47,:p.2128-2137.[6] Ajith Amerasekera , Charvaka Duvvury. ESD in siliconintegrated circuit. By JOHN WILEY & SONS, INC chapter 4.[7] Kazunori Kawamoto, Shigeki Takahashi, Seji Fujino, etc.A No-snapback LDMOSFET With Automotive ESDendurance. IEEE Tran. Electron Devices, 2002; V ol.49, No.11: p.2047-2052.作者简介肖艳,在读硕士研究生,主要从事功率集成电路静电保护设计与研究。