sa_mar12_f6_iht

Lenovo Storage D1224 Drive Enclosure for SAP HANA

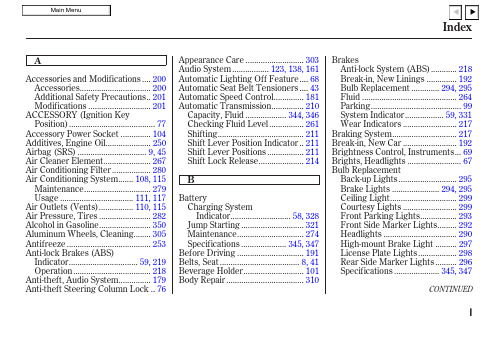

Lenovo Storage D1224 Drive Enclosure for SAP HANA Product GuideLenovo Storage D1224 Drive Enclosure models for SAP HANA provide additional required disk storage capacity for certain SAP HANA X6 systems with large memory configurations. They are designed specifically for SAP HANA certified appliance requirements and are supported on SAP HANA X6 systems. The D1224 for SAP HANA is a 2U rack-mount enclosure that has 24 SFF hot-swap drive bays and is attached to SAP HANA X6 systems via the ServeRAID M5225 RAID adapter. All D1224 models for SAP HANA contain single Environmental Service Module (ESM) with 3x 12 Gbps SAS x4 ports for direct-attach host connectivity.The D1224 for SAP HANA is shown in the following figure.Figure 1. Lenovo Storage D1224 Disk Expansion Enclosure for SAP HANADid you know?The D1224 expansion enclosures for SAP HANA offer flexible hybrid storage configurations with enterprise SAS hard disk drives (HDDs) and high performance SAS solid-state drives (SSDs).The D1224 expansion units for SAP HANA support 12 Gbps SAS connectivity, which doubles the data transfer rate compared to 6 Gb SAS solutions to maximize performance of storage I/O-intensive applications.Click here to check for updatesFigure 2. Front view of the D1224 drive enclosure for SAP HANAFigure 3. Rear view of the D1224 drive enclosure for SAP HANANote: The ESM (shown in Figure 4) has additional service ports with a specialized connector, and these ports are reserved for use by a Lenovo service technician.System specificationsThe following table lists the D1224 for SAP HANA system specifications.Table 1. System specificationsAttribute SpecificationDrivesThe following table lists drive options for the D1224 drive enclosure for SAP HANA. Table 4. SFF drive optionsDescription Part number FeaturecodeMaximumquantity perone D12242.5-inch SAS hot-swap HDDsLenovo Storage 300GB 15K 2.5" SAS HDD01DC197AU1J24 Lenovo Storage 600GB 10K 2.5" SAS HDD01DC427AU1Q24 Lenovo Storage 600GB 15K 2.5" SAS HDD01DC192AU1H24 Lenovo Storage 900GB 10K 2.5" SAS HDD01DC417AU1N24 Lenovo Storage 900GB 15K 2.5" SAS HDD01KP040AVP524 Lenovo Storage 1.2TB 10K 2.5" SAS HDD01DC407AU1L24 Lenovo Storage 1.8TB 10K 2.5" SAS HDD01DC402AU1K24 Lenovo Storage 2.4TB 10K 2.5" SAS HDD4XB7A09101B10324 2.5-inch NL SAS hot-swap HDDsLenovo Storage 1TB 7.2K 2.5" NL-SAS HDD01DC442AU1S24 Lenovo Storage 2TB 7.2K 2.5" NL-SAS HDD01DC437AU1R24 2.5-inch SAS hot-swap SED HDDsLenovo Storage 1.2TB 10K 2.5" SAS HDD (SED)01DC412AU1M24 2.5-inch SAS hot-swap SSDs (10 DWD)Lenovo Storage 400GB 10DWD 2.5" SAS SSD01DC462AUDK24 Lenovo Storage 800GB 10DWD 2.5" SAS SSD01DC452AUDH24 Lenovo Storage 1.6TB 10DWD 2.5" SAS SSD01DC447AUDG24 2.5-inch SAS hot-swap SSDs (3 DWD)Lenovo Storage 400GB 3 DWD 2.5" SAS SSD01DC482AU1V24 Lenovo Storage 800GB 3DWD 2.5" SAS SSD01DC477AU1U24 Lenovo Storage 1.6TB 3DWD 2.5" SAS SSD01DC472AU1T24 2.5-inch SAS hot-swap SSDs (1 DWD)Lenovo Storage 3.84TB 1DWD 2.5" SAS SSD (1200.2)01CX632AV2F24 Lenovo Storage 3.84TB 1DWD 2.5" SAS SSD (PM1633a)01KP065AVPA24 Lenovo Storage 7.68TB 1DWD 2.5" SAS SSD01KP060AVP924 Lenovo Storage 15.36TB 1DWD 2.5" SAS SSD4XB7A08817B10424 2.5-inch SAS hot-swap SED SSDs (10 DWD)Lenovo Storage 800GB 10DWD 2.5" SAS SSD (SED)01DC457AUDJ24 Power cablesPower cablesThe D1224 for SAP HANA ships standard with two 1.5m, 10A/100-250V, C13 to IEC 320-C14 rack power cables. Other power cable options are also available, and the part numbers and feature codes to order the power cables are listed in the following table (two power cables are required per each D1224 for SAP HANA).Table 5. Power cable optionsDescription PartnumberFeaturecodeRack power cables1.2m, 10A/100-250V, 2 Short C13s to Short C14 Rack Power Cable47C2487A3SS 1.2m, 16A/100-250V, 2 Short C13s to Short C20 Rack Power Cable47C2491A3SW1.5m, 10A/100-250V, C13 to IEC 320-C14 Rack Power Cable39Y793762012.5m, 10A/100-250V, 2 Long C13s to Short C14 Rack Power Cable47C2488A3ST 2.5m, 16A/100-250V, 2 Long C13s to Short C20 Rack Power Cable47C2492A3SX 2.8m, 10A/100-250V, 2 Short C13s to Long C14 Rack Power Cable47C2489A3SU 2.8m, 10A/100-250V, C13 to IEC 320-C14 Rack Power Cable None*6311 2.8m, 10A/100-250V, C13 to IEC 320-C20 Rack Power Cable39Y79386204 2.8m, 16A/100-250V, 2 Short C13s to Long C20 Rack Power Cable47C2493A3SY 4.1m, 10A/100-250V, 2 Long C13s to Long C14 Rack Power Cable47C2490A3SV 4.1m, 16A/100-250V, 2 Long C13s to Long C20 Rack Power Cable47C2494A3SZ 4.3m, 10A/100-250V, C13 to IEC 320-C14 Rack Power Cable39Y79326263 Line cords10A/125V C13 to NEMA 5-15P 4.3m line cord39Y79316207 10A/250V C13 to NEMA 6-15P 2.8m line cord46M2592A1RF Argentina 10A/250V C13 to IRAM 2073 2.8m line cord39Y79306222 Australia/NZ 10A/250V C13 to AS/NZ 3112 2.8m line cord39Y79246211 Brazil 10A/250V C13 to NBR 14136 2.8m line cord69Y19886532 China 10A/250V C13 to GB 2099.1 2.8m line cord39Y79286210 Denmark 10A/250V C13 to DK2-5a 2.8m line cord39Y79186213 European 10A/230V C13 to CEE7-VII 2.8m line cord39Y79176212 India 10A/250V C13 to IS 6538 2.8m line cord39Y79276269 Israel 10A/250V C13 to SI 32 2.8m line cord39Y79206218 Italy 10A/250V C13 to CEI 23-16 2.8m line cord39Y79216217 Japan 12A/125V C13 to JIS C-8303 2.8m line cord46M2593A1RE Korea 12A/250V C13 to KETI 2.8m line cord39Y79256219 South Africa 10A/250V C13 to SABS 164 2.8m line cord39Y79226214 Switzerland 10A/250V C13 to SEV 1011-S24507 2.8m line cord39Y79196216 Taiwan 15A/125V C13/CNS 10917 2.8m line cord00CG2676402 United Kingdom 10A/250V C13 to BS 1363/A 2.8m line cord39Y79236215Physical specificationsInteroperabilityLenovo provides end-to-end storage compatibility testing to deliver interoperability throughout the network. For end-to-end storage configuration support, refer to the Lenovo Storage Interoperation Center (LSIC): https:///us/en/lsicUse the LSIC to select the known components of your configuration and then get a list all other supported combinations, with details about supported hardware, firmware, operating systems, and drivers, plus any additional configuration notes. View results on screen or export them to Excel.Rack cabinetsThe following table lists the supported rack cabinets.Table 7. Rack cabinetsPart number Description93072RX25U Standard Rack (1000mm)93072PX25U Static S2 Standard Rack (1000mm)7D6DA007WW ThinkSystem 42U Onyx Primary Heavy Duty Rack Cabinet (1200mm)7D6DA008WW ThinkSystem 42U Pearl Primary Heavy Duty Rack Cabinet (1200mm)93604PX42U 1200mm Deep Dynamic Rack93614PX42U 1200mm Deep Static Rack93634PX42U 1100mm Dynamic Rack93634EX42U 1100mm Dynamic Expansion Rack93074RX42U Standard Rack (1000mm)7D6EA009WW ThinkSystem 48U Onyx Primary Heavy Duty Rack Cabinet (1200mm)7D6EA00AWW ThinkSystem 48U Pearl Primary Heavy Duty Rack Cabinet (1200mm)For specifications about these racks, see the Lenovo Rack Cabinet Reference, available from:https:///lp1287-lenovo-rack-cabinet-referenceFor more information, see the list of Product Guides in the Rack cabinets category:https:///servers/options/racksPower distribution unitsThe following table lists the power distribution units (PDUs) that are offered by Lenovo.Table 8. Power distribution unitsPart number Feature code Description 0U Basic PDUs00YJ776ATZY 0U 36 C13/6 C19 24A 1 Phase PDU N Y Y N N N N N N Y Y Y N 00YJ777ATZZ 0U 36 C13/6 C19 32A 1 Phase PDU Y Y N Y Y Y Y Y Y N N Y Y 0U Switched and Monitored PDUs00YJ783AU040U 12 C13/12 C19 Switched and Monitored48A 3 Phase PDUN N Y N N N Y N N Y Y Y N 00YJ781AU030U 20 C13/4 C19 Switched and Monitored 24A 1 Phase PDUN N Y N Y N Y N N Y Y Y N1U Switched and Monitored PDUs 4PU7A81117BNDV 1U 18 C19/C13 switched and monitored 48A 3P WYE PDU - ETLN N N N N N N N N N N Y N 4PU7A77467BLC41U 18 C19/C13 Switched and Monitored 80A 3P Delta PDUN N N N N N N N N Y N Y N 4PU7A77469BLC61U 12 C19/C13 switched and monitored 60A 3P Delta PDUN N N N N N N N N N N Y N 4PU7A77468BLC51U 12 C19/C13 switched and monitored 32A 3P WYE PDUY Y Y Y Y Y Y Y Y N Y Y Y 4PU7A81118BNDW1U 18 C19/C13 switched and monitored 48A 3P WYE PDU - CEY Y Y Y Y Y Y Y Y N Y N Y1U Ultra Density Enterprise PDUs (9x IEC 320 C13 + 3x IEC 320 C19 outlets)71763NU 6051Ultra Density Enterprise C19/C13 PDU 60A/208V/3PHN N Y N N N N N N Y Y Y N 71762NX6091Ultra Density Enterprise C19/C13 PDU ModuleY Y Y Y Y Y Y Y Y Y Y Y Y1U C13 Enterprise PDUs (12x IEC 320 C13 outlets)39Y89416010DPI C13 Enterprise PDU Module (WW)Y Y Y Y Y Y Y Y Y Y Y Y Y 1U Front-end PDUs (3x IEC 320 C19 outlets)39Y89386002DPI Single-phase 30A/120V Front-end PDU (US)Y Y Y Y Y Y Y Y Y Y Y Y Y 39Y89396003DPI Single-phase 30A/208V Front-end PDU (US)Y Y Y Y Y Y Y Y Y Y Y Y Y 39Y89346005DPI Single-phase 32A/230V Front-end PDU (International)Y Y Y Y Y Y Y Y Y Y Y Y Y 39Y89406004DPI Single-phase 60A/208V Front-end PDU (US)Y N Y Y Y Y Y N N Y Y Y N 39Y89356006DPI Single-phase 63A/230V Front-end PDU (International)Y Y Y Y Y Y Y Y Y Y Y Y Y1U NEMA PDUs (6x NEMA 5-15R outlets)39Y89055900DPI 100-127V NEMA PDUY Y Y Y Y Y Y Y Y Y Y Y YA N Z A S E A NB r a z i lE E T M E AR U C I S W E H T KI N D I A J A P A NL A N A P R CLine cords for 1U PDUs that ship without a line cord40K96116504 4.3m, 32A/380-415V, EPDU/IEC 309 3P+N+G 3ph wye (non-US) Line CordY Y Y Y Y Y Y Y Y Y Y Y Y 40K96126502 4.3m, 32A/230V, EPDU to IEC 309 P+N+G (non-US) Line CordY Y Y Y Y Y Y Y Y Y Y Y Y 40K96136503 4.3m, 63A/230V, EPDU to IEC 309 P+N+G (non-US) Line CordY Y Y Y Y Y Y Y Y Y Y Y Y40K96146500 4.3m, 30A/208V, EPDU to NEMA L6-30P (US)Line CordY Y Y Y Y Y Y Y Y Y Y Y Y 40K96156501 4.3m, 60A/208V, EPDU to IEC 309 2P+G (US)Line CordN N Y N N N Y N N Y Y Y N 40K96176505 4.3m, 32A/230V, Souriau UTG Female to AS/NZ 3112 (Aus/NZ) Line CordY Y Y Y Y Y Y Y Y Y Y Y Y40K961865064.3m, 32A/250V, Souriau UTG Female to KSC 8305 (S. Korea) Line CordY Y Y Y Y Y Y Y Y Y Y Y Y Part number Feature code Description For more information, see the Lenovo Press documents in the PDU category:https:///servers/options/pduUninterruptible power supply unitsA N Z A S E A NB r a z i lE E T M E AR U C I S W E H T KI N D I AJ A P A NL A N A P R CUninterruptible power supply unitsThe following table lists the uninterruptible power supply (UPS) units that are offered by Lenovo.Table 9. Uninterruptible power supply unitsPart number Description55941AX RT1.5kVA 2U Rack or Tower UPS (100-125VAC)55941KX RT1.5kVA 2U Rack or Tower UPS (200-240VAC)55942AX RT2.2kVA 2U Rack or Tower UPS (100-125VAC)55942KX RT2.2kVA 2U Rack or Tower UPS (200-240VAC)55943AX RT3kVA 2U Rack or Tower UPS (100-125VAC)55943KX RT3kVA 2U Rack or Tower UPS (200-240VAC)55945KX RT5kVA 3U Rack or Tower UPS (200-240VAC)55946KX RT6kVA 3U Rack or Tower UPS (200-240VAC)55948KX RT8kVA 6U Rack or Tower UPS (200-240VAC)55949KX RT11kVA 6U Rack or Tower UPS (200-240VAC)55948PX RT8kVA 6U 3:1 Phase Rack or Tower UPS (380-415VAC)55949PX RT11kVA 6U 3:1 Phase Rack or Tower UPS (380-415VAC)55943KT†ThinkSystem RT3kVA 2U Standard UPS (200-230VAC) (2x C13 10A, 2x GB 10A, 1x C19 16A outlets)55943LT†ThinkSystem RT3kVA 2U Long Backup UPS (200-230VAC) (2x C13 10A, 2x GB 10A, 1x C19 16A outlets)55946KT†ThinkSystem RT6kVA 5U UPS (200-230VAC) (2x C13 10A outlets, 1x Terminal Block output) 5594XKT†ThinkSystem RT10kVA 5U UPS (200-230VAC) (2x C13 10A outlets, 1x Terminal Block output)† Only available in China and the Asia Pacific market.For more information, see the list of Product Guides in the UPS category:https:///servers/options/upsLenovo Financial ServicesTrademarksLenovo and the Lenovo logo are trademarks or registered trademarks of Lenovo in the United States, other countries, or both. A current list of Lenovo trademarks is available on the Web athttps:///us/en/legal/copytrade/.The following terms are trademarks of Lenovo in the United States, other countries, or both:Lenovo®ServeRAIDSystem x®ThinkSystem®The following terms are trademarks of other companies:Linux® is the trademark of Linus Torvalds in the U.S. and other countries.Excel® is a trademark of Microsoft Corporation in the United States, other countries, or both.Other company, product, or service names may be trademarks or service marks of others.。

NuMicro N9H30系列开发板用户手册说明书

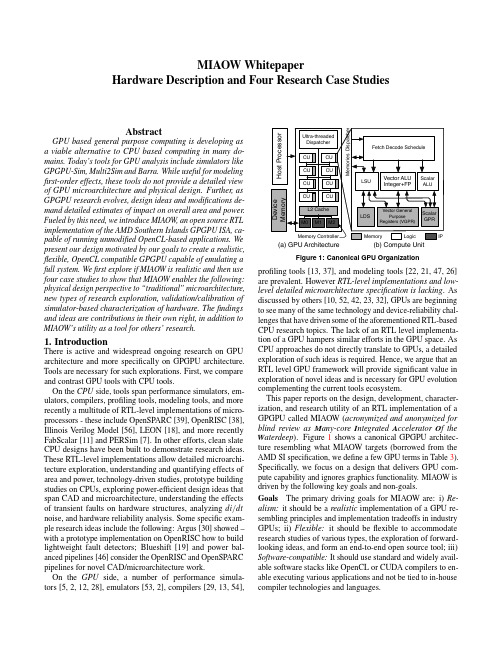

NuMicro®FamilyArm® ARM926EJ-S BasedNuMaker-HMI-N9H30User ManualEvaluation Board for NuMicro® N9H30 SeriesNUMAKER-HMI-N9H30 USER MANUALThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.Nuvoton is providing this document only for reference purposes of NuMicro microcontroller andmicroprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1OVERVIEW (5)1.1Features (7)1.1.1NuMaker-N9H30 Main Board Features (7)1.1.2NuDesign-TFT-LCD7 Extension Board Features (7)1.2Supporting Resources (8)2NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION (9)2.1NuMaker-N9H30 Board - Front View (9)2.2NuMaker-N9H30 Board - Rear View (14)2.3NuDesign-TFT-LCD7 - Front View (20)2.4NuDesign-TFT-LCD7 - Rear View (21)2.5NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB Placement (22)3NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS (24)3.1NuMaker-N9H30 - GPIO List Circuit (24)3.2NuMaker-N9H30 - System Block Circuit (25)3.3NuMaker-N9H30 - Power Circuit (26)3.4NuMaker-N9H30 - N9H30F61IEC Circuit (27)3.5NuMaker-N9H30 - Setting, ICE, RS-232_0, Key Circuit (28)NUMAKER-HMI-N9H30 USER MANUAL3.6NuMaker-N9H30 - Memory Circuit (29)3.7NuMaker-N9H30 - I2S, I2C_0, RS-485_6 Circuit (30)3.8NuMaker-N9H30 - RS-232_2 Circuit (31)3.9NuMaker-N9H30 - LCD Circuit (32)3.10NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 Circuit (33)3.11NuMaker-N9H30 - RMII_0_PF Circuit (34)3.12NuMaker-N9H30 - RMII_1_PE Circuit (35)3.13NuMaker-N9H30 - USB Circuit (36)3.14NuDesign-TFT-LCD7 - TFT-LCD7 Circuit (37)4REVISION HISTORY (38)List of FiguresFigure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation Board (5)Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board (6)Figure 2-1 Front View of NuMaker-N9H30 Board (9)Figure 2-2 Rear View of NuMaker-N9H30 Board (14)Figure 2-3 Front View of NuDesign-TFT-LCD7 Board (20)Figure 2-4 Rear View of NuDesign-TFT-LCD7 Board (21)Figure 2-5 Front View of NuMaker-N9H30 PCB Placement (22)Figure 2-6 Rear View of NuMaker-N9H30 PCB Placement (22)Figure 2-7 Front View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 3-1 GPIO List Circuit (24)Figure 3-2 System Block Circuit (25)Figure 3-3 Power Circuit (26)Figure 3-4 N9H30F61IEC Circuit (27)Figure 3-5 Setting, ICE, RS-232_0, Key Circuit (28)Figure 3-6 Memory Circuit (29)Figure 3-7 I2S, I2C_0, RS-486_6 Circuit (30)Figure 3-8 RS-232_2 Circuit (31)Figure 3-9 LCD Circuit (32)NUMAKER-HMI-N9H30 USER MANUAL Figure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit (33)Figure 3-11 RMII_0_PF Circuit (34)Figure 3-12 RMII_1_PE Circuit (35)Figure 3-13 USB Circuit (36)Figure 3-14 TFT-LCD7 Circuit (37)List of TablesTable 2-1 LCD Panel Combination Connector (CON8) Pin Function (11)Table 2-2 Three Sets of Indication LED Functions (12)Table 2-3 Six Sets of User SW, Key Matrix Functions (12)Table 2-4 CMOS Sensor Connector (CON10) Function (13)Table 2-5 JTAG ICE Interface (J2) Function (14)Table 2-6 Expand Port (CON7) Function (16)Table 2-7 UART0 (J3) Function (16)Table 2-8 UART2 (J6) Function (16)Table 2-9 RS-485_6 (SW6~8) Function (17)Table 2-10 Power on Setting (SW4) Function (17)Table 2-11 Power on Setting (S2) Function (17)Table 2-12 Power on Setting (S3) Function (17)Table 2-13 Power on Setting (S4) Function (17)Table 2-14 Power on Setting (S5) Function (17)Table 2-15 Power on Setting (S7/S6) Function (18)Table 2-16 Power on Setting (S9/S8) Function (18)Table 2-17 CMOS Sensor Connector (CON9) Function (19)Table 2-18 CAN_0 (SW9~10) Function (19)NUMAKER-HMI-N9H30 USER MANUAL1 OVERVIEWThe NuMaker-HMI-N9H30 is an evaluation board for GUI application development. The NuMaker-HMI-N9H30 consists of two parts: a NuMaker-N9H30 main board and a NuDesign-TFT-LCD7 extensionboard. The NuMaker-HMI-N9H30 is designed for project evaluation, prototype development andvalidation with HMI (Human Machine Interface) function.The NuMaker-HMI-N9H30 integrates touchscreen display, voice input/output, rich serial port serviceand I/O interface, providing multiple external storage methods.The NuDesign-TFT-LCD7 can be plugged into the main board via the DIN_32x2 extension connector.The NuDesign-TFT-LCD7 includes one 7” LCD which the resolution is 800x480 with RGB-24bits andembedded the 4-wires resistive type touch panel.Figure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation BoardNUMAKER-HMI-N9H30 USER MANUAL Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board1.1 Features1.1.1 NuMaker-N9H30 Main Board Features●N9H30F61IEC chip: LQFP216 pin MCP package with DDR (64 MB)●SPI Flash using W25Q256JVEQ (32 MB) booting with quad mode or storage memory●NAND Flash using W29N01HVSINA (128 MB) booting or storage memory●One Micro-SD/TF card slot served either as a SD memory card for data storage or SDIO(Wi-Fi) device●Two sets of COM ports:–One DB9 RS-232 port with UART_0 used 75C3232E transceiver chip can be servedfor function debug and system development.–One DB9 RS-232 port with UART_2 used 75C3232E transceiver chip for userapplication●22 GPIO expansion ports, including seven sets of UART functions●JTAG interface provided for software development●Microphone input and Earphone/Speaker output with 24-bit stereo audio codec(NAU88C22) for I2S interfaces●Six sets of user-configurable push button keys●Three sets of LEDs for status indication●Provides SN65HVD230 transceiver chip for CAN bus communication●Provides MAX3485 transceiver chip for RS-485 device connection●One buzzer device for program applicationNUMAKER-HMI-N9H30 USER MANUAL●Two sets of RJ45 ports with Ethernet 10/100 Mbps MAC used IP101GR PHY chip●USB_0 that can be used as Device/HOST and USB_1 that can be used as HOSTsupports pen drives, keyboards, mouse and printers●Provides over-voltage and over current protection used APL3211A chip●Retain RTC battery socket for CR2032 type and ADC0 detect battery voltage●System power could be supplied by DC-5V adaptor or USB VBUS1.1.2 NuDesign-TFT-LCD7 Extension Board Features●7” resolution 800x480 4-wire resistive touch panel for 24-bits RGB888 interface●DIN_32x2 extension connector1.2 Supporting ResourcesFor sample codes and introduction about NuMaker-N9H30, please refer to N9H30 BSP:https:///products/gui-solution/gui-platform/numaker-hmi-n9h30/?group=Software&tab=2Visit NuForum for further discussion about the NuMaker-HMI-N9H30:/viewforum.php?f=31 NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUAL2 NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION2.1 NuMaker-N9H30 Board - Front View Combination Connector (CON8)6 set User SWs (K1~6)3set Indication LEDs (LED1~3)Power Supply Switch (SW_POWER1)Audio Codec(U10)Microphone(M1)NAND Flash(U9)RS-232 Transceiver(U6, U12)RS-485 Transceiver(U11)CAN Transceiver (U13)Figure 2-1 Front View of NuMaker-N9H30 BoardFigure 2-1 shows the main components and connectors from the front side of NuMaker-N9H30 board. The following lists components and connectors from the front view:NuMaker-N9H30 board and NuDesign-TFT-LCD7 board combination connector (CON8). This panel connector supports 4-/5-wire resistive touch or capacitance touch panel for 24-bits RGB888 interface.Connector GPIO pin of N9H30 FunctionCON8.1 - Power 3.3VCON8.2 - Power 3.3VCON8.3 GPD7 LCD_CSCON8.4 GPH3 LCD_BLENCON8.5 GPG9 LCD_DENCON8.7 GPG7 LCD_HSYNCCON8.8 GPG6 LCD_CLKCON8.9 GPD15 LCD_D23(R7)CON8.10 GPD14 LCD_D22(R6)CON8.11 GPD13 LCD_D21(R5)CON8.12 GPD12 LCD_D20(R4)CON8.13 GPD11 LCD_D19(R3)CON8.14 GPD10 LCD_D18(R2)CON8.15 GPD9 LCD_D17(R1)CON8.16 GPD8 LCD_D16(R0)CON8.17 GPA15 LCD_D15(G7)CON8.18 GPA14 LCD_D14(G6)CON8.19 GPA13 LCD_D13(G5)CON8.20 GPA12 LCD_D12(G4)CON8.21 GPA11 LCD_D11(G3)CON8.22 GPA10 LCD_D10(G2)CON8.23 GPA9 LCD_D9(G1) NUMAKER-HMI-N9H30 USER MANUALCON8.24 GPA8 LCD_D8(G0)CON8.25 GPA7 LCD_D7(B7)CON8.26 GPA6 LCD_D6(B6)CON8.27 GPA5 LCD_D5(B5)CON8.28 GPA4 LCD_D4(B4)CON8.29 GPA3 LCD_D3(B3)CON8.30 GPA2 LCD_D2(B2)CON8.31 GPA1 LCD_D1(B1)CON8.32 GPA0 LCD_D0(B0)CON8.33 - -CON8.34 - -CON8.35 - -CON8.36 - -CON8.37 GPB2 LCD_PWMCON8.39 - VSSCON8.40 - VSSCON8.41 ADC7 XPCON8.42 ADC3 VsenCON8.43 ADC6 XMCON8.44 ADC4 YMCON8.45 - -CON8.46 ADC5 YPCON8.47 - VSSCON8.48 - VSSCON8.49 GPG0 I2C0_CCON8.50 GPG1 I2C0_DCON8.51 GPG5 TOUCH_INTCON8.52 - -CON8.53 - -CON8.54 - -CON8.55 - -NUMAKER-HMI-N9H30 USER MANUAL CON8.56 - -CON8.57 - -CON8.58 - -CON8.59 - VSSCON8.60 - VSSCON8.61 - -CON8.62 - -CON8.63 - Power 5VCON8.64 - Power 5VTable 2-1 LCD Panel Combination Connector (CON8) Pin Function●Power supply switch (SW_POWER1): System will be powered on if the SW_POWER1button is pressed●Three sets of indication LEDs:LED Color DescriptionsLED1 Red The system power will beterminated and LED1 lightingwhen the input voltage exceeds5.7V or the current exceeds 2A.LED2 Green Power normal state.LED3 Green Controlled by GPH2 pin Table 2-2 Three Sets of Indication LED Functions●Six sets of user SW, Key Matrix for user definitionKey GPIO pin of N9H30 FunctionK1 GPF10 Row0 GPB4 Col0K2 GPF10 Row0 GPB5 Col1K3 GPE15 Row1 GPB4 Col0K4 GPE15 Row1 GPB5 Col1K5 GPE14 Row2 GPB4 Col0K6GPE14 Row2GPB5 Col1 Table 2-3 Six Sets of User SW, Key Matrix Functions●NAND Flash (128 MB) with Winbond W29N01HVS1NA (U9)●Microphone (M1): Through Nuvoton NAU88C22 chip sound input●Audio CODEC chip (U10): Nuvoton NAU88C22 chip connected to N9H30 using I2Sinterface–SW6/SW7/SW8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5and J5)–SW6/SW7/SW8: 2-3 short for I2S function and connected to NAU88C22 (U10).●CMOS Sensor connector (CON10, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11)–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON10)Connector GPIO pin of N9H30 FunctionCON10.1 - VSSCON10.2 - VSSNUMAKER-HMI-N9H30 USER MANUALCON10.3 - Power 3.3VCON10.4 - Power 3.3VCON10.5 - -CON10.6 - -CON10.7 GPI4 S_PCLKCON10.8 GPI3 S_CLKCON10.9 GPI8 S_D0CON10.10 GPI9 S_D1CON10.11 GPI10 S_D2CON10.12 GPI11 S_D3CON10.13 GPI12 S_D4CON10.14 GPI13 S_D5CON10.15 GPI14 S_D6CON10.16 GPI15 S_D7CON10.17 GPI6 S_VSYNCCON10.18 GPI5 S_HSYNCCON10.19 GPI0 S_PWDNNUMAKER-HMI-N9H30 USER MANUAL CON10.20 GPI7 S_nRSTCON10.21 GPG2 I2C1_CCON10.22 GPG3 I2C1_DCON10.23 - VSSCON10.24 - VSSTable 2-4 CMOS Sensor Connector (CON10) FunctionNUMAKER-HMI-N9H30 USER MANUAL2.2NuMaker-N9H30 Board - Rear View5V In (CON1)RS-232 DB9 (CON2,CON6)Expand Port (CON7)Speaker Output (J4)Earphone Output (CON4)Buzzer (BZ1)System ResetSW (SW5)SPI Flash (U7,U8)JTAG ICE (J2)Power ProtectionIC (U1)N9H30F61IEC (U5)Micro SD Slot (CON3)RJ45 (CON12, CON13)USB1 HOST (CON15)USB0 Device/Host (CON14)CAN_0 Terminal (CON11)CMOS Sensor Connector (CON9)Power On Setting(SW4, S2~S9)RS-485_6 Terminal (CON5)RTC Battery(BT1)RMII PHY (U14,U16)Figure 2-2 Rear View of NuMaker-N9H30 BoardFigure 2-2 shows the main components and connectors from the rear side of NuMaker-N9H30 board. The following lists components and connectors from the rear view:● +5V In (CON1): Power adaptor 5V input ●JTAG ICE interface (J2) ConnectorGPIO pin of N9H30Function J2.1 - Power 3.3V J2.2 GPJ4 nTRST J2.3 GPJ2 TDI J2.4 GPJ1 TMS J2.5 GPJ0 TCK J2.6 - VSS J2.7 GPJ3 TD0 J2.8-RESETTable 2-5 JTAG ICE Interface (J2) Function●SPI Flash (32 MB) with Winbond W25Q256JVEQ (U7); only one (U7 or U8) SPI Flashcan be used●System Reset (SW5): System will be reset if the SW5 button is pressed●Buzzer (BZ1): Control by GPB3 pin of N9H30●Speaker output (J4): Through the NAU88C22 chip sound output●Earphone output (CON4): Through the NAU88C22 chip sound output●Expand port for user use (CON7):Connector GPIO pin of N9H30 FunctionCON7.1 - Power 3.3VCON7.2 - Power 3.3VCON7.3 GPE12 UART3_TXDCON7.4 GPH4 UART1_TXDCON7.5 GPE13 UART3_RXDCON7.6 GPH5 UART1_RXDCON7.7 GPB0 UART5_TXDCON7.8 GPH6 UART1_RTSCON7.9 GPB1 UART5_RXDCON7.10 GPH7 UART1_CTSCON7.11 GPI1 UART7_TXDNUMAKER-HMI-N9H30 USER MANUAL CON7.12 GPH8 UART4_TXDCON7.13 GPI2 UART7_RXDCON7.14 GPH9 UART4_RXDCON7.15 - -CON7.16 GPH10 UART4_RTSCON7.17 - -CON7.18 GPH11 UART4_CTSCON7.19 - VSSCON7.20 - VSSCON7.21 GPB12 UART10_TXDCON7.22 GPH12 UART8_TXDCON7.23 GPB13 UART10_RXDCON7.24 GPH13 UART8_RXDCON7.25 GPB14 UART10_RTSCON7.26 GPH14 UART8_RTSCON7.27 GPB15 UART10_CTSCON7.28 GPH15 UART8_CTSCON7.29 - Power 5VCON7.30 - Power 5VTable 2-6 Expand Port (CON7) Function●UART0 selection (CON2, J3):–RS-232_0 function and connected to DB9 female (CON2) for debug message output.–GPE0/GPE1 connected to 2P terminal (J3).Connector GPIO pin of N9H30 Function J3.1 GPE1 UART0_RXDJ3.2 GPE0 UART0_TXDTable 2-7 UART0 (J3) Function●UART2 selection (CON6, J6):–RS-232_2 function and connected to DB9 female (CON6) for debug message output –GPF11~14 connected to 4P terminal (J6)Connector GPIO pin of N9H30 Function J6.1 GPF11 UART2_TXDJ6.2 GPF12 UART2_RXDJ6.3 GPF13 UART2_RTSJ6.4 GPF14 UART2_CTSTable 2-8 UART2 (J6) Function●RS-485_6 selection (CON5, J5, SW6~8):–SW6~8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5 and J5) –SW6~8: 2-3 short for I2S function and connected to NAU88C22 (U10)Connector GPIO pin of N9H30 FunctionSW6:1-2 shortGPG11 RS-485_6_DISW6:2-3 short I2S_DOSW7:1-2 shortGPG12 RS-485_6_ROSW7:2-3 short I2S_DISW8:1-2 shortGPG13 RS-485_6_ENBSW8:2-3 short I2S_BCLKNUMAKER-HMI-N9H30 USER MANUALTable 2-9 RS-485_6 (SW6~8) FunctionPower on setting (SW4, S2~9).SW State FunctionSW4.2/SW4.1 ON/ON Boot from USB SW4.2/SW4.1 ON/OFF Boot from eMMC SW4.2/SW4.1 OFF/ON Boot from NAND Flash SW4.2/SW4.1 OFF/OFF Boot from SPI Flash Table 2-10 Power on Setting (SW4) FunctionSW State FunctionS2 Short System clock from 12MHzcrystalS2 Open System clock from UPLL output Table 2-11 Power on Setting (S2) FunctionSW State FunctionS3 Short Watchdog Timer OFFS3 Open Watchdog Timer ON Table 2-12 Power on Setting (S3) FunctionSW State FunctionS4 Short GPJ[4:0] used as GPIO pinS4Open GPJ[4:0] used as JTAG ICEinterfaceTable 2-13 Power on Setting (S4) FunctionSW State FunctionS5 Short UART0 debug message ONS5 Open UART0 debug message OFFTable 2-14 Power on Setting (S5) FunctionSW State FunctionS7/S6 Short/Short NAND Flash page size 2KBS7/S6 Short/Open NAND Flash page size 4KBS7/S6 Open/Short NAND Flash page size 8KBNUMAKER-HMI-N9H30 USER MANUALS7/S6 Open/Open IgnoreTable 2-15 Power on Setting (S7/S6) FunctionSW State FunctionS9/S8 Short/Short NAND Flash ECC type BCH T12S9/S8 Short/Open NAND Flash ECC type BCH T15S9/S8 Open/Short NAND Flash ECC type BCH T24S9/S8 Open/Open IgnoreTable 2-16 Power on Setting (S9/S8) FunctionCMOS Sensor connector (CON9, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11).–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON9).Connector GPIO pin of N9H30 FunctionCON9.1 - VSSCON9.2 - VSSCON9.3 - Power 3.3VCON9.4 - Power 3.3V NUMAKER-HMI-N9H30 USER MANUALCON9.5 - -CON9.6 - -CON9.7 GPI4 S_PCLKCON9.8 GPI3 S_CLKCON9.9 GPI8 S_D0CON9.10 GPI9 S_D1CON9.11 GPI10 S_D2CON9.12 GPI11 S_D3CON9.13 GPI12 S_D4CON9.14 GPI13 S_D5CON9.15 GPI14 S_D6CON9.16 GPI15 S_D7CON9.17 GPI6 S_VSYNCCON9.18 GPI5 S_HSYNCCON9.19 GPI0 S_PWDNCON9.20 GPI7 S_nRSTCON9.21 GPG2 I2C1_CCON9.22 GPG3 I2C1_DCON9.23 - VSSCON9.24 - VSSTable 2-17 CMOS Sensor Connector (CON9) Function●CAN_0 Selection (CON11, SW9~10):–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11) –SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensor connector (CON9, CON10)SW GPIO pin of N9H30 FunctionSW9:1-2 shortGPI3 CAN_0_RXDSW9:2-3 short S_CLKSW10:1-2 shortGPI4 CAN_0_TXDSW10:2-3 short S_PCLKTable 2-18 CAN_0 (SW9~10) Function●USB0 Device/HOST Micro-AB connector (CON14), where CON14 pin4 ID=1 is Device,ID=0 is HOST●USB1 for USB HOST with Type-A connector (CON15)●RJ45_0 connector with LED indicator (CON12), RMII PHY with IP101GR (U14)●RJ45_1 connector with LED indicator (CON13), RMII PHY with IP101GR (U16)●Micro-SD/TF card slot (CON3)●SOC CPU: Nuvoton N9H30F61IEC (U5)●Battery power for RTC 3.3V powered (BT1, J1), can detect voltage by ADC0●RTC power has 3 sources:–Share with 3.3V I/O power–Battery socket for CR2032 (BT1)–External connector (J1)●Board version 2.1NUMAKER-HMI-N9H30 USER MANUAL2.3 NuDesign-TFT-LCD7 -Front ViewFigure 2-3 Front View of NuDesign-TFT-LCD7 BoardFigure 2-3 shows the main components and connectors from the Front side of NuDesign-TFT-LCD7board.7” resolution 800x480 4-W resistive touch panel for 24-bits RGB888 interface2.4 NuDesign-TFT-LCD7 -Rear ViewFigure 2-4 Rear View of NuDesign-TFT-LCD7 BoardFigure 2-4 shows the main components and connectors from the rear side of NuDesign-TFT-LCD7board.NuMaker-N9H30 and NuDesign-TFT-LCD7 combination connector (CON1).NUMAKER-HMI-N9H30 USER MANUAL 2.5 NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB PlacementFigure 2-5 Front View of NuMaker-N9H30 PCB PlacementFigure 2-6 Rear View of NuMaker-N9H30 PCB PlacementNUMAKER-HMI-N9H30 USER MANUALFigure 2-7 Front View of NuDesign-TFT-LCD7 PCB PlacementFigure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement3 NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS3.1 NuMaker-N9H30 - GPIO List CircuitFigure 3-1 shows the N9H30F61IEC GPIO list circuit.Figure 3-1 GPIO List Circuit NUMAKER-HMI-N9H30 USER MANUAL3.2 NuMaker-N9H30 - System Block CircuitFigure 3-2 shows the System Block Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-2 System Block Circuit3.3 NuMaker-N9H30 - Power CircuitFigure 3-3 shows the Power Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-3 Power Circuit3.4 NuMaker-N9H30 - N9H30F61IEC CircuitFigure 3-4 shows the N9H30F61IEC Circuit.Figure 3-4 N9H30F61IEC CircuitNUMAKER-HMI-N9H30 USER MANUAL3.5 NuMaker-N9H30 - Setting, ICE, RS-232_0, Key CircuitFigure 3-5 shows the Setting, ICE, RS-232_0, Key Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-5 Setting, ICE, RS-232_0, Key Circuit3.6 NuMaker-N9H30 - Memory CircuitFigure 3-6 shows the Memory Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-6 Memory Circuit3.7 NuMaker-N9H30 - I2S, I2C_0, RS-485_6 CircuitFigure 3-7 shows the I2S, I2C_0, RS-486_6 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-7 I2S, I2C_0, RS-486_6 Circuit3.8 NuMaker-N9H30 - RS-232_2 CircuitFigure 3-8 shows the RS-232_2 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-8 RS-232_2 Circuit3.9 NuMaker-N9H30 - LCD CircuitFigure 3-9 shows the LCD Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-9 LCD Circuit3.10 NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 CircuitFigure 3-10 shows the CMOS Sensor,I2C_1, CAN_0 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit3.11 NuMaker-N9H30 - RMII_0_PF CircuitFigure 3-11 shows the RMII_0_RF Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-11 RMII_0_PF Circuit3.12 NuMaker-N9H30 - RMII_1_PE CircuitFigure 3-12 shows the RMII_1_PE Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-12 RMII_1_PE Circuit3.13 NuMaker-N9H30 - USB CircuitFigure 3-13 shows the USB Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-13 USB Circuit3.14 NuDesign-TFT-LCD7 - TFT-LCD7 CircuitFigure 3-14 shows the TFT-LCD7 Circuit.Figure 3-14 TFT-LCD7 CircuitNUMAKER-HMI-N9H30 USER MANUAL4 REVISION HISTORYDate Revision Description2022.03.24 1.00 Initial version NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUALImportant NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, anymalfunction or failure of which may cause loss of human life, bodily injury or severe propertydamage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomicenergy control instruments, airplane or spaceship instruments, the control or operation ofdynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all typesof safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claimsto Nuvoton as a result of customer’s Insecure Usage, custome r shall indemnify the damagesand liabilities thus incurred by Nuvoton.。

新核心网开站步骤(精)

关于阿朗CDMA的IPBH基站的整合步骤主要目的:因目前新局使用的基站使用IPBH和以前的frame relay方式不同,添加了阿朗的路由交换机7750设备代替了5E同基站连接。

根据新局现场(软件是R31版)的测试经验,总结基站部分的内容,方便SUB-C工程师查阅和尽快上手,也为客户准备技术文档。

步骤简介:根据IPBH基站的特点,主要三个部分步骤:一,基站硬件安装调测二,基站和7750确认传输路由的配合步骤三,基站的数据添加一,基站硬件安装调测1)基站硬件安装完毕2) 基站用RMT调测基站背板参数,把Frame 转为PPP模式,主要是在RMT/boot memory parameter窗口中/trunk group controller parameter简称TGCP和initial link configuration parameter简称ILCP/ recall成RMT自带的配置文件/自己电脑中的RMT目录/config/1bts/IEH/BMP/中根据URC功能配置分1X和EVDO两种:1X的URC是/Voice/URC-URCII/E1/IPBH-Voice/CDM has its owner E1s/TGCP-CDM(1-5-9-13)-IPBH-E1-v4和/Voice/URC-URCII/E1/IPBH-Voice/CDM has its owner E1s/ILCP-CDM(1-5-9-13)-IPBH-E1-v4EVDO的URCII是EVDO/URC-URCII/E1/PPP-EVDO/CDM has its owner E1s/TGCP-CDM(2-6-10-14)-PPP-E1-v4和EVDO/URC-URCII/E1/PPP-EVDO/CDM has its owner E1s/ILCP-CDM(2-6-10-14)-PPP-E1-v4二,基站和7750确认传输路由的配合步骤1,7750加数据需要的条件:1)基站RCS号2)基站传输编号,主要基站每条传输E1是第几个155M(7750连接40条155M)的第几个时隙(每条155M有63个时隙),需要电信客户传输部门提供3)基站现场的E1先自环并和7750工程师配合断开测试确认E1正常2,在基站现场确认得到IP地址,网线连接到基站,telnet 192.168.168.16(第一块URC)或192.168.168.32(第二块URC),执行下面的命令:用户名:lucent 密码:password自动出现背板参数击入:mlpppShow检查是否有MY IP和Primary DNS IP及Secondary DNS IP,这三个IP是7750配置的数据,必须全部是有IP地址的,如为0.0.0.0则基站信令不会起来的,需要联系7750工程师确认或添加数据。

AWG5000系列混合信号伪随机波形生成器说明书

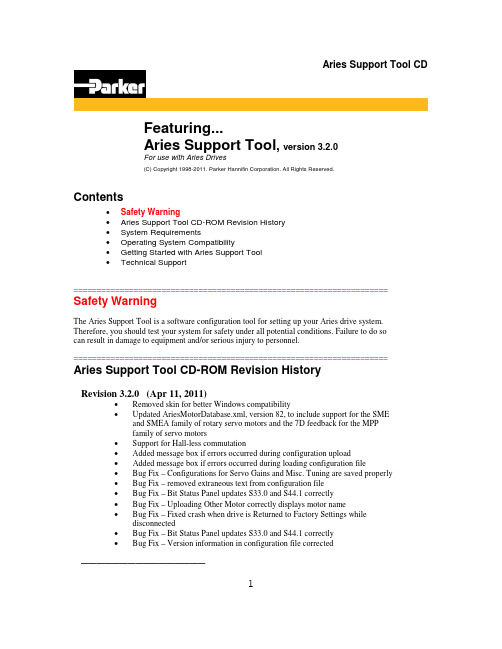

Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)The AWG5000 Series of Arbitrary Waveform Generators Delivers the Industry’s Best Mixed Signal Stimulus Solution for Today’s Complex Measurement ChallengesThe AWG5000 Series of Arbitrary Waveform Generators delivers theoptimal combination of industry leading sample rate, vertical resolution, signal fidelity and waveform memory length,all in an easy-to-use self-contained package.The series offers the industry’s best solution to the challenging signal stim-ulus issues faced by designers verifying,characterizing and debugging sophisti-cated electronic designs.Meeting the needs of today’s design engineers, the series provides excellent signal dynamic range and integrity.AWG5000 Series models, with a 14bits DA converter based sample rate from 600MS/s to 1.2GS/s, two to four output channels, synchronized four to eight digital marker outputs, and 28-channels of digital data outputs, easily solve the toughest measurement chal-lenges in wireless base band I/Q communications, digital consumer product design such as imaging devices, data conversion equipment and semiconductor design and test. The open Windows (Windows XP)-based instruments are easy and convenient to use and connect easily with peripherals and third-party software.AWG5000 Series.Features & Benefits1.2Gs/s and 600MS/s Models 14 bit Vertical Resolution 2 or 4Arbitrary WaveformDifferential/Single-ended Outputs –Up to 4.5V p-p Single-ended and 9V p-p at Differential Output into 50Ω–0.95ns Tr/Tf (10 to 90%) at 0.6V p-p–+/– 5ns Range (50ps Resolution) Inter Channel Skew Control–SFDR: 80dBc (1MHz),64dBc (10MHz)4 or 8Variable Level Marker Outputs–Up to 3.7V p-p Single-ended Output into 50Ω–300ps Tr/Tf (20 to 80%)at 0 to 1V–Up to 1ns Range (50ps Resolution) Delay Control28 Bits Ch 1/Ch 2Variable Level Digital Data Output–Up to 3.7V p-p Single-ended Output into 50Ω–300ps Tr/Tf (20 to 80%)at 0 to 1VUp to 32M Point Record Length For Longer Data Streams Down to 800ps Resolution Edge Timing Shift Control Real-time Sequencing Creates Infinite Waveform Loops, Jumps,and Conditional BranchesEasy to Use and Learn Shortens Test TimeIntuitive User Interface Based on Windows 2000 XP Convenient Bench Top Form FactorIntegrated PC Supports Network Integration and Provides a Built-in DVD, Removable Hard Drive,LAN and USB portsApplicationsDesigning, Testing and Deploying Wireless Communications: –High Fidelity QuadratureModulation I and Q Base-band Signals (Polar Modulation:I/Q + Magnitude Control, Two Pair of I/Q for MIMO)Imaging–Stimulus Signals for Imaging Display and Recording Devices (CCD, LCD)Data Conversion–Stimulus Signals for DataConversion Devices (ADC, DAC)Mixed Signal Design and Test –2/4Ch Analog + 4/8Ch Marker Outputs + 28 Bit Digital Data OutputsReal-world, Ideal or Distorted Signal Generation – Including All the Glitches, Anomalies and ImpairmentsEnhanced/Corrupted Playback of DSO Captured SignalsWaveform Vectors Imported from Third-party T ools such as MathCAD,MATLAB, Excel and OthersArbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)AWG5000 Series • /signal_sources2EVM/Constellation measurement.Typical Signal Injection.Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002) RTSA Spectrum view.9-PAM with 250 Mbps.Mixed signal test by TDS/TLA iView.™AWG5000 Series • /signal_sources3Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)4AWG5000 Series • /signal_sourcesArbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)AWG5014AWG5012AWG5004AWG5002Arbitrary WaveformsWaveform Length 1 to 16,200,000 points (or 1 to 32,400,000 points,option 01)Number of Waveforms 1 to 16,000Sequence Length 1 to 4,000stepsSequence Repeat Counter 1 to 65,536 or infiniteSequence Control Repeat count,Trigger,Go-to-N and JumpJump Mode Synchronous and AsynchronousRun ModesContinuous Waveform is iteratively output.If a sequence is defined,the sequence order and repeat functions are appliedTriggered Waveform is output only once when an external,internal,GPIB,LAN or manual trigger is receivedGated Waveform begins output when gate is true and resets to beginning when falseSequence Waveform is output as defined by the sequenceClock GeneratorSampling Frequency10 MS/s to 1.2GS/s10 MS/s to 600 MS/sResolution8digitsInternal ClockAccuracy Within ±(1 ppm + Aging),Aging:within ±1 ppm/yearClock Phase Noise Less than –90dBc/Hz at 100kHz offsetInternal Trigger GeneratorInternal Trigger RateRange 1.0μs to 10.0sResolution3digits,0.1μs minimumSkew Control Between OutputsRange– 5 ns to + 5nsResolution5psAWG5000 Series • /signal_sources5Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)AWG5000 Series • /signal_sources6AWG5014AWG5012AWG5004AWG5002Main Arbitrary Waveform Output Resolution14 bitsAnalog OutputOutput StyleDifferential Output Impedance 50ΩConnectorBNC FrontAmplitude Output Voltage Normal:–4.5 V to + 4.5V,Direct –0.3V to +0.3V Amplitude Normal:20mV p-p to 4.5V p-p ,Direct; 20mV p-p to 0.6V p-pResolution 1mVDC Accuracy±(2.0% of Amplitude + 2mV) at offset = 0V Offset (into 50Ω) Range Normal:–2.25V to +2.25V,Direct:N/A Resolution 1mVAccuracy±(2% of offset +10mV at minimum amplitudePulse Response Rise/Fall time:(10% to 90%).Normal:1.4ns (2.0V p-p ),Direct:0.95ns (0.6V p-p )Bandwidth (–3dB)Normal:250MHz (2.0V p-p ),Direct:370MHz (0.6V p-p )Ringing Normal:750mV p-p (4.5V p-p filter through),80mV p-p (2.0V p-p filter through),Direct:60mV p-p (0.6V p-p )Low Pass Filter High range:100MHz,20MHz,Low range:through,100MHz,20MHz,Direct:N/ADelay from Marker Normal:17.5ns to 19.4ns (20MHz filter),3.8ns to 5.7ns (100MHz filter),0 to 1.9ns (Through),Direct:–1.5ns to 0.4nsSine Wave Characteristics (1.2GS/s clock,32 waveform points,37.5MHz signal frequency)(600MS/s clock,32 waveform points,18.75MHz signal frequency)Harmonics Normal:≤–40dBc (2.0V p-p ),Direct ≤=–49dBc (0.6V p-p )Normal:≤–46dBc (2.0V p-p ),Direct ≤=–55dBc (0.6V p-p )Non Harmonics Normal:≤–60dBc (2.0V p-p ,DC to 600MHz)Normal:≤–60dBc (2.0V p-p ,DC to 300MHz)Phase noise ≤–85dBc/Hz (2.0V p-p ,10kHz offset) –85dBc/Hz (2.0V p-p ,10kHz offset) SFDR 50dBc (Normal,37.5MHz,1.2GS/s,2.0V p-p )56dBc (Normal,18.75MHz,600MS/s,2.0V p-p )60dBc (Normal,10MHz,600MS/s,1.0V p-p )60dBc (Normal,10MHz,600MS/s,1.0V p-p )80dBc (Normal,1MHz,600MS/s,1.0V p-p )80dBc (Normal,1MHz,600MS/s,1.0V p-p )64dBc (Direct,10MHz,600 MS/s,0.6V p-p )64dBc (Direct,10MHz,600MS/s,0.6V p-p )80dBc (Direct,1MHz,600 MS/s,0.6V p-p )80dBc (Direct,1MHz,600MS/s,0.6V p-p )Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002) Auxiliary OutputsOutput Style Single-endedOutput Impedance50ΩConnector BNC FrontLevel (into 50Ω)(Twice for Hi_Z input)Output Windows–1.00 V to + 2.7VAmplitude0.10 Vp-p to 3.7 Vp-pResolution10mVDC Accuracy±(10% of setting +120mV) Maximum Output Current±54mA /chRise/Fall Time (20% to 80%)300 ps(1.0 Vp-p,Hi +1.0V,Lo 0V) Skew Adjust Between MarkersRange0 to 1000ps Resolution50psRandom Jitter (Typical)1010 clock patternRMS5psrmsTotal Jitter (Typical)2^15–1PN data patternPeak to Peak (p-p)80psp-pClock (VCO) OutRange600MHz to 1.2GHzAmplitude0.4 Vp-pinto 50Ωto GND Impedance:50Ω,AC coupling Connector BNC Rear10MHz Reference OutAmplitude 1.2 Vp-p into 50Ω.Max 2.5 Vp-popenImpedance50Ω,AC couplingConnector BNC RearDC OutputsNumber of Outputs4:independently controlled outputsRange–3.0 to +5.0VResolution10mVMax.Current±100mAConnector2x4 pin header on front panelAWG5000 Series • /signal_sources7Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)AWG5000 Series • /signal_sources8Trigger In Impedance 1 k Ωor 50ΩPolarity POS or NEG ConnectorBNC FrontInput Voltage Range1 k Ω:±10V.50 Ω:±5V Threshold Level –5.0 V to 5.0VResolution 0.1VTrigger Jitter2.0ns to 4.5ns (Typical) Trigger Mode Minimum Pulse Width 20nsTrigger Hold-off 832* sampling_period – 100ns Delay to Analog Out128* sampling_period + 250ns Gate Mode Minimum Pulse Width 1024* sampling_period + 10ns Delay to Analog Out640* sampling_period + 260ns Event Input Impedance 1 k Ωor 50ΩPolarity POS or NEG ConnectorBNC FrontInput Voltage Range 1 k Ω:±10V.50 Ω:±5V Threshold –5.0 V to 5.0VResolution0.1VSequence Mode Mode Minimum Pulse Width 20nsEvent Hold Off 1024* Sampling Period + 10nsDelay to Analog Out640* Sampling Period + 280 ns (Jump timing:Asynchronous jump)External Clock IN Input Voltage Range 0.2 V p-p to 0.8 V p-p Impedance50Ω,AC coupledConnectorBNC RearReference Clock IN Input Voltage Range 0.2 V p-p to 3.0 V p-p Impedance50Ω,AC coupledFrequency Range 10MHz,20MHz,100MHz (with ±0.1%)ConnectorBNC RearPhase Lock IN Input Ranges5MHz to 600MHz (acceptable frequency drift is ±0.5%)Input Voltage Range 0.2 V p-p to 3 V p-pConnectorBNC RearAdd IN For each analog channel Impedance 50Ω,DC coupledDC Gain 1BandwidthDC to 100MHz at –3 dBInput Voltage Range ±1.0V ConnectorBNC RearArbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)(Third party software creation waveform data:MATLAB,MathCad,Excel)S/W driver for 3rd party S/W IVI-com driver and MATLAB libraryInstrument Control/Data Transfer PortsGPIB Remote control and data transfer.(Conforms to IEEE-Std 488.1,compatible with IEEE 488.2 and SCPI-1999.0)Ethernet (10/100/1000Base-T)Remote control and data transfer.(Conforms to IEEE 802.3).RJ-45Computer System & Peripherals Windows XP Professional,512 MB SDRAM,80 GB removable Hard Drive at rear (available front mount kit),CD-RW/DVD drive at front,included USB compact keyboard and mousePC I/O Ports USB 2.0 compliant ports (6 total,2 front,4 rear),PS/2mouse and keyboard connectors (rear panel),RJ-45 Ethernet connector (rear panel) supports 10/100/1000BASE-T,XGA outDisplay Characteristics10.4inch,LCD color display with touch screen,1024 (H)x768 (V) (XGA)Power Supply100 to 240VAC,47 to 63HzPower Consumption450WSafety UL61010-1,CAN/CSA-22.2,No.61010-1-04,EN61010-1,IEC61010-1Emissions EN 55011 (Class A),IEC61000-3-2,IEC61000-3-3Immunity IEC61326,IEC61000-4-2/3/4/5/6/8/11Regional CertificationsEurope EN61326Australia/New Zealand AS/NZS 2064AWG5000 Series • /signal_sources9Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)Ordering Information Arbitrary WaveformGenerator MainframeAWG50141.2GS/s,4-channel,14bits,16M point/channel Arbitrary Waveform Generator.AWG50121.2GS/s,2-channel,14bits,16M point/channel Arbitrary Waveform Generator.AWG5004600MS/s,4-channel,14bits,16M point/channel Arbitrary Waveform Generator.AWG5002600MS/s,2-channel,14bits,16M point/channel Arbitrary Waveform Generator.All Models Include:Accessory pouch,front cover, USB mouse,compact USB key board,lead set for DC output,stylus for touch screen 2 each, Windows®XP operating system restore DVD and instructions,AWG5000 Series product software CD and instructions,Document CD with Browser,Quick Start User Manual,registration card,Certificate of Calibration,power cable.Note:Please specify power cord and language option when ordering.Instrument OptionsAWG5014/AWG5012,AWG5004/AWG5002Opt.01 – Waveform Length Expansion (from 16 M to 32 M).AWG5012/AWG5002Opt. 03 –28 bits digital data outputs (digital data of ch 1 and ch 2).Common OptionsInternational Power PlugsOpt. A0 – North America power.Opt. A1 –Universal EURO power.Opt. A2 – United Kingdom power.Opt. A3 – Australia power.Opt. A5 – Switzerland power.Opt.A6 –Japan power.Opt.A10 – China power.Opt.A99 – No power cord or AC adapter.Language OptionsOpt. L0 – English.Opt. L5 – Japanese.Opt. L7 –Simplified Chinese.Opt. L8 – Traditional Chinese.ServiceOpt. CA1 – A single calibration event.Opt. C3 – Calibration service 3 years.Opt. C5 – Calibration service 5 years.Opt. D1 –Calibration data report.Opt. D3 – Calibration data report 3 years (withoption C3).Opt. D5 – Calibration data report 5 years (withoption C5).Opt. R3 –Repair service 3 years.Opt. R5 –Repair service 5 years.Post-sales Service Options:(e.g.,AWG5012-CA1).CA1 – A single calibration event.R3DW – Repair service coverage 3 years.R5DW – Repair service coverage 5 years.R2PW –Repair service coverage 2 yearspost warranty.R1PW –Repair service coverage 1 yearpost warranty.Product UpgradeAWG5014, AWG50UPOpt.M14 – Waveform Length Expansionfrom 16 M point to 32 M point.Product UpgradeAWG5012, AWG50UPOpt. M12 – Waveform Length Expansionfrom 16 M point to 32 M point.Opt.D13 –Digital Data Outputs.Product UpgradeAWG5004, AWG50UPOpt. M04 – Waveform Length Expansionfrom 16 M point to 32 M point.Product UpgradeAWG5002, AWG50UPOpt.M02 – Waveform Length Expansionfrom 16 M point to 32 M point.Opt.D03 –Digital Data Outputs.AWG5000 Series • /signal_sources 10Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)WarrantyOne-year parts and labor.AWG5000 Series • /signal_sources11Arbitrary Waveform GeneratorAWG5000 Series (AWG5014 • AWG5012 • AWG5004 • AWG5002)For Further InformationTektronix maintains a comprehensive, constantly expanding collection of application notes, technical briefs and other resources to help engineers working on the cutting edge of technology. Please visit Copyright © 2008, Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material.Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies. 07/08 JS/WOW 76W-20381-3Contact Tektronix:ASEAN/Australasia (65) 6356 3900Austria +41 52 675 3777Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777Belgium 07 81 60166Brazil & South America (11) 40669400Canada 1 (800) 661-5625Central East Europe, Ukraine and the Baltics +41 52 675 3777Central Europe & Greece +41 52 675 3777Denmark +45 80 88 1401Finland +41 52 675 3777France +33 (0) 1 69 86 81 81Germany +49 (221) 94 77 400Hong Kong (852) 2585-6688India (91) 80-22275577Italy +39 (02) 25086 1Japan 81 (3) 6714-3010Luxembourg +44 (0) 1344 392400Mexico, Central America & Caribbean 52 (55) 5424700Middle East, Asia and North Africa +41 52 675 3777The Netherlands ***********Norway 800 16098People’s Republic of China 86 (10) 6235 1230Poland +41 52 675 3777Portugal 80 08 12370Republic of Korea 82 (2) 6917-5000Russia & CIS +7 (495) 7484900South Africa +27 11 206 8360Spain (+34) 901 988 054Sweden 020 08 80371Switzerland +41 52 675 3777Taiwan 886 (2) 2722-9622United Kingdom & Eire +44 (0) 1344 392400USA 1 (800) 426-2200For other areas contact Tektronix, Inc. at: 1 (503) 627-7111Updated 12 November 2007roduct(s) are manufactured in ISO registered facilitie Product(s) complies with IEEE Standard 488.1-1987,RS-232-C,and with Tektronix Standard Codes and Formats.。

AJA FS2 Installation and Operation Guide

AJA FS2 Installation and Operation Installation and Operation GuideB e c a u s e i t m a t t e r s .7/31/2012 Version: 1.1.0.0TrademarksAJA®, KONA®, Ki Pro®, KUMO®, and XENA® are registered trademarks of AJA Video, Inc. Io Express™,Io HD™ and Io™ are trademarks of AJA Video, Inc. Apple, the Apple logo, AppleShare, AppleTalk,FireWire, iPod, iPod Touch, Mac, and Macintosh are registered trademarks of Apple Computer, Inc.Final Cut Pro, QuickTime and the QuickTime Logo are trademarks of Apple Computer, Inc. All othertrademarks are the property of their respective holders.NoticeCopyright © 2012 AJA Video, Inc. All rights reserved. All information in this manual is subject tochange without notice. No part of the document may be reproduced or transmitted in any form,or by any means, electronic or mechanical, including photocopying or recording, without theexpress written permission of AJA Inc.FCC Emission InformationThis equipment has been tested and found to comply with the limits for a Class A digital device,pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protectionagainst harmful interference when the equipment is operated in a commercial environment. Thisequipment generates, uses and can radiate radio frequency energy and, if not installed and usedin accordance with the instruction manual, may cause harmful interference to radiocommunications. Operation of this equipment in a residential area is likely to cause harmfulinterference in which case the user will be required to correct the interference at his own expense.Changes or modifications not expressly approved by AJA Video can effect emission complianceand could void the user’s authority to operate this equipment.Contacting SupportTo contact AJA Video for sales or support, use any of the following methods:180 Litton Drive, Grass Valley, CA. 95945 USATelephone: +1.800.251.4224 or +1.530.274.2048Fax: +1.530.274.9442Web: SupportEmail:***************SalesEmail:*************1FS2 Installation and Operation Manual — Limited Warranty Limited WarrantyAJA Video warrants that this product will be free from defects in materials and workmanship for aperiod of five years from the date of purchase. If a product proves to be defective during thiswarranty period, AJA Video, at its option, will either repair the defective product without charge forparts and labor, or will provide a replacement in exchange for the defective product.In order to obtain service under this warranty, you the Customer, must notify AJA Video of the defectbefore the expiration of the warranty period and make suitable arrangements for the performanceof service. The Customer shall be responsible for packaging and shipping the defective product to adesignated service center nominated by AJA Video, with shipping charges prepaid. AJA Video shallpay for the return of the product to the Customer if the shipment is to a location within the countryin which the AJA Video service center is located. Customer shall be responsible for paying allshipping charges, insurance, duties, taxes, and any other charges for products returned to any otherlocations.This warranty shall not apply to any defect, failure or damage caused by improper use or improper orinadequate maintenance and care. AJA Video shall not be obligated to furnish service under thiswarranty a) to repair damage resulting from attempts by personnel other than AJA Videorepresentatives to install, repair or service the product, b) to repair damage resulting from improperuse or connection to incompatible equipment, c) to repair any damage or malfunction caused bythe use of non-AJA Video parts or supplies, or d) to service a product that has been modified orintegrated with other products when the effect of such a modification or integration increases thetime or difficulty of servicing the product.THIS WARRANTY IS GIVEN BY AJA VIDEO IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED.AJA VIDEO AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY ORFITNESS FOR A PARTICULAR PURPOSE. AJA VIDEO’S RESPONSIBILITY TO REPAIR OR REPLACEDEFECTIVE PRODUCTS IS THE WHOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FORANY INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHERAJA VIDEO OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES. Important Safety InformationHazard!This symbol, when used in the manual, indicates a serious health hazard with risk of injury ordeath.Warning!This symbol, when used in the manual, indicates a serious risk or threat to personal safety.Caution!This symbol, when used in the manual, indicates important safety and complianceinformation.Table of Contents ContentsAJA FS2 Installation and Operation Guide. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .i Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ii Notice . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iiFCC Emission Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ii Contacting Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ii Limited Warranty. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii Important Safety Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vChapter 1:Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Video Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Available Video Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Audio Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Control and Other Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Typical Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3FS2 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Front Panel Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4Remote Web Browser Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 SNMP Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4GPI Inputs and Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Optional Remote Control Panel. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Optional Fiber I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Optional Dolby E Decoder and Encoder Cards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Technical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Video Processors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73G Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7Audio Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 What’s In The Box? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9In This Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10Chapter 2:Controls, Indicators, and Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Control and Indicator Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Front Panel Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Alphanumeric Display. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Operational Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Pushbuttons. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Control Knobs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 LED Indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Incompatibility Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Incompatible Video Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Example Reference and Video Incompatibility Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Rear Panel Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Connector Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 AC Power Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 AES/EBU Digital Audio In and Out. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Balanced Analog Audio In and Out. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 RS-422 Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 GPI Inputs and Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 LAN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 SDI In and Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Optical Fiber In and Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Component/Composite Analog Video In and Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 HDMI In and Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Composite NTSC/PAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Reference Video (looping) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 About Inputs and Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21Chapter 3:Installation & Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 Installation Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Installation Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Unpacking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Shipping Box Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Installing Optional Fiber Optic I/O Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Installing Optional Cards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Dolby Decoder Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 FS2 Chassis Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Physical Requirements for Mounting the Chassis. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Chassis Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Cabling and Cooling Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Power Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Network Connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291FS2 Installation and Operation Manual — ContentsNetwork Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Networking Using DHCP or Default Static IP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Networking the FS2 Using Your Own Static IP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Using Ping to Test the Network Connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Mac Ping Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Windows PC Ping Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Web Browser Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32Software Update Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Download the Latest FS2 Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Unpack the Software. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33Uploading and Installing the Software to the FS2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33System Cabling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34System Video/Audio Cable Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34GPI Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34FS2 Audio Level Choices—Pro or Consumer, US or EBU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35Chapter 4:Display Menus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37Controlling the FS2 via Front Panel Display Menus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37Parameter Menus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38Menu Group Buttons. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39SELECT and ADJUST Knobs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39Menu Operation Examples. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40Status Pages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40Simple Menus: Config Format Alarm Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41Multiple Parameter Menus: Video 1 ProcAmp. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Multiple Field Parameters: IP Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43STATUS Menu Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44S.1 I/O Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44S.2 Vid1 Format Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44S.3 Vid1 Format Alarm Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44S.4 Vid2 Format Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45S.5 Vid 2 Format Alarm Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45S.6 Output Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45S.7 Power/Temp Alarm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45S.8 Caption Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46S.9 Dolby Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46S.10 System Name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46REMOTE Menu Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471 Remote Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471.1 Authentication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472.1–4 GPI IN 1–4 Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 483.1–4 GPI 1–4 OUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49Interaction of Presets and GPIs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49Example of a Serial Recall. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49Example of an Unintended Recall. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49CONFIG Menu Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501 System Name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502.1 IP Config . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502.2 IP Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 512.3 Subnet Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 512.4 Default Gateway. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513 MAC Address (view only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 524.0 SNMP Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 524.1 SNMP Trap Destination 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 524.2 SNMP Trap Port 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 534.3 SNMP Trap Destination 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 534.4 SNMP Trap Port 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 545 Power Supply Alarm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546.1 Vid1 Format Alarm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546.2 Vid2 Format Alarm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 557 Reference Alarm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 558 Hidden Menus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 559 Display Intensity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5510 Serial Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5611 Software Version. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5612 Reboot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 PRESET Menu Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 571 Recall Preset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 572 Store Preset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57Interaction of Presets and GPIs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 SYSTEM Menu Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 581 Component In Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 582 Component Out Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 583 Analog Audio Std . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 584 SDI1 3G Detect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 595 SDI2 Input Protect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 596 Fiber1 3G Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 607 Fiber2 Input Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 618 Genlock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 619 Frame Rates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6110 NTSC Standard. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6211 Composite Downconv. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6212 HDMI RGB Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6214.0 AES/EBU SRC Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6314.1–14.8 AES/EBU SRC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6315 Dolby Decoder Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6416 Dolby Decoder Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6417 Dolby Decoder Aux Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6518 Dolby Decoder Aux Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65。

阿尔卡特朗讯程控话机功能代码

功能前缀0 Attendant Call 呼叫话务员9 Professional Trunk Group Seized 中继组出局*10 Set In/Out of service 退出/进入服务*11 Adjust Display Visibility 显示屏调整*12 Lock 话机锁定/解锁*13 Protect. against barge-in & beeps 临时通话保护*14 Substitution 替代*15 Language 语言选择*16 Sta. group exit 退出连选组*17 Sta. group entry 加入连选组*18 Camp-on Control 呼叫等待控制*19 Password modification 修改个人密码*20 Speed call to associated set 快速呼叫关联话机*21 Select Primary Line 选择主线路*22 Select Secondary Line 选择辅线路*23 Message deposit 回叫文本请求*24 Switch off Message LED 关闭留言灯*25 V oice Mail Deposit 点亮留言灯*26 Conversation Recording 通话录音*27 Recordable V oice Guides 动态语音提示录制*28 Remote Extension Activation 激活远程分机*29 Remote Extension Deactivation 取消远程分机*30 Agent processing group call pickup 坐席组代接*31 Secret/Identity 身份保密*32 Manual Hold 手动保持*33 Business account code 业务帐号代码*34 Access to waiting call 查询等待呼叫*35 Park Call/Retrieve 呼叫驻留*36 Night service answering 夜间服务代接*37 Common Hold 通用保持*38 Malicious call 恶意呼叫追踪*39 Direct trunk seizure 直接抓取中继线*40 ACD Prefixes ACD功能*41 Room status management 客房状态管理*42 Mini-bar 迷你酒吧管理*43 Last Caller Callback 回叫最后主叫*44 Meet-me Conference 遇我会议*45 Manual Add-on Conference 手动主控会议*46 Automatic Add-on Conference 自动主控会议*47 Announcement 广播*48 Explicit Precedence level 优先级别*49 Background Music 背景音乐*50 Remote forward 远端转移(跟我转移)*51 Overfl.busy to assoc.set 忙线时溢出至关联话机*52 Overfl.on no answer to associate 无应答时溢出至关联话机*53 Overf.busy/no answer to assoc.set 忙线或无应答时溢出至关联话机*54 Cancel Overfl.to associate 取消溢出至关联话机*55 Cancel auto. callback on busy 取消自动回叫*56 Personal directory Programming 个人通讯录编辑*57 Personal Directory Use 使用个人通讯录*58 Ubiquity Mobile Programming 一号通移动号码编辑*59 Ubiquity 一号通*60 Immediate forward 无条件立即转移*61 Immediate forward on busy 遇忙立即转移*62 Forward on no answer 无应答延时转移*63 Forward on busy or no answer 遇忙或无应答延时转移*64 Forward cancellation 取消转移*65 Cancel Remote forward 远程取消转移*66 Forward cancel.by destinat. 由目的地取消转移*67 Access Callback list 访问回叫列表*68 Suite Do Not Disturb 套房请勿打扰*69 Associated Direct. No. modif. 修改关联话机号码*70 Redial last number 重拨最后号码*71 Direct call pickup 直接代接*72 Group call pickup 组代接*73 Suite Wake-up 套房叫醒*74 Suite Wake-up Cancel 取消套房叫醒*75 Cancel Wake-up 取消叫醒*76 Wake-up/appointment reminder 约会提醒/叫醒服务*77 V oice Mail Access 查询语音消息*78 Do not disturb 请勿打扰*79 Tone test 音频检测# DTMF end-to-end dialing DTMF双音频透明发送功能后缀1 Broker Call 代理呼叫2 Consultation Call 查询呼叫3 Three-Party Conference 三方会议4 Barge-in 强插5 Callback On Free Or Busy Set 遇忙或无应答自动回叫6 Busy Camp-on 遇忙呼叫等待7 Call Announcement 呼叫通知8 V oice Mail Deposit 语音消息留言* DTMF end-to-end dialing DTMF双音频透明发送#71 Business number 业务帐号代码。

Anritsu Series 560-7XXX 和 5400-71XXX RF 检测器操作与维护手册