通信工程课程设计报告 钟控定时电路

通信工程应用技术课程设计报告报告

智能排队系统摘要随着现代技术的不断发展特别是计算机技术的应用,使排队技术的发展也突飞猛进。

智能排队机或称智能排队系统是一种综合运用计算机技术、网络技术、多媒体技术、通讯控制技术的高新技术产品。

它完全模拟了人群排队过程,通过取号、进队、排队等待、叫号服务等功能,取代各类服务性窗口传统的由顾客站立排队的方式,实现了计算机系统代替客户进行排队的过程。

适用于各类窗口服务行业,目前在国外已经广泛应用于金融、医院、电信、以及各级政府对外服务窗口等行业。

银行自动叫号系统就是电子排队管理统的一种,是针对银行服务窗口的特点而设计的。

这里以ATMEL 公司的AT89C52单片机为核心,设计了一个简单的把客户与服务机构相结合的排队叫号系统。

模拟排队叫号管理,科学地处理各种排队情况,操作简便,控制灵活,显示清晰,制作成本低,性价比较高。

关键词:排队技术智能排队系统银行排队叫号系统AT89C52AbstractWith the development of modern technology, especially the application of puter technology, the queuing technology also develops by leaps and bounds. Intelligent Automatic Call Distributor or intelligent queuing system is a kind of high and new technology products of the prehensive use of puter technology, network technology, multimedia technology and munication control technology. It pletely simulates the crowd queue process.Through the functions of taking number, into the team, waiting for the queue, calling the number and so on ,it replaces all kinds of service window of the traditional way by the customer to stand in line, and realizing the puter system instead of the process of the customers line up .it is suitable for all kinds of window service industry, and at present it has been widely used in foreign financial, hospital, telemunications, and government's foreign service windowat all levels , etc. Bank automatic station system is electronic queuing management system which is designed according to the characteristics of the bank service window. Here taking ATMEL pany's AT89C52 single-chip microputer as the core, i design a simple calling the number system which bine the customers with the facilitating agency .It simulates the queue station management and scientificly processes all kinds of queuing situation.It is simple to operate ,smart to control , and the display is clear, and the production is of low cost, high cost performance.Keywords:queuing technologyIntelligent Automatic Call DistributorBank queuing station system AT89C521设计目的与任务要求1.1 设计目的通过课程设计,使学生加强对电子电路的理解,学会对电路分析计算以及设计。

数字钟电路设计报告总结

数字钟电路设计报告总结

数字钟是一种电子设备,它通过电路控制钟表的走动,为用户提供准确的计时服务。

在本报告中,我们介绍了数字钟电路的设计过程,包括硬件设计、软件设计、测试和优化等方面。

首先,我们了解了数字钟的基本组成部分,包括时钟芯片、计数器、定时器、按键、显示屏等。

然后,我们分析了数字钟的用户需求,确定了数字钟的基本功能,如定时闹钟、整点报时、定时关闭等。

在硬件设计方面,我们选择了常用的数字钟电路模块,包括时钟芯片、计数器、定时器、按键、显示屏等,并进行了电路仿真和测试,以确保电路的稳定性和可靠性。

在软件设计方面,我们使用了 C 语言编写数字钟的驱动程序,实现了数字钟的各种功能,如定时闹钟、整点报时、定时关闭等。

同时,我们还优化了数字钟的算法,提高了计算速度和精度,使数字钟的计时更加准确。

最后,我们进行了数字钟的测试和优化,以确保数字钟的质量和性能。

我们使用了各种测试工具和仪器,对数字钟进行了功能测试、性能测试和可靠性测试等,以确保数字钟的可靠性和稳定性。

同时,我们还进行了优化,提高了数字钟的运算速度和精度,使数字钟的计时更加准确。

总的来说,我们介绍了数字钟电路的设计过程,包括硬件设计、软件设计、测试和优化等方面。

我们分析了数字钟的用户需求,选择了常用的数字钟电路模块,进行了电路仿真和测试,优化了数字钟的

算法,确保了数字钟的可靠性和稳定性,为用户提供了准确的计时服务。

通信工程专业课程设计

专业课程设计任务书一、总体要求及课程设计题目总体要求:对学生大学整个阶段知识积累的总结是毕业设计,而对一门课程的阶段性总结手段就是课程设计。

如果学生经过的是一个完善的课程设计环节,不仅可以提升学习兴趣、总结所学知识,更重要的是可以将学过的知识进行系统的整合,是一个有效的知识的再提高、再丰富的过程。

此次课程设计其目的在于加深对专业基础课与专业课基本知识的理解,掌握运用Multisim 软件对电路进行设计和仿真。

1)可以查找相关资料,使用网上免费信息资源,但要符合题目要求功能; 2、设计完成时进行答辩,答辩不通过为不合格。

设计题目:1)2ASK 调制与解调系统的设计(4人组) 主要技术指标:1.数字信号用施密特电路实现2.载波信号用LC 振荡器实现(频率:1MHz )频率稳定度00f f ∆≤4105-⨯/小时输出电压的峰峰值为P P V -≥1V 3.数字信号占空比可调(选作) 4.误码率(选作)2)2FSK 调制与解调系统的设计(4人组)主要技术指标:1.数字信号用施密特电路实现2.载波信号用LC 振荡器实现(频率:1MHz )频率稳定度00f f ∆≤4105-⨯/小时输出电压的峰峰值为P P V -≥1V 3.数字信号占空比可调(选作) 3)频率发生器的设计(3人组)主要技术指标:1. 用单片机设计一个频率发生器2. 产生100HZ 到100KHZ 之间的频率(100HZ 、500HZ 、1KHZ 、5 KHZ 、10 KHZ 、50 KHZ 、100 KHZ )3. 占空比可调4).集电极调幅电路的设计(4人组)已知条件:+Vcc =12V, 晶体管为3DG130(3DG12),回路电感根据所定频率选用活自绕,可用环形磁芯,也可用高频骨架绕制。

主要技术指标:1.中心频率0f =(根据设计及级联电路的要求自行决定,将你所选择的频率填上)2.输出功率0P ≥ 100 mw ,效率η> 40% , 调幅度a m ≥0.3 ,负载L R =51Ω 5).变容二极管直接调频电路(4人组)已知条件:+Vcc =12V, 晶体管为3DG100, 负载L R =1K Ω,变容二极管2CC1C, 回路电感根据所定频率选用或自绕主要技术指标:1.中心频率 0f =(根据设计及级联电路的要求自行决定,将你所选择的频率填上。

电子设计中的时钟和定时电路设计

电子设计中的时钟和定时电路设计在电子设计中,时钟和定时电路是非常重要的组成部分,它们负责控制各个模块之间的数据传输和协调系统各部分的工作。

时钟信号通常被用来同步各种操作,确保数字电路的正常工作。

在本文中,将重点介绍时钟和定时电路的设计原理和实际应用。

首先,时钟信号是一个周期性方波信号,周期性地产生并传输给整个系统,以便各个部分可以按照同一时间步进行工作。

时钟信号的频率和占空比取决于系统的要求,常见的频率为几十兆赫兹至几百兆赫茹。

时钟信号的稳定性和准确性对整个系统的性能有着重要影响,因此时钟信号的设计需要特别谨慎。

一般来说,时钟信号的生成可以通过晶振、振荡器或PLL(锁相环)等方式实现。

晶振是最常见的时钟信号源,通过晶体的压电效应产生稳定的频率。

振荡器则是通过放大和反馈的方式产生稳定的振荡信号,适用于一些简单的应用场景。

而PLL是一种通过与参考信号比较并调整输出频率的方式,非常适用于需要频率可调的场合。

另外,定时电路在电子设计中也起着至关重要的作用。

定时电路用于控制各种操作的时间顺序,保证系统的正确运行。

常见的定时电路包括计数器、定时器、触发器等。

计数器可以实现对时钟信号计数并产生指定时序的信号,用于控制一些周期性的操作。

定时器则是用于设置一个特定的时间延迟后产生触发信号,常用于各种定时控制场合。

而触发器则是一种可控制状态转换的元件,用于存储和改变系统的状态。

在实际的电子设计工程中,时钟和定时电路的设计需要考虑以下几点:时钟信号的稳定性和准确性、时序的要求、电路的功耗和面积等。

对于高性能的计算机系统或通信系统,时钟和定时电路的设计是至关重要的一环,设计师需要根据具体的应用场景灵活选择合适的时钟信号源和定时电路方案。

总之,时钟和定时电路设计是电子设计中的重要环节,它们的正确设计对整个系统的性能和稳定性有着重要影响。

设计师在设计时需要充分考虑系统的实际需求,并具备相应的电路设计和调试能力,才能设计出高性能、稳定可靠的时钟和定时电路。

通信工程课程设计报告

附件1西安邮电学院专业课程设计报告书系部名称:通信与信息工程学院学生姓名:专业名称:通信工程专业班级:时间:2011年10月10日至2011年10月21日附件2 西安邮电学院 通信工程 系 专业课程设计 成绩鉴定表 学生姓名专业班级/学号进行时间 2011年10月10日 — 2011年 10 月21日题目专业课程设计具体内容第一周基础型实验模块(实验一—实验四) 第二周 基础型实验模块(实验五—实验六) 提高型实验模块(实验一—实验五)成绩鉴定接受单位评价 (20分)学习态度(10分)学习纪律(10分)报告鉴定 (30分) 报告内容与教学计划内容结合程度(15分)报告质量(主题、结构、观点、逻辑、资料)(15分)验收鉴定 (50分)程序的合理性(15分)调试过程(20分) 调试结果(15分)评阅教师姓名职称成绩评语评阅教师签字年 月 日实验一时间表调度实验一、实验目的时间调度表实验用来考查自己对时间表调度原理的掌握情况。

二、实验原理及设计在程控数字交换的体系结构中,周期级程序(例如摘挂机检测程序、脉冲识别程序、位间隔识别程序)是由时间表调度实现的。

所谓时间表调度,是指每经过交换系统的最短有效时间(这通常是指各周期性程序周期的最大公约数),都会检查调度表的调度要求,如果某个程序在这时需要执行,则调度程序开始执行它。

调度表任务如下进行初始化:时间(10ms)\任务0:摘挂机检测任务1:脉冲检测任务2:位间隔检测任务0 0 1 01 0 1 02 0 1 03 0 1 04 0 1 05 0 1 06 0 1 07 0 1 08 0 1 09 0 1 110 0 1 011 0 1 012 0 1 013 0 1 014 0 1 015 0 1 016 0 1 017 0 1 018 0 1 019 1 1 1这个交换系统提供了三个周期性调度程序(摘挂机检测程序、脉冲识别程序和位间隔识别程序),它们的调用周期分别为200ms、10ms和100ms,所以我们系统的最小调度时间为10ms。

数字钟兼钟控定时器设计_课程设计

数字钟兼钟控定时器设计_课程设计四川航天职业技术学院电子工程系课程设计专业名称:电信课题名称:数字钟兼钟控定时器设计时间: 7>2013年 1月 7 日《数字钟兼钟控定时器课程设计》任务书一、课题名称:数字钟兼钟控定时器二、技术指标:1、显示时间时包括AM、PM、小时、分钟及秒(12小时制)。

2、整点报时时,白天报时,报时时唱一首歌,夜间不报时。

3、双定时在24h内任意时间开启、任意时间关闭家用电器的电源。

4、59min内任意时间倒计时定时功能。

功能键可以调时、调分钟、调开启时间、调关闭时间、调倒计时时间。

三、要求:1、能显示时间。

2、具有整点报时功能。

3、具有双定时功能。

4、能做为闹钟使用。

5、具有倒计时功能。

6、应具有功能设置键。

指导教师:学生:电子工程系―电信2013 年 1月 7日课程设计报告书评阅页课题名称:数字钟兼钟控定时器班级:电信姓名:2013 年 1月 7日指导教师评语:考核成绩:指导教师签名:年月日摘要随着社会的进步,信息化产业的发展,出现的高科技产品的技术含量也越来越来高,数字电子技术的掌握和发展是对新知识新技术接轨的一种直接途径;再加上定时器部分自动设置的结合可以说这也是一个现代化产品。

虽然现在它的技术含量并不高,但我相信通过努力创新和不断的改进与改装,也将会成为一种实用性强、水平高的产品。

可以知道《数字电子钟兼钟控定时器》这是以社会生活相接轨的课题,因此它会得到社会的认可和使用。

数字钟是采用数字电路实现时、分、秒数字显示的计时装置。

由于数字集成电路的发展和石英晶体振荡器的使用,使得数字钟的精度、稳定性远远超过了机械钟表,再者数字电子钟在我们的实际生活中经常见到,它的精度、稳定性远远超过了机械钟表,因此得到了广泛的使用。

关键字:数字钟、定时器、高精度、稳定性、LM8364目录一设计工具的简介71.1 Protel DXP简介71.2 数字电子技术简介7二基本原理与方案设计72.1 基本原理72.2 方案设计82.2.1 方案一82.2.2 方案二82. 3 方案论证与比较9三核心器件介绍 103.1 LM8364简介103.2 LM8364内部电路框图113.3 LM8364的功能11四设计过程134.1 60Hz信号产生电路134.2 整点报时电路 164.3 定时闹钟电路 174.4 误报时控制电路17五原理图与PCB板设计185.1 原理图的设计 185.2 PCB板的设计18六安装、调试及功能实现206.1 安装216.2 调试216.3 功能实现及拓展21七总结227.1 总结23参考文献24附录一25附录二26附录三27一设计工具的简介1.1 Protel DXP简介随着科技与技术的发展,手工制作印制板逐渐被软件代替了。

通信工程设计与监理《时钟和电源管理》

知识点时钟和电源管理

一、教学目标:

学会使用CC2530电源管理

二、教学重点、难点:

重点掌握CC2530电源管理控制的概念。

三、教学过程设计:

1知识点说明

CC2530不同的运行模式或供电模式用于低功耗运行。

超低功耗运行的实现通过关闭电源模块以防止损耗功耗。

2知识点内容

CC2530有五种不同的运行模式〔供电模式〕,分别被称作主动模式、空闲模式、2 和3 具有最低的功耗。

3知识点讲解

1〕CC2530电源管理:CC2530不同的运行模式或供电模式用于低功耗运行。

2〕CC2530电源管理控制:所需的供电模式通过使用存放器 SLEED 的MODE 位和位来选择。

3〕CC2530振荡器和时钟:设备有一个系统时钟或主时钟。

该系统时钟的源既可以用16 MH RC 振荡器,也可以采用32 MH 晶体振荡器。

4〕高频振荡器:是由32 MH晶振振荡器,16 MH RC 振荡器组

成。

5〕低频振荡器:32 HRC振荡器运行在H。

四、课后作业或思考题:

2530电源管理?

CC2530不同的运行模式或供电模式用于低功耗运行。

超低功耗运行的实现通过关闭电源模块以防止损耗功耗,还通过使用特殊的门控时钟和关闭振荡器来降低动态功耗。

五、本节小结:

CC2530电源管理有5种模式:主动模式、空闲模式、2 和H晶振振荡器

低频振荡器:是32 H晶体振荡器用于运行在H,为系统需要的时间精度提供一个稳定的时钟信号。

通信工程专业单片机原理及应用课程设计题目

题目一:数字电压表

设计框图如下:

要求:精确测量电压值,并进行数字显示,要求精确到小数点后第2位。

题目二:数字频率计

设计框图如下:

要求:准确测量脉冲信号频率并在显示模块上进行显示,要求精确到1Hz。

题目三:数字钟

设计框图如下:

要求:数字钟,显示小时、分钟、秒钟、厘秒,并可由键盘进行控制,包括定时、复位、闹钟、秒表计时等功能。

题目四:实况交通灯的设计

设计框图如下:

设计要求:实现四相位的控制,包括每个方向的直行、左转,更高要求可以考虑右转。

并要在数码显示管上显示相应路况的路权剩余或者等待剩余时间。

电路设计中的时钟与定时电路时钟和定时电路的设计原理和应用

电路设计中的时钟与定时电路时钟和定时电路的设计原理和应用电路设计中的时钟与定时电路时钟和定时电路在电路设计中扮演着非常重要的角色。

它们为电子设备提供准确的时间基准,并控制电路中各个部分的操作。

本文将介绍时钟和定时电路的设计原理和应用。

一、时钟的设计原理和应用时钟电路是电子设备中最基本的部分之一,它能够产生一系列等间隔的脉冲信号。

这些脉冲信号被用来同步和驱动其他部件,确保系统的正常运行和协调。

1.1 时钟信号的生成时钟信号可以通过不同的方式生成,最常见的方式是使用晶体振荡器。

晶体振荡器是一种利用晶体的压电效应产生稳定频率信号的装置。

当施加电压时,晶体会以固定频率振荡,并产生精确的时钟信号。

1.2 时钟的频率和精度时钟的频率决定了系统的工作速度,一般用赫兹(Hz)表示。

常见的时钟频率有1MHz、10MHz、100MHz等。

时钟的精度则决定了时钟信号的稳定性和准确度。

一般来说,时钟的精度越高,系统的性能越好。

1.3 时钟的分频和倍频时钟信号可以通过分频器进行分频,将时钟信号的频率降低到更适合其他部件的工作频率。

而倍频器则可以将时钟信号的频率提高到需要的频率水平。

分频和倍频技术可以实现不同部件之间频率的匹配。

1.4 时钟的同步和延迟在多个电子设备之间,时钟信号的同步非常重要。

时钟信号的同步能够保证不同部件之间的操作协调一致。

而延迟线则可以用来调整时钟信号在电路中传播的时间,以达到精确控制的目的。

二、定时电路的设计原理和应用定时电路用于产生一系列精确的时间延迟,用来控制电路中的各种操作。

定时电路广泛应用于计时器、时序电路、脉冲生成等领域。

2.1 定时电路的基本原理定时电路一般由计数器和比较器组成。

计数器可以按照设定的频率进行计数,当计数值达到比较器设定的值时,比较器将产生一个输出脉冲,实现时间延迟的功能。

2.2 定时电路的种类常见的定时电路包括单稳态电路、多谐振荡器和定时器。

单稳态电路产生一个固定宽度的脉冲信号,多谐振荡器可以产生具有特定周期的周期性信号,而定时器则可以根据需求产生不同时间延迟的信号。

数字钟课程设计

东华理工大学课程设计报告课程名称:数字钟系部:信息工程系通信工程专业班级:1421302小组成员:谢渊良指导教师:邓伶俐完成时间:2016/ 3/20报告成绩:目录摘要 (2)第一章:课程设计任务与要求 (3)第二章:设计内容 (3)2.1 基本设计思路 (3)第三章:详细设计及参数计算 (4)3.1 秒脉冲的产生 (4)3.2 时钟显示电路设计 (5)3.2.1时计数的设计 (6)3.2.2秒计数、分计数的设计................................................................73.3 整点报时电路设计 (8)第四章:系统的总体设计与仿真 (9)第五章:总结 (10)参考文献 (10)摘要电子钟在现代社会已经使用的非常广泛,伴随着数字电路技术的发展,数字钟的出现,更加方便了大家的生活,同时也大大地促进了社会的进步。

数字电路具有电路简单、可靠性高、成本低等优点,本设计就以数字电路为核心设计智能电子钟。

数字钟就是由电子电路构成的计时器。

是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。

它的计时周期为12小时,显示满刻度为11时59分59秒,另外应有校时功能和、报时等附加功能。

主电路系统由秒信号发生器、时、分、秒计数器,译码器及显示器,校时电路,整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现,这里采用555定时器。

秒信号产生器将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

计数器用的是74160。

译码显示电路将“时”、“分”、“秒”计数器的输出状态送到七段显示译码管译码显示出来。

定时闹钟设计 课程设计报告

按时闹钟设计之马矢奏春创作摘要:本设计目的是利用单片机设计制作一个简易的按时闹铃时钟,可以放在宿舍或教室使用,在夜晚或黑暗的场所也可以使用.可以设置现在的时间以及闹铃的时间而且显示出来,若时间到则发出一阵声响.本次设计的按时闹钟在硬件方面就采纳了AT89C52芯片,用6位LED数码管进行显示.LED用P0口进行驱动,采纳的是静态扫描显示,能够比力准确显示时时—分分—秒秒.通过五个功能按键可以实现对时间的修改、按时和闹铃终止,闹钟设置的时间到时蜂鸣器可以发作声响.在软件方面用C51编程.整个按时闹钟系统能完成时间的显示,调时和设置闹钟、停止响铃等功能,并经过系统仿真后获得了正确的结果.关键词:按时闹钟;蜂鸣器;AT89C52;74HC245;目录第1章绪论11.2.1设计要求:11.2.2设计任务:1第2章系统总体设计2系统设计需求总体设计方案第3章系统硬件设计43.2.3 74HC245芯片7??????LED显示模块????????按键模块??第4章系统软件设计11第5章系统测试13??测试环境??????测试步伐??????测试环境的构建??结论15致谢16参考文献17附录18第1章绪论本次课程设计的主题是按时闹钟,其基础部份是一个数字钟.电路系统由秒信号发生器、“时、分、秒”计数器、显示器组成.其中秒信号发生器是整个系统的时基信号,它直接决定计时系统的精度,这里用51单片机的按时器来实现.利用按时器获得每一秒的时刻,然后在法式中,我们就可以给秒进行逐秒赋值,满60秒则进位为1分,满60分则进位为1小时,满24小时则时间重置实现一天24小时的循环.译码显示电路将“时”、“分”、“秒”计数器的输出状态送到七段显示译码器译码,通过一个六位八段数码管显示出来.这里利用51单片机的相关知识,来实现电子闹钟的相关功能.实验使用了AT89C52、74HC245等芯片,通过单片机的P0、P3管脚来驱动数码管显示出相应的时刻.本文将讲述AT89C52、74HC245等芯片的基本功能原理,偏重点介绍该电子闹钟的设计.1.2.1设计要求:使用6位七段LED显示器来显示现在的时间;显示格式为“时时分分秒秒”;具有4个按键来做功能设置,可以设置现在的时间及显示闹铃设置时间;时间到则发出一阵声响,可通过按键复位;对单片机系统设计的过程进行总结,认真书写课程设计陈说并按时上交.1.2.2设计任务:利用51单片机结合七段LED显示器设计一个简易的按时闹铃时钟,可以放在宿舍或教室使用,由于用七段LED显示器显示数据,在夜晚或黑暗的场所也可以使用.可以设置现在的时间及显示闹铃设置时间,若时间到则发出一阵声响.论文分别叙述从硬件和软件上实现该设计的过程.第2章为总体设计方案.第3章主要介绍设计实现需要解决的硬件问题.依次介绍所使用的各种硬件的使用方法,并附上仿真电路图和文字说明.第4章从软件的角度说明实现该设计需要解决的问题.第2章系统总体设计系统要求实现以下功能:1.当电源接通时,系统能正确显示以后时间.2.以后时间与实时时间有误差时,可以通过键盘调整以后时间.3.系统允许进行闹钟设置,开启闹钟功能时,当设置的闹钟时间与以后时间一致的时候,系统通过蜂鸣器发出警报声而且可以通过按键停止.功能组成:本次设计中的计时功能很容易实现,难点在于时钟功能和闹钟功能的切换和时间的设置.该电子闹钟设计对51单片机按时器0装初值,使其初值对应50ms,按时器0的中断次数达到20次就刚好为1s,当秒部份计数到60时置零,并向分部份进一;当分部份计数到60时置零,并向时部份进一,那时部份计数到24时置零,从而满足时钟的正常工作.在设计过程中,我发现通过4个按键来完成一个闹钟的基础功能虽然可以实现,可是用户用起来就会很麻烦,因为有的键必需有多种功能和分歧的触发方式,我认为可以增加少许按键来方便用户快速了解到我们的闹钟是如何进行控制的.所以本次设计设置5个键依次对其进行“时间校准”、“闹钟设置”、“秒分时切换/终止警报”、“加1按钮”、“减1按钮”.“秒分时切换/终止报警”键在调时状态中,起时分秒切换的作用,在非调试状态下,起闹钟终止的作用.当用户按下“时间校准”的按钮后,法式会关闭T0按时器,之后时钟停止工作,此时数码管会显示以后静止的时间,说明已经进入时间校准的界面了.在完成时间校准后,翻开T0按时器,时钟会在设置好的时间上继续工作走秒.当用户按下“闹钟设置”按钮后,会将以后时间复制出来提供给按时界面,注意此时我们的时钟仍然在继续工作,只是数码管显示的是按时模式的静止时间.当设置好后,此时用户设置的时间只要没有触发过闹铃,再次按“闹钟设置”按钮就能检查并修改,即闹钟会保管下用户最后一次未被触发的闹钟时间.当正常工作的时钟时刻达到了预设的闹铃时刻,蜂鸣器发出警报声,屏幕会闪烁并显示以后时间.考虑到用户可能已经被提醒而不想继续被闹铃声干扰,还提供了一个能够终止闹铃的功能,此功能与“时分秒切换”功能共用同一按键,按下后时钟继续正常工作,且闹钟功能又可以重新设置.本设计在Keil编程环境下,使用C语言进行编程的编纂.编纂胜利后,通过仿真软件Proteus进行仿真测试.LED显示屏×1主控芯片:AT89C52闹钟提示:蜂鸣器人机交互:按键×5晶振:12KHz×1排阻:RESPACK8×1电容:10nf×2总线收发器:74HC245×2第3章系统硬件设计系统硬件模块主要分为以下几个模块:1.主控模块:控制其他子模块.2.时钟模块:为系统提供实时时间.3.显示模块:显示系统时间信息.4.按键模块:用户通过按键进行人机交互,修改实时时间、设置闹钟时间和终止闹钟报警. 5.闹钟模块:在所设闹钟时间发出警报声.(1).AT89C52简介AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash 只读法式存储器和256 bytes的随机存取数据存储器(RAM),器件采纳ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS51指令系统,片内置通用8位中央处置器和Flash 存储单位,AT89C52单片机在电子行业中有着广泛的应用.AT89C52有40个引脚,32个外部双向输入/输出(I/O)端口,同时内含2个外中断口,3个16位可编程按时计数器,2个全双工串行通信口,2 个读写口线,AT89C52可以依照惯例方法进行编程,也可以在线编程.其将通用的微处置器和Flash存储器结合在一起,特别是可反复擦写的Flash存储器可有效地降低开发本钱.AT89C52有PDIP、PQFP/TQFP及PLCC等三种封装形式,以适应分歧产物的需求.AT89C52引脚图如图3.2.1:(2).工作原理AT89C52为8 位通用微处置器,采纳工业标准的C51内核,在内部功能及管脚排布上与通用的8xc52 相同,其主要用于会聚调整时的功能控制.功能包括对会聚主IC 内部寄存器、数据RAM及外部接口等功能部件的初始化,会聚调整控制,会聚测试图控制,红外遥控信号IR的接收解码及与主板CPU通信等.主要管脚有:XTAL1(19 脚)和XTAL2(18 脚)为振荡器输入输出端口,外接12MHz 晶振.RST/Vpd(9 脚)为复位输入端口,外接电阻电容组成的复位电路.VCC(40 脚)和VSS(20 脚)为供电端口,分别接+5V电源的正负端.P0~P3 为可编程通用I/O 脚,其功能用途由软件界说,在本设计中,P0 端口(32~39 脚)被界说为N1 功能控制端口,分别与N1的相应功能管脚相连接,13 脚界说为IR输入端,10 脚和11脚界说为I2C总线控制端口,分别连接N1的SDAS(18脚)和SCLS(19脚)端口,12 脚、27 脚及28 脚界说为握手信号功能端口,连接主板CPU 的相应功能端,用于以后制式的检测及会聚调整状态进入的控制功能.P0 口:P0 口是一组8 位漏极开路型双向I/O 口, 也即地址/数据总线复用口.作为输出口用时,每位能吸收电流的方式驱动8 个TTL逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用.在访问外部数据存储器或法式存储器时,这组口线分时转换地址(低8 位)和数据总线复用,在访问期间激活内部上拉电阻.在Flash编程时,P0 口接收指令字节,而在法式校验时,输出指令字节,校验时,要求外接上拉电阻.P1 口:P1 是一个带内部上拉电阻的8 位双向I/O 口, P1 的输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路.对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口.作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL).与AT89C51 分歧之处是,P1.0 和P1.1 还可分别作为按时/计数器2 的外部计数输入(P1.0/T2)和输入(P1.1/T2EX),Flash 编程和法式校验期间,P1 接收低8 位地址.P2 口:P2 是一个带有内部上拉电阻的8 位双向I/O 口,P2 的输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路.对端口P2 写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL).在访问外部法式存储器或16 位地数据存储器(例如执行MOVX @DPTR 指令)时,P2 口送出高8 位地址数据.在访问8 位地址的外部数据存储器(如执行MOVX@RI 指令)时,P2 口输出P2锁存器的内容.Flash编程或校验时,P2亦接收高位地址和一些控制信号.P3 口:P3 口是一组带有内部上拉电阻的8 位双向I/O 口.P3 口输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路.对P3 口写入“1”时,它们被内部上拉电阻拉高并可作为输入端口.此时,被外部拉低的P3 口将用上拉电阻输出电流(IIL).P3 口除作为一般的I/O 口线外,更重要的用途是它的第二功能P3 口还接收一些用于Flash闪速存储器编程和法式校验的控制信号.RST:复位输入.当振荡器工作时,RST引脚呈现两个机器周期以上高电平将使单片机复位.ALE/PROG:当访问外部法式存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8 位字节.一般情况下,ALE 仍以时钟振荡频率的1/6 输出固定的脉冲信号,因此它可对外输出时钟或用于按时目的.要注意的是:每当访问外部数据存储器时将跳过一个ALE 脉冲.对Flash存储器编程期间,该引脚还用于输入编程脉冲(PROG).如有需要,可通过对特殊功能寄存器(SFR)区中的8EH 单位的D0 位置位,可禁止ALE 把持.该位置位后,只有一条MOVX 和MOVC指令才华将ALE 激活.另外,该引脚会被微弱拉高,单片机执行外部法式时,应设置ALE 禁止位无效.PSEN:法式贮存允许(PSEN)输出是外部法式存储器的读选通信号,当AT89C52 由外部法式存储器取指令(或数据)时,每个机器周期两次PSEN 有效,即输出两个脉冲.在此期间,当访问外部数据存储器,将跳过两次PSEN信号.EA/VPP:外部访问允许.欲使CPU 仅访问外部法式存储器(地址为0000H—FFFFH),EA 端必需坚持低电平(接地).需注意的是:如果加密位LB1 被编程,复位时内部会锁存EA端状态.如EA端为高电平(接Vcc端),CPU 则执行内部法式存储器中的指令.Flash存储器编程时,该引脚加上+12V 的编程允许电源Vpp,固然这必需是该器件是使用12V编程电压Vpp.XTAL1:振荡器反相放年夜器及内部时钟发生器的输入端.XTAL2:振荡器反相放年夜器的输出端.利用芯片内部的振荡电路,在XTAL1、XTAL2的引脚上外接按时元件,内部振荡器便能发生自激振荡.按时元件可以采纳石英晶体和电容组成的并联谐振电路,如图3.2.2所示.晶振可以在1.2~12MHZ之间任选,甚至可以达到24MHz,可是频率越高功耗也就越年夜.和晶振并联的电容C1、C2的年夜小对振荡频率有微小影响,可以起到频率微调作用.时钟电路如图3.2.2:3.2.3 74HC245芯片电路中用74HC245芯片充任总线收发器,作用是放年夜信号,它具有典范的CMOS型三态缓冲门电路.由于单片机或CPU的数据/地址/控制总线端口都有一定的负载能力,如果负载超越其负载能力,一般应加驱动器.引脚界说:1引脚DIR:未输入输出端口转换用,当它为高电平“1”时,信号由“A”端口输入“B”端口输出;当它为低电平“0”时,信号由“B”端口输入“A”端口输出.29引脚:“A”端口输入输出端,每个端口与“B”端口对应.1118引脚:“B”端口输入输出端,每个端口与“A”端口对应.10引脚:GUD,电源地.20引脚:VCC,电源正极.74HC245引脚图如图3.2.3(1):图3.2.3(1)仿真电路图如图3.2.3(2):图3.2.3(2)3.3 LED显示模块本次课程设计采纳了6位数码管显示电路.在6位LED显示时,为了简化电路,降低本钱,采纳静态显示的方式, 6个LED显示器共用一个8位的I/O, 6位LED数码管的位选线分别由相应的P2. 0~P2. 5控制,而将其相应的段选线并联在一起,由一个8位的I/O口控制,即P0口.译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来.达到按时电路时根据计时系统的输出状态发生脉冲信号,然后去触发音频发生器实现闹铃.校时电路时用来对“时”、“分”、“秒”显示数字进行校对换整的.LED仿真电路图如图3.3:图3.4 按键模块按键模块共设置了五个按键,功能分别如下:(1).时间校准键“CLOCK”: 自锁开关,按下后进入校准设置,再次按下后退出.(2).闹钟设置键“ALARM CLOCK”: 自锁开关,按下后进入闹钟设置,再次按下后退出.另外可供用户对已经设置的闹钟时间进行检查或修改.(3). 秒分时切换/终止报警键“SWITCH/STOP”: 按钮开关,在按下“CLOCK”或“ALARM CLOCK”键时,为时分秒切换功能,默认是“秒”,再次按下是“分”,然后是“时”之后是“秒”,以此类推.在“CLOCK”或“ALARM CLOCK”键未按下时,为终止报警功能.(4).时间增加键“+”:按钮开关,可以在进入校准设置和闹钟设置后,进行加一把持.(5).时间减少键“”: 按钮开关,可以在进入校准设置和闹钟设置后,进行减一把持.按键模块仿真电路图如图3.4:闹铃指示设置有声和光两种形式.声音形式的关键元件是蜂鸣器.蜂鸣器有无源和有源两种,前者需要输入声音频率信号才华正常发声,后者则只需外加适当直流电源电压即可,本次设计我们使用的是后者.闹钟电路是用比力器来比力计时系统和按时系统的输出状态,如果计时系统和按时系统的输出状态相同,则发出一个脉冲信号,再和一个高频信号混合,送到放年夜电路驱动扬声器发声,从而实现按时闹响的功能.蜂鸣器仿真电路图如图3.5:第4章系统软件设计该部份主要分为实时时钟模块、LED显示模块、键盘中断模块、闹钟模块.实时时钟部份主要包括实时时间的读写,时间的修改.LED显示模块主要包括显示屏的初始化,显示的命令字.键盘中断模块包括各键的界说和作用,按键的消抖,各按键跳转的子法式分配.闹钟模块包括闹钟时间的设置,以及对蜂鸣器启动和停止条件的设置和处置.主法式包括三个部份.一是主函数部份,负责系统的初始化把持;从中断服务取得实时时间;判断闹钟时间是否与实时时间相等并在相等时发出警报声.第二部份是按时中断部份,分两种情况:负责处置从中断服务获得的时间数据并送至LED显示缓冲显示,或者显示闹钟设置界面并显示闹钟时间的设置过程.第三部份是外部中断,主要界说5个按键的作用,分配每一个按键跳转的子法式.第三部份负责时间和日期的修改,闹钟时间的设置,停止蜂鸣器鸣叫的功能.断系统在单片机应用系统中起着十分重要的作用,是现代嵌入式控制系统广泛采纳的一种适时控制技术,能对突发事件进行及时处置,从而年夜年夜提高系统对外部事件的处置能力.正是有了中断技术,单片机才得以能够普及.因此,中断技术是单片机的一项重要技术,掌握中断技术能开发出灵活、高效的单机片应用系统.要让单机片停止以后的法式去执行其他法式,需要向它发出请求信号,CPU接收到中断请求信号后才华发生中断.让CPU发生中断的信号称为中断源(又称中断请求源).单片机提供5个中断源,其中两个为外部中断请求源INT0(P3.2)和INT1(P3.3),两个片内按时器/计数器T0和T1的溢出请求中断源TF0和TF1,1个片内串行口发送或接收中断请求源T1和R1.单片机内的CPU工作时,如果一个中断源向它发出中断请求信号,它就会发生中断.可是,如果同时有两个中断源发出中断请求信号,CPU就会优先接收级别高的中断请求源,然后再接收优先级别低的中断请求.表4.3.2列出5个自力中断请求源由其硬件结构决定的自然优先级排列顺序.表4.3.2 单片机中断源的自然优先级、入口地址及中断编号对应于单片机的5个自力中断源,应有相应的中断服务法式.这些中断服务法式有专门规定的寄存位置,即表4.3.2的中断入口地址.当有了中断请求后,CPU可以根据入口地址迅速找到中断服务法式并开始执行,年夜年夜提高执行效率.主法式见附录.第5章系统测试Proteus仿真模拟软件.(1).在Proteus软件中绘制好按时闹钟仿真模拟电路图.(2).将Keil编译器生成的.hex文件载入AT89C52芯片.(3).在Proteus软件中,点击左下角的“play”按钮启动按时闹钟.如下图,“play”按钮在第一个.图5.3.1(3)仿真电路运行控制按钮详细测试内容如下:按时闹钟是否能正确显示时间;是否能正确显示闹钟设置时的界面;是否能正确显示时间调整时的界面.(1).显示时间点击“play”键之后,时钟系统开始走时,如图5.5.2(1):图5.3.2(1)经测试,显示结果达到预期要求.(2).时间调整测试如果用户发现时间运行分歧毛病,要对时间进行修改和调整,就需要进入时间修改的界面.预期可以对时、分、秒进行调整和修改.系统能正确显示时间修改的界面.用户可以完成时间的修改.经测试,该部份运行正常.(3).闹钟设置测试在系统能正确显示时间之后,用户若想设置闹钟,可以通过按键完成闹钟时间的设置.设置时间到后蜂鸣器报警,按下“STOP”键后警报停止经测试,该部份能正常运行.结论:通过以上对仿真项目的全面测试,可知仿真部份运行正常.通过以上测试,证明本设计基本实现系统所有要求,即能够正确显示时间信息,能够对以后时间进行调整和修改,而且能够设定闹钟并在所设置的闹钟时间发出警报声,通过按键可以停止警报.结论该系统采纳单机片AT89C52作为核心芯片,结合一些其他外围设备,一起构成了一款能够显示时间而且能够对其进行修改和设置按时闹钟的按时闹钟系统.该系统采纳数码管显示屏,能够清晰显示时间信息,而且能够友好的引导用户进行时间的修改以及闹钟的设置.可以通过各个寄存地址对时间进行读写把持,即读取时间和修改时间.利用蜂鸣器为用户提供闹铃功能,能够在设按时间发出警报声提醒用户.采纳按键较少的自力式键盘供人机交互,把持简双方便.可以通过键盘修改时间,也可以设置闹铃时间和修改闹铃时间,另外,在闹铃时间与系统时间一致,蜂鸣器鸣叫时,可以通过按键中断警报声.总之,该按时闹钟系统完成了市场上一般闹钟应有的功能,能够显示时间和设置闹钟,可以给用户提供时间信息.该设计也存在一些缺点,就是实际生产时投入资金会比市场上一般闹钟价格昂贵,如果进行包装,价格还会上升一些.另外,外观不如市场销售的闹钟美观.致谢衷心感谢雷俊红老师的指导.参考文献[1] 李强,51系列单片机应用软件编程技术[M].北京:北京航空航天年夜学出书社,.4:134138.[2] 薛慧芳.MCS51单机片串行口的一口多用[J].南京化工年夜学学报(自然科学版),1998,S1:8486.[3] 王东锋,王会良,董冠强.单机片C语言应用100例[M].北京:电子工业出书社,.3:218219,148152.[4] 楼然苗,李光飞.单片机课程设计指导(第2版)[M].北京:北京航空航天年夜学出书社,.1:285289.附录:系统电路图如下:系统电路图系统法式如下:#include<reg52.h>sbit btnTime = P1^0;sbit btnClock = P1^1;sbit btnSwitch = P1^2;sbit btnUp = P1^3;sbit btnDown = P1^4;sbit pin1 = P2^0;sbit pin2 = P2^1;sbit pin3 = P2^2;sbit pin4 = P2^3;sbit pin5 = P2^4;sbit pin6 = P2^5;sbit pinBuz = P2^6;unsigned char timer = 0,sec,min,hour,count = 0,s = 60,m = 60,h = 24,flag = 0; unsigned char code numbers[] = {0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90}; void delayMs(unsigned int k){unsigned int i,j;for(i = k;i>0;i)for(j = 110;j>0;j);}void timeChange(){sec++;if(sec == 60){sec = 0;min++;if(min == 60){min = 0;hour++;if(hour == 24)hour = 0;}}}void showTime(unsigned char zs,unsigned char zm, unsigned char zh){ pin1 = 1;P0 = numbers[zh/10];delayMs(5);pin1 = 0;pin2 = 1;P0 = numbers[zh%10]&0x7f;delayMs(5);pin2 = 0;pin3 = 1;P0 = numbers[zm/10];delayMs(5);pin3 = 0;pin4 = 1;P0 = numbers[zm%10]&0x7f;delayMs(5);pin4 = 0;pin5 = 1;P0 = numbers[zs/10];delayMs(5);pin5 = 0;pin6 = 1;P0 = numbers[zs%10];delayMs(5);pin6 = 0;}void setTime(){unsigned char st,mt,ht;if(btnTime == 0){delayMs(10);if(btnTime == 0){st = sec,mt = min,ht = hour;TR0 = 0;while(btnTime == 0){showTime(st,mt,ht);if(btnSwitch == 0){delayMs(10);if(btnSwitch == 0){while(!btnSwitch);count++;if(count == 3)count = 0;}}if(btnUp == 0){delayMs(10);if(btnUp == 0){while(!btnUp);switch(count){case 0:st++;if(st == 60)st = 0;break;case 1:mt++;if(mt == 60)mt = 0;break;case 2:ht++;if(ht == 24)ht = 0;break;default:;}}}if(btnDown == 0){delayMs(10);if(btnDown == 0){while(!btnDown);switch(count){case 0:if(st>0)st;elsest = 0;break;case 1:if(mt>0)mt;elsemt = 0;break;case 2:if(ht>0)ht;elseht = 0;break;default : ;}}}}TR0 = 1;sec = st,min = mt,hour = ht;}}showTime(sec,min,hour);}void setClock(){if(btnClock == 0){delayMs(50);if(btnClock == 0){if(flag == 0){s = sec;m = min;h = hour;}flag = 1;while(btnClock == 0){showTime(s,m,h);if(btnSwitch == 0){delayMs(10);if(btnSwitch == 0){while(!btnSwitch);count++;if(count == 3)count = 0;}}if(btnUp == 0){delayMs(10);if(btnUp == 0){while(!btnUp);switch(count){case 0:s++;if(s == 60)s = 0;break;case 1:m++;if(m == 60)m = 0;break;case 2:h++;if(h == 24)h = 0;break;default:;}}}if(btnDown == 0){delayMs(10);if(btnDown == 0){while(!btnDown);switch(count){case 0:if(s>0)s;elses = 0;break;case 1:if(m>0)m;elsem = 0;break;case 2:if(h>0)h;elseh = 0;break;default:;}}}}}}}void buzzer(){if((hour == h)&&(min == m)&&(sec == s)){int i;for(i = 1;i<30;i++){if(btnSwitch == 0){delayMs(20);if(btnSwitch == 0){break;}}pinBuz = 1;delayMs(450);showTime(sec,min,hour);pinBuz = 0;delayMs(300);showTime(sec,min,hour);}flag = 0;}}void init(){TMOD = 0x01;TH0 = (6553645872)/256;TL0 = (6553645872)%256;EA = 1;ET0 = 1;TR0 = 1;pinBuz = 0;}void main(){init();while(1){setTime();setClock();buzzer();}}void T0_ms() interrupt 1{TH0 = (6553645872)/256;TL0 = (6553645872)%256;timer++;if(timer == 20){timer = 0;timeChange();}}。

电子电路中的时钟与定时技巧

电子电路中的时钟与定时技巧在现代电子设备中,时钟和定时功能起着至关重要的作用。

无论是计算机、手机、电视机还是家电产品,都需要准确和稳定的时钟信号来同步各个组件的操作。

本文将重点介绍电子电路中的时钟与定时技巧,帮助读者更好地理解和应用这些关键技术。

一、时钟信号的基本原理在电子电路中,时钟信号是一种周期性变化的电信号,用于驱动和同步各个组件的工作。

时钟信号通常由晶振或者时钟发生器产生,它的频率是固定的,用来确定各个操作的时间间隔。

时钟信号的频率一般以赫兹(Hz)为单位,常见的时钟频率有10MHz、20MHz等。

二、常见的时钟电路1. 晶振电路晶振是一种能够稳定振荡的石英晶体,它在电压的作用下会形成固定频率的机械振动,产生准确的时钟信号。

晶振电路通常由晶振、负载电容和负载电阻等组成。

晶振的频率由晶体的物理参数决定,一般常见的晶振频率有4MHz、8MHz等。

2. 时钟发生器电路时钟发生器是一种集成电路,能够产生各种频率的时钟信号。

相较于晶振,时钟发生器具有更高的频率可调节性和更低的功耗。

时钟发生器通常由振荡器、分频器和锁相环等组成。

振荡器产生基础频率,分频器将其分频得到所需频率,锁相环则用于提供更高精度的时钟信号。

三、定时技巧的应用1. 时序控制时序控制是指根据时钟信号的变化来控制电路的工作顺序和时间间隔。

通过合理设计时序控制电路,我们可以精确地实现各个组件的同步操作。

时序控制电路通常由触发器、计数器和多路选择器等组件构成,它们能够按照预定的顺序和时间间隔执行动作。

2. 定时器定时器是一种能够按照设定的时间进行计时和触发动作的电路。

定时器通常由计数器、比较器和控制逻辑等组成。

我们可以通过设置计数器的初值和比较器的阈值来实现不同的定时功能。

定时器广泛应用于蓝牙设备、家电产品和自动化系统中,能够实现定时开关、报警和定时采样等功能。

3. 时钟同步在某些应用场景下,需要多个设备之间保持时钟同步,以确保数据传输和通信的正确性。

电子电路的时钟与定时电路设计

电子电路的时钟与定时电路设计一、引言时钟与定时电路在现代电子产品中起到了至关重要的作用,它们能够帮助我们测量时间、进行计时,并且在一些应用中还可以实现自动控制功能。

本文将详细介绍时钟与定时电路的设计原理和步骤。

二、时钟电路设计1. 利用晶振实现稳定的时钟信号。

- 选择适当的晶振类型和频率。

- 根据晶振的参数计算所需的外部电容和电感。

2. 使用分频电路将时钟信号分频为所需的频率。

- 选择适当的分频器件,如计数器。

- 根据分频系数计算所需的输入时钟频率和输出频率。

3. 添加零位检测电路来保证时钟输出的准确性。

- 使用比较器或门电路实现零位检测。

- 根据需要调整零位检测的门槽电平和门槽宽度。

三、定时电路设计1. 使用555定时器实现常见的定时功能。

- 根据所需的定时时间和模式选择合适的555定时器芯片。

- 根据555定时器的引脚功能表连接外部元件,如电容和电阻。

2. 使用单片机实现复杂的定时功能。

- 选择合适的单片机芯片,并熟悉其编程语言和开发环境。

- 编写程序实现所需的定时功能,如定时器中断和时钟分频。

3. 结合外部元件实现高级的定时功能。

- 将传感器、继电器等外部元件与定时电路连接起来。

- 根据外部元件的状态和输入信号进行判断和控制。

四、注意事项1. 时钟和定时电路的设计要充分考虑电源电压、电路环境等因素,以保证电路的可靠性和稳定性。

2. 时钟和定时电路的设计要符合电路的特性和实际应用需求,避免过度设计或不足设计。

3. 在进行时钟和定时电路的设计前,进行充分的仿真和测试,以确保电路的正确性和可靠性。

五、总结时钟与定时电路的设计是电子工程师必备的技能之一,本文介绍了时钟与定时电路设计的原理和步骤。

通过合理选择元器件、连接电路和编写程序,我们可以实现各种各样的时钟和定时功能。

然而,在实际应用中,我们还需要综合考虑电路的稳定性、可靠性和应用需求,以达到最佳的设计效果。

希望本文能对读者的电路设计工作有所帮助。

时钟和定时电路设计与优化策略

时钟和定时电路设计与优化策略时钟和定时电路是电子设备中至关重要的组成部分,它们不仅仅用于显示时间,还在许多应用中用于同步各种操作和事件。

本文将探讨时钟和定时电路的设计原理及优化策略,以帮助读者更好地理解并应用于实际项目中。

一、时钟和定时电路的基本原理时钟电路是一种可以稳定产生和维持一定频率信号的电路,常用的时钟信号包括方波、脉冲和振荡信号等。

定时电路则是利用时钟信号来控制和计量特定时间,以便实现各种操作和事件的精确控制。

在设计时钟和定时电路时,有几个重要的参数需要考虑:1. 频率:时钟的频率以赫兹(Hz)或兆赫兹(MHz)作为单位表示,决定了时钟信号周期的长度。

2. 稳定性:时钟的稳定性表示时钟信号频率的精确度和稳定度,即使在环境变化或电源波动的情况下,时钟信号的频率变化也应尽可能小。

3. 延迟:延迟是指从时钟信号的上升沿或下降沿到达目标电路的某个特定点所需的时间。

延迟时间应根据具体应用场景和要求进行合理规划和衡量。

二、时钟和定时电路的设计策略1. 选择合适的时钟源:在时钟电路设计中,选择合适的时钟源非常重要。

一般来说,时钟源可以是晶体振荡器、射频信号或其他可靠的时钟信号发生器。

在选择时,需考虑到应用的稳定性和精确性要求。

2. 噪声抑制与滤波:在时钟源附近添加相应的电路组件,如滤波器、抑制电路等,可以减小噪声对时钟信号的干扰,提高稳定性和精确性。

3. 优化布线:合理设计电路板布线,减小时钟电路信号走线长度和交叉干扰,可以有效提高时钟信号的传输质量和抗干扰能力。

4. 时钟校准和校正:通过软件或硬件手段对时钟信号进行校准和校正,提高时钟的精确度和稳定度。

根据应用需求,可以采用自动校准方案或手动修正方式。

5. 引脚和接口设计:合理布局时钟电路和外部接口,避免时钟信号相互干扰和接口冲突,确保时钟与其他电路的良好协同工作。

三、时钟和定时电路的优化策略1. 简化电路结构:在时钟和定时电路设计中,应尽量简化电路结构,减少元器件的数量和复杂性,以提高系统可靠性和降低成本。

时钟和定时电路设计

时钟和定时电路设计随着科技的发展,时钟和定时电路的应用范围越来越广泛。

在现代的生产、制造、通讯等领域,它们都扮演着极其重要的角色。

本文将介绍时钟和定时电路的基本概念、设计方法和应用,希望对读者有所启示和帮助。

一、概述时钟是指一种能够持续发出规律的信号,并且可以测量和表示时间的装置。

在电子领域,时钟通常是由定时电路产生的。

定时电路是指一类电路,它们能够按照一定的时间间隔产生规律的电信号,常用于触发、计数、控制等方面。

时钟和定时电路设计的基础是时间控制,也就是根据需要精确地测量和控制时间。

时间控制的精度和稳定性对于某些应用特别重要,比如航天、导航、通信等。

为了实现精确的时间控制,需要采用一系列的方法和技术,如晶体振荡器、调制解调器、时钟芯片等。

二、晶体振荡器晶体振荡器(Crystal Oscillator)是一种利用晶体振动特性产生稳定高频信号的振荡器。

它的构成主要由晶体振荡回路、振荡管及放大器等组成。

晶体振荡器广泛应用于微波、通讯、测试、精密时钟等领域。

晶体振荡器的关键部分是晶体谐振器。

晶体谐振器通常由一块厚度和尺寸固定的石英晶体和两个电极组成。

在激励电压的作用下,晶体会发生压电振动,产生一定的周期性位移量,形成一个类似谐振的波动。

当晶体的振荡频率等于谐振频率时,晶体就会得到放大,输出的信号就会放大到一定的振幅。

晶体振荡器的优点是频率稳定性高、温度兼容性好、抗干扰能力强。

但其缺点是成本较高、尺寸较大、功耗较大,因此在一些低功耗、小型化等要求较高的应用场合可能会使用其他稳定的时钟源。

三、调制解调器调制解调器(Modem)是通信系统中的一种重要组成部分,它用于将数字信号转换成模拟信号,以便在模拟通道中传输。

调制解调器主要由调制器、解调器和接口电路组成,常用于广播、电话、电视、计算机等通信领域。

调制器(Modulator)将数字信号转换成模拟信号,常用的调制方式有幅度调制、频率调制和相位调制等。

解调器(Demodulator)则将模拟信号恢复成数字信号,恢复的精度对整个通讯系统的可靠性和效率有很大影响。

通信工程专业课程设计报告--多功能数字钟的设计与实现

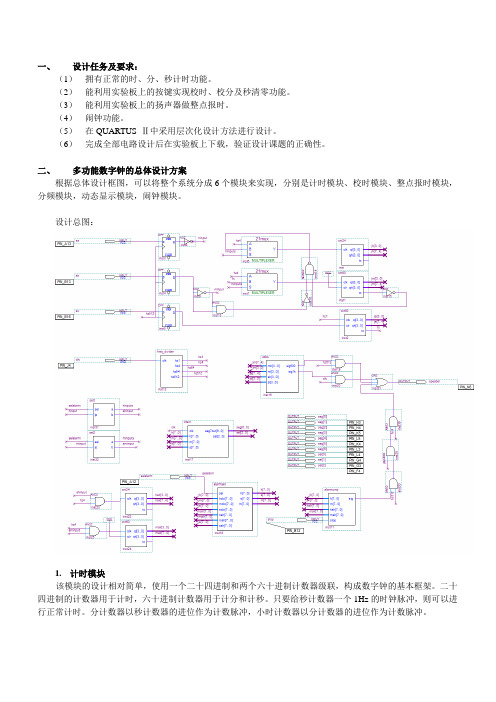

一、设计任务及要求:(1)拥有正常的时、分、秒计时功能。

(2)能利用实验板上的按键实现校时、校分及秒清零功能。

(3)能利用实验板上的扬声器做整点报时。

(4)闹钟功能。

(5)在QUARTUS Ⅱ中采用层次化设计方法进行设计。

(6)完成全部电路设计后在实验板上下载,验证设计课题的正确性。

二、多功能数字钟的总体设计方案根据总体设计框图,可以将整个系统分成6个模块来实现,分别是计时模块、校时模块、整点报时模块,分频模块,动态显示模块,闹钟模块。

设计总图:1.计时模块该模块的设计相对简单,使用一个二十四进制和两个六十进制计数器级联,构成数字钟的基本框架。

二十四进制的计数器用于计时,六十进制计数器用于计分和计秒。

只要给秒计数器一个1Hz的时钟脉冲,则可以进行正常计时。

分计数器以秒计数器的进位作为计数脉冲,小时计数器以分计数器的进位作为计数脉冲。

clk ql[3..0]qh[3..0]tccnt24instclk clr ql[3..0]qh[3..0]tccnt60inst1NOTinst15VCCjm[3..0]jm[7..4]jh[3..0]jh[7..4](24进制计数器构成时计数器,60进制计数器构成的秒、分计数器)24进制的仿真图:60进制的仿真图以下是计时模块设计VHDL语言:(1)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt24 isport(clk:in std_logic;ql,qh:out std_logic_vector(3 downto 0);tc:out std_logic);end cnt24;architecture one of cnt24 isbeginprocess(clk)variable iql,iqh:std_logic_vector(3 downto 0);beginif clk'event and clk='1' then iql:=iql+1;if iql="1010" then iqh:=iqh+1; iql:="0000";end if;if (iqh="0010")and(iql="0100") then tc<='0'; iqh:="0000"; iql:="0000";end if;end if;ql<=iql; qh<=iqh;end process;end one;(2)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt60 isport(clk,clr:in std_logic;ql,qh:buffer std_logic_vector(3 downto 0);tc:out std_logic);end cnt60;architecture behavor of cnt60 isbegintc<='0' when(clk='1' and ql="0000" and qh="0110") else '1';process(clk,clr,ql,qh)variable iql,iqh:std_logic_vector(3 downto 0);beginif(clr='0'or (iql="0000" and iqh="0110"))theniql:="0000";iqh:="0000";else if(clk'event and clk='1')theniql:=iql+1;if(iql="1010")theniql:="0000";iqh:=qh+1;end if;end if;end if;ql<=iql;qh<=iqh;end process;END behavor;2.校时模块该模块设计要求实现校时、校分及秒清零的功能。

【大学课件】通信工程数字钟课程设计 多功能数字钟课程设计

十分频

1Hz (1S)

1KHz CPA

100Hz

74LS90 QD

CPA

10Hz

74LS90 QD

CPA

74LS90 QD

ppt课件

8

T=1ms

T1=10ms

T2=100ms

T3=1s

74LS90分频电路

ppt课件

9

3、计数器的设计 (1)60进制秒、分的设计

ppt课件

10

(1)24进制小时设计

面包板的介绍

横通竖不通

断点

ppt课件

竖通横不通

17

芯片布局

断点

74LS47×4

74LS90×4

555

ppt课件

74LS90×3

18

四、组装调试步骤

1. 先用4片74LS90分别组成60进制分计数器和24进制小时计数器。 2. 将四位译码和共阳数码显示部分接好,每位数码管公共端3、8各接

一只510欧上拉限流电阻。 3. 先接实验台的10HZ~100HZ计数脉冲,调节合适频率,测试计数、

ppt课件

20

74LS90接地、置9端接线问题

555引入

十分频

1Hz (1S)

1KHz CPA

QD 100Hz CPA

QD 10HCPzA

QD

74LS90

74LS90

74LS90

ppt课件

21

附:芯片引脚图

74LS90二-五-十进制计数器

74LS47共阳七段译码驱动器

74LS86四-二输入异或门

74LS47译码驱动器功能表

ppt课件

13

译码显示电路设计

510Ω

6 2 1 7

数字钟电路设计报告

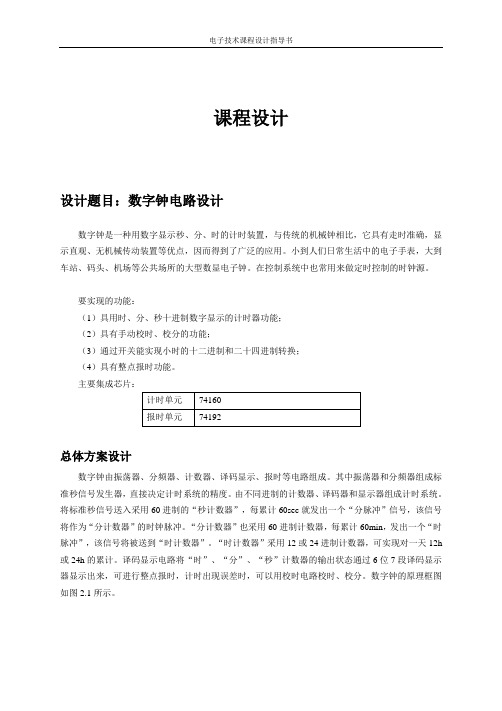

电子技术课程设计指导书课程设计设计题目:数字钟电路设计数字钟是一种用数字显示秒、分、时的计时装置,与传统的机械钟相比,它具有走时准确,显示直观、无机械传动装置等优点,因而得到了广泛的应用。

小到人们日常生活中的电子手表,大到车站、码头、机场等公共场所的大型数显电子钟。

在控制系统中也常用来做定时控制的时钟源。

要实现的功能:(1)具用时、分、秒十进制数字显示的计时器功能;(2)具有手动校时、校分的功能;(3)通过开关能实现小时的十二进制和二十四进制转换;(4)具有整点报时功能。

主要集成芯片:总体方案设计数字钟由振荡器、分频器、计数器、译码显示、报时等电路组成。

其中振荡器和分频器组成标准秒信号发生器,直接决定计时系统的精度。

由不同进制的计数器、译码器和显示器组成计时系统。

将标准秒信号送入采用60进制的“秒计数器”,每累计60sec就发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60min,发出一个“时脉冲”,该信号将被送到“时计数器”。

“时计数器”采用12或24进制计数器,可实现对一天12h 或24h的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过6位7段译码显示器显示出来,可进行整点报时,计时出现误差时,可以用校时电路校时、校分。

数字钟的原理框图如图2.1所示。

图2.1 数字钟原理框图各个部分的电路设计(1)秒脉冲产生电路秒脉冲产生电路在此例中的主要功能有两个:一是产生标准脉冲信号,二是可提供整点报时所需要的频率信号。

可用1Hz的秒脉冲时钟信号源替代。

V11 Hz5 V图2.2 1Hz的秒脉冲时钟信号源(2)秒、分、时计时器电路秒计时器本质上为对1Hz的秒脉冲时钟信号源进行60进制计数的计数器,其由一个10进制计数器(个位)和一个6进制计数器(十位)串接组成。

个位与十位计数器之间采用同步级联复位方式,将个位计数器的进位输出端RCO接至十位计数器的时钟信号输入端CLK,完成个位对十位计数器的进位控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子技术课程设计题目:①组装收音机②钟控定时电路姓名:柴琦学号:2008026102班级:通信081 指导教师:张俊星逄凌滨开设学期:2010 -2011 学年第 1 学期大连民族学院机电信息工程学院课设报告一、收音机部分1.收音机原理HX108-2型7管半导体收音机频率范围:525~1605KHZ;输出功率:100mW(最大);扬声器:φ57mm,8Ω;电源:5号电池二节。

由图知,整机中含7只三极管,因此称为7管收音机。

其中,三极管V1为变频管,V2、V3为中放管,V4为检波管,V5为低频前置放大管,V6、V7为低频功放管。

天线回路选出所需电台信号,经变压器B1耦合到变频管V1基极。

与此同时,由变频管V1、振荡线圈B2、双联同轴可变电容C1B等元器件组成的共基调射型变压器反馈式本机振荡器,其本振信号经电容C3注入到变频管V1发射极。

电台信号与本振信号在变频管V1中进行混频,混频后,V1管集电极电流中将含有一系列组合频率分量,其中包含本振信号与电台信号的差频(465KHZ)分量,经过中周B3(内含谐振电容),选出所需中频(465KHZ)分量,并耦合到中放管V2基极。

图中电阻R3是用来进一步提高抗干扰性的,二极管VD3是用以限制混频后中频信号振幅(即二次AGC)。

中放由V2、V3等元器件组成的两级小信号谐振放大器。

通过两级中放将混频后所获得的中频信号放大后,送入下一级检波器。

检波器由三极管V4(相当于二极管)等元件组成的大信号包络检波器。

检波器将放大的中频调幅信号还原为所需音频信号,经耦合电容C10送入后级低频放大器进行放大。

检波过程中,除产生所需音频信号之外,还产生反映输入信号强弱的直流分量,由检波电容之一C7两端取出后,经R8、C4组成的低通滤波器滤波后,作为AGC电压加到中放管V2基极,实现反向AGC。

即当输入信号增强时,AGC电压降低,中放管V2的基极偏置电压降低,工作电流IE将减小,中放增益随之降低,从而使得检波器输出的电平能够维持在一定的范围。

低放部分由前置放大器和低频功率放大器组成。

由V5组成的变压器耦合式前置放大器将检波器输出的音频信号放大后,经输入变压器B6送入功率放大器进行功率放大。

功率放大器由V6、V7等元器件组成,它们组成了变压器耦合式乙类推挽功率放大器,将音频信号功率放大到足够大后,经输出变压器B7耦合去推动扬声器发声。

其中R11、VD4用来给功放管V6、V7提供合适偏置电压,消除交越失真。

2.安装调试步骤1、对元器件清单目录表检查元件是否齐全;2、认识识别各种元器件以及认清其作用;3、学习收音机调频、调幅的工作原理;4、元器件的焊接、安装(安装时应检查元器件的好坏)5、检查各级晶体管的型号,安装位置和管脚是否正确;检查各级中周的安装顺序,初次级的引线是否正确;检查电解电容的引线正负接法是否正确;分段烧制的磁性天线线圈的初次级安装位置是否正确;6、做一些基本的调试,按黑、白、黄的顺序调试是音量、音质达到最好;7、把应该固定的地方牢固的封住;8、把焊接好的电路板与外壳组装;3.三极管各点的静态电位计算值V1: 电流0.2mA Ve=0.4V Vb=1.1V Vc=1.38V;V2: 电流0.6mA Ve=0.09V Vb=0.79V Vc=1.41V;V3: 电流1.5mA Ve=0.0765V Vb=0.7765V Vc=1.4V;V5: 电流4mA Ve= 0 V Vb=0.7V Vc=0.52V;V6: 电流0.35mA Ve= 0 V Vb=0.7V Vc= 3 V;V7: 电流0.35mA Ve= 0 V Vb=0.7V Vc= 3 V;测量值V1: 电流0.2mA Ve=0.35V Vb=0.91V Vc=1.33V;V2: 电流0.6mA Ve=0.01V Vb=0.68V Vc=1.31V;V3: 电流1.5mA Ve=0.06V Vb=0.65V Vc=1.29V;V5: 电流4mA Ve= 0 V Vb=0.73V Vc=0.48V;V6: 电流0.35mA Ve= 0 V Vb=0.65V Vc= 3.2 V;V7: 电流0.35mA Ve= 0 V Vb=0.65V Vc= 3.2 V;4.总结与体会在课程设计的第一周我们在老师的安排下进行了收音机的焊接,首先由老师讲解焊接过程中的一些注意事项,和之前的一些准备工作包括原理图的讲解和电原理图一些参考元件的数值上的计算,之后自己动手组装一台HX108-2七管半导体收音机,并对其进行了调试。

通过本次电子工艺实习——组装、焊机、调试HX108-2七管半导体收音机教学内容后,我有了一下几点收获:(1)大体上对收音机的安装、焊接、调试及生产过程初步有了一定的了解;(2)学会了利用工艺文件独立进行整机的焊接和调试,并达到产品的质量要求;(3)初步掌握了一定的焊接技术与简单电路元器件的识别、装配,并对故障的诊断和排除有了一定的检测和解决故障的能力及方法,为今后对复杂电路的分析奠定基础;(5)熟悉了电子电路安装、焊接工艺的基本知识和原理,初步掌握了焊接技术并且能正确的安装、焊接一台正规的收音机,并能对其进行相关的调试;在实习中,我锻炼了自己的动手技巧和能力,提高了解决问题的能力。

对于电阻阻值的识别,我们要了解电阻上各条彩色线的含义,电阻上第一、二条线都代表数字,第三条线代表0的个数,第四条线代表误差。

电容分为片电容和电解电容,电解电容长导线的为正极,短导线的为负极,对于片电容的识别,要了解它身上数字的含义:第1、2位数字代表电容值,第3位代表0的个数。

片电容不分正负极。

对于三极管,要分清基极b、集电极c、发射极e,用之前用万用表测一下是否正常,并与焊接前计算的三极管电压进行比对,并记录下来,对于二极管,我们要分清其正负极。

红色的那头为正极,黑色的那头为负极。

虽然在实习中会遇到难题,但是从中我学到了很多,使自己的动手能力也有所提高,我想在以后的理论学习中我就能够明白自己的学习方向,增进专业知识的强化。

二、课题设计部分1.课题设计任务及要求(1).、计时时间为0~99秒,用两位LED分别显示;(实做采用一位LED)(2)、定时控制时间的输入方式为串行输入(可用计数器实现),范围是0~99秒,用两位LED分别显示;(3)、手动开关控制系统的复位、时间的寄存及启动,定时时间到要有声响报警,报警时间为5秒;(4)、在计时开始前“0”=“0”不应报警,只有在启动后时间到才可以报警。

(5)、全部电路的控制开关不能超过2个。

2.方案论证及总体电路框图控制器是由74194和7402组成,每来一个脉冲,就把0移位进去,脉冲由按键1控制。

计数器和寄存器由4518构成,先是定时器,当按键1按到第二下时,开始按按键2,4518高脚就会显示要定时的数,当再按一下按键1时,4518的低脚就会开始计时。

比较器是由7485构成,把比较器和寄存器相应脚连到7485上,当相等时7485的6脚就会输出1,不相等时输出0。

保持电路是由4518构成,当到了定时时间时,比较电路控制蜂鸣器响,让计数器停止计数,控制响5秒,当响了5秒时保持电路在控制计数器重新计数。

钟控定时电路框图3.单元电路设计CD4060应用电路图控制电路计数电路定时电路蜂鸣5秒电路4.安装与调试(1)检查试验箱及各元件性能,(2)在试验箱上按仿真图进行连线并与原理图进行对比(3)检查无误后通电,观察实验现象是否与预期结果相一致(4)调整试验箱现象与结果一致,同时修正改变电路(5)进行焊接前的元件排布,和布线(6)焊接时要每部分单独焊接,每部分测试成功后,在进行整体连接(7)功能都实现后,把焊接面用纸包起来,在纸上画出每部分(8)然后再进行调试5.电路功能与操作说明(1)功能:定时时间到要有声响报警,报警时间为5秒;(2)操作:上电后,先按按键1进行清零,然后再按按键1给一个定时信号开始定时,按按键2进行定时,然后按按键1,开始计数,当计时的数与定时数相等时,蜂鸣器开始响,响五秒后蜂鸣器停止,计时器继续计时。

6.总体电路及器件清单(1)设计图仿真图(2)1个74L S00 1个74LS02 1个74LS08 2个74LS741个74LS85 2个4060 2个4511 2个45181个晶振1个10兆电阻2个数码显示管2个1千欧电阻2个10千欧电阻1个100千欧电阻1个蜂鸣器3个小灯2个开关1个三极管1个20pF电容1个30pF电容7.总结与体会这次课程设计应该是第一次完全由自己设计电路图,并在不断修改调试中完善整个电路要求,试验箱的连接看似简单,但之前的准备工作尤为重要,要细心、耐心的完成每一步的检查程序,首先要检查好导线的完好测试导线是否有短路、断路的现象,其次要检查实验箱我们用到的每一芯片的功能是否完好,接着在电路的连接时就不会有其他额外的事故,连接过程要两个人配合好确保每一根导线都连接到相应的两端,完成一部分就要进行相应的性能测试,是否满足我们的要求,如不满足及时改正,整个电路相连接好并测试我有的功能后,就可以开始进行线路板的拍不分配,一起带到合理的布线、美化,并节省焊接过程中一些不必要的麻烦,焊接时要注意对应好相应的引脚,出错很容易导致整个线路板的浪费,整个设计、仿真、模拟、实焊都要求精益求精,有一点错误都会导致前功尽弃,而我在焊接中也遇到许多困难比如焊好线路板之后,由于漏焊导致蜂鸣器不响,数码管显示不清晰等,还有开关不好用,原因是忘记接入输入信号,在老师的帮助下,我逐一克服困难,最后完成整个课程设计,也是我受益匪浅。