低频数字式相位测量仪 vhdl fpga

基于单片机和FPGA的低频数字相位测量仪研究

105相位是交流信号的重要参数之一,相位差的测量是电子和电力测量中经常遇到的问题,如何获得准确的相位差已经越来越重要。

例如在电力系统中,当电网合闸时,要求两电网信号的相位必须相同,如果信号相位不同,就会在电网中产生很大的冲击电流,造成严重事故。

因此,相位测量在信号提取、检测、处理等方面有重要的应用意义。

随着数字电子技术在实际生产应用中的发展,由数字逻辑电路组成的控制系统已经逐渐成为现代测量、检测技术中的主要方法。

本文介绍了一种基于单片机和FPGA的低频数字相位测量仪,该设计具有测量精度高、反应速度快、稳定性好、读数方便等明显特点。

[1]图1 FPGA 数据采集电路系统框图图2 FPGA 数据采集电路仿真图基于单片机和FPGA 的低频数字相位测量仪研究郭贝贝 仝战营(河南机电高等专科学校 河南新乡 453002)摘要:本文设计了一种基于单片机和FPGA的低频数字相位测量仪。

系统采用等精度的测量方法可以较精确的测量出两个相同频率信号的相位差。

系统中的FPGA部分进行数据采集,单片机部分对数据进行处理,并在数码管上显示待测信号的相位差。

与传统相位测量仪相比,本系统有处理速度快、稳定性高、性价比高等优点。

关键词:单片机 FPGA 低频相位差设计中图分类号:TP216文献标识码:A文章编号:1007-9416(2012)06-0105-02106取相应的数据,最后再将模板文件转换为html网页文件呈现给用户,供浏览器端查阅。

4、实现功能定制报表提供了能源成本管理、能源平衡管理、能源台账管理、能源介质结算管理、能源介质综合管理等方面的管理、呈现和分析,提供了对各个工序、厂区在每天、每月、每年产品和副产品产出、原料消耗、能源生产与消耗的成本情况和能源折标情况;对能源管理过程中的重要能源介质进行深入的分析和管理;提供了公司各个主要能源介质在结算时的采购情况和外售情况并对公司内的各系统在公司各个主体工序、重要耗能设备的消耗量、单耗情况进行了统一综合的统计和分析。

基于FPGA控制的低频数字式相位测量仪研究(胡云朋

基于FPGA控制的低频数字式相位测量仪研究胡云朋(电子信息工程学院微电子及固体电子专业 113114310)摘要:提出了一种基于Verilog开发的低频数字相位测量仪设计。

系统以FPGA为核心,构成完备的测量系统,可以对20Hz-20KHz的频率范围的信号进行频率、相位等参数的精确测量。

硬件结构简单,程序简单可读性强,与传统电路相比,具有处理速度快、稳定性高、性价比高的特点。

关键字:相位测量仪、FPGA、Verilog语言目录第一章研究背景 (3)第二章方案设计与论证 (3)一、设计指标要求 (3)二、设计方案论证 (4)第三章系统硬件设计 (6)硬件电路的设计: (6)第四章软件系统设计 (7)一、FPGA完成的任务 (7)二、FPGA芯片内部电路框图 (7)三、FPGA的Verilog程序及仿真结果 (7)第五章结束语 (11)参考文献: (11)第一章 研究背景随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

相位是交流信号的重要参数。

相位差的测量是电子和电力测量中经常遇到的问题,测量两路同频信号的相位差在工程上有着重要的意义。

其测量方法可分为模拟和数字方法两种:传统依靠模拟器件的方法,如二极管鉴相法、脉冲计数法等,测量系统复杂、需专用器件、硬件成本高、而且精度不高。

随着集成电路的发展,利用大规模集成电路来完成各种高速、高精度电子仪器的设计,已经成为一种行之有效的方法。

采用这种技术制成的电子仪器电路结构简单、性能可靠、测量精确且易于调试,而且精度明显高于一般的模拟式测量。

在工业和民用场合, 为了对各种低频信号进行测量分析,常常引入相位测量仪。

低频数字式相位测试仪在工业领域中是经常用到的一般测量工具,例如在电力系统中,当电网合闸时,要求两电网电信号的相位相同,如果两路信号的相位不同,会出现很大的电网冲激电流,对供电系统产生巨大的破坏力,因此,精确测量出两个信号的相位差是非常重要的。

低频数字式相位测量仪

低频数字式相位测量仪摘要本系统以AT89S51单片机为核心,由相位测量仪、移相网络、数字式移相信号发生器三个模块组成。

数字式相位测量仪实现了对20Hz到20KHz的峰-峰值为1V到5V的正弦信号、方波信号等进行精确的测频、测相的功能;移相网络则采用RC移相网络来实现,在100Hz、1KHz、10KHz三种情况下,通过切换电阻值的方法实现了最大相移±45°的调整。

被测信号的相位差、频率则通过数码管显示。

整个系统设计硬件结构简单,软件采用汇编语言实现,程序简单可读性强,效率高。

与传统的电路系统相比,具有处理速度快、稳定性高、性价比高的特点。

关键词:低频;相位测量;单片机;可编程逻辑器件AbstractThis is a system whose core is based on AT89S51 single chip and is composed of three modules by the phase measurement device,phase-shifting network,digital phase shifting generator.The digital phase measurement device can precisely measure the frequency and phase of sine signal from 20Hz to 20KHz with the voltage amplitude from 1Vp-p to 5Vp-p. The phase-shifting network uses the RC net. By changing the value of resistor, it can make the phase shift 45 degrees at most . The data are displayed on numberal displayer. Hardware is simple and software is realized by compiling language.Compared with traditional circuit, it has many advantages of faster processing speed, good stability and high ratio between property and price.Key W ords: low frequency; phase measure; MCU; CPLD目录1 引言 (1)2 总体设计 (2)2.1 方案论证 (2)2.1.1 移相网络 (2)2.1.2 数字式相位测量仪 (3)2.1.3 数字式移相信号发生器 (6)3 硬件设计 (8)3.1 移相网络 (8)3.2 相位测量仪 (11)3.2.1 信号调理部分 (11)3.2.2 CPLD测量模块 (12)3.2.3 单片机控制模块 (13)4 软件设计 (17)4.1 CPLD测量模块 (17)4.2 单片机控制模块 (19)5制作和调试 (21)5.1 硬件部分的制作和调试 (21)5.2 软件部分的制作和调试 (22)6总结 (22)致谢 (24)参考文献 (25)附录1 系统实物图 (26)附录2 实验原理图 (27)附录3 毕业设计作品说明书 (28)1 引言随着科学技术的突飞猛进的发展,电子技术广泛的应用于工业、农业、交通运输、航空航天、国防建设等国民经济的诸多领域中,而电子测量技术又是电子技术中进行信息检测的重要手段,在现代科学技术中占有举足轻重的作用和地位。

低频数字式相位测量仪设计报告

低频数字式相位测量仪摘要本低频数字式相位测量仪由数字式移相信号发生器、模拟移相网络、数字相位测量部分以及人机接口等模块组成。

数字式移相信号发生器采用双路时统DDS技术,基于FPGA实现。

相位测量部分采用基于相位—时间变换的等精度测量技术,由单片机控制CPLD实现。

本系统硬件设计应用了EDA技术,软件设计采用基于C51的模块化设计技术,总体上较好地完成了题目基本和发挥部分的要求。

并增加了扫频、扫相、扫幅及相位打印功能,扩展了模拟移相器移相范围及相位显示形式。

关键词:时统DDS数字移相等精度数字测相 FPGA/CPLD一.方案论证与选择根据题目要求本系统可分解为数字式移相信号发生器、模拟移相网络及相位测量部分等三个模块。

模拟移相网络已由题目给出,以下对另两部分实现方案进行论证。

(一)数字式移相信号发生器方案论证方案一:用PLL 频率合成技术产生正弦波信号,将其通过FFT 变换到频域,再乘以一定的旋转因子,即相当于时域的时延(移相)。

不同的旋转因子对应不同的移相,但对不同频率的输入信号进行移相时,需要调整滤波器参数或改变滤波器采样率。

前者运算量较大,后者需要用到PLL 技术,硬件繁琐。

方案二:应用单片机产生移相信号。

将正弦波信号数字化,形成数据表存入FLASH 或EPROM 等非易失性存储芯片中,单片机交叉读出该数据表中的数据,形成两路波形信号,送往两路D/A ,得到两路具有一定相位差的正弦波。

这种处理方式的实质是将数据地址的偏移量映射为信号间的相位差。

但受单片机速度限制,这种方法难以产生较高频率的信号。

方案三: 采用DDS 技术产生移相信号。

1、DDS 频率合成DDS 频率合成的基本原理是使用稳定的参考时钟源作为抽样时钟,通过地址累加来寻址波形查找表得到波形的幅度抽样值,然后将抽样值经D/A 转换和低通滤波输出平滑的波形。

图1.1给出了DDS 的工作原理框图。

相位累加器波形查找表DAC低通滤波器系统时钟K频率控制字NN Hf0图1.1 DDS 基本原理框图图1.1中相位累加器(N 为位数)以频率控制字K 为间隔对地址进行累加,将累加结果的最大有效位数H 作为ROM 查找表的地址(ROM 中存储波形数据),通过D/A 转换将所查地址单元的波形数据转化为模拟量,再由低通滤波器滤出其基波成分。

低频数字相位测量仪

摘要低频数字相位测量仪向文芳摘要设计了一个基于现场可编程门阵列(FPGA)和AT89S51单片机相结合的低频数字相位测量仪。

本系统可分为三大基本组成部分:数据测量电路、数据运算控制电路和数据显示电路。

FPGA数据测量电路的功能就是实现将待测正弦信号的周期、相位差转变为19位的数字量。

单片机数据运算控制电路的功能就是负责读取FPGA测量到的数据,并根据这些数据计算待测正弦信号的频率及两路同频正弦信号之间的相位差,同时通过功能键切换,显示出待测信号的频率和相位差。

数据显示电路的设计采用静态显示方式,显示电路由8片1位串入8位并出的74LS164芯片组成。

本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

整个系统发挥了FPGA和单片机各自的优势,具有高速而可靠的测控能力,具有比较强的数据处理能力,键盘输入及显示控制比较灵活,系统可扩展性比较好,整个系统性能价格比比较好。

关键词FPGA,单片机,频率,相位差,相位测量仪攀枝花学院本科毕业设计(论文)ABSTRACTABSTRACTThe paper has designed a low frequency digital phase measuring instrument based on the system which communicates FPGA and the microcontroller (AT89S51). This system includes three modules: data measuring electric circuit, data operation control circuit and data display electric circuit. The function of the FPGA data measuring electric circuit is transforms the cycle, phase difference of the two input sine signals to be 19 bit of digital data. The function about microcontroller data operation control circuit is to read the data which FPGA has measured, and according to these data computations the frequency and the phase difference between two group sine signals which have same frequencies, simultaneously through the function key switch, displaying the frequency and phase difference of the two group sine signals. The data display electric circuit’s design adopting the static state display mode, the display circuit is composed by 8 pieces of 74LS164 chip (8-bit Serial-Input/Parallel-Output shift Register).This system plans with FPGA and the microcontroller, framing the phase measuri ng instrument’s dominant measurement and control system. The overall system has displayed FPGA and the microcontroller respective superiority, has high speed and the reliable measurement and control ability, and has the quite strong capacity of deal with data, the keyboard entry and the display control also quite flexible. The system’s extension is quite good. All the superiorities make the good performance price ratio of this low frequency digital phase measuring instrument.Keywords FPGA, Microcontroller, Frequency, Phase difference, Phase measurement system目录摘要 (I)ABSTRACT (II)1绪论 (1)1.1课题背景 (1)1.1.1 研究意义 (1)1.1.2 研究现状、水平及发展趋势 (1)1.2课题核心 (3)2系统设计 (4)2.1设计要求 (4)2.2总体设计思想 (4)2.3总体测量思路 (5)3设计方案 (6)3.1测量方案 (6)3.1.1频率测量 (6)3.1.2 相位差测量 (8)3.2正弦波信号发生器设计 (9)3.3信号整形电路的设计 (9)3.3.1 方案论证 (9)3.3.2 关于四电压比较器LM339 (11)3.4移相网络设计 (11)3.4.1 性能要求 (11)3.4.2 方案论证 (11)4 FPGA数据测量电路的设计 (14)4.1设计原理 (14)4.1.1 设计思路 (14)4.1.2 FPGA数据测量电路的测量原理 (14)4.1.3 精度分析 (14)4.2 FPGA概述 (15)4.3设计平台 (16)4.3.1 软件设计平台 (16)4.3.2 硬件设计平台 (17)4.4具体软件设计 (18)4.4.1 QuartusⅡ应用 (18)4.4.2 软件设计方法 (19)4.4.3 模块功能描述和系统原理图 (19)4.4.4 运行监测程序 (20)4.4.5 程序中端口及引脚定义 (20)4.5具体硬件连接 (21)4.5.1 与单片机的连接 (21)4.5.2其它连接 (22)5单片机数据运算控制电路的设计 (23)5.1设计思路 (23)5.1.1 硬件电路和原理图 (23)5.1.2 精度分析 (24)5.2 AT89S51概述 (24)5.2.1 AT89S51单片机 (24)5.2.2 AT89S51特性 (24)5.2.3 引脚排列 (25)5.2.4 引脚功能 (26)5.2.5 低功耗运行模式 (28)5.3设计平台 (29)5.3.1 软件设计平台 (29)5.3.2 硬件设计平台 (29)5.4软件设计思路 (29)5.4.1 主程序设计 (29)5.4.2 数据读取模块 (30)5.4.3 频率计算模块 (30)5.4.4 相位差计算模块 (31)5.4.5 显示模块 (31)6数据显示部分 (33)6.1显示电路的设计 (33)6.1.1 设计思路 (33)6.1.2 LED显示器接口原理 (33)6.1.3 显示电路图 (34)6.2关于74LS164 (34)6.2.1 74LS164概述 (34)6.2.2 连接说明 (34)6.2.3 数码管的编码 (35)7系统仿真和硬件验证 (36)7.1系统的仿真 (36)7.1.1 系统调试的方法 (36)7.1.2 系统调试的软/硬件 (36)7.1.3 系统的有关仿真 (36)7.1.4 仿真分析 (37)7.2系统的硬件验证 (39)7.2.1 单元电路的调试 (39)7.2.2 系统的联合调试 (40)7.2.3 系统的硬件验证 (40)7.3数据测试 (40)7.3.1 数据记录 (40)7.3.2 数据分析 (41)结论 (42)附录A:本设计FPGA的VHDL源代码 (45)附录B:单片机的汇编语言源程序清单 (51)附录C:适合于QuartusⅡ的部分器件引脚对照表 (67)附录D:系统总图 (67)参考文献 (70)致谢 (71)1 绪论1.1 课题背景1.1.1 研究意义在电子测量技术中,频率测量是最基本的测量之一。

采用VHDL语言与FPGA芯片实现平均值相位差计的设计

采用VHDL语言与FPGA芯片实现平均值相位差计的设计相位差的测量在研究网络特性中具有重要作用,如何快速、精确地测量相位差已成为生产科研中的重要课题。

测量相位差的方法很多,有集成电路设计的,也有采用数字信号处理(DSP)实现的,现在普遍采用电子计数式的方法。

但传统的瞬时相位差计,需要用锁相环电路锁相跟踪被测信号,廉价的低端FPGA芯片无法完成,同时被测信号的频率范围也限制在低频内,为了解决上述问题,提出平均值相位差计的原理,并采用VHDL 语言编程,FPGA芯片实现,巧妙地简化了锁相跟踪电路,扩展了被测信号的频率范围,提高相位差计的性能参数,也大大降低了成本,具有很高的性价比。

1 总体设计方案与基本原理数字式相位计的基本原理如图1所示,两路同频率的信号U1,U2通过脉冲形成电路,产生两路过零脉冲信号U1,U2,再经过相位差提取电路得到宽度等于两信号相位差对应时间宽度的信号Ug,最后通过闸门、计数、显示就可以测量到相位差的数值。

各点的波形分析如图2中的U1,U2,U3,Ud,Ug,Ufc及Uf。

其中:U1,U2是同频率不同相位的两个信号;△T表示两个同频率正弦波过零点的时间差;Ufc为经过倍频的计数标准脉冲。

设被测信号的频率为f,信号的周期为T,若倍频数为360×10k,则fc=360×10kf,假设在1个信号周期内能计到的Ufc脉冲数为N,在相位差所对应的时间△T内计到的Uk脉冲数为n,那么N=fcT=360×10kfT=360×10k,所以相位差ψ=360△T/T=360n/N=10-bn,即计数值n的数字就代表两信号中相位差的度数;6表示小数点的位置。

这种测量原理,必须保持fc与f的严格比例关系,因此必须用到锁相倍频电路,若用FPGA 实现,就必须选用含锁相环的高端芯片,成本提高;同时,由于.fc=360×lOkf,若f=1 MHz,测量精度为±1°,则fc=3 600 MHz,系统的频率就相当高,目前的FPGA芯片几乎无法实现。

基于FPGA的低频数字相位测量仪的设计

1引言关于低频数字相位测量系统的设计与实现方法,提出了以单片机最小系统和复杂可编程逻辑芯片为核心的电路设计模型。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂,易受外界干扰影响以及准确度较差的缺点,限制了其作用进一步发挥。

近年来,随着计算机硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多关注,并且得到了较快发展。

同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有广泛的应用,如电工领域中的电机功角测试,介质材料的损耗角的确定等。

因此相位差测量有着广泛的实用价值。

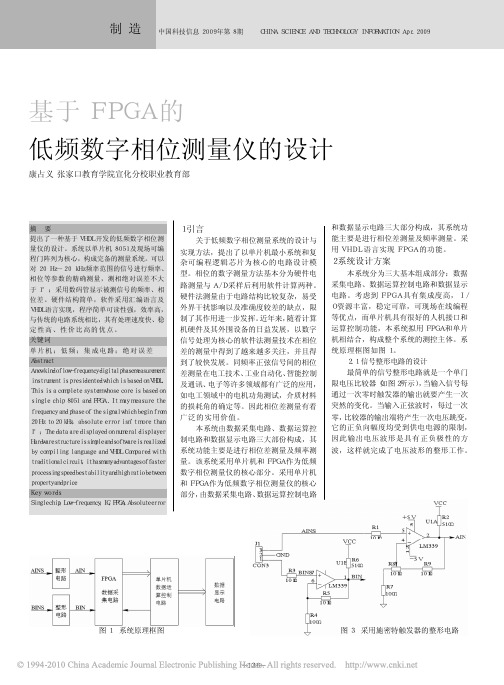

本系统由数据采集电路、数据运算控制电路和数据显示电路三大部份构成,其系统功能主要是进行相位差测量及频率测量。

该系统采用单片机和FPGA作为低频数字相位测量仪的核心部分。

采用单片机和FPGA作为低频数字相位测量仪的核心部分,由数据采集电路、数据运算控制电路基于FPGA的低频数字相位测量仪的设计康占义 张家口教育学院宣化分校职业教育部图1 系统原理框图图3 采用施密特触发器的整形电路和数据显示电路三大部分构成,其系统功能主要是进行相位差测量及频率测量。

采用VHDL语言实现FPGA的功能。

2系统设计方案本系统分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA和单片机相结合,构成整个系统的测控主体。

系统原理框图如图1。

2.1 信号整形电路的设计最简单的信号整形电路就是一个单门限电压比较器(如图2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

电气电子毕业设计100竞赛论文——低频数字式相位测量仪

电子竞赛——低频数字式相位测量仪目录摘要 (1)一.设计任务与设计要求 (2)1.1 设计任务 (2)1.2 设计要求 (2)1.2.1 基本要求 (2)1.2.2 发挥部分 (2)二.相位测量 (2)2.1相位测量方案选择与论证 (3)2.2相位测量框图 (3)2.3相位测量硬件电路设计与器件选择 (3)2.3.1 相位比较电路 (4)2.3.2 CPU与外围电路 (5)2.3.3键盘与显示电路 (6)2.3.4直流稳压电源电路 (6)2.4 测试方法与测试结果 (7)2.4.1 相位测试方法 (7)2.4.2相位测试结果 (7)2.4.3测量工具 (7)三.频率测量方案 (7)3.1 方案选择与论证 (7)3.2 硬件电路设计 (9)3.3 频率测量测试及结果 (9)3.4 测量工具 (10)四.移相网络电路参数计算 (10)4.1移相网络电路框图 (10)4.2移相网络电路参数计算 (10)4.3 移相网络测试 (12)4.4 测量工具 (12)五.发挥部分数字移相信号发生器 (12)5.1方案论证 (12)六.系统软件设计 (15)七.总的结果分析 (16)八.结论 (16)附录:移相信号发生器电路 (17)10-03设计题目:低频数字式相位测量仪参赛队员:刘传登韩春鹏王忠杰指导教师:车新生摘要本设计实现的是对两列信号的相位差的精确测量并数字显示测量结果。

为达到要求的精度本设计采用了将相位转换为直流电压的间接测量方法。

用16位A/D对输出的直流电压进行采样,送入单片机进行相位显示。

这样就使得相位差就具有足够高的分辨度,完成了任务要求。

在单片机P89C51实现以上功能的同时,利用单片机中的多位计数器/定时器对输入信号进行等精度频率测量。

为测量方便,又制作了移相网络电路,设计了移相信号电路和应用程序。

整个装置具有原理简单,测量精度高,测量范围宽,测量结果显示直观的特点。

关键词:相位测量等精度测量移相网络一.设计任务与要求1.1设计任务设计并制作一台低频相位测量系统,包括相位测量仪,数字式移相信号发生器和移相网络三部分。

【电子设计】低频数字式相位测量仪制作报告

低频数字式相位测量仪制作报告摘要本系统由低频数字相位频率测量仪,输入移相网络和数字式移相信号发生器组成。

利用CPLD,单片机控制模块实现了高精度的频率相位测量。

数字式移相信号发生器采用直接数字频率合成(DDFS)技术,输出频率范围宽,控制精度高。

由于在DDFS系统中采用了双D/A输出形式,信号幅度采用数字调节方式,输出信号幅度稳定。

移相网络的输入采用了自动增益控制(AGC),实现了高达48dB的宽范围输入,实现信号的自动稳幅输出。

此外,本系统友好的人机界面,合理实用的功能扩展,使整个系统更利于实际使用。

一.方案设计与论证1.相位频率测量部分方案一:对输入的两路正弦信号分别进行过零比较,并对生成的两路方波信号进行异或运算,得到占空比与相位差成正比的脉冲信号。

将该正弦送入单片机系统,对信号的脉宽进行测量,经计算得到输入的两路正弦信号的相位差。

单片机系统直接对过零比较后的方波信号计数,得到输入信号频率。

经单片机系统处理后,显示测量结果。

此方案电路相对简单,容易实现,但是受到单片机工作速度的限制,精度不高。

方案二:对输入的两路正弦信号分别进行过零比较,并对生成的两路方波信号进行异或运算,得到占空比与相位差成正比的脉冲信号。

由CPLD对相位差脉冲信号和频率信号进行计数,将计数结果送入单片机,单片机经过简单计算后显示测量结果。

此方案可以提高系统的测量精度,单片机要实现的功能相对简单,可以实现友好的人机界面。

缺点是电路相对复杂,成本较高。

系统框图详见图2-1。

综合考虑,这里采用了方案二。

2.移相网络部分方案一:直接采用题目中提供的参考电路。

此电路实现简单,但对于不同幅度的输入信号,不能做到自动稳幅输出。

对于小信号输入,无法满足题目输出峰-峰值0.3~5V的要求,除非采用可变增益放大器,在没有单片机控制的情况下,显然带来诸多不便。

方案二:以题目中提供的参考电路为基础,在信号输入前端加入自动增益控制电路(AGC),以适应各种幅度的信号输入。

基于FPGA与单片机控制技术结合的低频数字相位测量仪设计

设计(论文)题目:基于FPGA与单片机控制技术结合的低频数字相位测量仪设计一、基本任务及要求一)基本任务1)硬件设计:输入信号整形电路、单片机外围电路、显示电路;2)软件设计:数据采集模块的VHDL硬件描述语言实现、单片机控制程序。

二)要求1)本设计本分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

其功能为对两路输入正弦信号(1~5 V范围内变化)进行频率和相位测量(相位测量绝对误差≤2)及数字显示(相位读数为0~359.9,分辨力为0.1),其频率测量范围:20 Hz~20 kHz。

2)通过该项目设计,完成各单元模块的硬件设计,给出其设计过程和电路图;对数据采集、单片机控制模块分别给出VHDL硬件描述语言实现的源程序和控制程序,并进行程序调试及电路的仿真、给出仿真结果。

二、进度安排及完成时间:目录摘要 (IV)Abstract (V)第1章绪论.......................................................... - 1 -1.1 课题研究的背景................................................ - 1 -1.2 本课题的主要研究工作.......................................... - 3 - 第2章主要理论及技术................................................ - 4 -2.1 频率测量...................................................... - 4 -2.2 相位测量...................................................... - 5 -2.3 单门限电压比较器原理.......................................... - 6 -2.3.1 LM339介绍............................................... - 6 -2.4 FPGA可编程控制技术............................................ - 7 -2.4.1 FPGA 器件的设计开发流程.................................. - 7 -2.4.2 FPGA工作原理............................................ - 8 -2.4.3 VHDL语言介绍........................................... - 8 -2.4.4 Quartus II软件介绍...................................... - 9 -2.5 AT80C51单片机介绍............................................ - 10 - 第3章系统设计思路................................................. - 11 -3.1 系统总体设计思路............................................. - 11 -3.2 设计方案..................................................... - 11 - 第4章硬件设计...................................................... - 13 -4.1 信号整形电路的设计........................................... - 13 -4.2 FPGA数据采集电路的设计....................................... - 14 -4.3 单片机数据运算控制电路的设计................................. - 15 -4.4 数据显示电路的设计........................................... - 16 -4.4.1 LCD12864介绍........................................... - 16 -4.4.2 基本特性................................................ - 16 -4.4.3管脚说明................................................ - 16 -4.4.4 基本用途................................................ - 17 -4.4.5数据显示电路............................................ - 17 - 第5章软件设计...................................................... - 18 -5.1 FPGA数据测量电路............................................. - 18 -5.2 分频器模块................................................... - 19 -5.3 控制信号模块................................................. - 20 -5.4 数据检测模块................................................. - 22 -5.5 数据锁存模块................................................. - 23 -5.6 数据选择模块................................................. - 24 -5.7 FPGA数据测量模块总体设计..................................... - 26 -5.7 单片机数据运算控制电路....................................... - 27 - 结束语............................................................... - 30 - 参考文献............................................................. - 31 - 致谢............................................................... - 32 - 附录............................................................... - 33 - FPGA数据采集程序................................................. - 33 - 数据显示程序..................................................... - 36 - 硬件总电路图..................................................... - 40 -低频数字式相位测量仪的设计摘要:基于过零检测法原理,以单片机89C51和可编程逻辑器件CPLD为核心,从数据采集﹑数据运算控制、显示等电路功能电路设计,实现了一个低频数字式相位测量仪系统。

低频数字式相位测量仪 vhdl fpga

低频数字式相位测量仪栏目树形导航| 首页 | 学习中心 | 课设与竞赛 | 下载中心 | 图片现场 | 技术留言 | 关于我们 | 本站提供 ||竞赛与设计首页|关于竞赛|历届电子竞赛题目|竞赛作品选编|历届仪器元器件范围|单片机课程设计|您现在的位置:奔跑的单片机 >> 课设与竞赛 >> 竞赛作品选编 >> 信息正文用户登录新用户注册低频数字式相位测量仪热【字体:小大】低频数字式相位测量仪作者:lintel 信息来源:本站原创点击数:8523 更新时间:2006-4-3低频数字式相位测量仪(C题)摘要:设计了一基于现场可编程门阵列(FPGA)的低频数字式相位测量仪。

该测量仪包括数字式移相信号发生器和相位测量仪两部分,分别完成移相信号的发生及其频率、相位差的预置及数字显示、发生信号的移相以及移相后信号相位差和频率的测量与显示几个功能。

其中数字式移相信号发生器可以产生预置频率的正弦信号,也可产生预置相位差的两路同频正弦信号,并能显示预置频率或相位差值;相位测量仪能测量移相信号的频率、相位差的测量和显示。

两个部分均采用基于FPGA的数字技术实现,使得该系统具有抗干扰能力强, 可靠性好等优点。

关键词:现场可编程门阵列(FPGA)数字式相位测量仪Abstrct:The paper deals with designing of a low frequency phasemeasurement system based on FPGA technology. This phase measurement system includes two modules---a signal generator and a phase measurementsubsystem. Its signal generator module can generate a sin wave withpreconcerted frequency and two waves with preconcerted phase difference. It can continuously change signal phases through phase shifting. And its phase measurement subsystem has functions of measuring signal phase andphase difference of two signals. All of its three modules adopt digitaltechnology base on FPGA. This system is characteristic of its strongantijamming performance and fine stability.Key words:FPGA/Digital/Phase measurement system目录0 引言 (3)1 系统设计1.1设计要求 (3)1.2 方案比较 (4)1.2.1相位测量仪方案 (4)1.2.2移相网络方案 (4)1.2.3正弦波信号发生器方案 (5)1.2.4频率测量方案 (5)1.2.5幅度控制方案 (6)1.2.6滤波选择方案 (6)1.2.7显示界面方案 (7)1.3方案论证 (7)1.3.1总体思路 (7)1.3.2设计方案 (7)2单元电路设计2.1相位测量仪 (7)2.1.1原理方框图 (7)2.1.2相位测量原理 (8)2.1.4电路图分析………………………………………………………………………………2.2数字式移相信号发生器 (10)2.2.1 数字移相原理 (10)2.2.2正弦波信号发生 (10)3 软件设计3.1用VHDL编写程序…………………………………………………………………………123.2 程序流程 (12)3.2.1 等精度频率测量的实现 (12)3.3程序清单仿真 (13)4 系统测试……………………………………………………………………………………145 结论…………………………………………………………………………………………17参考文献……………………………………………………………………………………17 附录 (17)0.引言同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有着广泛的应用,如电工领域中的电机功角测试,介质材料损耗角的确定等。

毕业设计论文《低频数字式相位测量仪》

毕业设计论文《低频数字式相位测量仪》摘要该数字式相位测量仪以单片机 (89c52) 为核心 , 通过高速计数器 CD4040 为计数器计算脉冲个数从 , 而达到计算相位的要求 , 通过 8279 驱动数码管显示正弦波的频率,不采用一般的模拟的振动器产生 , 而是采用单片机产生 , 从而实现了产生到显示的数字化 . 具有产生的频率精确 , 稳定的特点 . 相移部分采用一般的 RC 移相电路 , 节省了成本。

一方案论证与比较 :1 常见正弦信号的测量方法 :方案一:采用模拟分离元件如二极管,三极管等非线性元件,实现频率的测量,检相的功能,使用起来方便,价格便宜,但采用分离元件由于分散性太大,不便于集成及数字化,而且测量误差大。

方案二:采用集成的检相器,检频器实现频率及相位的测量。

这种方法的实现框图如下:这种方法虽然可实现比较精确的测量,但由于模拟信号易受外界的干扰,不易调节,无法实现智能化,数字化的缺点,一般在要求较低的情况下使用。

方案三:此方案采用高速信号发生器产生 20MHz 的高频信号,其主要特点是采用 CD4040 高频计数器结合单片机,利用计数脉冲实现测量相位与频率的目标。

这种方法克服了模拟电路的缺点,实现了数字化与集成化。

本设计采用了这种方法。

这种方案的组成框图:二系统总体设计按照题目要求,我们设计的相位测量系统包括三部分:正弦波产生系统(包括频率调整电路),移相电路和相位显视系统,其总体框图如下:三各部分硬件电路设计及参数计算1、正弦波产生电路•方案一:利用 8038 芯片或 MAX038 可以实现压控的函数发生器通过改变少量的外围元件,可实现正弦波,方波,三角波,并可实现频率调节,但采用模拟器件由于元件分散性太大,即使使用单片函数发生器,参数也与外部元件有关,外接的电阻,电容对参数影响很大,因而产生的频率稳定度差,精度低,抗干扰能力差,调节困难,成本也高。

而且灵活性差,不能实现智能化。

基于FPGA的数字式相位测量仪的设计与制作 推荐

基于FPGA的数字式相位测量仪的设计与制作摘要:本设计给出了基于FPGA核心的数字式相位测量的基本原理与实现方案,实现的是对两列信号的相位差的精确测量并数字显示测量结果。

该系统利用可编程逻辑器件为主系统芯片,用VHDL对其进行设计开发,系统由相位测量仪、数字式移相信号发生器和移相网络三个模块构成,整个装置具有原理简单,测量精度高,测量结果显示直观的特点。

本次设计在EDA软件开发平台MAX+PLUSⅡ上利用硬件描述语言VHDL进行设计编程。

关键词:FPGA/CPLD、VHDL、测相仪FPGA-based digital phase-measuring instrument design and production Abstract: The design is based on the FPGA core of the digital phase measurement and realization of the basic principles of the programme, the realization of the two signals in the phase of precision measurement and statistics show that the measurement results. The system of programmable logic devices based system chips, with their VHDL design and development, the system by the phase-measuring instrument, the digital shift believe that the phase-shifting, generator and a network of three modules, the device has a simple theory, measurement High-precision measurement results show that the visual characteristics. The design of the EDA software development platform MAX + PLUS Ⅱ on the use of hardware description language VHDL design programming.Key words: FPGA / CPLD;VHDL;measurement of the instrument第1章绪论1.1 EDA技术概述1.1.1 引言20世纪末,电子技术获得飞速发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力推动社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

低频数字相位测量仪..

现代电子学实验报告实验题目:低频数字相位测量仪姓名:年级:2012级指导教师:完成日期:2015年10月14日原创性声明本人声明本实验报告涉及的电路图、程序代码均为自己设计,没有抄袭他人的成果。

特此声明!声明人:目录摘要 (1)一、系统设计要求与技术指标 (2)二、方案选择与可行性论证 (2)2.1总体框架 (2)2.2频率测量 (2)2.3相位测量 (3)三、系统模块设计 (3)3.1信号整形电路的设计 (3)3.2 FPGA数据采集电路的设计 (5)3.2.1硬件部分 (5)3.2.2精度分析 (5)3.2.3软件部分 (5)3.3、单片机数据运算控制电路的设计 (6)3.3.1硬件部分 (6)3.3.2软件部分 (7)3.4、数据显示电路的设计 (10)3.4.1显示部分设计方案 (10)3.4.2数据显示电路 (10)四、参考资料 (12)附录 (13)主要器件介绍 (13)FPGA数据采集程序 (15)硬件电路图 (21)低频数字式相位测量仪的设计摘要:基于过零检测法原理,以单片机89C51和可编程逻辑器件CPLD为核心,从数据采集﹑数据运算控制、显示等电路功能电路设计,实现了一个低频数字式相位测量仪系统。

在此过程中,采用MCU与FPGA相结合的方案,将软件部分为数据采集、运算、控制和单片机控制显示两部分,充分发挥单片机具有的控制、运算能力强,FPGA数据采集速度快的特点来对实现各个模块功能进行程序设计,同时还对相关程序进行调试和仿真,验证了其可行性,使其性能接近最优。

而对硬件电路设计包括采用施密特触发器组成的整形电路、显示电路、FPGA 芯片及单片机外围电路等,实现了对频率信号频率、相位差的显示,同时配合系统完成数据采集、运算、控制等功能。

在上述基础上,本文还对有关频率信号的频率、相位测量技术及理论进行了研究和分析,对FPGA可编程芯片、单片机控制等的运用进行了学习,从而为课题研究奠定了理论基础。

基于FPGA控制的低频数字式相位测量仪研究

法 两 种 : 统 依 靠 模 拟 器 件 的 方 法 , 二 极 传 如 管 鉴 相法 、脉 冲计 数 法 等 , 量 系统 复 杂 、 测 需专 用 器件 、硬 件 成本 高 、而 且精 度不 高 。 随 着 集 成 电 路 的 发 展 , 用 大 规 模 集 成 电 利

本 系 统 充 分 利 用 FPGA 对 数 据 的 高 速 处 理 能 力 , 使 得 系 统 设 计 高 效 , 可 靠 。 与 传 统 相 位 测 量 仪 相 比 , 系 统 具 有 处 理 速 度 快 、稳 该 定 性 高 、 性 价 比 高 , 易 于 实现 的优 点 。该 系统 具 有 较 强 的 实 用 价 值 和 良好 的 工 程 应 用 前 景 。 [ 键 词 ] 杂 可 编 程 逻 辑 器 件 低 频 相 位 测 量 仪 F 关 复 PGA VH DL 语 言 [ 图分类号1 2 中 x5 【 献标 识 码 】 文 A [ 章 编 号 l0 7 4 6 ( 0 0 0 - 0 6 4 文 10 -9 l 2 l ) 1 0 7 -0

视 频 字 符叠 加 的 一 种较 好 的 选 考 文献 ]

【 】 应 用 电 视 一一设 备 原 理 与 工 程 实 践 1 Ⅸ 京 : 子 工 业 出 版 社 》 中 国 广 播 电 视 设 北 电 备 工 业 协 会 应 用 电 视 专 业协 会 . [】Ga mi NC. GP 2 / 0 tc n cl 2 r nI S 5 2 e h ia

・

应 用研 究 ・

基于 F G P A控 制 的低 频数 字 式 相位 测量 仪研 究

王 振 红 于 磊

( 方 工 业 大 学 信 息 工 程 学 院 北 京 1 0 4 ) 北 0 1 4

低频数字式相位测量仪.

低频数字式相位测量仪摘要:本系统设计了一个基于现场可编程门阵列(FPGA)的低频数字式相位测量仪。

该测量仪包括数字式移相信号发生器和相位测量仪两部分,分别完成移相信号的发生及其频率、相位差的预置及数字显示、信号的移相以及移相后信号相位差和频率的测量与显示等功能。

其中数字式移相信号发生器可以产生预置频率的正弦信号,也可产生预置相位差的两路同频正弦信号,并能显示预置频率或相位差值;相位测量仪能对移相信号的频率、相位差的测量和显示。

两个部分均采用基于FPGA的数字技术实现,使得该系统具有抗干扰能力强, 可靠性好等优点。

关键词:现场可编程门阵列(FPGA),数字式移相信号发生器,相位测量仪1.总体方案设计根据系统的设计要求,本系统可分为三大基本组成部分:数据采集电路、数据运算控制电路和数据显示电路。

考虑到FPGA/CPLD具有集成度高,I/O资源丰富,稳定可靠,可现场在线编程等优点,而单片机具有很好的人机接口和运算控制功能,本系统拟用FPGA/CPLD 和单片机相结合,构成整个系统的测控主体。

如图1.1。

图1.1 系统原理框图1.1整形电路方案一:最简单的信号整形电路就是一个单门限电压比较器(如图1.2所示),当输入信号每通过一次零时触发器的输出就要产生一次突然的变化。

当输入正弦波时,每过一次零,比较器的输出端将产生一次电压跳变,它的正负向幅度均受到供电电源的限制,因此输出电压波形是具有正负极性的方波,这样就完成了电压波形的整形工作。

图1.2 采用单门限触发器的整形电路方案二:为了避免过零点多次触发的现象,我们使用施密特触发器组成的整形电路。

施密特触发器在单门限电压比较器的基础上引入了正反馈网络。

由于正反馈的作用,它的门限电压随着输出电压Uo 的变化而改变,因此提高了抗干扰能力。

本系统中我们使用两个施密特触发器对两路信号进行整形,电路图如图1.3所示。

图1.3 采用施密特触发器的整形电路1.2 相位测量方案方案一:采用脉冲填充计数法。

基于FPGA的相位测量仪

2.FPGA芯 片 介 绍

本 次 设 计采 用 杭 州 康 芯 电子 有 限 公 司生 产 的 以Altera公 司 生 产 的FPGA器件 ::Cyclone EP1c3T144c8N为主 体 的适 配 板作 为 数 据 采 集 电路 硬 件 的 核 心 , 该适 配 板 提 供 了 一片 集 成 度 为 1 5万 门的 EP1C3T144C8N,一个 20MHz时钟 ,一个 JATG下载 模 式 , 一个AS 模 式下 载 口,使 用起 来十 分 方便 。其 中它 所提 供 的20MHz时 钟可 直 接用 来 作为 数据 采集 时所 用 的基准 信 号源 。

3.设 计 的 理 论 分 析

FPGA数据 采 集 电路 测 量 正 弦波 信 号频 率 的 原理 是 :在 正 弦波

整 形后 得 到 的 方 波 信 号 的一 个 周 期为 Tc秒 的数 据采 样 信 号 进 行 计 数 ,其计 数结 果乘 以1/Tc,就 是被 测 正弦波 的频 率 ,单 位为 Hz。测 量 正弦 波 信 号 周 期 的原 理 是 :在 正 弦波 信 号 整 形后 得 到 的方 波 信 号 的一个 周期 为Tc秒 的数 据采 样信 号进 行计 数 ,其计 数 结果乘 以Tc 秒 ,就 是 被 测 信 号 的周 期 ,单 位 为秒 。测 量 两 个 同 频信 号 的相 位 差 ,关 键 就是 要测 出两个 同频 正弦 波信 号 起 点的 时 间差 △t,若 △t 测 出,则 根据 :A a=At×360。/t即可求 出相 位差 △a,因此 其测 量原 理与 测量 正弦 波信 号周 期 的原理 相似 。

基于FPGA的低频数字式相位测量仪

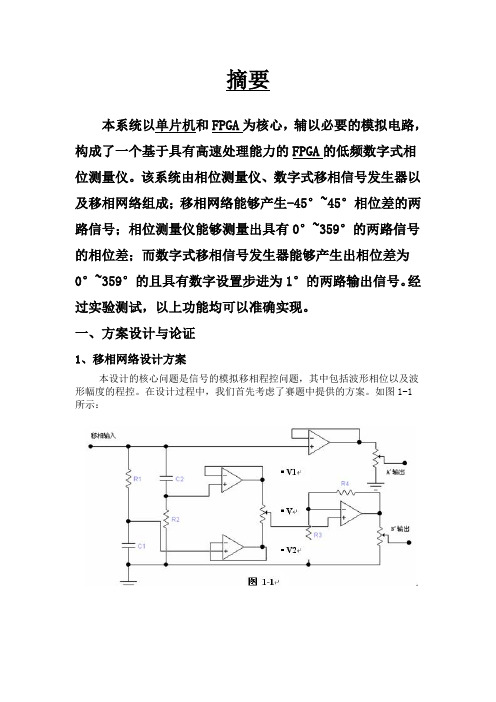

摘要本系统以单片机和FPGA为核心,辅以必要的模拟电路,构成了一个基于具有高速处理能力的FPGA的低频数字式相位测量仪。

该系统由相位测量仪、数字式移相信号发生器以及移相网络组成;移相网络能够产生-45°~45°相位差的两路信号;相位测量仪能够测量出具有0°~359°的两路信号的相位差;而数字式移相信号发生器能够产生出相位差为0°~359°的且具有数字设置步进为1°的两路输出信号。

经过实验测试,以上功能均可以准确实现。

一、方案设计与论证1、移相网络设计方案本设计的核心问题是信号的模拟移相程控问题,其中包括波形相位以及波形幅度的程控。

在设计过程中,我们首先考虑了赛题中提供的方案。

如图1-1所示:该模拟电路主要采用高、低通电路的临界截止点来产生极值相位的偏移。

当高、低通电路的截止频率等于输入信号频率时,根据其幅频特性,信号波形所产生的相位分别为45°和-45°,恰好满足赛题要求的连续相移范围-45°~45°的调节。

由于高、低通电路在截止点时会产生幅度的衰减,故电路在后级加了放大电路,且采用了电压串联负反馈的方式提高了输入阻抗并降低了输出阻抗,电路最后还设计有调幅装置,能够很好地满足A、B输出的正弦信号峰—峰值可分别在0.3V—5V范围内变化。

综上所述,该移相网络能够满足赛题的所有要求,且电路设计简单、易行,故我们直接采用了这种方式来产生模拟的相移输出。

2、数字式移相信号发生器设计方案本单元设计的关键在于两个波形相位差的准确定位,在设计中我们综合考虑了两种实现方案:方案一:采点式相位确定。

利用相位范围0°~ 360°设定每个波形含有360个点,即每一点都对应一度,以保证相位的精确定位。

但当输入波形频率较高时,FPGA中的 DDFS对该波形的采点数将降低,该方法也不再适合;此外360个点的波形很难利用DDFS的地址线准确产生,由于DDFS在运行时地址是不断向下扫描的,其多余地址中的零数据也将同样会被显示输出,使得波形不再准确。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

低频数字式相位测量仪栏目树形导航| 首页 | 学习中心 | 课设与竞赛 | 下载中心 | 图片现场 | 技术留言 | 关于我们 | 本站提供 ||竞赛与设计首页|关于竞赛|历届电子竞赛题目|竞赛作品选编|历届仪器元器件范围|单片机课程设计|您现在的位置:奔跑的单片机 >> 课设与竞赛 >> 竞赛作品选编 >> 信息正文用户登录新用户注册低频数字式相位测量仪热【字体:小大】低频数字式相位测量仪作者:lintel 信息来源:本站原创点击数:8523 更新时间:2006-4-3低频数字式相位测量仪(C题)摘要:设计了一基于现场可编程门阵列(FPGA)的低频数字式相位测量仪。

该测量仪包括数字式移相信号发生器和相位测量仪两部分,分别完成移相信号的发生及其频率、相位差的预置及数字显示、发生信号的移相以及移相后信号相位差和频率的测量与显示几个功能。

其中数字式移相信号发生器可以产生预置频率的正弦信号,也可产生预置相位差的两路同频正弦信号,并能显示预置频率或相位差值;相位测量仪能测量移相信号的频率、相位差的测量和显示。

两个部分均采用基于FPGA的数字技术实现,使得该系统具有抗干扰能力强, 可靠性好等优点。

关键词:现场可编程门阵列(FPGA)数字式相位测量仪Abstrct:The paper deals with designing of a low frequency phasemeasurement system based on FPGA technology. This phase measurement system includes two modules---a signal generator and a phase measurementsubsystem. Its signal generator module can generate a sin wave withpreconcerted frequency and two waves with preconcerted phase difference. It can continuously change signal phases through phase shifting. And its phase measurement subsystem has functions of measuring signal phase andphase difference of two signals. All of its three modules adopt digitaltechnology base on FPGA. This system is characteristic of its strongantijamming performance and fine stability.Key words:FPGA/Digital/Phase measurement system目录0 引言 (3)1 系统设计1.1设计要求 (3)1.2 方案比较 (4)1.2.1相位测量仪方案 (4)1.2.2移相网络方案 (4)1.2.3正弦波信号发生器方案 (5)1.2.4频率测量方案 (5)1.2.5幅度控制方案 (6)1.2.6滤波选择方案 (6)1.2.7显示界面方案 (7)1.3方案论证 (7)1.3.1总体思路 (7)1.3.2设计方案 (7)2单元电路设计2.1相位测量仪 (7)2.1.1原理方框图 (7)2.1.2相位测量原理 (8)2.1.4电路图分析………………………………………………………………………………2.2数字式移相信号发生器 (10)2.2.1 数字移相原理 (10)2.2.2正弦波信号发生 (10)3 软件设计3.1用VHDL编写程序…………………………………………………………………………123.2 程序流程 (12)3.2.1 等精度频率测量的实现 (12)3.3程序清单仿真 (13)4 系统测试……………………………………………………………………………………145 结论…………………………………………………………………………………………17参考文献……………………………………………………………………………………17 附录 (17)0.引言同频率正弦信号间的相位差测量在电工技术、工业自动化、智能控制及通讯、电子等许多领域都有着广泛的应用,如电工领域中的电机功角测试,介质材料损耗角的确定等。

因此,相位差测量技术有着广泛的实用价值。

相位的数字测量方法基本分为硬件电路测量与A/D采样后利用软件计算两种。

硬件法测量由于电路结构比较复杂、易受外界干扰影响以及准确度较差的缺点,限制了进一步发挥它的作用。

近年来,随着计算机软硬件及其外围设备的日益发展,以数字信号处理为核心的软件法测量技术在相位差的测量中得到了越来越多的关注,并取得了较快发展。

FPGA是20世纪90年代发展起来的大规模可编程逻辑器件,随着EDA(电子设计自动化)技术和微电子技术的进步,FPGA的时钟延迟可达到ns级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景;并且FPGA具有高集成度、高可靠性,几乎可将整个设计系统下载于同一芯片中,实现所谓片上系统,从而大大缩小其体积。

本设计基于FPGA设计的低频数字式相位测量系统,具有很好的发展前景和开发价值。

1 系统设计1.1 设计要求一、任务设计并制作一个低频相位测量系统,包括相位测量仪、数字式移相信号发生器和移相网络三部分,示意图如下:二、要求1、基本要求(1)设计并制作一个相位测量仪(参见图1)a.频率范围:20Hz~20kHz。

b.相位测量仪的输入阻抗≥100kΩ。

c.允许两路输入正弦信号峰-峰值可分别在1V~5V范围内变化。

d.相位测量绝对误差≤2°。

e.具有频率测量及数字显示功能。

f.相位差数字显示:相位读数为0°~ 359.9°,分辨力为0.1°。

(2)参考图2制作一个移相网络a.输入信号频率:100Hz、1kHz、10kHz。

b.连续相移范围:-45°~+45°。

c.A'、B'输出的正弦信号峰-峰值可分别在0.3V~5V范围内变化。

2.发挥部分(1)设计并制作一个数字式移相信号发生器(图3),用以产生相位测量仪所需的输入正弦信号,要求:a.频率范围:20Hz~20kHz,频率步进为20Hz,输出频率可预置。

b.A、B输出的正弦信号峰-峰值可分别在0.3V~5V范围内变化。

c.相位差范围为0~359°,相位差步进为1°,相位差值可预置。

d.数字显示预置的频率、相位差值。

(2)在保持相位测量仪测量误差和频率范围不变的条件下,扩展相位测量仪输入正弦电压峰-峰值至0.3V~5V范围。

(3)用数字移相信号发生器校验相位测量仪,自选几个频点、相位差值和不同幅度进行校验。

(4)其它。

1.2 方案比较1.2.1 相位测量方案该方案的关键问题是相位测量方法的选择。

方案一:采用直读法,可直接读出被测相位差的数值。

用单片机作为核心控制部件, 如图1.2.1示由于受限于时钟频率和若干指令运算的限制,测相速度较慢,无法满足高速、高精度的测相要求。

单片机89C52相位显示A输入B输入FPGA测量控制仪相位显示A输入B输入图1.2.1 以单片机为核心控制部件测量相位图1.2.2 以FPGA为核心控制部件测量相位方案二:采用直读法,用FPGA作为核心控制部件,其优点是方便、快速、可随时显示。

其原理框图如图1.2.2示。

并且结合现场可编程门阵列FPGA(Field Programmable GateArray)具有集成度高、高速和高可靠性的特点,使频率的测频范围可达到0.1Hz~100MHz,测频全域相对误差恒为1/1 000 000。

为满足基本部分和发挥部分的要求,采用第二种方案进行设计。

1.2.2 移相网络方案方案一:直接对模拟信号进行移相,如阻容移相,变压器移相等。

采用这种方式设计的移相器有许多不足之处,如:输出波形受输入波形的影响,移相操作不方便,移相角度随所接负载和时间等因素的影响而产生漂移等。

采用阻容移相网络的基本原理简述如下:由RC电路的原理可知,不同频率的正弦波电压通过RC电路时,输出端的电压幅度和相位,都与输入不同。

图1.2.3中画出了两种简单的移相电路。

图1.2.3 (a )相位超前的相移网络(b)相位滞后的相移网络图1.2.3中的模和相角分别为:(a)(b)式(1-2-1)由式(1-2-1)中的(a)和(b)式可知,两种相移网络都是随着频率的改变,单节RC电路中所产生的相移在0 o~90o之间变化。

因此,采用一个相位超前的相移网络和一个相位滞后的相移网络,可满足连续相移范围:-45o ~+45o的要求。

但电路复杂,难于调试。

方案二:采用数字移相技术,其核心是:先将模拟信号或移相角数字化,经移相后再还原成模拟信号。

该方案精度高,且易于传送。

原理框图如图1.2.4示。

模拟信号或移相角A/D、移相、D/A模拟信号图1.2.4 采用数字移相技术实现信号移相权衡以上两方案的优缺点,本设计选用第二种方案。

1.2.3正弦波信号发生器方案方案一:采用模拟分立元件或单片机压控函数发生器完成设计。

通过调整外部元件可以改变输出频率,产生正弦波。

但是采用模拟器件分散性大,产生的频率稳定性较差、精度低、抗干扰能力差、成本也比较高。

方案二:采用直接数字频率合成,用单片机作为核心控制部件,能达到较高的要求,实现各种波形输出,但受限于运算位数及运算速度,产生的波形往往需通过滤波器才能达到满意效果,并且频率可调范围小,很难得到较高频率。

方案三:采用直接数字频率合成,用FPGA器件作为核心控制部件,精度高稳定性好,得到波形平滑,特别是由于FPGA的高速度,能实现较高频率的波形。

且控制上更方便,可得到较宽频率范围的波形输出,步进小。

显然第三种方案具有更大的优越性、灵活性,所以采用第三种方案进行设计。

1.2.4 频率测量方案方案一:采用测周期法。

需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns(如图1.2.5示)。

这种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Ns有关。

为了保证测试精度,测周期法仅适用于低频信号的测量。

方案二:采用测频法。

测频法就是在确定的闸门时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx(如图1.2.6),则被测信号的频率为:fx=Nx/Tw。