Task Sequencing for Optimizing the Computation Cycle in a Timed Computation Model

计算机组成原理 英文

计算机组成原理英文Computer Organization Principles。

Computer organization is a fundamental topic in the field of computer science and engineering. It deals with the structure and components of a computer system, including the hardware and software aspects. Understanding the principles of computer organization is essential for computer professionals to design, develop, and optimize computer systems. In this document, we will explore the key concepts and principles of computer organization.1. Basic Concepts of Computer Organization。

At the core of computer organization are the concepts of data representation, storage, processing, and communication. Data representation involves encoding and interpreting data in various forms, such as binary, decimal, and hexadecimal. Storage refers to the mechanisms for storing and retrieving data, including primary storage (RAM) and secondary storage (hard drives, SSDs). Processing involves the manipulation of data through arithmetic and logic operations, as well as control flow. Communication encompasses the exchange of data between different components of a computer system, such as input/output devices, memory, and processors.2. Architecture and Organization。

课程安排英文作文

课程安排英文作文Title: Crafting a Well-Structured Course Schedule。

Designing a course schedule is akin to composing a symphony, where each element harmonizes to create acohesive and enriching experience for learners. In this essay, we will delve into the nuances of crafting a well-structured course schedule, focusing on key principles and considerations.Firstly, a well-designed course schedule should reflect clear learning objectives. These objectives serve asguiding beacons, illuminating the path for both instructors and students. By delineating what knowledge and skills learners are expected to acquire, educators can tailor the schedule to ensure comprehensive coverage of the curriculum.Moreover, a balanced distribution of topics isessential to maintain engagement and prevent cognitive overload. The schedule should be structured in a way thatintroduces concepts progressively, building upon foundational knowledge before delving into more complex ideas. This gradual progression not only facilitates comprehension but also fosters a sense of accomplishment as students master each stage of learning.In addition to content sequencing, the allocation of time plays a pivotal role in course scheduling. Each topic should be accorded sufficient time for thorough exploration and discussion, while also allowing for flexibility to address unexpected challenges or delve deeper into areas of particular interest. Furthermore, periodic assessments interspersed throughout the schedule serve as checkpoints, enabling both students and instructors to gauge progress and identify areas for improvement.Another critical aspect of course scheduling is the integration of diverse instructional methods and resources. While traditional lectures have their merits, incorporating interactive activities, group discussions, and multimedia presentations can enhance engagement and cater to different learning styles. By fostering a dynamic learningenvironment, educators can stimulate curiosity and foster collaborative learning experiences.Furthermore, the schedule should factor inopportunities for reflection and feedback. Scheduled breaks provide invaluable moments for students to consolidatetheir learning, recharge their mental faculties, andreflect on their progress. Similarly, allocating time for peer review sessions and one-on-one consultations allowsfor personalized feedback, nurturing a culture of continuous improvement and self-reflection.Equally important is the consideration of external factors that may impact the course schedule. Anticipating potential disruptions such as holidays, guest speakers, or extracurricular events enables educators to proactively adjust the schedule to accommodate such occurrences without compromising learning outcomes.In conclusion, crafting a well-structured course schedule is a multifaceted endeavor that requires careful planning, foresight, and adaptability. By aligning learningobjectives, balancing content distribution, optimizing time allocation, integrating diverse instructional methods, and incorporating opportunities for reflection and feedback, educators can orchestrate a transformative learning journey for their students. As we navigate the intricacies of course scheduling, let us strive to create schedules that inspire, engage, and empower learners to reach theirfullest potential.。

光伏功率预测英文作文

光伏功率预测英文作文英文:PV power prediction is an important task in the field of renewable energy. It helps to optimize the use of solar energy and improve the efficiency of photovoltaic systems. There are various methods to predict PV power, such as physical models, statistical models, and machine learning models.Physical models are based on the physical principles of solar radiation and the behavior of PV cells. They require detailed information about the weather conditions, solar irradiance, and PV module characteristics. Statistical models use historical data to identify patterns and trends in PV power output. They are less complex than physical models but may not be accurate in predicting sudden changes in weather conditions.Machine learning models are becoming increasinglypopular for PV power prediction. They use algorithms to learn from historical data and make predictions based on the learned patterns. They can adapt to changing weather conditions and improve their accuracy over time. However, they require a large amount of data for training and may not be suitable for small-scale PV systems.In my experience, I have found that a combination of physical and machine learning models works best for PV power prediction. The physical model provides a baseline prediction based on the weather conditions and PV module characteristics, while the machine learning model adjusts the prediction based on the historical data and current weather conditions.For example, let's say we want to predict the PV power output for a rooftop solar system on a cloudy day. The physical model may predict a lower power output due to the reduced solar irradiance, but the machine learning model may adjust the prediction based on the historical data of similar weather conditions and predict a slightly higher power output.Overall, PV power prediction is a complex task that requires a combination of different models and a large amount of data. It is important for optimizing the use of solar energy and improving the efficiency of photovoltaic systems.中文:光伏功率预测是可再生能源领域的重要任务。

软件项目计划英语作文

软件项目计划英语作文Title: Software Project Planning。

In today's digital era, software projects play apivotal role in various industries, ranging from finance to healthcare. Efficient planning is the cornerstone of successful software development endeavors. This essay delineates the key aspects of software project planning, elucidating its significance, phases, and best practices.Significance of Software Project Planning。

Software project planning is paramount as it sets the project's trajectory, ensuring alignment withorganizational goals and client requirements. A meticulously crafted plan serves as a roadmap, guiding the development team through various stages while mitigating risks and uncertainties. Moreover, it facilitates resource allocation, budget estimation, and timeline management, thereby enhancing project transparency and stakeholdersatisfaction.Phases of Software Project Planning。

11到20平方数计算方法

11到20平方数计算方法There are many different ways to calculate the square of a number, and each method has its own advantages and disadvantages.计算一个数的平方有很多种不同的方法,每种方法都有其优缺点。

One of the simplest methods to calculate the square of a number is by multiplying the number by itself. For example, to calculate 11 squared, you would simply multiply 11 by 11, which equals 121.计算一个数的平方最简单的方法之一就是将这个数乘以它本身。

例如,要计算11的平方,你只需将11乘以11,结果就是121。

Another method to calculate the square of a number is by using the concept of repeated addition. For instance, to find the square of 11, you could add 11 to itself 11 times, which would also give you the answer of 121.计算一个数的平方的另一种方法是使用重复加法的概念。

例如,要找到11的平方,你可以将11加上它本身11次,这样也会得到121的答案。

The process of computing squares can also be made easier by recognizing certain patterns and making use of them. For example, when finding the square of a number that ends in 5, you can take advantage of the fact that the ones place of the answer will alwaysbe 25 and then use simple multiplication to find the rest of the answer.通过认识到某些模式和利用它们,可以使计算平方的过程变得更容易。

从科学角度看英语作文

从科学角度看英语作文Title: The Scientific Perspective on English Composition。

English composition, often regarded as a creative endeavor, can also be analyzed from a scientific standpoint. In this essay, we delve into the intersection of scienceand English writing, exploring how principles fromcognitive psychology, linguistics, and communication theory can enhance our understanding and practice of English composition.Cognitive Psychology:Cognitive psychology offers insights into the cognitive processes involved in writing. When we compose in English, we engage in a series of complex mental activities,including planning, organizing, and revising. Understanding these processes can improve our writing efficiency and quality.One key concept from cognitive psychology is working memory. Working memory, a temporary storage system, plays a crucial role in writing as it holds information needed for composing sentences and structuring ideas. By optimizing working memory through strategies like chunking information or using external aids like outlines, writers can enhance their writing fluency and coherence.Moreover, cognitive psychology emphasizes the importance of metacognition, the awareness and control of one's thought processes. Writers who reflect on their writing strategies, set goals, and monitor their progress are better equipped to overcome challenges and improvetheir writing skills over time.Linguistics:Linguistics provides a scientific framework for understanding the structure and function of language, which is fundamental to English composition. By studyinglinguistic principles, writers can develop a deeperappreciation for the mechanics of language and make more informed choices in their writing.One area of linguistics relevant to English composition is syntax, the study of sentence structure. Understanding syntactic rules helps writers construct grammaticallycorrect and logically coherent sentences. Additionally, knowledge of syntax enables writers to vary sentence structure for stylistic purposes, creating rhythm and emphasis in their writing.Furthermore, linguistics offers insights into semantics, the study of meaning in language. Effective communication relies on conveying meaning accurately, and anunderstanding of semantics allows writers to choose words and phrases that convey their intended message precisely. Additionally, awareness of semantic ambiguity helps writers avoid misunderstandings and ambiguities in their writing.Communication Theory:Communication theory explores how messages aretransmitted and understood between individuals, providing valuable insights for English composition. By applying communication principles, writers can craft more persuasive and engaging compositions that resonate with their audience.One fundamental concept in communication theory is audience analysis. Writers must consider the characteristics, preferences, and expectations of their audience to tailor their message effectively. By adapting their language, tone, and content to suit their audience, writers can enhance the relevance and impact of their writing.Moreover, communication theory emphasizes theimportance of clarity and coherence in writing. Clear and well-organized writing facilitates comprehension and retention, allowing the audience to grasp the intended message more easily. Techniques such as logical sequencing, transitional devices, and concise expression contribute to clarity and coherence in English composition.In conclusion, approaching English composition from ascientific perspective enriches our understanding of the cognitive, linguistic, and communicative processes involved. By incorporating insights from cognitive psychology, linguistics, and communication theory, writers can refine their writing skills, enhance their communication effectiveness, and ultimately, produce more compelling and impactful compositions.。

AcceptanceList:验收单

Regular Paper

B219 Sudeep Roy, Akhil Kumar, and Ivo Pro vazník, Virtual screening, ADMET profiling, molecular docking and dynamics approaches to search for potent selective natural molecule b ased inhibitors against metallothionein-III to study Alzheimer’s disease

B357 Qiang Yu, Hongwei Huo, Xiaoyang Chen, Haitao Guo, Jeffrey Scott Vitter, and J un Huan, An Efficient Motif Finding Algorithm for Large DNA Data Sets

B244 Ilona Kifer, Rui M. Branca, Ping Xu, Janne Lehtio, and Zohar Yakhini, Optimizing analytical depth and cost efficiency of IEF-LC/MS proteomics

B276 Yuan Ling, Yuan An, and Xiaohua Hu, A Symp-Med Matching Framework for Modeling and Mining Symptom and Medication Relationships from Clinical Notes

B333 Mingjie Wang, Haixu Tang, and Yu zhen Ye, Identification and characterization of accessory genomes in bacterial species b ased on genome comparison and metagenomic recruitment

手机英语作文教程

手机英语作文教程Title: A Comprehensive Guide to Writing English Compositions on Mobile Phones。

In today's digital era, mobile phones have become an integral part of our daily lives, influencing various aspects including communication, education, and entertainment. Consequently, mastering English composition skills tailored for mobile platforms is increasingly essential. This comprehensive guide aims to provide insights and strategies for crafting effective English compositions on mobile phones.1. Understanding the Medium: 。

Writing on mobile phones necessitates awareness of the medium's limitations and strengths. Mobile screens are smaller compared to traditional writing mediums, influencing readability and formatting choices. Additionally, typing on mobile keyboards may affect thespeed and accuracy of writing. Thus, acknowledging these factors is crucial for optimizing the composition process.2. Choosing the Right App: 。

电脑性能的重要性英语作文

电脑性能的重要性英语作文Title: The Significance of Computer Performance。

In today's digital age, the importance of computer performance cannot be overstated. From personal use to professional endeavors, the efficiency and capability of a computer system significantly impact various aspects of our lives. In this essay, we delve into the significance of computer performance and explore why it holds such paramount importance.Firstly, computer performance directly influences productivity. Whether you're a student completing assignments, a professional working on projects, or an entrepreneur managing a business, a fast and responsive computer enables you to accomplish tasks swiftly and efficiently. A high-performance computer reduces waiting times, minimizes delays in processing data, and enhances overall workflow efficiency. This increased productivity translates into saved time and improved outcomes,ultimately contributing to personal and professional success.Secondly, computer performance is crucial for handling resource-intensive tasks. With the rise of multimedia content, complex software applications, and demanding computational processes, modern computing tasks often require significant processing power and memory resources. Whether you're editing high-resolution videos, running advanced simulations, or engaging in data analysis, a computer with robust performance capabilities ensures smooth execution and optimal results. Without adequate performance, these tasks may become sluggish, prone to errors, or even infeasible, hampering creativity, research, and innovation.Moreover, computer performance plays a vital role in gaming and entertainment. The gaming industry continues to push the boundaries of graphics, physics, and artificial intelligence, delivering immersive experiences that demand powerful hardware for optimal performance. A high-performance computer not only enables gamers to enjoysmooth gameplay at high resolutions and frame rates butalso facilitates the use of virtual reality (VR) and augmented reality (AR) technologies, opening up new realmsof interactive entertainment. Beyond gaming, superior computer performance enhances the viewing experience of multimedia content, such as streaming high-definitionvideos and editing digital photographs, enriching leisure activities and creative pursuits.Furthermore, computer performance influences competitiveness in various fields. In sectors ranging from finance and engineering to healthcare and scientific research, the ability to process vast amounts of dataquickly and accurately is indispensable. Organizations that invest in high-performance computing infrastructure gain a competitive edge by accelerating decision-making,optimizing operations, and unlocking insights from data analytics. Whether it's predicting market trends, designing innovative products, or discovering new treatments,superior computing performance empowers individuals and organizations to stay ahead in a rapidly evolving landscape.Additionally, computer performance contributes to technological advancements and innovation. As computational capabilities improve, new possibilities emerge for tackling complex problems, driving scientific discoveries, and creating transformative technologies. From artificial intelligence and machine learning to quantum computing and genomic sequencing, breakthroughs in computing performance pave the way for groundbreaking innovations with far-reaching implications for society. By fostering a conducive environment for experimentation, exploration, and invention, high-performance computing fuels progress and propels us towards a brighter future.In conclusion, the importance of computer performance cannot be overstated in today's interconnected world. From enhancing productivity and enabling resource-intensivetasks to fueling gaming and entertainment experiences, superior computing performance permeates every aspect ofour lives. Moreover, it fosters competitiveness, drives innovation, and shapes the trajectory of technological advancement. As we continue to harness the power of computing technology, investing in and prioritizingcomputer performance will remain essential for unlocking new possibilities and realizing our full potential.。

Oracle Fusion Cloud Supply Planning 商业文档说明书

Planning

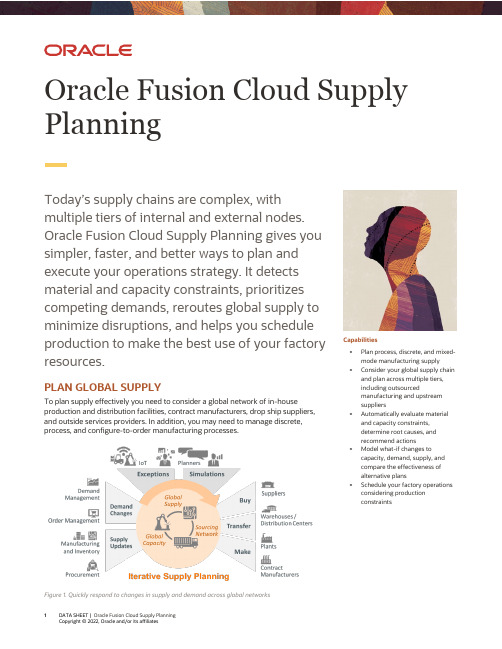

Today’s supply chains are complex, with multiple tiers of internal and external nodes. Oracle Fusion Cloud Supply Planning gives you simpler, faster, and better ways to plan and execute your operations strategy. It detects material and capacity constraints, prioritizes competing demands, reroutes global supply to minimize disruptions, and helps you schedule production to make the best use of your factory resources.

Schedule your factory operations considering production constraints

Figure 1. Quickly respond to changes in supply and demand across global networks

1 DATA SHEET | Oracle Fusion Cloud Supply Planning Copyright © 2022, Oracle and/or its affiliates

Automatically Evaluate and Select Alternatives

You may consider using alternate suppliers, substitute components, and other supply options to meet customer obligations when a disruption occurs. Supply Planning automatically evaluates all available options to overcome supply constraints to meet demand on time. It addresses material and resource constraints simultaneously to recommend alternative resources, alternate routings and bills-of-material, secondary material sources, and suppliers as needed.

他研究了水稻 英语作文

他研究了水稻英语作文Title: Exploring the Wonders of Rice: A Journey into Rice Research。

Rice, the staple food for more than half of the world's population, has been the focus of extensive research for centuries. In recent years, scientists have delved deeper into understanding this versatile grain, uncovering its genetic diversity, nutritional benefits, and ecological significance. This essay explores the fascinating world of rice research, highlighting its importance and the strides made in unraveling its mysteries.Understanding Genetic Diversity:One of the key areas of research in rice revolves around its genetic diversity. Scientists have been studying various rice varieties to identify genes responsible for traits such as yield, disease resistance, and tolerance to environmental stresses. By exploring the genetic makeup ofdifferent rice strains, researchers aim to develop improved varieties that can address the challenges faced by farmers worldwide.Unraveling Nutritional Benefits:Beyond its role as a staple food, rice offers a wealth of nutritional benefits. Research has shown that rice is a good source of carbohydrates, providing essential energyfor the body. Moreover, certain varieties of rice, such as brown and wild rice, are rich in vitamins, minerals, and dietary fiber, contributing to overall health and well-being. Scientists continue to explore ways to enhance the nutritional profile of rice through breeding and genetic modification.Exploring Ecological Significance:Rice cultivation plays a significant role in shaping ecosystems and landscapes. Wetland rice paddies provide habitat for diverse flora and fauna, contributing to biodiversity conservation. Additionally, rice fields serveas important carbon sinks, helping mitigate climate change by sequestering carbon dioxide from the atmosphere. Understanding the ecological dynamics of rice cultivationis crucial for sustainable agricultural practices and environmental stewardship.Advancements in Technology:The field of rice research has witnessed remarkable advancements in technology, enabling scientists to study rice at the molecular level. Techniques such as genome sequencing, marker-assisted breeding, and CRISPR gene editing have revolutionized rice breeding programs, allowing for the development of tailored varieties with desired traits. Furthermore, remote sensing and precision agriculture techniques aid in optimizing rice cultivation practices, increasing efficiency, and reducing environmental impact.Challenges and Future Directions:Despite the progress made in rice research, significantchallenges lie ahead. Climate change, water scarcity, pests, and diseases pose threats to rice production globally. Addressing these challenges requires interdisciplinary collaboration, innovative approaches, and sustainable solutions. Furthermore, ensuring equitable access to improved rice varieties and technologies is essential for food security and poverty alleviation in rice-growing regions.Conclusion:In conclusion, rice research continues to be a dynamic and vital field, with implications for food security, nutrition, and environmental sustainability. Through advancements in genetics, nutrition, ecology, and technology, scientists are unraveling the complexities of rice and paving the way for a more resilient and productive future. By recognizing the importance of rice and investing in research and development, we can ensure the well-beingof current and future generations while safeguarding the planet's resources.。

双创工作计划

双创工作计划英文回答:Double Innovation Work Plan。

I. Situation Analysis。

In recent years, with the rapid development of the national double innovation strategy, the innovation ecosystem has been continuously optimized, and the overall level of scientific and technological innovation has been significantly improved. However, there are still some shortcomings and weaknesses in innovation work, such as insufficient innovation vitality, insufficient transformation of scientific and technological achievements, and insufficient protection of intellectual property rights.II. Objectives。

Based on the current situation of innovation work, thefollowing objectives are proposed for the next three years:1. Comprehensively improve the innovation environment, optimize the innovation ecosystem, and stimulate thevitality of innovation.2. Strengthen the transformation of scientific and technological achievements, promote the integration of industry, education and research, and improve theefficiency of innovation.3. Enhance the protection of intellectual property rights, create a fair and just innovation environment, and stimulate innovation motivation.III. Key Tasks。

CCS优化简介

CCS优化简介Code Composer Studio (Optimization)Enry Shen Texas Instruments8th Texas Instruments Developer Conference India 30 Nov - 1 Dec 2005, BangaloreAgendaOverview of Application Code Tuning Compiler Consultant Code Size Tune T ool Cache Tune Tool1CCS Optimization Tool TutorialOverview of Application Code Tuning Compiler Consultant ToolIntroduction DemonstrationCode Size Tune T oolIntroduction DemonstrationCache Tune T oolIntroduction DemonstrationCCStudio Platinum EditionOne environment for all platformsMulti-platform IDE meets evolving developers needs OEMs realize substantial development tool savingsEasy To Use IDEExponential productivity improvementsUp to 80% faster debug via connect/ disconnect Single keystroke back-step with RewindMaximize TI DSP performance entitlementCode optimization and tuning tools Updated C compilers for each platformIntegrated CodeWright editor Lock versions of compiler andDSP/BIOS per design2Compiler Build OptionsNearly one-hundred compiler options available to tune your code's performance, size, etc. Following table lists most commonly used options:Options -mv6700 -mv67p -mv6400 -mv6400+ -fr-fsDebug Optimize (release) -g -ss -o3 -kDescription Generate 'C67x code ('C62x is default) Generate 'C672x code Generate 'C64x code Generate 'C64x+ code Directory for object/output files Directory for assembly files Enables src-level symbolic debugging Interlist C statements into assembly listing Invoke optimizer (-o0, -o1, -o2/-o, -o3) Keep asm files, but don't interlistCompiler Build OptionsNearly one-hundred compiler options available to tune your code's performance, size, etc. Following table lists most commonly used options:Options -mv6700 -mv67p -mv6400 -mv6400+ -fr-fsDebug Optimize (release)Description Generate 'C67x code ('C62x is default) Generate 'C672x code Generate 'C64x code Generate 'C64x+ code Directory for object/output files Directory for assembly files -g Enables src-level Debug and Optimizesymbolic debugging options conflict -ss Interlist C statements into assembly listing with each other, therefore-o2/-o, -o3) they should -o3 Invoke optimizer (-o0, -o1, not be used asm files, but don't interlist -k Keep together3Two Default Configurations-g -fr"$(Proj_dir)\Debug" -d"_DEBUG" -mv6700 -o3 -fr"$(Proj_dir)\Release" -mv6700For new projects, CCS automatically creates two build configurations: Debug (unoptimized) Release (optimized) Use the drop-down to quickly select build config.Two Default ConfigurationsAdd/Remove build config's with Project Configurations dialog (on project menus)Edit a configuration: 1. Set it active 2. Modify build options 3. Save project4Two Default ConfigurationsNow You can build with your new configurationRecommended Development FlowStartNoEditCompile -gDebugWorks? YesNo Done Goals Met? ProfileYesCompile -oDebug first. Tune second. After making sure you program is logically correct, We can use compiler optimizer to optimize.5First, Turn on the OptimizerAs we have seen, the optimizer can work miracles, but… Whatelse can we do with C after turning on the optimizer? Options -mv6700 -mv67p -mv6400 -mv6400+ -fr-fsDebug Optimize (release) -g -ss -o3 -k Description Generate 'C67x code ('C62x is default) Generate 'C672x code Generate 'C64x code Generate 'C64x+ code Directory for object/output files Directory for assembly files Enables src-level symbolic debugging Interlist C statements into assembly listing Invoke optimizer (-o0, -o1, -o2/-o, -o3) Keep asm files, but don't interlist Provide Compiler with More InsightWhy you program still not optimized even use –o3 option to turn on the optimizer?1. 2. 3. 4. 5.Restrict Memory Dependencies (Aliasing) Program Level Optimization: -pm –op2 -o3 #pragma UNROLL(# of times to unroll); #pragma MUST_ITERATE(min, max, %factor); #pragma DATA_ALIGN(variable, 2n alignment); Like –pm, #pragmas are an easy way to pass more information to the compiler The compiler uses this information to create "better" code #pragmas are ignored by other C compilers if they are not supported 6Memory Alias DisambiguationWhat happens if the function is called like this? fcn(*myVector, *myVector+1) void fcn(*in, *out) { LDW *in++, A0 ADD A0, 4, A1 STW A1, *out++ }in a b c d e ...in + 4Can reorder memory references only when they are not aliases Aliases access same memory location Sometimes Compiler cannot figure out two pointers point to independentaddresses or not Keyword restrict says pointer gives sole access to underlying memoryMemory Alias DisambiguationWhat happens if the function is called like this? fcn(*myVector, *myVector+1)in a in + 4 b void fcn(*in, *out) c { LDW void *in++, A0 *restrict in, short *out) fcn(short d ADD A0, 4, A1 STW A1, *out++ e } ...Can reorder memory references only when they are not aliases Aliases access same memory location Sometimes Compiler cannot figure out two pointers point to independent addresses or not Keyword restrict says pointer gives sole access to underlying memory7Program Level Optimization (-pm)-pm is critical in compiling for maximum performance -pm creates a temp.c file which includes all C source files, thus giving the optimizer a program-level optimization context -opn describes a program's external referencesProgram Level Optimization (-pm)-pm requires the use -o3 -pm requires the use -o3 Cannot be used as file or function specific Cannot be used as file or function specific option option Without knowing which -opn option to use, TI Without knowing which -opn option to use, TI couldn't use couldn't use -pm in default Release config -pm in default Release config Unfortunately, -pm cannot provide optimizer Unfortunately, -pm cannot provide optimizer with visibility into object code libraries with visibility into object code libraries External References: External References: For example, ififyour program modifies aa For example, your program modifies global variable from another code module, - globalvariable from another code module, op2 cannot be used op2 cannot be used Similarly, ififyour code calls aafunction in an Similarly, your code calls function in an external module (who's source isn't visible to external module (who's source isn't visible to the optimizer), -op2 cannot be used (and will the optimizer), -op2 cannot be used (and will be overriden) be overriden) 8UNROLL(# of times to unroll)#pragma UNROLL(2); for(i = 0; i < count ; i++) { sum += a[i] * x[i]; }Tells the compiler to unroll the for() loop twice The compiler will generate extra code to handle the case that count is odd The #pragma must come right before the for() loop UNROLL(1) tells the compiler not to unroll a loopMUST_ITERATE(min, max, %factor)#pragma UNROLL(2); #pragma MUST_ITERATE(10, 100, 2); for(i = 0; i < count ; i++) { sum += a[i] * x[i]; } Gives the compiler information about the trip (loop) count In the code above, we are promising that: count >= 10, count <= 100, and count % 2 == 0 If you break your promise, you might break your code Allows the compiler to remove unnecessary code Modulus (%) factor allows for efficient loop unrolling The #pragma must come right before the for() loop9#pragma DATA_ALIGN(variable, 2n alignment)#pragma DATA_ALIGN(a, 8); short a[256] = {1, 2, 3, … #pragma DATA_ALIGN(x, 8); short x[256] = {256, 255, 254, … #pragma UNROLL(2); #pragma MUST_ITERATE(10, 100, 2); for(i = 0; i < count ; i++) { sum += a[i] * x[i]; } Tell compiler to create variables on a 2n boundary Allows use of (double) word-wideoptimized loads/storesCode Size vs. Code Speed? What compiler options are best for your code size vs. speed tradeoff? Traditionally, figuring this out required running large permutations of options10Minimizing Space Option-ms level none -ms0 -ms1 -ms2 -ms3 Performance 100% 90 60 20 0 Code Size 0 10 40 80 100%The table shows the basic strategy employed by compiler and Asm-Opt when using the –ms options User must use the optimizer (-o) with –ms for the greatest effect. The optimizer provides a great deal of information for code-size reduction, as well as increasing performance Use program level optimization (-pm) Try -mh to reduce prolog/epilog code Use –oi0 to disable auto-inliningAnalyze and TuneCompiler Consultant Cache Tune Code Size Tune Tuning Dashboard11CCS Optimization Tool TutorialOverview of Application Code Tuning Compiler Consultant ToolIntroduction DemonstrationCode Size Tune T oolIntroduction DemonstrationCache Tune T oolIntroduction DemonstrationCompiler Consultant IntroductionC/C++ cannot express all the information needed to get the best optimization Compiler Consultant … Recognizes these gapsGives specific advice on filling the gap It analyzes your application and makes recommendations for changes to optimize the performance These suggestions include compiler optimization switches and pragmas to insert into your code that give the compiler more application information Performance Improvement comes quickly12Compiler Consultant Introduction1. 2. 3. 4. 5. 6. 7. 8. 9. Optionally, profile CPU performance Build with –-consultant Launch Profile Viewer to see advice in spreadsheet like format Sort loops to decide where to start See advice by double-clicking on Advice List cell of row for loop of interest Explore advice in web browser like interface Implement as much advice as desired Build to see improvements Repeat until satisfiedBenchmark Code PerformanceProfileClockView13Benchmark Code PerformanceWe set two breakpoints, one before and another after the dotp() Now we can benchmark clock cycles to execute this functionRun to the first breakpointBenchmark Code PerformanceRun to the first breakpointReset the Clock by double click the item14Benchmark Code PerformanceRun to the next breakpoint and get the result of clock cycles to performing this functionBenchmark with ProfilerProfiler SetupProfiler Viewer15Setup the ProfilerThis is a three step process:Click "Enable Profiling"Select the code we want to profile:Functions LoopsSelect the "Custom" ButtonSetup the ProfilerSelect the items to benchmark16Open up the ViewerCountTotalHow many times we run into this functionTotal number of clock cycles to execute this functionCompiler ConsultantProject Build Options17Compiler ConsultantClick on the checkbox Generate Compiler Consultant Advice (--consultant).Compiler ConsultantFrom the Profile menu, choose Viewer.Compiling with no Error18Compiler ConsultantOnce the Profile Viewer window appears, click on the Consultant tab.Compiler ConsultantOnce the Profile Viewer window appears, click on the Consultant tab.The Loop NameWe take 64 cycles to execute this loopTwo advises to optimize this loop19。

DS2208数字扫描器产品参考指南说明书

-05 Rev. A

6/2018

Rev. B Software Updates Added: - New Feedback email address. - Grid Matrix parameters - Febraban parameter - USB HID POS (formerly known as Microsoft UWP USB) - Product ID (PID) Type - Product ID (PID) Value - ECLevel

-06 Rev. A

10/2018 - Added Grid Matrix sample bar code. - Moved 123Scan chapter.

-07 Rev. A

11/2019

Added: - SITA and ARINC parameters. - IBM-485 Specification Version.

No part of this publication may be reproduced or used in any form, or by any electrical or mechanical means, without permission in writing from Zebra. This includes electronic or mechanical means, such as photocopying, recording, or information storage and retrieval systems. The material in this manual is subject to change without notice.

医学上的发明发现英语作文

医学上的发明发现英语作文英文回答:Medical Innovations and Discoveries.The field of medicine has witnessed a remarkable journey of scientific breakthroughs and technological advancements that have revolutionized healthcare. From the discovery of antibiotics to the advent of advanced imaging techniques, these innovations have profoundly impacted the way we prevent, diagnose, and treat diseases.Antibiotics.The discovery of antibiotics in the early 20th century marked a pivotal moment in medical history. Prior to their advent, bacterial infections were often fatal. Antibiotics, such as penicillin and streptomycin, have dramatically reduced the incidence and mortality rates associated with infections. Today, antibiotics are essential components ofmodern medicine, helping to combat a wide range ofbacterial diseases.Imaging Techniques.Advances in imaging technologies have revolutionizedthe diagnosis and monitoring of diseases. X-rays, computed tomography (CT), magnetic resonance imaging (MRI), and ultrasound provide clinicians with detailed cross-sectional images of the body's internal structures. These techniques enable accurate diagnoses and early detection of conditions, leading to more timely and effective treatments.Vaccines.The development of vaccines has played a crucial rolein preventing the spread of infectious diseases. Vaccines stimulate the body's immune system to produce antibodies against specific pathogens, thereby providing protection against future infections. Smallpox, polio, and measles are just a few examples of diseases that have been virtually eradicated thanks to the widespread use of vaccines.Surgical Techniques.Surgical techniques have also undergone significant advancements. Minimally invasive surgery, such as laparoscopy and robotic surgery, allows surgeons to perform complex procedures through small incisions. These techniques minimize pain, reduce scarring, and shorten recovery times for patients.Personalized Medicine.The rise of personalized medicine has empowered clinicians with the ability to tailor treatments to individual patients based on their genetic makeup and specific disease profiles. Genomic sequencing and biomarker analysis help identify patients who are likely to respond best to certain therapies, optimizing treatment outcomes.Artificial Intelligence (AI)。

然后去写作业英语

Certainly!Heres a detailed response to the task of doing homework in English:1.Identify the Assignment:First,make sure you understand what the assignment is asking for.Read the instructions carefully and note any specific requirements or deadlines.2.Gather Materials:Collect all the necessary materials such as textbooks,notes,and any online resources that might be helpful.3.Create a Study Space:Find a quiet and comfortable place where you can focus on your work without distractions.4.Break Down the Task:If the assignment is large or complex,break it down into smaller,manageable parts.This can make it less overwhelming and easier to tackle.5.Research:If your homework requires research,use reliable sources such as academic journals,educational websites,or books from the library.Take notes on the information you find.6.Draft Your Work:Start writing your assignment.Even if its not perfect,getting your ideas down on paper is a crucial first step.You can always revise and improve later.e Proper Grammar and Spelling:As you write,pay attention to grammar, punctuation,and spelling.These elements are important for clear communication and can affect your grade.8.Cite Your Sources:If youre using information from other sources,make sure to cite them properly to avoid plagiarism.Learn the citation style required by your teacher or school e.g.,APA,MLA,or Chicago.9.Revise and Edit:Once youve completed a draft,take some time to review your work. Look for areas where you can improve clarity,add more detail,or correct any errors.10.Ask for Feedback:If possible,ask a classmate,friend,or family member to read over your work and provide feedback.A fresh set of eyes can often spot mistakes or areas for improvement that you might have missed.11.Proofread:Before submitting your assignment,proofread it one last time to catch any final errors or typos.12.Submit Your Work:Make sure to submit your homework on time,following any specific submission guidelines provided by your teacher.Remember,doing homework is not just about completing a task its an opportunity to learn,practice,and improve your skills in English.Take it seriously and approach it with a positive attitude.。

英语作文-掌握集成电路设计中的时序设计与时钟网络优化

英语作文-掌握集成电路设计中的时序设计与时钟网络优化In the realm of integrated circuit (IC) design, mastering timing design and clock network optimization is crucial for ensuring the functionality and performance of electronic systems. Timing design involves synchronizing signals and managing the timing constraints within an IC, while clock network optimization focuses on enhancing the distribution of clock signals throughout the chip. This article delves into these two key aspects of IC design and explores their significance in achieving reliable and efficient electronic systems.Timing design is fundamental to the functionality of ICs as it governs the sequencing of operations within the circuit. In digital circuits, proper timing ensures that signals arrive at their destinations at the right time, preventing errors and maintaining the integrity of data transmission. Timing violations, such as setup and hold time violations, can lead to malfunctioning circuits and compromise the overall performance of the system. Therefore, designers must meticulously analyze and optimize timing paths to meet the desired specifications.One essential technique in timing design is the use of timing diagrams to visualize signal propagation and timing relationships. By plotting signal transitions against time, designers can identify critical paths, setup and hold times, and clock periods. Timing analysis tools aid in verifying timing constraints and identifying areas for improvement. Techniques such as pipelining, retiming, and clock domain crossing synchronization help mitigate timing issues and improve overall system performance.Clock network optimization complements timing design by ensuring the efficient distribution of clock signals across the IC. The clock signal serves as a heartbeat for the system, coordinating the timing of operations and synchronizing various components. A well-designed clock network minimizes clock skew, jitter, and power consumption while maximizing signal integrity and reliability.One approach to optimizing clock networks is through proper clock tree synthesis (CTS). CTS involves the generation of a hierarchical tree structure to distribute the clock signal from the source to all clocked elements within the IC. Techniques such as buffer insertion, wire sizing, and clock gating are employed to balance skew and minimize signal delays. Advanced CTS algorithms leverage optimization algorithms to achieve better performance metrics, such as reduced power consumption and improved signal integrity.Moreover, clock mesh and clock distribution networks offer alternative solutions for distributing clock signals in large-scale designs. Clock mesh architectures distribute the clock signal uniformly across the chip, reducing skew and improving synchronization. On the other hand, clock distribution networks utilize dedicated routing resources to deliver clock signals to specific regions of the chip efficiently.In conclusion, mastering timing design and clock network optimization is paramount in the field of integrated circuit design. These two aspects play a crucial role in ensuring the functionality, reliability, and performance of electronic systems. By employing advanced techniques and leveraging optimization algorithms, designers can overcome timing challenges and design robust ICs capable of meeting the stringent demands of modern technology.。

外延反应流程

外延反应流程Engaging in outward reaction processes can be a complex and challenging task. 外延反应流程可能是一个复杂而具有挑战性的任务。

This type of process involves the transformation of substances or compounds from their original state to a new form through the introduction of external factors. 这种过程涉及通过引入外部因素将物质或化合物从原始状态转化为新形式。

Whether it involves chemical reactions, biological processes, or other natural or synthetic processes, the outward reaction process requires careful planning, precise execution, and thorough monitoring. 无论涉及化学反应、生物过程还是其他自然或合成过程,外延反应流程都需要仔细计划、精确执行和彻底监控。

One of the key factors to consider in the outward reaction process is the selection of appropriate reactants or substrates. 在外延反应流程中需要考虑的关键因素之一是选择合适的反应物或底物。

This decision can greatly impact the outcome of the reaction, as well as the efficiency and effectiveness of the process as a whole. 这个决定会对反应的结果以及整个过程的效率和有效性产生极大的影响。

《生物工程专业英语》课件

Fermentation Engineering Application: Fermentation Products and Applications

Enzyme Characterization and Mechanism

Enzyme Engineering Application

Enzyme Evolution and Mutagenesis

Enzyme Engineering Application

Enzyme Application in Biocatalysis and Synthesis

Genetic material

This section introduces the genetic material, DNA, and its function in storage, replication, and expressing genetic information It also covers the structure of DNA and how it is packed into chromosomes

DNA isolation and purification

01

Techniques for extracting and purifying DNA from cells, including phenol chloroform extraction and column chromatography

Cell pass and free

Methods for introducing foreign DNA or RNA into cells using vectors or lipids to study gene expression or protein function

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Task Sequencing for Optimizing the Computation Cycle in a TimedComputation ModelSebastian Fischmeister and Guido Menkhaus,University of Salzburg,AustriaAbstractRecent developments in embedded control systems promote the timed computation model following the principles of logical execution time(LET). Resulting control applications are time deterministic,value deterministic,and their properties may be subject to formal verification against a mathematical model of the control design. However,the timed computation model introduces inefficiencies to computation cycles.As the LET of a real-time control task requires being greater than its worst-case execution time and computed values are always propagated at the end of the LET, actuator updates are unnecessarily delayed.This makes the control cycle less responsive.In this paper,we present an approach that allows the definition of task sequences for a timed computation model implemented by the timing definition language(TDL).Task sequences help minimizing timing delays between sensor readings and actuator updates(e.g.,in estimator-based control systems), managing startup and shutdown phases of control systems,and providing mechanisms forerror-detection in fault-tolerant systems. Keywords:real-time control systems,timed computation model1IntroductionReactive systems continuously receive stimuli from sensors,measure the environment,and react on the environment by controlling actuator states[1,2]. The systems must be able to sense and control the environment within a predefined time frame for which the environment dictates the exact length. Such systems can be found,for instance,in real-time process controls in manufacturing or embedded control systems in the automotive area.The design of a control system typically involves creating a set of periodically executed tasks.The system needs to react quickly to stimuli from the environment and sequencing of tasks is of primary concern[3].A sequence defines a logical relationship between tasks and the release event of one task depends upon the termination of its preceding task.This allows using resources in a certain order with data dependencies within the same period.Programming languages,which implement the timed computation model such as TDL[4]and Giotto[5]gained more recognition recently[6,7,8]. The essential idea of such languages istime-triggered cyclic computation in which computing a task follows reading inputs(e.g.,sensor data)and precedes updating actuators.The logical execution time(LET)and the worst-case execution time(WCET)describe the timing behavior of a task. The task is released at the beginning and terminated at the end of the LET.The release and the termination event are time-triggered.According to a scheduling scheme,the task starts after it has been released and completes its execution before the LET has elapsed.The end of the LET specifies the instance of time when the outputs of the computation of a task become available to other tasks or actuators,even if the output of a task is available earlier(e.g.,at the end of the WCET). TDL,for example,declares a set of modes,which define sets of task invocations and other activities that are executed periodically and in parallel.A task has a set of input ports and a set of output ports.A driver provides values for the input ports and drivers assign values to the output ports.Reading input ports and writing to output ports happens at theIn Proc. of the 23rd Intl. Digital Avionics and System Control Conference (DASC'04), 2004.beginning and the end of the LET.This is the reason, why task sequencing in TDL with data dependencies can only be arranged across task periods and not within the same period.The concept of a LET for tasks introduces determinism to the control system.A system is said to be value deterministic,if a set of tasks produces the same sequence of outputs given the same sequence of inputs,even though the environment changes.If the system produces the same output at always the same time,it is time deterministic.These properties apply only,if each task is itself value and time deterministic and the composition of the tasks is schedulable[9].The timed computation model favors system determinism and predictability over code efficiency and system reactivity[10].This a drawback when applying this model to real-time control systems.In this article,we introduce task sequencing using micro-tasks.Micro-tasks help minimizinginefficiencies in the timed computation model.They are useful in reducing timing delays between sensor readings and actuator updates(e.g.,estimator-based control systems),managing startup and shutdown phases of control systems,and providing mechanisms for error-detection in fault-tolerant systems.The remaining of the article is structured as follows: Section2presents the motivation of the work. Related work is discussed in Section3.We introduce the concept of task sequencing andmicro-tasks for a timed computation model in Section4.The implementation and a case study is discussed in Section5and we conclude the article in Section6with a brief outline about our future work. 2MotivationWhen programming embedded control systems in the automotive,aerospace,and manufacturing domain,it is necessary not only to specify a task execution frequency,but also a time-based order of the execution of tasks.The order defines a sequence of tasks having a specific execution frequency.It allows for splitting the calculation of a task into a set of micro-tasks to•specify a time-based causal order of tasks,which require to be executed one after theother,and•execute drivers for sensor readings and actuator updates intertwined with the invocation ofmicro-tasks.Intertwined Invocation.The intertwined invocation of micro-tasks with actuator updates can reduce the delay between reading sensor values and writing actuator updates in timed computation models.Such a delay has no effect in control systems in which the invocation period of the task that computes the control algorithm is comparable to the computation time of the control algorithm. However,usually the computation time required to calculate the control algorithm is small compared to the sampling period.The delay of updating an actuator only at the end of the LET can be severe in feedback control systems,where a long delay could be disastrous for stability[11].The specification of a sequence of tasks is desirable when the state of a real-time image of a real-time entity needs to be estimated before it is used[12].A real-time image is the current state of a real-time entity.A real-time entity is a controlled object.The estimation is necessary,if the real-time image has lost its validity due to the progression of time between the time of observation of the real-time entity and the time of usage of its real-time image. This delay between observation and usage can be caused by the time it takes to transport the observation of the real-time entity from the place of observation to the place of processing or it is due to a slow sampling frequency of the real-time entity. The delay between observation and usage introduces an error.However,the control algorithm can approximate the error and estimate the state of the real-time ually state estimation requires building a model of the dynamics of the real-time entity.The model allows the computation of the state of the real-time entity for the interval in which the real-time image has lost its validity[13]. System Startup and Shutdown.System startup and shutdown requires a specific sequence of tasks to be executed.Adherence to this sequence ensuresthat the system does not enter an unsafe state.In this sequence,parallel execution of the tasks is not an option,since the results of these tasks usually depend on each other and default/initial values may be unattainable.System startup and shutdown are no activities that are executed periodically and cannot be expressed by languages that support the description of periodic tasks,only.Error Detection.Error detection can be implemented using a system design that includes model redundancy[14].Model redundancy has been found effective against random errors.It uses a known model that estimates the properties of a physical system.Error detection identifies deviations between the model and the physical system.Task sequences are necessary,since the model is computed after the physical system has been controlled and before sensors report the new state of the system.3Related WorkWork on programming languages for control systems with real-time constraints can be broadly divided into three categories[9]:•The scheduled model assigns priorities to tasks.A scheduler decides on the sequence of theexecution of tasks,to meet all task deadlines,based on the current priorities of the set ofactive tasks.•The synchronous approach assumes that theunderlying platform is fast enough to executeall tasks related to an event before the nextevent arrives and the set of tasks related to thisevent is released.•The timed model defines a LET for each taskwith a release and a termination event for eachtask.Other tasks or activities operating on theenvironment can use the outputs of a task onlyafter the termination event of the task hasoccurred.We look at representatives of these categories and the concepts they use to provide task sequencing.OSEKWorks[15]is a OSEK/VDX compliantreal-time operating system[16].It supports tasks and different scheduling strategies and implements the scheduled-model approach.In OSEK/VDX each task must end with calling TerminateTask or ChainTask.TerminateTask ends the calling task. ChainTask defines a succeeding task to the calling task.OSEK/VDX specifies the succeeding task to be released as soon as the calling task has been terminated.Yet,the standard does not fully specify the behavior of ChainTask with respect to the scheduler and task queues.This may result innon-deterministic behavior of the control application.Esterel[17]and Lustre[18]are imperative synchronous programming languages for programming hardware and software controllers. Synchronous languages abstract away the time required to react to an input and computing an output.The computing platform is assumed to be fast enough to react to an event before the next event arrives.Conceptually,the zero-delay value propagation(outputs become available as inputs become available)allows for concurrency and determinism to coexist.Esterel implements task sequencing by passing control from one task instantaneously to the succeeding task.In a sequence such as p;q,the task described by the statement q starts immediately after task p has terminated.XGiotto[10]is an event-triggered programming language but bases its computation model on the same abstraction as Giotto.It introduces new programming constructs that allow for reacting to synchronous and asynchronous events.The construct react{b}until[e]defines a reaction block with a body b and an event e that terminates the tasks released within the reaction block b.A sequence of reaction blocks is processed sequentially.The body of a reaction block may declare a LET,determined by the time when the event e(e.g.,a time-triggered event)occurs.The system scheduler executes the set of tasks in the body of the reaction block concurrently and it is impossible to assign a LET to a single task. However,defining only one task per reaction block circumvents this limitation.MetaH[19]is a software-architecture specification language.It describes how the different elements of a system(e.g.,source,hardware,and communication)are integrated to form thefinal application.The tool chain of MetaH includes tools for visual editing,schedule or partition modeling, and analyzing relevant properties such as the timing behavior.Utilizing this tool chain,MetaH generates glue code for the interaction of individual elements of the system and takes care of the annotatedreal-time properties.MetaH provides means for creating task sequences via the concept of undelayed communication.Undelayed communication is implemented via precedence-scheduling constraints. MetaH generates scheduling constraints such that the source process(information producer)is dispatched andfinishes execution before the target process(information consumer)is released. Undelayed communication and thus task sequencing in MetaH has the following constraints:At least one of the processes must be aperiodic or both processes have harmonic periods or the period of one of the processes is an integer multiple of the other.MetaH limits undelayed communication to local nodes only, i.e.,two communicating processes must be bound to the same processor.Currently,TDL lacks programming constructs to describe a time-based order of the execution of sequences of tasks and actuator updates.Possible solutions to this problem have been discussed in [20].4Task Sequencing withMicro-Tasks in TDL Conceptually,TDL bases on Giotto,but it incorporates extensions such as the concept of a module,improved language syntax,and clean-house implementations of the underlying infrastructure on several hardware platforms[4].Listing1shows a TDL module fragment.A TDL module consists of one or more TDL modes.A mode consists of several,possibly concurrently executed task invocations and actuator updates.A TDL mode specifies the period,i.e.,the length of one computation cycle(e.g.,1000ms).A task period is determined with respect to the execution period of the mode to which the task is assigned(by dividing the invocation period of the mode by the task frequency).The specification of the task frequency is part of the task declaration in the mode. Listing1shows the mode main,which declares task mt1with the frequency of once-per-period(i.e., period of1000ms),task mt2with a frequency of twice-per-period(i.e.,period of500ms),and an actuator update with a frequency of once-per-period (i.e.,period of1000ms).Listing1.TDL module fragment.t a s k m1[WCET=100ms]{in p u t i n t i;output i n t o;u s e s f1(i,o);}t a s k m2[WCET=200ms]{in p u t i n t i;output i n t o;u s e s f2(i,o);}s t a r t mode main[1000ms]{t a s k[1]m1{i:=s2};[2]m2{i:=s1};...a c t u a t o r[1]a c t:=mt1.o;}4.1Concept of Micro-TasksThe underlying concept of micro-tasks is sequential element composition[21](see Figure1).A task is composed of a sequence of non-concurrent execution of micro-tasks and actuator updates.The task to which the micro-tasks are assigned to,is called parent task.A micro-task itself can be a parent task to other micro-tasks or so-called child tasks.Figure1shows the conceptual structure of TDL including the extension for task sequences.The TDL language consists of instances of the entities1 1The complete TDL language includes additional entities, however,they are not relevant for this paper.The language report [4]provides a complete list.Actuator,Task,and Mode.The new concept of tasks allows for Tasks and Modes to include other groupable elements.Instances of Tasks can now contain other Tasks(denoted as micro-tasks)and Actuators.Figure1.Structure of the TDL-language exten-sion for micro-tasks.Although both Tasks and Modes group elements such as tasks and actuators,they differ in syntax and treatment of the grouped elements.•Instances of Mode consist of a set of tasks andactuators and declare their invocation period.Modes periodically schedule their set of tasksand actuators.Instances of Task only specifytasks and actuators.They do not specifyfrequencies for micro-tasks,which is ratherdetermined by their parent task.•An arbitrary declaration order of tasks andactuators in instances of Mode does not changethe behavior of the control system.However,the correct declaration order of micro-tasks andactuators is key for the behavior of the systemin instances of Tasks.As a consequence of these changes,we can define sequences of tasks in TDL and havefine-grained access of execution paths.4.2SyntaxListing2is an excerpt of a TDL program using micro-tasks.Listing2.TDL module fragment with micro-tasks.t a s k m1[100ms]{in p u t i n t i;output i n t o;u s e s f1(i,o);}t a s k m2[200ms]{in p u t i n t i;output i n t o;u s e s f2(i,o);}t a s k t{in p u t i n t i;output i n t o;[LET=200ms]m1{i:=t h i s.i};a c t u a t o r a c t:=m1.o;[LET=300ms]i f g2()thenm2{i:=m1.o};}s t a r t mode main[1000ms]{t a s k[1]t{i:=s1};....}Task t contains a sequence of two micro-tasks mt1 and mt2.In between these two micro-tasks,it updates actuator act.The syntax of this example differs from the standard TDL syntax.The basic declaration of a task is still compatible with the standard TDL syntax(see the two tasks mt1and mt2).The declaration of tasks has been extended allowing for sequences of tasks and actuator updates.Task t uses the extended syntax,as it consists of a sequence of task mt1,one actuator update,and,conditionally,task mt2.To retain time and value determinism and be able to specify the exact timing of actuator updates,we introduce the attribute LET.This attribute specifies the LET of each micro-task.Actuators do not have a LET assigned,since they are executed synchronously in logical zero time.For example,in Listing2,the LET of micro-task mt1is200ms (which is significantly larger than its WCET of100 ms).Concluding from the LET of the micro-tasks and the order of instructions within the task t,the actuator will be updated200ms after the release of task t.The WCET of a parent task is computed from the LET of its micro-tasks.4.3E CodeThe TDL compiler [4]compiles TDL source code and generates E code for the E machine [22].The E machine is a virtual machine that executes the platform-independent E code and calls theplatform-dependent functionality code.The E code ensures the timing consistency of the task executions (see Figure 2).ProgramFunctionality TDL ProgramFigure 2.TDL system architecture.Listing 3presents a textual version of the E code for the TDL program of Listing 2.Listing 3.The E code for the TDL pro-gram of Listing 2.l b l 1:c a l l ,d [t ]2c a l l ,d [mt1]schedule ,mt14future ,200,l b l 2return6l b l 2:c a l l ,d [a c t ]i f n ,g2,l b l 38c a l l ,d [mt2]schedule ,mt210l b l 3:future ,800,l b l 1returnThe call instruction synchronously executes drivers of a task.The schedule instructionreleases a task to be activated by the scheduler of the operating system.The instruction future initiates the execution of a block E code instructions at some time in the future and the instruction return finishes the execution of the block of E code of the current label.For better readability,we added theinstruction ifn ,which is a conditional branch operation given the operand evaluates to false.The E code is presented in assembler-like style:lbl:opname(,arg1)?(,arg2)?.Labels for branching operations are declared at the beginning of a line.The next argument lists the instruction name.The instruction name defines the operation,which the E machine executes.The following elements list arguments passed to the operation.Depending on the type of operation,we specify zero to at most two arguments.The E code starts with the instruction at label lbl1(Line 1).In the first two instructions,the E machine calls the drivers of task t and micro-task mt1.This loads the arguments into the input ports of the tasks.The order of the driver calls is not arbitrary.As specified in the TDL example (see Listing 2),task mt1is a child-task of task t and requires as input the value of port i of task t .The driver of task t executes and terminates before the driver ofmicro-task mt1.The next instructions (Lines 3to 5)prepare the micro-task mt1for dispatching,release a future condition,and hand over control to the scheduler.In the case study (Section 5),we provide more details about the E code.Introducing micro-tasks requires additional blocks of E code.Each micro-task requires at least one additional label,additional drivers,and instructions (schedule and future ).However,the additional E code is necessary to ensure determinism when using micro-tasks.5Case StudyIn the following section,we present a case study of a control system utilizing micro-tasks for error detection.5.1Development EnvironmentThe target platform of the research prototype of the E machine is the Motorola PowerPC 603RISC processor.On this hardware,we run the Real-Time operating system for Embedded multi-processor Systems (RTEMS)[23,24].The selected compiler suite is the GNU compiler collection 3.2.3[25]witha set of patches specific to the target platform and the RTEMS operating system.Using the PSIM application bundled with the GNU debugger suite[26],we simulate the Motorola PowerPC603RISC processor.Within this simulator,we run and debug PowerPC machine code that is equivalent to machine code that would be executed by a hardware processor.We chose the PowerPC platform for our research prototypes,for we later port the system to boards hosting a Motorola PC555.RTEMS is an operating system especially tailored to multi-processor systems and POSIX compliance.It is open-source,so we can tailor it to our needs. Similar to other real-time operating system,RTEMS provides basic services such as timers,scheduling, and communication.It includes a POSIX API that bases on the POSIX1003.1b and supports a single process,multi-threaded environment.Regarding processes,RTEMS supports routines referred to as single user,single process.5.2Implementation Details of the EMachineThe E machine implementation in RTEMS uses the POSIX API to a large extent.Most functionality required by the E machine are standard services such as timers&clock,alarms,and scheduling.So, the implementation of the E machine can easily be ported to other POSIX-compliant platforms such as RT-Linux.In the current design of the E machine research prototype,the E code is not statically linked to the E machine,the driver,and the functionality code. Instead,the E code is dynamically loaded at boot time.It uses the in-memoryfile system(IMFS)that RTEMS provides.The IMFS provides full POSIX filesystem functionality,yet it is RAM based.The E code is stored in the root directory of the IMFS.To provide the data at boot time,we build an imagefile of the IMFS that is statically linked to the.data section of thefinal executable.At boot time, RTEMS uses this imagefile to initialize the IMFS. In the case study,we use the standard scheduler provided by RTEMS.The RTEMS scheduler allocates the processor using a priority-based, preemptive algorithm augmented to provide round-robin characteristics within individual priority groups.The goal of this algorithm is to guarantee that the task,which is executing on the processor at any point in time is the one with the highest priority among all tasks in the ready state[24].Most instructions of the E machine are trivial. Instructions such as ifn,call,or return are implemented straightforwardly.We look into the implementation of the two instructions schedule and future in more detail.The instruction schedule dispatches a task.In the implementation,we initialize a data stack and create a new task using the POSIX call pthread create.The new task is immediately dispatched.In theconfiguration of the RTEMS application,we must specify the maximum number of active tasks. Currently,this number is determined by the maximum count of schedule operations within one period of a mode.The instruction future is equivalent to a branch instruction that is evaluated at a specific point in time.The E machine implements this instruction via suspend operations and task preemption.The future instruction specifies the time span until the predicate associated to the future instruction evaluates to true.The E machine is suspended for this time span and wakes up at the specified point in time and preempts all tasks.5.3Splitting Control into Micro-TasksDefining task sequences is necessary,for example, for the design of controls laws using a current or predictive state estimation,when either the state elements of the system are inaccurate or they are not measured.It is possible to split the calculation for the estimation in a part before reading a sensor and a part after reading a sensor.In the case study in Section5.4,we use a similar approach formodel-based error detection.Figure3shows the logical execution of a task t computing the estimator and the control law.The LET of task t and thus its invocation period equals T.When the task is released the estimator calculates state element estimations and the control law computes actuator update values.The actuator values are made accessible to the actuator only when the termination event of the task occurs,i.e.,at theFigure3.Execution of a task in time-triggered processing systems.Figure4.Execution of a task in time-triggered processing systems with micro-tasks.end of the LET.When task t reads the sensor value at time t,it reacts on the plant only at time t+T.It logically reads again the sensor value at time t+T, i.e.,immediately after it has updated the actuator.It computes the estimation and control law on the basis of the new sensor value.Then,it updates the actuator value at time t+2T.This means that it senses only at time t+2T the impact of the control law output,based on the sensor input at time t,i.e.,two sampling periods later.Figure4shows the same scenario and how the logical execution would be described usingmicro-tasks.The task t is split into threemicro-tasks.Micro-task m3computes the part of the estimation that can be calculated before reading the sensor value,whereas micro-task mt1calculates the final state estimation using the current sensor value. Micro-task mt2computes the control law.Task t has LET t and each micro-task has assigned its own LET,LET mt1for micro-task mt1,LET mt2for micro-task mt2,and LET m3for micro-task m3, respectively.Actuator inputs can be made available at the end of the LET of the computation control law at LET mt2and before the LET t of task t has expired.Consequently,the impact of the sensor reading at time t can be sensed at time t+T.The advantage is an improvement of the systems reactivity.5.4Case Study DetailsIn the case study,we use task sequencing for error detection.The concept was outlined in Section2. We employ the same structure of micro-tasks as it was applied in the estimator-based control system. To compute the expected output value of the plant we use a known model and check the computed value exp y against the actual plant output y,reported by a sensor.If the difference between the values exceeds a certain threshold,we assume that a failure has been detected and an error has occurred. Listing4.TDL program with micro-tasks for error detection.t a s k e r r o r d e t e c t i o n[5ms]{inpu t double exp y;inpu t double y;output i n t al ar m;u s e s p e r f o r m c h e c k(exp y,y,a la r m);}t a s k p l a n t c o n t r o l l e r[5ms]{inpu t double y;inpu t double r;output double u;u s e s c o m p u t e c o n t r o l(y,r,u);}t a s k p l a n t m o d e l[20ms]{inpu t double u;output double exp y;u s e s compute model(u,exp y);}t a s k c t l w s a n i t y{inpu t double r,y;output i n t al ar m;s t a t e double s t e x p y:=0;[LET=10ms]e r r o r d e t e c t i o n{y:=t h i s.y;exp y:=s t e x p y,a la rm};[LET=10ms]i f n o t a l a r m(al a rm)thenp l a n t c o n t r o l l e r{y:=t h i s.y;r:=t h i s.r};i f n o t a l a r m(al a rm)thena c t u a t o r u:=p l a n t c o n t r o l l e r.u;[LET=30ms]i f n o t a l a r m(al a rm)thenp l a n t m o d e l{u:=p l a n t c o n t r o l l e r.u}; }s t a r t mode main[100ms]{t a s k[1]c t l w s a n i t y{r:=s1;y:=s2};....}Listing4shows the TDL module fragment that implements the behavior of the case study.Itspecifies three micro-tasks:error detection, plant controller,and plant model.These three micro-tasks are declared in their parent taskctl w sanity.Mapping the set of micro-tasks of Figure4to the task of Listing4,micro-taskerror detection corresponds to micro-taskmt1,micro-task plant controller tomicro-task mt2,and micro-task plant model to micro-task m3.Listing5.The E code generated from Listing4. l b l1:c a l l,d[c t l w s a n i t y]2c a l l,d[e r r o r d e t e c t i o n]schedule,e r r o r d e t e c t i o n4future,10,l b l2return6l b l2:i f n,n o t a l a r m,l b l3c a l l,d[p l a n t c o n t r o l l e r]8schedule,p l a n t c o n t r o l l e rl b l3:future,10,l b l410returnl b l4:i f n,n o t a l a r m,l b l512c a l l,d[u]c a l l,d[p l a n t m ode l]14schedule,p l a n t m o d e ll b l5:future,80,l b l116returnListing5shows the E code resulting from the case study.The mode period starts at lbl1(Line1).The driver of task ctl w sanity is executed,which updates the input ports r and y.The E machine executes the sanity check(Lines2to5)by releasing the micro-task error detection.The driver of the micro-task copies the value of the sensor reading to input port y and the calculated output value of task plant model(stored in the state variablest exp y)to input port exp y.As the LET of task error detection equals10ms,the E machine passes control to the scheduler and resume after10 ms(Line4).At Label lbl2,the E machine checks, if an alarm has been set(by the micro-taskerror detection).If the alarm has been set,the E machine immediately jumps to Label lbl3, waiting for10ms,and then continues at Labellbl4.This behavior is repeated at the beginning of each task-release sequence(Lines6and11).In Line 6,if no alarm has been set,the E machine releases。