errata

美国药典简介

美国药典简介1. 标题和修订(Title and Revision). 92. 药典地位和法律认可(Official status and legal recognition)92.10 药典正文(Official Text) 92.20 药典物品(Official Articles). 92.30 法律认可(Legal Recognition). 103. 与标准的符合性(Conformance to standard). 103.10 标准的适用性(Applicability of standard) 103.10.10 制剂、原料药、辅料的标准的适用性(Applicability of Standards to Drug Products, Drug Substances, and Excipients). 103.10.20 医疗器械、营养补充剂、以及其组成成分的标准的适用性(Applicability of Standards to Medical Devices, Dietary Supplements, and Their Components and Ingredients)113.20 一致性的标示(Indicating Conformance). 114. 药典各论和通则(Monographs and general chapters)124.10 各论(Monographs) 124.10.10 检测程序的适用性(Applicability of Test Procedures) 124.10.20 接受标准(Acceptance Criteria) 124.20 附录(General Chapter). 125. 各论组成(Monograph Components). 135.10 分子式(Molecular formula). 135.20 附加物质、赋形剂、组分(Added Substances, Excipients, and Ingredients) 135.20.10官方原料药中附加的物质、赋形剂、组分(Added Substances, Excipients, and Ingredien ts in Official Substances). 135.20.20官方制剂中的附加物质、赋形剂、组分(Added Substances, Excipients, and Ingredients in Official Products). 135.30 性状和溶解性(Description and Solubility). 145.40 鉴定试验(Identification Test). 145.50 含量分析(Assay). 155.50.10 效价单位(生物效价)(Units of Potency (Biological)) 155.60 杂质和外来物质(Impurities and Foreign Substances). 155.60.10 USP和NF物品的其它杂质(Other Impurities in USP and NF Articles)155.60.20 USP和NF物品中的残留溶剂(Residual Solvents in USP and NF Articles)165.70性能检测(Performance Tests). 165.80 USP标准品(Residual Solvents in USP and NF Articles). 166. 检验规范和分析方法(Testing practices and procedures)166.10 安全的实验室规范(Safe Laboratory Practices). 166.20 自动化程序(Automated Procedures). 166.30 可选择的和谐的方法与程序(Alternative and Harmonized Methods and Procedures)166.40 干燥的、无水的、灼烧的、无溶剂的(Dried, Anhydrous, Ignited, or Solvent-Free Basis)176.40.10 灼烧至恒重(Ignite To Constant Weight). 176.40.20 干燥至恒重(Dried To Constant Weight). 176.50 溶液的制备(Preparation of Solutions). 186.50.10 过滤(Filtration). 186.50.20 溶液(Solutions). 186.60 完成一个实验所需多少单位(Units Necessary to Complete a Test). 186.60.10 片剂(Tablets). 186.60.20 胶囊(Capsules). 196.70 试剂(Reagents). 196.80 设备(Equipment). 196.80.10 测量仪器(Apparatus for Measurement). 196.80.20 仪器设备(Instrumental Apparatus). 197. 测试结果(Test Results). 207.10 质量要求的解释(Interpretation of Requirements) 207.10.10 滴定程序中的等效表述(Equivalence Statements in Titrimetric Procedures) 207.20 修约原则(Rounding Rules) 208. 术语和定义(Terms and Definitions) 218.10 缩写(Abbreviations) 218.20 大约(About) 218.30 乙醇含量(Alcohol Content) 218.40 原子量(Atomic Weights) 228.50 空白试验(Blank Determinations) 228.60伴随(Concomitantly) 228.70 干燥器(Desiccator) 228.80 对数(Logarithms). 228.90 微生物菌株(Microbial Strain) 228.100 可忽略的(Negligible). 228.110 NLT/NMT 228.120 气味(Odor) 228.130 百分比(Percent) 228.140 百分比浓度(Percentage Concentrations) 238.150 压力(Pressure) 238.160 反应时间(Reaction Time) 238.170 比重(Specific Gravity) 238.180 温度(Temperatures) 238.190 时间(Time) 238.200 转移(Transfer). 238.210 真空(Vacuum). 238.220 真空干燥器(Vacuum Desiccator). 238.230 水(Water). 248.230.10 水作为官方制剂中的组分(Water as an Ingredient in an Official Product)24 8.230.20 水用于官方原料药的生产(Water in the Manufacture of Official Substances)24 8.230.30 药典实验操作用水(Water in a Compendial Procedure). 248.240 称量和测量(Weights and Measures). 249. 开处方和配药(Prescribing and Dispending). 259.10 公制单位的使用(Use of Metric Units). 259.20 体积的改变(Changes in Volume). 2510. 保存、包装、储存、贴签(preservation,packaging,storage and labeling)2510.10 在非特定条件下储存(Storage Under Nonspecific Conditions). 2510.20 包装容器(Containers). 2510.20.10显窃启包装(Tamper-Evident Packaging). 2610.20.20 避光容器(Light-Resistant Container). 2610.20.30密闭良好的容器(Well-Closed Container). 2610.20.40密封的容器(Tight Container). 2610.20.50严封的容器(Hermetic Container). 2710.20.60单元包装(Single-Unit Container). 2710.20.70单剂量包装(Single-Dose Container). 2710.20.80单元剂量容器(Unit-Dose Container). 2710.20.90单元使用的容器(Unit-of-Use Container). 2710.20.100多单元容器(Multiple-Unit Container). 2710.20.110多剂量容器(Multiple-Dose Container). 2710.20.120毒物保护包装法案(Requirements under the Poison Prevention Packaging Act (PPPA))2710.30 储存温度和湿度(Storage Temperature and Humidity). 2810.30.10 冷冻(Freezer). 2810.30.20冷处(Cold). 2810.30.30 凉处(Cool). 2810.30.40 可控的凉爽温度(controlled cold temperature). 2810.30.50 室温(room temperature). 2910.30.60 可控的室温(Controlled Room Temperature). 2910.30.70 温暖(warm). 2910.30.80 过热(Excessive Heat). 2910.30.90 防冻(Protection From Freezing). 2910.30.100 干燥处(Dry Place). 2910.40 标签(Labeling). 2910.40.10每个剂量单元中组分的量(Amount of Ingredient Per Dosage Unit)3010.40.20 首位和末位零的使用(Use of Leading and Terminal Zeros). 3010.40.30药品中盐的标示(Labeling of Salts of Drugs). 3010.40.40含维生素产品的标示(Labeling Vitamin-Containing Products). 3010.40.50含植物药材的产品的标示(Labeling Botanical-Containing Products)3110.40.60非肠道和局部制剂的标示(Labeling Parenteral And Topical Preparations)3110.40.70电解液的标示(Labeling Electrolytes). 3110.40.80乙醇的标示(Labeling Alcohol). 3110.40.90特殊的胶囊和片剂(Special Capsules and Tablets). 3110.40.100有效期和失效期(expiration date and beyond-use date). 3110.50 USP-NF药典正文中关于包装和储存的指南(Guidelines for Packaging and Storage State ments in USP–NF Monographs). 32General Notices and Requirements(凡例和要求)Change to read:凡例部分为药典的解释和应用提出了基本的假定、定义、默认条件。

2、名词的数(二):单数与复数

2.服装 jeans(牛仔裤) trousers(长裤) shorts(短裤) briefs(内裤) pants(短裤) slacks(休闲裤) pajamas(睡衣)

汉译英: A:我的眼镜在哪里? B:它不就在你的鼻子上戴着嘛!

A: Where are my glasses? B: They are right on your nose!

2) There were many people in the room.

比如当“民族”或“部族”讲时,那就是一个普通名词,有单复数 的变化。比如单数要用不定冠词a修饰,即a people(一个民 族),复数要在词尾加-s,即peoples。例句:

The Chinese are an industrious people. 中华民族是一个勤劳的民族。

二、以-man/-woman/-child结尾的复合名词 以-man/-woman/-child结尾的复合名词变复数时,将man/-woman/-child变为复数。例如: fireman/firemen(消防员) chairwoman/chairwomen(女主席) horseman/horsemen(骑兵) grandchild/grandchildren(孙子/女) policeman/policemen(警察) Englishman/Englishmen(英国人) Frenchman/Frenchmen(法国人) 但是German不是一个合成词,所以其复数形式是在词 尾直接加-s,即Germans。

三、以“辅音字母+y”结尾的名词,变-y为-i,再加-es; 而以“元音字母+y”结尾的名词,则加-s

country/countries, family/families, baby/babies, lady/ladies; play/plays, boy/boys, guy/guys, donkey/donkeys, monkey/monkeys, key/keys等。

errata2

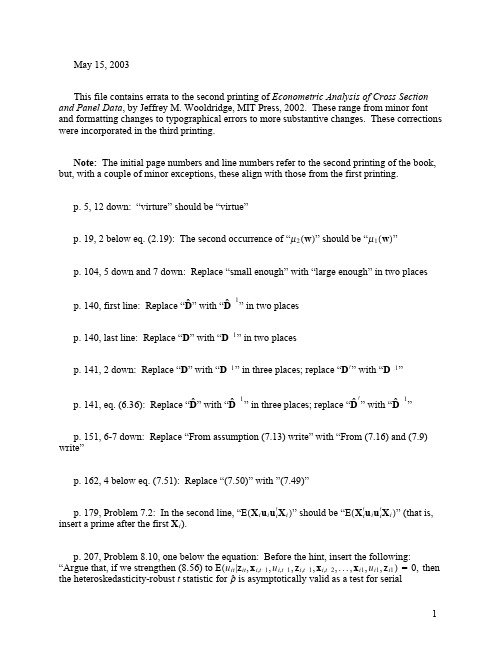

correlation.” p. 224, 4 below Subsection 9.3.2: replace “3SLS” with “3SLS, which is the same as the IV estimator in equation (8.22)” 13 437. 29” 22 437. 29” should be “ p. 236, 6 down: “ p. 236, 2 up: “can produce” should be “will produce” p. 236, 1 up: After “ 13 0" insert “, if Eu 1 |z 0” p. 261, 5 up: Replace “Section 10.4.4” with “Section 10.4.3” p. 270, 3 below eq. (10.51): Replace the second occurrence of “Eü it ü is ” with “Eu it ū i u is ū i ” p. 272, 8 down: Replace “NT K” with “NT K 1 ” p. 289, 2 up from eq. (10.78): after “variables” insert “or aggregate time variables” FE ” insert “a t statistic version of (10.78),” p. 290, 11 down: Before “ i” p. 291, 7 down: after “pooled OLS” add “estimation of (10.79), or with w i in place of w p. 295, Problem 10.11: Replace “LOWBRTH.RAW” with “LOWBIRTH.RAW” p. 296, Problem 10.13: In the first equation replace “ 2 ” with “ 2 u” p. 297, Problem 10.14, 1 below the equation: add “1 K” after “x it ” and “1 M” after “z i ” p. 300, 2 below eq. (11.4): insert “the sequential exogeneity” before “assumption (11.3)” p. 305, the equation just above Subsection 11.1.2: Delete “^” over the secon32, Problem 11.1, part d: Replace “parts b and c” with “parts a and c” ” nor “” should be boldface p. 333, Problem 11.3: Neither “ FE p. 337, Problem 11.14, part a: Replace “Estimate” with “Use the data in EZUNEM.RAW to estimate”

erratas翻译

erratas翻译Erratas 是指书籍、文件或印刷品中的错误或纰漏。

下面是关于erratas 的翻译和一些用法和中英文对照例句:翻译:- 英文:erratas- 中文:勘误表用法:1. 提交勘误表:- 英文:Submit an errata.- 中文:提交勘误表。

2. 修正错误:- 英文:Correct the erratas.- 中文:纠正勘误表中的错误。

3. 更新版本:- 英文:Publish an updated version with the erratas.- 中文:发布一份包含勘误表的更新版。

4. 修订出版物:- 英文:Revise the publication to address the erratas.- 中文:修订出版物以处理勘误表中的错误。

中英文对照例句:1. The author has provided an errata for the book, addressing the errors found in the previous edition.(作者为这本书提供了一份勘误表,解决了上一版中发现的错误。

)2. The publisher released an updated version of the textbook, including all the erratas that were reported by readers.(出版商发布了一份更新版教科书,其中包含了读者报告的所有勘误表。

)3. The author was quick to acknowledge the erratas in the research paper and issued a formal apology.(作者迅速承认了研究论文中的勘误表,并发表了正式道歉。

)4. The editorial team carefully reviewed the manuscript and identified several erratas that needed to be corrected before publication.(编辑团队仔细审查了手稿,并确定了几处在出版之前需要纠正的勘误表。

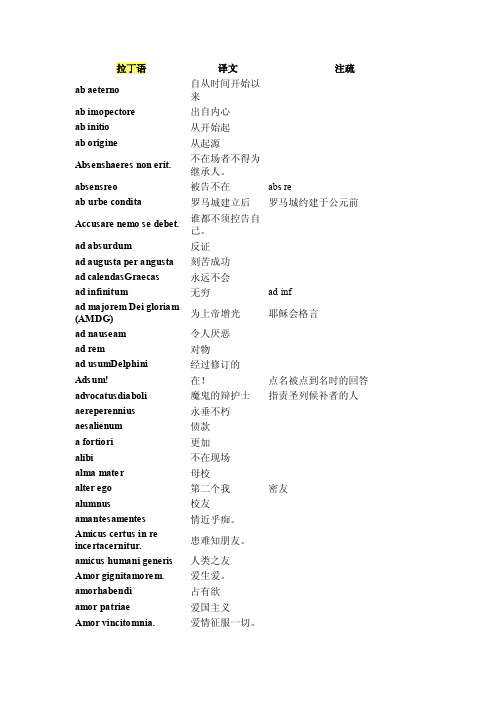

拉丁短语——精选推荐

拉丁语译文注疏ab aeterno自从时间开始以来ab imopectore出自内心ab initio从开始起ab origine从起源Absenshaeres non erit.不在场者不得为继承人。

absensreo被告不在abs reab urbe condita罗马城建立后罗马城约建于公元前Accusare nemo se debet.谁都不须控告自己。

ad absurdum反证ad augusta per angusta刻苦成功ad calendasGraecas永远不会ad infinitum无穷ad infad majorem Dei gloriam(AMDG)为上帝增光耶稣会格言ad nauseam令人厌恶ad rem对物ad usumDelphini经过修订的Adsum!在!点名被点到名时的回答advocatusdiaboli魔鬼的辩护士指责圣列候补者的人aereperennius永垂不朽aesalienum债款a fortiori更加alibi不在现场alma mater母校alter ego第二个我密友alumnus校友amantesamentes情近乎痴。

Amicus certus in reincertacernitur.患难知朋友。

amicus humani generis人类之友Amor gignitamorem.爱生爱。

amorhabendi占有欲amor patriae爱国主义Amor vincitomnia.爱情征服一切。

animal bipesimplume 没有羽毛的两腿动物柏拉图为人类下的定义animus iniuriandi伤害的意图annicurrentis本年anno Domini公元 ..... 年耶稣降生后Annuitcoeptis.神佑我邦。

美国国徽背面ante Christum公元前ante meridiem上午AMapplicatio externa外用法(药)applicatiointerna内用法(药)aqua destillata蒸馏水Aquilla non capitmuscas.老鹰不捉苍蝇。

PIC18F1XK22_LF1XK22 Family Silicon Errata and Data Sheet Clarification

© 2009 Microchip Technology Inc.DS80437B-page 1PIC18F1XK22/LF1XK22The PIC18F1XK22/LF1XK22 family devices that you have received conform functionally to the current Device Data Sheet (DS41365B ), except for the anomalies described in this document.The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in T able 2.The errata described in this document will be addressed in future revisions of the PIC18F1XK22/LF1XK22silicon.Data Sheet clarifications and corrections start on page 6,following the discussion of silicon issues.The silicon revision level can be identified using the current version of MPLAB ® IDE and Microchip’s programmers, debuggers, and emulation tools, which are available at the Microchip corporate web site ().For example, to identify the silicon revision level using MPLAB IDE in conjunction with MPLAB ICD 2 or PICkit™ 3:1.Using the appropriate interface, connect the device to the MPLAB ICD 2 programmer/debugger or PICkit™ 3.2.From the main menu in MPLAB IDE, select Configure>Select Device , and then select the target part number in the dialog box.3.Select the MPLAB hardware tool (Debugger>Select Tool ).4.Perform a “Connect” operation to the device (Debugger>Connect ). Depending on the development tool used, the part number and Device Revision ID value appear in the Output window.The DEVREV values for the various PIC18F1XK22/LF1XK22 silicon revisions are shown in Table 1.Note:This document summarizes all silicon errata issues from all revisions of silicon,previous as well as current.Note:If you are unable to extract the silicon revision level, please contact your local Microchip sales office for assistance.TABLE 1:SILICON DEVREV VALUESPart NumberDevice ID Revision ID for Silicon Revision (1)A1A2A3PIC18F14K224F20h 01h 02h 03h PIC18F13K224F40h 01h 02h 03h PIC18LF14K224F60h 01h 02h 03h PIC18LF13K224F80h01h02h03hNote 1:The Device IDs (DEVID and DEVREV) are located at the last two implemented addresses in program memory. They are shown in hexadecimal in the format “DEVID:DEVREF”.2:Refer to the “PIC18F1XK22/LF1XK22 Flash Memory Programming Specification” (DS41357) for detailed information on Device and Revision IDs for your specific device.PIC18F1XK22/LF1XK22 Family Silicon Errata and Data Sheet ClarificationPIC18F1XK22/LF1XK22DS80437B-page 2© 2009 Microchip Technology Inc.TABLE 2:SILICON ISSUE SUMMARYSilicon Errata Issues1.Module:ADC (Analog-to-DigitalConverter)ADC conversion on AN3/OSC2 will have large INL error up to approximately 8LSb.Work aroundNone for the AN3 pin. For better accuracy, use another analog pin.Affected Silicon Revisions 2.Module:ECCP2.1Changing direction in Full-Bridge mode inserts a dead band time of 4/F OSC *TMR2prescale instead of 1/F OSC *TMR2 prescale as specified in the data sheet.Work around None.Affected Silicon Revisions 2.2In Full-Bridge mode, when PR2=CCPR1L,DC1B<1:0> = 00, and the direction is changed, then the dead time before the modulated output starts is compromised.The modulated signal improperly starts immediately with the direction change and stays on for T OSC *TMR2Presale *DC1B<1:0>.Work aroundAvoid changing direction when the duty cycle is within three least significant steps of 100% duty cycle. Instead, clear the DC1B<1:0> bits before the direction change and then set them to the desired value after the direction change is complete.Affected Silicon Revisions 3.Module:EUSART3.1In Asynchronous Receive mode, the RCIDL bit of the BAUDCON register will properly go low when a low pulse greater than 1/16th of a bit time is received on the RX input. The RCIDL bit will then improperly go high if a low pulse less than 1/16 bit time occurs on the RX input within one bit period after the falling edge of the first pulse. This erratum affects only users monitoring the RCIDL bit as a part of their serial protocol.Module Feature Item Number Issue SummaryAffected Revisions (1)A1A2A3ADC ADC Conversion rge INL error on AN3.X X X ECCP Full Bridge mode2.Delay time with direction change.X X X EUSART — 3.RCIDL bit, clearing the OERR flag, and RX pin.X X X MSSP —4.I 2C™ mode and SPI mode.X XXOscillator LP Osc. 5.Osc. switching and LP Osc. fails at hot.X V REF CV REF output6.RC2 disabled.X ICSP™—7.ICSP works only at V DD >2V.X X X Internal Oscillator —8.Frequency tolerance.XXXNote 1:Only those issues indicated in the last column apply to the current silicon revision.Note:This document summarizes all silicon errata issues from all revisions of silicon,previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (A1).A1A2A3XXXA1A2A3XXXA1A2A3XXXPIC18F1XK22/LF1XK22Work aroundNone.Affected Silicon Revisions3.2The OERR flag of the RCSTA register isreset only by either clearing the CREN bit ofthe RCSTA register or by a device Reset.Clearing the SPEN bit of the RCSTA registerdoes not clear the OERR flag.Work aroundClear the OERR flag by clearing the CRENbit in lieu of clearing the SPEN bit.Affected Silicon Revisions3.3When the SPEN bit of the RCSTA register isset and the CREN bit of the RCSTA registeris clear, the RX pin is not available for gen-eral purpose output. Likewise, when theSPEN bit of the RCSTA register is set andthe TXEN bit of the TXSTA register is clear,the TX pin is not available for general pur-pose output. However, both the RX and TXpins can be read regardless of the state ofthe RCSTA and TXSTA control registers.Work aroundNone.Affected Silicon Revisions4.Module:MSSP (Master SynchronousSerial Port)4.1In I2C™ Master mode, baud rates obtainedby setting SSPADD to a value less than 0x03will cause unexpected operation.Work aroundEnsure SSPADD is set to a value greaterthan or equal to 0x03.Affected Silicon Revisions 4.2In SPI Master mode, when the CKE bit iscleared and the SMP bit is set, the last bit ofthe incoming data stream (bit 0) at the SDIpin will not be sampled properly.Work aroundNone.Affected Silicon Revisions4.3When SPI is enabled in Master mode withCKE=1 and CKP=0, a 1/F OSC wide pulsewill occur on the SCK pin.Work aroundConfigure the SCK pin as an input until afterthe MSSP is setup.Affected Silicon Revisions4.4I2C Master mode, SSPADD values of 0x00,0x01, 0x02 are invalid. The current I2C BaudRate Generator (BSG) is not set up togenerate a clock signal for these values.Work aroundNone.Affected Silicon Revisions4.5I2C Master mode, RCEN bit not cleared byhardware if improper Stop is received on thebus.Work aroundReset the module via clearing and settingthe SSPEN bit of SSPCON1.Affected Silicon RevisionsA1A2A3 X X XA1A2A3 X X XA1A2A3 X X XA1A2A3 X X X A1A2A3 X X XA1A2A3 X X XA1A2A3 X X XA1A2A3 X X X© 2009 Microchip Technology Inc.DS80437B-page 3PIC18F1XK22/LF1XK22DS80437B-page 4© 2009 Microchip Technology Inc.4.6SPI Master mode, when the SPI clock is configured for Timer2/2(SSPCON1<3:0>=0011), the first SPI high time may be short.Work around None.Option 1: Ensure TMR2 value rolls over tozero immediately before writing to SSPBUF.Option 2: Turn Timer2 off and clear TMR2before writing SSPBUF. Enable TMR2 after SSPBUF is written.Affected Silicon Revisions 4.7In any SPI Master mode, SCK =TMR2/2; if SSPBUF is written to while shifting out data,a ninth SCK pulse is incorrectly generated.At that point, the module locks user from writ-ing to the SSPBUF register, but a write attempt will still cause 8 or 9 more SCK pulses to be generated.Work aroundThe WCOL bit of the SSPCON register is correctly set to indicate that there was a write collision. Any time this bit is set the module must be disabled and enabled (toggle SSPEN) to return to correct operation. The bus will remain out of synchronization.Affected Silicon Revisions .5.Module:Oscillator5.1Disabling the Primary External Oscillator circuitry (PRI_SD = 1) immediately following a change in system clock from external LP oscillator to the internal oscillator will halt code execution indefinitely.Work aroundAfter changing from external LP oscillator to the internal oscillator, allow at least two instruction cycles before disabling the Primary External Oscillator circuitry.Affected Silicon Revisions 5.2The external LP Oscillator could fail operation at temperatures above 100degrees Celsius.Work around None.Affected Silicon Revisions 6.Module:Programmable VoltageReferenceThe V REF voltage reference can be output to the device CV REF pin by setting the DAC1OE bit of the VREFCON1 register to ‘1’. When the CV REF pin is enabled, pin RC2 is incorrectly set to Analog mode. The digital output buffer and digital input threshold detector functions of that pin are disabled.Work aroundPin RC2 may only be used for analog functions when the voltage reference output is enabled on the CV REF pin. Ensure that the TRIS bit for pin RA0 is set to ‘1’ for proper operation of the CV REF output.Affected Silicon Revisions 7.Module:In-Circuit Serial Programming™(ICSP™)The device cannot be programmed using ICSP when the device V DD is less than 2.0 volts.Work aroundEnsure that the device voltage is 2.0 volts or higher when programming the device.Affected Silicon Revisions A1A2A3X XXA1A2A3XXXA1A2A3XA1A2A3XA1A2A3XA1A2A3XXXPIC18F1XK22/LF1XK228.Module: Internal OscillatorThe frequency tolerance of the HFINTOSC inter-nal oscillator is +2% to -2.5% from 0-85°C.Work aroundNone.Affected Silicon RevisionsA1A2A3X X X© 2009 Microchip Technology Inc.DS80437B-page 5PIC18F1XK22/LF1XK22DS80437B-page 6© 2009 Microchip Technology Inc.Data Sheet ClarificationsThe following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS41365B ).1.Module: Electrical SpecificationsIn Table 25-10 Comparator Specifications of the data sheet (DS41365B ), the Input Offset Voltage should be +/-50mV in High-Power mode and +/-80mV in Low-Power mode as shown below.TABLE 25-10:COMPARATOR SPECIFICATIONS2.Module:Device OverviewIn Table 1-2, PIC18F1XK22/LF1XK22 Pin Sum-mary of the data sheet (DS41365B ), under pin name RA2, the Buffer Type should be ‘ST ’.Note:Corrections are shown in bold . Where possible, the original bold text formatting has been removed for clarity.Operating Conditions: 1.8V < V DD < 5.5V, -40°C < T A < +125°C (unless otherwise stated).Param No.Sym.CharacteristicsMin.Typ. Max.UnitsComments CM01V IOFF Input Offset Voltage—±7.5±50 mV High-Power mode ——±80 mV Low-Power modeCM02V ICM Input Common Mode Voltage 0—V DD V CM03CMRR Common Mode Rejection Ratio 55——dB CM04T RESP Response Time—150400ns Note 1CM05T MC 2OVComparator Mode Change to Output Valid*——10μs*These parameters are characterized but not tested.Note 1:Response time measured with one comparator input at V DD /2, while the other input transitions from V SS to V DD .PIC18F1XK22/LF1XK22 APPENDIX A:DOCUMENTREVISION HISTORYRev. A Document (3/2009)Initial release of this document.Rev. B Document (5/2009)Revised Table 1; Added Table 2; Added Module 8:Internal Oscillator.Added Data Sheet Clarifications Module 1: ElectricalSpecifications and Module 2: Device Overview.© 2009 Microchip Technology Inc.DS80437B-page 7PIC18F1XK22/LF1XK22NOTES:DS80437B-page 8© 2009 Microchip Technology Inc.© 2009 Microchip Technology Inc.DS80437B-page 9Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION,INCLUDING BUT NOT LIMITED TO ITS CONDITION,QUALITY , PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE . Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer’s risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims,suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.TrademarksThe Microchip name and logo, the Microchip logo, dsPIC, K EE L OQ , K EE L OQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV , MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, , dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP , ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP , Omniscient Code Generation, PICC, PICC-18, PICkit,PICDEM, , PICtail, PIC 32 logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.All other trademarks mentioned herein are property of their respective companies.© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.Printed on recycled paper.Note the following details of the code protection feature on Microchip devices:•Microchip products meet the specification contained in their particular Microchip Data Sheet.•Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.•There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to ourknowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.•Microchip is willing to work with the customer who is concerned about the integrity of their code.•Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as “unbreakable.”Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company’s quality system processes and procedures are for its PIC ® MCUs and dsPIC ® DSCs, K EE L OQ ® code hoppingdevices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip’s quality system for the design and manufacture of development systems is ISO 9001:2000 certified.AMERICASCorporate Office2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200Fax: 480-792-7277 Technical Support: Web Address: AtlantaDuluth, GATel: 678-957-9614Fax: 678-957-1455BostonWestborough, MATel: 774-760-0087Fax: 774-760-0088 ChicagoItasca, ILTel: 630-285-0071Fax: 630-285-0075 Cleveland Independence, OHTel: 216-447-0464Fax: 216-447-0643DallasAddison, TXTel: 972-818-7423Fax: 972-818-2924DetroitFarmington Hills, MITel: 248-538-2250Fax: 248-538-2260 KokomoKokomo, INTel: 765-864-8360Fax: 765-864-8387Los AngelesMission Viejo, CATel: 949-462-9523Fax: 949-462-9608Santa ClaraSanta Clara, CATel: 408-961-6444Fax: 408-961-6445 TorontoMississauga, Ontario, CanadaTel: 905-673-0699Fax: 905-673-6509ASIA/PACIFICAsia Pacific OfficeSuites 3707-14, 37th FloorTower 6, The GatewayHarbour City, KowloonHong KongTel: 852-2401-1200Fax: 852-2401-3431Australia - SydneyTel: 61-2-9868-6733Fax: 61-2-9868-6755China - BeijingTel: 86-10-8528-2100Fax: 86-10-8528-2104China - ChengduTel: 86-28-8665-5511Fax: 86-28-8665-7889China - Hong Kong SARTel: 852-2401-1200Fax: 852-2401-3431China - NanjingTel: 86-25-8473-2460Fax: 86-25-8473-2470China - QingdaoTel: 86-532-8502-7355Fax: 86-532-8502-7205China - ShanghaiTel: 86-21-5407-5533Fax: 86-21-5407-5066China - ShenyangTel: 86-24-2334-2829Fax: 86-24-2334-2393China - ShenzhenTel: 86-755-8203-2660Fax: 86-755-8203-1760China - WuhanTel: 86-27-5980-5300Fax: 86-27-5980-5118China - XiamenTel: 86-592-2388138Fax: 86-592-2388130China - XianTel: 86-29-8833-7252Fax: 86-29-8833-7256China - ZhuhaiTel: 86-756-3210040Fax: 86-756-3210049ASIA/PACIFICIndia - BangaloreTel: 91-80-3090-4444Fax: 91-80-3090-4080India - New DelhiTel: 91-11-4160-8631Fax: 91-11-4160-8632India - PuneTel: 91-20-2566-1512Fax: 91-20-2566-1513Japan - YokohamaTel: 81-45-471- 6166Fax: 81-45-471-6122Korea - DaeguTel: 82-53-744-4301Fax: 82-53-744-4302Korea - SeoulTel: 82-2-554-7200Fax: 82-2-558-5932 or82-2-558-5934Malaysia - Kuala LumpurTel: 60-3-6201-9857Fax: 60-3-6201-9859Malaysia - PenangTel: 60-4-227-8870Fax: 60-4-227-4068Philippines - ManilaTel: 63-2-634-9065Fax: 63-2-634-9069SingaporeTel: 65-6334-8870Fax: 65-6334-8850Taiwan - Hsin ChuTel: 886-3-6578-300Fax: 886-3-6578-370Taiwan - KaohsiungTel: 886-7-536-4818Fax: 886-7-536-4803Taiwan - TaipeiTel: 886-2-2500-6610Fax: 886-2-2508-0102Thailand - BangkokTel: 66-2-694-1351Fax: 66-2-694-1350EUROPEAustria - WelsTel: 43-7242-2244-39Fax: 43-7242-2244-393Denmark - CopenhagenTel: 45-4450-2828Fax: 45-4485-2829France - ParisTel: 33-1-69-53-63-20Fax: 33-1-69-30-90-79Germany - MunichTel: 49-89-627-144-0Fax: 49-89-627-144-44Italy - MilanTel: 39-0331-742611Fax: 39-0331-466781Netherlands - DrunenTel: 31-416-690399Fax: 31-416-690340Spain - MadridTel: 34-91-708-08-90Fax: 34-91-708-08-91UK - WokinghamTel: 44-118-921-5869Fax: 44-118-921-5820 W ORLDWIDE S ALES AND S ERVICE03/26/09DS80437B-page 10© 2009 Microchip Technology Inc.。

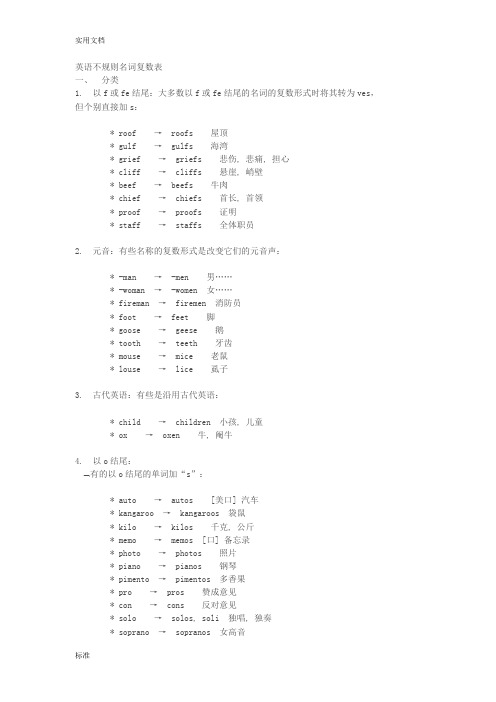

英语名词变复数表

英语不规则名词复数表一、分类1.以f 或fe 结尾:大多数以f 或fe 结尾的名词的复数形式时将其转为ves,但个别直接加s:roof →roofs 屋顶[ru:f]gulf →gulfs 海湾[gʌlf]grief →griefs 悲伤, 悲痛, 担心英[ɡriːf ] 美[grif]cliff →cliffs 悬崖, 峭壁[klif]beef →beefs 牛肉英[bi:f] 美[bif]chief →chiefs 首长, 首领[tʃi:f]proof →proofs 证明英[pru:f] 美[pruf]staff →staffs 全体职员英[stɑːf]美[stæf; stɑf]2.元音:有些名称的复数形式是改变它们的元音声:man →men 男[mæn]woman →women 女[ˈwʊmən]fireman →firemen 消防员[ˈfaɪəmən]foot →feet 脚[fʊt]goose →geese 鹅[guːs]tooth →teeth 牙齿英[tu:θ] 美[tuθ]mouse →mice 老鼠[maus]louse →lice 虱子英[laʊs] 美[laʊs; laʊz]3.古代英语:有些是沿用古代英语:child →children 小孩, 儿童[tʃaɪld]ox →oxen 牛, 阉牛英[ɒks] 美[ɑks]4.以o 结尾:有的以o 结尾的单词加“s”:auto →autos [美口] 汽车英[ˈɔːtəʊ] 美[ˈɔtoʊ; ˈɑtoʊ]kangaroo →kangaroos 袋鼠英[ˌkæŋɡəˈruː]美[ˌkæŋgəˈru]kilo →kilos 千克, 公斤['ki:ləu]memo →memos [口] 备忘录英[ˈmɛməʊ; ˈmiːməʊ] 美[ˈmɛmoʊ]photo →photos 照片['fəutəu]piano →pianos 钢琴英[pɪˈænəʊ] 美[piˈɑnoʊ; pjˈænoʊ ]pimento →pimentos 多香果[pi'mentəu] n. 1.蒲桃树的干果制成的香料2.西班牙甘椒pro →pros 赞成意见英[prəʊ] 美[proʊ]con →cons 反对意见英[kɒn] 美[kɑn]solo →solos, soli 独唱, 独奏英[ˈsəʊləʊ] 美[ˈsoʊloʊ]soprano →sopranos 女高音英[səˈprɑːnəʊ] 美[səˈprænoʊ]studio →studios 工作室英[ˈstjuːdɪˌəʊ] 美[ˈstudiˌoʊ; ˈstjudioʊ]tattoo →tattoos 文身英[tæˈtuː]美[tæˈtu]video →videos 视频英[ˈvɪdɪˌəʊ] 美[ˈvɪdiˌoʊ]zoo →zoos 动物园英[zuː]美[zu]bamboo →bamboos 竹子[bæm'bu:]radio →radios 收音机英[ˈreɪdɪəʊ] 美[ˈreɪdiˌoʊ]mulatto →mulattos 白黑混血儿[mju'lætəu]有的则加“es”:echo →echoes 回声, 反响英[ˈɛkəʊ] 美[ˈɛkoʊ]embargo →embargoes 禁运, 禁运令英[ɛmˈbɑːɡəʊ] 美[ɛmˈbɑrgoʊ; ɪmˈbɑrgoʊ]hero →heroes 英雄英['hiərəu] 美['hɪro]potato →potatoes 土豆英[pəˈteɪtəʊ] 美[pəˈteɪtoʊ; pəˈteɪtə]tomato →tomatoes 番茄英[tə'mɑ:təu] 美[tə'meitəu]torpedo →torpedoes 鱼雷, 水雷英[tɔːˈpiːdəʊ] 美[tɔrˈpidoʊ]veto →vetoes 否决, 否决权['vi:təu]negro →negroes 黑人英[ˈniːgrəʊ] 美[ˈnigroʊ]jingo →jingoes 侵略主义,沙文主义['dʒingəu]mango →mangoes 芒果英[ˈmæŋɡəʊ] 美[ˈmæŋgoʊ]有的两种都可以:buffalo →buffalos / buffaloes / buffalo 水牛英[ˈbʌfəˌləʊ] 美[ˈbʌfəˌloʊ]cargo →cargos / cargoes (船/飞机的)货物英[ˈkɑːɡəʊ] 美[ˈkɑrgoʊ]halo →halos / haloes 光环英[ˈheɪləʊ] 美[ˈheɪloʊ]mosquito →mosquitos / mosquitoes 蚊子[məs'ki:təu]motto →mottos / mottoes 箴言, 格言['mɔtəu]no →nos / noes 没有英[nəʊ] 美[noʊ]tornado →tornados / tornadoes 龙卷风英[tɔːˈneɪdəʊ] 美[tɔrˈneɪdoʊ]volcano →volcanos / volcanoes 火山英[vɒlˈkeɪnəʊ] 美[vɑlˈkeɪnoʊ; vɔlˈkeɪnoʊ]zero →zeros / zeroes 零英[ˈzɪərəʊ] 美[ˈzɪroʊ; ˈziroʊ]commando →commands / commandoes 突击员英[kəˈmɑːndəʊ] 美[kəˈmændoʊ; kəˈmɑndoʊ ]5.不变:有的则不变:cod →cod 鳕鱼英[kɒd] 美[kɑd]deer →deer 鹿[diə]fish →fish 鱼, 鱼类[fɪʃ]offspring →offspring 子孙, 后裔, 幼崽英['ɔ:fspriŋ]美['ɔf,sprɪŋ]perch →perch 鲈鱼英[pɜːtʃ] 美[pɜrtʃ]sheep →sheep 绵羊英[ʃiːp]美[ʃip]trout →trou 鲑鱼[traʊt]bison →bison 野牛['baisn]moose →moose 驼鹿英[muːs]美[mus]aircraft →aircraft 飞机, 飞行器英[ˈɛəˌkrɑːft]美[ˈɛrˌkræft]barracks →barracks 兵营[ˈbærəks]crossroads →crossroads 十字路口英[ˈkrɒsˌrəʊdz] 美[ˈkrɔsˌroʊdz]dice →dice 骰子[dais]gallows →gallows 绞刑架['gæləuz]headquarters →headquarters 总部英[ˌhɛdˈkwɔːtəz] 美[ˈhɛdˌkwɔrtərz]means →means 方法, 手段, 途径英[miːnz]美[minz]series →series 系列英[ˈsɪəriːz]美[ˈsɪriz]species →species 物种['spi:ʃiz]6.借用单词:英语中有些单词是借用其他语言的。

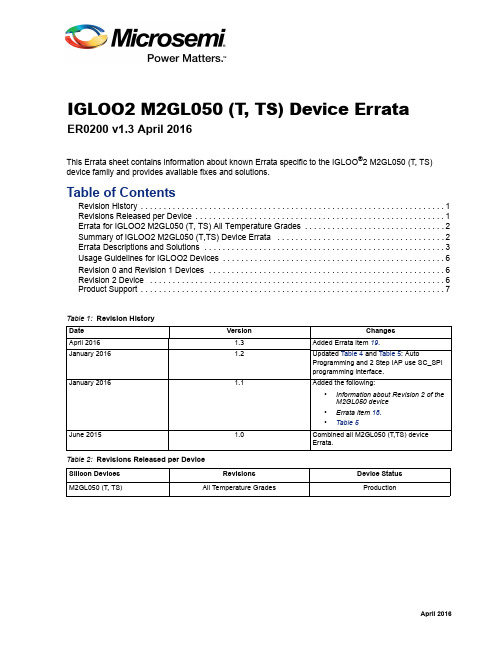

IGLOO2 M2GL050 (T, TS) 设备 Errata 表说明书

IGLOO2 M2GL050 (T , TS) Device ErrataER0200 v1.3 April 2016April 2016This Errata sheet contains information about known Errata specific to the IGLOO ®2 M2GL050 (T, TS) device family and provides available fixes and solutions.Table of ContentsRevision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1Revisions Released per Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1Errata for IGLOO2 M2GL050 (T, TS) All Temperature Grades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2Summary of IGLOO2 M2GL050 (T,TS) Device Errata . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2Errata Descriptions and Solutions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3Usage Guidelines for IGLOO2 Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6Revision 0 and Revision 1 Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6Revision 2 Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6Product Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7Table 1: Revision HistoryDate Version ChangesApril 2016 1.3Added Errata item 19.January 20161.2Updated Table 4 and Table 5: AutoProgramming and 2 Step IAP use SC_SPI programming interface.January 2016 1.1Added the following:•Information about Revision 2 of the M2GL050 device •Errata item 18.•Table 5June 20151.0Combined all M2GL050 (T,TS) device Errata.Table 2: Revisions Released per DeviceSilicon Devices Revisions Device Status M2GL050 (T, TS)All Temperature GradesProduction2IGLOO2 M2GL050 (T, TS) Device Errata ER0200 v1.3 April 2016Errata for IGLOO2 M2GL050 (T, TS) All Temperature GradesTable 3 lists the specific device Errata and the affected IGLOO2 M2GL050 (T, TS) revisions of all temperature grade devices .Table 3: Summary of IGLOO2 M2GL050 (T, TS) Device ErrataErrata No.ErrataSilicon Revisions M2GL050 (T, TS)Software ErrataRev (0, 1)Rev 21.MDDR and FDDR AXI interface does not support exclusive access X X –2.Apply DEVRST_N after ISP programmingX ––3.AXI wrap transfers with more than 32 bytes in burst mode are not supported for MDDR and FDDRX X –4.The MDDR/FDDR controller must be used with sequential burst mode with BL = 8 and PHY = 32, or PHY = 16X X –5.HPMS may reset when ENC_DATA_AUTHENTICATION or DEVICE_INFO STAPL commands are sentX ––6.VPP must be set to 2.5 V when programming/writing the eNVM at Industrial temperature rangeX ––7.Over-voltage support on MSIOs during Flash*Freeze mode X ––8.Verification of the FPGA fabric at junction temperatures higher than 50°C erroneously indicates a failureX ––9.DDR_OUT and I/O-Reg functional Errata due to a software bug ––X 10.Dedicated differential I/O driving the reference clock of the CCC may cause a functional failure due to a software bug––X 11.NVM Ready bit in eNVM Status register can generate a false READY signalX ––12.Power-up Digest is not supportedX ––13.Programming of the eNVM must only occur as part of a bitstream also containing the FPGA fabric––X 14.Updating eNVM from the FPGA fabric requires changes in the NV_FREQRNG registerX X –15.SYSCTRL_RESET_STATUS macro is not supported X X –16.Zeroization is not supportedX X –17.PCIe Hot Reset support requires a soft reset solutionX X –18.The DDR I/Os in M2GL050 (T, TS)-FG896 are non-compliant with the DDR3 standardX X –19.For S (security) grade devices, user must not enable write protection for Protected 4 K Regions, also known as Special Sectors in the eNVMXX–Note:Contact Microsemi SoC technical support , if you have additional questions. To order a specific die, contact your localMicrosemi sales office.IGLOO2 M2GL050 (T, TS) Device ErrataER0200 v1.3 April 20163Errata Descriptions and Solutions1.MDDR and FDDR AXI interface does not support exclusive accessThe MDDR and FDDR AXI interface in the M2GL050 device is compliant with AMBA AXI Protocol Specification v1.0, except for the exclusive access functionality. The future version of the Errata will have an updated information about the exclusive access functionality for the AXI interface.2.Apply DEVRST_N after ISP programmingM2GL050 devices support device programming in JTAG, Slave SPI, and ISP programming modes. However, after ISP programming, DEVRST_N needs to be asserted to reset the device or power cycle the device to run the new design.3.AXI wrap transfers with more than 32 bytes in burst mode are not supported for MDDR and FDDRDo not use wrap transfers with more than 32 bytes.4.The MDDR/FDDR controller must be used with sequential burst mode with BL = 8 and PHY = 32, or PHY = 16Though the MDDR and FDDR controllers in the M2GL050 devices support various burst modes/ lengths and PHY settings (as specified in the UG0446: SmartFusion2 and IGLOO2 FPGA High Speed DDR Interfaces User Guide), only a subset of these settings are supported.Recommendation:Only use sequential burst mode with BL = 8 for PHY16, or PHY32 modes for the MDDR or FDDR.5.HPMS may reset when ENC_DATA_AUTHENTICATION or DEVICE_INFO STAPL commands are sentThe HPMS resets after executing one of the following STAPL actions:•ENC_DATA_AUTHENTICATION •DEVICE_INFOAdditionally, if any of these actions are executed while a SmartDebug session is active, HPMS resets are observed.6.VPP must be set to 2.5 V when programming/writing the eNVM at Industrial temperature rangeVPP can be set to 2.5 V or 3.3 V. However, when writing or programming the eNVM of the M2GL050 devices below 0°C, VPP must be set to 2.5 V.Refer to the DS0128: IGLOO2 FPGA and SmartFusion2 SoC FPGA Datasheet for VPP minimum and maximum settings. Note that the eNVM reading with VPP set to 3.3 V or 2.5 V operates as intended.7.Over-voltage support on MSIOs during Flash*Freeze modeWhen the input voltage is driven above the reference voltage for that bank, additional current can be consumed in Flash*Freeze mode.4IGLOO2 M2GL050 (T, TS) Device Errata ER0200 v1.3 April 20168.Verification of the FPGA fabric at junction temperatures higher than 50°C erroneously indicates a failureStandalone verification (STAPL VERIFY action) must run at temperatures lower than 50°C. If aVERIFY action is run at temperatures higher than 50°C, a false verify failure may be reported. Note that the Check Digest system services can be used to confirm design integrity at temperatures within the recommended operation conditions.9.DDR_OUT and I/O-Reg functional Errata due to a software bugThis Errata is applicable only if you have created or updated the design using Libero ® SoC v11.1 SP1 or v11.1 SP2.The corresponding I/O does not function properly in the silicon due to the wrong software implementation of the I/O macro, if you have one of the following in the design:•If you use DDR_OUT macro in the design•If you combine an output or output enable register with an I/O using the PDC command set_io<portName> -register yesSolution:Both Errata are fixed in Libero SoC v11.1 SP3. Migrate the design to Libero SoC v11.1 SP3 or a newer version, and re-run Compile and Layout.10.Dedicated differential I/O driving the reference clock of the CCC may cause afunctional failure due to a software bugIf the design has a dedicated differential I/O pair driving the reference clock of the CCC, the input clock may not propagate to CCC due to a software bug and the device fails during silicon testing. There are several options to drive the ref clock of the CCC. One of the options is to drive from"Dedicated Input PAD x" (x = 0 to 3); this uses hardwired routing. In this option, choose single-ended I/O or differential I/O as the ref clock. This Errata exists when you choose the differential I/O option (dedicated differential I/O is used as CCC reference clock input).This Errata cannot be detected in any functional simulation, and can only be detected in silicon testing.Solution:The Errata is fixed in the Libero SoC 11.1 SP3. Migrate the design to Libero SoC 11.1 SP3 or newer version, and re-run Compile and Layout.11.NVM Ready bit in eNVM Status register can generate a false READY signalIf you send an instruction to the eNVM controller and then start polling the READY signal (bit0 of the eNVM Status register) to check when the eNVM controller is ready for the next function, the first assertion of the READY signal occurs when the eNVM controller is not yet ready, resulting in the generation of a false READY signal. However, the immediate next assertion of the READY signal correctly indicates that the eNVM controller is ready.Workaround:Add an extra eNVM Status bit read that polls/reads the eNVM Status bit twice as READY .12.Power-up Digest is not supportedWorkaround:Use NVM Data Integrity Check System service after the device is switched ON, and check the data integrity.IGLOO2 M2GL050 (T, TS) Device ErrataER0200 v1.3 April 2016513.Programming of the eNVM must only occur as part of a bitstream alsocontaining the FPGA fabricThe Bitstream Configuration Dialog Box in the Libero SoC allows the user to program eNVM and the FPGA fabric separately. However, for the current production of IGLOO2 FPGAs, the user needs to program the eNVM along with the FPGA fabric. The fabric can be programmed separately if needed.Solution:The Errata is fixed in the Libero SoC 11.1 SP3. Migrate the design to the Libero SoC 11.1 SP3 or newer version, and re-run Compile and Layout.14.Updating eNVM from the FPGA fabric requires changes in the NV_FREQRNGregisterWhen updating the eNVM from the FPGA fabric, NV_FREQRNG register must be changed from 0x07(default) to 0x0F, eNVM reads are not affected.15.SYSCTRL_RESET_STATUS macro is not supported 16.Zeroization is not supported17.PCIe Hot Reset support requires a soft reset solutionOn the IGLOO2 devices, a PCIe ® Hot Reset requires a soft FPGA logic reset scheme which clears the sticky bits of the PCI configuration space.Workaround:The application note AC437: Implementing PCIe Reset Sequence in SmartFusion2 and IGLOO2 Devices describes the PCIe Hot Reset reset scheme. However, this reset scheme causes PCIe violations in some cases.•At Gen1 rates, there are no violations.•At Gen2 rates, there are two PCIe CV violations.–Test case 1: TD_1_7 (Advanced Error Reporting Capability)–Test case 2: TD_1_41 (LinkCap2Control2Status2 Reg)18.The DDR I/Os in M2GL050 (T, TS)-FG896 are non-compliant with the DDR3standardThe DDR controller in the M2GL050-FG896 device is non-compliant with the DDR3 standard. Contact SoC tech support for additional information.19.For S (security) grade devices, user must not enable write protection forProtected 4 K Regions, also known as Special Sectors in the eNVMFor S (security) devices, there are two or four 4 KB regions per eNVM array that can be protected for read and write, these regions are known as Protected 4 K Regions or Special Sectors. If writeprotection is enabled for any of these regions, none of the locked pages inside the same eNVM block can be unlocked.6IGLOO2 M2GL050 (T, TS) Device Errata ER0200 v1.3 April 2016Usage Guidelines for IGLOO2 DevicesMicrosemi recommends the following conditions for the IGLOO2 device usage.1. Programming SupportThere may be package dependencies that may not expose certain programming interfaces. Refer to the DS0124: IGLOO2 Pin Descriptions Datasheet for device/package specific features.2. SHA-256 System ServiceMicrosemi recommends the message required to be on byte boundary when using SHA-256 System Service for the IGLOO2 devices.3. Accessing the PCIe Bridge Register in High-speed Serial InterfaceThe PCIe Bridge registers must not be accessed before the PHY is ready. Wait for the PHY_READY signal (which indicates when PHY is ready) to be asserted before updating the PCIe Bridge registers.The PHY_READY signal is normally asserted within 200 μs after the device is powered up. Wait for 200 μs before accessing the PCIe Bridge registers.Table 4: Revision 0 and Revision 1 DevicesProgramming Mode JTAG SPI Slave AutoProgramming Auto Update2 Step IAP Programming RecoveryProgramming Interface JTAG SC_SPI SC_SPI SPI_0SC_SPI SPI_0M2GL050 (T,TS)YesYesNoNoNoNoTable 5: Revision 2 DeviceProgramming Mode JTAG SPI Slave AutoProgramming Auto Update2 Step IAP Programming RecoveryProgramming Interface JTAG SC_SPI SC_SPI SPI_0SC_SPI SPI_0M2GL050 (T,TS)YesYesYesNoYesNoIGLOO2 M2GL050 (T, TS) Device ErrataER0200 v1.3 April 20167Product SupportMicrosemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.Customer ServiceContact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.From North America, call 800.262.1060From the rest of the world, call 650.318.4460Fax, from anywhere in the world 650. 318.8044Customer Technical Support CenterMicrosemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creatingapplication notes, answers to common design cycle questions, documentation of known Errata and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.Technical SupportFor Microsemi SoC Products Support, visit/products/fpga-soc/design-support/fpga-soc-supportWebsiteYou can browse a variety of technical and non-technical information on the SoC home page , at /products/fpga-soc/fpga-and-soc .Contacting the Customer Technical Support CenterHighly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.EmailYou can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.The technical support email address is **********************.My CasesMicrosemi SoC Products Group customers may submit and track technical cases online by going to My Cases .Outside the U.S.Customers needing assistance outside the US time zones can either contact technical support via email(**********************) or contact a local sales office. Visit About Us for sales office listings and corporate contacts.8IGLOO2 M2GL050 (T, TS) Device Errata ER0200 v1.3 April 2016ITAR Technical SupportFor technical support on RH and RT FPGAs that are regulated by International Traffic in ArmsRegulations (ITAR), contact us via **********************. Alternatively, within My Cases, select Yes in the ITAR drop-down list. For a complete list of ITAR-regulated Microsemi FPGAs, visit the ITAR web page.Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.Microsemi Corporate Headquarters One Enterprise, Aliso Viejo,CA 92656 USAWithin the USA : +1 (800) 713-4113 Outside the USA : +1 (949) 380-6100Sales : +1 (949) 380-6136Fax : +1 (949) 215-4996E-mail: ***************************© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks andservice marks are the property of their respective owners.Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services.Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at .55900200-1.3/04.16。

英语不规则名词复数表

英语不规则名词复数表一、分类1. 以f或fe结尾:大多数以f或fe结尾的名词的复数形式时将其转为ves,但个别直接加s:* roof →roofs 屋顶* gulf →gulfs 海湾* grief →griefs 悲伤, 悲痛, 担心* cliff →cliffs 悬崖, 峭壁* beef →beefs 牛肉* chief →chiefs 首长, 首领* proof →proofs 证明* staff →staffs 全体职员2. 元音:有些名称的复数形式是改变它们的元音声:* -man →-men 男……* -woman →-women 女……* fireman →firemen 消防员* foot →feet 脚* goose →geese 鹅* tooth →teeth 牙齿* mouse →mice 老鼠* louse →lice 虱子3. 古代英语:有些是沿用古代英语:* child →children 小孩, 儿童* ox →oxen 牛, 阉牛4. 以o结尾:有的以o结尾的单词加“s”:* auto →autos [美口] 汽车* kangaroo →kangaroos 袋鼠* kilo →kilos 千克, 公斤* memo →memos [口] 备忘录* photo →photos 照片* piano →pianos 钢琴* pimento →pimentos 多香果* pro →pros 赞成意见* con →cons 反对意见* solo →solos, soli 独唱, 独奏* soprano →sopranos 女高音* studio →studios 工作室* tattoo →tattoos 文身* video →videos 视频* zoo →zoos 动物园* bamboo →bamboos 竹子⌝有的则加“es”:* echo →echoes 回声, 反响* embargo →embargoes 禁运, 禁运令* hero →heroes 英雄* potato →potatoes 土豆* tomato →tomatoes 番茄* torpedo →torpedoes 鱼雷, 水雷* veto →vetoes 否决, 否决权* negro →negroes 黑人⌝有的两种都可以:* buffalo →buffalos / buffaloes / buffalo 水牛* cargo →cargos / cargoes (船/飞机的)货物* halo →halos / haloes 光环* mosquito →mosquitos / mosquitoes 蚊子* motto →mottos / mottoes 箴言, 格言* no →nos / noes 没有* tornado →tornados / tornadoes 龙卷风* volcano →volcanos / volcanoes 火山* zero →zeros / zeroes 零* commando →commands / commandoes突击员5. 不变:有的则不变:* cod →cod 鳕鱼* deer →deer 鹿* fish →fish 鱼, 鱼类* offspring →offspring 子孙, 后裔, 幼崽* perch →perch 鲈鱼* sheep →sheep 绵羊* trout →trou 鲑鱼* bison →bison 野牛* moose →moose 驼鹿* aircraft →aircraft 飞机, 飞行器* barracks →barracks 兵营* crossroads →crossroads 十字路口* dice →dice 骰子* gallows →gallows 绞刑架* headquarters →headquarters 总部* means →means 方法, 手段, 途径* series →series 系列* species →species 物种6. 借用单词:英语中有些单词是借用其他语言的。

802[1].3ae-2002_errata

![802[1].3ae-2002_errata](https://img.taocdn.com/s3/m/b190af2f7375a417866f8fad.png)

IEEE 802.3ae™-2002(Amendment to IEEE Std 802.3™2002)Corrections toIEEE Standard for Information technology—Telecommunications and information exchange between systems—Local and metropolitan area networks—Specific requirementsPart 3: Carrier Sense Multiple Access withCollision Detection (CSMA/CD) Access Methodand Physical Layer SpecificationsAmendment: Media Access Control (MAC) Parameters, Physical Layers, and Management Parameters for 10 Gb/s OperationS ponsorLAN/MAN Standards Committeeof theIEEE Computer SocietyCorrection SheetIssued 20 July 2004Copyright © 2004 by the Institute of Electrical and Electronics Engineers, Inc.All rights reserved. Published 2004. Printed in the United States of America.This correction sheet may be freely reproduced and distributed in order to maintainthe utility and currency of the underlying Standard. This correction sheet may notbe sold, licensed or otherwise distributed for any commercial purposes whatso-ever. The content of this correction sheet may not be modified.4.2.7 – 4.2.9 is incorrect and should be replaced with the following 4.2.7 – 4.2.9:4.2.7 Global declarationsChange 4.2.7 and its related subclauses to read as follows:This subclause provides detailed formal specifications for the CSMA/CD MAC sublayer. It is a specification of generic features and parameters to be used in systems implementing this media access method. Subclause 4.4 provides values for these sets of parameters for recommended implementations of this media access mechanism.4.2.7.1 Common constants, types, and variablesThe following declarations of constants, types and variables are used by the frame transmission and reception sections of each CSMA/CD sublayer:constaddressSize = ... ; {48 bits in compliance with 3.2.3}addressSize = 48; {In bits, in compliance with 3.2.3}lengthOrTypeSize = 16; {iIn bits}clientDataSize = ...; {in bits, MAC client Data, see 4.2.2.2, (1)(c)}clientDataSize = ...; {In bits, size of MAC client data; see 4.2.2.2, a) 3)}padSize = ...; {iIn bits, = max (0, minFrameSize – (2 x addressSize + lengthOrTypeSize +clientDataSize + crcSize))} dataSize = ...; {iIn bits, = clientDataSize + padSize}crcSize = 32; {In bits, 32-bit CRC = 4 octets}frameSize = ...; {in bits, = 2 x addressSize + lengthOrTypeSize + dataSize + crcSize, see 4.2.2.2, (1)}frameSize = ...; {In bits, = 2 x addressSize + lengthOrTypeSize + dataSize + crcSize; see 4.2.2.2, a)}minFrameSize = ... ; {iIn bits, implementation-dependent, see 4.4}maxUntaggedFrameSize = ... ; {iIn octets, implementation-dependent, see 4.4}qTagPrefixSize = 4; {iIn octets, length of QTag Prefix, see 3.5}extend = ...; {Boolean, true if (slotTime – minFrameSize) > 0, false otherwise}extensionBit = ...; {aA nondata value which is used for carrier extension and interframe during bursts}extensionErrorBit = ...; {aA nondata value which is used to jam during carrier extension}minTypeValue = 1536; {mMinimum value of the Length/Type field for Type interpretation}maxValidFrame = maxUntaggedFrameSize – (2 x addressSize + lengthOrTypeSize + crcSize) / 8;{iIn octets, the maximum length of the MAC client data field. This constant isdefined for editorial convenience, as a function of other constants}slotTime = ... ; {In bit times, unit of time for collision handling, implementation-dependent, see 4.4}preambleSize = ...; {56 bits, see 4.2.5}preambleSize = 56; {In bits, see 4.2.5}sfdSize = 8; {8 bitIn bits, start frame delimiter}headerSize = ...; {64 bits, sum of preambleSize and sfdSize}headerSize = 64; {In bits, sum of preambleSize and sfdSize}typeBit = 0..1(0, 1);PhysicalBit = 0,1, extensionBit, extensionErrorBit(0, 1, extensionBit, extensionErrorBit);{bBits transmitted to the Physical Layer can be either 0, 1, extensionBit orextensionErrorBit. Bits received from the Physical Layer can be either 0, 1or extensionBit.}AddressValue = array [1..addressSize] of Bit;LengthOrTypeValue = array [1..lengthOrTypeSize] of Bit;DataValue = array [1..dataSize] of Bit; {Contains the portion of the frame that starts with the first bitfollowing the Length/Type field and ends with the last bitprior to the FCS field. For VLAN Tagged frames, this valueincludes the Tag Control Information field and the originalMAC client Length/Type field. See 3.5}CRCValue = array [1..crcSize] of Bit;PreambleValue = array [1..preambleSize] of Bit;SfdValue = array [1..sfdSize] of Bit;ViewPoint = (fields, bits); {Two ways to view the contents of a frame}HeaderViewPoint = (headerFields, headerBits);Frame = record {Format of Media Access frame}case view: ViewPoint offields: (destinationField: AddressValue;sourceField: AddressValue;lengthOrTypeField: LengthOrTypeValue;dataField: DataValue;fcsField: CRCValue);bits: (contents: array [1..frameSize] of Bit)end; {Frame}Header = record {Format of preamble and start frame delimiter}case headerView : HeaderViewPoint ofheaderFields : (preamble : PreambleValue;sfd : SfdValue);headerBits : (headerContents : array [1..headerSize] of Bit)headerBits: (headerContents: array [1..headerSize] of Bit)end; {dDefines header for MAC frame}varhalfDuplex: Boolean; {Indicates the desired mode of operation. halfDuplex is a static variable; its valueshall only be changed by the invocation of the Initialize procedure}its value does not change between invocations of the Initialize procedure}4.2.7.2 Transmit state variablesThe following items are specific to frame transmission. (See also 4.4.)constinterFrameSpacing = ... ; {In bit times, minimum time gap between frames. Equal to interFrameGap,see 4.4}interFrameSpacingPart1 = ... ; {In bit times, duration of the first portion of interFrameSpacing. In therange of 0 up to 2/3 of interFrameSpacing}interFrameSpacingPart2 = ... ; {In bit times, duration of the remainder of interFrameSpacing. Equal tointerFrameSpacing – interFrameSpacingPart1}interFrameSize = ... ; {in bits, length of interframe fill during a burst. Equal to interFrameGapdivided by the bit period}ifsStretchRatio = ...; {In bits, determines the number of bits in a frame that require one octet ofinterFrameSpacing extension, when ifsStretchMode is enabled; implementationdependent, see 4.4}attemptLimit = ... ; {Max number of times to attempt transmission}backOffLimit = ... ; {Limit on number of times to back off}burstLimit= ... ; {in bits: LimitIn bits, limit for initiation of frame transmission in Burst Mode,implementation dependent, see 4.4}jamSize = ... ; {in bits:In bits, the value depends upon medium and collision detect implementation} varoutgoingFrame: Frame; {The frame to be transmitted}outgoingHeader: Header;currentTransmitBit, lastTransmitBit: 1..frameSize; {Positions of current and last outgoing bits inoutgoingFrame}lastHeaderBit: 1..headerSize;deferring: Boolean; {Implies any pending transmission must wait for the medium to clear}frameWaiting: Boolean; {Indicates that outgoingFrame is deferring}attempts: 0..attemptLimit; {Number of transmission attempts on outgoingFrame}newCollision: Boolean; {Indicates that a collision has occurred but has not yet been jammed}transmitSucceeding: Boolean; {Running indicator of whether transmission is succeeding}burstMode: Boolean:; {Indicates the desired mode of operation, and enables the transmission ofmultiple frames in a single carrier event. burstMode is a static variable; itsvalue does not change between invocations of the Initialize procedure.}value shall only be changed by the invocation of the Initialize procedure} bursting: Boolean; {In burstMode, the given station has acquired the medium and the burst timer hasnot yet expired}burstStart: Boolean; {In burstMode, indicates that the first frame transmission is in progress}extendError: Boolean; {Indicates a collision occurred while sending extension bits}ifsStretchMode: Boolean; {Indicates the desired mode of operation, and enables the lowering of theaverage data rate of the MAC sublayer (with frame granularity), usingextension of the minimum interFrameSpacing. ifsStretchMode is a staticvariable; its value shall only be changed by the invocation of the Initializeprocedure}ifsStretchCount: 0..ifsStretchRatio; {In bits, a running counter that counts the number of bits during aframe’s transmission that are to be considered for the minimuminterFrameSpacing extension, while operating in ifsStretchMode} ifsStretchSize: 0..(((maxUntaggedFrameSize + qTagPrefixSize) x 8 + headerSize + interFrameSpacing + ifsStretchRatio – 1) div ifsStretchRatio);{In octets, a running counter that counts the integer number of octets that are to beadded to the minimum interFrameSpacing, while operating in ifsStretchMode}4.2.7.3 Receive state variablesThe following items are specific to frame reception. (See also 4.4.)varincomingFrame: Frame; {The frame being received}receiving: Boolean; {Indicates that a frame reception is in progress}excessBits: 0..7; {Count of excess trailing bits beyond octet boundary}receiveSucceeding: Boolean; {Running indicator of whether reception is succeeding}validLength: Boolean; {Indicator of whether received frame has a length error}exceedsMaxLength: Boolean; {Indicator of whether received frame has a length longer than themaximum permitted length}extending: Boolean; {Indicates whether the current frame is subject to carrier extension}extensionOK: Boolean; {Indicates whether any bit errors were found in the extension part of a frame,which is not checked by the CRC}passReceiveFCSMode: Boolean; {Indicates the desired mode of operation, and enables passing ofthe frame check sequence field of all received frames from theMAC sublayer to the MAC client. passReceiveFCSMode is astatic variable}4.2.7.4 Summary of interlayer interfacesa)The interface to the MAC client, defined in 4.3.2, is summarized below:typeTransmitStatus = (transmitDisabled, transmitOK, excessiveCollisionError, lateCollisionErrorStatus);{Result of TransmitFrame operation, reporting of lateCollisionErrorStatus isoptional for MACs operating at speeds at or below 100Mb/s}ReceiveStatus = (receiveDisabled, receiveOK, frameTooLong, frameCheckError, lengthError,alignmentError); {Result of ReceiveFrame operation}function TransmitFrame (destinationParam: AddressValue;sourceParam: AddressValue;lengthOrTypeParam: LengthOrTypeValue;dataParam: DataValue): TransmitStatus; {Transmits one frame}dataParam: DataValue;fcsParamValue: CRCValue;fcsParamPresent: Bit): TransmitStatus; {Transmits one frame}function ReceiveFrame (var destinationParam: AddressValue;var sourceParam: AddressValue;var lengthOrTypeParam: LengthOrTypeValue;var dataParam: DataValue): ReceiveStatus; {Receives one frame}var dataParam: DataValue;var fcsParamValue: CRCValue;var fcsParamPresent: Bit): ReceiveStatus; {Receives one frame}b)The interface to the Physical Layer, defined in 4.3.3, is summarized in the following:varreceiveDataValid: Boolean; {Indicates incoming bits}carrierSense: Boolean; {In half duplex mode, indicates that transmission should defer}transmitting: Boolean; {Indicates outgoing bits}collisionDetect: Boolean; {Indicates medium contention}procedure TransmitBit (bitParam: PhysicalBit); {Transmits one bit}function ReceiveBit: PhysicalBit; {Receives one bit}procedure Wait (bitTimes: integer); {Waits for indicated number of bit times}4.2.7.5 State variable initializationThe procedure Initialize must be run when the MAC sublayer begins operation, before any of the processes begin execution. Initialize sets certain crucial shared state variables to their initial values. (All other global variables are appropriately reinitialized before each use.) Initialize then waits for the medium to be idle, and starts operation of the various processes.NOTE—Care should be taken to ensure that the time from the completion of the Initialize process to when the first packet transmission begins is at least an interFrameGap.If Layer Management is implemented, the Initialize procedure shall only be called as the result of the initializeMAC action (30.3.1.2.1).procedure Initialize;begin beginframeWaiting := false;deferring := false;newCollision := false;transmitting := false; {IAn interface to Physical Layer; see below}receiving := false;halfDuplex := ...; {tTrue for half duplex operation, false for full duplex operation. For operation atspeeds above 1000 Mb/s, halfDuplex shall always be false}halfDuplex is a staticvariable; its value does not change between invocations of the Initialize bursting := false;burstMode := ...; { tTrue for half duplex operation at speeds above 100 Mb/s an operating speed of 1000Mb/s, when multiple frames’ transmission in a single carrier event is desired andsupported, false otherwise}. burstMode is a static variable; its value does not changebetween invocations of the Initialize procedure}extending := extend and and halfDuplex;ifsStretchMode := ...; {True for operating speeds above 1000 Mb/s when lowering the average data rateof the MAC sublayer (with frame granularity) is desired and supported, falseotherwise}ifsStretchCount := 0;ifsStretchSize := 0;passReceiveFCSMode := ...; {True when enabling the passing of the frame check sequence of allreceived frames from the MAC sublayer to the MAC client is desired andsupported, false otherwise}while carrierSense or receiveDataValid do nothingif halfDuplex then while carrierSense or receiveDataValid do nothingelse while receiveDataValid do nothing{Start execution of all processes}end; {Initialize}4.2.8 Frame transmissionChange subclause 4.2.8 to read as follows:The algorithms in this subclause define MAC sublayer frame transmission. The function TransmitFrame implements the frame transmission operation provided to the MAC client:function TransmitFrame (destinationParam: AddressValue;sourceParam: AddressValue;lengthOrTypeParam: LengthOrTypeValue;dataParam: DataValue): TransmitStatus;dataParam: DataValue;fcsParamValue: CRCValue;fcsParamPresent: Bit): TransmitStatus;procedure TransmitDataEncap; ... {n{Nested procedure; see body below}beginif transmitEnabled thenbeginTransmitDataEncap;TransmitFrame := TransmitLinkMgmtendelse TransmitFrame := transmitDisabledend; {TransmitFrame}If transmission is enabled, TransmitFrame calls the internal procedure TransmitDataEncap to construct the frame. Next, TransmitLinkMgmt is called to perform the actual transmission. The TransmitStatus returned indicates the success or failure of the transmission attempt.TransmitDataEncap builds the frame and places the 32-bit CRC in the frame check sequence field:procedure TransmitDataEncap;beginwith outgoingFrame dobegin {aAssemble frame}view := fields;destinationField := destinationParam;sourceField := sourceParam;lengthOrTypeField := lengthOrTypeParam;dataField := ComputePad (dataParam);fcsField := CRC32(outgoingFrame);if fcsParamPresent thenbegindataField := dataParam; {No need to generate pad if the FCS is passed from MAC client}fcsField := fcsParamValue {Use the FCS passed from MAC client}endelsebegindataField := ComputePad(dataParam);fcsField := CRC32(outgoingFrame)end;view := bitsend {aAssemble frame}with outgoingHeader dobeginheaderView := headerFields;preamble := ...; {* ‘1010...10,’ LSB to MSB*}sfd := ...; {* ‘10101011,’ LSB to MSB*}headerView := headerBitsendend; {TransmitDataEncap}If the MAC client chooses to generate the frame check sequence field for the frame, it passes this field to the MAC sublayer via the fcsParamValue parameter. If the fcsParamPresent parameter is true, TransmitDataEncap uses the fcsParamValue parameter as the frame check sequence field for the frame. Such a frame shall not require any padding, since it is the responsibility of the MAC client to ensure that the frame meets the minFrameSize constraint. If the fcsParamPresent parameter is false, the fcsParamValue parameter is unspecified.TransmitDataEncap first calls the ComputePad function, followed by a call to the CRC32 function to generate the padding (if necessary) and the frame check sequence field for the frame internally to the MAC sublayer.ComputePad appends an array of arbitrary bits to the MAC client data to pad the frame to the minimum frame size.: function ComputePad(var dataParam: DataValue): DataValue;beginComputePad := {Append an array of size padSize of arbitrary bits to the MAC client dataField} end; {ComputePadParam}function ComputePad(var dataParam: DataValue): DataValue;beginComputePad := {Append an array of size padSize of arbitrary bits to the MAC client dataField} end; {ComputePad}TransmitLinkMgmt attempts to transmit the frame. In half duplex mode, it first defers to any passing traffic. In half duplex mode, if a collision occurs, transmission is terminated properly and retransmission is scheduled following a suitable backoff interval:function TransmitLinkMgmt: TransmitStatus;beginattempts := 0;transmitSucceeding := false;lateCollisionCount := 0;deferred := false; {iInitialize}excessDefer := false;while (attempts < attemptLimit) and (not transmitSucceeding)and (not extend or lateCollisionCount = 0) do{nNo retransmission after late collision if operating at > 100 1000 Mb/s} begin {lLoop}if bursting then {tThis is a burst continuation}frameWaiting := true {sStart transmission without checking deference}else {nNon bursting case, or first frame of a burst}beginif attempts > 0 then BackOff;if halfDuplex then frameWaiting := true;frameWaiting := true;while deferring do {dDefer to passing frame, if any1}if halfDuplex then deferred := true;beginnothing;‡if halfDuplex then deferred := trueend;burstStart := true;if burstMode then bursting := trueend;lateCollisionError := false;StartTransmit;frameWaiting := false;if halfDuplex thenbeginframeWaiting := false;1. The Deference process ensures that the reception of traffic does not cause deferring to be true when in full duplex mode. Deferring is used in full duplex mode to enforce the minimum interpacket gap spacing.while transmitting do WatchForCollision;if lateCollisionError then lateCollisionCount := lateCollisionCount + 1;lateCollisionCount := lateCollisionCount + 1;attempts := attempts + 1end {hHalf duplex mode}else while transmitting do nothing {fFull duplex mode}end; {lLoop}LayerMgmtTransmitCounters; {uUpdate transmit and transmit error counters in 5.2.4.2}if transmitSucceeding thenbeginif burstMode then burstStart := false; {Can’t be the first frame anymore}TransmitLinkMgmt := transmitOKendelse if (extend and lateCollisionCount > 0) then TransmitLinkMgmt := lateCollisionErrorStatus;TransmitLinkMgmt := lateCollisionErrorStatus;else TransmitLinkMgmt := excessiveCollisionErrorend; {TransmitLinkMgmt}Each time a frame transmission attempt is initiated, StartTransmit is called to alert the BitTransmitter process that bit transmission should begin:procedure StartTransmit;begincurrentTransmitBit := 1;lastTransmitBit := frameSize;transmitSucceeding := true;transmitting := true;lastHeaderBit: = := headerSizeend; {StartTransmit}In half duplex mode, TransmitLinkMgmt monitors the medium for contention by repeatedly calling WatchForCollision, once frame transmission has been initiated:procedure WatchForCollision;beginif transmitSucceeding and collisionDetect thenbeginif currentTransmitBit > (slotTime –headerSize) then lateCollisionError := true;lateCollisionError := true;newCollision := true;transmitSucceeding := false;if burstMode thenbegin:=false;burstingif not burstStart thenlateCollisionError := true {Every collision is late, unless it hits the first frame in a burst} endendend; {WatchForCollision}WatchForCollision, upon detecting a collision, updates newCollision to ensure proper jamming by the BitTransmitter process. The current transmit bit number is checked to see if this is a late collision. If the collision occurs later than a collision window of slotTime bits into the packet, it is considered as evidence of a late collision. The point at which the collision is received is determined by the network media propagation time and the delay time through a station and, as such, is implementation-dependent (see 4.1.2.2). While operating at speeds of 100 Mb/s or lower, an implementation may optionally elect to end retransmission attempts after a late collision is detected. While operating at speeds above 100 Mb/s the speed of 1000 Mb/s, an implementation shall end retransmission attempts after a late collision is detected.After transmission of the jam has been completed, if TransmitLinkMgmt determines that another attempt should be made, BackOff is called to schedule the next attempt to retransmit the frame.function Random (low, high: integer): integer;beginRandom := ...{uUniformly distributed random integer r, such that low ≤ r < high}end; {Random}BackOff performs the truncated binary exponential backoff computation and then waits for the selected multiple of the slot time.:var maxBackOff: 2..1024; {Working variable of BackOff}procedure BackOff;beginif attempts = 1 then maxBackOff := 2else if attempts ≤ backOffLimit then maxBackOff := maxBackOff x 2;Wait(slotTime x Random(0, maxBackOff))end; {BackOff}BurstTimer is a process that does nothing unless the bursting variable is true. When bursting is true, BurstTimer increments burstCounter until the burstLimit limit is reached, whereupon BurstTimer assigns the value false to bursting.:process BurstTimer;var burstCounter: integer;begincyclewhile not bursting do nothing; {wait for a burst}burstCounter := 0;while bursting and (burstCounter < burstLimit) dobeginWait(1);burstCounter := burstCounter + 1end;bursting := falseend {burstMode cycle}end; {BurstTimer}process BurstTimer;begincyclewhile not bursting do nothing; {Wait for a burst}Wait(burstLimit);bursting := falseend {burstMode cycle}end; {BurstTimer}The Deference process runs asynchronously to continuously compute the proper value for the variable deferring. In the case of half duplex burst mode, deferring remains true throughout the entire burst. Interframe spacing may be used to lower the average data rate of a MAC at operating speeds above 1000 Mb/s in the full duplex mode, when it is necessary to adapt it to the data rate of a WAN-based physical layer. When interframe stretching is enabled, deferring remains true throughout the entire extended interframe gap, which includes the sum of interFrameSpacing and the interframe extension as determined by the BitTransmitter:process Deference;var realTimeCounter: integer; wasTransmitting: Boolean;beginif halfDuplex then cycle{hHalf duplex loop}while not carrierSense do nothing; {wWatch for carrier to appear}deferring := true; {dDelay start of new transmissions}wasTransmitting := transmitting;while carrierSense or transmitting do wasTransmitting := wasTransmitting or transmitting;wasTransmitting: = wasTransmitting or transmitting;if wasTransmitting then Wait(interFrameSpacingPart1) {Time out first part of interframe gap} beginStartRealTimeDelay; {time out first part interframe gap}while RealTimeDelay(interFrameSpacingPart1) do nothingendelsebeginStartRealTimeDelay;repeatwhile carrierSense do StartRealTimeDelayuntil not RealTimeDelay(interFrameSpacingPart1)realTimeCounter := interFrameSpacingPart1;repeatwhile carrierSense do realTimeCounter := interFrameSpacingPart1;Wait(1);realTimeCounter := realTimeCounter – 1until (realTimeCounter = 0)end;StartRealTimeDelay; {time out second part interframe gap}while RealTimeDelay(interFrameSpacingPart2) do nothing;Wait(interFrameSpacingPart2); {Time out second part of interframe gap}deferring: = := false; {aAllow new transmissions to proceed}while frameWaiting do nothing {aAllow waiting transmission, if any}end {hHalf duplex loop}else cycle {fFull duplex loop}while not transmitting do nothing; {wWait for the start of a transmission}deferring := true; {iInhibit future transmissions}while transmitting do nothing; {wWait for the end of the current transmission}StartRealTimeDelay; {time out an interframe gap}while RealTimeDelay(interFrameSpacing) do nothing;Wait(interFrameSpacing + ifsStretchSize x 8); {Time out entire interframe gap and IFS extension}if not frameWaiting then {Don’t roll over the remainder into the next frame}beginWait(8);ifsStretchCount := 0enddeferring := false {dDon’t inhibit transmission}end {fFull duplex loop}end; {Deference}If the ifsStretchMode is enabled, the Deference process continues to enforce interframe spacing for an additional number of bit times, after the completion of timing the interFrameSpacing. The additional number of bit times is reflected by the variable ifsStretchSize. If the variable ifsStretchCount is less than ifsStretchRatio and the next frame is ready for transmission (variable frameWaiting is true), the Deference process enforces interframe spacing only for the integer number of octets, as indicated by ifsStretchSize, and saves ifsStretchCount for the next frame’s transmis-sion. If the next frame is not ready for transmission (variable frameWaiting is false), then the Deference process ini-tializes the ifsStretchCount variable to zero.procedure StartRealTimeDelaybegin{reset the realtime timer and start it timing}end; {StartRealTimeDelay}function RealTimeDelay (µsec:real): Boolean;begin{return the value true if the specified number of microseconds havenot elapsed since the most recent invocation of StartRealTimeDelay,otherwise return the value false}end; {RealTimeDelay}The BitTransmitter process runs asynchronously, transmitting bits at a rate determined by the Physical Layer’s Trans-mitBit operation:process BitTransmitter;begincycle {oOuter loop}if transmitting thenbegin {iInner loop}extendError := false;if ifsStretchMode then {Calculate the counter values}beginifsStretchSize := (ifsStretchCount + headerSize + frameSize + interFrameSpacing) divifsStretchRatio; {Extension of the interframe spacing}ifsStretchCount := (ifsStretchCount + headerSize + frameSize + interFrameSpacing)mod ifsStretchRatio {Remainder to carry over into the next frame’s transmission} end;PhysicalSignalEncap; {Send preamble and start of frame delimiter}while transmitting dobeginif (currentTransmitBit > lastTransmitBit) then TransmitBit(extensionBit)else if extendError then TransmitBit(extensionErrorBit) {Jam in extension}if extendError thenTransmitBit(extensionErrorBit) {jam in extension}else TransmitBit(outgoingFrame[currentTransmitBit]);TransmitBit(outgoingFrame[currentTransmitBit]);if newCollision then StartJam else NextBitend;if bursting thenbegin。

ULPI_v1_0 Errata