EDA技术实验指导书

电子设计自动化(eda)实验指导书

电子设计自动化(EDA)实验指导书前言近些年来,电子设计自动化(EDA)技术发展迅速。

一方面,各种大容量、高性能、低功耗的可编程逻辑器件不断推出,使得专用集成电路(ASIC)的生产商感受到空前的竞争压力。

另一方面,出现了许多EDA设计辅助工具,这些工具大大提高了新型集成电路的设计效率,使更低成本、更短周期的复杂数字系统开发成为可能。

于是一场ASIC与FPGA/CPLD之争在所难免。

然而PLD器件具有先天的竞争优势,那就是可以反复编程,在线调试。

EDA技术正是这场较量的推动引擎之一。

一般来说,EDA技术就是以计算机为平台,以EDA软件工具为开发环境,以HDL为设计语言,以可编程器件为载体,以ASIC、SOC芯片为目标器件,以电子系统设计为应用方向的电子产品自动化设计过程。

设计者只需编写硬件描述语言代码,然后选择目标器件,在集成开发环境里进行编译,仿真,综合,最后在线下载调试。

整个过程,大部分工作由EDA软件完成。

全球许多著名的可编程器件提供商都推出了自己的集成开发工具软件,如Altera 公司的MAX+PLUSⅡ、Quartus Ⅱ软件;Xilinx公司的Foundation 、ISE软件,Lattice公司的ispExpert软件,Actel公司的Libero 软件等。

这些软件的推出,极大地促进了集算法设计、芯片编程、电路板设计于一体的EDA技术的发展。

另外,在以SOC芯片为目标器件的电子系统设计要求下,可编程器件的内部开始集成高速的处理器硬核、处理器软核、DSP模块、大量的存储资源、高速的串行收发模块、系统时钟管理器、多标准的I/O接口模块,亦使得设计者更加得心应手,新一轮的数字革命由此引发。

EDA技术是一门实践性很强的学科,要培养出具有竞争力的一流IC设计人才,动手能力是关键。

只有通过理论学习,加上现场实验,在使用软件编程加硬件调试的过程中真正获得锻炼,增长技能。

ZY11EDA13BE型实验系统采用主板加适配板加扩展板的灵活结构,可方便进行基于不同PLD芯片的实验开发,并易于升级,符合当前高校在此方面对人才培养的要求。

EDA实验指导书

EDA技术实验指导书2012.09第一章针对HDL设计的EDA基本实验与设计实验1.计数器设计(1) 实验目的:熟悉Quartus II的Verilog/VHDL文本设计流程全过程,学习计数器的设计、仿真和硬件测试。

掌握原理图与文本混合设计方法。

(2) 实验原理:参考教材[1]3.3节。

实验程序为例(3) 实验内容1:根据教材[1]的4.1节在Quartus II上对例3-22进行编辑、编译、综合、适配、仿真。

说明例中各语句的作用。

给出其所有信号的时序仿真波形,根据波形详细描述此设计的功能特点,包括RST、EN、LOAD、DA TA,CLK等信号等异步和同步特性。

查阅编译后的计数器的时序特点,从时序仿真图和编1 原理图示意图译报告中了解计数时钟输入至计数数据输出的延时情况,包括设定不同优化约束后的改善情况以及当选择不同FPGA后的延时情况,给出分析报告。

(4) 实验内容2:用教材[1]第4章介绍的不同方式锁定引脚并硬件下载测试。

引脚锁定后进行编译、下载和硬件测试实验。

将实验过程和实验结果写进实验报告。

硬件实验中,注意测试所有控制信号和显示信号,包括RST、EN、LOAD、DA TA等的同步、异步特性,进位信号等。

时钟CLK换不同输入:手动有抖动或无抖动键输入,1Hz或4Hz时钟脉冲输入,这需要附录1.3的模块B4板才能获得,或直接使用KX_DN5/7系列EDA/SOPC实验系统。

(5) 实验内容3:使用SignalTap II对此计数器进行实时测试,流程与要求参考教材[1]第4章,给出报告。

(6) 实验内容4:从设计中去除SignalTap II,要求全程编译后,将生成的SOF文件转变成用于配置器件EPCS4的压缩的间接配置文件*. jic,并使用USB-Blaster对实验板上的EPCS4进行编程,最后进行验证。

编程和全程编译前,按教材[1]图4-6所示,设定所有控制和参数。

(7) 实验内容5:为此项设计加入一个可用于SignalTap II采样的独立的时钟输入端CLK0。

EDA实验指导书(已改)

10-11学年第二学期《EDA实验指导书》(试用)学时:12班级:机电811、812指导教师:孙立香盐城纺织职业技术学院机电系电子教研室目录实验一 Protel 99 SE 启动、建库、文件环境参数设置 (3)实验二熟悉元器件库,编辑简单原理图 (5)实验三电路原理图设计 (6)实验四原理图元件制作 (9)实验五 PCB 设计基础 (11)实验六 PCB 图元件制作 (12)附加印制电路板设计 (14)实验一 Protel 99 SE 启动、建库、文件环境参数设置一、实验目的1 .熟悉 scH 99 的基本界面。

2 .学会文件环境参数设置。

二、实验内容1. 启动 Protel99SE ,建立名为 MYPRO 的文件夹,并在文件夹中建立名为MYFIRST 的设计数据库文件。

提示:单击桌面上的 Protel99SE 快捷图标,进入 Protel99SE 设计环境。

若环境中已经有设计数据库文件,就执行菜单 File/Close Design 将其关闭。

若环境中没有设计数据库文件,就执行菜单 File/New ,在弹出的窗口中,单击Browse 按钮,在弹出的文件名输入窗口中建立 MYPRO 的文件夹,并在文件夹中建立 MYFIRST 的设计文件。

2. 在练习 1 的基础上,建立名为 FIRSCH 的原理图文件,并进入原理图设计窗口。

提示:执行 File/New 菜单,在弹出的窗口中选择 Schematic Document 图标。

3. 设置原理图的图纸尺寸为 A0 ,去掉可视栅格,去掉标题栏。

提示:在原理图设计环境中,执行菜单 Design/Options ,在弹出的窗口中选择 Sheet Options 页面,在页面右上角的 Standard Styles 下拉框中选择A0 。

4. 把光标设置成大十字,并把光标移动到图纸边沿时的移动速度设置为 Auto Pan Recenter 。

提示:设置光标:在原理图设计环境中,执行菜单 Tools/Preferences ,在弹出的窗口中选择 Graphical Editing 页面,然后在该页面 Cursor/Grid Options 区域的 Cursor Type 下拉列表框中选择 Large Cursor 90 。

EDA实验指导书(最新)

EDA技术实验指导书吕常智尹唱唱卫阿盈山东科技大学信息与电气工程学院EDA实验室使用说明本实验指导书适用于EDA技术、VHDL语言及电子设计自动化等相关课程使用。

它们都属于实践性很强的软件应用类课程,主要包含电子线路设计与仿真(EWB,MuiltSim等)、电子线路原理图与印刷电路板的设计与绘制(Protel99SE、PowerPCB等)、可编程逻辑器件CPLD/FPGA、VHDL语言及其应用设计(MAX+PlusII/QuartusII)等相关内容,涉及到电子信息、通信工程、电气技术、自动化、生物医学等所有电气信息类专业。

基于以上原因,在设计本实验指导书时考虑到各专业和课程的需要,安排了有关EWB的实验一个,Protel99SE的实验两个,基于CPLD/FPGA的VHDL语言的实验十七个。

二十个实验中包含验证性实验9个、设计性实验2个、综合性实验9个(具体请查看试验大纲)。

实验的设计强调了提高学生的实践动手能力和创新设计能力,实验时,课程教师可以根据专业和课程的需要进行选择。

由于所有试验都是基于软件开发平台的上机操作完成,实现设计和运行的方法较多,因此本指导书没有固定实验步骤和规定试验结果记录方式,这些在书写报告时由实验者自己拟定。

另外,本实验指导书基于EDA 实验系统GW48-PK3编排,有关试验系统的默认设置及相关资料请参考附件1,并要求学生实验时一定注意预览。

当然,由于涉及的知识面比较广,时间紧迫,水平也比较有限,实验的编排不一定非常合理,书中也难免有误,不当之处敬请课程教师、实验指导教师及实验指导书使用者批评指正。

目录试验一EWB设计应用 (1)试验二Protel99SE 原理图设计 (4)试验三Protel99SE 印刷板设计 (5)试验四Max+plusII/QuartusII软件应用 (7)试验五VHDL软件设计 (8)试验六3-8译码器 (9)试验七组合逻辑电路的VHDL描述 (10)试验八触发器的VHDL描述 (11)试验九扫描显示驱动电路 (13)试验十VHDL硬件设计 (15)试验十一数字钟 (18)试验十二字符发生器 (19)试验十三模拟信号检测 (20)试验十四函数信号发生器 (22)试验十五VHDL硬件设计 (23)试验十六序列检测器设计 (27)试验十七嵌入式锁相环PLL的应用实验 (28)试验十八信号采集与频谱分析 (30)试验十九循环冗余校验CRC模块设计 (32)试验二十USB与FPGA通信实验 (33)附录1 GW48 EDA/SOPC主系统使用说明 (35)实验一EWB设计应用一、实验目的1、熟悉EWB的使用环境和EWB使用一般步骤。

EDA实验指导书全

实验一Quartus II开发环境入门一、实验目的1、了解QuartusII软件及基本操作2、熟悉图形编辑器Block Builder/Schematic File的设计输入3、掌握电路的编译和适配4、掌握电路仿真与时序分析5、熟悉3/8线译码器工作原理和五人表决器设计二、实验原理1、以3/8线译码器为例,总体思路以EP1C3中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七个彩灯上显示。

2、三、实验步骤主要仪器和设备:计算机,EDA实验箱。

步骤一:1、建立工程,设计输入。

选择菜单“File”→“New Preject Wizard”将设计文件加入工程中:点击下方的“Next” 按钮,在弹出的对话框中点击“File”栏的按钮,将此工程相关的所有VHDL文件加入进此工程(如果有的话)。

Cyclone系列的EP1C3T144C8按下“Next”后,出现仿真工具选择对话框。

不作任何选择。

4、完成设置点击“Next”后,完成工程的设定,点击“finish”。

步骤二:1、选择File/New或点击主菜单中的空白图标,进入新建程序文件状态,选择VHDL file 。

VHDL程序文件的扩展名是:* .vhd程序代码:-- A simple 3 to 8 decoderlibrary ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;步骤三:1、选择菜单“File”→“New ” →“ Schematic File”,即弹出原理图编辑框。

EDA 实验指导书

EDA技术基础实验指导书海南大学信息学院编目录实验一MAX –plusII及开发系统使用 1 实验二高速四位乘法器设计7 实验三秒表的设计9 综合性设计性实验实验四序列检测器的设计12 实验五数字频率计的设计14 数字密码锁17 交通灯控制器182EDA实验指导书实验一MAX –plusII及开发系统使用一、实验目的1、熟悉利用MAX-plusⅡ的原理图输入方法设计简单的组合电路2、掌握层次化设计的方法3、熟悉DXT-BⅢ型EDA试验开发系统的使用二、主要实验设备PC 机一台(中档以上配置),DXT-B3 EDA实验系统一台。

三、实验原理数字系统设计系列实验是建立在数字电路基础上的一个更高层次的设计性实验。

它是借助可编程逻辑器件(PLD),采用在系统可编程技术(ISP),利用电子设计自动化软件(EDA),在计算机(PC)平台上进行的。

因为本实验是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面:1、实验器材集中化,所有实验基本上在一套实验设备上进行。

传统的实验每作完一个实验,实验器材基本上都要变动(个别除外)。

而做本实验时,只要在计算机上把不同的程序输进去,其它步骤所有实验都一致;2、实验耗材极小(基本上没有耗材);3、在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单;4、下载后,实验结果清晰;5、实验仪器损耗少,维护简单;下面,我们就本套实验设备做一个简单的介绍。

3(一)Max+plusⅡ10.0的使用。

1、Max+PlusII软件的安装步骤:第一步:系统要求奔3CPU以上,128M内存以上,4G 以上硬盘,98 操作系统(98或Me操作系统才可以下载,其他操作系统下载必须安装驱动,否则只能仿真,如果大家只进行仿真的话,对系统没要求)第二步:安装点击安装可执行文件进行安装,安装完毕后会弹出一对话框,点击是或否都可以。

第三步:将安装文件夹中的License 文件夹打开,里面有一个License.bat 注册文件,将此文件复制到你的安装目录下(你的安装目录可放在任一个驱动器下,然后建立一个Max10的文件夹,将系统安装在此文件夹中,安装后此文件夹中会有三个文件夹)的任一个文件夹中,要清楚位置。

EDA技术实验指导书

《EDA技术》实验指导书面向专业:通信工程信息工程自动化电子信息工程电气工程及其自动化信息与通信工程学院2016年9月前言一、课程性质本课程是电子信息工程、通信工程、信息工程和自动化专业必修的专业实验课程。

通过本课程的教学,使学生掌握EDA技术的开发流程,学会利用以硬件描述语言为描述工具,以可编程逻辑器件为实现载体,在数字系统设计领域熟练应用EDA技术,使其具备研究和开发现代数字系统的能力。

二、专业安排本系统分为多个模块,适合通信工程、信息工程、自动化、电子信息工程、电气工程及其自动化等专业使用。

三、本书特点本实验指导书的特点是引入工程项目机制来管理实验项目,着重培养学生的方案设计、算法分析和现场调试能力,为培养卓越工程师打下坚实的基础。

目录前言 (I)第一章实验系统 (1)1.1 系统整体结构 (1)1.2 核心板 (1)1.3 基础扩展模块 (2)1.4 自动控制模块 (3)1.5 信号处理模块 (3)1.6 通信接口模块 (4)第二章开发平台简介 (5)2.1 Quartus II简介 (5)2.2 Quartus II开发流程 (5)第三章实验项目 (9)实验1 平台应用及全加器设计 (9)实验2 信号发生器设计 (11)实验3 数字电压表设计 (13)实验4 数字频率计设计 (16)实验5 交通灯控制器设计 (19)第一章实验系统1.1 系统整体结构本实验指导书采用的EDA综合实验开发系统是我院电子信息与通信技术实验教学中心自主研制,整体结构如图所示。

1.2 核心板核心板采用Altera公司的EP4CE22E22C8N芯片,具有低内核电压、低功耗的特点。

芯片内部具有22320个逻辑单元,594kbit RAM嵌入式储存器,66个嵌入式18×18乘法器,4组通用PLL。

1、DIP开关主要功能是控制高低电平,通过手动控制为系统提供稳定的逻辑信号。

系统总共提供了3位拨档开关,当开关的档位在上方时则输出高电平“1”,反之则为低电平“0”。

EDA技术实验指导书(DOC)

EDA技术实验指导书唐浦华西华大学机械工程学院二零一六年制定目录实验一:实验环境和平台的建立 (1)实验二:译码器设计 (2)实验三:码制变换译码器设计 (5)实验四:四位加法器设计 (7)实验五:时序逻辑电路设计 (9)实验六:分频器的设计 (10)实验七:通用移位寄存器的设计 (11)实验八:数码管扫描显示的设计 (12)实验九:正弦信号发生器的设计 (14)实验十:序列检测器的设计 (24)实验一:实验环境和平台的建立一、实验目的:熟悉Quartus II的VHDL文本设计流程,学习8-3编码器的设计、仿真。

二、实验内容:用VHDL编写8-3编码器的VHDL代码并仿真。

三、实验环境PC 机(Pentium100 以上)、Altera KAX+plus II 10.2 CPLD/FPGA 集成开环境。

四、实验原理在数字系统中,常常需要将某一信息(输入)变换为某一特定的代码(输出)。

把二进制码按一定的规律排列,例如8421码、格雷码等,使每组代码具有一特定的含义(代表某个数字或是控制信号)称为编码。

具有编码功能的逻辑电路称为编码器。

编码器有若干个输入,在某一时刻只有一个输入被转换为二进制码。

例如8线-3线编码器和10线-4线编码器分别有8输入、3位输出和10位输入、4位输出。

8线-3线编码器的真值表见表1-1,管脚图如图1-1所示。

输入输出A7 A6 A5 A4 A3 A2 A1 A0 Y2 Y1 Y00 0 0 0 0 0 0 1 0 0 00 0 0 0 0 0 1 0 0 0 10 0 0 0 0 1 0 0 0 1 00 0 0 0 1 0 0 0 0 1 10 0 0 1 0 0 0 0 1 0 00 0 1 0 0 0 0 0 1 0 10 1 0 0 0 0 0 0 1 1 01 0 0 0 0 0 0 0 1 1 1表1-1 8-3编码器真值表图1-1 8-3编码器管脚图五、实验步骤参见课件。

EDA实验指导书

EDA实验指导书计算机科学与技术系2008.09目录实验一Quartus II 开发环境实验 (3)实验二半加器 (18)实验三全加器 (19)实验四多路数据选择器 (21)实验五编码器 (23)实验六7段数码管控制接口 (25)实验七计数器 (28)实验八MOORE机 (30)实验九MEALY机 (34)实验十串入/并出移位寄存器 (38)实验十一并入/串出移位寄存器 (40)实验十二数字钟 (42)实验一Quartus II 开发环境实验一、实验目的:1、通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:Quartus II软件的基本操作与应用三、实验内容:学习Quartus II软件的基本操作并设计3人表决器一.Quartus II 7.2 启动◆方法一、直接双击桌面上的图标,可以打开Quartus II 7.2 软件;◆方法二、执行:【开始】→【程序】→【Altera】→【Quartus II 7.2】→【Quartus II 7.2 TalkBackInstall】菜单命令,可以打开软件。

◆启动软件后,若你的电脑没有连接到Internet互联网,会出现提示,提示你没有连接到Altera的官方网站,将无法获得更新的资源。

点击〖确定〗继续,因为这不影响软件的正常使用。

二.Quartus II 7.2软件界面Quartus II 7.2软件的默认启动界面如下图所示,由标题栏、菜单栏、常用工具栏、资源管理窗口、程序编译或仿真运行状态的显示窗口、程序编译或仿真的结果显示窗口和工程编辑工作区组成。

三.Quartus II 7.2软件使用1. 新建项目工程使用QuartusII7.2设计一个数字逻辑电路,并用时序波形图对电路的功能进行仿真,同时还可以将设计正确的电路下载到可编程的逻辑器件(CPLD、FPGA)中。

EDA技术实验指导书

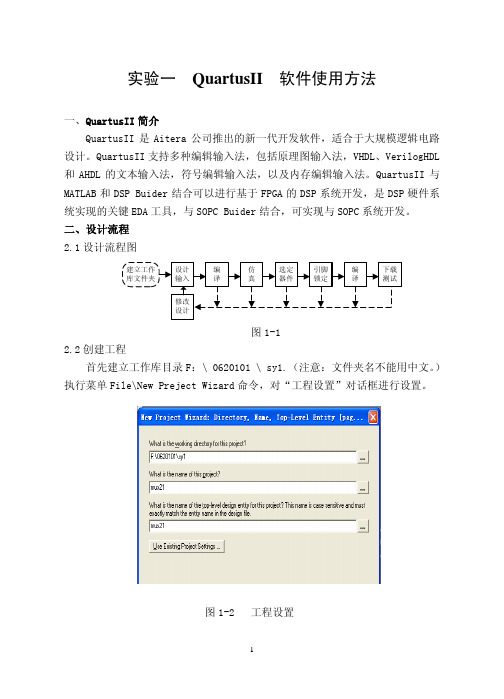

实验一 QuartusII 软件使用方法一、QuartusII简介QuartusII是Aitera公司推出的新一代开发软件,适合于大规模逻辑电路设计。

QuartusII支持多种编辑输入法,包括原理图输入法,VHDL、VerilogHDL 和AHDL的文本输入法,符号编辑输入法,以及内存编辑输入法。

QuartusII与MATLAB和DSP Buider结合可以进行基于FPGA的DSP系统开发,是DSP硬件系统实现的关键EDA工具,与SOPC Buider结合,可实现与SOPC系统开发。

二、设计流程2.1设计流程图图1-12.2创建工程首先建立工作库目录F:\ 0620101 \ sy1.(注意:文件夹名不能用中文。

)执行菜单File\New Preject Wizard命令,对“工程设置”对话框进行设置。

图1-2 工程设置图中第一行表示工程所在的工作库文件夹,第二行表示此项工程的工程名,工程名可以取任何其它的名,也可直接用顶层文件的实体名作为工程名,第三行是当前工程顶层文件的实体名。

单击Finish按钮,在工程管理窗中可以看到本工程项目的层次结构和各层次的实体名。

2.3设计输入2.3.1 VHDL文本输入选择菜单File\New,在New窗口中的Device Design Files中选择文件的类型为VHDL File (如图1-4所示)。

在VHDL文本编译窗中输入VHDL程序后保存,存盘文件名应该与实体名一致,扩展名为*.vhd。

图1-4 文件类型选择2.3.2 原理图输入在图 1-4中选择Block Diagram/Schematic File进入原理图编辑器。

如图1- 5所示。

图1-5 原理图编辑执行命令:Edit\Insert Symbol 或双击鼠标左键,将出现元件选择对话框,如图1-6。

进行器件选择和输入逻辑电路符号及进行电路连接,如图1-7。

绘制完成后,点击保存按钮,对原理图进行保存,扩展名为*.bdf。

EDA技术实验指导书(印刷版)

EDA技术实验指导书长沙学院电子与通信工程系2007年8月目录实验一简单逻辑电路实验 (1)实验二2选1多路选择器 (4)实验三D触发器设计 (5)实验四1位二进制全加器设计 (6)实验五4位加法计数器 (9)实验六7段数码显示译码器设计 (10)实验七带有复位和时钟使能的十进制计数器 (12)实验八带有并行置位的移位寄存器 (14)实验九较复杂电路的原理图设计 (16)实验十数控分频器的设计 (18)实验十一8位十六进制频率计设计 (20)实验十二基于LPM_COUNTER的数控分频器设计 (23)实验十五正弦信号发生器设计与LPM定制 (31)附录 (33)实验一简单逻辑电路实验一、实验目的1.学习Create-SOPC实验平台的使用方法;2.熟悉Quartus II 软件平台和使用VHDL 语言设计电路的方法;3.学习简单逻辑电路的设计、仿真和硬件测试。

二、实验内容运用Quartus II 集成环境下的VHDL文本设计方法设计半加器,进行波形仿真、引脚分配并下载到实验设备上进行逻辑功能验证。

三、实验步骤及参考程序1.创建个人实验文件夹(最好使用英文字母命名不要用中文或数字名称)如:D:\example2.运行Quartus Ⅱ软件。

3.创建一个VHDL设计文件:File -> New,在Device Design Files 中选择VHDL File。

在程序编辑窗输入VHDL程序并保存;在弹出对话框中输入文件名(必须和程序中实体名相同)并使下方小框内出现“√”,点击保存会弹出“是否创建新工程”提示信息如图1-1所示。

图1-1 图1-24.创建一个新工程:点击图1-1中“是”可进入创建工程向导(也可以File -> New project Wizard进入向导),此时看到的默认工程名、顶层实体名都为h_adder(其中工程名可换名但顶层实体名必与编写的程序实体名一致),如图1-2。

EDA技术实验指导书

EDA技术实验指导书福建农林大学计算机与信息学院电子信息工程系《EDA技术》课程组目录第一章GW48 EDA实验开发系统的概要说明1.1GW48教学实验系统原理与使用介绍 (3)1.2实验电路结构图说明 (6)1.3实验电路结构图 (8)1.4 GW48CK/PK2/PK3/PK4 系统万能接插口与结构图信号/与芯片引脚对照表 (12)第二章《EDA技术》课程的实验项目实验一、QuartusII 9.0软件的使用 (15)实验二、用文本输入法设计2选1多路选择器 (16)实验三、用文本输入法设计7段数码显示译码器 (17)实验四、用原理图输入法设计8位全加器 (19)实验五、乐曲硬件演奏电路的设计 (21)第一章 GW48 EDA 实验开发系统的概要说明1.1 GW48教学实验系统原理与使用介绍一、GW48系统使用注意事项 (用户必读!!!) ● 闲置不用GW48系统时,必须关闭电源!!!● 在实验中,当选中某种模式后,要按一下右侧的复位键,以使系统进入该结构模式工作。

注意此复位键仅对实验系统的监控模块复位,而对目标器件FPGA 没有影响,FPGA 本身没有复位的概念,上电后即工作,在没有配置前,FPGA 的I/O 口是随机的,故可以从数码管上看到随机闪动,配置后的I/O 口才会有确定的输出电平。

● 换目标芯片时要特别注意,不要插反或插错,也不要带电插拔,确信插对后才能开电源。

其它接口都可带电插拔。

请特别注意,尽可能不要随意插拔适配板,及实验系统上的其他芯片。

● 未用到+/-12V 时,请务必把右上角的开关关闭,指示灯亮时开,不亮时关。

康芯GW48系列EDA 设备较以前有较大的改进,每个型号详细说明在提供的关盘“系统特色及功能说明”文件夹里。

使用实验系统前,查阅此文件夹.以下将详述GW48系列SOPC/EDA 实验开发系统(GW48-PK2/PK3/PK4)结构与使用方法,对于这3种型号的共同之处将给予说明。

EDA技术实验指导书

可编程逻辑设计实验指导书2010.9实验一利用原理图输入法设计简单组合电路一、实验目的:熟悉QuartusII软件界面, 学习简单组合电路的多层次化电路设计方法,掌握文本输入和原理图输入设计方法。

掌握时序仿真测试及测试结果分析的方法。

二、实验原理:三选一数据选择器可以由两个二选一数据选择器构成,原理图如图1 所示。

图1 三选一数据选择器上图中,二选一数据选择器MUX21A的功能如下:当s=0时,y=a;当s=1时,y=b 。

两个MUX21A 如上图连接后,实现三选一功能s1s0=00,outy=a1;s1s0=01,outy=a1;s1s0=10,outy=a2;s1s0=11,outy=a3。

三、实验内容:1.利用QuartusⅡ完成2选1多路选择器MUX21A的文本编辑输入,然后编译、仿真,检查程序设计正确无误后,生成一个元件待用。

给出文本设计文件和仿真波形图。

entity mux21a isport (a,b:in bit;s:in bit;y:out bit);end entity mux21a;architecture one of mux21a isbeginy<=a when s='0' else b;end architecture one;INCLUDEPICTURE "C:\\Documents and Settings\\Administrator\\Application Data\\Tencent\\Users\\970546411\\QQ\\WinTemp\\RichOle\\97Y2MLW9QPY[F5VI2 9$OZ{2.jpg" \* MERGEFORMATINET2.利用原理图输入法,按照图1进行连线,完成三选一电路的设计。

然后编译、仿真测试,结果正确后锁定管脚,下载到FPGA芯片中,进行硬件测试。

给出原理图设计文件和仿真设计图。

EDA技术实验指导书

电子系统设计与EDA技术实验指导书实验须知:1.实验前认真阅读实验任务书,明确实验目的、内容及要求等;2.实验过程中要注意爱护实验设备,按要求接线、按步骤操作;3.要养成严谨科学的实验态度和勇于探索的实验精神,注重实践创新,对于在实验中遇到的困难,鼓励独立思考,用新思路、新方法解决;4.实验完成后,按学院资料入库标准认真完成实验报告,撰写实验报告要实事求是,严禁抄袭。

目录实验一MAX+plusⅡ的基本应用 (4)实验二简单组合逻辑设计 (6)实验三数码管扫描显示电路 (8)实验四简单时序逻辑电路设计 (11)实验六 4位二进制加法器设计 (13)实验七彩色LED组跑马灯的实现 (14)实验九数字钟的设计 (17)实验一MAX+plusⅡ的基本应用一、实验目的:1.熟悉MAX+plusⅡ的基本操作;2.掌握MAX+plusⅡ环境下的设计输入方法;3.熟悉相关的元件库以及功能模块的应用。

二、实验内容及步骤:1.通过2选1多路选择器的设计,熟悉VHDL文本输入的设计流程。

1)安装MAX+plusⅡ;2)启动MAX+plusⅡ(注意:第一次运行MAX+PLUSII时,需进行License设置。

从Option 菜单中选择License Setup进入License设置窗口,单击Browse按钮,选择License.dat文件即可);3)按照以下流程完成2选1多路选择器的VHDL设计:设计输入→保存→建立设计项目→编译→创建默认符号;2.通过1位二进制全加器的设计,熟悉图形输入设计流程。

1)半加器图形设计文件输入(后缀为.gdf)→保存→建立设计项目→编译→创建默认符号;2)顶层文件设计:全加器图形设计文件输入→保存→建立设计项目→编译→引脚分配及锁定→功能仿真→时序分析;三、实验要求:1.实验前预习2选1多路选择器的VHDL程序以及全加器的原理图;2.按照实验步骤完成本次实验任务,记录主要的设计流程;3.分析全加器功能仿真的波形;4.认真完成实验报告。

《EDA》实验指导书

EDA技术与应用实验指导书实验一MAX+PLUSII 软件使用实验一 实验目的1 熟悉MAX+PLUSII 软件的使用2 了解图形法的设计过程 二 实验内容1 在MAX+PLUSII 环境下,执行“File ”→“New ”命令,弹出如图1.1所示的“编辑文件类型”对话框,选择“Graphic Editor file ”后单击“OK ”按钮,进入MAX+PLUSII 图形编辑方式,其界面如图1.2所示。

图形编辑界面中的空白处,即原理图编辑区,相当于一张空白图纸,设计者可以在此画出自己的电路设计图。

图1.1 编辑文件类型对话框图形编辑器文件 符号编辑器文件 文本编辑器文件 波形编辑器文件图1.2图形编辑器界面在原理图编辑区的任何一个空白位置上双击鼠标的左键,将弹出一个“元件选择”对话框,如图1.3所示。

调出所需的器件后,连线,修改输入输出引脚的名称,存盘。

原理图如下:由此输入所需的元件名用户自己设置的元件库基本逻辑元件库老式宏函数元件库参数可设置的强函数元件库基本逻辑元件库的元件图1.3 元件选择对话框 图1.4 模12进制原理图2 编译执行“File ” →“Project ” →“Set Project Current File ”。

单击“MAX+plusII ” →“Compiler ”,在弹出的编译对话框中单击“Start ”按钮,即可对当前文件进行编译。

如果当前文件不存在问题,编译后的结果如图2.1所示。

在编译中,MAX+plusII 自动完成编译网表提取(Compiler Netlist Extractor )、数据库建立(Database Bulder )、逻辑综合(Logic Synthesizer )、逻辑分割(Partitioner )、适配(Fitter )、延时网表提取(Timing SNF Extractor )和编译文件汇编(Assembler )等操作,并检查设计文件是否正确。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《EDA技术》实验指导书面向专业:通信工程信息工程自动化电子信息工程电气工程及其自动化信息与通信工程学院2016年9月前言一、课程性质本课程是电子信息工程、通信工程、信息工程和自动化专业必修的专业实验课程。

通过本课程的教学,使学生掌握EDA技术的开发流程,学会利用以硬件描述语言为描述工具,以可编程逻辑器件为实现载体,在数字系统设计领域熟练应用EDA技术,使其具备研究和开发现代数字系统的能力。

二、专业安排本系统分为多个模块,适合通信工程、信息工程、自动化、电子信息工程、电气工程及其自动化等专业使用。

三、本书特点本实验指导书的特点是引入工程项目机制来管理实验项目,着重培养学生的方案设计、算法分析和现场调试能力,为培养卓越工程师打下坚实的基础。

目录前言 (I)第一章实验系统 (1)1.1 系统整体结构 (1)1.2 核心板 (1)1.3 基础扩展模块 (2)1.4 自动控制模块 (3)1.5 信号处理模块 (3)1.6 通信接口模块 (4)第二章开发平台简介 (5)2.1 Quartus II简介 (5)2.2 Quartus II开发流程 (5)第三章实验项目 (9)实验1 平台应用及全加器设计 (9)实验2 信号发生器设计 (11)实验3 数字电压表设计 (13)实验4 数字频率计设计 (16)实验5 交通灯控制器设计 (19)第一章实验系统1.1 系统整体结构本实验指导书采用的EDA综合实验开发系统是我院电子信息与通信技术实验教学中心自主研制,整体结构如图所示。

1.2 核心板核心板采用Altera公司的EP4CE22E22C8N芯片,具有低内核电压、低功耗的特点。

芯片内部具有22320个逻辑单元,594kbit RAM嵌入式储存器,66个嵌入式18×18乘法器,4组通用PLL。

1、DIP开关主要功能是控制高低电平,通过手动控制为系统提供稳定的逻辑信号。

系统总共提供了3位拨档开关,当开关的档位在上方时则输出高电平“1”,反之则为低电平“0”。

2、复位开关复位开关可以通过手动控制为系统提供脉冲信号。

在系统中一共提供了5位的按键开关,当按下键后其输出为低电平“0”,反之则为高电平“1”。

3、发光二极管LED由一片74HC573锁存器驱动,74HC573使能后,IO口输出高电平LED点亮,反之LED则熄灭,可以模拟二进制数据输出。

4、数码管采用2位共阴极数码管,由一片74HC573锁存器驱动数码管段选,由两个三极管S8050驱动数码管位选,用于显示两位数值。

5、蜂鸣器由1个无源蜂鸣器和1个三极管S8050组成。

6、储存在本系统中采用1个32M×8位的串行Flash W25Q256,通过对其编程控制,进行数据储存与提取。

如:语音存储与回放实验。

7、时钟使用50MHz有源晶振,可以为AD/DA和数字频率计提供参考时钟。

1.3 基础扩展模块基础扩展模块有时钟模块、数字信号源、数码管模块、矩阵键盘模块、红外模块和温度模块。

1、时钟模块时钟模块中的主芯片是DS1302,DS1302由VCC1或VCC2(备用电池)两者中的较大者供电。

当VCC2大于VCC1+0.2V时,VCC2给DS1302供电。

当VCC2小于VCC1时,DS1302由VCC1供电。

X1和X2是振荡源,外接32.768kHz晶振。

RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送;I/O为串行数据输入输出端(双向);SCLK始终是输入端。

2、数字信号源数字信号源由74HC04反相缓冲器、74HC163计数器、74HC4060计数器组成,24MHz 晶振通过74HC04反相缓冲器输出5V,24M正弦波,通过74HC163二、四、八分频,74HC4060也是实现分频,其分频输出的频率都在模块的相应位置查看。

3、数码管模块数码管模块使用的是4位共阴数码管,由两片74HC573驱动位选信号以及段选信号。

74HC573当锁存使能端LE为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

OE为片选端。

4、矩阵键盘模块4×4键盘主要是通过编程实现0~F的输入,也可以作为一个控制键。

其中行占用4个I/O,列占用4个I/O。

5、红外模块红外模块中由红外接收头HS0038和一个上拉电阻组成,红外接收头的工作频率为38kHz。

当红外接收头接收到38kHz的信号时输出低电平“0”,反之输出高电平“1”,从而实现红外信号的解码。

6、温度模块温度模块由DS18B20和一个上拉电阻组成,DS18B20工作原理:刚启动时将进入低功耗等待状态,当需要执行温度测量和AD转换时,总线控制器发出[44H]指令完成温度测量和AD转换,DS18B20将产生的温度数据以两个字节的形式存储到高速暂存器的温度寄存器中,然后,DS18B20继续保持等待状态。

当DS18B20芯片由外部电源供电时,总线控制器在温度转换指令之后发起“读时隙”,从而读出测量到的温度数据通过总线完成与单片机的数据通讯,DS18B20正在温度转换中由DQ引脚返回0,转换结束则返回1。

1.4 自动控制模块自动控制模块有交通灯、步进电机和直流电机控制,其控制引脚均已标注在自动控制模块相应位置。

1、交通灯控制交通灯控制为模拟十字路口交通灯的控制,有红、绿、黄3种指示灯,共4个方向,分12个IO口控制。

LED灯的负极接在FPGA的IO口上,正极通过一个1K的限流电阻接在+3.3V电源上, LED指示灯的亮灭通过控制相应的IO口输出电平来实现。

2、步进电机控制通过将脉冲信号转变成角位移实现步进电机的精确定位,共用到4个IO口。

控制其正反转时IO口需按照一定顺序输出高低电平。

步进电机的驱动芯片为L293DD,有4个输入引脚4个输出引脚,输入输出引脚的电平关系是一一对应的,每个输出引脚能输出600mA的电流。

3、直流电机控制直流电机的控制采用脉冲宽度调制技术(PWM)。

基本原理是在固定周期内,高电平占的比重越多,电机转速就越快。

通过PNP三极管S8550提供大电流驱动直流电机,当IO口为高电平时,三极管不导通,反之则导通。

1.5 信号处理模块信号处理模块有AD采集、DA输出、语音采集、语音回放和电压调节部分。

1、AD采集AD采集部分是由AD9280采集芯片采集,信号通过SMB接口输入AD8065调节后送入AD采集。

AD9280是一款单芯片、8位、32 MSPS模数转换器(ADC),采用单电源供电,内置一个片内采样保持放大器和基准电压源。

它采用多级差分流水线架构,数据速率达32 MSPS,在整个工作温度范围内保证无失码。

语音采集部分由前级放大电路和300Hz~3.4Khz带通滤波电路组成,语音信号可由MIC接口或驻极体咪头输入,经放大电路后滤波输出至AD部分采集。

电压调节部分是由5V加在可调电阻上,实现输出电压0~5输出可调。

通过输入AD采集前级电路调节偏置后输入AD采集。

2、DA输出DA输出部分是由AD9708芯片差分输出,信号通过七阶巴特沃斯滤波后经过AD8065差分相减后再经AD8065放大后由SMB接口输出。

AD9708是TxDAC系列的8位分辨率成员系列的高性能,低功耗的CMOS数字-模拟转换器(DAC)。

该TxDAC系列包括针兼容8位,10位,12位,14位DAC,是专门opti-而得到优化用于通信系统的发射信号路径。

所有的设备共享相同的接口选项,小外形封装和引脚分布,从而提供了一个向上或向下的根据性能,分辨率选择适合的器件和成本。

AD9708提供出色的交流和直流性能同时支持更新速率高达125MSPS。

语音回放部分由滤波电路及功率放大LM386部分组成。

信号由喇叭输出。

语音信号由DA输出至滤波电路滤波,可通过调节阀调节信号幅度。

1.6 通信接口模块通信接口模块有RS232接口、PS/2接口、RS485接口、USB接口、VGA接口。

其信号输入输出均已标注在通信接口模块相应位置。

1、RS232接口RS232接口通过一个标准的DB9母头和外部的串口线连接带有串口的电脑或者其他设备,实现RS232串口通信。

2、PS/2接口PS/2接口用于连接电脑鼠标和键盘等PS/2设备,通过PS/2口,仅仅需要两个IO 口,就可以扩展一个键盘。

3、RS485接口RS485接口通过MAX485芯片实现逻辑电平转换,通过两个端口和外部RS485设备连接,即A和B,不需要GND,可实现多点双向通信,数据传输距离可达千米。

4、USB接口USB接口采用PL2303来实现USB转串口,同时对串口信号设置了两个LED指示灯,用于指示串口数据收发。

5、VGA接口VGA接口主要是通过编程实现VGA视频信号在监视器上显示,其中包含R、G、B、HS、VS来控制视频显示。

第二章开发平台简介2.1 Quartus II简介Quartus II是Altera公司的综合性EDA开发软件,支持原理图、VHDL、Verilog HDL和AHDL等设计模式,内嵌综合器和仿真器,可以完成从设计输入到硬件配置的完整设计流程。

Quartus II支持Altera的IP核,集成了LPM/MegaFunction宏功能模块库,简化了设计的复杂性、加快了设计速度。

用户可以使用第三方EDA工具。

2.2 Quartus II开发流程一、创建工程1、建立工程目录新建一个文件夹,用于存放工程文件。

文件路径中不能包含中文。

2、新建工程单击菜单File | New Project Wizard。

指定工程目录、名称和顶层设计实体,选择目标芯片。

将工程视图切换到Files标签。

3、新建文件单击工具栏上的按钮或菜单File | New。

选择Design Files下的Block Diagram/Schematic File,新建原理图文件。

选择Design Files下的Verilog HDL File,新建源程序文件。

选择Memory Files下的Hexadecimal File或Memory Initialization File,新建内存初始化文件。

选择Verifica/Debugging Files下的Unive Program VWF,新建仿真波形文件。

在原理图编辑窗口双击左键,即可打开插入元件对话框。

展开元件所在的类的图标,或直接在Name框中输入元件名称,可找到需要的元件。

单击MegaWizard Plug-In Manager按钮,即可启动宏功能定制向导。

4、保存文件单击工具栏上的按钮或菜单File | Save As,保存文件。

在工程视图中,如果没有所需文件的图标,选中Files图标,单击右键后选择Add/Remove Files in Project。