寄生参数提取-CalibrexRC培训班

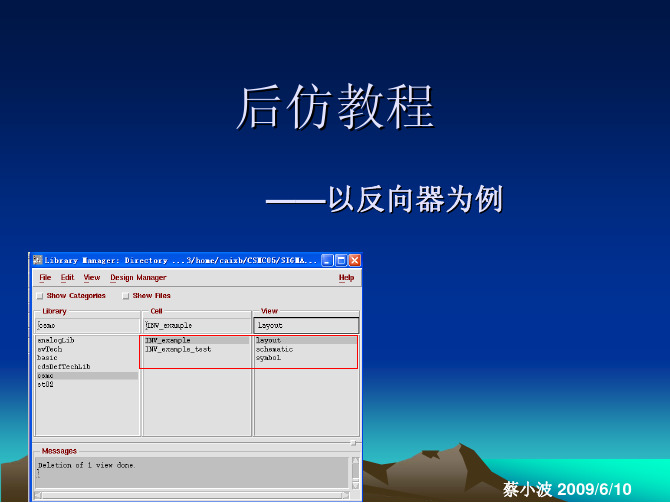

cadence后仿教程

点击Start RVE导出如上图窗口,再点击“寄生虫” 按扭,弹出寄生参数窗口(见下页)

这里列出了所有节点的 名称,到地电容(C) 和线间电容(CC)的大小. 如果想要具体察看某个 节点到其他节点的寄生 电容的大小,那么选选 中这个节点,如左图所 示,再点击按扭”P”,弹出 窗口(如左下图),在 Capacitance选项卡中 列出了节点IN与 OUT,GND,VDD之间的 寄生电容的大小.

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

设置好库文件和仿真类型,点击Run 即可开始后仿!

方法二:

请参见LAB2 里的

Mixed-level simulation (简单说就是建一个config 文件,可以自己配制仿真 所调用的view的类型)

<3>指定提取哪些节点的寄生参数: 默认是ALL Nets(提取所有节点) 也可以自定义(Specified Nets):可以提取除了指

定节点以外的所有节点(Exclude),也可以只提取指定的 节点(Include),在相应的文本框里写入节点的net名即 可,或者点击右侧的小箭头,然后在弹出的原理图里选择你 想输入的节点,按ESC键,你所选择的节点名就自动填在左 侧文本框中.

至此,我们仍未进行后仿,我们只是提取出 了寄生参数,并生成了带这些寄生参数的 calibre view,这都是为后仿做准备. 接下来介绍如何后仿.

参数提取

对GDSII database进行gate-level寄生参数抽取VIMICRO 祝侃1.Abstract伴随着SOC技术的发展,自动布局布线规模不断扩大,同时产品的上市周期由于市场竞争的加剧压力也愈来愈大。

因此,如何提高自动布局布线设计中寄生参数验证的效率成为众多IC设计者必须要考虑的重要课题。

通过引入calibre DRC/LVS/XRC,vimicro已经发展了一套提高自动布局布线设计验证效率的方法,这些方法包括GDSII文件的直接处理,使用gate-level寄生参数抽取来满足数字电路的时序分析验证,以及修改相应的文件来加速寄生参数的抽取等。

2. Introduction首先,在自动布局布线结束后,我们通常会进行DRC/LVS检查,然后在 layout editor (如Virtuoso)里修改错误,最后得到DRC/LVS clean的GDSII 文件。

这个时候前端设计人员发现功能有问题进行了修改,要求自动布局布线作 ECO。

这样原先的DRC/LVS检查都要重新做一遍。

对DRC/LVS clean的GDSII 文件抽取寄生参数,然后拿这个含有寄生参数的网表作 STA,如果时序可以满足要求的话,就不需要做那些重复的工作了。

Calibre xRC可以对GDSII 数据进行gate level 的寄生参数抽取.这样的设计流程是针对于简单的ECO改动,例如IO位置的调整,或者对为数不多的逻辑门连接关系的修改。

对于复杂的改动,还必须应用自动布局布线的 ECO流程.3. Flow Description1).Run hierarchical LVS (PHDB Generation)执行hierarchical LVS是为了对layout做器件和连接关系的抽取,并且建立版图和网表的cross-reference.2).抽取寄生参数 (PDB Generation)Calibre XRC 抽取gate level的寄生参数.3).写出网表 (FMT)Calibre xRC 从第二步抽取的寄生参数数据中写出DSPF 或 SPEF 网表.4).静态时序分析 (STA)PrimeTime 读入DSPF 或 SPEF 网表,还有原来的verilog 网表 和cell library,产生SDF文件.1).LVS-H首先要Run hierarchical LVS,就需要设定hcell list.Calibre xRC 叫做xcell.这个xcell list跟普通的LVS使用的hcell list差不多,只是比LVS要更严格一些,需要Calibre识别出所有的standard cells and micro blocks.这样在第二步抽取寄生参数的时候Calibre才知道那些出现在hcell list里的cells里面是不要抽取寄生参数的而只需要抽取top cell的连接线部分就好了.判断xcell是不是正确的,要看lvs report file里top cell的统计结果是不是都是cells而没有devices.比如下面这个结果虽然LVS clean, 但是并不适合做gate level RC extraction.LAYOUT CELL NAME: chip_topSOURCE CELL NAME: chip_topINITIAL NUMBERS OF OBJECTSLayout Source Component Type------ ------ --------------Ports: 370 370Nets: 11098 11098Instances: 303 303 MN (4 pins)307 307 MP (4 pins)150 150 ADFULD1 (7 pins)2873 2873 ADFULDL (7 pins)一定要保证在top level的报告中看不到device才可以.LAYOUT CELL NAME: chip_topSOURCE CELL NAME: chip_topINITIAL NUMBERS OF OBJECTSLayout Source Component Type------ ------ --------------Ports: 370 370Nets: 10207 10207Instances: 150 150 ADFULD1 (7 pins)2873 2873 ADFULDL (7 pins)33 33 AOI33D1 (9 pins)1 1 AOI33D2 (9 pins)1 1 AOI33D4 (9 pins)LVS的执行命令跟普通的LVS是完全一样的:calibre –lvs –hier –hcell <hcell list> -spice svdb/<layout netlist file> <rulefile> |tee <lvs log file>2).PDB Extraction第二步抽取寄生参数,Calibre XRC 从2006.3版本开始有个新的选项 -asic,使用了这个选项,xRC会对asic design进行优化以提高抽取的速度.这个新的选项可以使gate level extraction的速度提高10倍,并且对内存的消耗也大大降低.calibre –xrc –pdb –asic –hcell <hcell list> [-rc] <rulefile> |tee <pdb log file>3).Ouput netlistCalibre xRC可以写出符合不同后仿真工具的网表格式,比如ELDO,HSPICE, SPECTRE 等. 使用PrimeTime一般需要DSPF 或 SPEF 格式. Calibre xRC从 2006.3 的版本开始有一个新的选项 “PRIMETIME”来控制DSPF 和SPEF输出格式,可以使输出的SDPF和SPEF网表更加符合PrimeTime的要求,且网表大小缩小10倍以上.PEX NETLIST DISTRIBUTED filename DSPF [PRIMETIME]PEX NETLIST DISTRIBUTED filename SPEF [PRIMETIME]在rulefile里设置好这个选项就可以写出网表了:calibre –xrc –fmt –hcell <hcell list> -all [–g] <rulefile> |tee <fmt log file> 由于是从GDSII文件抽取gate level的寄生参数,calibre 读入的是GDSII和 spice netlist,但是要输出供PrimeTime使用的网表就需要对输出网表作一些特别处理.需要设置几个环境变量:PEX_FMT_SPF_INSTANCE_SECTION OFFPEX_FMT_NOXREF_MODEL_MODE NONEPEX_FMT_SPF_NAME_FILTER_MODE “X”PEX_FMT_SPF_LUMPED_MODEL_MODE NONE新的[PRIMETIME]选项也可以自动设置PEX_FMT_SPF_INSTANCE_SECTION OFF 和 PEX_FMT_SPF_NAME_FILTER_MODE “X”.大家千万不要被这么多的运行命令和环境变量吓坏了,其实写个批处理就很方便了.比如批处理的名字叫run_xrc#!/bin/csh -fsetenv PEX_FMT_SPF_NAME_FILTER_MODE "X"setenv PEX_FMT_NOXREF_MODEL_MODE NONEsetenv PEX_FMT_EXCLUDE_NET_FILTER ONsetenv PEX_FMT_SPF_INSTANCE_SECTION OFF\rm -rf ./svdbcalibre -lvs -hier -hcell hcells -spice svdb/DESIGN.sp rules |tee lvs.logcalibre -xrc -pdb -turbo -asic -hcell hcells -rc rules |tee pdb.logcalibre -xrc -fmt -all -hcell hcells rules |tee fmt.log4. Conclusion在这个流程中,Calibre LVS是一个被业界认可并且广泛采用的工具.在 LVS 的基础上对GDSII数据进行寄生参数抽取就变得非常简单,易于掌握.Calibre xRC 既可以做transistor level extraction也可以做gate level extraction.在这里我们使用Calibre xRC对GDSII数据进行gate level 寄生参数抽取,使整个设计流程,特别是后端设计过程变得更加简单并且节省时间.。

新一代寄生参数提取软件ICExt

l 袢值 ( ) 时M() F群值( } f i s b m 谖 箍f Ii() 加 速 比 %) f u s  ̄J j '

图 2 1一个典型 的 3 D互连寄生 电容结构 . 一

宜例 l 蛮例 2 例3

0 59 5 8 N. A.

快几十甚至上百倍 。Q E B M采用的是基于直接边 界

内存原因已经无法计算 , Q E 而 B M依 然在较短 的时

间得到了计算结果。 这些测试结果表 明 Q E B M相 比 三维场求解提 取软件 x确实具有三维结构处理能

的 6 %与 I 5 c技术有关 。它对 国民生产总值的贡献 两种电容计算方法 ,对于具有复杂三维互连结构的 进行大规模 的全芯 是计算机产业的 2 , 倍 是钢铁产业 的 20 倍 。过去 关键线 网采用 维场求解方法 , 00

四十年来 , 技术一直按 M o 定律持续高速地发 I c or e

维普资讯

新一代寄生参数提取软件 I t OE x

北京华天 中汇科技有限公 司 陆涛涛 杜 玉惠

中芯国际集成电路制造 ( 上海 ) 有限公 司 文建

寿国平

1 背 景 .

在高速发展 的现代科学技术中,作为信息产业

算速度快 , 但精度较低 , 以准确处理复杂的三维结 难 构。 ● 数值模拟方法通过求解场方程计算互连 电

18 48 5 5 4l

9 56 5 3 29 l

,. (3 】% -. 8

64 9 4 5 4

2f 3 i 56 7

匀介质 , 此产品具有一定的影响。随机漫步方法是

注 : 件 X的 版 本 是 2 0 . 6 软 4 0 0

利用统计学原理的非确定性数值算法 ,已用于软件

eetop[1].cn_05nCalibre xRC

![eetop[1].cn_05nCalibre xRC](https://img.taocdn.com/s3/m/32308bf59e31433239689340.png)

应用Calibre xRC 辅助模拟电路版图纠错威盛电子(中国)有限公司 蔡光杰[摘要]在模拟电路设计中,在版图完成之后进行带寄生参数仿真是必要的,该仿真能够检查实际的版图在多大程度上符合我们的设计要求。

Calibre xRC是一款优秀的版图寄生电阻电容抽取工具,它能提供非常详细的寄生参数信息。

但是,越是详细的寄生参数网表就必然导致越长的仿真时间,这往往给电路的后仿真带来一些不方便,增加电路纠错的周期。

本文将根据实际工作的经验,介绍如何使用Calibre xRC的RC-Reduction和Lumped C功能来简化寄生参数网表,以缩短电路纠错的周期,以及在实际中的应用效果。

1.寄生电阻电容对模拟电路的影响在模拟电路设计中,电路中的各种寄生效应对性能影响很大。

一般来说,寄生电阻和寄生电容对电路的影响最为明显。

如果忽略寄生效应的影响,会导致仿真结果偏离了真实情况,甚至会出现错误的结果。

如果能抽取出这些寄生效应的数据,结合电路进行仿真,就能够比较准确的模拟真实电路的特性。

Calibre xRC 为我们提供了抽取电路寄生参数的解决方案。

通过对电路版图的分析,Calibre xRC能够抽取对电路性能影响最为重要的寄生电阻和寄生电容。

然而随着电路的复杂度上升,我们抽取出来的带有寄生电容和寄生电阻的网表变得巨大而且复杂,使用这样的网表进行仿真需要的时间也变得非常长。

如果我们通过仿真发现电路存在问题,需要寻找问题所在并要进行多次仿真,则可以通过Calibre xRC 的一些选项来简化网表,并且使得问题更容易被发现。

下面两个例子分别使用RC-Reduction和Lumped C来简化后仿真网表,并且使我们能迅速找到问题所在。

2.快速定位影响电路性能的主要寄生电阻下面举的例子是应用在Audio方面的电路,如图1所示,相对应的版图如图2所示。

图1图2这是一个单声道功率放大器,带音量调节功能和静音功能。

电路由三部分组成,功率放大器,可调电阻单元,数字逻辑控制单元。

RC寄生参数提取在数模混合IC设计中的应用

1概述基于全定制设计方法设计的模拟模块以及标准单元库在完成版图工作后,为确保版图符合设计要求且连线正确需要进行DRC和LVS检查。

集成电路通过版图设计最终转化到硅片后,由于同层以及不同层材料之间寄生参数的影响会使电路性能与最初仿真结果产生偏差甚至使电路无法正常工作。

因此,电路完成DRC和LVS后还需进行版图寄生参数提取(LPE:layout parasitic extraction)和寄生电阻提取(PRE,parasitic resistance extraction)[1]。

大规模数字集成电路芯片的物理实施中,完成布线后的一项重要工作是进行静态时序分析(STA:static timing analysis)。

在时序分析前,则首先需要对芯片的物理版图设计进行包括电阻、电容以及电感的参数提取,再进行延时计算。

版图设计的完整寄生参数应当包括R、C、L、K,其中L(电感)和K(互感)在单元库版图和低频数字IC中常常忽略[2]。

LPE/PRE完成后我们将会得到一个含有大量寄生元件信息的电路SPICE或CDL 格式网表文件。

该网表文件反映了电路版图的精确特性。

用它进行SPICE后仿真(post-simulation)。

如RC寄生参数提取在数模混合IC设计中的应用王巍(国家集成电路设计深圳产业化基地)摘要:目前的数模混合集成电路设计中,需要对模拟部分进行后版图仿真并对整体电路进行时序分析。

版图后仿真需要进行晶体管级的寄生参数提取,芯片时序分析则需要对互连线进行寄生参数提取。

RC 寄生参数提取的精确度和效率在很大程度上影响着整体芯片设计的质量和效率。

Abstract:In the current mixed analog-digital circuit design,the analog module need to do post-layout simulation and the full-chip need to do STA.While the post-layout simulation need the RC extraction in transistor-level and the interconnect delay also need to be extracted in order to do STA.The definition and efficiency of the RC extraction are very important to the quality of the full-chip design.果后仿真结果同样满足设计要求,那么这时就能够确定版图设计有问题。

后仿真calibre

name重复即可。比如,取做calibre_r,calibre_rc或calibre_rcc,以分别代

表不同的提取形式,本文中直接取成calibre。Cellmap File是描述寄生参量提

取前后器件对应关系的文件,默认的是./calview.cellmap,即 Virtuoso启动目

数提取。Calibre xRC被主流 foundry所支持,具有良好的精确性,特别是对于

模拟和射频电路,输出能够反标回主流的仿真工具中,满足不同的设计流程。使

用 Calibre xRC进行寄生参量提取时,选择 calibreview的输出形式,可以非常

方便的在 Virtuoso的 ADE中直接进行后仿真,以及进行前后仿真结果的比较。

6

XCELL YES语句。最后,采用 gate level的方式进行寄生参量提取,确保工具

将 RF器件识别为一子电路。如果采用 GUI的方式,在图 3所示的界面中,选择

gate level提取,而不是transistor level级提取。同时在input选项中的xcell

部分选择已写好的 xcell文件,如图 8所示。

给出了本例中的LNA前仿真和提取RCC之后的后仿真的瞬态结果对比。由此可见,

采用 calibreview的输出形式能够非常方便的在 Virtuoso的 ADE中进行后仿真

和比较前后仿真结果。

5

图 7 LNA前仿真和后仿真瞬态波形对比

使用 XCELL避免寄生参量的重复提取

图 1中,黑线框所示为 RF器件。与一般的 MOS器件不同,这类器件的模型

calibre寄生参数提取

calibre寄生参数提取

寄生参数提取是指从设计中提取出寄生参数,以进行后续的分析和仿真。

在Calibre 中,有多种寄生参数提取器可供选择,以下是其中几种:

- RCX:标准RC提取器,可以提取晶体管和互连线的电容和电阻等寄生参数。

- xRC:扩展RC提取器,提供了更高级的功能,如几何抽象、子网合并、等效电路分析等。

- StarRC:寄生参数提取器,可以提取复杂的芯片级互连线寄生参数,包括互联线交叉、几何扭曲、设备变形等。

- QRC:快速RC提取器,可以在短时间内提取大规模的互连线寄生参数,支持多线程计算和分布式计算等高级功能。

- PEX:功率网提取器,可以提取功率网的电容和电阻等寄生参数。

在使用Calibre提取寄生参数时,你需要根据设计需求和工艺厂提供的文件,选择合适的提取器并进行相应的设置。

如果你需要了解更详细的信息,可以查阅Calibre的文档或联系技术支持。

Calibre xRC的使用

Calibre xRC 的使用1.版图中的寄生参数在使用Calibre xRC提取寄生参数之前,先介绍一下电路中的寄生参数。

一般来讲,寄生参数有寄生电阻、寄生电容、寄生电感等,其中寄生电阻和寄生电容对电路的影响最为明显。

在版图中,各导电层如铝线、多晶等及导电层之间的接触孔只要有电流通过就会有寄生电阻。

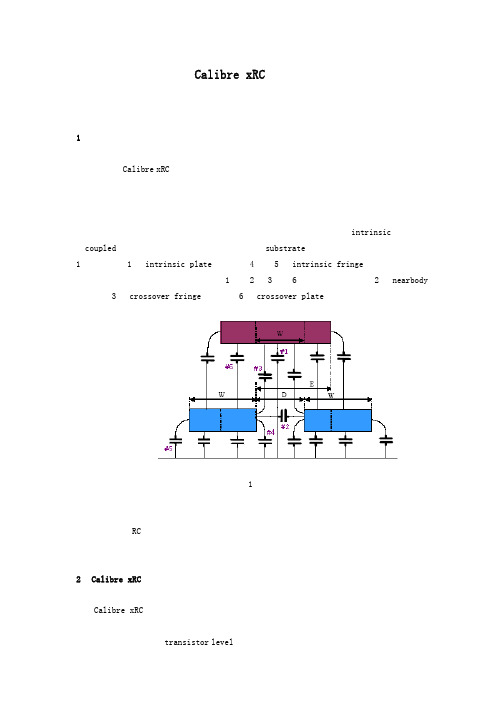

两层导电层之间会存在寄生电容,寄生电容一般可分为本征(intrinsic)和耦合(coupled)两种,本征电容是指导电层到衬底(substrate)的电容,它有两种类型,如图1中所示:#1为intrinsic plate电容,#4和#5为intrinsic fringe电容;耦合电容是指导电层在不同网线之间的电容,图1中#2、#3和#6就属于这种,其中#2为nearbody 电容,#3为crossover fringe电容,#6为crossover plate电容。

图1 寄生电容模型电路中寄生参数的存在给电路的工作造成了一定的影响,寄生电阻的存在会影响到电路的功耗,寄生RC会影响电路中的信号完整性,等等。

所以在版图完成后,必须提取出版图中的寄生参数,将它们反标入逻辑电路中一起进行仿真,以此来检查版图设计的准确性。

2.Calibre xRC功能简介Calibre xRC提供了多种寄生参数提取解决方案。

它可以根据电路设计的不同要求来提取不同的寄生参数网表,针对全定制电路和模拟电路可以提取晶体管级(transistor level)的网表,针对自动布局布线产生的电路可以提取门级(gate level)网表,针对数模混合电路可以提取混合级(ADMS)的电路网表。

它还可以根据不同的电路分析要求进行提取,针对电路的功耗(Power)分析,只进行寄生电阻的提取,针对电路的噪声(Noise)分析而仅对寄生电容的提取,针对电路的时序(Timing)分析而提取相应的RC或RCC网表,针对电路的信号完整性(Signal Integrity)分析提取寄生RC或RCC网表。

集成电路设计实践1_187401985

课程简介

成绩评定:

• 平时成绩: 20%

– 中期检查,安排在选题及方案设计、电路设计、 版图设计等阶段

• 答辩及总结报告: 80%

– 课程项目的完成质量 – 答辩情况 – 总结报告的书写质量

• 选题, 设计, 流片, 答辩, 总结报告等缺一不 可, 否则不给成绩

课程简介

• 总结报告要求

第一部分: 摘要 (中、英文) 300字 包括设计的内容、预期目的、主要电路结构、测试

课程历史

开课时间:2000年~ 开课单位:电子系 微电子所 授课对象:工学硕士 工程硕士 加工工艺:0.8um 0.6um 0.5um 授课老师:李冬梅 黄亚东 李福乐 授课方式:设计实践为主 设计实践/课堂教学 并重 选题范围:自由选题 单一命题 自由选题 教学效果:(IC设计)课程学习课题研究的桥梁

第11~18周

流水加工

答辩会

测试

秋季学期

课程报告

课程项目:

课程简介

• 结合本人的论文课题方向自行设计题目 • 结合实验室的科研任务设计题目 • 鼓励做有创新的、有用的设计 • 参考题目:

– Bandgap+LDO, 温漂<50ppm – LDO/Charge pump buck – On-Chip Temp. Sensor – 传感器接口电路(电容/电阻) – DAC/DDS信号合成电路 – ADC:Flash, SAR, Cyclic, Pipeline, sigma-delta, … – Low-pass Active-RC or Switched-capacitor filter – Oscillator (Crystal, RC) – PLL时钟倍频电路,Fi = 8MHz, Fo = 64MHz – SRAM • 自由组队,合作完成,1~2人/题目 • 每组推选一个组长,负责任务的协调分配,每组交一个设计报告,在 报告最后需说明组内个人的工作内容

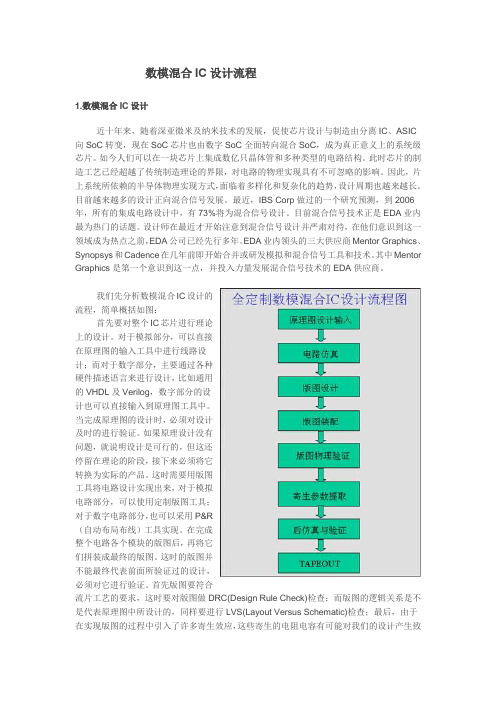

数模混合IC设计流程

数模混合IC设计流程1.数模混合IC设计近十年来,随着深亚微米及纳米技术的发展,促使芯片设计与制造由分离IC、ASIC 向SoC转变,现在SoC芯片也由数字SoC全面转向混合SoC,成为真正意义上的系统级芯片。

如今人们可以在一块芯片上集成数亿只晶体管和多种类型的电路结构。

此时芯片的制造工艺已经超越了传统制造理论的界限,对电路的物理实现具有不可忽略的影响。

因此,片上系统所依赖的半导体物理实现方式,面临着多样化和复杂化的趋势,设计周期也越来越长。

目前越来越多的设计正向混合信号发展。

最近,IBS Corp做过的一个研究预测,到2006年,所有的集成电路设计中,有73%将为混合信号设计。

目前混合信号技术正是EDA业内最为热门的话题。

设计师在最近才开始注意到混合信号设计并严肃对待,在他们意识到这一领域成为热点之前,EDA公司已经先行多年。

EDA业内领头的三大供应商Mentor Graphics、Synopsys和Cadence在几年前即开始合并或研发模拟和混合信号工具和技术。

其中Mentor Graphics是第一个意识到这一点,并投入力量发展混合信号技术的EDA供应商。

我们先分析数模混合IC设计的流程,简单概括如图:首先要对整个IC芯片进行理论上的设计。

对于模拟部分,可以直接在原理图的输入工具中进行线路设计;而对于数字部分,主要通过各种硬件描述语言来进行设计,比如通用的VHDL及Verilog,数字部分的设计也可以直接输入到原理图工具中。

当完成原理图的设计时,必须对设计及时的进行验证。

如果原理设计没有问题,就说明设计是可行的,但这还停留在理论的阶段,接下来必须将它转换为实际的产品。

这时需要用版图工具将电路设计实现出来,对于模拟电路部分,可以使用定制版图工具;对于数字电路部分,也可以采用P&R(自动布局布线)工具实现。

在完成整个电路各个模块的版图后,再将它们拼装成最终的版图。

这时的版图并不能最终代表前面所验证过的设计,必须对它进行验证。

CMOS模拟集成电路版图设计课程大纲

CMOS模拟集成电路版图设计课程大纲第一讲CMOS模拟集成电路版图基础⏹CMOS模拟版图概述⏹CMOS模拟集成电路版图的定义⏹CMOS模拟集成电路版图设计流程❑版图规划❑版图设计实现❑版图验证❑版图完成⏹CMOS模拟集成电路版图设计工具第二讲模拟集成电路版图器件与互连⏹概述⏹器件❑MOS管❑电阻❑电容❑电感❑三极管⏹互连❑金属(第一层金属,第二层金属……)❑通孔第三讲寄生参数⏹概述⏹寄生电容⏹线电阻压降(IR drop)⏹寄生电感⏹连线寄生模型⏹MOS管寄生效应第四讲器件匹配⏹概述⏹指状交叉法线⏹共质心法⏹虚拟器件⏹MOS晶体管匹配⏹电阻匹配⏹电容匹配⏹差分线布线⏹器件匹配总则第五讲设计规则⏹概述⏹工艺库中各类器件的层信息⏹设计规则细则⏹工业标准的基本数据格式第六讲验证⏹设计规则检查(DRC)Design Rule Check⏹版图与电路图的对照(LVS)Layout Versus Schematic⏹电气规则检查(ERC)Electrical Rule Check⏹天线规则检查(ANT)⏹静电放电检查(ESD)第七讲可靠性设计⏹天线效应⏹闩锁效应⏹静电放电保护(Electro-Static Discharge ,ESD)⏹数模混合集成电路版图设计第八讲工艺设计工具包(PDK)⏹ 1.PDK名称的涵义⏹ 2.PDK中包含的内容● 2.1 IO lib2.1.1 GDS文件的导入操作2.1.2 网表导入2.1.3 IO使用文档介绍● 2.2 SMIC_13_PDK_v2.6_20142.2.1 Smic13mmrf_1233文件夹2.2.2 model 文件夹2.2.3 Calibre 文件夹● 2.3 SMIC_13_TF_LG_LIST_2014122.3.1 Standard cell Timing lib2.3.2 Calview.cellmap2.3.3 Standard cell netlist及网表导入操作2.3.4 Ant rule (天线规则)第九讲Cadence spectre概述与操作界面⏹Cadence spectre 概述⏹Cadence spectre的特点⏹Cadence spectre的仿真设计方法⏹Cadence spectre与其他EDA软件的连接⏹Cadence spectre的基本操作第十讲Spectre窗口和库元件⏹模拟设计环境(Analog Design Environment)⏹波形显示窗口(Waveform)⏹波形计算器(Waveform Calculator)⏹Spectre库中的基本器件第十讲Cadence Virtuoso版图设计工具⏹Cadence Virtuoso概述⏹Virtuoso 界面介绍⏹Virtuoso 基本操作第十一讲Mentor Calibre版图验证工具⏹Mentor Calibre版图验证工具概述⏹Mentor Calibre版图验证工具调用⏹Mentor Calibre DRC验证⏹Mentor Calibre LVS验证⏹Mentor Calibre寄生参数提取(PEX)第十二讲版图设计与验证流程实例⏹设计环境准备⏹反相器链电路的建立和前仿真⏹反相器链版图设计⏹反相器链版图验证与参数提取⏹反相器链电路后仿真⏹输入输出单元环设计⏹主体电路版图与输入输出单元环的连接⏹导出GDSII文件。

使用 Calibre 实现RFCMOS 电路的寄生参量提取

使用Calibre xRC实现RFCMOS电路的寄生参量提取及后仿真中国科学院微电子研究所郭慧民[摘要]Calibre xRC是Mentor Graphics公司用于寄生参量提取的工具,其强大的功能和良好的易用性使其得到业界的广泛认可。

本文以采用RFCMOS工艺实现的LNA为例,介绍使用Calibre xRC对RFCMOS电路寄生参量提取,以Calibreview 形式输出以及在Virtuoso的ADE中直接后仿真的流程。

本文还将讨论Calibre xRC特有的XCELL方式对包含RF器件的电路仿真结果的影响。

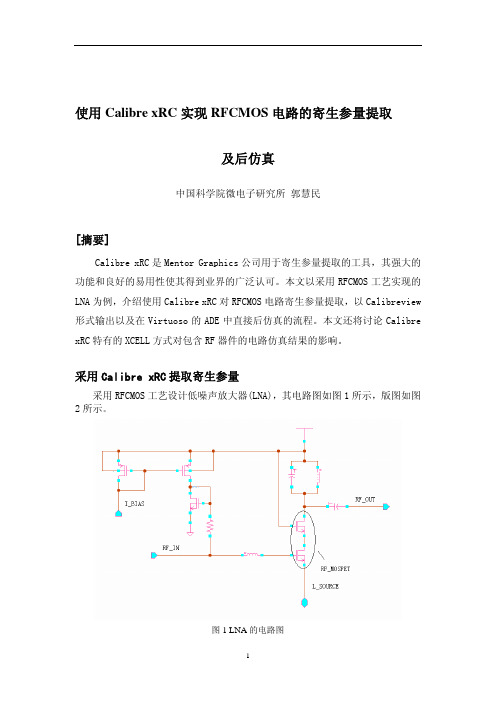

采用Calibre xRC提取寄生参量采用RFCMOS工艺设计低噪声放大器(LNA),其电路图如图1所示,版图如图2所示。

图1 LNA的电路图图2 LNA的版图Calibre支持将其快捷方式嵌入在Virtuoso平台中。

用户只需在自己.cdsinit文件中加入以下一行语句:load( strcat( getShellEnvVar("MGC_HOME") "/lib/calibre.skl" ))就可以在virtuoso的菜单中出现“calibre”一项,包含如下菜单:点击Run PEX,启动Calibre xRC的GUI,如图3所示。

Outputs菜单中的Extraction Type里,第一项通常选择Transistor Level或Gate Level,分别代表晶体管级提取和门级提取。

第二项可以选择R+C+CC,R+C,R,C+CC,其中R 代表寄生电阻,C代表本征寄生电容,CC代表耦合电容。

第三项可以选择No Inductance,L或L+M,分别代表不提取电感,只提取自感和提取自感与互感。

这些设置由电路图的规模和提取的精度而定。

在Format一栏中,可以选择SPECTRE,ELDO,HSPICE等网表形式,也可以选择Calibre xRC提供的CALIBREVIEW形式。

cadence后仿教程

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

默认第一项是 spectre,意味着 INV_example_tes t里调用的是 INV_example的 schmatic view来 进行仿真

如要进行后仿我们得 修改Switch View List, 把calibre加在spectre 前面,意味着仿真的时 候INV_example_test 调用INV_example的 calibre view来进行仿 真,这就是后仿!!!

设置好库文件和仿真类型,点击Run 即可开始后仿!

方法二:

请参见LAB2 里的

Mixed-level simulation (简单说就是建一个config 文件,可以自己配制仿真 所调用的view的类型)

得修改引用路径,直接写成绝对路径就行

引用了LVS文件, 所以说PEX之 前其实又做了 一遍LVS

点一下就可 以对文本 进行修改

4.设置Inputs选项

5.设置Outputs选项

<1>提取类型选择:R表示提取寄生电阻 C表示提取到地寄生电容 CC表示提取线间寄生电容 在电路规模较大情况下,一般不提电阻寄生电阻, 因为这会导致电路节点极剧增多,无法进行后仿, 所以电阻的提取只限示小模块电路.一般选C+CC.

PMOS管 NMOS管

寄生电容的映射模型 选择理想电容,即 analogLib中的cap. 如果你选择了提取寄 生电阻,那么相应 的应该选择 analogLib中的res. 最终弹出Calibre Info(如左图所示), “0 warnings and 0 errors”说明 CalibreView成功生 成.

Calibre使用简介B

2019年10月

9

DRC Rule File

下面是一个简单的calibre LVS Rule File,右边是对它的解释。#与//后是注释部分 layout system gdsii #指明输入的版图格式是GDSII,calibre 还可支持其他格 式 layout path “/ layout/basic_drc.gds” #输入版图的路径 layout primary basic_drc # 要检查的版图的top cell 名字 drc results database “/training/drc_results_db” # drc 的输出, 将来可以用 calibre 结合virtuoso 分析 variable metal_width 3 #定义一个变量 layer substrate 0 # 本行和下面相似的行定义了输入版图中每一层的名字 layer pwell 1 # 本行把GDS 的layer 1 定义为pwell,接下来pwell 都指输入的 GDS 的layer1。 layer oxide 2 layer res 3 layer poly 4 layer nplus 5 layer pplus 6 layer contact 7 layer metal1 8

© 2006 微电子中心

2019年10月

8

因为做DRC 会产生很多文件,建议建立一个专属于此Layout 做DRC 时的 新文件夹。然后拷贝Rule File 至此工作目录下。

从版图中导出GDS文件至此工作目录下,亦可在Calibre DRC 图形界面中 选择从当前版图中导出GDS文件。

© 2006 微电子中心

1

Calibre使用简介

寄生参数提取 starrc流程

寄生参数提取 starrc流程Parasitic parameter extraction is an important process in the semiconductor industry that involves analyzing the parasitic effects of transistor components on circuit performance. This process plays a crucial role in ensuring the accurate simulation and design of integrated circuits. 寄生参数提取是半导体行业中的一个重要流程,涉及分析晶体管元件对电路性能的寄生效应。

这一过程在确保集成电路的准确仿真和设计中起着至关重要的作用。

One of the key challenges in parasitic parameter extraction is accurately identifying and quantifying the parasitic effects of various components in a circuit. This requires sophisticated modeling techniques and simulation tools to capture the complex interactions between different elements. 寄生参数提取中的一个关键挑战是准确识别和量化电路中各种组件的寄生效应。

这需要复杂的建模技术和仿真工具来捕获不同元件之间的复杂相互作用。

Moreover, the increasing complexity and shrinking dimensions of integrated circuits make parasitic parameter extraction even more challenging. As transistors and other components become smaller,the parasitic effects become more pronounced and can significantly impact circuit performance. 此外,集成电路日益复杂和尺寸缩小使得寄生参数提取变得更加困难。

pex提取寄生参数

pex提取寄生参数摘要:I.引言- 介绍pex 提取寄生参数的概念II.pex 提取寄生参数的方法- 简述pex 提取寄生参数的具体步骤III.pex 提取寄生参数的应用- 阐述pex 提取寄生参数在实际问题中的运用IV.pex 提取寄生参数的优缺点- 分析pex 提取寄生参数的优点和不足V.结论- 总结pex 提取寄生参数的重要性和前景正文:I.引言在数据分析、机器学习等领域,特征提取是关键步骤,它直接影响到后续模型效果的好坏。

寄生参数(parasitic parameter)指的是在特征提取过程中,除了目标参数以外的其他辅助参数,这些参数可能对目标参数的提取起到一定作用,但同时也可能带来噪声。

近年来,pex 提取寄生参数的方法逐渐受到研究者们的关注。

II.pex 提取寄生参数的方法pex 提取寄生参数主要包括以下几个步骤:1.数据准备:收集与目标参数相关的数据,进行预处理,如缺失值填充、异常值处理等。

2.特征工程:利用现有的特征提取方法,如主成分分析(PCA)、自动编码器(AE)等,对数据进行特征提取。

3.参数估计:根据提取到的特征,使用统计方法或机器学习算法,估计目标参数和寄生参数。

4.模型评估:对估计出的参数进行模型评估,检查模型效果。

5.参数优化:根据模型评估结果,调整特征提取方法和参数估计方法,以提高模型效果。

III.pex 提取寄生参数的应用pex 提取寄生参数在实际问题中具有广泛应用,例如在金融领域的信用评分卡、医疗领域的疾病预测等。

通过寄生参数的提取,可以降低目标参数的估计误差,提高模型预测效果。

IV.pex 提取寄生参数的优缺点pex 提取寄生参数的优点在于能够提高目标参数估计的精确度,降低模型预测误差。

然而,它也存在一些不足,如在特征提取过程中可能引入过多噪声,导致模型过拟合。

此外,pex 提取寄生参数的方法依赖于数据和特征,当数据量不足或特征选择不当时,可能无法有效提高模型效果。

寄生参数素材课件

目录 Contents

• 寄生参数概述 • 寄生电阻 • 寄生电容 • 寄生电感 • 寄生参数提取技术 • 寄生参数在电路设计中应用案例

01

寄生参数概述

定义与分类

定义

在电子电路中,除元件本身的电 阻、电容和电感等基本参数外, 还存在一些附加参数,称为寄生 参数。

分类

主要包括寄生电阻、寄生电容和 寄生电感等。

降低电路效率

寄生电感可能增加电路中的无功功率,降低电路 的工作效率。

减小寄生电感方法

1 2

优化布线

合理布局导线,减小导线长度和回路面积,降低 寄生电感。

使用低电感元件

选择引脚电感较小的电子元件,降低寄生电感的 影响。

3

采用多层板结构

利用多层板结构,将电源线和地线分别布置在不 同层,减小互感。

05

提高接触质量

优化导体之间的接触质量 ,如采用镀金、镀银等工 艺,降低接触电阻。

优化焊接工艺

改进元器件引脚的焊接工 艺,确保焊接质量良好, 降低引脚电阻。

03

寄生电容

寄生电容产生原因

导线之间电容

由于导线之间存在电场,导线之间会形成电容,即导线间寄生电 容。

元件引脚与地之间电容

元件引脚与地之间存在电场,形成引脚与地之间的寄生电容。

寄生参数影响

01

02

03

04

信号完整性

寄生参数可能导致信号失真、 衰减和噪声增加,影响信号完

整性。

电源完整性

寄生参数可能引起电源波动、 纹波和噪声,影响电源完整性

。

电磁兼容性

寄生参数可能产生电磁干扰( EMI)和电磁兼容性(EMC)

问题。

电路性能

calibredrc和lvs验证总结

v2lvs能够把verilog网表和相对应的spice库、verilog子库转成Calibre LVS用

RULECHECK CT_11 ................ TOTAL Result Count = 0

RULECHECK CT_12 ................ TOTAL Result Count = 0

RULECHECK M1_1 ................. TOTAL Result Count = 0

(1)Calibre是一个“Edge-Based”Tool,默认错误的显示是边

(2)DRC 检查的结果有are、Opposite。

(3)常用的几条检查规则,具体可阅读Calibre的手册

(a)Internal(内边对内边)用来检查 Width、Overlap;

RULECHECK M1_6 ................. TOTAL Result Count = 3

RULECHECK M2_1 ................. TOTAL Result Count = 0

RULECHECK M2_2 ................. TOTAL Result Count = 0

Merge if space is less than

NW_2b

0 0 2 Jan 2 20:10:47 2004

Rule File Pathname:

Minimum space between two NW with different potential is

NW_3

……

Rule File Pathname:

RULECHECK PD_M1 ................ TOTAL Result Count = 0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

寄生参数提取-Calibre xRC培训班

(1天)

课程描述:

Mentor Graphics 的Calibre 是深亚微米物理验证的工业标准。

本次课程将教会用户IC设计流程中有效的使用Calibre xRC进行寄生参数提取。

更有相应的练习课程可加深对Calibre xRC概念和技术的理解,增加Calibre xRC的使用经验。

在这次课中可以学到:

●如何编写Calibre xRC所需的文件;

●如何使用Calibre xRC进行寄生参数提取,产生Lumped-C、Distributed

RC和RCC网表等;

●如何分析Calibre xRC的报告和了解提取出来的网表结果等;

●了解Calibre xRC与其他EDA供应商的工具的接口。

适合的听众:

●IC设计工程师和版图工程师;

●需要编写rule files的工程师;

●CAD支持小组。

需要的知识:

●IC版图设计的知识;

●使用Calibre LVS的经验;

●了解电路仿真的基本知识;

●了解SPICE网表;

●熟悉UNIX;

●版图验证概念和工具的知识(非必需)。

附录1:

Calibre xRC for Parasitic Extraction Training Course Schedule

●Morning

⏹Introduce Calibre xRC

⏹Foundational Flow Concepts

⏹Parasitic Elements and Netlists

⏹Transistor-Level Extraction

⏹Lab

●Morning

⏹Gate-Level Extraction

⏹Customizing Output Netlists

⏹Hierarchical Extraction

⏹Lab

⏹Q&A。