ISL6115芯片手册

ZL50112中文资料(Zarlink Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

芯片中文手册,看全文,戳

ZL50110/11/14

数据包处理功能

• 灵活多协议数据包封装包括IPv4,IPv6RTP,MPLS,L2TPv3ITU-T Y.1413,IETF CESoPSN模式,IETF SATOP和用户可编程

• 包重测序,允许丢失数据包检测 • 利用出口队列四大类服务优先级可编程机制(WFQ和SP) • 传入分组层2,3,4灵活分类,和5 • 最多支持通过分组交换网络128单独CESoP连接

• 结构感知TDM电路仿真服务在分组交换网络(CESoPSN模式) - 选秀ietfpwe3-cesopsn

该ZL50110/11/14提供高达三倍100 MbpsMII端口或双冗余1000 MbpsGMII / TBI端口.

所述ZL50110/11/14包含一系列每个TDM流强大时钟恢复机制,允许在源时钟频率,可以忠实在目地产生 ,实现更高系统性能和质量.定时使用RTP或类似协议进行,双方自适应和差分时钟恢复方案包括,允许客户选择 正确方案应用.一个外部提供时钟,也可以用于驱动ZL50110/11/14TDM接口.

设备

ZL50114 ZL50110

ZL50111

TDM接口

4 T1,4 E1或1 J 2流或 4 MVIP / ST-BUS流以2.048 Mbps或 1 H.110 / H-MVIP / ST-BUS流在8.192 Mbps

8 T1,8个E1或2 J2流或 8 MVIP / ST-BUS流以2.048 Mbps或 2 H.110 / H-MVIP / ST-BUS流在8.192 Mbps

2.0物理规格. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

ESDH155ADM用户手册

MCL1005多层芯片感应器技术数据说明书

MCL1005 Multilayer chip inductorProduct features• 0402 (1005 metric) package• High self resonant frequency (SRF)• Multilayer monolithic construction yields high reliability• Suitable for wave and reflow soldering• Inductance range from 1.0 nH to 360 nH • Moisture sensitivity level (MSL): 1Applications• Industrial connectivity (IoT)• Wireless communiations• Bluetooth• WiFi• Antenna• Machine-to-machine (M2M)• Mobile phones• Wearable devices• Wireless LAN• Computing/gaming consoles• Broadband components• RF transciever modulesEnvironmental data• Operating temperature range: -55 °C to +125 °C (ambient plus self-temperature rise)• Solder reflow temperature:J-STD-020 (latest revision) compliantPb HALOGENHFFREE2Technical Data 10925Effective June 2019MCL1005Multilayer chip inductor/electronicsProduct specificationsPart numberOCL (nH) ±5%I Rated(mA) maximumDCR (Ω)maximum @ +25°CSRF(MHz) minimumQ(minimum)Test frequency (MHz)Test voltage (mV)MCL1005-1R0-R 1.0 ±0.3nH 4000.1010000810050MCL1005-1R1-R 1.1 ±0.3nH 4000.1010000810050MCL1005-1R2-R 1.2 ±0.3nH 4000.1010000810050MCL1005-1R3-R 1.3 ±0.3nH 4000.1010000810050MCL1005-1R5-R 1.5 ±0.3nH 3000.106000810050MCL1005-1R6-R 1.6 ±0.3nH 3000.126000810050MCL1005-1R8-R 1.8 ±0.3nH 3000.126000810050MCL1005-2R0-R 2.0 ±0.3nH 3000.156000810050MCL1005-2R2-R 2.2 ±0.3nH 3000.156000810050MCL1005-2R4-R 2.4 ±0.3nH 3000.156000810050MCL1005-2R7-R 2.7 ±0.3nH 3000.156000810050MCL1005-3R0-R 3.0 ±0.3nH 3000.206000810050MCL1005-3R3-R 3.3 ±0.3nH 3000.206000810050MCL1005-3R6-R 3.6 ±0.3nH 3000.204000810050MCL1005-3R9-R 3.9 ±0.3nH 3000.204000810050MCL1005-4R3-R 4.3 ±0.3nH 3000.204000810050MCL1005-4R7-R 4.7 ±0.3nH 3000.254000810050MCL1005-5R1-R 5.1 ±0.3nH 3000.254000810050MCL1005-5R6-R 5.6 ±0.3nH 3000.254000810050MCL1005-6R2-R 6.2 ±0.3nH 3000.303900810050MCL1005-6R8-R 6.8 3000.303900810050MCL1005-7R5-R 7.5 3000.403700810050MCL1005-8R2-R 8.23000.403600810050MCL1005-9R1-R 9.13000.403400810050MCL1005-100-R 103000.403200810050MCL1005-120-R 123000.502700810050MCL1005-150-R 153000.502300810050MCL1005-180-R 183000.602100810050MCL1005-200-R 203000.602000810050MCL1005-220-R 223000.601900810050MCL1005-270-R 273000.701600810050MCL1005-330-R 332000.801300810050MCL1005-390-R 39200 1.001200810050MCL1005-430-R 43200 1.101100810050MCL1005-470-R 47200 1.101000810050MCL1005-560-R 56200 1.20750810050MCL1005-680-R 68180 1.40750810050MCL1005-820-R 82150 2.40750810050MCL1005-101-R1001502.607008100501. Test frequency and voltage are for OCL and Q at +25 °C2. Resistance to soldering heat: +260 ±5 °C for 10 ± 1 second3. At low temperature resistance (-55 ±2°C) the inductance change is within ±10% and the Q within ±20%4. At high temperature resistance (+125 ±2°C) the inductance change is within ±10% and the Q within ±20%5. At high temperature load (+125 ±2°C) the inductance change is within ±10% and the Q within ±20%6. Rated I: When rated I is applied to the product, self-temperature rise will be 40 °C or less.7. Part Number Definition: MCL1005-xxx-R MCL1005 = Product code and sizexxx= inductance value in nH, R= decimal point,If no R is present then last character equals number of zeros -R suffix = RoHS compliant3Technical Data 10925Effective June 2019MCL1005Multilayer chip inductor /electronics No part markingAll soldering surfaces to be coplanar within 0.1 millimeters Tolerances are ±0.2 millimeters unless stated otherwisePad layout tolerances are ±0.1 millimeters unless stated otherwise Do not route traces or vias underneath the inductorDimensions (mm)SchematicProduct specificationsPart numberOCL (nH) ±5%I Rated(mA) maximumDCR (Ω)maximum @ +25°CSRF(MHz) minimumQ(minimum)Test frequency (MHz)Test voltage (mV)MCL1005-121-R 120150 2.80600810050MCL1005-151-R 150100 3.20550810050MCL1005-181-R 180100 3.70500810050MCL1005-221-R 220100 4.00450810050MCL1005-271-R 270100 4.50400810050MCL1005-331-R 330507.0035065050MCL1005-361-R360507.50300650501. Test frequency and voltage are for OCL and Q at +25 °C2. Resistance to soldering heat: +260 ±5 °C for 10 ± 1 second3. At low temperature resistance (-55 ±2°C) the inductance change is within ±10% and the Q within ±20%4. At high temperature resistance (+125 ±2°C) the inductance change is within ±10% and the Q within ±20%5. At high temperature load (+125 ±2°C) the inductance change is within ±10% and the Q within ±20%6. Rated I: When rated I is applied to the product, self-temperature rise will be 40 °C or less.7. Part Number Definition: MCL1005-xxx-R MCL1005 = Product code and sizexxx= inductance value in nH, R= decimal point,If no R is present then last character equals number of zeros -R suffix = RoHS compliantPart Number L W T a A B CMCL1005-xxx-R 1.0 ±0.150.50 ±0.150.50 ±0.150.25 ±0.100.85 ±0.100.8 ±0.100.2 ±0.104MCL1005Multilayer chip inductor/electronicsFrequency MHzQ vs frequency5Technical Data 10925Effective June 2019MCL1005Multilayer chip inductor /electronics Solder reflow profileTable 1 - Standard SnPb solder (T c )Package ThicknessVolume mm3 <350Volume mm3 ≥350<2.5 mm)235 °C 220 °C ≥2.5 mm220 °C220 °CTable 2 - Lead (Pb) free solder (T c )Package thicknessVolume mm 3 <350Volume mm 3350 - 2000Volume mm 3 >2000<1.6 mm 260 °C 260 °C 260 °C 1.6 – 2.5 mm 260 °C 250 °C 245 °C >2.5 mm250 °C245 °C245 °CT e m p e r a t u r eT LT PReference J-STD-020Profile featureStandard SnPb solderLead (Pb) free solderPreheat and soak • Temperature min. (T smin )100 °C 150 °C • Temperature max. (T smax )150 °C 200 °C • Time (T smin to T smax ) (t s )60-120 seconds 60-120 seconds Average ramp up rate T smax to T p 3 °C/ second max. 3 °C/ second max.Liquidous temperature (T l ) Time at liquidous (t L )183 °C60-150 seconds 217 °C60-150 seconds Peak package body temperature (T P )*Table 1Table 2Time (t p )** within 5 °C of the specified classification temperature (T c )10 seconds**10 seconds**Average ramp-down rate (T p to T smax ) 6 °C/ second max. 6 °C/ second max.Time 25 °C to peak temperature6 minutes max.8 minutes max.* Tolerance for peak profile temperature (T p ) is defined as a supplier minimum and a user maximum.** Tolerance for time at peak profile temperature (t p ) is defined as a supplier minimum and a user maximum.EatonElectronics Division 1000 Eaton Boulevard Cleveland, OH 44122United States/electronics © 2019 EatonAll Rights Reserved Printed in USAPublication No. 10925 BU-MC19057June 2019MCL1005Multilayer chip inductorTechnical Data 10925Effective June 2019Life Support Policy: Eaton does not authorize the use of any of its products for use in life support devices or systems without the express writtenapproval of an officer of the Company. Life support systems are devices which support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.Eaton reserves the right, without notice, to change design or construction of any products and to discontinue or limit distribution of any products. Eaton also reserves the right to change or update, without notice, any technical information contained in this bulletin.T e m p e r a t u r eTimeT T T T Wave solder profileReference EN 61760-1:2006Profile featureStandard SnPb solderLead (Pb) free solderPreheat • Temperature min. (T smin )100 °C 100 °C • Temperature typ. (T styp )120 °C 120 °C • Temperature max. (T smax )130 °C 130 °C • Time (T smin to T smax ) (t s )70 seconds 70 seconds D preheat to max Temperature150 °C max.150 °C max.Peak temperature (T P )*235 °C – 260 °C 250 °C – 260 °C Time at peak temperature (t p )10 seconds max5 seconds max each wave 10 seconds max5 seconds max each wave Ramp-down rate~ 2 K/s min ~3.5 K/s typ ~5 K/s max ~ 2 K/s min ~3.5 K/s typ~5 K/s max Time 25 °C to 25 °C4 minutes4 minutesManual solder+350 °C, 4-5 seconds. (by soldering iron), generally manual, hand soldering is not recommended.Eaton is a registered trademark.All other trademarks are property of their respective owners.Follow us on social media to get the latest product and support information.。

ISL85005和ISL85005A演示板用户指南说明书

ISL85005ADEMO1Z ISL85005DEMO1ZISL85005DEMO1Z and ISL85005ADEMO1Z Demonstration Boards User GuideDescriptionThe ISL85005 and ISL85005A are 4.5V to 18V input, 5A synchronous buck regulators for applications with input voltage from multi-cell batteries or regulated 5V and 12Vpower rails. These devices also provide an integrated bootstrap diode for the high-side gate driver to reduce the external parts count. The ISL85005DEMO1Z and ISL85005ADEMO1Zplatforms allow quick demonstration of the high performance features of the ISL85005 and ISL85005A buck regulators.SpecificationsThese boards have been configured and optimized for the following operating conditions: •Input voltage ranges from 7V to 15V •5V nominal output voltage •Up to 5A output current capability•Default internally set 500kHz switching frequency •Default internally set 2.3ms soft-start•Operating temperature range: -40°C to +85°CKey Features•Switch selectable EN (enabled/disabled)•Selectable mode (DEM/Forced CCM) (ISL85005DEMO1Z)•Internal and external compensation options•Frequency synchronization option (ISL85005DEMO1Z)•Adjustable soft-start option (ISL85005ADEMO1Z)•Small and compact designRelated Literature•For a full list of related documents please visit our website -ISL85005 and ISL85005A product pagesOrdering InformationPART NUMBER DESCRIPTIONISL85005DEMO1Z Small form-factor demonstration board for ISL85005FRZISL85005ADEMO1ZSmall form-factor demonstration board for ISL85005AFRZFIGURE 1A.ISL85005DEMO1ZFIGURE 1B.ISL85005ADEMO1ZFIGURE 1.BLOCK DIAGRAMSYNC/PG EN FB COMP BOOT VDD VIN VIN PHASE AGND234151*********PHASE PGNDC 3C 4C 5C 6C 8C 9MODE GND = DEM; VCC = FCCM EN PG MODE V INL 1V OUTISL85005R 2C 1R 1PGENFB COMP BOOT VDD VIN VIN PHASE AGND234151110912867PHASE PGNDC 3C 4C 5C 6C 8C 9EN PG V INL 1V OUTISL85005AR 2C 1R 1SS C SSUser Guide 110User Guide 110Connector and Selection Jumper DescriptionsThe ISL85005DEMO1Z and ISL85005ADEMO1Z demonstration boards include I/O connectors and a selection jumper as shown in Table1.Quick Setup GuideRefer to the following Quick Setup Guide to configure and power-up the board for proper operation.1.Set the power supply voltage to 12V, and turn off the powersupply. Connect the positive output of power supply to J3 (VIN) and the negative output to J4 (GND).2.Connect an electronic load to J5 (VOUT) for the positiveconnection and J6 (GND) for the negative connection.3.Measure the output voltage (J5 and J6) with the voltmeter.4.Place scope probes on VOUT and other test points of interest.5.Set EN jumper (J1) to ON position.6.Set the load current to be 0.1A and turn on the power supply,the output voltage should be in regulation with a nominal 5V output.7.Slowly increase the load up to 5A while monitoring the outputvoltage which should remain in regulation with a nominal 5V output.8.Slowly sweep VIN from 7V to 15V, the output voltage shouldremain in regulation with a nominal 5V output.9.Decrease the input voltage to 0V to shut down the regulator. Operation Mode Selection (ISL85005DEMO1Z)The ISL85005DEMO1Z can be configured in either forced Continuous Conduction Mode (CCM) or Diode Emulation Mode (DEM):•In the default configuration of ISL85005DEMO1Z,SYNC/MODE (Pin 1) of ISL85005 is floating, the ISL85005 operates in forced CCM.•To configure the ISL85005 in DEM, short the SYNC/MODE pin to GND by populating a 0Ω resistor for C SS. DEM enables automatic transition from CCM to DCM and higher efficiency at light-load conditions.Frequency Synchronization (ISL85005DEMO1Z)The ISL85005 can be synchronized to an external clock with frequency ranges from 300kHz to 2MHz by applying the external clock to the SYNC/MODE pin on the ISL85005DEMO1Z demonstration board. The external clock should meet the specifications of the pulse width and voltage level described in the datasheet.Adjusting Soft-Start Time(ISL85005ADEMO1Z)With the SS pin floating, the ISL85005A features an internally set 2.3ms of soft-start time. The soft-start time can be set to a desired value by connecting an external capacitor (C SS on the ISL85005ADEMO1Z demonstration board) between the SS pin and AGND. The capacitance can be calculated by Equation1:Evaluating Other Output VoltagesBoth ISL85005DEMO1Z and ISL85005ADEMO1Z have a nominal 5V output voltage. The output voltages are programmable by an external resistor divider formed by R1 and R2 as shown in Figure1 on page1. R1 is usually chosen first, then the value for R2 can be calculated based on R1 and the desired output voltage using Equation2.PCB Layout ConsiderationsThe PCB layout is critical for proper operation of the ISL85005 and ISL85005A. The following guidelines should be followed to achieve good performance.e a multilayer PCB structure to achieve optimizedperformance, a four-layer PCB is recommended for thisdesign.e a combination of bulk capacitors and smaller ceramiccapacitors with lower ESL for the input capacitors and place them as close to the IC as possible.3.Place the VDD decoupling capacitor close to the IC betweenVDD and GND. A 1µF ceramic capacitor is typically used. 4.Place a bootstrap capacitor close to the IC between the BOOTand PHASE pins. A 0.1µF ceramic capacitor is typically used.5.Connect the feedback resistor divider between the outputcapacitor positive terminal and the AGND pin of the IC, and place the resistors close to the FB pin of the IC.6.Connect the EPAD of the IC to the GND planes underneathusing multiple thermal vias to improve thermal performance.TABLE 1.CONNECTORS AND JUMPERREFERENCEDESIGNATOR DESCRIPTIONJ1Selection Jumper for Enable (EN)J3Input voltage positive connectionJ4Input voltage return connectionJ5Output voltage positive connectionJ6Output voltage return connectionC SS nF[] 3.5t SS ms[] 1.6nF–⋅=(EQ. 1)R2R10.8V⋅V OUT0.8V–----------------------------------=(EQ. 2)User Guide 110 ISL85005xDEMO1Z Demonstration BoardFIGURE 2.TOP VIEW SchematicFIGURE 3.ISL85005xDEMO1Z SCHEMATICUser Guide 110 Bill of MaterialsMANUFACTURER PART NUMBER REFERENCEDESIGNATOR QTY DESCRIPTION MANUFACTURERISL85005FRZ(ISL85005DEMO1Z)U11IC-BUCK REGULATOR W/ SYNC/MODE PIN, 12PIN, DFN, 3x4, ROHS INTERSILISL85005AFRZ(ISL85005ADEMO1Z)1IC-BUCK REGULATOR W/ SS PIN, 12PIN, DFN, 3x4, ROHS INTERSILGRM1555C1H120JA01D C41CAP, SMD, 0402, 12pF, 50V, 5%, NP0, ROHS MURATAC7, C8, C SS0CAP, SMD, 0402, DNP-PLACE HOLDER, ROHSGRM188R71E104KA01D C31CAP, SMD, 0603, 0.1µF, 25V, 10%, X7R, ROHS MURATAGRM188R61E105KA12D C91CAP, SMD, 0603, 1µF, 25V, 10%, X5R, ROHS MURATAC1206X7R250-106KNE C1, C22CAP, SMD, 1206, 10µF, 25V, 10%, X7R, ROHS VENKELCL32A476KOJNNNE C5, C62CAP, SMD, 1210, 47µF, 16V, 10%, X5R, ROHS SAMSUNG744314330L11COIL-PWR INDUCTOR, SMD, 6.9mm2, 3.3µH, 9A 9mΩ, WW, ROHS WURTH ELEKTRONIK 1514-2J3, J4, J5, J64CONN-TURRET, TERMINAL POST, TH, ROHS KEYSTONEERJ2RKF20R0R41RES, SMD, 0402, 20Ω, 1/16W, 1%, TF, ROHS PANASONICCR0402-16W-00T R111RES, SMD, 0402, 0Ω, 1/16W, 5%, TF, ROHS VENKELMCR01MZPF2003R7, R142RES, SMD, 0402, 200k, 1/16W, 1%, TF, ROHS ROHMCR0402-16W-4993FT R11RES, SMD, 0402, 499k, 1/16W, 1%, TF, ROHS VENKELRC0402FR-0795K3L R21RES, SMD, 0402, 95.3k, 1/16W, 1%, TF, ROHS YAGEOR3, R80RES, SMD, 0402, DNP, DNP, DNP, TF, ROHS929950-00Jumper1CONN-JUMPER, SHORTING, 2PIN, BLK, OPEN TOP, 2.54mmPITCH,ROHS3MPEC03SAAN J11 3 Positions Header, 100 mil (2.54mm) spacing, Through Hole Tin Sullins Connector Solutions ISL85005xDEMO1Z PCB1PWB-PCB, ISL85005xDEMO1Z, REVA, ROHS AnyUser Guide 110 ISL85005xDEMO1Z PCB LayoutUser Guide 110Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the document is current before proceeding.For information regarding Intersil Corporation and its products, see Typical Performance CurvesV IN = 12V, V OUT = 5V, L = 3.3µH, f SW = 500kHz, T A = +25°C, unless otherwise noted.FIGURE 9.START-UP WITH EN, I OUT = 5AFIGURE 10.SHUTDOWN WITH EN, I OUT = 5AFIGURE 11.LOAD TRANSIENT, 0A → 2.5A → 0A, 2.5A/µsV OUT (2V/DIV)I L (2A/DIV)EN (10V/DIV)1ms/DIV200µs/DIV V OUT (2V/DIV)EN (10V/DIV)I L (2A/DIV)50µs/DIVV OUT (100mV/DIV),I OUT (1A/DIV)AC COUPLINGISL85005ADEMO1Z ISL85005DEMO1Z。

PMC-6510说明书(V1.3版)(071210)

PMC-6510微机型保护测控装置操作使用说明书(V1.3版)深圳市中电电力技术有限公司2007年12月10日(修订)目录1装置简介 (1)1.1概述 (1)1.2产品特点 (1)1.3基本功能 (1)1.4产品使用 (2)2技术指标 (2)2.1工作环境条件 (2)2.2额定参数 (2)2.3精度及误差 (2)2.4遥信分辨率 (3)2.5过载能力 (3)2.6继电器输出 (3)2.7开关量输入 (3)2.8电气绝缘性能 (3)2.9机械性能 (3)2.10电磁兼容性能 (4)3功能说明 (4)3.1保护功能 (4)3.1.1速断保护 (4)3.1.2复合电压元件 (4)3.1.3限时速断 (5)3.1.4定时限过流 (5)3.1.5反时限过流保护 (5)3.1.6过热保护 (6)3.1.7过负荷保护 (6)3.1.8起动时间过长保护 (6)3.1.9堵转保护 (7)3.1.10充电保护 (7)3.1.11零序过流保护(I、II段) (7)3.1.12负序过流保护 (8)3.1.13过压保护 (8)3.1.14低压保护 (8)3.1.15低周减载 (9)3.1.16电容器差压保护 (9)3.1.17绝缘监视 (9)3.1.18TV断线 (9)3.1.19重要遥信处理 (10)3.2测量监视功能 (10)3.2.1测量 (10)3.2.2遥信功能 (10)3.3控制功能 (11)3.4通讯功能 (11)3.5记录功能 (11)3.5.1事件记录 (11)3.5.2故障录波记录 (11)4操作使用说明 (12)4.1按键操作 (12)4.2信号指示灯 (12)4.3默认显示页面 (12)4.4显示结构 (13)4.5画面详细说明 (13)4.5.1数据查询 (14)4.5.2定值查询 (15)4.5.3事件记录 (16)4.5.4参数设置 (18)4.5.5装置维护 (21)4.5.6装置信息 (22)4.5.7定值清单 (23)5安装调试说明 (26)5.1安装 (26)5.1.1装置安装图 (27)5.1.2背板端子布置 (27)5.1.3端子排总体布置: (27)5.1.4模拟量输入 (28)5.1.5工作电源 (28)5.1.6接地线的连接 (28)5.1.7通信接线 (28)5.2开出继电器的应用 (28)5.3开关量输入的应用 (28)5.4通电试验 (28)5.5模拟试验 (29)5.6装置故障分析 (29)6接线原理图 (31)7售后服务承诺 (32)7.1质量保证 (32)7.2装置升级 (32)7.3质保范围 (32)附录1:手册变更信息 (33)危险和警告本设备只能由专业人士进行安装,对于因不遵守本手册的说明所引起的故障,厂家将不承担任何责任。

AiP1651中文使用手册

江苏省无锡市蠡园经济开发区滴翠路 100 号 9 栋 2 层

http://www.i-core. cn

邮编:214072

第 5 页 共 11 页 版本:2012-01-B1

表 733-11-I

无锡中微爱芯电子有限公司

Wuxi I-CORE Electronics Co., Ltd.

写SRAM 数据地址自动加1 模式:

DIG1

SG1 SG2 SG3 SG4 SG5 SG6 SG7

a

DPY

b

a

cf d

g

b

ee

c

f

d

g [LEDgn]

DIG2

SG1 S1 SG2 S2 SG3 S3 SG4 S4 SG5 S5 SG6 S6 SG7 S7

滤波 电容与 IC的VDD、GND的回 路应尽 量短

VDD

104 + 100uF

SG1 SG2 SG3 SG4 SG5 SG6 SG7

编号:AiP1651-AX-BJ-81

3.3、电气特性 参数名称

符号

测试条件

规范值

单

最小 典型 最大

位

电气特性(Ta = -40~+85℃,VDD = 4.5 ~ 5.5 V,GND = 0 V)

i-core IOL1

低电平输出电流 IOL2

高电平输出电流

低电平输出电流 高电平输出电流 容许量 输出上拉电阻 输入电流

-50 200 400 -40~+85 -65~+150 245 250

3.2、推荐使用条件(Ta=-40~+85℃,VDD=4.5~5.5V,GND=0V)

单位 V V mA mA mW ℃ ℃

ISL6115芯片手册

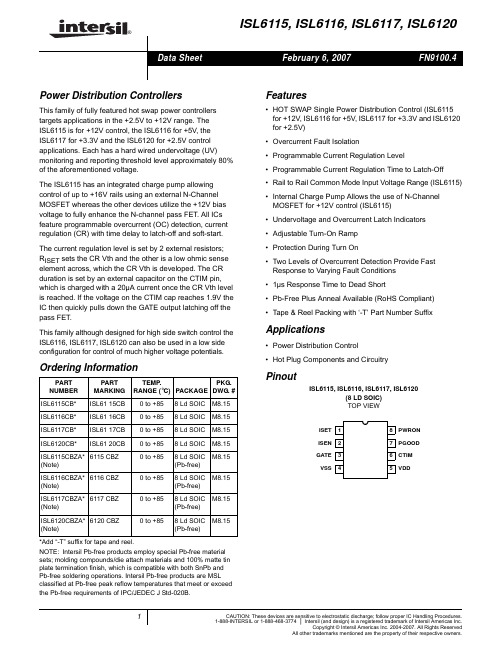

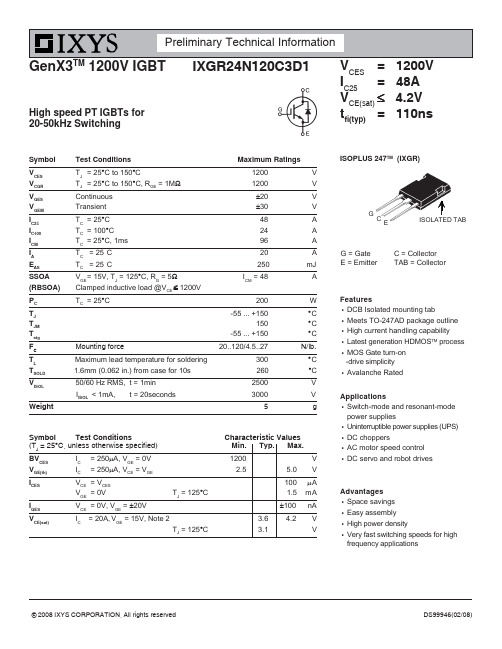

®ISL6115, ISL6116, ISL6117, ISL6120Power Distribution ControllersThis family of fully featured hot swap power controllers targets applications in the +2.5V to +12V range. TheISL6115 is for +12V control, the ISL6116 for +5V, theISL6117 for +3.3V and the ISL6120 for +2.5V control applications. Each has a hard wired undervoltage (UV) monitoring and reporting threshold level approximately 80% of the aforementioned voltage.The ISL6115 has an integrated charge pump allowing control of up to +16V rails using an external N-Channel MOSFET whereas the other devices utilize the +12V bias voltage to fully enhance the N-channel pass FET. All ICs feature programmable overcurrent (OC) detection, current regulation (CR) with time delay to latch-off and soft-start.The current regulation level is set by 2 external resistors;R ISET sets the CR Vth and the other is a low ohmic sense element across, which the CR Vth is developed. The CR duration is set by an external capacitor on the CTIM pin, which is charged with a 20µA current once the CR Vth level is reached. If the voltage on the CTIM cap reaches 1.9V the IC then quickly pulls down the GATE output latching off the pass FET.This family although designed for high side switch control the ISL6116, ISL6117, ISL6120 can also be used in a low side configuration for control of much higher voltage potentials.Features•HOT SWAP Single Power Distribution Control (ISL6115 for +12V, ISL6116 for +5V, ISL6117 for +3.3V and ISL6120 for +2.5V)•Overcurrent Fault Isolation•Programmable Current Regulation Level •Programmable Current Regulation Time to Latch-Off •Rail to Rail Common Mode Input Voltage Range (ISL6115)•Internal Charge Pump Allows the use of N-Channel MOSFET for +12V control (ISL6115)•Undervoltage and Overcurrent Latch Indicators •Adjustable Turn-On Ramp•Protection During Turn On•Two Levels of Overcurrent Detection Provide Fast Response to Varying Fault Conditions•1µs Response Time to Dead Short•Pb-Free Plus Anneal Available (RoHS Compliant)•Tape & Reel Packing with ‘-T’ Part Number Suffix Applications•Power Distribution Control•Hot Plug Components and CircuitryPinoutISL6115, ISL6116, ISL6117, ISL6120(8 LD SOIC)TOP VIEWOrdering InformationPART NUMBERPARTMARKINGTEMP.RANGE (°C)PACKAGEPKG.DWG. #ISL6115CB*ISL61 15CB0 to +858 Ld SOIC M8.15 ISL6116CB*ISL61 16CB0 to +858 Ld SOIC M8.15 ISL6117CB*ISL61 17CB0 to +858 Ld SOIC M8.15 ISL6120CB*ISL61 20CB0 to +858 Ld SOIC M8.15ISL6115CBZA* (Note)6115 CBZ0 to +858 Ld SOIC(Pb-free)M8.15ISL6116CBZA* (Note)6116 CBZ0 to +858 Ld SOIC(Pb-free)M8.15ISL6117CBZA* (Note)6117 CBZ0 to +858 Ld SOIC(Pb-free)M8.15ISL6120CBZA* (Note)6120 CBZ0 to +858 Ld SOIC(Pb-free)M8.15*Add “-T” suffix for tape and reel.NOTE:Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.ISETISENGATEVSS12348765PWRONPGOODCTIMVDDApplication One - High Side ControllerApplication Two - Low Side Controller+12V-+PWRONLOADPGOODOC12348765ISL6115+V supply to be controlledISL6116ISL6117ISL6120LOAD12V REG+VBUSOC12348765PWRONISL6116/7/20Simplified Block Diagram+-I SETI SENGATEV SSV DD CTIMPGOODPWRONCLIMWOCLIMENABLEOC10µAFALLING EDGE DELAY18V+- V REF +- 1.86V12V+-R R SQN QENABLEPOR V DD8VRISING EDGE PULSE+-+-UV18V20µA7.5K+-+-20µAUV DISABLEISL611X Pin DescriptionsPIN #SYMBOL FUNCTIONDESCRIPTION1ISET Current Set Connect to the low side of the current sense resistor through the current limiting set resistor. This pin functions as the current limit programming pin.2ISEN Current SenseConnect to the more positive end of sense resistor to measure the voltage drop across this resistor.3GATEExternal FET Gate Drive PinConnect to the gate of the external N-Channel MOSFET. A capacitor from this node to ground sets the turn-on ramp. At turn-on this capacitor will be charged to V DD +5V (ISL6115) and to V DD (ISL6116, ISL6117, ISL6120) by a 10μA current source.4 VSS Chip Return 5V DD Chip Supply 12V chip supply. This can be either connected directly to the +12V rail supplying the switched load voltage or to a dedicated V SS +12V supply.6CTIMCurrent Limit Timing CapacitorConnect a capacitor from this pin to ground. This capacitor determines the time delaybetween an overcurrent event and chip output shutdown (current limit time-out). The duration of current limit time-out is equal to 93k Ω x C TIM .7 PGOODPower Good IndicatorIndicates that the voltage on the ISEN pin is satisfactory. PGOOD is driven by an open drain N-Channel MOSFET and is pulled low when the output voltage (VISEN) is less than the UV level for the particular IC.8 PWRON Power ONPWRON is used to control and reset the chip. The chip is enabled when PWRON pin is driven high to a maximum of 5V or is left open. After a current limit time out, the chip is reset by a low level signal applied to this pin. This input has 20μA pull up capability.Absolute Maximum Ratings T A = +25°C Thermal InformationV DD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +16V GATE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to V DD+8V ISEN, PGOOD, PWRON, CTIM, ISET. . . . . . . -0.3V to V DD + 0.3V ESD Classification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5kV Operating ConditionsV DD Supply Voltage Range. . . . . . . . . . . . . . . . . . . . . . +12V ±15% Temperature Range (T A) . . . . . . . . . . . . . . . . . . . . . . . 0°C to +85°C Thermal Resistance (Typical, Note 1)θJA (°C/W) SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98 Maximum Junction Temperature (Plastic Package) . . . . . . .+150°C Maximum Storage Temperature Range. . . . . . . . . .-65°C to +150°C Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . .+300°C (SOIC - Lead Tips Only)CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTES:1.θJA is measured with the component mounted on a high effective thermal conductivity test board in free air. (See Tech Brief, #TB379.1 fordetails.)2.All voltages are relative to GND, unless otherwise specified3.G.N.T. Guaranteed by design and characterization but Not Tested.Electrical Specifications V DD = 12V, T A = T J = 0°C to +85°C, Unless Otherwise SpecifiedPARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS CURRENT CONTROLISET Current Source I ISET_ft18.52021.5μA ISET Current Source I ISET_pt T J = +15°C to +55°C192021μA Current Limit Amp Offset Voltage Vio_ft V ISET - V ISEN-606mV Current Limit Amp Offset Voltage Vio_pt V ISET - V ISEN, T J = +15°C to +55°C-202mV GATE DRIVEGATE Response Time To Severe OC pd_woc_amp V GATE to 10.8V-100-ns GATE Response Time to Overcurrent pd_oc_amp V GATE to 10.8V-600-ns GATE Turn-On Current I GATE V GATE to = 6V8.41011.6μA GATE Pull Down Current OC_GATE_I_4V Overcurrent4575-mA GATE Pull Down Current (3)WOC_GATE_I_4V Severe Overcurrent0.50.8-A ISL6115 Undervoltage Threshold12V UV_VTH9.29.610V ISL6115 GATE High Voltage12VG GATE Voltage V DD + 4.5V V DD + 5V-V ISL6116 Undervoltage Threshold5V UV_VTH 4.0 4.35 4.5V ISL6117 Undervoltage Threshold3V UV_VTH 2.4 2.6 2.8V ISL6120 Undervoltage Threshold2V UV_VTH 1.8 1.85 1.9V ISL6116, 17, 20 GATE High Voltage VG GATE Voltage V DD - 1.5V V DD-V BIASV DD Supply Current I VDD-35mAV DD POR Rising Threshold V DD_POR_L2H VDD Low to High7.88.49VV DD POR Falling Threshold V DD_POR_H2L VDD High to Low7.58.18.7VV DD POR Threshold Hysteresis V DD_POR_HYS V DD_POR_L2H - V DD_POR_H2L0.10.30.6V PWRON Pull-Up Voltage PWRN_V PWRON Pin Open 2.7 3.2-V PWRON Rising Threshold PWR_Vth 1.4 1.7 2.0V PWRON Hysteresis PWR_hys130170250mV PWRON Pull-Up Current PWRN_I91725μADescription and OperationThe members of this family are single power supply distribution controllers for generic hot swap applications across the +2.5V to +12V supply range. The ISL6115 is targeted for +12V switching applications whereas theISL6116 is targeted for +5V, the ISL6117 for +3.3V and the ISL6120 for +2.5V applications. Each IC has a hardwired undervoltage (UV) threshold level approximately 17% lower than the stated voltages.These ICs feature a highly accurate programmable overcurrent (OC) detecting comparator, programmablecurrent regulation (CR) with programmable time delay to latch off, and programmable soft-start turn-on ramp all set with a minimum of external passive components. The ICs alsoinclude severe OC protection that immediately shuts down the MOSFET switch should a rapid load current transient such as a near dead short cause the CR Vth to exceed theprogrammed level by 150mV. Additionally, the ICs have a UV indicator and an OC latch indicator. The functionality of the PGOOD feature is enabled once the IC is biased, monitoring and reporting any UV condition on the ISEN pin.Upon initial power up, the IC can either isolate the voltage supply from the load by holding the external N-ChannelMOSFET switch off or apply the supply rail voltage directly to the load for true hot swap capability. The PWRON pin must be pulled low for the device to isolate the power supply from the load by holding the external N-channel MOSFET off. With the PWRON pin held high or floating the IC will be in true hot swap mode. In both cases the IC turns on in a soft-start mode protecting the supply rail from sudden in-rush current.At turn-on, the external gate capacitor of the N-Channel MOSFET is charged with a 10μA current source resulting in a programmable ramp (soft-start turn-on). The internal ISL6115 charge pump supplies the gate drive for the 12V supply switch driving that gate to ~V DD +5V, for the other three ICs the gate drive voltage is limited to the chip bias voltage, VDD.Load current passes through the external current senseresistor. When the voltage across the sense resistor exceeds the user programmed CR voltage threshold value, (see T able 1 for R ISET programming resistor value and resulting nominal current regulation threshold voltage, V CR ) thecontroller enters its current regulation mode. At this time, the time-out capacitor, on C TIM pin is charged with a 20μA current source and the controller enters the current limit time to latch-off period. The length of the current limit time to latch-offduration is set by the value of a single external capacitor (see T able 2) for CTIM capacitor value and resulting nominal current limited time out to latch-off duration placed from the CTIM pin (pin 6) to ground. The programmed current level is held until either the OC event passes or the time out period expires. If the former is the case then the N-Channel MOSFET is fully enhanced and the C TIM capacitor isdischarged. Once CTIM charges to 1.87V, signaling that the time out period has expired an internal latch is set whereby the FET gate is quickly pulled to 0V turning off the N-Channel MOSFET switch, isolating the faulty load.This IC responds to a severe overcurrent load (defined as a voltage across the sense resistor >150mV over the OC Vth set point) by immediately driving the N-Channel MOSFET gate to 0V in about 10μs. The gate voltage is then slowly ramped up turning on the N-Channel MOSFET to the programmed current regulation level; this is the start of the time out period.Upon a UV condition the PGOOD signal will pull low when tied high through a resistor to the logic or VDD supply. This pin is a UV fault indicator. For an OC latch off indication, monitor CTIM, pin 6. This pin will rise rapidly from 1.9V to VDD once the time out period expires.See Figures 12 to 16 for waveforms relevant to text.The IC is reset after an OC latch-off condition by a low level on the PWRON pin and is turned on by the PWRON pin being driven high.CURRENT REGULATION DURATION/POWER GOOD C TIM Charging CurrentC TIM _ichg0V CTIM = 0V162023μA C TIM Fault Pull-Up Current (Note 3)-20-mA Current Limit Time-Out Threshold Voltage C TIM _Vth CTIM Voltage 1.3 1.8 2.3V Power Good Pull Down CurrentPG_IpdV OUT = 0.5V-8-mAElectrical SpecificationsV DD = 12V, T A = T J = 0°C to +85°C, Unless Otherwise Specified (Continued)PARAMETERSYMBOLTEST CONDITIONSMINTYPMAX UNITSTABLE 1.R ISET RESISTORNOMINAL OC VTH10k Ω200mV 4.99k Ω100mV 2.5k Ω50mV 750Ω15mVNOTE:Nominal Vth = R ISET x 20μA.TABLE 2.C TIM CAPACITORNOMINAL CURRENT LIMITED PERIOD0.022μF 2ms 0.047μF 4.4ms 0.1μF9.3msNOTE:Nominal time-out period = C TIM x 93k Ω.Application ConsiderationsDuring the soft-start and the time-out delay duration with the IC in its current limit mode, the V GS of the external N-Channel MOSFET is reduced driving the MOSFET switch into a (linear region) high r DS(ON) state. Strike a balance between the CR limit and the timing requirements to avoid periods when the external N-Channel MOSFET s may be damaged or destroyed due to excessive internal power dissipation. Refer to the MOSFET SOA information in the manufacturer’s data sheet.When driving particularly large capacitive loads a longer soft-start time to prevent current regulation upon charging and a short CR time may offer the best application solution relative to reliability and FET MTF.Physical layout of R SENSE resistor is critical to avoid the possibility of false overcurrent occurrences. Ideally, trace routing between the R SENSE resistors and the IC is as direct and as short as possible with zero current in the sense lines (See Figure 1).Using the ISL6116 as a -48V Low Side Hot Swap Power ControllerTo supply the required V DD , it is necessary to maintain the chip supply 10 to 16V above the -48V bus. This may be accomplished with a suitable regulator between the voltage rail and pin 5 (VDD). By using a regulator, the designer may ignore the bus voltage variations. However, a low-costalternative is to use a Zener diode (See Figure 2 for typical 5A load control); this option is detailed below.Note that in this configuration the PGOOD feature (pin 7) is not operational as the I SEN pin voltage is always < UV threshold.See Figures 17 to 20 for waveforms relevant to -48V and other high voltage applications.Biasing the ISL6116Table 3 gives typical component values for biasing the ISL6116 in a ±48V application. The formulas andcalculations deriving these values are also shown below.When using the ISL6116 to control -48V, a Zener diode may be used to provide the +12V bias to the chip. If a Zener is used then a current limit resistor should also be used. Several items must be taken into account when choosing values for the current limit resistor (R CL ) and Zener Diode (DD1):•The variation of the V BUS (in this case, -48V nominal)•The chip supply current needs for all functional conditions •The power rating of R CL .•The current rating of DD1Formulas1.Sizing R CL :R CL = (V BUS,MIN - 12)/I CHIP 2.Power Rating of R CL :P RCL = I C (V BUS,MAX - 12)3.DD1 Current Rating:I DD1 = (V BUS,MAX - 12)/R CLCORRECTTO ISEN ANDCURRENT SENSE RESISTORINCORRECTFIGURE 1.SENSE RESISTOR PCB LAYOUTR ISETTABLE 3.TYPICAL VALUES FOR A -48V HOT SWAPAPPLICATION SYMBOLPARAMETERR CL 1.58k Ω, 1WDD112V Zener Diode, 50mA Reverse CurrentV BUSLOAD12348765ISL6116PWRONNCFIGURE 2.-48VR CL DD112V1.58k Ω1W0.01µF0.047µF1.47k Ω0.0051%0.001µF2k Ω1%ExampleA typical -48V supply may vary from -36 to -72V. Therefore,V BUS,MAX = -72V V BUS,MIN = -36V I CHIP = 15mA (max)Sizing R CL :R CL = (V BUS,MIN - 12)/I C R CL = (36 - 12)/0.015R CL = 1.6k Ω [Typical Value = 1.58k Ω]Power Rating of R CL :P RCL = I C (V BUS,MAX - 12)P RCL = (0.015)(72 - 12)P RCL = 0.9W [Typical Value = 1W]DD1 Current Rating:I DD1 = (VBUS,MAX - 12)/R CL I DD1 = (72 - 12)/1.58k ΩI DD1 = 38mA [Typical Value = 12V rating, 50mA reverse current]Typical Performance CurvesFIGURE 3.VDD BIAS CURRENTFIGURE 4.ISET SOURCE CURRENTFIGURE 5.C TIM CURRENT SOURCEFIGURE 6.C TIM OC VOLTAGE THRESHOLD4.54.03.53.02.52.020305080100TEMPERATURE (°C)5.0S U P P L Y C U R R E N T (m A )104060709020.2TEMPERATURE (°C)I S E T C U R R E N T µA )20305080100104060709020.019.019.219.419.619.820.5020.3220.0019.66C T I M = 0V , C U R R E N T S O U R C E (µA )TEMPERATURE (°C)20305080100104060709019.5020.1619.82C TIM - 0V1.891.881.871.861.851.83C T I M O C V O L T A G E T H R E S H O LD (V )TEMPERATURE (°C)2030508010010406070901.84FIGURE 7.ISL6115/6116 UV THRESHOLD FIGURE 8.ISL6117/6120 UV THRESHOLDFIGURE 9.GATE CHARGE CURRENT FIGURE 10.GATE DRIVE VOLTAGE, VDD = 12VFIGURE 11.POWER ON RESET VOLTAGE THRESHOLD FIGURE 12.ISL6115 +12V TURN-ONTEMPERATURE (°C)I S L 6115, 12V U V T H R E S H O L D (V )203050801001040607090I S L 6116, 5V U V T H R E S H O L D (V )9.769.749.754.374.354.36ISL6116ISL6115TEMPERATURE (°C)I S L 6117, 3.3V U V T H R E S H O L D (V )203050801001040607090I S L 6120, 2.5V U V T H R E S H O L D (V )2.702.651.8601.8501.855ISL61172.60ISL6120TEMPERATURE (°C)203050801001040607090G A T E C H A R G E C U R R E N T (μA )9.69.79.89.910.010.110.217.20017.18317.16617.15017.13317.10012.0011.9911.9811.9711.9611.9511.94TEMPERATURE (°C)I S L 6116,17,20 G A T E D R I V E (V )I S L 6115, G A T E D R I V E (V )20305080100104060709017.116P O W E R O N R E S E T (V )TEMPERATURE (°C)2030508010010406070908.08.58.18.28.38.4VDD LO TO HIVDD HI TO LO5V/DIV. 0.5A/DIV 1ms/DIVGATE VOUTPWRONIOUTPGOODFIGURE 13.ISL6116 +5V TURN-ON FIGURE 14.ISL6115 ‘LOW’ OVERCURRENT RESPONSEFIGURE 15.ISL6115 ‘HIGH’ OVERCURRENT RESPONSE FIGURE 16.ISL6116 ‘HIGH’ OVERCURRENT RESPONSEFIGURE 17.+50V LOW SIDE SWITCHING CGATE = 100pF FIGURE 18.-50V LOW SIDE SWITCHING CGATE = 1000pF2V/DIV 0.5A/DIV 1ms/DIV GATEVOUTPWRONIOUTPGOOD5V/DIV 0.5A/DIV 1ms/DIVCTIMIOUTPGOODVOUTGATE5V/DIV 0.5A/DIV 1ms/DIVIOUTGATECTIMPGOODVOUT 2V/DIV 0.5A/DIV 1ms/DIVIOUTPGOOD CTIMGATEVOUT5ms/DIVVDRAIN 10V/DIV.+50VPWRON 5V/DIV.0V0VVGATE 5V/DIV.IOUT 1A/DIV.5ms/DIVIOUT 1A/DIV.0V0VVGATE 5V/DIV.EN 5V/DIV.-50VVDRAIN 10V/DIV.ISL6115EVAL1 BoardThe ISL6115EVAL1 is configured as a +12V high side switch controller with the CR level set at ~1.5A. (See Figure 21 for ISL6115EVAL1 schematic and Table 4 for BOM). Bias and load connection points are provided along with test points for each IC pin.With the chip to be biased from the +12V bus beingswitched, through B2, GND B5, the load connected between B3 and B4 and with jumper J1 installed the ISL6115 can be evaluated. PWRON pin pulls high enabling the ISL6115 if not driven low.With R2 = 750Ω the CR Vth is set to 15mV and with the 10m Ω sense resistor the ISL6115EVAL1 has a nominal CR level of 1.5A. The 0.047μF delay time to latch-off capacitors results in a nominal 4.4ms before latch-off of outputs after an OC event.Also included with the ISL6115EVAL1 board are one each of the ISL6116, ISL6117 and ISL6120 for evaluation.ISL6116EVAL1 BoardThe ISL6116EVAL1 is default configured as a negative voltage low side switch controller with a ~2.4A CR level. (See Figure 22 for ISL6116EVAL1 schematic and Table 4 for BOM and component description). This basic configuration is capable of controlling both larger positive or negative potential voltages with minimal changes.Bias and load connection points are provided in addition to test points, TP1-8 for each IC pin. The terminals, J1 and J4 are for the bus voltage and return, respectively, with the more negative potential being connected to J4. With the load between terminals J2 and J3 the board is now configured for evaluation. The device is enabled through LOGIN, TP9 with a TTL signal. ISL6116EVAL1 includes a level shifting circuit with an opto-coupling device for the PWRON input so that standard TTL logic can be translated to the -V reference for chip control.When controlling a positive voltage, PWRON can be accessed at TP8.The ISL6116EVAL1 is provided with a high voltage linear regulator for convenience to provide chip bias from ±24V to ±350V. This can be removed and replaced with the zener & resistor bias scheme as discussed earlier. High voltage regulators and power discrete devices are no longer available from Intersil but can be purchased from other semiconductor manufacturers.Reconfiguring the ISL6116EVAL1 board for a higher CR level can be done by changing the R SENSE and R ISET resistor values as the provided FET is 75A rated. Ifevaluation at >60V, an alternate FET must be chosen with an adequate BV DSS .FIGURE 19.+350V LOW SIDE SWITCHING CGATE = 100pF FIGURE 20.+350V LOW SIDE SWITCHING CGATE = 1000pF2ms/DIV+350V0VIOUT 1A/DIVVDRAIN 50V/DIVVGATE 5V/DIVPWRON 5V/DIV2ms/DIV+350V0VIOUT 1A/DIVPWRON 5V/DIVVGATE 5V/DIV.VDRAIN 50V/DIVFIGURE 21.ISL6115EVAL1 HIGH SIDE SWITCH APPLICATIONFIGURE 22.ISL6116EVAL1 NEGATIVE VOLTAGE LOW SIDECONTROLLER56874321ISL6115Q1R2R3C1C2R4D1R5D2JP1V BIAS V+ B2DD1+12VC3R1LOAD -+PWRON 3.3VB1B5B3B4U156874321ISL6116Q2R2R7C1R5D2C3R1LOADDD13.3V+VBUS-VBUSOT1R9R8HI J2J3 LOR6R11R10ONOFF 0-5VU1J1J4PWRONTP8LOGIN TP9R G 1TABLE 4.BILL OF MATERIALS, ISL6115EVAL1, ISL6116EVAL1COMPONENT DESIGNATORCOMPONENT NAMECOMPONENT DESCRIPTIONQ1HUF76132SK811.5m Ω, 30V, 11.5A Logic Level N-Channel Power MOSFET or equiv.Q2HUF7554S3S10m Ω, 80V, 75A N-Channel Power MOSFET or equiv.R1Load Current Sense ResistorDale, WSL-2512 10m Ω 1W Metal Strip ResistorHigh Side R2Overcurrent Voltage Threshold Set Resistor 750Ω 805 Chip Resistor (Vth = 15mV)Low side R2Overcurrent Voltage Threshold Set Resistor 1.21k Ω 805 Chip Resistor (Vth = 24mV)C2Time Delay Set Capacitor 0.047μF 805 Chip Capacitor (4.5ms)C1Gate Timing Capacitor 0.001μF 805 Chip Capacitor (<2ms)C3IC Decoupling Capacitor 0.1μF 805 Chip Capacitor R3Gate Stability Resistor 20Ω 805 Chip Resistor R7Gate to Drain Resistor 2k Ω 805 Chip ResistorJP1Bias Voltage Selection Jumper Install if switched rail voltage is = +12V ±15%. Remove and provide separate +12V bias voltage to U1 via TP5 if ISL6116, ISL6117, ISL6120 being evaluated.R4, R5LED Series Resistors 2.32k Ω 805 Chip Resistor D1, D2Fault Indicating LEDs Low Current Red SMD LEDDD1Fault Voltage Dropping Diode 3.3V Zener Diode, SOT-23 SMD 350mW OT1PWRON Level Shifting Opto-Coupler PS2801-1 NECR8Level Shifting Bias Resistor 2.32k Ω 805 Chip Resistor R9Level Shifting Bias Resistor 1.18k Ω 805 Chip Resistor R10Level Shifting Bias Resistor 200Ω 805 Chip Resistor RG1HIP5600ISHigh Voltage Linear Regulator R6Linear Regulator RF1 1.78k Ω 805 Chip Resistor R11Linear Regulator RF215k Ω 805 Chip ResistorTP1-TP8Test Points for Device Pin Numbers 1-8All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.Intersil Corporation’s quality certifications can be viewed at /design/qualityIntersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.For information regarding Intersil Corporation and its products, see Small Outline Plastic Packages (SOIC)NOTES:1.Symbols are defined in the “MO Series Symbol List” in Section2.2 of Publication Number 95.2.Dimensioning and tolerancing per ANSI Y14.5M -1982.3.Dimension “D” does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006inch) per side.4.Dimension “E” does not include interlead flash or protrusions. Inter-lead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.5.The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.6.“L” is the length of terminal for soldering to a substrate.7.“N” is the number of terminal positions.8.Terminal numbers are shown for reference only.9.The lead width “B”, as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).10.Controlling dimension:MILLIMETER. Converted inch dimensionsare not necessarily exact.M8.15 (JEDEC MS-012-AA ISSUE C)8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGESYMBOLINCHESMILLIMETERS NOTESMIN MAX MIN MAX A0.05320.0688 1.35 1.75-A10.00400.00980.100.25-B 0.0130.0200.330.519C 0.00750.00980.190.25-D 0.18900.1968 4.80 5.003E 0.14970.1574 3.80 4.004e 0.050 BSC 1.27 BSC-H0.22840.2440 5.80 6.20-h 0.00990.01960.250.505L 0.0160.0500.401.276N887a0°8°0°8°-Rev. 1 6/05。

L series IPM 应用手册

第5代IPM应用手册Part 2第5代IPM应用手册L系列L系列智能功率模块 系列智能功率模块 应用和设计手册61第5代IPM应用手册1. L系列IPM的 概 念1.1 IPM的优点IPM自从三菱电机最初开发和量产以来,其有用性已经得到广泛认可并占据了功率器件的一个分支。

越来越多 的制造商开发了同样概念的产品。

本应用手册介绍的L系列IPM具有如下优点。

L系列IPM通过采用低功耗IGBT减少了噪声的产生,实现了高性能和环保的两者兼顾。

另外,由于同系列IPM 600V/1200V产品封装相同,从而也有助于实现装置的小型化。

TM 由于采用CSTBT ,实现了低功耗。

影响噪声产生的输出电流在小电流范围内时放慢开关速度,以此降低IPM 放射噪声。

因此不需要噪声滤波器,使得装置的小型化和高性能化成为可能。

小型・新封装◆ ◆ ◆ 50~150A/600V, 25~75A/1200V的模块开发了新的小型封装。

~75A的模块,除了主端子是螺丝型的模 块外,还有一部分节省空间的针型引脚的模块产品线。

450~600A/600V, 200~450A/1200V容量级的模块第一次开发出内含6单元IGBT的小型封装。

200~300A/600V, 100~150A/1200V在开发了新封装的同时,也实现了与原来的S-DASH系列的兼容。

低功耗◆ 采用了第5代1μm IGBT硅片(CSTBT ),降低了功耗,可以减小了散热器的体积。

TM缩短了项目开发周期◆ 内置IGBT的栅极驱动电路。

控制电源只需+15V(不需要反向偏压电源),简化了周边电路的设计。

实现了控制电路CMOS化,降低了控制电路的电力功耗。

内置故障检测和保护电路(短路过电流、过温、控制电源欠压)。

这样就减少了原来的设计 >> 试制 >> 评价 >> 再设计的多次循环工作。

◆不需要防静电措施◆ 和双极性TTL一样使用,不需要另外针对IGBT模块的措施。

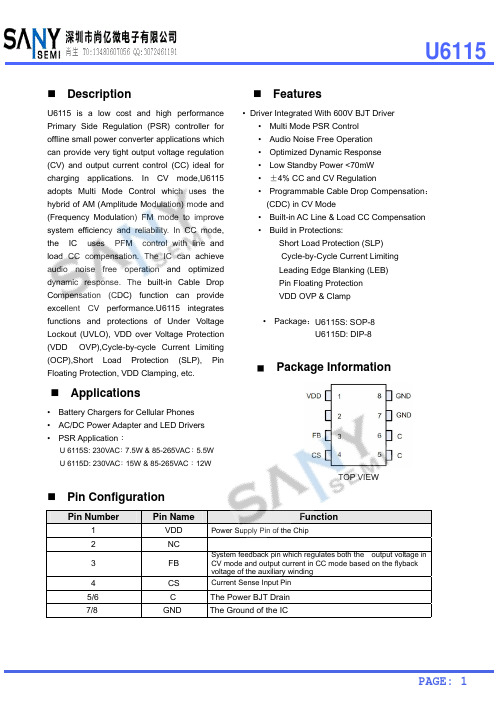

U6115PDF内置三极管5W开关电源

PAGE: 3

U6115

Short Load Protection (SLP) Threshold Short Load Protection (SLP) Debounce Time

Demagnetization Comparator Threshold Minimum OFF time Maximum OFF time Maximum Cable Drop compensation current

Value

7-24 -40 to 85 -65 to 150 70 35

Unit

V ºC ºC kHz KHz

Electrical Characteristics (TA = 25°C, VDD=20V, if not otherwise noted)

Parameter Supply Voltage Section(VDD Pin) Start-up current into VDD pin Operation Current Standby Current

VFB_SLP TFB_SHORT VFB_DEM T Off_min T Off_max ICable_max

(Note 3)

0.6

v

ms

10

25 2 5 60

mV us ms uA

Current Sense Input Section (CS Pin)

CS Input Leading Edge Blanking Time Current limiting threshold Over Current Detection and Control Delay

Features

• Driver Integrated With 600V BJT Driver • Multi Mode PSR Control • Audio Noise Free Operation • Optimized Dynamic Response • Low Standby Power <70mW • ±4% CC and CV Regulation • Programmable Cable Drop Compensation: (CDC) in CV Mode • Built-in AC Line & Load CC Compensation • Build in Protections: Short Load Protection (SLP) Cycle-by-Cycle Current Limiting Leading Edge Blanking (LEB) Pin Floating Protection VDD OVP & Clamp

瑞萨电子ISL2110、ISL2111 100V、3A 4A Peak高频半桥驱动器说明书

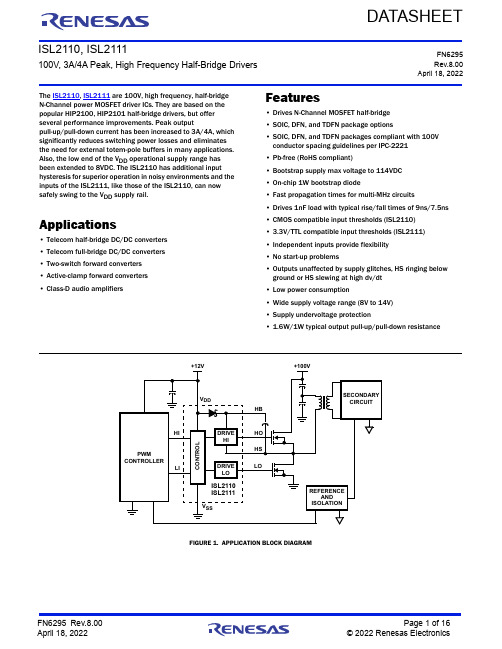

FN6295Rev.8.00April 18, 2022ISL2110, ISL2111100V, 3A/4A Peak, High Frequency Half-Bridge DriversDATASHEETThe ISL2110, ISL2111 are 100V, high frequency, half-bridge N-Channel power MOSFET driver ICs. They are based on the popular HIP2100, HIP2101 half-bridge drivers, but offer several performance improvements. Peak outputpull-up/pull-down current has been increased to 3A/4A, which significantly reduces switching power losses and eliminates the need for external totem-pole buffers in many applications. Also, the low end of the V DD operational supply range has been extended to 8VDC. The ISL2110 has additional input hysteresis for superior operation in noisy environments and the inputs of the ISL2111, like those of the ISL2110, can now safely swing to the V DD supply rail.Applications•Telecom half-bridge DC/DC converters •Telecom full-bridge DC/DC converters •Two-switch forward converters •Active-clamp forward converters •Class-D audio amplifiersFeatures•Drives N-Channel MOSFET half-bridge •SOIC, DFN, and TDFN package options•SOIC, DFN, and TDFN packages compliant with 100V conductor spacing guidelines per IPC-2221•Pb-free (RoHS compliant)•Bootstrap supply max voltage to 114VDC •On-chip 1W bootstrap diode•Fast propagation times for multi-MHz circuits•Drives 1nF load with typical rise/fall times of 9ns/7.5ns •CMOS compatible input thresholds (ISL2110)•3.3V/TTL compatible input thresholds (ISL2111)•Independent inputs provide flexibility •No start-up problems•Outputs unaffected by supply glitches, HS ringing below ground or HS slewing at high dv/dt •Low power consumption•Wide supply voltage range (8V to 14V)•Supply undervoltage protection•1.6W/1W typical output pull-up/pull-down resistanceFIGURE 1.APPLICATION BLOCK DIAGRAMSECONDARY CIRCUIT+100VC O N T R O LCONTROLLERPWMLIHIHO LOV DDHSHB+12V V SSREFERENCEAND ISOLATIONDRIVE LODRIVE HIISL2110ISL2111Functional Block DiagramFIGURE 2.FUNCTIONAL BLOCK DIAGRAMUNDER VOLTAGEV DDHILI V SSDRIVERDRIVERHBHOHSLOLEVEL SHIFTUNDER VOLTAGEEPAD (DFN Package Only)ISL2111ISL2111*EPAD = Exposed Pad. The EPAD is electrically isolated from all other pins. For best thermal performance, connect the EPAD to the PCB power ground plane.Application DiagramsSECONDARY ISOLATIONPWM+48V+12VCIRCUITFIGURE 3.TWO-SWITCH FORWARD CONVERTERISL2110ISL2111SECONDARY CIRCUITISOLATIONPWM+48V+12VFIGURE 4.FORWARD CONVERTER WITH AN ACTIVE-CLAMPISL2110ISL2111Ordering InformationPART NUMBER (Notes2, 3)PARTMARKINGPACKAGE DESCRIPTION(RoHS COMPLIANT)PKG.DWG. #CARRIER TYPE(Notes1)TEMP RANGEISL2110ABZ 2110ABZ 8 Ld SOIC M8.15Tube-40 to +125°CISL2110ABZ -T Reel, 2.5kISL2110AR4Z2110AR4Z 12 Ld 4x4 DFN L12.4x4A TubeISL2110AR4Z-T Reel, 6kISL2111ABZ2111ABZ 8 Ld SOIC M8.15TubeISL2111ABZ-T Reel, 2.5kISL2111AR4Z2111AR4Z 12 Ld 4x4 DFN L12.4x4A TubeISL2111AR4Z-T Reel, 6kISL2111ARTZ2111ARTZ 10 Ld 4x4 TDFN L10.4x4TubeISL2111ARTZ-T Reel, 6kISL2111BR4Z2111BR4Z 8 Ld 4x4 DFN L8.4x4TubeISL2111BR4Z-T Reel, 6kNOTES:1.See TB347 for details about reel specifications.2.These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plateplus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.3.For Moisture Sensitivity Level (MSL), please see device information page for ISL2110, ISL2111. For more information on MSL, see TB363.Pin ConfigurationsISL2111ARTZ (10 LD 4x4 TDFN)TOP VIEW ISL2110AR4Z, ISL2111AR4Z(12 LD 4x4 DFN)TOP VIEW2 3 4 1 59 8 7 10 6VDD HB HO HS NC LOVSSLIHINCVDDNCNCHBHOLOVSSNCNCLIHS HI234151110912867EPAD**EPAD = EXPOSED PADISL2110ABZ, ISL2111ABZ(8 LD SOIC)TOP VIEWISL2111BR4Z (8 LD 4x4 DFN)TOP VIEWPin Configurations56874321VDD HB HO HSLO LI HIVSS 23417658VDD HB HO HSLO VSS LI HIEPAD**EPAD = EXPOSED PADPin DescriptionsSYMBOL DESCRIPTIONVDD Positive supply to lower gate driver. Bypass this pin to VSS.HB High-side bootstrap supply. External bootstrap capacitor is required. Connect positive side of bootstrap capacitor to this pin. Bootstrap diode is on-chip.HO High-side output. Connect to gate of high-side power MOSFET.HS High-side source connection. Connect to source of high-side power MOSFET. Connect negative side of bootstrap capacitor to this pin. HI High-side input LI Low-side inputVSS Chip negative supply, which will generally be ground.LO Low-side output. Connect to gate of low-side power MOSFET.NC No connectEPADExposed pad. Connect to ground or float. The EPAD is electrically isolated from all other pins.Absolute Maximum Ratings Thermal InformationSupply Voltage, V DD, V HB - V HS (Notes4, 5) . . . . . . . . . . . . . . . 0.3V to 18V LI and HI Voltages (Note5) . . . . . . . . . . . . . . . . . . . . . . .-0.3V to V DD + 0.3V Voltage on LO (Note5). . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to V DD + 0.3V Voltage on HO relative to HS (Repetitive Transient < 100ns). . . . . . . . .-2V Voltage on LO relative to GND (Repetitive Transient < 100ns). . . . . . . .-2V Voltage on HO (Note5) . . . . . . . . . . . . . . . . . . . . . .V HS - 0.3V to V HB + 0.3V Voltage on HS (Continuous) (Note5). . . . . . . . . . . . . . . . . . . . . -1V to 110V Voltage on HB (Note5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118V Average Current in V DD to HB Diode . . . . . . . . . . . . . . . . . . . . . . . . . 100mA Maximum Recommended Operating ConditionsSupply Voltage, V DD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8V to 14V Voltage on HS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1V to 100V Voltage on HS . . . . . . . . . . . . . (Repetitive Transient < 100ns) -5V to 105V Voltage on HB . . . . . . . . . . .V HS+7V to V HS+14V and V DD - 1V to V DD+100V HS Slew Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .<50V/ns Thermal Resistance (Typical)θJA (°C/W)θJC (°C/W) 8 Ld SOIC (Notes6, 9) . . . . . . . . . . . . . . . . . 954610 Ld TDFN (Notes7, 8) . . . . . . . . . . . . . . . 40 2.512 Ld DFN (Notes7, 8) . . . . . . . . . . . . . . . . 39 2.58 Ld DFN (Notes7, 8). . . . . . . . . . . . . . . . . . 40 4.0 Max Power Dissipation at +25°C in Free Air8 Ld SOIC (Notes6, 9). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.3W 10 Ld TDFN (Notes7, 8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.0W 12 Ld DFN (Notes7, 8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.1W 8 Ld DFN (Notes7, 8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.1W Storage Temperature Range. . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C Junction Temperature Range . . . . . . . . . . . . . . . . . . . . . . .-55°C to +150°C Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see TB493CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.NOTES:4.The ISL2110 and ISL2111 are capable of derated operation at supply voltages exceeding 14V. Figure 24 shows the high-side voltage derating curvefor this mode of operation.5.All voltages referenced to V SS unless otherwise specified.6.θJA is measured with the component mounted on a high-effective thermal conductivity test board in free air. See Tech Brief TB379 for details.7.θJA is measured in free air with the component mounted on a high-effective thermal conductivity test board with “direct attach” features. See TechBrief TB379.8.For θJC, the “case temp” location is the center of the exposed metal pad on the package underside.9.For θJC, the “case temp” location is taken at the package top center.Electrical Specifications V DD = V HB = 12V, V SS = V HS = 0V, no load on LO or HO, unless otherwise specified.PARAMETERS SYMBOL TEST CONDITIONST J = +25°C T J = -40°C to +125°CUNIT MIN(Note10)TYPMAX(Note10)MIN(Note10)MAX(Note10)SUPPLY CURRENTSV DD Quiescent Current I DD ISL2110; LI = HI = 0V- 0.100.25-0.30mA V DD Quiescent Current I DD ISL2111; LI = HI = 0V- 0.300.45-0.55mA V DD Operating Current I DDO ISL2110; f = 500kHz- 3.4 5.0- 5.5mA V DD Operating Current I DDO ISL2111; f = 500kHz- 3.5 5.0- 5.5mA Total HB Quiescent Current I HB LI = HI = 0V-0.100.15-0.20mA Total HB Operating Current I HBO f = 500kHz- 3.4 5.0- 5.5mA HB to V SS Current, Quiescent I HBS LI = HI = 0V; V HB = V HS = 114V-0.05 1.50-10µA HB to V SS Current, Operating I HBSO f = 500kHz; V HB = V HS = 114V- 1.2---mA INPUT PINSLow Level Input Voltage Threshold V IL ISL2110 3.7 4.4- 3.5-V Low Level Input Voltage Threshold V IL ISL2111 1.4 1.8- 1.2-V High Level Input Voltage Threshold V IH ISL2110- 6.67.4-7.6V High Level Input Voltage Threshold V IH ISL2111- 1.8 2.2- 2.4V Input Voltage Hysteresis V IHYS ISL2110- 2.2---VInput Pull-Down Resistance R I-210-100500k ΩUNDERVOLTAGE PROTECTION V DD Rising Threshold V DDR 6.1 6.67.1 5.87.4V V DD Threshold Hysteresis V DDH -0.6---V HB Rising Threshold V HBR 5.5 6.1 6.8 5.07.1V HB Threshold Hysteresis V HBH-0.6---VBOOTSTRAP DIODELow Current Forward Voltage V DL I VDD-HB = 100µA -0.50.6-0.7V High Current Forward Voltage V DH I VDD-HB = 100mA -0.70.9-1V Dynamic Resistance R DI VDD-HB = 100mA-0.71-1.5ΩLO GATE DRIVER Low Level Output Voltage V OLL I LO = 100mA-0.10.18-0.25V High Level Output Voltage V OHL I LO = -100mA, V OHL = V DD - V LO -0.160.23-0.3V Peak Pull-Up Current I OHL V LO = 0V -3---A Peak Pull-Down Current I OLLV LO = 12V-4---AHO GATE DRIVER Low Level Output Voltage V OLH I HO = 100mA-0.10.18-0.25V High Level Output Voltage V OHH I HO = -100mA, V OHH = V HB - V HO -0.160.23-0.3V Peak Pull-Up Current I OHH V HO = 0V -3---A Peak Pull-Down CurrentI OLHV HO = 12V-4---AElectrical SpecificationsV DD = V HB = 12V, V SS = V HS = 0V, no load on LO or HO, unless otherwise specified. (Continued)PARAMETERSSYMBOL TEST CONDITIONST J = +25°CT J = -40°C to +125°CUNIT MIN (Note 10)TYP MAX (Note 10)MIN (Note 10)MAX (Note 10)Switching SpecificationsV DD = V HB = 12V, V SS = V HS = 0V, No Load on LO or HO, unless otherwise specified.PARAMETERSSYMBOL TESTCONDITIONS T J = +25°CT J = -40°C to +125°C UNIT MIN (Note 10)TYP MAX (Note 10)MIN (Note 10)MAX (Note 10)Lower Turn-Off Propagation Delay (LI Falling to LO Falling)t LPHL -3250-60ns Upper Turn-Off Propagation Delay (HI Falling to HO Falling)t HPHL -3250-60ns Lower Turn-On Propagation Delay (LI Rising to LO Rising)t LPLH -3950-60ns Upper Turn-On Propagation Delay (HI Rising to HO Rising)t HPLH -3850-60ns Delay Matching: Upper Turn-Off to Lower Turn-On t MON 18--16ns Delay Matching: Lower Turn-Off to Upper Turn-On t MOFF 16--16ns Either Output Rise Time (10% to 90%)t RC C L = 1nF -9---ns Either Output Fall Time (90% to 10%)t FC C L = 1nF -7.5---ns Either Output Rise Time (3V to 9V)t R C L = 0.1µF -0.30.4-0.5µs Either Output Fall Time (9V to 3V)t F C L = 0.1µF-0.190.3-0.4µs Minimum Input Pulse Width that Changes the Output t PW ----50ns Bootstrap Diode Turn-On or Turn-Off Timet BS-10---nsNOTE:10.Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterizationand are not production tested.Timing DiagramsFIGURE 5.PROPAGATION DELAYSFIGURE 6.DELAY MATCHINGt HPLH ,t LPLHt HPHL ,t LPHLHI , LIHO , LOt MONt MOFFLIHILOHOTypical Performance CurvesFIGURE 7.ISL2110 I DD OPERATING CURRENT vs FREQUENCY FIGURE 8.ISL2111 I DD OPERATING CURRENT vs FREQUENCYFIGURE 9.I HB OPERATING CURRENT vs FREQUENCYFIGURE 10.I HBS OPERATING CURRENT vs FREQUENCYFIGURE 11.HIGH LEVEL OUTPUT VOLTAGE vs TEMPERATURE FIGURE 12.LOW LEVEL OUTPUT VOLTAGE vs TEMPERATURE0.11.010.0FREQUENCY (Hz)I D D O (m A )T = +25°CT = -40°CT = +125°CT = +150°C10k100k1.103k10k100k1.103k0.11.010.0FREQUENCY (Hz)I D D O (m A )T = +25°CT = -40°CT = +150°CT = +125°CFREQUENCY (Hz)I H B O (m A )0.011.010.0T = +25°CT = -40°CT = +125°CT = +150°C10k100k1.103k0.1FREQUENCY (Hz)I H B S O (m A )0.011.010.0T = -40°CT = +125°CT = +150°C10k100k1.103k0.1T = +25°C-505010015050100150200250300TEMPERATURE (°C)V O H L , V O H H (m V )V DD = V HB = 12VV DD = V HB = 14VV DD = V HB = 8V-505010015050100150200V O L L , V O L H (m V )TEMPERATURE (°C)V DD = V HB = 12VV DD = V HB = 14VV DD = V HB = 8VFIGURE 13.UNDERVOLTAGE LOCKOUT THRESHOLD vsTEMPERATUREFIGURE 14.UNDERVOLTAGE LOCKOUT HYSTERESIS vsTEMPERATUREFIGURE 15.ISL2110 PROPAGATION DELAYS vs TEMPERATURE FIGURE 16.ISL2111 PROPAGATION DELAYS vs TEMPERATUREFIGURE 17.ISL2110 DELAY MATCHING vs TEMPERATURE FIGURE 18.ISL2111 DELAY MATCHING vs TEMPERATURETypical Performance Curves (Continued)V D D R , V H B R (V )-50501001506.7TEMPERATURE (°C)V HBRV DDR6.56.36.15.95.75.55.3V D D H , V H B H (V )-50501001500.70TEMPERATURE (°C)V HBHV DDH0.650.600.550.500.450.4025303540455055t L P L H , t L P H L , t H P L H , t H P H L (n s )-5050100150TEMPERATURE (°C)t LPHLt HPHLt LPLHt HPLH25303540455055t L P L H , t L P H L , t H P L H , t H P H L (n s )-5050100150TEMPERATURE (°C)t LPHLt HPHLt LPLHt HPLH4.04.55.05.56.06.57.07.58.0t M O N , t M O F F (n s )-5050100150TEMPERATURE (°C)t MOFFt MON4.04.55.05.56.06.57.07.58.08.59.09.510.0t M O N , t M O F F (n s )-50050100150TEMPERATURE (°C)t MOFFt MONFIGURE 19.PEAK PULL-UP CURRENT vs OUTPUT VOLTAGE FIGURE 20.PEAK PULL-DOWN CURRENT vs OUTPUT VOLTAGEFIGURE 21.ISL2110 QUIESCENT CURRENT vs VOLTAGE FIGURE 22.ISL2111 QUIESCENT CURRENT vs VOLTAGEFIGURE 23.BOOTSTRAP DIODE I-V CHARACTERISTICSFIGURE 24.V HS VOLTAGE vs V DD VOLTAGETypical Performance Curves (Continued)48101200.51.01.52.02.53.03.5V LO , V HO (V)I O H L , I O H H (A )2648101201.52.02.53.03.54.04.5V LO , V HO (V)I O H L , I O H H (A )261.00.505101520102030405060708090100110120V DD , V HB (V)I D D , I H B (µA )I HBI DD05101520V DD , V HB (V)I D D , I H B (µA )20406080100120140160180200220240260280300320I HBI DD0.30.40.50.60.70.81.10-30.010.101.00FORWARD VOLTAGE (V)F O R W A R D C U R R E N T (A )1.10-41.10-51.10-61213141516020406080100120V H S T O V S S V O L T A G E (V )V DD TO V SS VOLTA GE (V)Revision History The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.DATE REVISION CHANGEApril 18, 2022FN6295.8Updated the Ordering information table to comply with the new standard, updated notes.In Absolute Maximum Ratings, added Voltage on HO relative to HS and Voltage on LO relative to GND.Updated POD M8.15 to the latest version: “Added the coplanarity spec into the drawing.”Removed Related Literature and About Intersil sections.Mar 16, 2017FN6295.7Corrected the branding of FG ISL2111BR4Z in the order information table from "211 1BR4A" to "2111BR4Z".Added Revision History table and About Intersil information.Updated L10.4x4 Package Outline Drawing from Rev 1 to Rev 2. Change since Rev 1 is:“Tiebar note update from ‘Tiebar shown (if present) is a non-functional feature’ to ‘Tiebar shown (ifpresent) is a non-functional feature and may be located on any of the 4 sides (or ends)’”.Updated L12.4x4A Package Outline Drawing from Rev 1 to Rev 3. Changes since Rev 1 are:“Tiebar note update from ‘Tiebar shown (if present) is a non-functional feature’ to ‘Tiebar shown (ifpresent) is a non-functional feature and may be located on any of the 4 sides (or ends)’”;“Bottom View changed from ‘3.2 REF’ TO ‘2.5 REF’";“Typical Recommended Land Pattern changed from ‘3.80’ to ‘3.75’";“Updated to new POD format by removing table listing dimensions and moving dimensions onto drawing”,and “Added typical recommended land pattern”.Updated M8.15 Package Outline Drawing from Rev 3 to Rev 4. Change since Rev 3 is:“Changed Note 1 from 1982 to 1994“.Updated L8.4x4 Package Outline Drawing from Rev 0 to Rev 1. Change since Rev 0 is:“Tiebar note update from ‘Tiebar shown (if present) is a non-functional feature’ to ‘Tiebar shown (ifpresent) is a non-functional feature and may be located on any of the 4 sides (or ends)’”.10 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 2, 4/15TYPICAL RECOMMENDED LAND PATTERNDETAIL "X"SIDE VIEWTOP VIEWBOTTOM VIEWlocated within the zone indicated. The pin #1 identifier may be Unless otherwise specified, tolerance : Decimal ± 0.05The configuration of the pin #1 identifier is optional, but must be between 0.15mm and 0.30mm from the terminal tip.Dimension b applies to the metallized terminal and is measured Dimensions in ( ) for Reference Only.Dimensioning and tolerancing conform to AMSE Y14.5m-1994.6.either a mold or mark feature.3.5.4.2.Dimensions are in millimeters.1.NOTES:4.00 2.600.15(3.80)(4X)(10X 0.30)(8X 0.8)0 .75BASE PLANE CSEATING PLANE0.08C0.10C10 X 0.30SEE DETAIL "X"0.104C A M B INDEX AREA6PIN 14.00ABPIN #1 INDEX AREABSC3.2REF8X 0.806(10 X 0.60)0 . 00 MIN.0 . 05 MAX.C0 . 2 REF10X 0 . 403.00(2.60)( 3.00 )0.05M C 65101Tiebar shown (if present) is a non-functional feature and may be located on any of the 4 sides (or ends).12 LEAD DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 3, 3/15TYPICAL RECOMMENDED LAND PATTERNDETAIL "X"SIDE VIEWTOP VIEWBOTTOM VIEWlocated within the zone indicated. The pin #1 identifier may be Unless otherwise specified, tolerance : Decimal ± 0.05The configuration of the pin #1 identifier is optional, but must be between 0.15mm and 0.30mm from the terminal tip.Lead width applies to the metallized terminal and is measured Dimensions in ( ) for Reference Only.Dimensioning and tolerancing conform to AMSE Y14.5m-1994.6.either a mold or mark feature.3.5.4.2.Dimensions are in millimeters.1.NOTES:4.00 1.580.15( 3.75)(4X)( 12X 0 . 25)( 10X 0 . 5 )1.00 MAXBASE PLANE CSEATING PLANE0.08C0.10C12 X 0.25SEE DETAIL "X"0.104C A M B INDEX AREA6PIN 14.00ABPIN #1 INDEX AREA2.5REF10X 0.50 BSC6( 12 X 0.65 )0 . 00 MIN.0 . 05 MAX.C0 . 2 REF12X 0 . 452.80( 1.58)( 2.80 )0.05M C 76121Tiebar shown (if present) is a non-functional feature and may be located on any of the 4 sides (or ends).8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE8 LEAD DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 1, 03/15TYPICAL RECOMMENDED LAND PATTERNDETAIL "X"SIDE VIEWTOP VIEWBOTTOM VIEWlocated within the zone indicated. The pin #1 identifier may be Unless otherwise specified, tolerance : Decimal ± 0.05The configuration of the pin #1 identifier is optional, but must be between 0.15mm and 0.30mm from the terminal tip.Dimension applies to the metallized terminal and is measured Dimensions in ( ) for Reference Only.Dimensioning and tolerancing conform to ASME Y14.5m-1994.6.either a mold or mark feature.3.5.4.2.Dimensions are in millimeters.1.NOTES:4.00 2.50 ± 0.100.15( 3.80)(4X)( 8X 0 . 30 )( 6X 0 . 8 )0 .9 ± 0.10BASE PLANE CSEATING PLANE0.08C0.10C8 X 0.30SEE DETAIL "X"0.104C A M B INDEX AREA6PIN 14.00ABPIN #1 INDEX AREABSC2.4REF6X 0.806( 8 X 0.60 )8X 0 . 40 ± 0.103.45 ± 0.10( 2.50)( 3.45 )0.05M C 54810 . 00 MIN.0 . 05 MAX.C0 . 2 REFTiebar shown (if present) is a non-functional feature and may be located on any of the 4 sides (or ends).Corporate HeadquartersTOYOSU FORESIA, 3-2-24 Toyosu,Koto-ku, Tokyo 135-0061, Japan Contact InformationFor further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:/contact/TrademarksRenesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.IMPORTANT NOTICE AND DISCLAIMERRENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDINGREFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.(Rev.1.0 Mar 2020)。

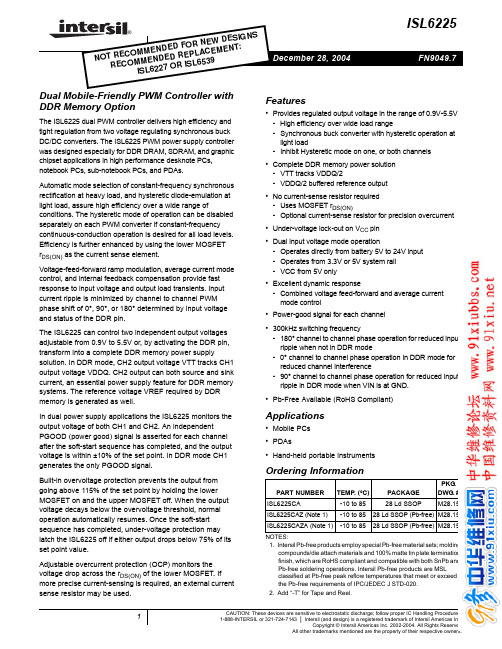

ISL6161芯片手册