基于FPGA器件的RS232_C接口设计及其扩展

基于FPGA Verilog RS232串口回环测试例程,附源程序仿真源码及测试图片

FPGA Verilog RS232串口回环测试基于FPGA Verilog RS232串口回环测试例程,支持多byte数据传输,附源程序仿真源码及测试图片。

测试基于SSCOM/友善之臂上位机软件测试,测试结果如下图一图二所示。

图一SSCOM图二图三连续发送仿真截图图四连续接收仿真截图后附verilog源程序代码及testbech仿真例程,注释欠。

重点:多byte回环测试要点,上位机串口多位数据连续发送停止位和起始位之间无间隔,回环程序在接收和发送都需要具备在停止位后能立马跳转到下一个起始位的能力。

重点关注cnt_bit的处理方式。

附录1 顶层例化uart_txd uart_txd(.clk_50m(sys_clk_50m),.reset_n(sys_rst_n),.tx_data(rx_data),.baud_set(3'd4),.send_en(rx_done),.send_done(),.send_busy(send_busy),.uart_tx(uart_tx));uart_rxd uart_rxd(.clk_50m(sys_clk_50m),.reset_n(sys_rst_n),.rx_data(rx_data),.baud_set(3'd4),.rx_done(rx_done),.rx_busy(rx_busy),.uart_rx(uart_rx));附录2 串口发送源程序`timescale1ns/1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 2020/06/21 09:45:23// Design Name:// Module Name: uart_txd// Project Name:// Target Devices:// Tool Versions:// Description://// Dependencies:// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart_txd(clk_50m,reset_n,tx_data,baud_set,send_en,send_done,send_busy,uart_tx);input clk_50m;input reset_n;input[7:0] tx_data;input[2:0] baud_set;input send_en;output reg send_done;output reg send_busy;output reg uart_tx;reg[12:0] cnt;reg[12:0] baud_rate_cnt_max;reg[3:0] cnt_bit;reg[7:0] tx_data_r;localparam baud_rate_9600 =13'd5207;localparam baud_rate_19200 =13'd2603;localparam baud_rate_38400 =13'd1301;localparam baud_rate_57600 =13'd867;localparam baud_rate_115200 =13'd433;always@(posedge clk_50m or negedge reset_n)if(!reset_n)baud_rate_cnt_max <= baud_rate_115200;elsecase(baud_set)3'd0:baud_rate_cnt_max = baud_rate_9600;3'd1:baud_rate_cnt_max = baud_rate_19200;3'd2:baud_rate_cnt_max = baud_rate_38400;3'd3:baud_rate_cnt_max = baud_rate_57600;3'd4:baud_rate_cnt_max = baud_rate_115200;default:baud_rate_cnt_max = baud_rate_115200;endcasealways@(posedge clk_50m or negedge reset_n)if(!reset_n)tx_data_r <=8'd0;else if(send_en)tx_data_r <= tx_data;elsetx_data_r <= tx_data_r;always@(posedge clk_50m or negedge reset_n)if(!reset_n)send_busy <=1'b0;else if(send_en)send_busy <=1'b1;else if(cnt == baud_rate_cnt_max)beginif(cnt_bit ==4'd10)send_busy <=1'b0;elsesend_busy <= send_busy;endelsesend_busy <= send_busy;always@(posedge clk_50m or negedge reset_n)if(!reset_n)send_done <=1'b0;else if(cnt == baud_rate_cnt_max)beginif(cnt_bit ==4'd10)send_done <=1'b1;elsesend_done <=1'b0;endelsesend_done <=1'b0;always@(posedge clk_50m or negedge reset_n)if(!reset_n)cnt <=13'd0;else if(send_busy)beginif(cnt == baud_rate_cnt_max)cnt <=13'd0;elsecnt <= cnt +1'b1;endelsecnt <= cnt;/****************************************always@(posedge clk_50m or negedge reset_n)if(!reset_n)cnt_bit <= 4'd0;else if(send_en) //send_en needs to be 1 clock high pulse cnt_bit <= 4'd1;else if(cnt == baud_rate_cnt_max)beginif(cnt_bit == 4'd10)cnt_bit <= 4'd0;elsecnt_bit <= cnt_bit + 1'b1;endelsecnt_bit <= cnt_bit;******************************************/always@(posedge clk_50m or negedge reset_n)if(!reset_n)cnt_bit <=4'd0;else if(send_busy &&(cnt_bit ==4'd11))cnt_bit <=4'd1;else if(cnt ==1)cnt_bit <= cnt_bit +1'b1;elsecnt_bit <= cnt_bit;always@(posedge clk_50m or negedge reset_n)if(!reset_n)beginuart_tx <=1'b1;endelsecase(cnt_bit)4'd0:;4'd1: uart_tx <=1'b0;//start4'd2: uart_tx <= tx_data_r[0];//bit 04'd3: uart_tx <= tx_data_r[1];4'd4: uart_tx <= tx_data_r[2];4'd5: uart_tx <= tx_data_r[3];4'd6: uart_tx <= tx_data_r[4];4'd7: uart_tx <= tx_data_r[5];4'd8: uart_tx <= tx_data_r[6];4'd9: uart_tx <= tx_data_r[7];//bit 84'd10: uart_tx <=1'b1;//stopdefault:;endcaseendmodule附录3 串口发送testbench`timescale1ns/1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 2020/06/21 11:38:04// Design Name:// Module Name: uart_txd_tb// Project Name:// Target Devices:// Tool Versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart_txd_tb();reg clk_50m;reg reset_n;reg[7:0] tx_data;reg[2:0] baud_set;reg send_en;wire send_done;wire send_busy;wire uart_tx;parameter CLK_PERIOD =20;initial clk_50m =0;always#(CLK_PERIOD /2) clk_50m =~clk_50m;initial begintx_data =8'h55;baud_set =4;reset_n =0;send_en =0;#(CLK_PERIOD *100);reset_n =1;# CLK_PERIOD;send_en =1;#(CLK_PERIOD );send_en =0;#(CLK_PERIOD *4340);send_en =1;#(CLK_PERIOD );send_en =0;#(CLK_PERIOD *4340);#(CLK_PERIOD *100);$stop;enduart_txd uart_txd(.clk_50m(clk_50m),.reset_n(reset_n),.tx_data(tx_data),.baud_set(baud_set),.send_en(send_en),.send_done(send_done),.send_busy(send_busy),.uart_tx(uart_tx));endmodule附录4 串口接收源程序`timescale1ns/1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 2020/06/21 15:30:30// Design Name:// Module Name: uart_rxd// Project Name:// Target Devices:// Tool Versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart_rxd(clk_50m,reset_n,rx_data,baud_set,rx_done,rx_busy,uart_rx);input clk_50m;input reset_n;output reg[7:0] rx_data;input[2:0] baud_set;output reg rx_done;output reg rx_busy;input uart_rx;reg[12:0] cnt;reg[12:0] baud_rate_cnt_max;reg[3:0] cnt_bit;reg uart_rx_r1;reg uart_rx_r2;wire nedge;localparam baud_rate_9600 =13'd5207;localparam baud_rate_19200 =13'd2603;localparam baud_rate_38400 =13'd1301;localparam baud_rate_57600 =13'd867;localparam baud_rate_115200 =13'd433;always@(posedge clk_50m or negedge reset_n)if(!reset_n)baud_rate_cnt_max <= baud_rate_115200;elsecase(baud_set)3'd0:baud_rate_cnt_max = baud_rate_9600;3'd1:baud_rate_cnt_max = baud_rate_19200;3'd2:baud_rate_cnt_max = baud_rate_38400;3'd3:baud_rate_cnt_max = baud_rate_57600;3'd4:baud_rate_cnt_max = baud_rate_115200;default:baud_rate_cnt_max = baud_rate_115200;endcasealways@(posedge clk_50m or negedge reset_n)if(!reset_n)beginuart_rx_r1 <=8'd0;uart_rx_r2 <=8'd0;endelse beginuart_rx_r1 <= uart_rx;uart_rx_r2 <= uart_rx_r1;endassign nedge = uart_rx_r2 &(!uart_rx_r1);always@(posedge clk_50m or negedge reset_n) if(!reset_n)rx_busy <=1'b0;else if(nedge)rx_busy <=1'b1;else if(cnt == baud_rate_cnt_max)begin if(cnt_bit ==4'd10)rx_busy <=1'b0;elserx_busy <= rx_busy;endelserx_busy <= rx_busy;always@(posedge clk_50m or negedge reset_n) if(!reset_n)rx_done <=1'b0;else if(cnt == baud_rate_cnt_max)begin if(cnt_bit ==4'd10)rx_done <=1'b1;elserx_done <=1'b0;endelserx_done <=1'b0;always@(posedge clk_50m or negedge reset_n) if(!reset_n)cnt <=13'd0;else if(rx_busy)beginif(cnt == baud_rate_cnt_max)cnt <=13'd0;elsecnt <= cnt +1'b1;endelsecnt <= cnt;always@(posedge clk_50m or negedge reset_n) if(!reset_n)cnt_bit <=4'd1;else if(cnt == baud_rate_cnt_max )begin if(cnt_bit ==4'd10)cnt_bit <=4'd1;elsecnt_bit <= cnt_bit +1'b1;endelsecnt_bit <= cnt_bit;always@(posedge clk_50m or negedge reset_n)if(!reset_n)beginrx_data <=8'd0;endelse if(cnt == baud_rate_cnt_max /2)case(cnt_bit)4'd1:;//start4'd2: rx_data[0]<= uart_rx_r2;//bit 04'd3: rx_data[1]<= uart_rx_r2;4'd4: rx_data[2]<= uart_rx_r2;4'd5: rx_data[3]<= uart_rx_r2;4'd6: rx_data[4]<= uart_rx_r2;4'd7: rx_data[5]<= uart_rx_r2;4'd8: rx_data[6]<= uart_rx_r2;4'd9: rx_data[7]<= uart_rx_r2;//bit 74'd10:;//stopdefault:;endcaseelserx_data <= rx_data;endmodule附录5串口接收testbench`timescale1ns/1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 2020/06/21 19:44:29// Design Name:// Module Name: uart_rxd_tb// Project Name:// Target Devices:// Tool Versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart_rxd_tb();reg clk_50m;reg reset_n;wire[7:0] rx_data;wire rx_done;wire rx_busy;reg uart_rx;parameter CLK_PERIOD =20;initial clk_50m =0;always#(CLK_PERIOD /2) clk_50m =~clk_50m;initial beginreset_n =0;uart_rx =1;//idle#(CLK_PERIOD *100);reset_n =1;# CLK_PERIOD;uart_rx =0;//start#(CLK_PERIOD *434);uart_rx =1;//bit0#(CLK_PERIOD *434);uart_rx =0;//bit1#(CLK_PERIOD *434);uart_rx =1;//bit2#(CLK_PERIOD *434);uart_rx =0;//bit3#(CLK_PERIOD *434);uart_rx =1;//bit4#(CLK_PERIOD *434);uart_rx =0;//bit5#(CLK_PERIOD *434);uart_rx =1;//bit6#(CLK_PERIOD *434);uart_rx =0;//bit7#(CLK_PERIOD *434);uart_rx =1;//stop#(CLK_PERIOD *434);uart_rx =1;//idle#(CLK_PERIOD *434);#(CLK_PERIOD *434);#(CLK_PERIOD *434);uart_rx =0;//start #(CLK_PERIOD *434);uart_rx =0;//bit0#(CLK_PERIOD *434);uart_rx =1;//bit1#(CLK_PERIOD *434);uart_rx =0;//bit2#(CLK_PERIOD *434);uart_rx =1;//bit3#(CLK_PERIOD *434);uart_rx =0;//bit4#(CLK_PERIOD *434);uart_rx =1;//bit5#(CLK_PERIOD *434);uart_rx =0;//bit6#(CLK_PERIOD *434);uart_rx =1;//bit7#(CLK_PERIOD *434);uart_rx =1;//stop#(CLK_PERIOD *434);uart_rx =1;//idle#(CLK_PERIOD *434);#(CLK_PERIOD *434);#(CLK_PERIOD *434);$stop;enduart_rxd uart_rxd(.clk_50m(clk_50m),.reset_n(reset_n),.rx_data(rx_data),.baud_set(3'd4),.rx_done(rx_done),.rx_busy(rx_busy),.uart_rx(uart_rx));endmodule。

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

一种基于SPI配置模式FPGA在线升级方案

• 37•的难度。

所以,应发挥导频实际应用性,加强对导频财务支出方面内容的研究,在分析该方面内容时应了解其资金的支出情况与运行情况,使用导频服用技术设计导频信号,进而可以确保导频财支出财务的有效性,此外,在校正信道标准时,应遵守互异性原则。

针对大规模天线系统来说,如果基站天线用户量增加,会导致用户获得信息速度带来阻碍。

因此,从获取信息的角度出发,控制对导频资金方面的投入。

如果开发导频的开销比用户的数量大很多,这会对用户获取信息带来阻碍。

因此,为了能够有效的减少导频的投入,应将已开发的导频资源功能发挥出来。

导频的内容主要包括设计信号、复用手段等内容,以下介绍判断信道互异性的两个标准:(1)第一,电路的判断。

其主要是针对硬件电路,应用多路方式,并采用耦合器与信道天线进行关联,确保信道线路的接收与发送工作可以有效的进行;(2)第二,校准与判断空间信号。

对校准的信息与数据进行计算与判断,进而达到对现代化数据与信息获取的目的。

3.2 5G网络大规模天线无线的理论传输方法实际上该技术是在广播与接入信道的基础上所设计出的一种传输性渠道,从理论的角度来看,通过对接入信道通的检测,可以满足容量的基本要求。

其中广播信道,可以采用污纸编码的方式达到目的。

随着天线和使用该系统数量的增加,难以实现对该系统的传输功能。

从理论角度通过对该系统进行分析与讨论,如果MIMO技术的天线数量最多时,为了能够保障其达到接近容量的目的,其上行应使用最大比进行合并,而下行可以使用MRT。

此外,如果使用规模大的天线时,能够减少上行和下行之间信息难度,但由于受到多种因素的影响,增加了其复杂性;因此,针对这一现象,应采用适当的解决方式,例如,采用空分多址等传输方式。

3.3 系统的资源配置该系统中,为了可以更好的提升资源利用率;因此,应合理的优化该系统资源,做好资源配置工作,为了能将该系统的优势作用发挥出来,应采用优化和分配资源的方式进行,这种方式属于一种较为高和较为简单的设计方案,以下笔者分析与探讨该系统中的MIMO技术的空域资源的实际分配情况得出以下结论:(1)采用统计空分复用的方式可有效降低MIMO技术的难度,并在其进行使用过程中用户分簇会产生一定的影响;(2)要实现将容量最大化的目的,可以合理的对信道信息进行统计,此外为了达到用户分簇的目的,可以采用统计信道信息和贪婪算法,井将一些存在相似信道的用户分配于同簇内;(3)由于相关工作人员对分簇方法的具体实施与其性能有着一定的影响,所以,其传输方法会对其性能产生极大影响;所以应适当的调整分族度量,可以使用弦距离代替,并指出分簇算法,以达到合理分配资源的目的;(4)5G大规模天线无线传输理论和技术,属于目前重要的研究题目,对该方面的研究虽已获得明显的效果,但是该技术在降低其复杂性的方面,还需要进行深入研究,并找出合理的应对措施,深入研究无线系统的资源分配方案的设计,进而推动该技术的可持续发展。

RS232串行口扩展设计

《电子线路CAD实习》实习课题五:RS232串行口扩展设计一、功能要求利用MAX232芯片实现将一路RS232串行输出信息扩展为八路RS232串行输出信息。

二、原理设计根据电平匹配和输出要求选择实现方案,设计出系统原理图,并进行参数计算和元器件选择,说明电路的工作原理。

三、设计要求1)在所选原理图中要有自己绘制的元件符号;2)利用自动布局、自动布线的方法,将原理图转换为印刷电路板图;3)印刷电路板图上的元件要按工艺要求和电气性能进行排列,布线率要求100%;4)电源线的宽度为20mil,接地线的宽度为30mil,其余接线宽度为10mil,并分别将电源、接地、输入、输出等端用接插件或焊盘引出,输入/输出信息采用DB9插座;5)利用手工编辑的方法对电路板进行编辑和修饰;6)利用系统的网络表比较功能,对原理图和印刷电路板图进行比较,结果应完全一致;7)绘制完毕,要产生自己的项目封装库;8)将所设计内容在屏幕上演示出来。

9)根据具体情况进行电路仿真:3D仿真,检查布局和布线的合理性。

四、撰写实习报告实习报告是在完成设计、仿真、绘制后,对学生归纳技术文档、撰写科学论文和科研总结报告能力的训练。

通过编写实习报告,不仅可以将设计、绘制、仿真及技术参数的内容进行全面总结,而且可以把实践内容提升到理论高度。

实习报告通常包括如下的内容:1)课题名称。

2)内容摘要。

3)设计内容及技术要求。

4)系统方案,画出系统原理图。

5)单元电路设计,参数计算和元器件选择。

6)画出完整的原理图,并说明电路的工作原理。

7)设计PCB板图,PCB图的3D仿真图。

8)列出系统所需要的元器件清单。

9)总结收获体会:总结设计电路的特点和方案的优缺点,归纳课题核心及其应用价值,提出改进意见。

10)列出参考文献。

五、参考图芯片原理见附件。

rs232电路设计

rs232电路设计【原创实用版】目录1.RS232 概述2.RS232 电路设计原理3.RS232 电路设计步骤4.RS232 电路设计注意事项5.RS232 电路设计的应用正文一、RS232 概述RS232 是一种串行通信接口标准,它是电子设备之间进行数据传输最常用的一种方式。

RS232 标准定义了数据传输的电平、波特率、奇偶校验等参数,使得不同厂商生产的设备能够互相通信。

二、RS232 电路设计原理RS232 电路设计主要是通过电平转换器(如 MAX232)实现逻辑电平与 RS232 电平的转换。

逻辑电平一般为 0-5V,而 RS232 电平为 -12V 至 12V。

此外,还需要考虑数据传输的波特率、奇偶校验等因素。

三、RS232 电路设计步骤1.确定通信设备参数:首先需要了解通信设备的接口类型、波特率、奇偶校验等参数。

2.选择合适的电平转换器:根据设备的通信参数,选择合适的电平转换器,如 MAX232、MAX485 等。

3.设计电路:根据所选电平转换器的引脚定义,设计电路连接方式。

4.编写程序:编写相应的程序实现数据发送和接收。

5.测试:通过调试程序和观察通信状态,检查通信是否正常。

四、RS232 电路设计注意事项1.电平转换:确保逻辑电平与 RS232 电平之间的转换正确。

2.波特率匹配:通信设备之间的波特率需要一致。

3.奇偶校验:根据设备需求设置奇偶校验位。

4.电源保护:对于电源电压不稳定的场合,需要考虑电源保护措施。

五、RS232 电路设计的应用RS232 电路设计广泛应用于电子设备之间的数据通信,如计算机与外设、工控系统、通信设备等。

基于FPGA的接口转换电路设计

基于FPGA的接口转换电路设计摘要:21世纪是信息化的世纪,计算机技术迅速发展,越来越多的计算机采用传输速率更快且性能更加优良的USB接口,而个人计算机上的RS232,正在逐渐被淘汰。

但在工业领域中RS232应用仍十分广泛。

本文在此应用背景下,研究和设计USB与RS232之间的接口转换电路,硬件开发采用了SOPC设计,添加不同功能的模块,构建NIOSII系统,在QuartuII中完成硬件开发,而软件开发在NIOSIIIDE中完成,利用FPGA 平台,实现USB与RS232之间的接口转换,实现上位控制计算机与底层设备之间的数据通信。

关键词:USB接口;RS232接口;FPGA;SOPC随着计算机科学技术的迅速发展,如今对计算机的数据通信速度有了更高的要求,因此计算机的外围接口也发展迅速。

由于USB在个人计算机上应用越来越广泛,逐渐淘汰了RS232,但目前仍然很多采用RS232串行接口的工业设备、仪器仪表领域中,考虑到可行性和成本原因,立即将这些设备改造成USB接口是不可行的。

因此本文选择在FPGA开发平台下实现USB转RS232接口,通过这样将计算机与传统的设备相连,实现USB与RS232接口的双向数据传输,同时也扩大了USB的传输距离。

一、基于FPGA嵌入式IP的SOPC系统基于FPGA的嵌入式IP硬核SOPC系统是在FPGA中预先植入NIOS处理器。

为了更好的通用性,必须将常规的嵌入式处理器集成诸多通用和专用的接口,但这样又不得不增加芯片的成本和功耗。

但如果将ARM或者其他处理器核以IP硬核的方式植入FPGA中,利用FPGA的可编程逻辑资源和可擦除性,按照系统功能需求来添加接口功能模块,如USB模块和RS232模块,既能实现目标系统功能,又能实现系统的低成本和低功耗。

这样使得FPGA灵活的硬件设计与处理器的强大软件功能有机地结合在一起,更有效地实现SOPC系统。

虽然基于FPGA嵌入IP硬核能有效降低系统成本和功耗,但也有不足之处:(1)IP硬核多来自第三方公司。

RS-232串口通信设计课程设计

《CPLD/FPGA 》课程设计报告题目: RS-232串口通信设计院(系):信息科学与工程学院专业班级:通信工程11 学生姓名:学号:指导教师:2014年06 月 09 日至2014年 6 月 20 日RS-232串口通信设计课程设计任务书目录1. 课程设计的目的 (4)2. 课程设计题目描述和要求 (4)3. 课程设计报告内容 (4)3.1 课题设计方案及基本原理 (4)3.2 软件设计 (7)3.3 问题 (14)4.总结 (15)5.参考资料 (16)附录程序清单 (17)1.课程设计的目的:(1)学习RS-232串口通信数据结构,并编程完成串行数据的接收和显示。

(2)掌握RS-232的工作机制与原理。

(3)熟练掌握Quartus2软件的使用。

(4)了解CPLD/FPGA实验箱。

2.课程设计题目描述和要求:(1)课程设计题目:基于FPGA的串口通信程序设计。

(2)课程设计要求:下述设计内容需由学生个人独立完成:1.理解电路原理图与工作过程;2.掌握RS-232电气特性;3.掌握RS-232通信原理及串口通信数据格式,并编程完成串行数据的接收和显示;4.能正确处理编程与调试过程中所遇到的问题;5. 在FPGA中构造一个异步串行通信控制模块,完成PC机发送的接收,并设计显示模块,完成接收数据的显示(3)要求的设计成果:1.程序结构合理,语言简洁,格式规范,注释详细;2. 掌握RS-232的工作机制与原理;3. 格式为:1位起始位,8位数据位,1位停止位,无奇偶校验位,波特率设定为300Baud。

能与计算机正常通信;4. 按要求完成课程设计报告,格式符合学校规范标准,字数不少于2000字。

3.课程设计报告内容:3.1课程设计方案及基本原理:设计方案:利用实验箱上的MAX232芯片控制通过适当分频(分频的目的是为了达到要求的波特率,控制数据传输速率)的串行输入信号,并将其转换为并行信号并通过实验箱上的数码管的后两位显示从计算机中传输出来的16进制数。

基于uart的rs232串口通信 毕设论文

基于FPGA的RS232串口通信摘要:UART是设备和设备间进行通信的关键,当一个设备需要和另一个连接的设备进行通信时,通常采用数字信号,这种源自并行的信号必须转换成串行信号才能通过有线或无线传输到另一台设备。

在接收端,串行信号又转换成并行信号进行处理,UART处理这种数据总线和串行口之间的串-并和并-串转换。

本文所要实现的就是就是这种串-并和并-串的转换,使之能够进行数据的传输。

本文介绍了用FPGA技术实现UART电路的一种方法,用VHDL进行编程,在Modelsim下进行编译及仿真等。

本设计包含UART发送器、接收器和波特率发生器。

关键词:串口通信RS232 FPGA VHDL UARTAbstractUART is the key for equipment and devices to communicate , when a device needs to communicate with another connected device, commonly use digital signal, this signal must be converted from parallel to serial signal to pass into a wired or wireless transmission to the other device.In the receiver, the serial signal is converted to parallel signal to process, UART process data between the bus and serial port string - and and and - string conversion.This article is aimed to achieve this series - and and and - string conversion to enable data transmission.This article describes the UART circuit using FPGA technology .and programming with VHDL ,compile under and simulation in Modelsim .The design includes UART transmitter, receiver and baud rategenerator.Keywords: serial communication RS232 FPGA VHDL UART第一章引言1.1串口通信技术1.1-1 什么是串口通信串口是计算机上一种非常通用设备通信的协议。

基于FPGA的CAN总线驱动设计与实现

摘要:机载产品通常系统复杂,功能单元众多,实现国产化周期长、难度大。

FPGA是一种通过编程改变逻辑功能的半定制芯片,具有编程配置灵活、开发周期短等特点,为机载产品国产化提供了新思路。

鉴于此,深入研究了CAN 总线通信协议,分析了CAN驱动的数据流和组织结构,实现了基于FPGA的SJA1000 CAN总线驱动设计,并将该设计应用于某综合电子战管理系统,证实了其有效性和可靠性。

关键词:FPGA;CAN总线;驱动设计0 引言随着嵌入式系统互联通信的高速发展,传统的RS232、RS485、RS422等总线受传输距离、抗干扰能力、负载能力、传输速率的影响,逐渐制约了嵌入式系统的发展。

CAN总线系统是一种多主控的总线系统,在总线控制器的协调下实现两个节点之间大量数据的传输,由于CAN网络消息的发送是广播式的,即所有节点侦测的数据是一致的,因此非常适合控制信息和数据信息的传输。

CAN总线具有超长的传输距离,理论上限为10 km,因此被广泛应用于超远距离信息传输的工业项目中。

单条总线可负载110个节点,互不干扰;高波特率保证了数据传输速率。

由于国产化需求,进口芯片需要进行原位替换,面对功能可裁剪的嵌入式系统,本文提出了一种基于FPGA实现的CAN总线驱动,并对其设计进行了详细介绍。

1 SJA10001.1 CAN通信结构CAN通信结构如图1所示,以FPGA实现的CAN协议IP核为中心,采用CPU+FPGA+驱动器的架构。

FPGA和CPU之间通过Local Bus进行通信,外挂国微SM65HVD230D型收发器对外进行CAN通信,模块支持5路CAN总线接口。

1.2 CAN通信帧CAN通信帧分为两种,包括11位标识符的标准帧和29位标识符的扩展帧,两者只是在标识符长度即帧ID的长度上不一样。

CAN标准帧信息包括信息和数据两部分共11个字节,前3个字节为信息部分,后8个字节为数据部分。

第一个字节为帧信息,其中前4位DLC表示数据帧的实际长度,第6位(RTR)为帧类型,数据帧设置为0,远程帧设置为1;第7位(FF)为帧格式,标准帧设置为0。

基于FPGACPLD设计与实现UART(VHDL)

基于FPGA/CPLD设计与实现UART(VHDL)1 引言由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。

特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。

可以说EDA 产业已经成为电子信息类产品的支柱产业。

EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(HDL)描述电路系统。

就FPGA和CPLD开发而言,比较流行的HDL主要有Verilog HDL、VHDL、ABEL-HDL和 AHDL 等,其中VHDL 和Verilog HDL因适合标准化的发展方向而最终成为IEEE标准。

下面的设计就是用VHDL来完成实现的。

2 UART设计实例通常设计数字电路大都采用自顶向下将系统按功能逐层分割的层次化设计方法,这比传统自下向上的EDA设计方法有更明显的优势(当时的主要设计文件是电路图)。

因为由自顶向下的设计过程可以看出,从总体行为设计开始到最终逻辑综合,形成网络表为止。

每一步都要进行仿真检查,这样有利于尽早发现系统设计中存在的问题,从而可以大大缩短系统硬件的设计周期。

下面以UART的设计为例具体说明:(本设计只对本设计的总模块做各种基于MAX+PLUS II环境下的各种分析,对于各分模块只是作些必要的说明。

) UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是一种应用广泛的短距离串行传输接口。

UART允许在串行链路上进行全双工的通信。

串行外设用到的RS232-C异步串行接口,一般采用专用的集成电路即UART实现。

如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。

或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。

基于RS232接口的调制解调器开发设计

基于RS232接口的调制解调器开发设计在现代计算机和通信领域中,RS232接口已经成为一种非常常见的通信接口。

这种接口可以用于连接串口设备,例如调制解调器。

调制解调器是一种用于传输数据的设备,其主要作用是将信号从计算机转换成模拟信号,以便通过电话线路传输。

随着计算机和通信技术的不断发展,调制解调器的使用也越来越普遍。

因此,本文将讨论基于RS232接口的调制解调器开发设计的相关问题。

一、调制解调器的基本原理调制解调器(Modem)是一种传输媒介,它可以使计算机通过电话线路连接到其他计算机或网络。

调制解调器的原理很简单:将数字信号变成模拟信号,以便通过电话线路传输,并将模拟信号转换回数字信号。

这样,我们就可以通过电话线路进行数据传输。

调制解调器的运行原理大致如下:在数据发送端,计算机将数字信号转换成模拟信号,并通过电话线路发送到接收端;在数据接收端,调制解调器将接收到的模拟信号转换成数字信号,并传输到计算机。

二、RS232接口的作用RS232接口是一种用于串行通信的标准接口,它已经成为计算机系统中的一种标准接口方式。

通过RS232接口,可以将计算机与其他设备(如调制解调器)连接起来,并通过电话线路进行数据传输。

在RS232接口标准中,规定了数据传输的格式、速率以及基本的通信协议。

在使用RS232接口进行通信时,我们需要遵循这些规则,以确保传输的数据的正确性和完整性。

三、基于RS232接口的调制解调器开发设计基于RS232接口的调制解调器开发设计可以分为以下两个方面进行:1. 调制解调器硬件设计调制解调器主要由模拟前端、数字前端和通信控制三部分组成。

模拟前端主要负责将数字信号转换成模拟信号,数字前端负责将模拟信号转换成数字信号,通信控制则负责调控整个转换过程的控制。

在调制解调器的硬件设计中,需要考虑如何设计模拟前端部分的电路、数模转换电路、模数转换电路,以及与计算机连接的RS232接口等。

此外,还需要考虑如何通过通信控制进行命令控制和数据传输。

基于FPGA的RS232转429接口电路的设计与实现

s o a h e i to sr a o a l n f c ie h w t t e d sg me d i e s n b e a d ef t . h t n h e v

Ke r s: y wo d EPFl OK1 C8 OL 4;smu ai n;VHDL i lt o

2 2 3

I铡息} 接 _ 粒电 羟{ _ - 涮路 蛊

也路

零 处 理

2¨蹦} 待测品 9 电 _ 检产 j 按 —

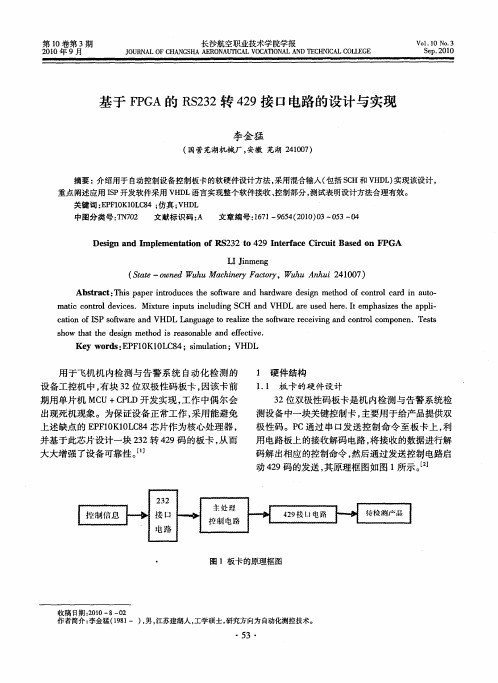

图 1板 卡的原理框图

收稿 日期 :0 0—8— 2 21 0 作者简介 : 李金猛 (9 1 ) 男 , 1 8 一 。 江苏建湖人 , 工学硕士 , 研究方 向为 自 动化测控技术。

・

5 ・ 3

长沙航空职业技术 学院学报

第1 0卷

12 各 组 成 电 路 的 设 计 .

4 9接 口电路 部分 : 2 电平 转换 部 分是 把 串行 的

本 卡共 由电源 电路 、 晶振 电路 、3 2 2接 口电路 、

49接口电路、 2 主处理 电路等 5部分组成 , 其连接 线路如图 2 所示 , 中电源电路部分省略掉。 其 22 3 通信 电路 部分 : 系统 控制通讯 接 口采用 R 22 该接 收 电 路 部 分 采 用 可 调 波 特率 ( 件 可 S3 , 软 以修 改 ) 行异 步 通讯 , 1 进 每 0位 1个 字符 , 据 位 数 为8 , 位 第一位 和最后一位分别 为起始位 和停 止 位, 波特率为 90 b / , 60 i s每位时间约 14 s t 0 u。为提

用 于 飞机机 内检 测与 告 警 系 统 自动 化 检 测 的 设 备工 控机 中 , 块 3 双极性 码板 卡 , 有 2位 因该 卡前 期 用单 片机 MC U+C L P D开 发实 现 , 工作 中偶 尔会 出现死 机现象 。为保证 设备 正 常工 作 , 采用 能 避免 上 述缺 点 的 E F0 0 C 4芯 片作 为核心 处理 器 , P 1K1L 8 并基 于 此芯片 设计 一块 22转 49码 的板卡 , 而 3 2 从 大大 增强 了设 备 可靠性 。 …

基于FPGA的ASIC设计

基于FPGA的ASIC设计—RS232接口功能一、设计说明为了配合课程设计,完成RS232通信功能,以Verilog为硬件描述语言在FPGA开发板上实现串行通信的接受和发送模块,通过本项目掌握基于FPGA的ASIC设计的流程方法。

1. RS232介绍RS232是一种异步串行通信接口,RS232只是一个物理层的标准,只规定了信号物理特性,链路层的协议是UART,RS232接口的逻辑设计就是这部分内容。

其设置包括三部分:波特率、奇偶校验、停止位。

所谓波特率,指单位时间内传送二进制数据的位数,以位/ 秒为单位,是衡量串行数据传输快慢的重要指标。

如果某串口的波特率为115 200,指的是该串口以115 200bits/s 的速率在传输数据。

奇偶校验:是用来验证数据的正确性。

奇偶校验是通过修改每一发送字节(也可以限制发送的字节)来工作的。

在偶校验中,因为奇偶校验位会被相应的置1或0(一般是最高位或最低位),所以数据会被改变以使得所有传送的数位(含字符的各数位和校验位)中“1”的个数为偶数;在奇校验中,所有传送的数位(含字符的各数位和校验位)中“1”的个数为奇数。

奇偶校验可以用于接受方检查传输是否发送生错误——如果某一字节中“1”的个数发生了错误,那么这个字节在传输中一定有错误发生。

如果奇偶校验是正确的,那么要么没有发生错误要么发生了偶数个的错误。

停止位:是在每个字节传输之后发送的,它用来帮助接受信号方硬件重同步。

2. RS232的特性使用9针的"DB-9"插头(它一共有9个引脚,最重要的3个引脚是:引脚2 RxD (接收数据). 引脚3: TxD (发送数据). 引脚5: GND (地)). 允许全双工的双向通讯,最大可支持的传输速率为10KBytes/sRS232通信线上的电平RS-323标准对逻辑电平的定义。

对于数据(信息码):逻辑“1”(传号)的电平低于-3V,逻辑“0”(空号)的电平高于+3V;对于控制信号;接通状态(ON)即信号有效的电平高于+3V,断开状态(OFF)即信号无效的电平低于-3V,也就是当传输电平的绝对值大于3V时,电路可以有效地检查出来,介于-3~+3V之间的电压无意义,低于-15V或高于+15V的电压也认为无意义,因此,实际工作时,应保证电平在±(3~15)V之间。

基于FPGA的UART通信接口电路设计

基于FPGA的UART通信接口电路设计张蕾【摘要】随着煤矿设备自动化程度的不断提高,对信号的传输也提出了越来越高的要求.本文设计了一种基于现场可编程门阵列(field programmable gate array,FPGA)的RS232接口电路.首先,分析了FPGA在设计通用串行收发器(universal asynchronous receiver and transmitter,UART)接口电路中的优势.该接口电路主要分为UART接收子模块、波特率发生器、先进先出(first in first out,FIFO)模块、UART发送子模块、通信校验模块等.然后,基于Xilinx公司的FPGA平台,使用Verilog HDL语言编写并实现了整个系统,给出了完整的电路结构框图及实验结果.实验结果验证了所设计RS232接口电路的有效性.【期刊名称】《山西焦煤科技》【年(卷),期】2011(035)008【总页数】3页(P18-20)【关键词】通用串行收发器(UART);可编程门阵列(FPGA);过采样;先进先出(FIFO)【作者】张蕾【作者单位】山西煤炭进出口集团有限公司,山西太原 030006【正文语种】中文【中图分类】TD65目前,我国的煤矿设备自动化程度不断提高,井下作业对信号传输的要求也愈趋严格。

本文研究的通用串行收发器(universal asynchronous receiver and transmitter,UART)可通过串行线传输并行数据,其本质功能是作为控制器和串行设备间的编码转换装置,在基于RS232、RS485等标准协议的通信系统中广泛应用[1-3],非常适合矿井通信系统。

常用的单片机、DSP控制器等一般都集成有专用的UART外设,极大地方便了基于RS232等协议的通信系统设计。

但这类预先固化好的系统也存在一定的不足,如工作模式不够灵活,数据位数固定、通信的波特率一般限制在几个固定的数值,可扩展性较小。

基于FPGA的单片机端口扩展设计

在需 要 同时 控制 多 片 AD C去 采集 多 路信 号 的场 合

需要 复 杂 的逻辑 控制 才 能实现 , 因此 扩 展单 片 机 的

Uo端 口资 源显得 非 常有 必要 , 统 的方 法 常 常 采 传

用锁 存 器来 实现 端 口复用 以达 到 扩 展 的 目的 , 是 但

这种 方 法非 常受 限制 , 而且 在很 多 场 合 根本 无 法 使

全 能够 满 足本 系统 中对 端 口数量 的要 求 。 E 2 8 4 C 是美 国 P C T1 4 8 E A推 出 的低成 本 R C c n] 列 F GA, 在 总 体 性 能 上 优 于 上 一 代 yl e 系 o ] P 它

Ccn yl e系 列 F G o P A。本 文 采 用 的 E 2 8 1 4 8 P C T 4C

1 引 言

众 所周 知 , 片机 的 Io 端 口资 源都 比较 少 , 单 /

现这 样 的控制 , 而简 化控 制逻 辑 又需 要 庞 大 的端 然

口数 量 , 对 于单 片机 来 说完 全 无 法 实 现 。而 F — 这 P

GA 最 多可达 到 6 0多个 用 户 可 配 置 I0 端 口, 0 / 完

2 60 ) 6 4 5

( 装 驻 沈 阳 地 区航 空 军 事 代 表 室 ” 沈 阳 1 0 3 ) 海 军 9 8 0部 队 。 青 岛 海 10 4 ( 24

摘

要

针 对 单 片 机 端 口少 的 问 题 , 用 F GA 对 单 片机 进 行 端 口扩 展 。 F GA 端 口数 量 巨 大 , 上 资 源 丰 富 , 以 应 P P 片 可

用 。本 文提 出 一 种 基 于 F GA 的 端 口扩 展 方 法 , P

基于FPGA的多串口通信设计与实现

Ke y Wo  ̄S : s e r i a l p o r t ; AS I C; F P GA; UAl k T; i n t e =u p t c o n t r o l l e r ; VHDL

串行通信 因为具有传输线少、 成本低、 配置灵活等特 点, 得到了 广泛应用 , 通用异步收发传 输器 ( Un i v e r s a l As y n c h r o n o u s Re — c e i v e r / Tr a n s mi t t e r ) , 是一种 比较常用的接 口电路 , 主要用于 串行数 据和并行数据的转换。 一般该接 口由专用的UAR T 芯片完成 , 例如 S Cl 6 C 5 5 4 B I B 6 4 , 该接 口芯片具有4 路独立 的通道 , 同时提供多种控 制功能 , 但在实际使用 中往往只使用一种特定控制方式 , 这 不仅造 成 电路复杂和浪费 , 而且会使P C B 面积增 大, 布线复杂 。 [ 1 1 F P G A( F i e l d - P r o g r a mma b l e G a t e Ar r a y ) , 即现场可编程 门 阵列 , 它是作为专用集成电路领域中一种 半定制电路出现 的 , 既解 决了定制 电路的不足, 又克服了原有可编程器件 门电路数有 限的缺 点。 F P G A中具有 丰富的触发器和I / O口, 采用描述语言(ቤተ መጻሕፍቲ ባይዱVHD L 和 V e r i l o g HD L )  ̄行设计 , 用户可以根据需要, 描述 出具有各种功 能的

rs232电路设计

rs232电路设计摘要:I.引言- 介绍RS232 电路设计的基本概念II.RS232 电路设计原理- 讲解RS232 通信协议的基本原理- 分析RS232 电平与信号传输的关系III.RS232 电路设计要素- 电源设计- 信号传输线路设计- 信号转换与放大设计- 信号防护与抗干扰设计IV.RS232 电路设计实践- 给出实际RS232 电路设计案例- 分析案例中各部分的设计思路与实现方法V.RS232 电路设计常见问题及解决方法- 分析RS232 电路设计中可能遇到的问题- 提供相应的解决措施VI.总结- 回顾RS232 电路设计的关键要点- 展望RS232 电路设计的未来发展正文:I.引言RS232 电路设计是电子工程技术中的一项重要内容,涉及计算机串行通信、数据采集、远程控制等领域。

本文将围绕RS232 电路设计展开讨论,帮助读者了解其基本原理与设计方法。

II.RS232 电路设计原理RS232 是一种串行通信协议,基于异步传输方式,传输距离较短。

其基本原理是通过电平转换实现数据传输。

在发送端,计算机内部逻辑电平转换为RS232 电平;在接收端,RS232 电平转换为计算机内部逻辑电平。

III.RS232 电路设计要素A.电源设计:RS232 电路设计需要稳定的电源供应,一般采用±12V、+5V 电源。

B.信号传输线路设计:采用双绞线或同轴电缆作为信号传输线路,需考虑传输距离、信号衰减等因素。

C.信号转换与放大设计:根据实际传输距离与信号要求,设计合适的信号转换与放大电路。

D.信号防护与抗干扰设计:采用屏蔽线、隔离变压器等措施,提高信号抗干扰能力。

IV.RS232 电路设计实践以下为一个简单的RS232 电路设计案例:1.电源设计:采用±12V、+5V 电源,设计合适的电源电路。

2.信号传输线路设计:采用双绞线连接计算机与RS232 设备,确保传输距离在有效范围内。

3.信号转换与放大设计:根据实际传输距离与信号要求,设计合适的信号转换与放大电路。

基于SOPC的CAN_RS232接口转换器设计

设 计 , 实现 片上 集 成其 它协 议接 口转 换 器 的 设 计奠 定 了基础 为

关 键 词 : g ; p ; isI;a r23 f a s c no Icn s 2 p o

_

中 图分 类 号 : 3 1 TP 3

_

文献 标 识 码 : A

文章 编 号 :0 9 3 4 (0 11 — 1 9 0 1 0 — 0 4 2 1 )3 3 6 — 2

A b tac :CAN K S 32 i tra e ta s r lrha e lz d, h c sng Ale aC o po ai sr t 2 n efc r n f l e sr aie w ih u i t r r rton SCycon Isre o T l e I e sFPGA n i h I S i a d us ng t e N O

De in ft sg o he CAN RS 3 n e f c a s o m s d o o c 2 2 I t r a e Tr n f r Ba e n S p

W EIX io—do g, I Yun a n X A

(c o l f t a E e tc n o ue E g e r g Unv r t o a g a fr c n ea dT c n l y S a g a 2 0 9 , hn) S h o o i l l r a a d C mp t n i e n , i sy f h n h io i c n eh oo , h n h i 0 0 3 C ia Op c — c l i r n i ei S Se g

题, 本设 计 采 用 了 A ea的 C co eI 系 列 F A, S C平 台下 利 用 N OSI 理 器 来 实现 接 口的 转换 。 hr y ln I PG 在 OP I I处

RS 232 C

详细介绍

综述 电气特性

机械特性 接口信号

RS -232C标准(协议)的全称是EIA-RS-232C标准,其中EIA(Electronic Industry Association)代表 美国电子工业协会,RS(recommended standard)代表推荐标准,232是标识号,C代表RS232的最新一次修改 (1969),在这之前,有RS232B、RS232A。它规定连接电缆和机械、电气特性、信号功能及传送过程。常用物理 标准还有有EIA-RS-232-C、EIA-RS-422-A、 EIA-RS-423A、EIA-RS-485。这里只介绍EIA-RS-232-C(简称232, RS232)。例如,目前在IBM PC机上的COM1、COM2接口,就是RS-232C接口。

允许发送(Clear to send-CTS)——用来表示DCE准备好接收DTE发来的数据,是对请求发送信号RTS的响 应信号。当MODEM已准备好接收终端传来的数据,并向前发送时,使该信号有效,通知终端开始沿发送数据线TxD 发送数据。

这对RTS/CTS请求应答联络信号是用于半双工MODEM系统中发送方式和接收方式之间的切换。

以上规定说明了RS-232C标准对逻辑电平的定义。对于数据(信息码):逻辑“1”(传号)的电平低于-3V, 逻辑“0”(空号)的电平高于+3V;对于控制信号;接通状态(ON)即信号有效的电平高于+ 3V,断开状态 (OFF)即信号无效的电平低于-3V,也就是当传输电平的绝对值大于3V时,电路可以有效地检查出来,介于-3~ +3V之间的电压无意义,低于-15V或高于+15V的电压也认为无意义,因此,实际工作时,应保证电平在±(3~15) V之间。

基于FPGA技术的RS232接口时序电路设计

基于FPGA技术的RS232接口时序电路设计郝立兵【期刊名称】《现代电子技术》【年(卷),期】2012(035)011【摘要】RS 232接口是现在最常用的一种通信接口.随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量,提高系统集成度和可靠性.详细阐述了如何通过FPGA实现RS 232接口的时序逻辑设计.%RS 232 interface is now the most commonly used form of communication interface. With the rapid development of FPGA technology, the time-sequence circuit of some common interface circuit can be achieved through the FPGA. This design can reduce the quantity of circuit components, and improve system integration and reliability. The implementation method of the sequential logic design of the RS 232 interface by means of FPGA is described.【总页数】2页(P175-176)【作者】郝立兵【作者单位】中国电子科技集团公司第二十研究所,陕西西安710068【正文语种】中文【中图分类】TN47-34【相关文献】1.基于STM32的CAN总线/RS232接口转换器的设计 [J], 曾璐阳2.基于CP2102/CP2103的RS232接口转换为USB接口的应用设计 [J], 徐民;张博3.嵌入式系统外围接口的时序分析与电路设计 [J], 濮小川;赵秋霞;蒋烈辉;马鸣锦;杜威4.基于RS232接口实现多路PIP同屏显示 [J], 朱彧;赵哲懿;张勇5.基于RS232接口的交流电源系统设计 [J], 郭宝军;高贝贝;崔金龙;张亚娟因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第23卷第5期攀枝花学院学报2006年10月V ol.23.No.5Journal o f Panzhihua U niver sity Oct.2006 自然科学研究基于FPGA器件的RS232 C接口设计及其扩展陈炳权(1.吉首大学物理科学与信息工程学院湖南吉首416000; 2.湖南大学电气与信息工程学院湖南长沙410082)摘要串行外设常常用到RS232 C接口,传统上采用诸如8250,8251,NSl6450等U ART器什实现,然而此类器做得相当复杂,RS232 C接口常常不需要使用完整的U ART的功能,而且对于多串口的设备或需要加密通讯的场合使用UA RT也是不合适的。

笔者将RS232 C接口所需要的U ART功能集成到FPG A的XILINX的XCS30内部,利用V HDL将R8232 C的核心功能集成,从而使整个设计更加紧凑小巧,系统功能更稳定可靠。

同时该系统通过扩展,完成多点通信的数据过滤功能,大大降低CPU的负担,提高系统性能。

关键词FP GA/CPL D;U A RT;VH DL;F PG A I P;U AR T多点通信作者简介陈炳权(1972 ),男,湖南省桃源县人,土家族,吉首大学物理科学与信息工程学院讲师,硕士,主要从事电路与系统教学与研究。

随着IC设计技术的不断提高,系统芯片的复杂性越米越高。

为了提高效率,复用以前的砹计模块用A SIC芯片和SO PC实现已经成为SOC设计的必上之路SO PC技术用大规模可编程器件实现SOC的功能,它为SO C的实现提供了一种简单易行而义成本低廉的手段,极人地促进了SO C的发展,笔者设计的系统就是基于大规模可编程器件设计方案,以具有知识产权的内核(IP Core)复作和超深亚微米技术为支撑,采用SO PC技术设计并实现的芯片是面向特定作户的芯片,它能最大程度满足嵌入式系统的要求,充分利川lP技术,减少了产品设计复杂性和开发成本,缩短了产品开发的时间,有效地降低系统功耗,简化了系统加工的复杂性,减少甚至避免电路板信号传送时所造成的系统信号串扰。

U A RT(U niver sal Asy nchro no us Receiv er T r ansmitter)通作异步收发器,是一种应用广泛的短距离串行传输接口,往往用于短距离、低速低成本的微机与下位机的通讯中,并允许在串行链路上进行全双工的通信,串行外设有到RS232 C异步串行接口,然而这类芯片已经相当复杂,有的含有许多辅助的模块(如FI FO),常常不需要使川完整的U AR T的功能利这些辅助功能。

笔者以FP GA为设计,全部用V HD L进行描述,并借助SP EEDW A V E进行语言级的仿真,用XIL IN X的F2.1进行顶层仿真,最后和P C的仿真终端进行联机,功能一切止常,整个U ART所需要的触发器为78,一般的P LD都可以完成。

与目前流行的SCl6C550B串行数据通信的U A RT相比,虽然速度不达不到3M bit/s,但设计紧凑,性能稳定,并能住此没计基础上更容易扩展为URAT IP,通过硬件完成多点通信中的数据过滤功能,从而大大降低了CPU的开销,提高CPU的利用率,1实现RS232 C接口的电路结构串行端口的本质功能是作为CPU和串行设备间的编码转换器。

当数据从CP U经过串行端口送出去时,字节数据转换为串行的位。

在接收数据时,串行的位被转换为字节数据。

在Window s环境(Window s N T、Win98、W indow s2000)下,串口是系统资源的一部分。

一个完整的RS232 C接口有22根线,采川标准的25芯插头座(或者9芯插头座),串行外设常常用到RS232C接口,通常采用诸如8250,8251,NSl6450等U ART器件实现,常见的UA RT主要由数据总线接口、控制逻辑和状态接口、波特率发生器、发送和接受等部分组成,如图1所示,其功能包括微处理器接口,发送缓冲器(tbr)、发送移位寄存器(tsr)、帧产生、奇偶校验、并转串、数据接收缓冲器(rbr)、接收移位寄存器(r sr)、帧产生、奇偶校验、串转并。

从图1可以看出,U A RT的接收和发送是按照相同的波特率进行收发的,波特率是可以通过CPU的总线接口设置的。

U AR T收发的每一个数据宽度都是波特率发生器输山的时钟周期的16倍,对于接收同样存在9、10、11位二种串行数据长度的问题,常必须根据所设置的情况而将数据完整地取下米。

然而它的移何时钟不是一直存在的,这个时钟必须在接受剑起始位的中问开始产生,到停止位的中间结束。

接受到停止位后,必须给出中断,并提供相应的校验出错、FRA M E错以及溢山等状态,需引入hunt和idle两个信号,其中:hunt为高表示捕捉到起始位,idle为高表示不在移位状态,利用这两个信号就可以生成接收所需要的移位时钟。

溢出标志很简单,那就是在idle 从低变高,也就是说在接收剑一个完整的串行序列后,去判断一下当前的中断是否有效。

如果为高那么溢出,否则没有。

在移位的时候,同时对接收的数据进行校验,这样就可以判断接收的数据是否有错,在接收完成时根据当前的R X 是否为高电平就可以知道F RA M E 是否有错。

能实现RS232 C 接口功能的U RA T 的帧格式如图2所示。

包括线路空闲状态(idle,高电平)、起始何(start bit,低电平)、5~8位数据位(data bits)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。

这种格式是由起始位和停止位米实现字符的同步。

U A RT 内部一般有配置寄存器,可以配置数据何数(5~8位)、是否有校验位和校验的类型、停止位的位数(1,1.5,2)等设置。

2 完成RS232 C 功能的UART 的设计与实现2.1发送器发送器每隔16个CL K l6时钟周期输出1位,次序遵循1位起始位、8位数据何(假定数据何为8位)、1位校验何(可选)、1位停止位(通常只要改变G ener ic 参数F ramelen 就可)。

CPU 何时可以向发送缓冲器tbr 写入数据,也就是说CPU 要写数据到tbr 时必须判断当前是否可写,如果不判断这个条件,发送的数据会出错。

数据的发送是由微处理器控制,微处理器给山wen 信号,发送器根据此信号将并行数据din[7..0]锁存到发送缓冲器tbr[7..0],并通过发送移位寄存器tsr[7..0]发送串行数据至串行数据输出端dout 。

在数据发送过程中用输出信号tr e 作为标志信号,当一帧数据发送完毕时,tre{信号为1,通知CPU 在下个时钟装入新数据,其发送状态机状态图如图3,发送器端口信号如图4所示。

引入发送字符长度和发送次序计数器leng th no ,if std log ic vecto r(1eng th no)=!0001∀then tsr<=t br :--发送缓冲器tbr 数据进入发送移位寄存器tsrtre<=#0#:--发送移位寄存器空标志置!0∀elsif std lo gic v ecto r(length no)=!00l0∀t hendo ut<=#0#:一发送起始位信号!0∀elsif std_log ic_vecto r(1ength_no)>=!0011∀and st d_log ic_vector(1eng th_no)<=!1010∀t hentsr<=#0#&tsr(7dow nt o 1):一从低位到高 2.2接收器串行数据帧和接收时钟是异步的,发送来的数据由逻辑i 变为逻辑0可以视为一个数据帧的开始,为了避免毛刺影响,能够得到正确的起始位信号,必须要求接收剑的起始住波特率时钟采样的过程中至少有一半都是属丁逻辑0才可以认定接收剑的是起始何。

接收器先要捕捉起始位,确定r xd 输入由1到0,实现的部分VHDL 程序如下:elsif clklx #event and clklx =#l #then if std_lo gic_vector (1eng th_no)>=!0001∀and std_log ic_v ect or(1engt h_no )<=!1001∀then rsr(0)<=rx da;rsr(7dow nt o 1)<=rsr (6dow nto 0);par ity <=第23卷 陈炳权:基于FPG A 器件的RS232 C 接口设计及其扩展 第5期实现的部分V HD L 程序如卜:位进行移位输山至串行输出端doutdo ur <=tsr(0):par ity <=par ity xo r tsr (0):一奇偶校验elsif std_log ic_vecto r(1ength_no)!1011∀t hendo ur <=pa rity ;--校验位输山elsif std_log ic_vecto r(1ength_no)=!1100∀t hendo ut<=#1#:--停止位输出tre<=#1#:--发送完毕标忠置!1∀end if:逻辑0要8个CL Kl6时钟周期,才是正常的起始何,然后在每隔16个CL K l6时钟周期采样接收数据,移位输入接收移位寄存器rsr ,最后输出数据dour,只有起始位的确是16个bclk 周期长,那么接下来的数据将在每个位的中点被采样,如上文图2所示,同时还要输出一个数据接收标忠信号标忠数据接收完。

接收器的状态图利端口信号如图5,6所示。

par ity xo r r sr (7):elsif std_lo g ic_vecto r(1eng th_no)=!1010∀then rbr <=rsr;--接收移何寄存器数据进入接收缓冲器∃∃endif2.3波特率发生器波特率发生器实际上是一个简单的分频器。

U A RT 的接收和发送是按照相同的波特率进行收发的。

波特率发生器产生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,目的是为在接收时进行精确地采样,以提出异步的串行数据。

根据给定的晶振时钟和要求的波特率算出波特率分频因子。

通过波特率发生器、发送器和接收器模块的设计与仿真,能较容易地实现通用异步收发器总模块,对于收发的数据帧和发生的波特率时钟频率能较灵活地改变,而且硬件实现不需要很多资源,尤其能较灵活地嵌入到FP GA 的开发中。

住EDA 技术平台上进行设计、仿真与实现具有较好的优越性。

一般对于波特率发生器中的系数是固定的(同U RA T 专用芯片不同,FPG A 具体设计的易改性,专用U RA T 芯片还要附加复杂的接口以便在使用时改变波特率),但对于不同的实现,这个系数的更改只要通过V HDL 的Generic 语句可使问题两全其美的解决。