MBRB2515LT4G;MBRB2515LG;MBRB2515LT4;中文规格书,Datasheet资料

MBR1645G;MBR1635G;MBRB1645T4G;中文规格书,Datasheet资料

MBR1635, MBR1645, MBRB1645MBR1645 is a Preferred Device SWITCHMODE EPower Rectifiers16 A, 35 and 45 VThese state−of−the−art devices use the Schottky Barrier principle with a platinum barrier metal.Features•Guard−ring for Stress Protection•Low Forward V oltage•175°C Operating Junction Temperature•Pb−Free Packages are AvailableMechanical Characteristics:•Case: Epoxy, Molded•Weight:1.9 Grams for TO−2201.7 Grams for D2PAK•Finish: All External Surfaces Corrosion Resistant and Terminal Leads are Readily Solderable•Lead Temperature for Soldering Purposes:260°C Max. for 10 SecondsMAXIMUM RATINGSRating Symbol Value UnitPeak Repetitive Reverse Voltage Working Peak Reverse VoltageDC Blocking Voltage MBR1635MBR1645MBRB1645V RRMV RWMV R354545VAverage Rectified Forward Current Delay (Rated V R, T C = 163°C) Total Device I F(AV)16APeak Repetitive Forward Current, PerLeg(Rated V R, Square Wave,20 kHz, T C = 157°C) Total DeviceI FRM32ANon−Repetitive Peak Surge Current (Surge Applied at Rated Load Conditions Halfwave, Single Phase, 60 Hz)IFSM150APeak Repetitive Reverse Surge Current(2.0 m s, 1.0 kHz)I RRM 1.0A Storage Temperature Range T stg−65 to +175°C Operating Junction Temperature (Note 1)T J−65 to +175°C Voltage Rate of Change (Rated V R)dv/dt10,000V/m s Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.The heat generated must be less than the thermal conductivity fromJunction−to−Ambient: dP D/dT J < 1/R q JA.Device Package ShippingORDERING INFORMATIONMBR1635TO−22050 Units / RailMBR1635G TO−220(Pb−Free)50 Units / RailPreferred devices are recommended choices for future use and best overall value.1, 4MARKINGDIAGRAMSA= Assembly LocationY= YearWW= Work WeekB16x5= Device Codex= 3 or 4KA= Diode PolarityG= Pb−Free PackageMBR1645TO−22050 Units / Rail MBR1645G TO−220(Pb−Free)50 Units / RailB1645GAYWWD2PAKCASE 418BSTYLE 34B1645= Device CodeA= Assembly LocationY= YearWW= Work WeekG= Pb−Free PackageMBRB1645T4G D2PAK(Pb−Free)800 Units / Rail34THERMAL CHARACTERISTICSCharacteristic Symbol Value Unit Maximum Thermal Resistance, Junction−to−Case R q JC 1.5°C/W ELECTRICAL CHARACTERISTICSCharacteristic Symbol Value UnitMaximum Instantaneous Forward Voltage (Note 2) (i F = 16 Amps, T C = 125°C)(i F = 16 Amps, T C = 25°C)v F0.570.63VMaximum Instantaneous Reverse Current (Note 2) (Rated dc Voltage, T C = 125°C)(Rated dc Voltage, T C = 25°C)i R400.2mA2.Pulse Test: Pulse Width = 300 m s, Duty Cycle ≤2.0%.Figure 1. Typical Forward Voltage Figure 2. Typical Reverse Currentv F , INSTANTANEOUS FORWARD VOLTAGE (V)10070205010V R , REVERSE VOLTAGE (V)i F , I N S T A N T A N E O U S F O R W A R D C U R R E N T (A )7.05.03.02.01.030 1.0E −1.0E −1.0E −1.0E −1.0E −1.0E −1.0E −R Figure 3. Current Derating, Case, Per LegFigure 4. Current Derating, AmbientFigure 5. Forward Power DissipationI F(AV), AVERAGE FORWARD CURRENT (A)168.06.04.02.00P 141012, A V E R A G E P O W E R D I S S I P A T I O N (W )F (A V E )T C , CASE TEMPERATURE (°C)T A , AMBIENT TEMPERATURE (°C)02468I F (A V ), A V E R A G E F O R W A R D C U R R E N T (A )I F (A V ), A V E R A G E F O R W A R DC U R R E N T (A )10121410121416182022242628161820STYLE 3:PIN 1.ANODE2.CATHODE3.ANODE4.CATHODED 2PAK CASE 418B −04ISSUE Jǒmm inchesǓ*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.V DIM MIN MAX MIN MAX MILLIMETERS INCHES A 0.3400.3808.649.65B 0.3800.4059.6510.29C 0.1600.190 4.06 4.83D 0.0200.0350.510.89E 0.0450.055 1.14 1.40G 0.100 BSC 2.54 BSC H 0.0800.110 2.03 2.79J 0.0180.0250.460.64K 0.0900.110 2.29 2.79S 0.5750.62514.6015.88V0.0450.0551.14 1.40NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.418B −01 THRU 418B −03 OBSOLETE,NEW STANDARD 418B −04.F 0.3100.3507.878.89L 0.0520.072 1.32 1.83M 0.2800.3207.118.13N 0.197 REF 5.00 REF P0.079 REF 2.00 REF R 0.039 REF 0.99 REF VARIABLEVIEW W −WVIEW W −WVIEW W −W123TO −220PLASTIC CASE 221B −04ISSUE EUDIM MIN MAX MIN MAX MILLIMETERSINCHES A 0.5950.62015.1115.75B 0.3800.4059.6510.29C 0.1600.190 4.06 4.82D 0.0250.0350.640.89F 0.1420.161 3.61 4.09G 0.1900.210 4.83 5.33H 0.1100.130 2.79 3.30J 0.0140.0250.360.64K 0.5000.56212.7014.27L 0.0450.060 1.14 1.52Q 0.1000.120 2.54 3.04R 0.0800.110 2.04 2.79S 0.0450.055 1.14 1.39T 0.2350.255 5.97 6.48U0.0000.0500.000 1.27NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further noticeto any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONSWITCHMODE is a trademark of Semiconductor Components Industries, LLC.分销商库存信息:ONSEMIMBR1645G MBR1635G MBRB1645T4G。

MBRB1645TRLPBF资料

Document Number: 94304For technical questions, contact: diodes-tech@Schottky Rectifier, 16 AMBRB16..PbFVishay High Power ProductsFEATURES•150 °C T J operation•High frequency operation •Low forward voltage drop•High purity, high temperature epoxyencapsulation for enhanced mechanical strength and moisture resistance•Guard ring for enhanced ruggedness and long term reliability•Lead (Pb)-free (“PbF” suffix)•Designed and qualified for Q101 levelDESCRIPTIONThis MBRB16.. Schottky rectifier has been optimized for low reverse leakage at high temperature. The proprietary barrier technology allows for reliable operation up to 150 °C junction temperature. Typical applications are in switching power supplies, converters, freewheeling diodes, and reverse battery protection.PRODUCT SUMMARYI F(AV)16 A V R 35/45 V I RM40 mA at 125 °CMAJOR RATINGS AND CHARACTERISTICSSYMBOL CHARACTERISTICSVALUES UNITS I F(AV)Rectangular waveform16A V RRM 35/45V I FSM t p = 5 µs sine 1800A V F 16 Apk, T J = 125 °C0.57V T J- 65 to 150°CVOLTAGE RATINGSPARAMETERSYMBOLMBRB1635PbFMBRB1645PbFUNITS Maximum DC reverse voltageV R 3545VMaximum working peak reverse voltageV RWMABSOLUTE MAXIMUM RATINGSPARAMETERSYMBOL TEST CONDITIONSVALUES UNITSMaximum average forward currentI F(AV)T C = 134 °C, rated V R 16ANon-repetitive peak surge currentI FSM5 µs sine or 3 µs rect. pulseFollowing any rated load condition and with rated V RRM applied1800Surge applied at rated load condition halfwave single phase 60 Hz150Non-repetitive avalanche energy E AS T J = 25 °C, I AS = 3.6 A, L = 3.7 mH24mJ Repetitive avalanche currentI ARCurrent decaying linearly to zero in 1 µsFrequency limited by T J maximum V A = 1.5 x V R typical3.6A* Pb containing terminations are not RoHS compliant, exemptions may apply元器件交易网 For technical questions, contact: diodes-tech@Document Number: 94304MBRB16..PbFVishay High Power ProductsSchottky Rectifier, 16 ANote(1)Pulse width < 300 µs, duty cycle < 2 %ELECTRICAL SPECIFICATIONSPARAMETER SYMBOL TEST CONDITIONSVAL U ES UNITS Maximum forward voltage drop V FM (1)16 AT J = 25 °C 0.63V T J = 125 °C 0.57Maximum instantaneous reverse currentI RM (1)T J = 25 °C Rated DC voltage0.2mA T J = 125 °C40Maximum junction capacitance C T V R = 5 V DC (test signal range 100 kHz to 1 MHz) 25 °C 1400pF Typical series inductance L S Measured lead from top of terminal to mounting plane 8.0nH Maximum voltage rate of change dV/dtRated V R10 000V/µsTHERMAL - MECHANICAL SPECIFICATIONSPARAMETERSYMBOLTEST CONDITIONSVALUES UNITS Maximum junction temperature range T J - 65 to 150°CMaximum storage temperature range T Stg - 65 to 175Maximum thermal resistance,junction to caseR thJC DC operation1.50°C/WTypical thermal resistance, case to heatsink R thCSMounting surface, smooth and greased0.50Approximate weight 2g 0.07oz.Mounting torque minimum 6 (5)kgf · cm (lbf · in)maximum12 (10)Marking deviceCase style D 2PAKMBRB1645元器件交易网Document Number: 94304For technical questions, contact: diodes-tech@MBRB16..PbFSchottky Rectifier, 16 AVishay High Power ProductsFig. 2 - Typical Values of Reverse Current vs.Reverse VoltageFig. 3 - Typical Junction Capacitance vs. Reverse VoltageFig. 4 - Maximum Thermal Impedance Z thJC Characteristics元器件交易网 For technical questions, contact: diodes-tech@Document Number: 94304MBRB16..PbFVishay High Power ProductsSchottky Rectifier, 16 AAverage Forward CurrentFig. 8 - Unclamped Inductive Test CircuitNote(1)Formula used: T C = T J - (Pd + Pd REV ) x R thJC ;Pd = Forward power loss = IF(AV) x V FM at (I F(AV)/D) (see fig. 6);Pd REV = Inverse power loss = V R1 x I R (1 - D); I R at V R1 = Rated V R applied元器件交易网元器件交易网Schottky Rectifier, 16 A Vishay High Power ProductsORDERING INFORMATION TABLELINKS TO RELATED DOCUMENTSDimensions /doc?95046Part marking information /doc?95054Packaging information /doc?95032Document Number: 94304For technical questions, contact: diodes-tech@ Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网Document Number: 。

MBRB745中文资料

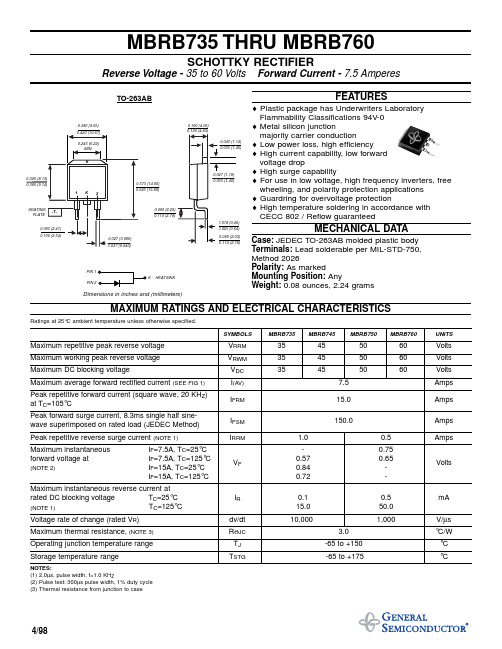

MBRB735 THRU MBRB760SCHOTTKY RECTIFIERReverse Voltage - 35 to 60 Volts Forward Current -7.5 AmperesFEATURESRatings at 25°C ambient temperature unless otherwise specified.SYMBOLS MBRB735MBRB745MBRB750MBRB760UNITS Maximum repetitive peak reverse voltage V RRM35455060Volts Maximum working peak reverse voltage V RWM35455060Volts Maximum DC blocking voltage V DC35455060Volts Maximum average forward rectified current (SEE FIG 1)I(AV)7.5Amps Peak repetitive forward current (square wave, 20 KH Z)at T C=105°CI FRM15.0Amps Peak forward surge current, 8.3ms single half sine-wave superimposed on rated load (JEDEC Method)I FSM150.0Amps Peak repetitive reverse surge current (NOTE 1)I RRM 1.00.5Amps Maximum instantaneous I F=7.5A, T C=25°C-0.75forward voltage at I F=7.5A, T C=125°CV F 0.570.65Volts(NOTE2)I F=15A, T C=25°C0.84-I F=15A, T C=125°C0.72-Maximum instantaneous reverse current atrated DC blocking voltage T C=25°C I R0.10.5mA (NOTE 1)T C=125°C15.050.0Voltage rate of change (rated V R)dv/dt10,0001,000V/µs Maximum thermal resistance,(NOTE 3)RΘJC 3.0°C/W Operating junction temperature range T J-65 to +150°C Storage temperature range T STG-65 to +175°C NOTES:(1) 2.0µs, pulse width, f=1.0 KH Z(2) Pulse test: 300µs pulse width, 1% duty cycle(3) Thermal resistance from junction to case4/98TO-263AB11010025507510012515017500.10.20.30.40.50.60.70.80.9 1.01.1 1.20.010.1110500.1110100401001,0004,0000.010.11101000.11101000501001500246810204060801000.0010.010.111050FIG. 1 - FORWARD CURRENT DERATING CURVECASE TEMPERATURE, °CA V E R A G E F O R W A R D C U R R E N T ,A M P E R E SFIG. 2 - MAXIMUM NON-REPETITIVE PEAK FORWARDSURGE CURRENTNUMBER OF CYCLES AT 60 H ZP E A K F O R W A R D S U R G E C U R R E N T ,A M P E R E SFIG. 3 - TYPICAL INSTANTANEOUS FORWARDCHARACTERISTICSFIG. 4 - TYPICAL REVERSE CHARACTERISTICSI N S T A N T A N E O U S F O R W A R D C U R R E N T , A M P E R E SI N S T A N T A N E O U S R E V E R S E C U R R E N T , M I L L I A M P E R E SINSTANTANEOUS FORWARD VOLTAGE,VOLTSPERCENT OF RATED PEAK REVERSEVOLTAGE, %FIG. 5 - TYPICAL JUNCTION CAPACITANCEJ U N C T I O N C A P A C I T A N C E , p FREVERSE VOLTAGE, VOLTST J =T J max.8.3ms SINGLE HALF SINE-WAVE (JEDEC Method)T J =75°CT J =25°CT J =25°CT J =125°CPULSE WIDTH = 300µsT J =25°C f=1.0 MHz Vsig=50mVp-pRESISTIVE OR INDUCTIVE LOADT J =125°CFIG. 6 - TYPICAL TRANSIENT THERMAL IMPEDANCEt, PULSE DURATION, sec.T R A N S I E N T T H E R M A L I M P E D A N C E , °C /WMBR735 - MBR745MBR750 & MBR760MBRB735 - MBRB745MBRB750 & MBBR760MBRB735 - MBRB745MBRB750 & MBBR760MBRB735 - MBRB745MBRB750 & MBBR760RATINGS AND CHARACTERISTIC CURVES MBRB735 THRU MBRB760。

TH2515 仪器说明书

Ver 2.1目录Ver 2.0 (2)第1章仪器简介与开箱安装 (8)1.1仪器简介 (8)1.2开箱检查 (8)1.3电源连接 (8)1.4保险丝 (8)1.5环境 (8)1.6使用测试夹具 (9)1.7预热 (9)1.8仪器的其它特性 (9)第2章前面板说明及入门操作 (10)2.1前面板说明 (10)2.2后面板说明 (11)2.3显示区域的定义 (12)2.4按键及其相应的显示页面 (13)2.4.1测量主菜单按键【DISP】 (13)2.4.2系统设置主菜单按键【SETUP】 (13)2.5基本操作 (13)2.6开机 (14)第3章基本操作 (15)3.1<测量显示>页面 (15)3.1.1测试功能 (15)3.1.2测试量程 (16)3.1.3测试速度 (17)3.1.4文件管理 (17)3.1.5其他工具 (17)3.2<比较显示>页面 (18)3.2.1文件管理 (19)3.2.2工具 (19)3.2.3比较 (19)3.2.4比较模式和上下限、百分比误差设置 (19)3.3<档显示>页面 (19)3.4<统计显示>页面 (21)3.4.1边界模式和其相应值的设定 (21)3.4.2统计状态 (21)3.4.3统计分析参数说明 (21)3.4.4工具 (22)3.4.5文件 (22)3.5<测量设置>页面 (22)3.6<TC/Δt设置>页面 (24)3.6.1温度校正(Temperature Correction 简称TC) (25)3.6.2温度转换(temperature conversion 简称t ) (25)3.6.3温度传感器的类型 (26)3.6.4参数设定 (27)3.6.5文件 (27)3.7<档设置>页面 (27)3.7.1文件 (29)3.7.2工具 (29)第4章系统设置和文件管理 (30)4.1系统设置 (30)4.1.1触摸音 (30)4.1.2语言 (30)4.1.3口令 (31)4.1.4总线模式 (31)4.1.5波特率 (32)4.1.6总线地址 (32)4.1.7EOC信号 (32)4.1.8Err.OUT信号 (33)4.1.9电源频率 (34)4.1.10时间和日期设定 (34)4.2<文件管理>功能页面 (34)4.2.1存储/调用功能简介 (34)4.2.2U盘上的文件夹/文件结构 (35)4.2.3DHCP (39)4.2.4IP地址 (40)4.2.5子网掩码 (40)4.2.6网关 (40)4.2.7首选DNS、备用DNS (40)第5章性能指标 (41)5.1测量功能 (41)5.1.1测量参数及符号 (41)5.1.2测量组合 (41)5.1.3等效方式 (41)5.1.4量程 (41)5.1.5触发 (41)5.1.6测试端方式 (41)5.1.7测量中的各种时间的开销 (41)5.1.8平均 (42)5.1.9显示的位数 (42)5.2测试信号 (42)5.2.1量程电流 (42)5.2.2开路输出电压 (42)5.2.3测量显示最大范围 (42)5.3测量准确度 (43)5.3.2温度测量的准确度(Pt500) (44)5.3.3温度测量的准确度(模拟输入) (45)5.3.4温度修正系数K (45)第6章远程控制 (46)6.1RS232C接口说明 (46)6.2GPIB接口说明(选购件) (47)6.2.1GPIB接口功能 (49)6.2.2GPIB 地址 (49)6.2.3GPIB总线功能 (49)6.2.4可编程仪器命令标准(SCPI) (50)6.3LAN远程控制系统 (50)6.3.1通过浏览器访问TH2515 (52)6.3.2通过上位机软件访问TH2515 (52)6.4USBTMC远程控制系统 (53)6.4.1系统配置 (53)6.4.2安装驱动 (53)6.5USBVCOM虚拟串口 (54)6.5.1系统配置 (54)6.5.2安装驱动 (54)第7章RS232命令参考 (55)7.1SCPI系统命令 (55)7.1.1DISPlay子系统命令集 (55)7.1.2FUNCtion 子系统命令集 (56)7.1.3APERture子系统命令集 (61)7.1.4TRIGer子系统命令集 (61)7.1.5FETCh?子系统命令集 (63)7.1.6TEMPerature子系统命令集 (64)7.1.7COMParator子系统命令集 (66)7.1.8BIN子系统命令集 (69)7.1.9STA Tistics子系统命令集 (73)7.1.10IO子系统命令集 (76)7.1.11MEMory子系统命令集 (77)7.1.12SYSTem 子系统命令集 (78)7.1.13SCPI公用命令 (81)7.2MODBUS系统命令 (83)7.2.1MODBUS协议说明 (84)7.2.2公用指令操作说明 (85)7.2.3DISP指令操作说明 (86)7.2.4FUNC指令操作说明 (86)7.2.5APER指令操作说明 (87)7.2.6TRIG指令操作说明 (87)7.2.7FETC指令操作说明 (88)7.2.8TEMP指令操作说明 (88)7.2.10BIN指令操作说明 (90)7.2.11STA T指令操作说明 (93)7.2.12IO指令操作说明 (94)7.2.13SYST指令操作说明 (94)第8章Handler接口使用说明及程序升级方法 (99)第9章包装及保修 (103)9.1标志 (103)9.2包装 (103)9.3运输 (103)9.4贮存 (103)9.5保修 (103)本说明书所描述的可能并非仪器所有内容,同惠公司有权对本产品的性能、功能、内部结构、外观、附件、包装物等进行改进和提高而不作另行说明!由此引起的说明书与仪器不一致的困惑,可通过封面的地址与我公司进行联系。

RL251G-RL257G整流二极管中文资料

·端子: 镀锡轴向引线 Terminals: Plated axial leads ·极性: 色环端为负极 Polarity: Color band denotes cathode end ·安装位置: 任意 Mounting Position: Any

极限值和温度特性 TA = 25℃ 除非另有规定。 Maximum Ratings & Thermal Characteristics Ratings at 25℃ ambient temperature unless otherwise specified.

10

2 1

0.2

0.1

Tj = 25 °C

0.01 0.6 0.8 1.0 1.2 1.4 1.6

正向电压 VF(V) VF Instantaneous Forward Voltage (V)

浪涌特性曲线(最大值) MAXIMUM NON REPETITIVE PEAK FORWARD SURGE CURRENT

40

pF

大昌电子 DACHANG ELECTRONICS

正向电流 IF(A) IF Instantaneous Forward Current (A)

SIYU R

特性曲线 Characteristic Curves

正向特性曲线(典型值) TYPICAL FORWARD CHARACTERISTIC

V

VRMS

35

70 140 280 420 560 700

V

最大直流阻断电压 Maximum DC blocking voltage

最大正向平均整流电流 Maximum average forward rectified current

MBRB3045CT-1G;MBR3045STG;MBR3045ST;中文规格书,Datasheet资料

MBR3045ST,MBRB3045CT-1SWITCHMODE ™Power RectifierFeatures and Benefits•Dual Diode Construction — Terminals 1 and 3 May Be Connected for Parallel Operation at Full Rating •45 V Blocking V oltage •Low Forward V oltage Drop•175°C Operating Junction Temperature •Pb −Free Packages are AvailableApplications•Power Supply − Output Rectification •Power Management •InstrumentationMechanical Characteristics•Case: Epoxy, Molded•Weight (Approximately):1.9 Grams (TO −220AB)1.5 Grams (TO −262)•Finish: All External Surfaces Corrosion Resistant and Terminal Leads are Readily Solderable•Lead Temperature for Soldering Purposes:260°C Max. for 10 Seconds•Epoxy Meets UL 94 V −0 @ 0.125 inMAXIMUM RATINGSRatingSymbol Value Unit Peak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRM V RWM V R 45VAverage Rectified Current Per Device (T C = 130°C)Per DiodeI F(AV)3015A Peak Repetitive Forward Current, per Diode (Square Wave, V R = 45 V, 20 kHz)I FRM 30A Non −Repetitive Peak Surge Current (Surge Applied at Rated Load Conditions,Halfwave, Single Phase, 60 Hz)IFSM150APeak Repetitive Reverse Current, per Diode (2.0 m s, 1.0 kHz)I RRM 2.0A Storage Temperature RangeT stg −65 to +175°C Operating Junction Temperature (Note 1)T J −65 to +175°C Peak Surge Junction Temperature (Forward Current Applied)T J(pk)175°CVoltage Rate of Change (Rated V R )dv/dt10,000V/m sStresses exceeding Maximum Ratings may damage the device. MaximumRatings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.The heat generated must be less than the thermal conductivity from Junction −to −Ambient: dP D /dT J < 1/R q JA .TO −220AB CASE 221A STYLE 6SCHOTTKY BARRIERRECTIFIER 30 AMPERES 45 VOLTS312, 4MARKING DIAGRAMSA = Assembly Location Y = YearWW = Work WeekAKA = Polarity Designator G = Pb −Free DeviceI 2PAK (TO −262)CASE 418D PLASTICAYWW B3045CTG AKASee detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.ORDERING INFORMATIONTHERMAL CHARACTERISTICS (Per Diode)CharacteristicSymbol Value Unit Thermal Resistance, Junction to CaseR θJC1.5°C/WELECTRICAL CHARACTERISTICS (Per Diode)Instantaneous Forward Voltage (Note 2)(i F = 15 Amp, T C = 25°C)(i F = 15 Amp, T C = 125°C)(i F = 30 Amp, T C = 25°C)(i F = 30 Amp, T C = 125°C)v F0.620.570.760.72VoltsInstantaneous Reverse Current (Note 2)(V R = 45 Volts, T C = 25°C)(V R = 45 Volts, T C = 125°C)I R0.240mA2Pulse Test: Pulse Width = 300 μs, Duty Cycle ≤ 2.0%Figure 1. Typical Forward VoltageFigure 2. Maximum Reverse Currentv F , INSTANTANEOUS FORWARD VOLTAGE (VOLTS)100010V R , REVERSE VOLTAGE (VOLTS)0.20.040.02i F , I N S T A N T A N E O U S F O R W A R D C U R R E N T (A M P S )I 1.00.10.41.00.1, R E V E R S E C U R R E N T (m A )R 4.02.01020100402001000.01Figure 3. Typical Reverse Currentv F , MAXIMUM FORWARD VOLTAGE (VOLTS)100010i F , M A X I M U M F O R W A R D C U R R E N T (A M P S )1.00.1100Figure 4. Current Derating, Case Figure 5. Current Derating, AmbientFigure 6. Forward Power Dissipation 110T C , CASE TEMPERATURE (°C)208.04.00T A , AMBIENT TEMPERATURE (°C)2024168.0040I F , AVERAGE FORWARD CURRENT (AMPS)3216128.04.00I I F (A V ), A V E R A G E F O R W A R D C U R R E N T (A M P S )1201301401706080180P 28, A V E R A G E F O R W A R D C U R R E N T (A M P S )F (A V )202416122420124.0100120140, A V E R A G E P O W E R D I S S I P A T I O N (W A T T S )F (A V )Figure 7. Capacitance0V R , REVERSE VOLTAGE (V)100010103040C , C A P A C I T A N C E (p F )100501000020150160160ORDERING INFORMATIONDevicePackage Shipping MBR3045ST TO −22050 Units/Rail MBR3045STG TO −220(Pb −Free)50 Units/Rail MBRB3045CT −1TO −26250 Units/Rail MBRB3045CT −1GTO −262(Pb −Free)50 Units/RailTO −220CASE 221A −09ISSUE AFNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION Z DEFINES A ZONE WHERE ALL BODY AND LEAD IRREGULARITIES ARE ALLOWED.STYLE 6:PIN 1.ANODE 2.CATHODE 3.ANODE 4.CATHODEDIM MIN MAX MIN MAX MILLIMETERS INCHES A 0.5700.62014.4815.75B 0.3800.4059.6610.28C 0.1600.190 4.07 4.82D 0.0250.0350.640.88F 0.1420.161 3.61 4.09G 0.0950.105 2.42 2.66H 0.1100.155 2.80 3.93J 0.0140.0250.360.64K 0.5000.56212.7014.27L 0.0450.060 1.15 1.52N 0.1900.210 4.83 5.33Q 0.1000.1202.543.04R 0.0800.110 2.04 2.79S 0.0450.0551.15 1.39T 0.2350.255 5.97 6.47U 0.0000.0500.00 1.27V 0.045--- 1.15---Z---0.080--- 2.04FSEATINGPLANEI 2PAK (TO −262)CASE 418D −01ISSUE DNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.D DIM MIN MAX MIN MAX MILLIMETERSINCHES A 0.3350.3808.519.65B 0.3800.4069.6510.31C 0.1600.185 4.06 4.70D 0.0260.0350.660.89E 0.0450.055 1.14 1.40G 0.100 BSC 2.54 BSC H 0.0940.110 2.39 2.79J 0.0130.0250.330.64S 0.390 REF 9.90 REF V 0.0450.070 1.14 1.78W0.5220.55113.2514.00MBM 0.13 (0.005)T F 0.122 REF 3.10 REF K 0.5000.56212.7014.27ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONSWITCHMODE is a trademark of Semiconductor Components Industries, LLC.分销商库存信息:ONSEMIMBRB3045CT-1G MBR3045STG MBR3045ST。

24G15N 用户手册说明书

24G15N安全 (1)标志惯例 (1)电源 (2)安装 (3)清洁 (4)其它 (5)设置 (6)物品清单 (6)安装支架和底座 (7)调整视角 (8)连接显示器 (9)Adaptive-Sync功能 (10)HDR (11)调节显示器 (12)热键 (12)OSD设定 (13)Luminance(明亮度) (14)Color Setup(颜色设置) (15)Picture Boost(窗口增亮) (16)OSD Setup(OSD设置) (17)Game Setting(游戏设置) (18)Extra(其它) (19)Exit(退出) (20)LED指示灯 (21)故障排除 (22)规格 (23)主要规格 (23)预设显示模式 (24)引脚分配 (25)即插即用版权说明.................................................................................................................................................................. ..................................................................................................................................................................2626安全标志惯例以下小节描述此文档中使用的标志惯例。

注释、注意和警告在本指南中,文本块可能带有图标并且以粗体或斜体打印。

这些文本块是注释、注意和警告,如下所示:注释:注意事项指示帮助你更好地使用你的计算机系统的重要信息。

注意:“注意”表示潜在的硬件损坏或数据丢失,并告诉您如何避免出现问题。

关于肖特基MBR系列

关于肖特基MBR系列:为什么要取名为“MBR”?M:是以最早MOTOROLA的命名,取MB:Bridge 桥,整流桥R:Rectifier,整流器SCHOTTKY:肖特基SCHOTTKY RECTIFIER DIODES:肖特基整流二极管。

肖特基二极管也称肖特基势垒二极管(简称SBD),国内厂家也有叫做“SB1045CT、SR10100、SL....、BL....、1、肖特基它是一种低功耗、超高速半导体器件,广泛应用于开关电源、变频器、驱动器等电路,作高频、低压、大电流整流二极管、续流二极管、保护二极管使用,或在微波通信等电路中作整流二极管、小信号检波二极管使用。

2、肖特基二极管的结构肖特基二极管在结构原理上与PN结二极管有很大区别,它的内部是由阳极金属(用钼或铝等材料制成的阻挡层)、二氧化硅(SiO2)电场消除材料、N 外延层(砷材料)、N型硅基片、N阴极层及阴极金属等构成。

在N型基片和阳极金属之间形成肖特基势垒。

当在肖特基势垒两端加上正向偏压(阳极金属接电源正极,N型基片接电源负极)时,肖特基势垒层变窄,其内阻变小;反之,若在肖特基势垒两端加上反向偏压时,肖特基势垒层则变宽,其内阻变大。

肖特基二极管分为有引线和表面安装(贴片式)两种封装形式。

采用有引线式封装的肖特基二极管通常作为高频大电流整流二极管、续流二极管或保护二极管使用。

它有单管式和对管(双二极管)式两种封装形式。

肖特基对管又有共阴(两管的负极相连)、共阳(两管的正极相连)和串联(一只二极管的正极接另一只二极管的负极)三种管脚引出方式。

采用表面封装的肖特基二极管有单管型、双管型和三管型等多种封装形式,有A~19种管脚引出方式。

3、常用的肖特基二极管常用的有引线式肖特基二极管有1N5817、1N5819、MBR1045、MBR20200等型号。

常用的表面封装肖特基二极管,SCHOTTKY取第一个字母“S”,片式表面贴片SMD取第一个字母“S”,即为SS,如:SS12、SS14....电流最小的肖特基是BAT42(0.2A);BAT54、BAT54A、BAT54C(0.3A);电流最大的肖特基是440A,如:440CMQ030、444CNQ045;超过440A的必定是模块。

肖特基二极管MBR系列命名规则

肖特基二极管MBR系列命名规则肖特基势垒二极管(Schottky Barrier Diode)Schottky Barrier Diode:肖特基势垒二极管简称:SBDSchottky:肖特基(发明人名称)Barrier:势垒SB:即为肖特基势垒二极管MBR、SR、SL、SB、SBT、STP都是常见的半导体公司对肖特基产品的型号命名。

各厂家命名有不同。

肖特基二极管也称肖特基势垒二极管,国内厂家也有叫做"SB1045CT、SR10100、SL…、BL…看懂肖特基二极管MBR系列:M:是以最早MOTOROLA的命名,取MB:Bridge桥;Barrier:势垒R:Rectifier,整流器"MBR"意为整流器件SCHOTTKY RECTIFIER DIODES:肖特基整流二极管例1:MBR10100CTM:MOTOROLA缩写MB:Barrier缩写BR:Rectifier缩写R10:正向电流10A100:反向耐压100VC:表示TO-220AB封装,常指半塑封(铁封)。

T:表示管装例2:MBR6045PTM:MOTOROLA缩写MB:Barrier缩写BR:Rectifier缩写R60:正向电流60A45:反向耐压45VP:表示TO-247(3P)封装T:表示管装例3:MBR20200FCTM:MOTOROLA缩写MB:Barrier缩写BR:Rectifier缩写R20:正向电流20A200:反向耐压200VF:表示ITO-220AB(TO-220F)全塑封T:表示管装肖特基二极管有哪些主要参数呢?IF(IO):正向电流(A)VRRM:反向耐压(V)IFSM:峰值瞬态浪涌电流(A)IF:测试电流(A)VF:正向压降(V)IR:反向漏电流(UA)TRR:反向快恢复时间(NS)肖特基二极管常见选型型号:。

MBR和分区表DPT

MBR和分区表DPT零磁道,MBR和分区表DPT:零磁道处于硬盘上一个非常重要的位置,硬盘的主引导记录区(MBR)就在这个位置上。

零磁道一旦受损,将使硬盘的主引导程序和分区表信息遭到严重破坏,从而导致硬盘无法自举。

MBR:当通过Fdisk或其他分区工具对硬盘进行分区时,分区软件会在硬盘0柱面0磁头1扇区建立MBR(Main Boot Record),即为主引导记录区,位于整个硬盘的第一个扇区,在总共512字节的主引导扇区中,主引导程序只占用了其中的446个字节,64个字节交给了DPT(DiskPartion Table硬盘分区表),最后两个字节(55 AA)属于分区结束标志。

主引导程序的作用就是检查分区表是否正确以及确定哪个分区为引导分区,并在程序结束时把该分区的启动程序调入内存加以执行。

DPT:分区表DPT(Disk Partion Table),把硬盘空间划分为几个独立的连续的存储空间,也就是分区。

分区表DPT则以80H或00H为开始标志,以55AAH为结束标志。

分区表决定了硬盘中的分区数量,每个分区的起始及终止扇区、大小以及是否为活动分区等。

通过破坏DPT,即可轻易地损毁硬盘分区信息。

分区表分为主分区表和扩展分区表。

主分区表位于硬盘MBR的后部。

从1BEH字节开始,共占用64个字节,包含四个分区表项,这也就是为什么一个磁盘的主分区和扩展分区之和总共只能有四个的原因。

每个分区表项的长度为16个字节,它包含一个分区的引导标志、系统标志、起始和结尾的柱面号、扇区号、磁头号以及本分区前面的扇区数和本分区所占用的扇区数。

其中”引导标志”表明此分区是否可引导,即是否活动分区。

当引导标志为”80″时,此分区为活动分区;”系统标志”决定了该分区的类型,如”06″为DOSFAT16分区,”0b”为DOSFAT32分,”63″为UNIX分区等;起始和结尾的柱面号、扇区号、磁头号指明了该分区的起始和终止位置。

分区表项的16个字节分配如下:第1字节:引导标志第2字节:起始磁头第3字节:低6位为起始扇区,高2位与第4字节为起始柱面第4字节:起始柱面的低8位第5字节:系统标志第6字节:终止磁头第7字节:低6位为终止扇区,高2位与第8字节为终止柱面第8字节:终止柱面的低8位第9-12字节:该分区前的扇区数目第13-16字节:该分区占用的扇区数目扩展分区作为一个主分区占用了主分区表的一个表项。

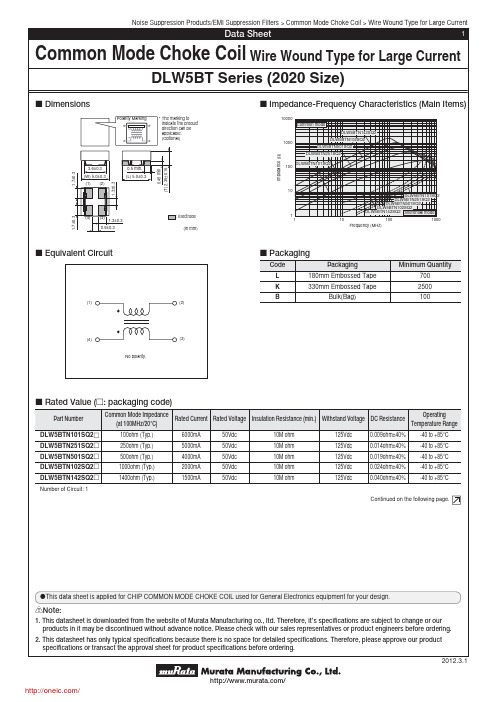

DLW5BTN142SQ2L;DLW5BTN102SQ2L;DLW5BTN101SQ2L;DLW5BTN251SQ2L;DLW5BTN501SQ2L;中文规格书,Datasheet资料

Operating

(at 100MHz/20°C)

Temperature Range

DLW5BTN101SQ2p DLW5BTN251SQ2p DLW5BTN501SQ2p DLW5BTN102SQ2p DLW5BTN142SQ2p Number of Circuit: 1

100ohm (Typ.) 250ohm (Typ.) 500ohm (Typ.) 1000ohm (Typ.) 1400ohm (Typ.)

Noise Suppression Products/EMI Suppression Filters > Common Mode Choke Coil > Wire Wound Type for Large Current

Data Sheet

1

Common Mode Choke Coil Wire Wound Type for Large Current

2012.3.1

/

/

Noise Suppression Products/EMI Suppression Filters > Common Mode Choke Coil > Wire Wound Type for Large Current

0.5 min. (L) 5.0±0.3

0.45 min. (T) 2.35±0.15

1.3±0.3

1.7±0.3

(4) (3) 1.3±0.3 0.9±0.3

: Electrode (in mm)

c Impedance-Frequency Characteristics (Main Items)

10000 Common mode

Notice Solderability of Tin plating termination chip might be deteriorated when low temperature soldering profile where peak solder temperature is below the Tin melting point is used. Please confirm the solderability of Tin plating termination chip before use.

常用二极管型号及参数大全

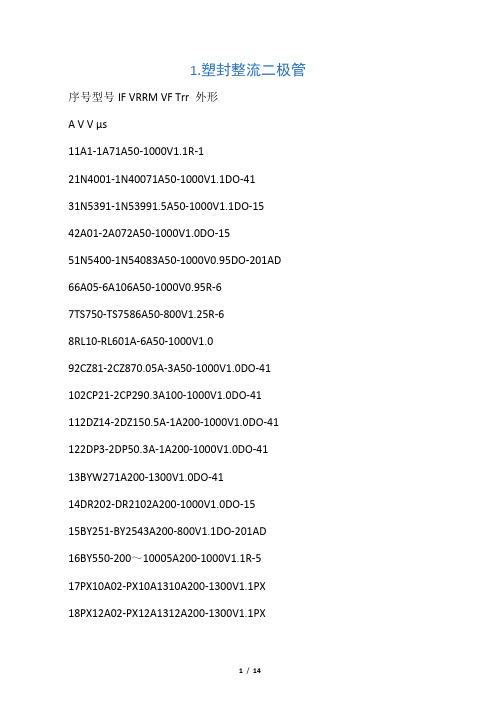

1.塑封整流二极管序号型号IF VRRM VF Trr 外形A V V μs11A1-1A71A50-1000V1.1R-121N4001-1N40071A50-1000V1.1DO-4131N5391-1N53991.5A50-1000V1.1DO-1542A01-2A072A50-1000V1.0DO-1551N5400-1N54083A50-1000V0.95DO-201AD66A05-6A106A50-1000V0.95R-67TS750-TS7586A50-800V1.25R-68RL10-RL601A-6A50-1000V1.092CZ81-2CZ870.05A-3A50-1000V1.0DO-41102CP21-2CP290.3A100-1000V1.0DO-41112DZ14-2DZ150.5A-1A200-1000V1.0DO-41 122DP3-2DP50.3A-1A200-1000V1.0DO-4113BYW271A200-1300V1.0DO-4114DR202-DR2102A200-1000V1.0DO-1515BY251-BY2543A200-800V1.1DO-201AD16BY550-200~10005A200-1000V1.1R-517PX10A02-PX10A1310A200-1300V1.1PX18PX12A02-PX12A1312A200-1300V1.1PX19PX15A02-PX15A1315A200-1300V1.1PX20ERA15-02~131A200-1300V1.0R-121ERB12-02~131A200-1300V1.0DO-1522ERC05-02~131.2A200-1300V1.0DO-1523ERC04-02~131.5A200-1300V1.0DO-1524ERD03-02~133A200-1300V1.0DO-201AD25EM1-EM21A-1.2A200-1000V0.97DO-1526RM1Z-RM1C 1A200-1000V0.95DO-1527RM2Z-RM2C 1.2A200-1000V0.95DO-1528RM11Z-RM11C 1.5A200-1000V0.95DO-1529RM3Z-RM3C 2.5A200-1000V0.97DO-201AD 30RM4Z-RM4C 3A200-1000V0.97DO-201AD2.快恢复塑封整流二极管序号型号IF VRRM VF Trr 外形A V V μs(1)快恢复塑封整流二极管11F1-1F71A50-1000V1.30.15-0.5R-12FR10-FR601A-6A50-1000V1.30.15-0.531N4933-1N49371A50-600V1.20.2DO-4141N4942-1N49481A200-1000V1.30.15-0.5DO-41 5BA157-BA1591A400-1000V1.30.15-0.25DO-416MR850-MR8583A100-800V1.30.2DO-201AD7EU1-EU20.25A-1A100-1000V1.30.4DO-41820DF1-20DF102A100-1000V1.30.2DO-15930DF1-30DF103A100-1000V1.30.2DO-201AD 10RU1-RU40.25A-3A100-1000V1.30.411ERA22-02~100.5A200-1000V1.30.4R-112ERA18-02~100.8A200-1000V1.30.4R-113ERB43-02~100.5A200-1000V1.30.4DO-4114ERB44-02~101A200-1000V1.30.4DO-1515ERC18-02~101.2A200-1000V1.30.4DO-1516ERD28-02~101.5A200-1000V1.30.4DO-201AD 17ERD29-02~102.5A200-1000V1.30.4DO-201AD 18ERD32-02~103A200-1000V1.30.4DO-201AD 19ERD09-13~153A1300-1500V1.50.6R-5(2)SK、2CG系列快恢复整流二极管1SK1-02~301.5A200-3000V1.3-40.5-1DO-152SK2-02~301A200-3000V1.3-40.5-1DO-413SK3-02~302A200-3000V1.3-40.5-1DO-154SK4-02~300.5A300-3000V1.3-40.5-1DO-4152CG04-2CG300.2A300-3000V1.3-40.5-1DO-41 (3)快恢复塑封阻尼二极管12CN1-2CN1C1A200-1200V1.32DO-4122CN2D-2CN2M0.5A200-1000V1.32DO-4132CN3D-2CN3M1A200-1000V1.36DO-4142CN4D-2CN4M1.5A200-1000V1.30.8DO-15 52CN5D-2CN5M1.5A200-1000V1.01DO-1562CN6D-2CN6M1A200-1000V1.36DO-4172CN12D-2CN12M3A200-1000V1.31DO-201AD 8RH1Z-RH1C 0.6A200-1000V1.34DO-419TVR4J-TVR4N 1.2A600-1000V1.220DO-15 3.超高频塑封二极管1ERA34-100.1A1000V30.15R-12ERA32-02~101A200-1000V1.30.1DO-413ERB32-02~101.2A200-1000V1.30.1DO-154ERC30-02~101.5A200-1000V1.30.1DO-155ERC32-02~103A200-1000V1.30.1DO-201AD 6EG01E-EG01C 0.5A200-1000V20.1DO-417EG1E-EG1C 1A200-1000V1.80.1DO-418RG10Z-RG10C 1.2A200-1000V20.1DO-159RG2Z-RG2C 1.5A200-1000V1.80.1DO-1510RG4Z-RG4C 3A200-1000V20.1D0-201AD4.超快恢复塑封二极管序号型号IF VRRM VF Trr 外形A V V ns(1)超快恢复塑封二极管1SF10-SF501-5A50-1000V0.95-1.7352SF80-SF1608-16A50-600V0.95-1.435TO-2203EGP10-EGP501-5A50-200V1.1354ERC38~04-ERC38~101A400-1000V1.750DO-415RL2-RL2C 2A400-1000V1.750DO-156RL3-RL3C 3A400-1000V1.750DO-201AD71H1-1H81A50-1000V1.1-1.750-75R-18HER10-HER601-6A50-1000V1.1-1.750-759HER80-HER1608-6A50-1000V1.1-1.750-75TO-22010UF10-UF601-6A50-1000V1.1-1.750-7511EL1Z-EL11.5A200-350V1.350DO-15(2)MUR超快恢复整流二极管1MUR120-MUR11201A200-1200V0.95-1.535-50DO-412MUR420-MUR41204A200-1200V0.95-1.635-75DO-201AD 3MUR820-MUR81208A200-1200V1.3-2.135-75TO-220AC4MUR1020-MUR1012010A200-1200V1.3-2.135-75TO-220AC 5MUR1520-MUR1512015A200-1200V1.3-2.135-75TO-220AC 6MUR2020-MUR2012020A200-1200V1.3-2.135-75TO-220AB7MUR3020-MUR3012030A200-1200V1.3-2.135-75TO-247AD 8MUR6020-MUR6012060A200-1200V1.3-2.135-75TO-247AD (3)RHRP、RHRG超快恢复二极管1RHRP820-RHRP81208A200-1200V2.1-3.235-70TO-220AC2RHRP1520-RHRP1512015A200-1200V2.1-3.240-75TO-220AC 3RHRP3020-RHRP3012030A200-1200V2.1-3.245-75TO-220AC 4RHRG3020-RHRG3012030A200-1200V2.1-3.245-75TO-247AC 5RHRG5020-RHRG5012050A200-1200V2.1-3.250-100TO-247AC 6RHRG6020-RHRG6012060A200-1200V2.1-3.245-75TO-247AD (4)BYV29~79、BYT28~79超快恢复二极管1BYW29-100~2008A100-200V1.125TO-220AC2BYV29-300~5009A300-500V1.2560TO-220AC3BYQ28 -100~20010A100-200V1.120TO-220AB4BYT28-300~50010A300-500V1.460TO-220AB5BYV79-100~20014A100-200V1.330TO-220AC6BYT79-300~50014A300-500V1.460TO-220AC7BYV32-100~20020A100-200V1.125TO-220AB8BYV34-300~50020A300-500V1.160TO-220AB9BYV42-100~20030A100-200V1.128TO-220AB10BYV44-300~50030A300-500V1.2560TO-220AB5.xx整流二极管序号型号IF VRRM VF 外形A V V(1)xx塑封整流二极管11N5817-1N58191A20-40V0.45-0.6DO-4121N5820-1N58223A20-40V0.45-0.6DO-201AD3SRT12-SRT1001A20-100V 0.55-0.85R-14SR10-SR501-5A20-100V0.55-0.855SB120-SB1B01A20-100V0.55-0.85DO-416SB220-SB2B02A20-100V0.55-0.85DO-157SB320-SB3B03A20-100V0.55-0.85DO-201AD8SB520-SB5B05A20-100V0.55-0.85D0-201AD9ERA81-002~0091A20-90V0.55-0.9DO-4110ERB81-002~0092A20-90V0.55-0.9DO-1511ERC81-002~0093A20-90V0.55-0.9DO201AD 12EK03-EK091A20-90V0.55-0.81DO-4113EK13-EK191.5A20-90V0.55-0.81DO-1514EK33-EK392A20-90V0.55-0.81DO-1515EK43-EK493A20-90V0.55-0.81DO-201AD(2)MBR、PBYR系列大电流肖特基整流二极管1MBR1020-MBR106010A20-60V0.57-0.8TO-220AC 2MBR1620-MBR166016A20-60V0.57-0.8TO-220AC3MBR2020CT-2060CT 20A20-60V0.57-0.8TO-220AB4MBR2520CT-2560CT 25A20-60V0.57-0.8TO-220AB5MBR3020PT-3060PT 30A20-60V0.57-0.8TO-247AD6MBR4020PT-4060PT 40A20-60V0.57-0.8TO-247AD7MBR6020PT-6060PT 60A20-60V0.57-0.8TO-247AD8PBYR735-7457A20-45V0.56-0.66TO-220AC9PBYR1020-106010A20-60V0.56-0.77TO-220AC10PBYR1635-166016A20-60V0.56-0.77TO-220AC11PBYR2020CT-2045CT 20A20-45V0.56-0.65TO-220AB 12PBYR3035PT-3060PT 30A20-60V0.56-0.77TO-247AD 6.玻球快恢复二极管、玻钝芯片塑封二极管序号型号IF VRRM VF Trr 外形A V V ns(1)BYV、BYT、BYM、BYW玻球快恢复二极管1BYV26A-BYV26E 1A200-1000V1.50.03DO-204AP2BYV12-BYV161.5A100-1000V1.50.3DO-204AP3BYV96A-BYV96E 1.5A100-1000V1.50.3DO-204AP4BYV27-50~2002A50-200V1.10.025DO-204AP5BYV28-50~2003.5A50-200V1.10.03G36BYT52A-BYT52M 1A50-1000V1.30.2DO-204AP7BYT54A-BYT54M 1.25A50-1000V1.50.1DO-204AP8BYT53A-BYT53M 1.5A50-1000V1.10.05DO-204AP9BYT56A-BYT56M 3A200-1000V1.40.1G310BYM26A-BYM26M 2.3A200-1000V1.50.03G311BYM36A-BYM36M 3A200-1000V1.10.15G312BYW32-BYW382A200-1000V1.10.2DO-204AP13BYW52-BYW562A200-1000V1.14DO-204AP14BYW72-BYW763A200-600V1.10.2G315BYW96A-BYW96E 3A200-1000V1.50.2G316BY2283A1500V1.520G3(2)GP、RGP系列玻钝芯片塑封二极管17GP10-GP301-3A50-1000V1.118RGP01-10~RGP01-200.1A1000-2000V20.2-0.5DO-41 19RGP05-10~RGP05-200.5A1000-2000V20.2-0.5DO-41 20RGP10-RGP601-6A50-2000V1.30.15-0.57.PD、TR、PR系列高压塑封二极管1PD0112-PD01600.1A1200-6000V1.2-5DO-412PD0312-PD03600.3A1200-6000V1.2-5DO-153PD0512-PD05600.5A1200-6000V1.2-5DO-154PD112-PD1301A1200-3000V1.2-4DO-155PD1512-PD15301.5A1200-3000V1.2-4DO-156PD212-PD2202A1200-2000V1.2-2.5DO-201AD7PD312-PD3203A1200-2000V1.2-2.5DO-201AD8PD612-PD6206A1200-2000V1.2-2.5R-69TR0112-TR01600.1A1200-6000V1.5-80.5-0.8DO-41 10TR0312-TR03600.3A1200-6000V1.5-80.5-0.8DO-15 11TR0512-TR05600.5A1200-6000V1.5-80.5-0.8DO-15 12TR112-TR1301A1200-3000V1.5-60.5-0.8DO-1513TR1512-TR15301.5A1200-3000V1.5-60.5-0.8DO-15 14TR212-TR2202A1200-2000V1.5-2.70.5-0.8DO-201AD 15TR312-TR3203A1200-2000V1.5-2.70.5-0.7DO-201AD 16TR612-TR6206A1200-2000V1.5-2.70.5-0.8R-617PR01-PR10.1-1A1200-3000V1.5-40.1-0.5DO-1518RC20.3A2000V30.5DO-4119RU4D-RP3F 1.5A-2A1300-1500V1.50.3DO-201AD 8.稳压二极管序号名称型号PZM VZW V稳压二极管1BZX550.5W2.4V-47V21N5985B~1N6031B0.5W2.4V-200V31N4728~1N47641W3.3V-100V41N5911B~1N5956B1.5W2.7V-200V52CW37-2.4~360.5W2.4V-36V62CW51-2CW680.25W3V-28.5V72CW101-2CW1211W3V-37.5V82DW50-2DW641W41V-190V92DW80-2DW1903W41V-190V102DW110-2DW15110W4.3V-470V112DW170-2DW20250W4.3V-200V12温度补偿稳压二极管2DW230-2DW2360.2W5.8V-6.6V 9.高速开关二极管序号型号IC VRM Trr 外形mA V ns11N4148150100V4DO-3521N4149-1N415415035-100V2-4DO-3531N4446-1N445415040-100V1-4DO-3541N91475100V4DO-355BAV17-BAV2125025-250V50DO-356BAW75-BAW7630035-75V4DO-3572CK70-2CK7910-28020-60V3-10DO-3582CK80-2CK8510-30020-60V5-10DO-3591S1553-1S155510070-35V3DO-35101S2471-1S2473130-11090-40V3DO-35几种常用二极管的特点1.整流二极管整流二极管结构主要是平面接触型,其特点是允许通过的电流比较大,反向击穿电压比较高,但PN结电容比较大,一般广泛应用于处理频率不高的电路中。

MBRB1545CT中文资料

RθJC RθJA

2.0 50

°C/W

Designer’s and SWITCHMODE are trademarks of Motorola, Inc. Thermal Clad is a trademark of the Bergquist Company

Preferred devices are Motorola recommended choices for future use and best overall value.

元器件交易网

MBRB1545CT

INFORMATION FOR USING THE D2PAK SURFACE MOUNT PACKAGE

MINIMUM RECOMMENDED FOOTPRINTS FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection interface

元器件交易网

MOTOROLA

Designer's

SEMICONDUCTOR TECHNICAL DATA

Order this document by MBRB1545CT/D

™ Data Sheet SWITCHMODE™ Power

D2PAK Surface Mount Power Package

Rectifier

MBRB1545CT

MX25L512中文资料

MX25L512512K-BIT [x 1] CMOS SERIAL FLASH FEATURESGENERAL• Serial Peripheral Interface (SPI) compatible -- Mode 0 and Mode 3• 524,288 x 1 bit structure• 16 Equal Sectors with 4K byte each- Any Sector can be erased individually• S ingle Power Supply Operation- 2.7 to 3.6 volt for read, erase, and program operations• L atch-up protected to 100mA from -1V to Vcc +1VPERFORMANCE• H igh Performance- Fast access time: 85MHz serial clock (15pF + 1TTL Load) and 66MHz serial clock (30pF + 1TTL Load)- Fast program time: 1.4ms(typ.) and 5ms(max.)/page (256-byte per page)- Fast erase time: 60ms(typ.) and 120ms(max.)/sector (4K-byte per sector) ; 1s(typ.) and 2s(max.)/chip(512Kb)• L ow Power Consumption- Low active read current: 12mA(max.) at 85MHz, 8mA(max.) at 66MHz and 4mA(max.) at 33MHz- Low active programming current: 15mA (max.)- Low active erase current: 15mA (max.)- Low standby current: 10uA (max.)- Deep power-down mode 1uA (typical)• M inimum 100,000 erase/program cyclesSOFTWARE FEATURES• Input Data Format- 1-byte Command code• Block Lock protection- The BP0~BP1 status bit defines the size of the area to be software protected against Program and Erase in-structions.• Auto Erase and Auto Program Algorithm- Automatically erases and verifies data at selected sector- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)• Status Register Feature• Electronic Identification- JEDEC 2-byte Device ID- RES command, 1-byte Device IDHARDWARE FEATURES• SCLK Input- Serial clock input• SI Input- Serial Data Input• SO Output- Serial Data Output• WP# pin- Hardware write protection• HOLD# pin- pause the chip without diselecting the chip• PACKAGE- 8-pin SOP (150mil)- 8-USON (2x3mm)- All Pb-free devices are RoHS CompliantGENERAL DESCRIPTIONMX25L512 is a CMOS 524,288 bit serial Flash memory, which is configured as 65,536 x 8 internally. MX25L512 features a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). SPI access to the device is enabled by CS# input.MX25L512 provide sequential read operation on whole chip.After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the spec-ified page or sector/block locations will be executed. Program command is executed on page (256 bytes) basis, and erase command is executes on chip or sector (4K-bytes).To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 10uA DC cur-rent.The MX25L512 utilize MXIC's proprietary memory cell, which reliably stores memory contents even after 100,000 program and erase cycles.PIN CONFIGURATIONSSYMBOL DESCRIPTION CS#Chip SelectSI Serial Data Input SO Serial Data Output SCLK Clock InputHOLD#Hold, to pause the device without deselecting the device WP#Write ProtectionVCC + 3.3V Power Supply GNDGroundPIN DESCRIPTION8-PIN SOP (150mil)CS#SO WP#GND VCC HOLD#SCLK SI8-LAND USON (2x3mm)CS#SO WP#GND VCC HOLD#SCLK SIBLOCK DIAGRAMDATA PROTECTIONMX25L512 is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state ma-chine in the standby mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.• Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.• Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:- Power-up- Write Disable (WRDI) command completion- Write Status Register (WRSR) command completion- Page Program (PP) command completion- Sector Erase (SE) command completion- Block Erase (BE) command completion- Chip Erase (CE) command completion• Software Protection Mode (SPM): by using BP0-BP1 bits to set the part of Flash protected from data change.• Hardware Protection Mode (HPM): by using WP# going low to protect the BP0-BP1 bits and SRWD bit from data change.• Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Sig-nature command (RES).Table 1. Protected Area SizesStatus bitProtect level 512b BP1 BP00 0 0 (none) None 0 1 1 (All)All 1 0 2 (All)All 113 (All)AllHOLD FEATUREHOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Se-rial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 1.The Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.Figure 1. Hold Condition OperationTable 2. COMMAND DEFINITION(1) ADD=00H will output the manufacturer's ID first and ADD=01H will output device ID first.(2) BE command may erase whole 512Kb chip.(3) It is not recommended to adopt any other code which is not in the above command definition table.COMMAND (byte)WREN (write enable)WRDI (write disable)RDID (readidentification)RDSR (read status register)WRSR (write status register)READ(read data)Fast Read(fast readdata)1st 06 (hex)04 (hex)9F (hex)05 (hex)01 (hex)03 (hex)0B (hex)2nd AD1AD13rd AD2AD24th AD3AD35th xActionsets the (WEL) write enable latch bit resets the (WEL) write enable latchbit outputs manufacturer ID and 2-byte device IDto read out the status register to write new values to the status register n bytes read out until CS# goes highCOMMAND (byte)SE(Sector Erase)BE (2)(Block Erase)CE (Chip Erase)PP(Page Program)DP(Deep Power Down) RDP(Release from Deep Power-down) RES (ReadElectronicID)REMS (ReadElectronicManufacturer& Device ID)1st 20 (hex)52 or D8 (hex)60 or C7 (hex)02 (hex) B9 (hex)AB (hex)AB (hex)90 (hex)2nd AD1AD1AD1x x 3rd AD2AD2AD2x x 4th AD3AD3AD3xADD(1)5th ActionOutput the manufacturer ID and deviceIDDEVICE OPERATION1. Before a command is issued, status register should be checked to ensure device is ready for the intended op-eration.2. When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby modeuntil next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.3. When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next CS# rising edge.4. Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The difference of SPI mode 0 and mode 3 is shown as Figure 2.Figure 2. SPI Modes SupportedSCLKMSBCPHA shift inshift outSI 01CPOL(Serial mode 0)(Serial mode 3)1SO SCLKMSB5. For the following instructions: RDID, RDSR, READ, FAST_READ, RES and REMS the shifted-in instruction se-quence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP , RDP and DP the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.6. During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglect-ed and not affect the current operation of Write Status Register, Program, Erase. Table 3. Memory OrganizationNote:CPOL indicates clock polarity of SPI master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which SPI mode is supported.Sector Address Range1500F000h 00FFFFh:::3003000h 003FFFh 2002000h 002FFFh 1001000h 001FFFh 0000000h 000FFFhCOMMAND DESCRIPTION(1) Write Enable (WREN)The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN in-struction setting the WEL bit.The sequence of issuing WREN instruction is: CS# goes low-> sending WREN instruction code-> CS# goes high. (see Figure 11)(2) Write Disable (WRDI)The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.The sequence of issuing WRDI instruction is: CS# goes low-> sending WRDI instruction code-> CS# goes high. (see Figure 12)The WEL bit is reset by following situations:- Power-up- Write Disable (WRDI) instruction completion- Write Status Register (WRSR) instruction completion- Page Program (PP) instruction completion- Sector Erase (SE) instruction completion- Block Erase (BE) instruction completion- Chip Erase (CE) instruction completion(3) Read Identification (RDID)RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manu-facturer ID is C2(hex), the memory type ID is 20(hex) as the first-byte device ID, and the individual device ID of second-byte ID is as followings: 10(hex) for MX25L512.The sequence of issuing RDID instruction is: CS# goes low→sending RDID instruction code→24-bits ID data out on SO→to end RDID operation can use CS# to high at any time during data out. (see Figure. 13)While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cy-cle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.(4) Read Status Register (RDSR)The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress. The sequence of issuing RDSR instruction is: CS# goes low→sending RDSR instruction code→Status Register data out on SO (see Figure. 14)The definition of the status register bits is as below:WIP bit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the de-vice will not accept program/erase/write status register instruction.BP1, BP0 bits. The Block Protect (BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed)SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protec-tion (WP#) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP# pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP1, BP0) are read only.Note: 1. See the table "Protected Area Sizes".2. The endurance cycles of protect bits are 100,000 cycles; however, the tW time out spec of protect bits isrelaxed as tW = N x 15ms (N is a multiple of 10,000 cycles, ex. N = 2 for 20,000 cycles) after 10,000 cycles on those bits.bit7bit6bit5bit4bit3bit2bit1bit0SRWD (status register write protect)0BP1 (level of protected block)BP0 (level of protected block)WEL (write enable latch)WIP (write inprogress bit)1=status register write disable(note 1)(note 1)1=write enable 0=not write enable 1=write operation 0=not in write operation(5) Write Status Register (WRSR)The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in ad-vance. The WRSR instruction can change the value of Block Protect (BP1, BP0) bits to define the protected area of memory (as shown in table 1). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM) is entered.The sequence of issuing WRSR instruction is: CS# goes low-> sending WRSR instruction code-> Status Register data on SI-> CS# goes high. (see Figure 15)The WRSR instruction has no effect on b6, b5, b4, b1, b0 of the status register.The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing, and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.Table 4. Protection ModesNote:1. As defined by the values in the Block Protect (BP1, BP0) bits of the Status Register, as shown in Table 1.As the table above showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM). Software Protected Mode (SPM):- When SRWD bit=0, no matter WP# is low or high, the WREN instruction may set the WEL bit and can changethe values of SRWD, BP1, BP0. The protected area, which is defined by BP1, BP0, is at software protected mode (SPM).- When SRWD bit=1 and WP# is high, the WREN instruction may set the WEL bit can change the values ofSRWD, BP1, BP0. The protected area, which is defined by BP1, BP0, is at software protected mode (SPM)ModeStatus register condition WP# and SRWD bit status Memory Software protectionmode (SPM)Status register can be written in (WEL bit is set to "1") andthe SRWD, BP0-BP1bits can be changed WP#=1 and SRWD bit=0, or WP#=0 and SRWD bit=0, or WP#=1 and SRWD=1The protected areacannotbe program or erase.Hardware protectionmode (HPM)The SRWD, BP0-BP1 of status register bits cannot bechangedWP#=0, SRWD bit=1The protected areacannotbe program or erase.Note: If SRWD bit=1 but WP# is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.Hardware Protected Mode (HPM):- When SRWD bit=1, and then WP# is low (or WP# is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP1, BP0 and hard-ware protected mode by the WP# to against data modification.Note: to exit the hardware protected mode requires WP# driving high once the hardware protected mode is entered. If the WP# pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP1, BP0.(6) Read Data Bytes (READ)The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing READ instruction is: CS# goes low→ sending READ instruction code→ 3-byte address on SI→ data out on SO→ to end READ operation can use CS# to high at any time during data out. (see Figure. 16) (7) Read Data Bytes at Higher Speed (FAST_READ)The FAST_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST_READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing FAST_READ instruction is: CS# goes low→ sending FAST_READ instruction code→ 3-byte address on SI→ 1-dummy byte address on SI→data out on SO→ to end FAST_READ operation can use CS# to high at any time during data out. (see Figure. 17)While Program/Erase/Write Status Register cycle is in progress, FAST_READ instruction is rejected without any im-pact on the Program/Erase/Write Status Register current cycle.(8) Sector Erase (SE)The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". A Write Enable (WREN) in-struction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 3) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.Address bits [Am-A12] (Am is the most significant address) select the sector address.The sequence of issuing SE instruction is: CS# goes low → sending SE instruction code→ 3-byte address on SI → CS# goes high. (see Figure 19)The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.(9) Block Erase (BE)The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". A Write Enable (WREN) in-struction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 3) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing BE instruction is: CS# goes low → sending BE instruction code→ 3-byte address on SI → CS# goes high. (see Figure 20)The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Block Erase (BE) instruction will not be executed on the page.(10) Chip Erase (CE)The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruc-tion must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 3) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not ex-ecuted.The sequence of issuing CE instruction is: CS# goes low→ sending CE instruction code→ CS# goes high. (see Figure 20)The self-timed Chip Erase Cycle time (tCE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Chip Erase cycle is in progress. The WIP sets 1 during the tCE timing, and sets 0 when Chip Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the chip is protected by BP1, BP0 bits, the Chip Erase (CE) instruction will not be executed. It will be only executed when BP1, BP0 all set to "0".(11) Page Program (PP)The Page Program (PP) instruction is for programming the memory to be "0". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Page Program (PP). If the eight least sig-nificant address bits (A7-A0) are not all 0, all transmitted data which goes beyond the end of the current page are programmed from the start address if the same page (from the address whose 8 least significant address bits (A7-A0) are all 0). The CS# must keep during the whole Page Program cycle. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed. If more than 256 bytes are sent to the device, the data of the last 256-byte is programmed at the request page and previous data will be disregarded. If less than 256 bytes are sent to the device, the data is programmed at the request address of the page without effect on other address of the same page.The sequence of issuing PP instruction is: CS# goes low→ sending PP instruction code→ 3-byte address on SI→at least 1-byte on data on SI→ CS# goes high. (see Figure 18)The self-timed Page Program Cycle time (tPP) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Page Program cycle is in progress. The WIP sets 1 during the tPP timing, and sets 0 when Page Program Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Page Program (PP) instruction will not be executed.(12) Deep Power-down (DP)The Deep Power-down (DP) instruction is for setting the device on the minimizing the power consumption (to enter-ing the Deep Power-down mode), the standby current is reduced from ISB1 to ISB2). The Deep Power-down mode requires the Deep Power-down (DP) instruction to enter, during the Deep Power-down mode, the device is not ac-tive and all Write/Program/Erase instruction are ignored. When CS# goes high, it's only in standby mode not deep power-down mode. It's different from Standby mode.The sequence of issuing DP instruction is: CS# goes low→ sending DP instruction code→ CS# goes high. (see Fig-ure 22)Once the DP instruction is set, all instruction will be ignored except the Release from Deep Power-down mode (RDP) and Read Electronic Signature (RES) instruction. (RES instruction to allow the ID been read out). When Power-down, the deep power-down mode automatically stops, and when power-up, the device automatically is in standby mode. For RDP instruction the CS# must go high exactly at the byte boundary (the latest eighth bit of instruction code been latched-in); otherwise, the instruction will not executed. As soon as Chip Select (CS#) goes high, a delay of tDP is required before entering the Deep Power-down mode and reducing the current to ISB2.(13) Release from Deep Power-down (RDP), Read Electronic Signature (RES)The Release from Deep Power-down (RDP) instruction is terminated by driving Chip Select (CS#) High. When Chip Select (CS#) is driven High, the device is put in the Stand-by Power mode. If the device was not previously in the Deep Power-down mode, the transition to the Stand-by Power mode is immediate. If the device was previously in the Deep Power-down mode, though, the transition to the Stand-by Power mode is delayed by tRES2, and Chip Select (CS#) must remain High for at least tRES2(max), as specified in Table 6. Once in the Stand-by Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.RES instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not the same as RDID instruction. It is not recommended to use for new design. For new deisng, please use RDID instruction. Even in Deep power-down mode, the RDP and RES are also allowed to be executed, only except the device is in progress of program/erase/write cycle; there's no effect on the current program/erase/ write cycle in progress.The sequence is shown as Figure 23,24.The RES instruction is ended by CS# goes high after the ID been read out at least once. The ID outputs repeat-edly if continuously send the additional clock cycles on SCLK while CS# is at low. If the device was not previously in Deep Power-down mode, the device transition to standby mode is immediate. If the device was previously in Deep Power-down mode, there's a delay of tRES2 to transit to standby mode, and CS# must remain to high at least tRES2(max). Once in the standby mode, the device waits to be selected, so it can be receive, decode, and execute instruction.The RDP instruction is for releasing from Deep Power Down Mode.(14) Read Electronic Manufacturer ID & Device ID (REMS)The REMS instruction is an alternative to the Release from Power-down/Device ID instruction that provides both the JEDEC assigned manufacturer ID and the specific device ID.The REMS instruction is very similar to the Release from Power-down/Device ID instruction. The instruction is initi-ated by driving the CS# pin low and shift the instruction code "90h" followed by two dummy bytes and one bytes address (A7~A0). After which, the Manufacturer ID for MXIC (C2h) and the Device ID are shifted out on the falling edge of SCLK with most significant bit (MSB) first as shown in figure 25. The Device ID values are listed in Table of ID Definitions on page 16. If the one-byte address is initially set to 01h, then the device ID will be read first and then followed by the Manufacturer ID. The Manufacturer and Device IDs can be read continuously, alternating from one to the other. The instruction is completed by driving CS# high.Table of ID Definitions:RDID Command manufacturer ID memory type memory density C22010RES Command electronic ID05REMS Command manufacturer ID device ID C205。

B2514 用户指南说明书

B2514用户指南目录第1章调整和使用显示器 (3)物品清单 (3)舒适和辅助功能 (4)安排您的工作区域 (4)放置显示器 (4)调整显示器图像 (5)使用直接访问控件 (5)使用On-Screen Display(OSD,屏幕显示)控件 (6)选择受支持的显示模式 (10)了解电源管理 (11)第2章参考信息 (12)显示器规格 (12)故障排除 (14)手动图像设置 (15)附录 A.服务和支持 (15)电话技术支持 (15)附录 B.电源线和电源适配器 (16)《废弃电器电子产品回收处理管理条例》提示性说明 (16)中国能源效率标识 (16)有害物质 (16)第1章调整和使用显示器物品清单本产品包装中应含有以下物品:1.信息页2.显示器3.电源适配器4.信号线(VGA线)5.支架6.底座本节介绍如何调整和使用此显示器。

舒适和辅助功能良好的人体工程学设计对于舒适地使用个人计算机非常重要。

应根据您的个人需要和从事的工作类型,合理安排您的工作场所和使用的设备。

此外,健康的工作习惯也能帮助您在使用计算机时实现最佳效率和舒适程度。

安排您的工作区域使用高度适宜的工作台面和足够的工作区域以便您舒适地工作。

根据您使用资料和设备的方式,合理安排您的工作区域。

将常用的资料整齐有序地放在工作区域中,将频繁使用的物品(如计算机鼠标或电话)放在便于操作的位置。

设备的放置和设备对工作姿势非常重要。

以下主题介绍如何优化设备以实现和保持良好的工作姿势。

放置显示器为舒适地观看显示器,在放置和调整计算机显示器时应考虑下列因素:●眼睛和显示器屏幕之间建议的观看距离是1.5x屏幕对角线。

在狭小的办公室符合此要求距离的解决方案包括:使桌子与墙壁或隔板保持一定距离以便给显示器留出空间,使用平板或较小的显示屏并使显示器处于桌子边角,或将键盘放到一个可调的抽屉板中打造更深的工作台面。

●显示器高度:放置显示器时,使您头部和颈部处于自然舒适(垂直或竖立)的位置。

MBR2545CT中文资料

MBR2535CT - MBR2560CTMBR2535CT - MBR2560CT, Rev. A©1999 Fairchild Semiconductor CorporationMBR2535CT - MBR2560CT, Rev. ATRADEMARKSACEx™CoolFET™CROSSVOLT™E 2CMOS TM FACT™FACT Quiet Series™FAST ®FASTr™GTO™HiSeC™The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROV AL OF FAIRCHILD SEMICONDUCTOR CORPORA TION.As used herein:ISOPLANAR™MICROWIRE™POP™PowerTrench™QS™Quiet Series™SuperSOT™-3SuperSOT™-6SuperSOT™-8TinyLogic™1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status Definition Advance InformationPreliminary No Identification Needed Obsolete This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.This datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Formative or In DesignFirst ProductionFull ProductionNot In ProductionDISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.。

MBRB1645中文资料

MBRB1635 THRU MBRB1660SCHOTTKY RECTIFIERReverse Voltage - 35 to 60 Volts Forward Current - 16.0 AmperesFEATURES♦Plastic package has Underwriters Laboratory Flammability Classifications 94V-0♦Metal silicon junction,majority carrier conduction♦Low power loss, high efficiency♦High current capability, low forward voltage drop ♦High surge capability♦Guardring for overvoltage protection♦For use in low voltage, high frequency inverters, free wheeling, and polarity protection applications ♦High temperature soldering in accordance with CECC 802 / Reflow guaranteedMECHANICAL DATACase:JEDEC TO-263AB molded plastic body Terminals:Lead solderable per MIL-STD-750,Method 2026Polarity:As marked Mounting Position :AnyWeight:0.08 ounce, 2.24 gramsMAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICSRatings at 25°C ambient temperature unless otherwise specified.SYMBOLS MBRB1635MBRB1645MBRB1650MBRB1660UNITSMaximum repetitive peak reverse voltage V RRM 35455060Volts Maximum working peak reverse voltage V RWM 35455060Volts Maximum DC blocking voltageV DC 35455060Volts Maximum average forward rectified current at T C =125°CI (AV)16.0Amps Peak repetitive forward current at T C =125°C(rated V R , sq.wave,20 KH Z ) I FRM 32.0Amps Peak forward surge current,8.3ms single half sine-wavesuperimposed on rated load (JEDEC Method)I FSM 150.0AmpsPeak repetitive reverse surge current (NOTE 1)I RRM1.00.5Amps Maximum instantaneous forward voltage at:(NOTE 2)I F =16A, T C =25°C V F 0.630.75VoltsI F =16A, T C =125°C 0.570.65Maximum instantaneous reverse current at rated DC blocking voltage T C = 25°CI R 0.2 1.0(NOTE 2)T C =125°C 40.050.0mA Voltage rate of change (rated V R )dv/dt 10,000V/µs Maximum typical thermal resistance (NOTE 3)R ΘJC 1.5°C/W Operating junction temperature range T J -65 to +150°C Storage temperature rangeT STG-65 to +175°CNOTES:(1) 2.0µs pulse width, f=1.0 KH Z(2) Pulse test: 300µs pulse width, 1% duty cycle (3) Thermal resistance from junction to case4/98TO-263ABDimensions in inches and (millimeters)NEW PRODUCTNEW PRODUCT NEW PRODUCT元器件交易网元器件交易网。

MBR和GBT

安装系统的时候涉及到MBR和GPT,现在也贴上来,供以后复习使用。

MBR 和 GPT 的问题已经走到了非常现实的阶段-3T硬盘开始普及。

MBR 由于对 3T 硬盘寻址无法支持,终于要开始被弃用了。

但仅仅只是“开始”,我感觉至少10年之内 MBR 还不会消失。

恐怕当GPT适应不了需求的时候,MBR才会消失。

一、MBR 的失误说“失误”牵强了一点。

我们不能要求当年只有5M的硬盘就扣出2M来放寻址信息。

计算机永远比你想象的要发展的快。

首先你要有一些基本的硬盘的MBR知识,如果你不熟悉,可以先在 wiki 看一看硬盘的基本结构。

在了解了磁道、柱面、扇区之后,再看下面的 MBR 结构就很了然了:表 1.MBR 永远占用了第一个扇区,通常为512bytes大小。

在这512bytes中被MBR本身的程序用去了446bytes。

于是,真正描述分区信息的就只有 64 bytes。

而根据4个主分区的设计,每一个分区能用到的只有 16bytes. 那么!这16bytes是如何工作的?表 2.在表2中,有2个“开始位置”,我们分开理解。

硬盘的历史过程中,第一个遇到的问题就是 8G 瓶颈。

这就是因为在 CHS 描述方式中,描述起点和终点均为3个 byte。

我们假设是 FF FF FF ,所以是 16*16*16*16*16*16*512=8589934592 这就是 8G 瓶颈的由来了。

但是今天 CHS 方式几乎已经不用了。

后面还有 4 个 bytes 的“启始” 是给 LPA 方式用的。

他的极限就是 8589934592 * 256 =2199023255552 这就是 2T 的限制由来了。

在硬盘容量的历史中,有很多因素决定了它的限制。

BIOS,ATA(IDE),文件系统。

百度上的这篇文章简单的介绍了各个阶段的限制。

二、GPT 的思路GPT (GUID Partition Table)属于 EFI 方案中的一部分。

虽然很早就开始制定这个标准,但到今天,还是有很多系统不支持 GPT。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© Semiconductor Components Industries, LLC, 2005 September, 2005 − Rev. 61Publication Order Number:MBRB2515L/DMBRB2515LPreferred Device SWITCHMODE tPower RectifierORing Function DiodeD2PAK Surface Mount Power PackageThe D2PAK Power Rectifier employs the Schottky Barrier principle in a large metal−to−silicon power diode. State−of−the−art geometry features epitaxial construction with oxide passivation and metal overlay contact. Ideally suited for use in low voltage, high frequency switching power supplies, free wheeling diodes, and polarity protection diodes.Features•Guardring for Stress Protection•Low Forward V oltage•100°C Operating Junction Temperature•Epoxy Meets UL 94 V−0 @ 0.125 in•Short Heat Sink Tab Manufactured − Not Sheared •Similar in Size to the Industry Standard TO−220 Package •Pb−Free Packages are AvailableMechanical Characteristics:•Case: Epoxy, Molded, Epoxy Meets UL 94 V−0•Weight: 1.7 Grams (Approximately)•Finish: All External Surfaces Corrosion Resistant and Terminal Leads are Readily Solderable•Lead and Mounting Surface Temperature for Soldering Purposes: 260°C Max. for 10 Seconds•Device Meets MSL1 Requirements•ESD Ratings:Machine Model, C (>400 V)Human Body Model, 3B (>8000 V)MAXIMUM RATINGSRating Symbol Value UnitPeak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRMV RWMV R15VAverage Rectified Forward Current(Rated V R, T C = 90°C)I F(AV)25APeak Repetitive Forward Current(Rated V R, Square Wave,20 kHz, T C = 100°C)I FRM30ANon−Repetitive Peak Surge Current(Surge Applied at Rated Load ConditionsHalfwave, Single Phase, 60 Hz)I FSM150A Storage Temperature Range Tstg−65 to +150°C Operating Junction Temperature T J100°CVoltage Rate of Change (Rated V R)dv/dt10,000V/m s Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits areexceeded, device functional operation is not implied, damage may occur and reliability may be affected.Preferred devices are recommended choices for future use and best overall value.2THERMAL CHARACTERISTICSCharacteristicSymbol Value Unit Thermal Resistance,−Junction−to−Case−Junction−to−Ambient (Note 1)R q JC R q JA1.050°C/W1.When mounted using minimum recommended pad size on FR−4 board.ELECTRICAL CHARACTERISTICSCharacteristicSymbol Value Unit Maximum Instantaneous Forward Voltage (Note 2)(i F = 19 Amps, T J = 70°C)(i F = 25 Amps, T J = 70°C)(i F = 25 Amps, T J = 25°C)v F0.380.420.45VMaximum Instantaneous Reverse Current (Note 2)(Rated dc Voltage, T J = 70°C)(Rated dc Voltage, T J = 25°C)I R20015mA2.Pulse Test: Pulse Width = 300 m s, Duty Cycle ≤2.0%.ORDERING INFORMATIONDevicePackage Shipping †MBRB2515L D 2PAK 50 Units / Rail MBRB2515LG D 2PAK (Pb−Free)50 Units / Rail MBRB2515LT4D 2PAK 800 Units / Tape & Reel MBRB2515LT4GD 2PAK (Pb−Free)800 Units / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.Figure 3. Typical Forward Power DissipationFigure 4. Current Derating, Case507.02.05.01.00I F(AV), AVERAGE FORWARD CURRENT (AMPS)25105.00T C , CASE TEMPERATURE (°C)656070i F , I N S T A N T A N E O U S F O R W A R D C U R R E N T (A M P SP 0.70.50.31020304075801000.20.1, A V E R A G E F O R W A R D P O W E R D I S S I P A T I O N (W A T T S )F (A V ) 3.02015304035859095102030 5.01525353PACKAGE DIMENSIONSD 2PAK 3CASE 418B−04ISSUE JVARIABLEVIEW W−WVIEW W−WVIEW W−W123STYLE 3:PIN 1.ANODE2.CATHODE3.ANODE4.CATHODE*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ǒmm inchesǓSCALE 3:1SWITCHMODE is a trademark of Semiconductor Components Industries, LLC.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息:ONSEMIMBRB2515LT4G MBRB2515LG MBRB2515LT4。